# (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3729953号 (P3729953)

(45) 発行日 平成17年12月21日 (2005.12.21)

(24) 登録日 平成17年10月14日 (2005.10.14)

| (51) Int.C1. <sup>7</sup> | F 1        |      |

|---------------------------|------------|------|

| HO1L 27/14                | HO1L 27/14 | K    |

| HO1L 21/336               | HO1L 27/12 | A    |

| HO1L 27/12                | HO1L 27/14 | C    |

| HO1L 27/146               | HO1L 29/78 | 612Z |

| HO1L 29/786               |            |      |

請求項の数 5 (全8頁)

(73)特許権者 590000248 (21) 出願番号 特願平8-321566 (22) 出願日 平成8年12月2日(1996.12.2) コーニンクレッカ フィリップス エレク (65) 公開番号 特開平10-163463 トロニクス エヌ ヴィ (43) 公開日 平成10年6月19日 (1998.6.19) Koninklijke Philips 審査請求日 平成15年12月1日 (2003.12.1) Electronics N. V. オランダ国 5621 ベーアー アイン ドーフェン フルーネヴァウツウェッハ 1 Groenewoudseweg 1, 5 621 BA Eindhoven, T he Netherlands

(74) 代理人 100087789 弁理士 津軽 進

最終頁に続く

### (54) 【発明の名称】 TFTアレイ基板とその製法

# (57)【特許請求の範囲】

### 【請求項1】

ガラス基板上に共通の金属材料により形成されたソース電極、ソースバス、ドレイン電極及び蓄積容量電極と、

前記ソース電極とドレイン電極との間の領域及びその領域の近傍に形成された a - S i よりなる半導体層と、

その半導体層のソース電極及びドレイン電極との間の界面に形成された $n^+$  a - Siよりなるオーミックコンタクト層と、

前記半導体層、ソース電極、ソースバス、ドレイン電極及び蓄積容量電極を覆うように 一面に形成された第1の絶縁膜と、

前記第1の絶縁膜上に共通の金属材料により形成されたゲート電極、ゲートバス及び第 1のチャージコレクタと、

前記ゲート電極、ゲートバス及び中央部を除く第1のチャージコレクタ上を覆うように 一面に形成された第2の絶縁膜と、

前記第2の絶縁膜及び第1のチャージコレクタ上に形成されたITOよりなる第2チャージコレクタと、

### を具備し、

前記第1のチャージコレクタは、前記第1の絶縁膜に形成されたコンタクトホールを通じて前記ドレイン電極に接続されていることを特徴とするTFTアレイ基板。

### 【請求項2】

前記ゲート電極、ゲートバス及び第1のチャージコレクタが、A1層の上下に他のメタル層を配した3層膜か、又はA1層の上に他のメタル層を配した2層膜で形成されていることを特徴とする請求項1記載のTFTアレイ基板。

### 【請求項3】

前記ゲート電極、ゲートバス及び第1のチャージコレクタ上に形成された絶縁膜が感光性絶縁膜であることを特徴とする請求項1記載のTFTアレイ基板。

### 【請求項4】

ガラス基板上にソース電極、ソースバス、ドレイン電極及び蓄積容量電極を共通の金属材料により形成し、

前記ソース電極とドレイン電極との間の領域及びその領域の近傍にa - Siよりなる半導体層を形成すると共に、その半導体層のソース電極及びドレイン電極との間の界面にn \* a - Siよりなるオーミックコンタクト層を形成し、

前記半導体層、ソース電極、ソースバス、ドレイン電極及び蓄積容量電極を覆うように 一面に第1の絶縁膜を形成した後、ドレイン電極上にコンタクトホールを形成し、

前記第1の絶縁膜上にゲート電極、ゲートバス及び第1チャージコレクタを共通の金属材料により形成すると共に、第1のチャージコレクタを前記コンタクトホールを通じて前記ドレイン電極に接続し、

前記ゲート電極、ゲートバス及び中央部を除く第1チャージコレクタ上を覆うように感 光性絶縁膜を一面に形成し、

前記感光性絶縁膜及び第1チャージコレクタ上にITOよりなる第2チャージコレクタ 20 を形成することを特徴とするTFTアレイ基板の製法。

#### 【請求項5】

前記ゲート電極、ゲートバス及び第1のチャージコレクタを、A1層の上下に他のメタル層を配した3層膜か、又はA1層の上に他のメタル層を配した2層膜で形成することを特徴とする請求項4記載のTFTアレイ基板の製法。

## 【発明の詳細な説明】

# [0001]

### 【発明の属する技術分野】

近年、レントゲン写真に代って、X線を生体に照射してリアルタイムで生体内を診断する X線イメージセンサが開発されている。この発明は、このX線メイージセンサに用いられるTFT(薄膜トランジスタ)アレイ基板に関し、特に製造工程数の縮減に関する。

# [0002]

### 【従来の技術】

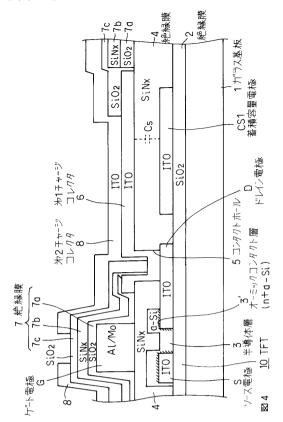

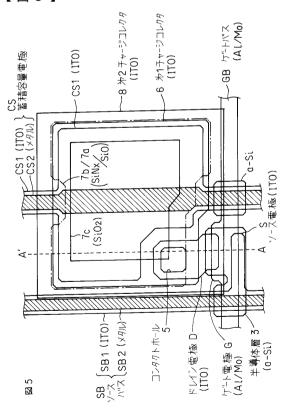

X線イメージセンサは、生体を透過又は反射したX線を受光する表面膜状部と、その下に重ねて配されるTFTアレイ基板を有する。TFTアレイ基板にはTFTドットマトリクスLCDの場合と同様に、TFT及び各画素がマトリクス状に配列されている。従来のTFTアレイ基板を図4、図5に示し、その製造工程を順に説明する。

### [0003]

- (1)ガラス基板1の内面に必要に応じSiO。などの絶縁膜2をコートする。

- (2) ITOを一面に着膜し、ホトリソグラフィ技術を用いたエッチング処理(以下ホト 40 リソ・エッチングと言う)によりソース電極 S、ソースバス SB1、ドレイン電極 D、蓄積容量電極 CS1を形成する。

## [0004]

- (3) モリブデン (Mo) などのメタルを一面に着膜した後、ホトリソ・エッチングにより、ソースバスSB2、蓄積容量電極CS2を形成する。

- (4)ソース電極S及びドレイン電極Dの表面にP(燐)処理を施す。

- (5) a Si(アモルファスシリコン)を一面に着膜し、ホトリソ・エッチングにより 半導体層3を形成すると共にソース電極S及びドレイン電極Dとの界面にn \* a - Siよ り成るオーミックコンタクト層3 を形成する。

## [0005]

(6)SiN $_{x}$  などの絶縁膜 4 を一面に着膜した後、ホトリソ・エッチングによりコンタクトホール 5 を形成する と共に、ガラス基板の周辺のゲートバス G B、ソースバス S B 及び蓄積容量電極 C S の各端末(端子を形成する部分)上の絶縁膜 4 を除去する。

(7) ITOを一面に着膜した後、ホトリソ・エッチングにより第1チャージコレクタ6を形成する。

(8) AlとMoの2層膜(Alが上)を一面に着膜した後、ホトリソ・エッチングによりゲート電極G、ゲートバスGBを形成する。

### [0006]

(9)SiO $_2$  膜 7 a とSiN $_x$  膜 7 b とより成る 2 層膜を一面に着膜した後、ホトリソ・エッチングにより第 1 チャージコレクタ 6 上の大部分の 2 層膜 7 a , 7 b を除去する。(10)SiO $_2$  膜 7 c を一面に着膜した後、ホトリソ・エッチングにより第 1 チャージコレクタ 6 の中央部上のSiO $_2$  膜 7 c を除去する。

### [0007]

(11) ITOを一面に着膜し、ホトリソ・エッチングにより第2チャージコレクタ8を 形成する。

(12) TFTアレイ基板の周辺に延長されたゲートバスGB、ソースバスSB(SB1, SB2より成る)及び蓄積容量電極CS(CS1, CS2より成る)の各端末上の絶縁膜7a,7b,7cを2回のホトリソ・エッチングにより除去して、各端末(接続端子となるものであるが図示していない)を露出させる。

### [0008]

その後、セレン等のX線照射により電荷を発生させる層がチャージコレクタ上に形成される。

X線イメージセンサにX線が照射されると、TFTアレイ基板の各画素に対応する第2チャージコレクタ8上に電荷が蓄積される。各行のゲートバスGBを順に走査してTFTをオンに制御することにより、各列のソースバスSBの端末に接続された検出手段により各画素の信号電荷を検出し、その検出値に対応するデータを表示器に表示させることにより、リアルタイムで、X線を照射された生体内の映像を診断することができる。

### [0009]

# [0010]

### 【発明が解決しようとする課題】

TFTアレイ基板を製造する上で、時間の掛かる工程はホトリソ・エッチング工程(ホト 工程とも言う)である。従来の技術では図3に示すように11工程にもなる多くのホトエ 程を必要としていたために、生産性が低く、製造コストが大きくなる問題があった。この 発明は、ホトリソ・エッチング工程数を減らして生産性を向上させることを目的としてい る。

# [0011]

### 【課題を解決するための手段】

(1)請求項1のTFTアレイ基板は、ガラス基板上にソース電極、ソースバス、ドレイン電極及び蓄積容量電極が共通の金属材料により形成され、ソース電極とドレイン電極の間の領域及びその領域の近傍にa‐Siより成る半導体層が形成され、その半導体層のソース電極及びドレイン電極との界面に、n<sup>+</sup> a‐Siより成るオーミックコンタクト層が形成される。半導体層、ソース電極、ソースバス、ドレイン電極及び蓄積容量電極を覆うように一面に絶縁膜4が形成され、その絶縁膜上にゲート電極、ゲートバス及び第1チャージコレクタが共通の金属材料により形成される。

## [0012]

40

10

20

ゲート電極、ゲートバス及び第1チャージコレクタ(しかし第1チャージコレクタの中央部を除く)上を覆うように、絶縁膜が一面に形成され、その絶縁膜及び第1チャージコレクタ上に第2チャージコレクタがITOにより形成される。第1チャージコレクタは絶縁膜4に形成されたコンタクトホールを通じてドレイン電極に接続される。

[0013]

- (2)請求項2の発明は、前記(1)において、ゲート電極、ゲートバス及び第1チャージコレクタが、A1層の上下に他のメタル層を配した3層膜か、またはA1層の上に他のメタル層を配した2層膜で形成される。

- (3)請求項3の発明は前記(1)において、ゲート電極、ゲートバス及び第1チャージコレクタ上に形成された絶縁膜が感光性絶縁膜とされる。

[0014]

- (4)請求項4の発明は、請求項1のTFTアレイ基板を製法としてクレイムしたものである。

- (5)請求項5の発明は、請求項2のTFTアレイ基板を製法としてクレイムしたものである。

[0015]

【発明の実施の形態】

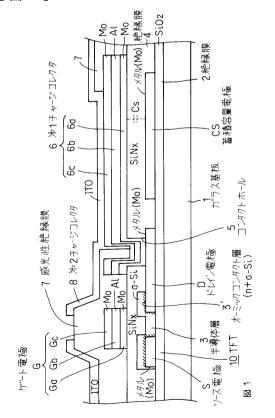

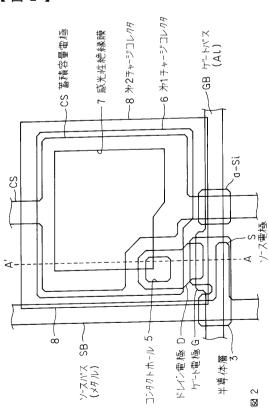

この発明の実施例を図1、図2に、図4、図5と対応する部分に同じ符号を付けて示し、 工程順に説明する。

(1)ガラス基板1上に必要に応じSiO。などの絶縁膜2を一面に着膜する。

[0016]

- (2)例えばモリブデンなどのメタルを一面に着膜して、ホトリソ・エッチングにより、 ソース電極S、ソースバスSB、ドレイン電極D、蓄積容量電極CSを形成する。

[0017]

- (4) SiN $_{x}$  などの絶縁膜 4を一面に着膜した後、ホトリソ・エッチングによりコンタクトホール 5を形成する。

- (5) 例えばMo/Al/MoまたはMo/Al(Moが上)より成る多層金属膜を一面に着膜した後、ホトリソ・エッチングによりゲート電極G、ゲートバスGB及び第1チャージコレクタ6を形成する。第1チャージコレクタ6はコンタクトホール5を通じてドレイン電極Dに接続される。

[0018]

- (6)感光性アクリル樹脂などの感光性絶縁膜7を一面に着膜した後、ホトリソにより第1チャージコレクタ6の中央部上の絶縁膜7を除去する。

- (7) ITOを一面に着膜した後、ホトリソ・エッチングにより第2チャージコレクタ8を形成する。

- (8) TFTアレイ基板の周辺に延長されたゲートバスGB、ソースバスSB及び蓄積容 40量電極CSの各端末(端子として使用される)上の感光性絶縁膜<u>7を</u>ホトリソ・エッチングにより除去して、各端末を露出させる。

[0019]

上述したこの発明の製法では必要なホトリソ・エッチング工程(ホト工程)は図3に示すように7工程となり、従来より4工程少くなる。以下、この工程の縮減について詳細に説明する。

1 従来はa - SiのITOとの界面にオーミックコンタクト層 3 を形成する技術しか持たなかったので、ソース電極 S 及びドレイン電極 D の少くともその表面側はITOで形成する必要があった。そのため、ソース電極 S、ソースバス S B 1、ドレイン電極 D、蓄積容量電極 C S 1を I T O で形成し、導電性を更によくする必要のあるソースバス S B

10

20

30

や蓄積容量電極 C S は、 I T O の上にメタル製の S B 2 や C S 2 を形成する必要があり、このため 2 つのホト工程を必要としていた。しかし a - S i のメタルとの界面にオーミックコンタクト層を形成する技術がこの発明者の一人によって既に提案され、適用可能となっているので、この発明ではこの新しい技術を用いることにより、これらの電極を全て M o などのメタルで形成することによってホト工程を 1 工程縮減している。

### [0020]

2 従来では、第1チャージコレクタ6は、ITOより成る第2チャージコレクタ8と接触させることから、ゲート電極の材料となっているA1を用いることができなかった。その理由は、A1とITOがある現像液にさらされるとA1が腐食される恐れがあること、A1とITOが接触しているとITO中の酸素(O)によってA1が酸化される恐れがあることからである。そのため、第1チャージコレクタ6はゲート電極6と同じA1を用いることができず、ITOを用いてゲート電極Gとは別工程をとっていた。

### [0021]

しかし、この発明では第1チャージコレクタ6を例えばMo/A1/MoまたはMo/A 1(Moが上)の多層金属膜で形成することによってITOより成る第2チャージコレクタ8とA1が接触しないようにすると共に、ゲート電極G及びゲートバスGBも第1チャージコレクタ6と同じ多層金属膜を用いることによって、同一ホト工程で形成し、1工程を縮減している。

#### [0022]

### [0023]

4 TFTアレイ基板の周辺のソースバス、ゲートバス及び蓄積容量電極の各端末にそれぞれ電極端子を形成するために、これら端末上の絶縁物を除去する必要がある。従来は各端末上の絶縁膜7は3層構造であり、1つのホト工程で除去するのは困難であるので、同じホトマスクを用いたホト工程を2回繰返していた。この発明では、各端末上の絶縁膜7は感光性アクリル樹脂などの1層で充分耐えるようにしたので、1つの工程で除去することができ、1ホト工程を縮減している。

### [0024]

# 【発明の効果】

1 以上述べたように、この発明では、メタル製のソース電極S及びドレイン電極Dと接する半導体層3の界面にオーミックコンタクト層3 を形成する技術を用いることによって、これらの電極及びソースバスSB、蓄積容量電極CSを共通の金属材料を用いて同じホト工程で形成できる。

## [0025]

2 この発明では、第1チャージコレクタ6を、第2チャージコレクタ(ITO)6と 40 A 1 が直接接触しないような多層金属膜(例えば A 1 を M o でサンドイッチする)を用いると共に、ゲート電極 G、ゲートバス G B も同じ多層膜を用いることによって同一ホト工程で形成できる。

3 ゲート電極 G、ゲートバス G B 上に一層の感光性絶縁膜 7 を用いることによって、 絶縁膜 7 を除去するホト工程を 1 工程のみにすることができる。

# [0026]

4 絶縁膜 7 を一層とすることによって、<u>1回の</u>ホト工程で、端子として使用するソースバス端末、ゲートバス端末及び蓄積容量電極端末を露出させることができる。 以上により、この発明ではホト工程を従来より 4 工程縮減することが可能となり、生産性を大幅に向上できる。 10

30

20

# [0027]

5 感光性絶縁膜 7 を使用することによって、ソース入力容量(ソースバス S B と第 2 チャージコレクタ 8 との間の容量)を低減することが可能となり、ソース入力容量を通じてのるソースバス S B のノイズレベルが下がり、 X 線照射量を減らして、生体に与える影響をより少なくすることができる。

### 【図面の簡単な説明】

- 【図1】この発明の実施例を示す図で、図2のA-A 断面図。

- 【図2】この発明の実施例を示す平面図。

- 【図3】この発明のTFTアレイ基板に必要なホト工程を従来と比較して示した図。

- 【図4】従来のTFTアレイ基板を示す図で、図5のA-A 断面図。

- 【図5】従来のTFTアレイ基板の平面図。

# 【図1】

# 【図2】

# 【図3】

|   | -          | 0, S, SB1, CS1 (ITO)                 |                                |

|---|------------|--------------------------------------|--------------------------------|

|   | 2          | SB2, CS2 (メタル)                       | (1/8,58 (≠9/V)                 |

|   | 3          | * *                                  | 半導体層 (0-5:1                    |

|   | 4          | コンタクトホール                             | 7.871 tt-11/                   |

|   | 5          | ************************************ |                                |

|   | 9          | G, 7"- F/1" X(AL/Mn)                 | 6, か1チャージコレクタ                  |

|   | 7          | Si Nx/SiO2 を除去                       |                                |

|   | 8          | Si 02 除去                             | ] 歇尤旺稅祿膜7除去                    |

|   | 6          | か2 チャーション48 (ITO)                    | か2チャージョレルタ (ITO)               |

|   |            | ケート/パス端子(AL)                         | 】 丁"- HV" ス 如 子                |

|   | <br>:<br>: | /- / / / / / / / / / / / / / /       | <b>〉ソ−スパス加子</b><br>  装積容 暑 は3. |

| - | 工程数        | 11                                   |                                |

# 【図4】

# 【図5】

# フロントページの続き

(72)発明者 鵜飼 育弘

兵庫県神戸市西区高塚台4-3-1 ホシデン株式会社 開発技術研究所内

(72) 発明者 湯川 禎三

兵庫県神戸市西区高塚台4-3-1 ホシデン株式会社 開発技術研究所内

(72)発明者 新庄 正路

兵庫県神戸市西区高塚台4-3-1 ホシデン株式会社 開発技術研究所内

# 審査官 恩田 春香

(56)参考文献 特開昭64-68968(JP,A)

特開平2-83939(JP,A)

特開平5-173183(JP,A)

特開平4-336530(JP,A)

(58)調査した分野(Int.CI.<sup>7</sup>, DB名)

H01L 27/14 - 27/148

H01L 29/786

G02F 1/136 - 1/1368