# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-38306 (P2009-38306A)

(43) 公開日 平成21年2月19日(2009.2.19)

(51) Int.Cl.

FL

テーマコード (参考)

HO1L 21/8242 (2006, 01) HO1L 27/108 (2006.01) HO1L 27/10 681C

5F083

#### 審査請求 未請求 請求項の数 3 OL (全 12 頁)

| (21) 出願番号<br>(22) 出願日 | 特願2007-203316 (P2007-203316)<br>平成19年8月3日 (2007.8.3) | (71) 出願人          | 500174247<br>エルピーダメモリ株式会社 |

|-----------------------|------------------------------------------------------|-------------------|---------------------------|

| , ,                   |                                                      |                   | 東京都中央区八重洲2-2-1            |

|                       |                                                      | (74)代理人           |                           |

|                       |                                                      | ( -) ( -)         | 弁理士 宮崎 昭夫                 |

|                       |                                                      | (74)代理人           | 100106138                 |

|                       |                                                      | (* 2)   (* 2)     | 弁理士 石橋 政幸                 |

|                       |                                                      | (74)代理人           | 100127454                 |

|                       |                                                      | (0.2) (0.2)       | 弁理士 緒方 雅昭                 |

|                       |                                                      | (72)発明者           | 成并 誠司                     |

|                       |                                                      | (12) ) 2 - 91 - 1 | 東京都中央区八重洲2-2-1 エルピー       |

|                       |                                                      |                   | ダメモリ株式会社内                 |

|                       |                                                      | (72)発明者           |                           |

|                       |                                                      | (12) 75-71        | 東京都中央区八重洲2-2-1 エルピー       |

|                       |                                                      |                   | ダメモリ株式会社内                 |

|                       |                                                      |                   | 最終頁に続く                    |

|                       |                                                      | 1                 | 取が 良 (こが) \               |

# (54) 【発明の名称】半導体記憶装置

# (57)【要約】

【課題】チップサイズを削減することができ、かつ、安 定した動作を得ることのできる、半導体記憶装置を提供 する。

【解決手段】情報として電荷が蓄積される複数のメモリ セルを備える、アレイ状に配置された複数のマット10 と、一端が外部電源から供給される電圧を降圧または昇 圧する内部電源に共通に接続された複数の電源線30と を有する半導体記憶装置であって、各電源線30は、複 数のマット10が形成された領域上に、一定方向に延伸 するように配線されており、各電源線30の他端が端マ ット10 a上で共通に接続されている。

# 【選択図】図1

### 【特許請求の範囲】

# 【請求項1】

情報として電荷が蓄積される複数のメモリセルを備える、アレイ状に配置された複数のマットと、

一端が外部電源から供給される電圧を降圧または昇圧する内部電源に共通に接続された複数の電源線と、を有し、

前記複数の電源線は、前記複数のマットが形成された領域上に、一定方向に延伸するように配線されており、該電源線の他端が、前記複数のマットのうちの前記一定方向において最も端に位置するマット上で共通に接続されている、ことを特徴とする、半導体記憶装置。

【請求項2】

前記複数のマットのそれぞれは、前記複数のメモリセルから情報を読み出すための複数のセンスアンプを有し、

前記複数の電源線が、前記複数のセンスアンプに駆動電圧を供給する電源線である、請求項1に記載の半導体記憶装置。

#### 【請求項3】

前記端に位置するマット上に形成された電源線の幅が端以外のマット上に形成された電源線の幅より大きい、請求項1または2に記載の半導体記憶装置。

【発明の詳細な説明】

### 【技術分野】

[ 0 0 0 1 ]

本発明は、DRAM (Dynamic Random Access Memory) に代表される半導体記憶装置に関する。

#### 【背景技術】

### [0002]

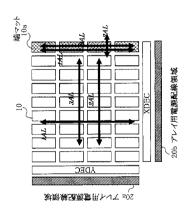

それぞれが独立した動作を行う複数のバンクから構成されるDRAMが知られている( 特許文献1参照)。図6に、DRAMのレイアウトを示す。

# [ 0 0 0 3 ]

図6を参照すると、DRAMは、4つの独立した動作を行うバンクB0~B3からなる。バンクB0~B3の各々には、ワード線(WL)を選択するためのXデコーダ(XDEC)と、ビット線(BL)を選択するためのYデコーダ(YDEC)が設けられている。バンクB0~B3の各々は、行列状に配置された複数のマットを有する。バンクB0~B3の各々では、行方向(ビット線の延伸方向)に33個、列方向(ワード線の延伸方向)に16個のマットが配置されている。

# [0004]

マット10は、メモリセルアレイ、センスアンプ部およびサブワードドライバを有する。メモリセルアレイは、一定の間隔で平行に配線された複数のビット線と、これらビット線と交差する、一定の間隔で平行に配線されたワード線と、これらビット線とワード線の各交差部に形成された、スイッチ素子と容量素子とからなる複数のメモリセルとを有する

[00005]

センスアンプ部は、ビット線毎に設けられた複数のセンスアンプからなり、メモリセルアレイの両側に配置されている。サブワードドライバは、ワード線毎に設けられた複数の駆動トランジスタからなり、メモリセルアレイを挟むように上下に配置されている。これらセンスアンプ部およびサブワードドライバは、隣接するマット10間で共用される。

### [0006]

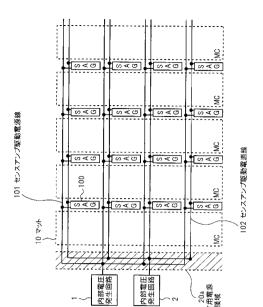

バンクを構成する、複数のマットからなるメモリセルアレイ部上には、各マットのセンスアンプに電源を供給するためのセンスアンプ駆動電源線が形成される。図 7 に、センスアンプ駆動電源線のレイアウトを示す。

### [0007]

10

20

40

30

図 7 に示すレイアウトは、図 6 に示したバンク B 1 の行方向に配置された複数のマット 1 0 と、これらマット 1 0 上に形成されるセンスアンプ駆動電源線とを模式的に示したものである。なお、図 7 では、マットの数を 5 つに省略している。

#### [00008]

隣接するマット10の間には、4つのセンスアンプグループ(SAG)100が列方向に配置されている。これらSAG100は、センスアンプ部を4つに分割したものである。センスアンプには、駆動電圧として第1の電圧(ハイレベル)と第2の電圧(ロウレベル)が供給される。センスアンプは、これら電圧に基づいてメモリセルに保持した電荷の情報判定を行う。

# [0009]

第1の電圧をセンスアンプに供給するためのセンスアンプ駆動電源線101および第2の電圧をセンスアンプに供給するためのセンスアンプ駆動電源線102がそれぞれ、SAG100の行ごとに設けられている。

# [0010]

各センスアンプ駆動電源線101は、一端がアレイ電源配線領域20aにおいて共通に接続され、そこから行方向に延伸するように形成されている。また、各センスアンプ駆動電源線101は、行方向に並ぶマット10を全て貫通するように形成されており、その他端はどこにも接続されていない。

### [0011]

各センスアンプ駆動電源線102も同様に、一端がアレイ電源配線領域20aにおいて 共通に接続され、そこから行方向に延伸するように形成されている。また、各センスアン プ駆動電源線102も、行方向に並ぶマット10を全て貫通するように形成されており、 その他端はどこにも接続されていない。

#### [ 0 0 1 2 ]

内部電圧発生回路1、2はそれぞれ、不図示の外部電源から供給された電圧を降圧して第1、第2の電圧を発生する。内部電圧発生回路1には、各センスアンプ駆動電源線10 1が接続され、内部電圧発生回路2には、各センスアンプ駆動電源線102が接続されている。

# [0013]

バンクを構成するメモリセルアレイ部に周囲には、メモリセルに対するデータの書き込みや読み出しを行う際のアドレスを指定する、不図示のXデコーダ(XDEC)およびYデコーダ(YDEC)が配置されており、内部電圧発生回路1、2は、メモリセルアレイ部の、Yデコーダが配置された側に形成される。アレイ電源配線領域20aは、内部電圧発生回路1、2が形成される領域とYデコーダが配置される領域の間に形成される。

# [ 0 0 1 4 ]

以上は、センスアンプの駆動電源線についてのレイアウトの説明であるが、サブワードドライバを駆動する電源線も、センスアンプの駆動電源線の場合と同様なレイアウトとされる。この場合、内部電圧発生回路は、外部電源から供給される電圧を昇圧したり、場合によっては、負電圧を生成したりして、サブワードドライバを駆動するための電圧を生成する。

【特許文献1】特開平11-007762号公報

### 【発明の開示】

【発明が解決しようとする課題】

# [0015]

外部電源からの電圧を内部電圧生成回路で降圧してセンスアンプの駆動電圧を得る場合、センスアンプ駆動電源線の抵抗が高いと、センスアンプの負荷容量が極めて大きいため、センスアンプ駆動の際にセンスアンプ駆動電源線に供給される電圧が一時的に大きく低下する場合がある。この結果、センスアンプによる信号レベルの判定処理に時間がかかり、場合によっては、所定の時間に判定処理が終了しないことになる。判定処理が所定の時間に終了しないと、メモリセルからの信号読み出しを正確に行うことができなくなり、D

10

20

30

40

RAMの動作が不安定になる。したがって、DRAMの安定した動作を実現するためには、センスアンプ駆動電源線の低抵抗化の対策が必須とされている。

### [0016]

これまで、バンクを構成するメモリセルアレイ部の、マット(メモリセルアレイ)とセンスアンプ駆動電源線のレイアウト設計では、レイアウト設計システムで使用するマスクデータ量を削減することを目的として、通常、1つのレイアウトパターン(メモリセルのブロックと配線のブロックの組み合わせ)の繰り返しで、メモリセルとセンスアンプ駆動電源線のレイアウトを作成する。このレイアウトによれば、センスアンプ駆動電源線のパターンも含め、ビット線、ワード線等メモリセル近傍に配置された各種配線のパターンについて各マットを完全同一にすることができ、メモリセルの読み出し書き込み動作時の各種配線間のクロストークノイズも同一にすることができる。このことは、各マットでクロストークノイズの最適化設計が容易となるため半導体装置全体のノイズ耐性も向上する。このようにして作成したメモリセルとセンスアンプ駆動電源線のレイアウトが、図7に示したレイアウトである。

# [0017]

しかし、図7に示したレイアウトでは、センスアンプ駆動電源線101、102の他端はどこにも接続されていないため、センスアンプ駆動電源線101、102の抵抗値が大きくなる。このため、図7に示したレイアウトを有するDRAMでは、センスアンプ駆動電源線の抵抗値が大きいために、DRAMの動作が不安定になる、という問題が生じる。

# [0018]

なお、図 7 に示したレイアウトにおいて、センスアンプ駆動電源線 1 0 1 、 1 0 2 の他端を共通に接続することで、センスアンプ駆動電源線 1 0 1 、 1 0 2 の抵抗値を下げることができる。しかし、この場合は、以下のような問題が生じる。

#### [0019]

図 8 に、センスアンプ駆動電源線 1 0 1 の他端を共通に接続した場合のレイアウトを模式的に示す。

# [0020]

同じレイアウトパターンの繰り返しで、マット10(メモリセルアレイ)とセンスアンプ駆動電源線101のレイアウトを作成した場合、センスアンプ駆動電源線101は、行方向に並ぶマット10を全て貫通する状態とされる。この場合、センスアンプ駆動電源線101の他端は、端のマット10aよりもさらに外側に位置することとなる。このため、センスアンプ駆動電源線101の他端を共通に接続するアレイ用電源配線領域20cは、端のマット10aの列よりも、さらに外側(メモリセルアレイ部の領域の外側)に形成される。つまり、メモリセルアレイ部の両側には、アレイ用電源配線領域20a、20cが形成されることになる。

# [0021]

アレイ用電源配線領域がメモリセルアレイ部の両側に設けられるDRAMにおいては、 隣接するメモリセルアレイ部の間の領域において、一方のメモリセルアレイ部のアレイ用 電源配線領域20aと他方のメモリセルアレイ部のアレイ用電源配線領域20cが形成されることになる。このように、隣接するメモリセルアレイ部の間に2つのアレイ用電源配 線領域を形成することは、チップサイズの削減の妨げとなる。

# [0022]

本発明の目的は、上記問題を解決し、チップサイズを削減することができ、かつ、安定した動作を得ることのできる、半導体記憶装置を提供することにある。

# 【課題を解決するための手段】

# [0023]

上記目的を達成するため、本発明の半導体記憶装置は、情報として電荷が蓄積される複数のメモリセルを備える、アレイ状に配置された複数のマットと、一端が外部電源から供給される電圧を降圧または昇圧する内部電源に共通に接続された複数の電源線と、を有し、前記複数の電源線は、前記複数のマットが形成された領域上に、一定方向に延伸するよ

10

20

30

40

うに配線されており、該電源線の他端が、前記複数のマットのうちの前記一定方向において最も端に位置するマット上で共通に接続されている、ことを特徴とする。

### 【発明の効果】

[0024]

本発明によれば、電源線の他端を共通に接続したことにより、電源線の抵抗値が小さくなるので、動作の安定した半導体記憶装置(DRAM)を提供することができる。

[0025]

また、電源線の他端は端のマット上で共通に接続されているので、アレイ用電源配線領域をメモリセルアレイ部の両側に配置する必要がない。よって、アレイ用電源配線領域がメモリセルアレイ部の両側に配置されるものに比べて、チップサイズを削減することができる。

10

【発明を実施するための最良の形態】

[0026]

次に、本発明の実施形態について図面を参照して説明する。

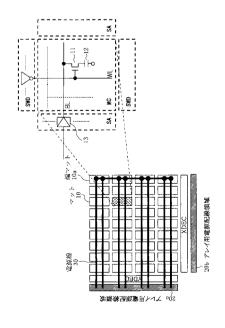

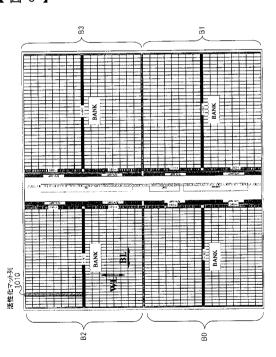

[ 0 0 2 7 ]

図1は、本発明の一実施形態である半導体記憶装置の構成を示す模式図である。

[0028]

図 1 を参照すると、半導体記憶装置は、それぞれが独立した動作を行う複数のバンクから構成される D R A M に代表される半導体メモリであって、マトリクス状に配置された複数のマット 1 0 よりなるメモリセルアレイ部を有する。この例では、マット 1 0 の配置は、4 行 9 列の簡易的な配置とされているが、これに限定されるものではない。

20

[0029]

マット 1 0 はいずれも同じ構成であって、メモリセルアレイ M C 、センスアンプ部 S A およびサブワードドライバ S W D を有する。

[0030]

メモリセルアレイMCは、一定の間隔で平行に配線された複数のビット線BLと、これらビット線BLと交差する、一定の間隔で平行に配線された複数のワード線WLと、これらビット線BLとワード線WLの各交差部に形成された、スイッチ素子11と容量素子12とからなる複数のメモリセルとを有する。スイッチ素子11は、例えばMOS(Metal Oxide Semiconductor)トランジスタである。容量素子12はコンデンサである。スイッチ素子11の一方の端子はビット線BLに接続され、他方の端子は容量素子12に接続されている。スイッチ素子11の制御端子は、ワード線WLに接続されている。

30

[0031]

センスアンプ部SAは、ビット線BL毎に設けられた複数のセンスアンプ13からなり、メモリセルアレイ部の両側に配置されている。サブワードドライバSWDは、ワード線毎に設けられた複数の駆動トランジスタからなり、メモリセルアレイMCを挟むように上下に配置されている。隣接するマット10間でセンスアンプ部SAを共用できるように、ビット線BLとこれに接続されるセンスアンプは、所謂、千鳥状に形成されている。これと同様に、サブワードドライバSWDについても、隣接するマット10間で共用できるように、ワード線WLとこれに接続される駆動トランジスタは、千鳥状に形成されている。なお、センスアンプ部SAとビット線、サブワードドライバSWDとワード線の配置は、千鳥状の配置に限定されるものではなく、他の配置であってもよい。

40

[0032]

メモリセルアレイ部上には、メモリセルの制御に用いる信号線の他、不図示の内部電圧発生回路で生成した電圧をセンスアンプに供給するための電源線30が形成されている。電源線30は、行方向に延伸する複数の電源線からなり、各電源線の一端はアレイ用電源配線領域20aにおいて共通に接続され、各電源線の他端は、メモリセルアレイ部の、アレイ用電源配線領域20aが形成された側とは反対の辺部に位置する端のマット10a上の領域において共通に接続されている。

[0033]

アレイ用電源配線領域 2 0 a は、電源線 3 0 をメモリセルアレイ部の周辺部にある外部電源パッドや内部電源発生回路と接続するための領域であって、ワード線の延伸方向に沿って形成されている。

# [0034]

図1には示されていないが、サブワードドライバSWDを駆動するための電源線もメモリセルアレイ部上に複数形成されており、各電源線の一端はアレイ用電源配線領域20bにおいて共通に接続され、各電源線の他端は、メモリセルアレイ部の、アレイ用電源配線領域20bが形成された側とは反対の辺部に位置する端のマットの列の領域上で共通に接続されている。アレイ用電源配線領域20bも、電源線をメモリセルアレイ部の周辺部にある外部電源パッドや内部電源発生回路と接続するための領域であって、ビット線の延伸方向に沿って形成されている。

[0035]

メモリセルアレイ部の周りには、メモリセルに対するデータの書き込みや読み出しを行う場合のアドレス指定を行うための、 X デコーダ (XDEC) および Y デコーダ (YDEC) が設けられている。 Y デコーダは、ワード線の延伸方向に沿って形成されている。 X デコーダは、ビット線の延伸方向に沿って形成されている。

[0036]

上記のとおりのレイアウト構造によれば、電源線30の他端を共通に接続したことにより、電源線30の抵抗値が小さくなり、その結果、DRAMの安定した動作を実現することができる。

[0037]

また、電源線30の他端は、端マット10a上で共通に接続されているので、アレイ用電源配線領域をメモリセルアレイ部の両側に配置する必要がない。よって、チップサイズは、アレイ用電源配線領域がメモリセルアレイ部の両側に配置されるものよりも小さくなる。

[0038]

なお、電源線30のレイアウト設計では、端マット10aと他の端マット10とで異なるレイアウトパターンを用いる。端マット10aでは、電源線のパターンが鉤状のパターンとされることから、電源線からメモリセルアレイ側へのノイズのクロストークが生じることが予想される。しかし、最近のメモリセルの微細化に伴い、メモリセルアレイ上に形成される格子状のメタル配線(ワード線、ビット線などの種々の信号線)の間隔(隙間)も非常に小さくなっている。このような隙間の小さな格子状のメタル配線の層は、電源線からのノイズ(電磁放射ノイズ)を遮蔽する作用があり、その遮蔽効果は非常に高いものとなっている。よって、鉤状のパターンを用いても、電源線からメモリセルアレイ側へのノイズのクロストークが問題になることはない。

[0039]

また、センスアンプの駆動電源線だけでなく、サブワードドライバを駆動するための電源線においても、内部の電源線の抵抗値が大きくなると、やはり負荷容量が大きいために選択ワード線の電位の立ち上がりが極端に遅くなるなどの原因でDRAMの動作が不安定になる場合がある。本実施形態では、サブワードドライバを駆動するための電源線も、他端を共通に接続しているので、DRAMの安定した動作を実現することができる。また、アレイ用電源配線領域をメモリセルアレイ部の両側に設ける必要がないので、チップサイズの削減も可能である。

[0040]

次に、本実施形態の半導体記憶装置のメモリセルアレイ部の詳細な構造について説明する。

[0041]

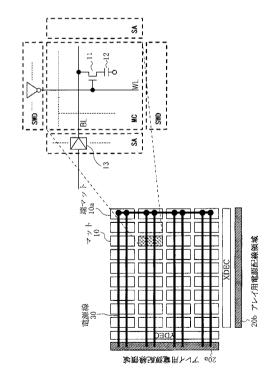

図 2 に、メモリセルアレイ部上に形成される電源線のレイアウトの模式図である。図 2 に示す電源線のレイアウトは、センスアンプ駆動電源線の他端を端マット 1 0 a 上で共通に接続した点以外は、図 7 に示したレイアウトと同じものである。

10

20

30

40

### [0042]

各マット間には、4つのSAG100が形成されている。これら4つのSAG100は、図1に示したセンスアンプ部SAを構成する複数のセンスアンプ13を4つのグループに纏めたものである。SAG100は、複数のセンスアンプ13からなる。

### [0043]

センスアンプ駆動電源線101、102がそれぞれ、SAG100の行ごとに設けられている。各センスアンプ駆動電源線101は、一端がアレイ電源配線領域20aにおいて共通に接続され、そこから行方向に延伸するように形成されている。各センスアンプ駆動電源線101の他端は、端マット10a上で共通に接続されている。各センスアンプ駆動電源線102も、一端がアレイ電源配線領域20aにおいて共通に接続され、そこから行方向に延伸するように形成されている。各センスアンプ駆動電源線102の他端も、端マット10a上で共通に接続されている。

#### [0044]

内部電圧発生回路1、2はそれぞれ、不図示の外部電源から供給された電圧を降圧して第1、第2の電圧を発生する。内部電圧発生回路1には、各センスアンプ駆動電源線101が接続され、内部電圧発生回路2には、各センスアンプ駆動電源線102が接続されている。第1の電圧が、内部電圧発生回路1からセンスアンプ駆動電源線101を通じてSAG100に供給される。第2の電圧が、内部電圧発生回路2からセンスアンプ駆動電源線102を通じてSAG100に供給される。SAG100内のセンスアンプ13は、内部電圧発生回路1、2から供給された第1、第2の電圧に基づいて、メモリセルに保持した電荷の信号レベルの判定を行う。

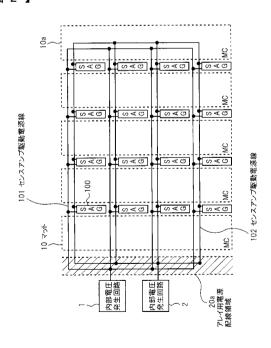

#### [0045]

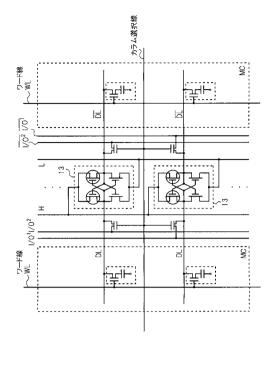

図 3 に、センスアンプ駆動電源線 1 0 1 、 1 0 2 に接続される S A G 1 0 0 およびマット 1 0 の構成を示す。

### [0046]

図3を参照すると、SAG100は4つのセンスアンプ13を有する。各センスアンプ13の第1の電圧入力端子は第1の配線に共通に接続され、各センスアンプ13の第2の電圧入力端子は第2の配線に共通に接続されている。第1の配線の一端はスイッチ素子(pMOS)103を介してセンスアンプ駆動電源線101に接続されている。第2の配線の一端はスイッチ素子(nMOS)104を制御することで、各センスアンプ13への第1、第2の電圧の供給を制御することができる。

#### [0047]

図4に、センスアンプの構成を示す。図4を参照すると、センスアンプ13は、互いの端子(ドレイン/ソース)および制御端子が接続されたpMOSおよびnMOSトランジスタからなる回路を左右対称に配置したものであり、端子(ドレイン/ソース)の接続ラインが一方の側に配置されたメモリセルのビット線に接続されている。各pMOSトランジスタのもう一方の端子(ドレイン/ソース)は図3に示した第1の配線に接続されている。各nMOSトランジスタのもう一方の端子(ドレイン/ソース)は図3に示した第2の配線に接続されている。このような構成のセンスアンプは、フリップフロップ回路で構成されるセンスアンプとして知られている。

# [0048]

センスアンプ13の列の両側には、ワード線WLと平行に配置された第1および第2の I/O配線がそれぞれ配置されている。センスアンプ13の間には、カラム選択線105 がビット線と平行に配置されている。

### [0049]

上述したとおりのレイアウト構造によれば、センスアンプ駆動電源線101、102の 他端を共通に接続したことにより、センスアンプ駆動電源線101、102の抵抗値が小 さくなり、その結果、DRAMの安定した動作を実現することができる。 10

20

30

40

### [0050]

また、センスアンプ駆動電源線101、102の他端は、端マット10a上で共通に接 続されているので、アレイ用電源配線領域をメモリセルアレイ部の両側に配置する必要が ない。よって、チップサイズは、アレイ用電源配線領域がメモリセルアレイ部の両側に配 置されるものよりも小さくなる。

# [0051]

なお、図2に示した構成において、第2の電圧を接地電位とする場合は、センスアンプ 駆動電源線102を接地する。この場合は、内部電源発生回路2は不要となる。

# [0052]

本実施形態によれば、上述の効果に加えて、電源線の低抵抗化による以下のような効果 も奏する。

### [0053]

図6に示したDRAMにおいて、バンクを構成する各マットのセンスアンプは、ワード 線方向に複数選択されて活性化される(活性化マット列1010)。この場合の消費電流 は、その選択方向である活性化方向(ワード線の延伸方向に同じ)に集中する。本実施形 態によれば、メモリセルアレイ部上に形成される電源線は、消費電流が集中する活性化方 向と交差(例えば直交)する方向(ビット線の延伸方向に同じ)に多く配線されており、 しかも、低抵抗化がなされているので、シグナル・インテグリティのさらなる向上を図る ことが可能である。

# [0054]

活性化方向と交差する方向へより多くの電源線を形成するためには、多層配線が有効せ る。 図 1 に示した電源線や図 2 に示したセンスアンプ駆動電源線 1 0 1 、 1 0 2 が形成さ れる配線層を、多層配線とすることで、さらなる低抵抗化を行うことが可能である。

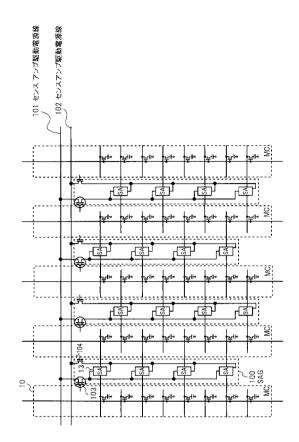

#### [0055]

図 5 に、図 1 に示したメモリセルアレイ部における電源線の多層構造における配線方向 を示す模式図である。

# [0056]

図5を参照すると、電源線30が形成される配線層は、第1乃至第3のアルミ配線層か らなる。メモリセルアレイ部の、端マット10aの領域を除く領域上において、第2およ び第3のアルミ配線層は、行方向に延伸するように配線され、第1のアルミ配線層は、列 方向に延伸するように配線される。このような多層配線構造によれば、活性化方向と交差 する方向へより多くの電源線を形成することができるので、例えば第2および第3のアル ミ配線を電源線に割り当てて並列接続するなどして電源線のさらなる低抵抗化を図ること ができる。

# [0057]

また、端マット10aの列の領域上においては、第1および第3のアルミ配線層は、列 方向に延伸するように配線され、第2のアルミ配線層は、行方向に延伸するように配線さ れる。これにより、電源線を端マット10a上で共通に接続する構造を容易に実現するこ とができる。

### [0058]

端マット10a上に形成される電源線の幅を、端マット10a以外のマット上に形成さ れる電源線の幅より大きくしてもよい。このように構成することで、電源線の抵抗をさら に小さくすることができる。

# 【図面の簡単な説明】

### [0059]

【図1】本発明の一実施形態である半導体記憶装置の構成を示す模式図である。

【 図 2 】メモリセルアレイ部上に形成される電源線のレイアウトを示すプロック図である

【図3】図2に示すレイアウトにおけるセンスアンプ駆動電源線とSAGおよびマットの 接続を示すブロック図である。

10

20

30

40

- 【図4】センスアンプの構成を示す回路図である。

- 【図 5 】図 1 に示すメモリセルアレイ部における電源線の多層構造における配線方向を説明するための模式図である。

- 【図6】DRAMのレイアウトを示す模式図である。

- 【図7】センスアンプ駆動電源線のレイアウトを示すブロック図である。

- 【図8】図7に示すレイアウトにおけるセンスアンプ駆動電源線の他端を共通に接続した 状態を説明するための模式図である。

# 【符号の説明】

# [0060]

- 11 スイッチ素子

- 12 容量素子

- 13 センスアンプ

- 10 マット

- 10a 端マット

- 20 a、20 b アレイ用電源配線領域

- 3 0 電源線

# 【図1】

# 【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

# フロントページの続き

F ターム(参考) 5F083 AD00 GA09 GA11 JA36 LA03 LA04 LA05 LA13 LA17 LA25 LA29