# **PCT**

# INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 4:

G06F 15/06, 15/32

(11) International Publication Number:

**WO 88/ 09016**

A1

(43) International Publication Date:

17 November 1988 (17.11.88)

(21) International Application Number:

PCT/JP88/00464

(22) International Filing Date:

14 May 1988 (14.05.88)

(31) Priority Application Number:

62/117719

(32) Priority Date:

14 May 1987 (14.05.87)

(33) Priority Country:

JP

(71) Applicant (for all designated States except US): FUJIT-SU LIMITED [JP/JP]; 1015, Kamikodanaka, Nakahara-ku, Kawasaki-shi, Kanagawa 211 (JP).

(72) Inventors; and

(75) Inventors/Applicants (for US only): HOSHINO, Akihiko [JP/JP]; 1-22-8, Nakahara, Mitaka-shi, Tokyo 181 (JP). NAKATANI, Shoji [JP/JP]; 99, Shimokodanaka, Nakahara-ku, Kawasaki-shi, Kanagawa 211 (JP). KU-RODA, Koji [JP/JP]; Shimonogeryo 302, 878, Shimonoge, Takatsu-ku, Kawasaki-shi, Kanagawa 213 (JP). KAWAI, Tetsu [JP/JP]; 1-2-705, Minamidai, Nagata, Minami-ku, Yokohama-shi, Kanagawa 232 (JP). (74) Agents: AOKI, Akira et al.; Seiko Toranomon Bldg., 8-10, Toranomon 1-chome, Minato-ku, Tokyo 105 (JP).

(81) Designated States: AT (European patent), BE (European patent), CH (European patent), DE (European patent), FR (European patent), GB (European patent), IT (European patent), JP, KR, LU (European patent), NL (European patent), SE (European patent), US.

#### Published

With international search report.

(54) Title: VECTOR PROCESSOR FOR PROCESSING RECURRENT EQUATIONS AT A HIGH SPEED

(57) Abstract

An improved vector processor for processing a modified recurrent equation:  $a_i = a_{i-2} \times b_{i-1} \times b_i \times c_{i-1} + c_i$ , where i is an integer: i = 1, 2, 3, ..., n, at a high speed. The vector processor includes a data distribution circuit (40a, 40b), at least one odd term calculation circuit (10A, 10AA), and at least one even term calculation circuit (10B, 10BB). The odd term calculation circuit calculates odd terms of the modified recurrent equation:  $a_i = (a_{j-2} \times b_{j-1} \times b_j) + (b_j \times c_{j-1}) + c_j$ , where j is an odd integer. The even term calculation circuit calculates even terms of the recurrent equations:  $a_k = (a_{k-2} x)^2$  $b_{k-1} \times b_k$  +  $(b_k \times c_{k-1})$  +  $c_k$ , where k is an even integer. The data distribution circuit receives an initial, data  $a_0$  and input vector (operand) data (bi) and (ci), and distributes that data to the odd and even term calculation circuits in a predetermined manner so that the above odd and even terms are calculated.

# FOR THE PURPOSES OF INFORMATION ONLY

$Codes \ used \ to \ identify \ States \ party \ to \ the \ PCT \ on \ the \ front \ pages \ of \ pamphlets \ publishing \ international \ applications \ under \ the \ PCT.$

| ΑT | Austria                      | FR                     | France                       | ML | Mali                     |

|----|------------------------------|------------------------|------------------------------|----|--------------------------|

| ΑU | Australia                    | GA                     | Gabon                        | MR | Mauritania               |

| BB | Barbados                     | GB                     | United Kingdom               | MW | Malawi                   |

| BE | Belgium                      | HU                     | Hungary                      | NL | Netherlands              |

| BG | Bulgaria                     | IT                     | Italy                        | NO | Norway                   |

| BJ | Benin                        | JP                     | Japan                        | RO | Romania                  |

| BR | Brazil                       | KP                     | Democratic People's Republic | SD | Sudan                    |

| CF | Central African Republic     |                        | of Korea                     | SE | Sweden                   |

| CG | Congo                        | KR                     | Republic of Korea            | SN | Senegal                  |

| CH | Switzerland                  | $\mathbf{L}\mathbf{I}$ | Liechtenstein                | SU | Soviet Union             |

| CM | Cameroon                     | LK                     | Sri Lanka                    | TD | Chad                     |

| DE | Germany, Federal Republic of | LU                     | Luxembourg                   | TG | Togo                     |

| DK | Denmark                      | MC                     | Monaco                       | US | United States of America |

| FI | Finland                      | MG                     | Madagascar                   |    |                          |

- 1 -

#### DESCRIPTION

TITLE OF THE INVENTION

Vector Processor for Processing Recurrent Equations at a High Speed

TECHNICAL FIELD

35

The present invention relates to a data processing system, more particularly, to a vector processor for processing recurrent equations at a high speed.

BACKGROUND ART

Recent remarkable advances in computer technologies have improved the operation speed of supercomputers by providing, for example, vector processors. These vector processors are used to carry out scientific calculations, such as a numerical solution of linear equations or a numerical solution of differential equations, etc., at a very high speed.

In scientific technical calculations, the following recurrent operational algorithm (or recurrent equation) is frequently used to solve first order linear equations by a numerical solution, or differential equations by a difference method, etc.

$$a_i = a_{i-1} \times b_i + c_i$$

... (1) where,  $i = 1, 2, 3, ..., n$

This operational algorithm (1) shows the recurrent relationship between a datum a<sub>i</sub> and a datum a<sub>i-1</sub>. In general, the operation of the above recurrent equation is not suitable for calculations by the vector processor at a high speed, since the datum a<sub>i-1</sub> is used again to calculate the datum a<sub>i</sub>, i.e., the term a<sub>i</sub> must be calculated after calculation of the term a<sub>i-1</sub>. Therefore, prior art vector processors cannot calculate the recurrent equations at a high speed. The prior art vector processor used for handling recurrent equation will be described later with reference to the drawings.

Nevertheless, there is a strong demand for a capability to calculate the recurrent equation at a high

speed by using a vector processor, since many recurrent equations are used in the scientific technical calculation field.

DISCLOSURE OF THE INVENTION

An object of the present invention is to provide a vector processor which can process recurrent equations at a high speed.

Another object of the present invention is to provide a vector processor having a simple circuit construction which can be easily formed.

According to the present invention, there is provided a vector processor including a vector instruction control unit for controlling vector instructions, a vector storage access unit for accessing input vector 15 data and calculated data to a main storage unit, a vector calculation unit for calculating vector data under the control of the vector instruction unit, and a data distribution unit for transferring data between the vector data access unit and the vector calculation unit, 20 characterized in that the vector processor comprises a vector calculation unit including at least one odd term calculation circuit and at least one even term calculation circuit, and a data distribution unit operatively connected to and cooperative with said vector calcu-25 lation unit, to process a modified recurrent equation. Each odd term calculation circuit is formed to calculate odd terms of the modified recurrent equation and includes an adding circuit, a multiplication circuit, at least one data storage circuit holding a calculated odd term, and at least one feedback line for feeding back the calculated odd term to the multiplication circuit and/or the adding circuit through the data storage circuit. Each even term calculation circuit is formed to calculated even terms of the recurrent equation and includes another adding circuit, another multiplication circuit, at least one another data storage circuit holding a calculated even term, and at least one another

feedback line for feeding back the calculated even term to another multiplication circuit and/or another adding circuit through another data storage circuit. The data distribution unit includes a first data setter for outputting zero, a second data setter for outputting one, first to sixth selectors for selecting input operands using for calculating the recurrent equation, constant data 0 and 1 from the setters, and the calculated odd and even terms, and a selector control circuit for controlling the selectors in a predetermined manner defined by the modified recurrent equation, to supply selected data to the odd and even term calculation circuits.

The recurrent equation expressed by the formula (1) 15 can be modified as shown in the following formula, when a first-order development is applied:

$$a_{i} = a_{i-1} \times b_{i} + c_{i}$$

$$= \{ (a_{i-2} \times b_{i-1}) + c_{i-1} \} \times b_{i} + c_{i}$$

$$= a_{i-2} \times b_{i-1} \times b_{i} + b_{i} \times c_{i-1} + c_{i}$$

$$\dots (2)$$

When an index  $\underline{i}$  is even, for example, an even index  $\underline{k}$  = 2, 4, and 6.

$$a_2 = a_6 \times b_1 \times b_2 + b_2 \times c_1 + c_2$$

$a_4 = a_2 \times b_3 \times b_4 + b_4 \times c_3 + c_4$

$a_6 = a_4 \times b_5 \times b_6 + b_6 \times c_5 + c_6$  .... (3)

When an index  $\underline{i}$  is odd, for example, an odd index  $\underline{j}$  = 1, 3, 5, and 7.

$$a_{1} = a_{0} \times b_{1} \times 1 + 1 \times c_{1} + 0$$

$$a_{3} = a_{1} \times b_{2} \times b_{3} + b_{3} \times c_{2} + c_{3}$$

$$a_{5} = a_{3} \times b_{4} \times b_{5} + b_{5} \times c_{4} + c_{5}$$

$$a_{7} = a_{5} \times b_{6} \times b_{7} + b_{7} \times c_{6} + c_{7} \qquad \dots (4)$$

Note that there is no direct recurrent relationship between the terms  $a_2$  and  $a_0$ ,  $a_4$  and  $a_2$ , and  $a_6$  and  $a_4$ . Similarly, there is no direct recurrent relationship between the terms  $a_3$  and  $a_1$ ,  $a_5$  and  $a_3$ , and  $a_7$  and  $a_5$ . Accordingly, the odd term calculation circuit can calculate odd terms  $a_4$  without a delay by the direct

recurrence, and the even term calculation circuit can calculate even terms  $\mathbf{a}_k$  without a delay by the direct recurrence, and thus contribute to a high speed calculation of the recurrent equations.

BRIEF DESCRIPTION OF THE DRAWINGS

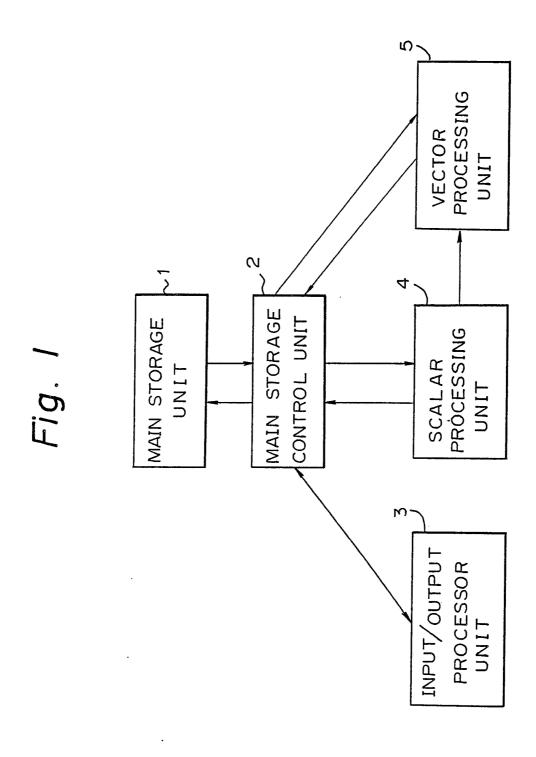

Figure 1 is a block diagram of a high speed data processing system which includes a vector processor of the present invention;

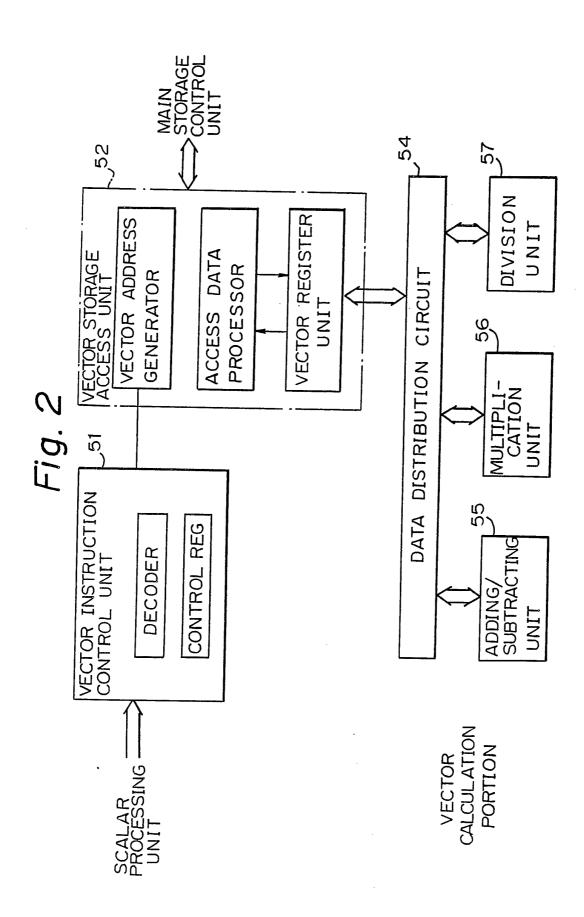

Figure 2 is a block diagram of a general vector 10 processor used in the data processing system shown in Fig. 1;

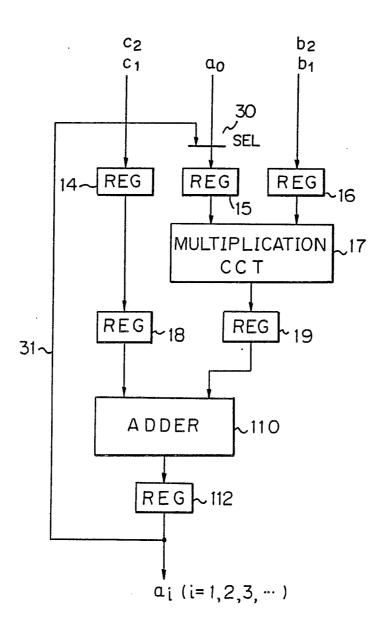

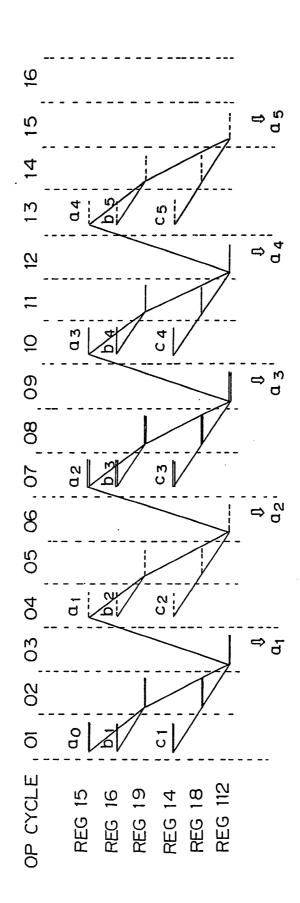

Figure 3 is a circuit diagram of a prior art vector processor;

Figure 4 is an operation timing chart of the vector 15 processor shown in Fig 3;

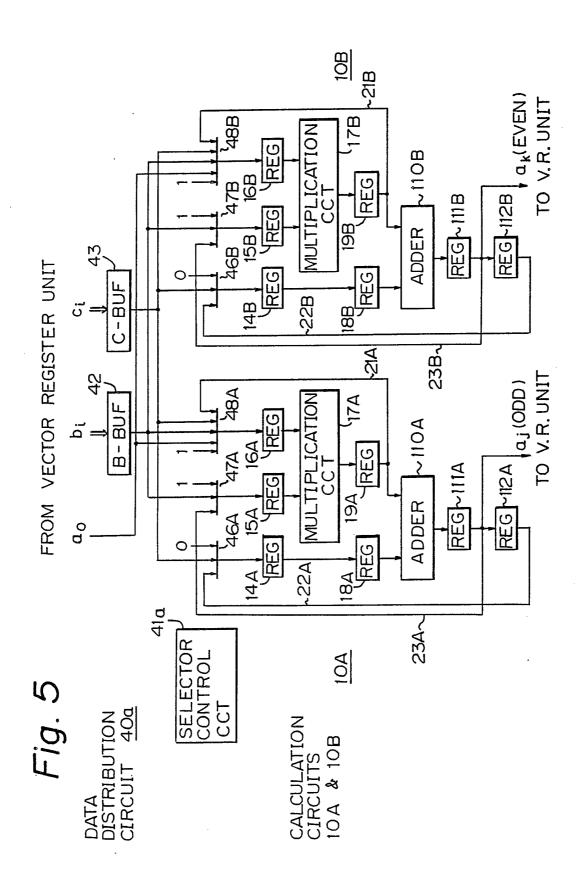

Figure 5 is a circuit diagram of an embodiment of a vector processor in accordance with the present invention;

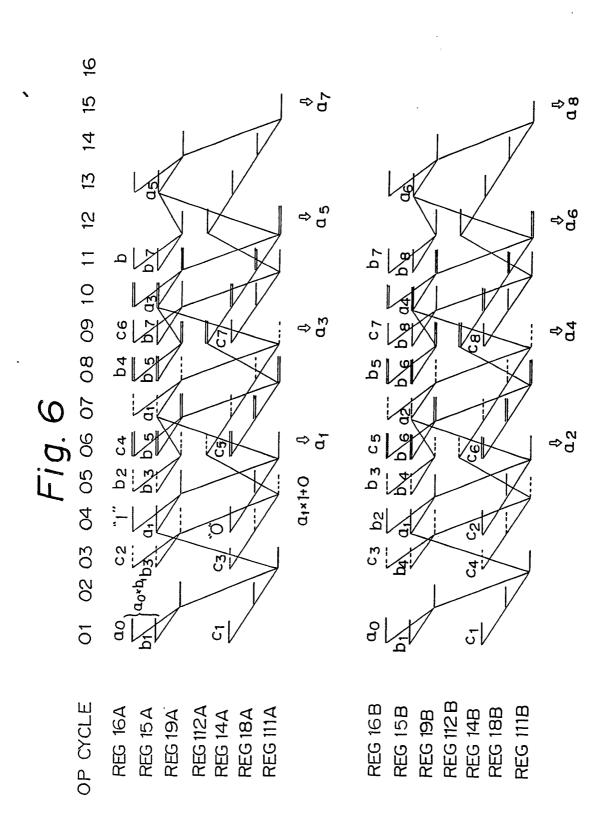

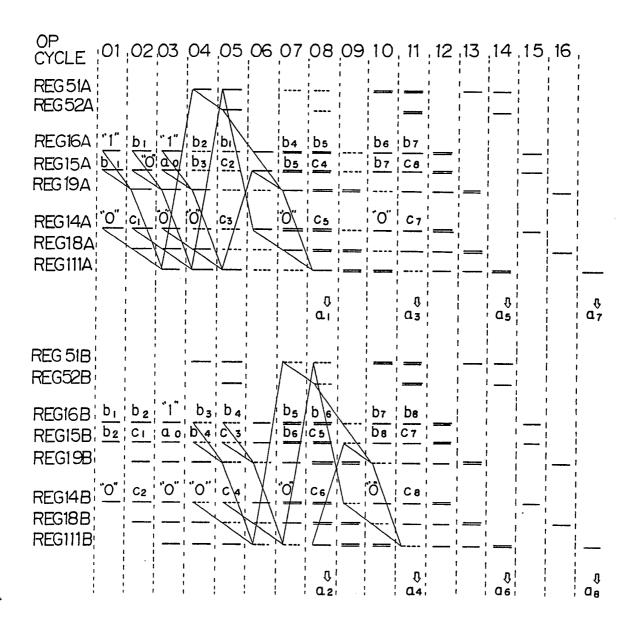

Figure 6 is an operation timing chart of the vector 20 processor shown in Fig. 5;

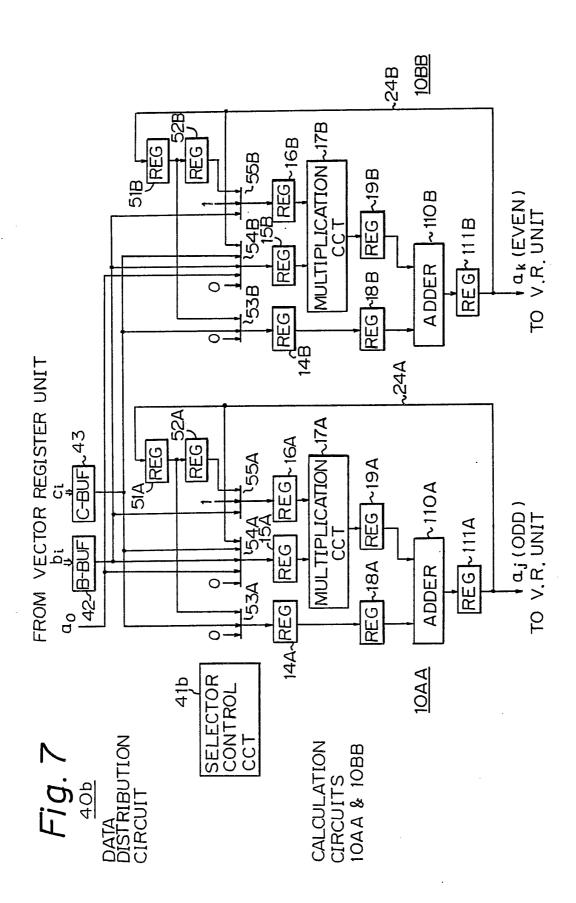

Figure 7 is a circuit diagram of another embodiment of a vector processor in accordance with the present invention; and,

Figure 8 is an operation timing chart of the vector 25 processor shown in Fig. 7.

BEST MODE OF CARRYING OUT THE INVENTION

Before describing preferred embodiments of a vector processor in accordance with the present invention, a high speed data processing system in which the vector processor is provided will be described with reference to Fig. 1.

In Fig. 1, the high speed data processing system consists of a main storage unit (MSU) 1, a main storage control unit (MSCU) 1, an input/output (I/O) processing unit 3, a scalar data processing unit (scalar processor) 4, and a vector data processing unit (vector processor) 5. The I/O processing unit 3 inputs data to

be calculated and outputs data calculated at the scalar processor 4 and/or the vector processor 5. The MSU 1 stores the input data and the calculated data. The scalar processor 4 controls all calculations. When operation commands concern a scalar operation, the scalar processor 4, per se, executes a scalar data calculation. When operation commands concern a vector operation, the scalar processor 4 transfers control to the vector processor 5 to carry out a vector calculation at the vector processor 5. Namely, the vector processor 5 is triggered by the scalar processor 4 when the vector calculation is requested, and carries out the vector calculation. The MSCU 2 controls the data flow among the MSU 1, the I/O processing unit 3, the scalar processor 4, and the vector processor 5.

A general configuration of the vector processor 5 shown in Fig. 1 is shown in Fig. 2. In Fig. 2, the vector processor 5 includes a vector instruction control unit (VICU) 51 having a decoder and a control register, a vector storage access unit (VSAU) 52 having a vector 20 address generator, an access data processor and a vector register unit, a data distribution unit 54, and a vector calculation portion having an adding and subtracting unit 55, a multiplication unit 56, and a division unit 57. The VICS 51 receives data control instructions 25 from the scalar processor 4. The control register saves control data of the data control instructions. decoder decodes the data control instructions. VSAU 52 transfers data between the MSU 1 and the vector 30 calculation portion through the MSCU 2 and the data distribution unit 54. The vector address generator generates addresses for accessing data in the MSU 1 in accordance with the decoded instructions. The access data processor controls data between the MSU 1 and the 35 vector register unit. Data to be used for a vector calculation are once stored in the vector register unit. Also, data calculated at the vector calculation portion

are stored in the vector register unit. The data distribution unit 40 distributes the data from the vector register unit to supply the same to the adding-subtracting unit 55, the multiplication unit 56, and the division unit 57 in accordance with the decoded instruction. The units 55, 56, and 57 are operatively connected to perform the vector calculation. The vector calculated data are stored in the vector register unit through the data distribution unit 40, thereafter, are stored in the MSU 1.

A prior art of a vector processor will be described with reference to Figs. 3 and 4. Figure 3 shows an elementary circuit diagram for processing the recurrent equation discussed above. Figure 4 shows an operation timing chart of the vector processor of Fig. 3.

In Fig. 3, the vector processor includes a selector 30, registers 14, 15 and 16, a multiplication circuit 17, registers 18 and 19, an adder 110, a register 112, and a feedback line 31 connected between 20 an output terminal of the register 112 and an input terminal of the selector 30. These circuit components are a part of the vector calculation portion shown in Fig. 3. The multiplication circuit 17 calculating a term:  $a_{i-1} \times b_i$ . The adder 110 adds  $c_i$  and the result 25 from the multiplication circuit 17. On one hand, the added data is fed back to the multiplication circuit 17 through the feedback line 31, the selector 30 and the register 15 to use a next term calculation, and on other hand, is output to the vector register unit. 30 selector 30 outputs an initial vector data  $\mathbf{a}_{0}$  at an initial time. The registers 14, 15, and 16, the registers 18 and 19, and the register 112 are provided to hold the data, respectively. The register 112 and the feedback line 31 are provided to feed back the calculated data  $\mathbf{a}_i$  to the register 15 for calculating a next term a 1+1.

Note that, since subtraction and division are not

needed to calculate the recurrent equation, a subtracting circuit and a division circuit are omitted in Fig. 3.

The operation of the vector processor shown in 5 Fig. 3 will be described in more detail with reference to Fig. 4.

When an integer  $\underline{i}$  indicating an index of the recurrent equation is 1, the recurrent equation is expressed as follows:

10  $a_1 = a_0 \times b_1 + c_1$

Thus, at the operation cycle 01, initial data c<sub>1</sub>, a<sub>0</sub>, and b<sub>1</sub> are loaded into the registers 14, 15, and 16 from the vector register unit shown in Fig. 2. Then, a multiplication of (a<sub>0</sub> x b<sub>1</sub>) is carried out at the

15 multiplication circuit 17. At the operation cycle 02, the data c<sub>1</sub> loaded in the register 14 is transferred to the register 18. Also, the data calculated at the multiplication circuit 17 is transferred to the register 19. Thereafter, the adder 110 adds the data c<sub>1</sub> and the data stored in the register 19, to obtain the result a<sub>1</sub>. At the operation cycle 03, the result a<sub>1</sub> is stored in the register 112, and is then output to the vector register unit shown in Fig. 2 through the data distribution unit 54.

25 At the operation cycle 04, the next vector data  $b_2$  and  $c_2$  are loaded into the registers 16 and 14 through the vector register unit. At the same time, the data  $a_1$  stored in the register 112 is loaded into the register 15 through the feedback line 31 and the selector 30.

30 During the operation cycles 04 - 06, a calculation of a next term:  $a_2 = a_1 \times b_2 + c_2$  is carried out.

Similarly, during the operation cycles 07 = 09, a calculation of a term:  $a_3 = a_2 \times b_3 + c_3$  is carried out. During the operation cycles 10 - 12, a calculation of a term:  $a_4 = a_3 \times b_4 + c_4$  is carried out. During the operation cycles 13 - 15, a calculation of a term:  $a_5 = a_4 \times b_5 + c_5$  is carried out.

30

As described above, a calculation time for obtaining one term a requires three operation cycles. If 100 terms of vector processing are required, 300 operation cycles are needed to obtain calculated data of 100 recurrent equations. Accordingly, a high speed operation for calculating the recurrent equations, in particular, for high order recurrent equations, can not be achieved by the prior art vector processor.

tionship wherein a calculation of a term a must be carried out after a calculation of a just previous term a led. Thus, the prior art vector processor is made idle in order to calculate the just previous term before proceeding to a calculation of a next term. Therefore, even though the vector processor correctly solves the above recurrent equation, the vector processor still suffers from the above described low speed operation.

The present invention solves the above defect by modifying the recurrent equation.

The recurrent equation described above can be modified as follows:

$$a_{i} = a_{i-1} \times b_{i} + c_{i}$$

$$= (a_{i-2} \times b_{i-1} + c_{i-1}) \times b_{i} + c_{i}$$

$$= (a_{i-2} \times b_{i-1} \times b_{i}) + b_{i} \times c_{i-1} + c_{i}$$

(2)

where,  $\underline{i}$  is an integer indicating an index,  $\underline{i} = 1, 2, 3, \ldots, \underline{n}$   $a_i$  are calculated vector data,  $b_i$  are input vector data, and  $c_i$  are input vector data.

From the formula (2), it is recognized that there is no direct recurrent relationship between a term  $a_i$  and another term  $a_{i-2}$  like the direct recurrent relationship between a term  $a_i$  and another term  $a_{i-1}$  discussed above. According to the above formula (2), a calculation of the term  $a_i$  is not affected by a calculation of a just previous term  $a_{i-1}$ . The term  $a_{i-2}$  is

already calculated two steps prior to a calculation of the term a; , and thus a calculation of the term a; can be carried out immediately without a delay in the calculation of the just previous term a; But, the above concept cannot be realized unless odd terms and even terms are separately operated.

When an index  $\underline{i}$  is even, an even index  $\underline{k}$  is used, and the above formula (2) is expressed as follows:

... (3)

When an index  $\underline{i}$  is odd, an odd index  $\underline{j}$  is used, and the above formula (1) is expressed as follows:

$$j = 1$$

:  $a_1 = a_0 \times b_1 \times 1 + 1 \times c_1 + 0$

$j = 3$ :  $a_3 = a_1 \times b_2 \times b_3 + b_3 \times c_2 + c_3$

$j = 5$ :  $a_5 = a_3 \times b_4 \times b_5 + b_5 \times c_4 + c_5$

:

... (4)

Note that, since there is no direct recurrent relationship between, for example, the terms  $a_0$  and  $a_2$ , the terms  $a_2$  and  $a_4$ , the terms  $a_4$  and  $a_6$ , the terms  $a_1$  and  $a_3$ , or the terms  $a_3$  and  $a_5$ , except for the terms  $a_0$  and  $a_1$ , a pair of terms, for example,  $a_3$  and  $a_4$ , can be calculated in parallel. This enables a high speed vector data calculation. Nevertheless, a calculation of the terms  $a_3$  and  $a_4$  must be carried out after the calculation of the terms  $a_3$  and  $a_4$  and  $a_2$ .

A first embodiment of a vector processor in accordance with the present invention will be specifically described with reference to Fig. 5.

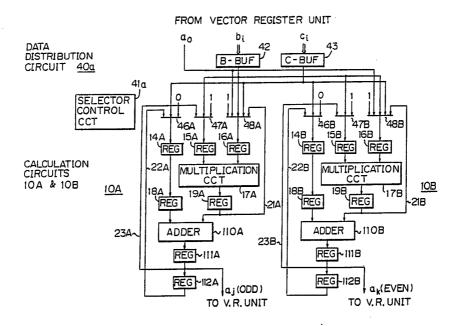

In Fig. 5, the vector processor includes a data distribution circuit 40a, and a vector data calculation unit consisting of an odd term calculation circuit 10A

and an even term calculation circuit 10B.

The data distribution circuit 40a is provided in the vector register unit shown in Fig. 2, the odd term calculation circuit 10A, and the even term calculation circuit 10B, to supply an initial operand (data) a<sub>0</sub>, and operands (input vector data) b<sub>i</sub> and c<sub>i</sub> to the odd and even term calculation circuits 10A and 10B, in a predetermined manner discussed later. The data distribution circuit 40a also receives odd term data a<sub>i</sub> calculated at the odd term calculation circuit 10A and even term data a<sub>k</sub> calculated at the even term calculation circuit 10B, and outputs the same to the vector register unit.

The data distribution circuit 40a includes a

15 selector control circuit 41a, a B-buffer (B-BUFF) 42 of

a first-in first-out type (FIFO) buffer, for first

inputting the operands b and first outputting the same,

and a C-buffer (C-BUFF) 43, which is also a FIFO buffer,

for first inputting the operands c and first outputting

20 the same. The data distribution circuit 40a also

includes selectors 46A, 47A, 48A, 46B, 47B, and 48B.

The data distribution circuit 40a further includes a

zero (0) setter (not shown) for outputting zero to the

selectors 46A and 46B, and a one (1) setter (not shown)

25 for outputting one to the setters 47A, 48A, 47B, and 48B.

The odd term calculation circuit 10A for calculating the odd terms a includes first stage registers 14A, 15A and 16A, a multiplication circuit 17A, second stage registers 18A and 19A, an adder 110A, a third stage registers 111A, a fourth stage register 112A, a first feedback line 21A connected between an output terminal of the register 19A and an input terminal of the selector 48A, and a second feedback line 22A connected between an output terminal of the register 112A and an input terminal of the selector 46A, and a third feedback line 23A connected between an output terminal of the register 111A and an input

terminal of the selector 47A. Calculated odd terms a are sequentially output from the register lllA to the vector register unit.

The registers 111A and/or 112A can be included in 5 the data distribution circuit 40a.

The even term calculation circuit 10B for calculating the even terms a<sub>k</sub> has the same circuit construction as that of the odd term calculation circuit 10A, because the operational algorithms, per se, are the same in both cases. Since both the odd and even term calculation circuits 10A and 10B can have the identical construction, the design, production and mounting thereof on a printed circuit board (PCB) are greatly simplified. Both of the odd and even term calculation circuits 10A and 10B are operable independently and simultaneously.

The operation of the vector processor shown in Fig. 5 will be described.

Supposing that the operands a<sub>i</sub> , c<sub>i</sub> and the initial operand a<sub>0</sub> are previously stored in the MSU 2 shown in Fig. 1, and the following instruction set is detected at the scalar processor 4, the scalar processor 4 transfers control of the operation to the vector processor shown in Fig. 5, triggering the vector processor.

#### TABLE 1

VL A(0) TO VR00

VL B(I) TO VR01

VL C(i) TO VR02

VCAL A(i) = A(i-1) X B(I) + C(i)

VST A(i) TO VR00

where, VL indicates a "Vector Load" instruction,

VCAL indicates a "Vector Calculation"

instruction,

VST indicates a "Vector Store" instruction A(i), B(i) and C(i) correspond to  $a_i$ ,  $b_i$

and c<sub>i</sub> , and VR00, VR01 and VR02 indicate vector registers 00, 01 and 02 in the vector register unit shown in Fig. 2. Note, in this embodiment, each vector register has a memory capacity of 100 words.

First, the vector storage access unit (VSAU) 52

shown in Fig. 2 loads vector data a<sub>0</sub>, b<sub>1</sub> -- b<sub>100</sub>, and c<sub>1</sub> -- c<sub>100</sub> stored in the main storage unit (MSU) 1 into

10 the vector registers VR00, VR01 and VR02 of the vector register unit through the main storage control unit (MSCU) 2, in response to the above "Vector Load" instruction, under the control of the vector instruction control unit (VICU) 51 shown in Fig. 2.

During the above vector data loading, a calculation of recurrent equation:  $a_i = a_{i-1} \times b_i + c_i$  at the circuit shown in Fig. 5, and a store of calculated data  $a_i$  into the vector register VR00 are carried out, in response to the above "Vector Calculation" and "Vector Store" instructions, under the control of the VICU 51.

The calculated data  $a_i$  in the vector register VR00 can be stored in the MSU 1 during the above operation.

Now, a detailed operation of the circuit of Fig. 5 will be described with reference to Fig. 6.

A calculation consists of an initial term calculation for calculating the initial terms  $\mathbf{a}_1$  and  $\mathbf{a}_2$ , and a normal term calculation for calculating subsequent terms, for example,  $\mathbf{a}_3$  and  $\mathbf{a}_4$ ,  $\mathbf{a}_5$  and  $\mathbf{a}_6$ , etc.

30 First, the initial term calculation will be described.

Below TABLE 2 and TABLE 3 show data loaded into the registers 14A, 15A, 16A and 111A, and the registers 14B, 15B, and 16B, and 111B under the control of the selector control circuit 40b.

| т  | አ | ъ.     | rr | 2 |

|----|---|--------|----|---|

| т. | м | $\Box$ | டட |   |

| OP<br>CYCLE | REG<br>14A | REG<br>15A                                       | REG<br>16A     | REG<br>111A    |

|-------------|------------|--------------------------------------------------|----------------|----------------|

| · 01        | cl         | b <sub>1</sub>                                   | a <sub>0</sub> |                |

| 02          |            |                                                  |                |                |

| 03          |            |                                                  |                |                |

| 04          | 0          | a <sub>0</sub> x b <sub>1</sub> + c <sub>1</sub> | 1              |                |

| 05          |            |                                                  |                |                |

| 06          |            |                                                  |                | a <sub>l</sub> |

TABLE 3

| OP<br>CYCLE | REG<br>14B     | REG<br>15B             | REG<br>16B     | REG<br>111B |

|-------------|----------------|------------------------|----------------|-------------|

| 01          | cl             | b <sub>1</sub>         | a <sub>0</sub> |             |

| 02          |                |                        |                |             |

| 03          |                |                        |                |             |

| 04          | c <sub>2</sub> | $a_0 \times b_1 + c_1$ | b <sub>2</sub> |             |

| 05          |                |                        |                |             |

| 06          |                |                        |                | a           |

The data distribution circuit 40a loads initial operands  $a_0$ ,  $b_1$  and  $c_1$  therein; the operands  $b_1$  and  $c_1$  being stored in the B-BUFF 42 and the C-BUFF 43, respectively.

### OPERATION CYCLE 01

30 At the operation cycle 01, the selector control circuit 41a controls the selectors 46A, 47A, and 48A to output the operands  $c_1$ ,  $b_1$ , and  $a_0$  to the registers 14A, 15A, and 16A in the odd term calculation circuit 10A. These registers 14A, 15A, and 16A store the operands  $c_1$ ,  $b_1$ , and  $a_0$ . At the same time, the selector control circuit 41a controls the selectors 46B, 47B, and 48B to output the operands  $c_1$ ,  $b_1$ , and  $a_0$  to

the registers 14B, 15B, and 16B in the even term calculation circuit 10B. These registers 14B, 15B, and 16B also save the operands  ${\bf a_0}$  ,  ${\bf b_1}$  , and  ${\bf c_1}$ .

In the odd term calculation circuit 10A, the register 16A outputs the saved operand  $\mathbf{a}_0$  to the multiplication circuit 17A as a multiplicand, and the register 15A outputs the saved operand  $\mathbf{b}_1$  to the multiplication circuit 17A as a multiplier. Thus, the multiplication circuit 17A calculates  $(\mathbf{a}_0 \times \mathbf{b}_1)$ .

At the same time, in the even term calculation circuit 10B, the register 16B outputs the saved operand  $a_0$  to the multiplication circuit 17B as a multiplicand, and the register 15B outputs the saved operand  $b_1$  to the multiplication circuit 17B as a multiplier. The multiplication circuit 17B calculates  $(a_0 \times b_1)$ .

# OPERATION CYCLE 02

In the odd term calculation circuit 10A, data (a<sub>0</sub> x b<sub>1</sub>) calculated at the multiplication circuit 17A is transferred to the register 19A and saved therein. The data c<sub>1</sub> saved at the register 14A is also transferred to the register 18A and saved therein.

At the same time, in the even term calculation circuit 10B, data (a<sub>0</sub> x b<sub>1</sub>) calculated at the multi25 plication circuit 17B is transferred to the register 19B and saved therein. The data c<sub>1</sub> saved at the register 14B is transferred to the register 18B.

Thereafter, in the odd term calculation circuit 10A, the adder 110A adds the data  $(a_0 \times b_1)$  and the data  $c_1$ . As a result, the following first odd term is obtained.

$$a_1 = a_0 \times b_1 + c_1$$

Similarly, at the same time, in the even term calculation circuit 10B, the above first odd term a is obtained by the adder 110B.

## OPERATION CYCLE 03

In the odd term calculation circuit 10A, the

calculated first odd term  $a_1$  is transferred to the register 111A and saved therein.

Also, in the even term calculation circuit 10B, the calculated first odd term  $a_1$  is transferred to the register 111B and saved therein.

During the above operation, the data distribution circuit 40a loads operands (b $_2$  , b $_3$  , b $_4$ ) and (c $_2$  , c $_3$  , c $_4$ ) into the B-BUFF 42 and the C-BUFF 43 from the vector registers VR01 and VR02, respectively.

Note that, although having obtained the first odd term  $a_1$ , the data distribution circuit 40a does not output the same to the vector register VR00 at this time, because a first even term  $a_2$  has not been obtained.

# 15 OPERATION CYCLES 04 - 06

Until the first even term  $a_2$  is obtained at the even term calculation circuit 10B, the odd term calculation circuit 10A and the data distribution circuit 40a cooperate to keep the data  $a_1$  as is, and to prepare operands used for calculating a second odd term  $a_3$ .

As the operation cycle 04, the selector control circuit 41a controls the selectors 46A, 47A, and 48A to set zero data to the register 14A, the calculated first odd term a<sub>1</sub> to the register 15A through the register 111A and the feedback line 23A, and a data of one (1) to the register 16A. As a result, at the operation cycle 04, the multiplication circuit 17A calculates (a<sub>1</sub> x 1), and at the operation cycle 06, the adder 110A adds the data (a<sub>1</sub> x 1) from the register 19A and the data of zero (0) from the registers 18A. Namely, the following dummy calculation is effected.

$$a_1 = (a_1 \times 1) + 0$$

During the above operation, at the operation cycle 05, the selector control circuit 41a controls the selectors 47A and 48A to set an operand  $\mathbf{b}_3$  to the register 15A, and an operand  $\mathbf{b}_2$  to the register 16A. The data  $\mathbf{a}_1$  is transferred to the register 111A at the

operation cycle 05, and is further stored in the register 112A at the operation cycle 06.

Conversely, in the even term calculation circuit 10B, the following first even term a<sub>2</sub> is calculated by using the first odd term a<sub>1</sub> calculated therein and saved in the registers 112B.

$$a_2 = (a_1 \times b_2) + c_2$$

For this purpose, at the operation cycle 04, the selector control circuit 41a controls the selectors 46B, 47B, and 48B to set the operand c<sub>2</sub> to the register 14B, the first odd term a<sub>1</sub> saved in the register 111B to the register 15B through the feedback line 23B, and the operand b<sub>2</sub> to the register 16B. At the operation cycle 05, the first even term a<sub>2</sub> is obtained at the adder 110B, and at the operation cycle 06, the first even term a<sub>2</sub> is stored in the registers 111B.

The data distribution circuit 40a transfers the pair of first odd and even terms  $a_1$  and  $a_2$  to the vector register VR00 from the register lllA and lllB.

The initial term calculation is thus completed.

The normal term calculation will now be described.

OPERATION CYCLES 03 - 09

First, a calculation of a second odd term  $a_3$  in the odd term calculation circuit 10A will be described.

Since the second odd term a<sub>3</sub> is defined by the following formula, the selector control circuit 41a controls the selectors 46A, 47A, and 48A to load data as shown in TABLE 4 into the registers 14A, 15A, and 16A at the following operation cycles shown in TABLE 4.

$$a_3 = a_1 \times (b_2 \times b_3) + b_3 \times c_3 + c_3$$

TABLE 4

| OP<br>CYCLE | REG<br>14A             | REG<br>15A     | REG<br>16A       |

|-------------|------------------------|----------------|------------------|

| 03          | c <sub>3</sub>         | b <sub>3</sub> | c <sub>2</sub>   |

| 04          |                        |                |                  |

| 05          | Mass made Cons         | b <sub>3</sub> | b <sub>2</sub>   |

| 06          |                        |                |                  |

| 07          | $b_3 \times c_2 + c_3$ | $\mathtt{a}_1$ | $b_2 \times b_3$ |

| 08          |                        |                | •                |

| 09          |                        |                |                  |

At the operation cycle 03, a multiplication value

(b<sub>3</sub> x c<sub>2</sub>) is obtained at the multiplication circuit 17A. At the operation cycle 05, a sum (b<sub>3</sub> x c<sub>2</sub>) + c<sub>3</sub> is obtained at the adder 110A. At the operation cycle 05, a multiplication value (b<sub>2</sub> x b<sub>3</sub>) is obtained at the multiplication circuit 17A. At the operation cycle 07, a multiplication value (a<sub>1</sub> x b<sub>2</sub> x b<sub>3</sub>) is obtained at the multiplication circuit 17A. At the operation cycle 08, the calculated data (a<sub>1</sub> x b<sub>2</sub> x b<sub>3</sub>) is supplied to the adder 110A. The above second odd term a<sub>3</sub> is obtained at the adder 111A. The calculated second odd term a<sub>3</sub> is saved at the register 111A at the operation cycle 08. At the operation cycle 09, the second odd term a<sub>3</sub> saved in the register 111A is transferred to the vector register VR00 and saved in the register 112A.

In the above, the data  $a_1$  saved in the register 100 ter 112A is fed back to the register 15A through the feedback line 22A. Also, the data  $(b_2 \times b_3)$  saved in the register 19A is fed back to the register 16A through the feedback line 21A. The sum  $(b_3 \times c_2) + c_3$  stored in the register 111A is fed back to the register 14A through the feedback line 23A.

Similarly, the following second even term  $\mathbf{a}_4$  is

obtained at the even term calculation circuit 10B.

$a_4 = a_2 \times b_3 \times b_4 + b_4 \times c_3 + c_4$

The selector control circuit 41a also controls the selectors 46B, 47B, and 47B to load the following data shown in TABLE 5 into the registers 14B, 15B, and 16B.

5

TABLE 5

| OP<br>CYCLE | REG<br>14B             | REG<br>15B     | REG<br>16B                      |

|-------------|------------------------|----------------|---------------------------------|

| 03          | c <sub>4</sub>         | b <sub>4</sub> | c <sub>3</sub>                  |

| 04          |                        |                | •                               |

| 0.5         |                        | b <sub>4</sub> | b <sub>3</sub>                  |

| 06          | •                      |                |                                 |

| 07          | $c_3 \times b_4 + c_4$ | a <sub>2</sub> | b <sub>3</sub> x b <sub>4</sub> |

| 08          |                        |                |                                 |

| 09          |                        |                |                                 |

At the operation cycle 09, the odd and even terms  $a_3$  and  $a_4$  are transferred to the vector register VR00 in the vector register unit.

#### OPERATION CYCLES 06 - 12

Similarly, during the operation cycles 06 - 12, the following third odd and even terms a<sub>5</sub> and a<sub>6</sub> are obtained at the odd and even term calculation circuits 10A and 10B.

$$a_5 = a_3 \times b_4 \times b_5 + b_5 \times c_4 + c_5$$

$a_6 = a_4 \times b_5 \times b_6 + b_6 \times c_5 + c_6$

To achieve the above calculation, the selector control circuit 41a controls the selectors 46A, 47A, 48A, 46B, 47B and 48B to load the following data shown in TABLE 6 and TABLE 7 to the registers 14A, 15A, 16A, 14B, 15B and 16B.

TABLE 6

| OP<br>CYCLE | REG<br>14A             | REG<br>15A     | REG<br>16A                      |

|-------------|------------------------|----------------|---------------------------------|

| 06          | c <sub>5</sub>         | b <sub>5</sub> | c <sub>4</sub>                  |

| 07          |                        |                |                                 |

| 08          |                        | b <sub>5</sub> | $\mathtt{b}_4$                  |

| 09          |                        |                |                                 |

| 10          | $c_4 \times b_5 + c_5$ | a <sub>3</sub> | b <sub>4</sub> x b <sub>5</sub> |

| 11          |                        |                |                                 |

| 12          |                        |                |                                 |

TABLE 7

| OP<br>CYCLE | REG<br>14B                                       | REG<br>15B     | REG<br>16B                      |

|-------------|--------------------------------------------------|----------------|---------------------------------|

| 06          | c <sub>6</sub>                                   | ь <sub>6</sub> | c <sub>5</sub>                  |

| 07          |                                                  |                |                                 |

| 08          | o≠ o=                                            | b <sub>6</sub> | b <sub>5</sub>                  |

| 09          |                                                  |                | •                               |

| 10          | c <sub>5</sub> x b <sub>6</sub> + c <sub>6</sub> | a <sub>4</sub> | b <sub>5</sub> x b <sub>6</sub> |

| 11          |                                                  |                |                                 |

| 12          |                                                  |                |                                 |

At the operation cycle 11, the odd and even terms  $a_5$  and  $a_6$  are obtained at the adders 111A and 111B and are transferred to the vector register VR00.

Other pluralities of pairs of odd and even terms are obtained in the same way as described above.

A calculation of a pair of odd and even terms

requires only three operation cycles, except for a calculation of the first odd and even terms. This time is same as that of the prior art vector processor.

According to the vector processor shown in Fig. 5, twice the amount of data can be obtained in three operation cycles, except for the initial calculation. Thus, the vector processor shown in Fig. 5 doubles the calculation performance compared with that of the prior art vector processor, when many terms of the recurrent equations are to be calculated.

Another embodiment of the vector processor in accordance with the present invention will be described 10 with reference to Fig. 7.

In Fig. 7, the vector processor includes a data distribution circuit 40a and a vector data calculation unit consisting of an odd term calculation circuit 10AA and an even term calculation circuit 10BB.

The data distribution circuit 40b is provided in the vector register unit shown in Fig. 2, the odd term calculation circuit 10AA, and the even term calculation circuit 10BB, to supply an initial operand a<sub>0</sub> and operands (input data) b<sub>i</sub> and c<sub>i</sub> to the odd and even term calculation circuits 10AA and 10BB in a predetermined manner, as described later. The data distribution circuit 40b also receives a pair of odd term data a<sub>j</sub> calculated at the odd term calculation circuit 10AA and even term data a<sub>k</sub> calculated at the even term calculation circuit 10BB, and outputs the same to the vector register unit.

The data distribution circuit 40b includes a selector control circuit 41b, the B-BUFF 42, the C-BUFF 43, buffer registers 51A and 52A, selectors 53A, 54A, and 55A, registers 51B and 52B, and selectors 53B, 54B and 55B. The data distribution circuit 40b also includes the zero setter and the one setter (not shown).

The odd term calculation circuit 10AA includes the first-stage registers 14A, 15A, and 16A, the multiplication circuit 17A, the second-stage registers 18A and 19A, the adder 110A, the third-stage register 111A, and a feedback line 24A connected between an output

terminal of the register 111A and an input terminal of the register 51A.

The even term calculation circuit 10BB has the same circuit construction as that of the odd term calculation 5 circuit 10AA.

The vector processor shown in Fig. 7 calculates the recurrent equation defined by the formula (2). The odd term calculation circuit 10AA and the data distribution circuit 40b cooperate to calculate the recurrent

equations defined by the formula (4), and the even term calculation circuit 10BB and the data distribution circuit 40b also cooperate to calculate the recurrent equations defined by the formula (3).

The operation of the vector processor shown in 15 Fig. 7 will be specifically described with reference to Fig. 8, when the instruction set shown in TABLE 1 is given.

The operation of the MSU 1, the MSCU 2, the VICU 51, and the VSAU 52, shown in Fig. 2, is omitted, since the operation thereof is substantially the same as that described above.

In Fig. 8, the cooperation cycles consist of initial operation cycles 01 - 08, and normal operation cycles 04 - 11, 10 - 14, etc.

## 25 OPERATION CYCLE 01 - 08

The following TABLE 8 and TABLE 9 show data in the registers 14A, 15A, 16A, and 111A, and data in the registers 14B, 15B, 16B, and 111B, during the initial operation cycles.

TABLE 8

| OP<br>CYCLE | REG<br>14A                          | REG<br>15A             | REG<br>16A             | REG<br>111A |

|-------------|-------------------------------------|------------------------|------------------------|-------------|

| 01          | 0                                   | b <sub>1</sub>         | 1 .                    |             |

| 02          | c <sub>1</sub>                      | 0                      | b <sub>1</sub>         |             |

| 03          | 0                                   | a <sub>0</sub>         | 1                      |             |

| 04          |                                     |                        |                        |             |

| 05          |                                     | •                      |                        |             |

| 0.6         | b <sub>1</sub> x 0 + c <sub>1</sub> | 1 x a <sub>0</sub> + 0 | 1 x b <sub>1</sub> + 0 |             |

| 07          |                                     | ·                      |                        |             |

| 08          |                                     |                        |                        | a           |

|             |                                     | TABLE 9                | • .                    | -           |

| OP<br>CYCLE | REG<br>14B                                       | REG<br>15B             | REG<br>16B           | REG<br>111B |

|-------------|--------------------------------------------------|------------------------|----------------------|-------------|

| 01          | 0                                                | b <sub>2</sub>         | b <sub>1</sub>       | •           |

| 02          | . c <sub>2</sub>                                 | cl                     | b <sub>2</sub>       |             |

| 03          | 0                                                | a <sub>0</sub>         | 1                    |             |

| 04          |                                                  | -                      |                      |             |

| 05          | •                                                |                        |                      |             |

| 06          | c <sub>1</sub> x b <sub>2</sub> + c <sub>2</sub> | 1 x a <sub>0</sub> + 0 | $b_1 \times b_2 + 0$ |             |

| 07          |                                                  | •<br>•                 | <u>.</u>             |             |

| 08          |                                                  |                        |                      | a.          |

The selector control circuit 41b controls the selectors 53A, 54A, and 55A to load data into the registers 14A, 15A, and 16A, as shown in TABLE 8, and the selector control circuit 41b controls the selectors 53B, 54B, and 55B to load data into the registers 14B, 15B, and 16B, as shown in TABLE 9.

First, a calculation of the term  $\mathbf{a}_{\mathbf{i}}$  in the odd term

35

calculation circuit 10AA will be described.

### OPERATION CYCLE 01

Data 0,  $b_1$  , and 1 are loaded into the registers 14A, 15B, and 16A, and a calculation of ( $b_1$  x 1) is carried out at the multiplication circuit 17A.

## OPERATION CYCLE 02

Data 0 and ( $b_1$  x 1) are loaded into the registers 18A and 19A, and both data are added at the adder 110A, to obtain the result ( $b_1$  x 1 + 0). At the same time, data  $c_1$ ,  $b_1$  and 0 are loaded into the registers 14A, 15A, and 16A, and a calculation of ( $b_1$  x 0) is carried out at the multiplication circuit 17A.

### OPERATION CYCLE 03

The data ( $b_1 \times 1 + 0$ ) is stored in the register 111A.

The data  $c_1$  stored in the register 18A and the data ( $b_1 \times 0$ ) stored in the register 19A are added at the adder 110A, to obtain the result ( $b_1 \times 0 + c_1$ ). At the same time, data 0,  $a_0$ , and 1 are loaded into the registers 14A, 15A, and 16A, and a calculation of ( $a_0 \times 1$ ) is carried out at the multiplication circuit 17A.

### OPERATION CYCLE 04

The data ( $b_1 \times 1 + 0$ ) stored in the register 111A is transferred to the register 51A. The data 0 stored in the register 18A and the data ( $a_0 \times 1$ ) stored in the register 19A are added at the adder 111A, to obtain the result ( $a_0 \times 1 + 0$ ).

# OPERATION CYCLE 05

The data ( $b_1 \times 1 + c_1$ ) and ( $b_1 \times 0 + c_1$ ) are 30 sequentially loaded into the registers 51A and 52A, respectively. The data ( $a_0 \times 1 + 0$ ) is stored in the register 111A.

# OPERATION CYCLE 06

The data ( $a_0 \times 1 + 0$ ) stored in the register 111A 35 is transferred to the register 15A, and the data ( $b_1 \times 1 + 0$ ) stored in the register 52A is transferred to the register 16A. As a result, the data ( $a_0 \times 1 + 0$ ) x (1

$x b_1 + 0$ ) is obtained at the multiplication circuit 17A. The data ( $b_1 \times 0 + c_1$ ) stored in the register 51 is loaded into the register 14A.

## OPERATION CYCLE 07

The data  $(b_1 \times 0 + c_1)$  from the register 14A is loaded into the register 18A.

The data  $(b_1 \times 0 + c_1)$  stored in the register 18A and the data  $(a_0 \times 1 + 0) \times (1 \times b_1 + 0)$  stored in the register 19A are added at the adder 110A, to obtain the 10 resulting data

$$(a_0 \times 1 + 0) \times (1 \times b_1 + 0) + (b_1 \times 0 + c_1)$$

=  $a_0 \times b_1 + c_1$

=  $a_1$

## OPERATION CYCLE 08

The calculated data a is stored in the register VR00.

Next, a calculation of the term  $a_2$  in the even term calculation circuit 10BB will be described with reference to TABLE 9.

# 20 OPERATION CYCLE 01

Data 0,  $b_2$ , and  $b_1$  are loaded into the registers 14B, 15B, and 16B, and a calculation of  $(b_1 \times b_2)$  is carried out at the multiplication circuit 17B.

### OPERATION CYCLE 02

Data 0, and  $(b_1 \times b_2)$  are loaded into the registers 18B and 19B, and both data are added at the adder 110B, to obtain the result  $(b_1 \times b_2 + 0)$ . At the same time, data  $c_2$ ,  $c_1$ , and  $b_2$  are loaded into the registers 14B, 15B, and 16B, and a calculation of  $(c_1 \times b_1)$  is carried out at the multiplication circuit 17B.

## OPERATION CYCLE 03

The data ( $b_1 \times b_2 + 0$ ) is stored in the register 18B and ter 111B. The data  $c_2$  stored in the register 18B and the data ( $c_1 \times b_2$ ) stored in the register 19B are added at the adder 110B, to obtain the result ( $c_1 \times b_2 + c_2$ ). At the same time, data 0,  $a_1$ , and 1 are loaded into the registers 14B, 15B, and 16B, and a calculation of ( $a_0$ )

x 1) is carried out at the multiplication circuit 17B.

OPERATION CYCLE 04

The data ( $b_1 \times b_2 + 0$ ) stored in the register 111B is transferred to the register 51B. The data ( $c_1 \times b_2$ 5 +  $c_2$ ) is stored in the register 111B. The data 0 stored in the register 18B and the data ( $a_0 \times 1 + 0$ ) stored in the register 19B are added at the adder 110B to obtain the result ( $a_0 \times 1 + 0$ ).

## OPERATION CYCLE 05

The data  $(c_1 \times b_2 + c_2)$  and  $(b_1 \times b_2 + 0)$  are loaded into the registers 51B and 52B, respectively. The data  $(a_0 \times 1 + 0)$  is stored in the register 111B.

# OPERATION CYCLE 06

The data  $(c_1 \times b_2 + c_2)$  is loaded into the 15 register 14B.

The data stored in the register lllB is transferred to the register 15B, and the data  $(b_1 \times b_2 + 0)$  stored in the register 52B is transferred to the register 16B. As a result, data  $(a_0 \times 1 + 0) \times (b_1 \times b_2 + 0)$  is obtained at the multiplication circuit 17B.

# OPERATION CYCLE 07

The data  $(c_1 \times b_2 + c_2)$  stored in the register 18B and the data  $(a_0 \times 1 + 0) \times (b_1 \times b_2 + 0)$  are added at the adder 110B, to obtain the resulting data.

25

$$(a_0 \times 1 + 0) \times (b_1 \times b_2 + 0) + (c_1 \times b_2 + c_2)$$

$$= a_0 \times b_1 \times b_2 + b_2 \times c_1 + c_2$$

$$. = a_2$$

## OPERATION CYCLE 08

The calculated data  $a_2$  is stored in the regis-30 ter 111B and transferred to the vector register VR00 together with the data  $a_1$ .

The initial calculation is terminated.

Now, the normal calculation will be briefly described. The normal calculation is similar to the initial calculation, except for the data loading and transferring. Thus, the following description is mainly of the data loading.

# OPERATION CYCLE 04 - 11

During these cycles, the odd term  $\mathbf{a}_3$  and the even term  $\mathbf{a}_4$  are calculated.

The following TABLE 10 and TABLE 11 show data in the registers 14A, 15B, 16A and 111A, and data in the registers 14B, 15B, and 16B, and 111B.

TABLE 10

| OP<br>CYCLE | REG<br>14A                                       | REG<br>15A     | REG<br>16A                          | REG<br>111A    |

|-------------|--------------------------------------------------|----------------|-------------------------------------|----------------|

| 04          | 0                                                | b <sub>3</sub> | b <sub>2</sub>                      |                |

| 0.5         | c <sub>3</sub>                                   | c <sub>2</sub> | p³                                  |                |

| 06          |                                                  |                |                                     |                |

| 07          | •                                                |                |                                     |                |

| 08          |                                                  |                | 2.0                                 |                |

| 09          | b <sub>3</sub> x c <sub>2</sub> + c <sub>3</sub> | $\mathtt{a}_1$ | b <sub>2</sub> x b <sub>3</sub> + 0 |                |

| 10          | ·                                                |                | ~ <b>J</b>                          |                |

| 11          |                                                  |                |                                     | a <sub>3</sub> |

TABLE 11

| OP<br>CYCLE | REG<br>14B             | REG<br>15B     | REG<br>16B           | REG<br>111B |

|-------------|------------------------|----------------|----------------------|-------------|

| 04          | 0                      | b <sub>4</sub> | . <sup>b</sup> 3     |             |

| 05          | c <sub>4</sub>         | c <sub>3</sub> | b <sub>4</sub>       |             |

| 06          |                        |                |                      |             |

| 07          |                        |                |                      |             |

| 08          |                        |                |                      |             |

| 09          | $b_4 \times c_3 + c_4$ | a <sub>2</sub> | $b_3 \times b_4 + 0$ |             |

| 10          | •                      | -              | <u>.</u>             |             |

| 11          |                        |                |                      | a           |

# OPERATION CYCLES 07 - 14

During these operation cycles, the odd term  $\mathbf{a}_5$  and the even term  $\mathbf{a}_6$  are calculated.

The following TABLE 12 and TABLE 13 show data in the registers 14A, 15A, 16A, and 111A, and data in the registers 14b, 15b, 16b, and 111B.

TABLE 12

| OP<br>CYCLE | REG<br>14A                                       | REG<br>15A            | REG<br>16A           | REG<br>111A    |

|-------------|--------------------------------------------------|-----------------------|----------------------|----------------|

| 07          | . 0                                              | <b>b</b> <sub>5</sub> | b <sub>4</sub>       |                |

| 08          | c <sub>5</sub>                                   | c <sub>4</sub>        | b <sub>5</sub>       |                |

| 09          |                                                  |                       |                      |                |

| 10          |                                                  |                       |                      | •              |

| 11          |                                                  |                       |                      |                |

| 12          | b <sub>5</sub> x c <sub>4</sub> + c <sub>5</sub> | a <sub>3</sub>        | $b_4 \times b_5 + 0$ |                |

| 13          |                                                  |                       |                      |                |

| 14          |                                                  |                       |                      | a <sub>5</sub> |

TABLE 13

| OP<br>CYCLE | REG<br>14B                                       | REG<br>15B     | REG<br>16B           | REG<br>111B    |

|-------------|--------------------------------------------------|----------------|----------------------|----------------|

| 07          | . 0                                              | <sup>ь</sup> 6 | b <sub>5</sub>       |                |

| 08          | c <sub>6</sub>                                   | °5             | b <sub>6</sub>       |                |

| 09          |                                                  |                |                      |                |

| 10          |                                                  |                |                      |                |

| 11          |                                                  |                |                      |                |

| 12          | b <sub>6</sub> x b <sub>5</sub> + c <sub>6</sub> | a 4            | $b_5 \times b_6 + 0$ |                |

| 13          |                                                  |                |                      | a <sub>6</sub> |

| 14          |                                                  |                |                      |                |

Other pluralities of pairs of odd and even terms can be calculated in the same way as described above.

The present invention is not limited by the above embodiments. For example, in the above embodiments, first-order developed recurrent equations as expressed by the formulas (2) to (4) were described. When the recurrent equation as expressed by the formula (1) is modified by using a second-order development, the following formula is obtained.

$$a_{i} = a_{i-1} \times b_{i} + c_{i}$$

$$= a_{i-2} \times b_{i-1} \times b_{i} + b_{i} \times c_{i-1} + c_{i}$$

$$= a_{i-3} \times b_{i-2} \times b_{i-1} \times b_{1} + b_{i-2} \times b_{i-1} \times c_{i-2}$$

$$+ b_{i} \times c_{i-1} + c_{i}$$

Apparently, the above formula shows that there is no direct recurrent relationship between the terms  $a_i$  and  $a_{i-3}$ .

When an index  $\underline{i}$  is odd, for example, an odd index  $\underline{j}$  is 3 and 5, the above formula is expressed as follows:

$$j = 3$$

:  $a_3 = a_0 \times b_1 \times b_2 \times b_3 + b_1 \times b_2 \times c_1 + b_3 \times c_2 + c_3$  ... (6)

$j = 5$ :  $a_5 = a_2 \times b_3 \times b_4 \times b_5 + b_3 \times b_4 \times c_3 + b_5 \times c_4 + c_5$

... (7)

When an index  $\underline{i}$  is even, for example, an even index  $\underline{k}$  is 4 and 6, the above formula is expressed as follows:

$$k = 4: \quad a_4 = a_1 \times b_2 \times b_3 \times b_4 + b_2 \times b_3 \times c_2 + b_4 \times c_3 + c_4$$

$$k = 6: \quad a_6 = a_3 \times b_4 \times b_5 \times b_1 + b_4 \times b_5 \times c_4 + b_6 \times c_5 + c_6$$

$$(8)$$

From the above formulas (6) to (9), two odd terms  $a_3$  and  $a_5$ , and two even terms  $a_4$  and  $a_6$  can be simultaneously calculated at a same timing. Thus, the

operation time is further shortened. In this embodiment, an odd term calculation circuit is formed to calculate two adjacent odd terms, for example, a<sub>3</sub> and a<sub>5</sub>, at a same timing. Similarly, an even term calculation circuit is formed to calculate two adjacent even terms at a same timing. A data distribution circuit is formed to distribute data to the odd and even term calculation circuits so that the above formulas can be calculated.

#### 10 INDUSTRIAL APPLICABILITY

The vector processor of the present invention can be applied to a variety of data processing systems.

#### CLAIMS

- A vector processor including a vector instruction control unit (51) for controlling vector instructions, a vector storage access unit (52) for accessing input vector data and calculated data to a main storage unit, a vector calculation unit for calculating vector data under the control of the vector instruction unit, and a data distribution unit (54) for transferring data between the vector data access unit and the vector calculation unit,

- characterized in that the vector processor comprises a vector calculation unit including at least one odd term calculation circuit (10A, 10AA) and at least one even term calculation circuit (10B, 10BB), and a data distribution unit (40a, 40b) operatively connected to and cooperative with said vector calculation unit, to process a modified recurrent equation,

- each odd term calculation circuit being formed to calculate odd terms of said modified recurrent equation and include an adding circuit (110A), a multiplication circuit (17A), at least one data storage circuit (112A, 51A, 52A) holding a calculated odd term, and at least one feedback line (21A, 22A, 23A, 24A) for feeding back the calculated odd term to said

- 25 multiplication circuit and/or said adding circuit through said data storage circuit,

- each even term calculation circuit being formed to calculate even terms of said modified recurrent equation and include another adding circuit (110B),

- another multiplication circuit (17B), at least one another data storage circuit (112B, 51B, 52B) holding a calculated even term, and at least one another feedback line (21B, 22B, 23B, 24B) for feeding back the calculated even term to said another multiplication circuit and/or

- 35 said another adding circuit through said another data storage circuit, and

said data distribution unit including a first data setter for outputting zero, a second data setter for outputting one, first to sixth selectors (46A, 47A, 48A, 46B, 47B, 48B) for selecting input operands (a, b, using for calculating said recurrent equation, constant data 0 and 1 from said setters, and the calculated odd and even terms, and a selector control unit (40a, 40b) for controlling said selectors in a predetermined manner defined by said modified recurrent equation, to supply selected data to said odd and even term calculation circuits.

- 2. A vector processor according to claim 1, wherein said odd and even term calculation circuits are independently and simultaneously operable to calculate at least one pair of adjacent odd and even terms  $(a_i, a_{i+1})$  of said recurrent equation, at a same operation time.

- 3. A vector processor according to claim 2, wherein said data distribution unit (40a, 40b) comprises a first first-in and first-out type buffer (42) for inputting and outputting a plurality of said first operands (b<sub>i</sub>) as source multipliers and/or multiplicands, and a second first-in and first-out type buffer (43) for inputting and outputting a plurality of said second operands (c<sub>i</sub>) as source addends.

- 4. A vector processor according to claim 3, wherein said modified recurrent equation is expressed by the following formula when first order developed,

$$a_{i} = a_{i-2} \times b_{i-1} \times b_{i} + b_{i} \times c_{i-1} + c_{i}$$

said odd term calculation circuit calculating the following formulas, and

$$a_1 = a_0 \times b_1 + c_1$$

$a_j = a_{j-2} \times b_{j-1} \times b_j + b_j \times c_{j-1} + c_j$

where,

$$\underline{j}$$

is as odd integer,

$\underline{j} = 1, 3, \dots, \underline{n}$

said even term calculation circuit calculating the following formula:

$$a_k = a_{k-2} \times b_{k-1} \times b_k + b_k \times c_{k-1} + c_k$$

... (3)

where,  $\underline{k}$  is an even integer,  $\underline{k} = 2, 4, ..., n+1$

- 5. A vector processor according to claim 4, wherein said odd term calculation circuit comprises first to third feedback lines (21A, 22A, 23A), and is formed so that

- (a) said adding circuit (110A) receives an addend from said first selector (46A),

- (b) said multiplication circuit (17A) receives a multiplier and a multiplicand from said second and third selectors (47A, 48A),

- (c) said adding circuit (110A) receives a data multiplied at said multiplication circuit,

- (d) said data storage circuit (112A) receives a data added at said adding circuit,

- (e) said first selector (46A) receives constant of zero, said second operand (c<sub>i</sub>) from said second buffer (43), and said data stored in said data storage circuit (112A) through said second feedback line (22A),

- 25 (f) said second selector (47A) receives said constant of one, said first operand (b<sub>i</sub>), and said added data through said third feedback line (23A), and

- (g) said third selector (48A) receives said constant of one, an initial data (a<sub>0</sub>), said first and second operands from said first and second buffers (42, 43), and said multiplied data from said multiplication circuit (17A) through said first feedback line (21A), and

said even term calculation circuit

35 comprises another first to third feedback lines (21B, 22B, 23B), and is formed so that

(h) said another adding circuit (110B)

receives an addend from said fourth selector (46B),

- (i) said another multiplication circuit (17B) receives a multiplier and a multiplicand from said fifth and sixth selectors (47B, 48B),

- 5 (j) said another adding circuit (110B) receives a data multiplied at said another multiplication circuit.

- (k) said another data storage circuit (112B) receives a data added at said another adding

10 circuit,

- (1) said fourth selector (46B) receives said constant of zero, said second operand ( $c_i$ ) from said second buffer (43), and said data stored in said data storage circuit (112B) through said second feedback line (22B),

- (m) said fifth selector (47B) receives said constant of one, said first operand ( $b_i$ ), and said added data through said another third feedback line (23B), and

- 20 (n) said sixth selector (48B) receives said constant of one, said initial data  $(a_0)$ , said first and second operand  $(b_i, c_i)$  from said first and second buffer (42, 43), line (22B), and said multiplied data from said multiplication circuit (17B) through said another first feedback line (21B).

- 6. A vector processor according to claim 5, wherein said odd term calculation circuit (10A) comprises

- a first-stage first data storage cir-30 cuit (14A) connected to said first selector (46A), for temporarily storing data therefrom,

first stage second and third data storage circuits (15A, 16A) connected between said second and third selectors (47A, 48A), and said multiplication

- 35 circuit (17A), for temporarily storing data from said second and third selectors,

- a second-stage first data storage cir-

cuit (18A) connected between said first-stage first data storage circuit and said adding circuit, for temporarily storing data from said first-stage first data storage circuit,

- a second-stage second data storage circuit (19A), an input terminal thereof being connected to said multiplication circuit and an output terminal thereof being connected to said adding circuit and said first feedback line, said second-stage second data storage circuit temporarily storing data multiplied at said multiplication circuit, and

- a third-stage data storage circuit (111A) connected between said adding circuit and said data storage circuit (112A) and to said third feedback line, for temporarily storing data added at said adding circuit, and

said even term calculation circuit (10B) comprises

another first-stage first data storage

20 circuit (14B) connected to said another first selector (46B), for temporarily storing data therefrom,

another first-stage second and third data storage circuits (15B, 16B) connected between said another second and third selectors (47B, 48B), and said another multiplication circuit (17B), for temporarily storing data from said another second and third selectors.

another second-stage first data storage circuit (18B) connected between said another first-stage first data storage circuit and said another adding circuit, for temporarily storing data from said another first-stage first data storage circuit,

another second-stage second data storage circuit (19B), an input terminal thereof being connected to said another multiplication circuit and an output terminal thereof being connected to said another adding circuit and said another first feedback line, said

another second-stage second data storage circuit temporarily storing data multiplied at said another multiplication circuit, and

another third-stage data storage cir

5 cuit (lllB) connected between said another adding circuit and said another data storage circuit (ll2A) and to said another third feedback line, for temporarily storing data added at said another adding circuit.

7. A vector processor according to claim 6, 10 wherein,

at an initial operation time,

said odd term calculation circuit and

said data distribution circuit cooperate to calculate

the following terms during two operation times,

$$a_1 = a_0 \times b_1 + c_1$$

$a_1 = a_1 \times 1 + 0$

said even term calculation circuit and said data distribution circuit cooperate to calculate the following terms during said two operation times,

$$a_1 = a_0 \times b_1 + c_1$$

$a_2 = a_1 \times b_2 + c_2$

at a normal operation time after said initial operation time,

said odd term calculation circuit and

25 said data distribution circuit cooperate to calculate

each odd term of the following formula in each operation

time, and

$$a_{j} = a_{j-2} \times b_{j-1} \times b_{j} + b_{j} \times c_{j-1} + c_{j}$$

where,  $j = 3, 5, \dots, n$

said even term calculation circuit and said data distribution circuit cooperate to calculate each even term of the following formula in said operation time.

$$a_{k} = a_{k-2} \times b_{k-1} \times b_{k} + b_{k} \times c_{k-1} + c_{k}$$

where,  $k = 4, 6, \dots, n+1$

8. A vector processor according to claim 7, wherein each said operation time comprises a plurality

35

of operation cycles of said vector processor,

said operation times are identical for

calculating each term, and

adjacent operation times for calculating adjacent terms are partially overlapped.

- 9. A vector processor according to claim 8, wherein said data distribution unit (40a) receives data from said third-stage and said another third-stage data storage circuits (110A, 110B), and outputs said data to said vector storage access unit (52).

- 10. A vector processor according to claim 9, wherein said vector storage access unit comprises a vector register unit for temporarily storing said input operands and said calculated odd and even terms, and

- said data distribution circuit transfers said input operands and said calculated odd and even terms.

- 11. A vector processor according to claim 4,

wherein said odd term calculation circuit comprises

20 a feedback line (24A), and first and second data storage

circuits (51A, 52A) connected in series for storing

calculated odd terms supplied through said feedback line

(24A), and is formed so that

- (a) said adding circuit (110A) receives 25 an addend from said first selector (53A),

- (b) said multiplication circuit (17A) receives a multiplier and a multiplicand from said second and third selectors (54A, 55A),

- (c) said adding circuit (110A) receives 30 a data multiplied at said multiplication circuit,

- (d) said first data storage circuit (51A) receives a data added at said adding circuit,

- (e) said second data storage circuit (52A) receives a data from said first data storage circuit,

- (f) said first selector (53A) receives said constant of zero, said second operand ( $c_i$ ) from

said second buffer (43), and a data from said first data storage circuit,

- (g) said second selector (54A) receives said constant of zero, an initial data  $(a_0)$ , said first and second operand  $(b_i, c_i)$ , and said data added at said adding circuit through said feedback line, and

- (h) said third selector (55A) receives said constant of one, said first operand from said first buffer (42), and said data stored in said second data storage circuit (52A),

said even term calculation circuit comprises another feedback line (24B), and another first and second data storage circuits (51B, 52B) connected in series and for storing said calculated even terms supplied through said another feedback line (24B), and is formed so that

- (i) said another adding circuit (110B) receives an addend from said fourth selector (53B),

- (j) said another multiplication cir-20 cuit (17B) receives a multiplier and a multiplicand from said fifth and sixth selectors (54B, 55B),

- (k) said another adding circuit (110B)

receives a data multiplied at said another multiplication circuit,

- 25 (1) said another first data storage circuit (51B) receives a data added at said another adding circuit,

- (m) said another second data storage circuit (52B) receives a data from said another first 30 data storage circuit,

- (n) said fourth selector (53B) receives said constant of zero, said second operand ( $c_i$ ) from said second buffer (43), and a data from said first data storage circuit,

- 35 (o) said fifth selector (54B) receives said constant of zero, said initial data  $(a_0)$ , said first and second operands  $(b_i, c_i)$ , and said data added

at said another adding circuit through said another feedback line, and

- (p) said sixth selector (55B) receives said constant of one, said first operand from said first buffer (42), and said data stored in said another second data storage circuit (52B),

- 12. A vector processor according to claim 11, wherein said odd term calculation circuit (10AA) comprises

- a first-stage first data storage circuit (14A) connected to said first selector (53A), for temporarily storing a data therefrom,

first-stage second and third data storage circuits (15A, 16A) connected between said second and third selectors (54A, 55A) and said multiplication circuit (17A), for temporarily storing data from said second and third selectors,

a second-stage first data storage circuit (18A) connected between said first-stage first data

storage circuit and said adding circuit, for temporarily

storing data from said first-stage first data storage

circuit,

a second-stage second data storage circuit (19A), an input terminal thereof being connected to said multiplication circuit and an output terminal thereof being connected to said adding circuit, said second-stage second data storage circuit temporarily storing data multiplied at said multiplication circuit, and

- a third-stage data storage circuit (111A) connected between said adding circuit and said data storage circuit (51A) through said feedback line, for temporarily storing data added at said adding circuit, and

- 35 said even term calculation circuit (10B) comprises

another first-stage first data storage

circuit (14B) connected to said another first selector (53B), for temporarily storing data therefrom, another first-stage second and third data storage circuits (15B, 16B) connected between said another second and third selectors (54B, 55B) and said another multiplication circuit (17B), for temporarily storing data from said another second and third selectors,

another second-stage first data storage

10 circuit (18B) connected between said another first-stage

first data storage circuit and said another adding

circuit, for temporarily storing data from said another

first-stage first data storage circuit,

another second-stage second data storage

circuit (19B), an input terminal thereof being connected to said another multiplication circuit and an output terminal thereof being connected to said another adding circuit, said another second-stage second data storage circuit temporarily storing data multiplied at said

another multiplication circuit, and

another third-stage data storage circuit (111B) connected between said another adding

circuit and said another data storage circuit (51B)

through said another feedback line, for temporarily

25 storing data added at said another adding circuit.

13. A vector processor according to claim 12, wherein,

at an initial operation time,

said odd term calculation circuit and

30 said data distribution circuit cooperate to calculate

the following terms during two operation times,

$$a_1 = a_0 \times b_1 + c_1$$

$a_1 = a_1 \times 1 + 0$

said even term calculation circuit and 35 said data distribution circuit cooperate to calculate the following terms during said two operation times,

$$a_1 = a_0 \times b_1 + c_1$$

$a_2 = a_1 \times b_2 + c_2$