**(19) 대한민국특허청(KR)**

**(12) 공개특허공보(A)**

|                                          |                                                                                                                                                |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| (51) Int. Cl. <sup>5</sup><br>H03K 21/00 | (11) 공개번호      특 1993-0005374<br>(43) 공개일자      1993년03월23일                                                                                    |

| (21) 출원번호      특 1992-0014524            |                                                                                                                                                |

| (22) 출원일자      1992년08월12일               |                                                                                                                                                |

| (30) 우선권주장                               | 91-201771 1991년08월12일 일본(JP)<br>92-209991 1992년08월06일 일본(JP)                                                                                   |

| (71) 출원인                                 | 후지쓰 가부시끼가이샤 세끼사와 요시<br>일본국 가나가와肯 가와사끼시 나카하라구 가미고다나까 1015                                                                                       |

| (72) 발명자                                 | 다마무라 마사야<br>일본국 가나가와肯 가와사끼시 나카하라구 가미고다나까 1015<br>시오쓰 신이찌<br>일본국 가나가와肯 가와사끼시 나카하라구 가미고다나까 1015<br>노무라 가쓰노부<br>일본국 가나가와肯 가와사끼시 나카하라구 가미고다나까 1015 |

| (74) 대리인                                 | 문병암                                                                                                                                            |

**심사청구 : 있음****(54) 존스 타입 카운터를 이용한 카운터 회로와 그 응용 회로****요약**

내용 없음.

**대표도****도11****명세서****[발명의 명칭]**

존스 타입 카운터를 이용한 회로와 그 응용회로

**[도면의 간단한 설명]**

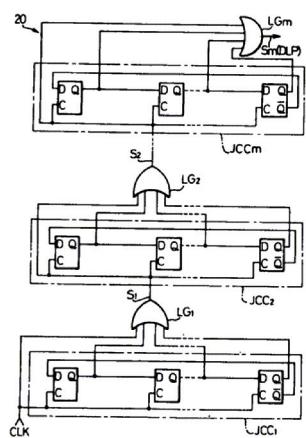

제11도는 본 발명의 1차 구조에 따른 카운터 회로의 기본 구조를 도시한 회로도,

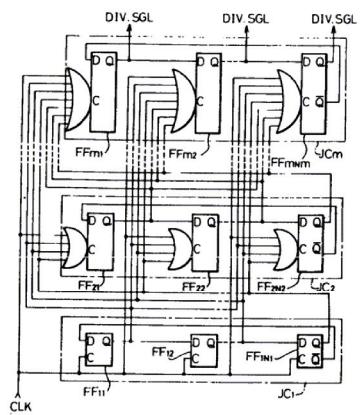

제12도는 본 발명의 2차 구조에 따른 분할 신호 발생 회로의 기본 구조를 도시한 회로도,

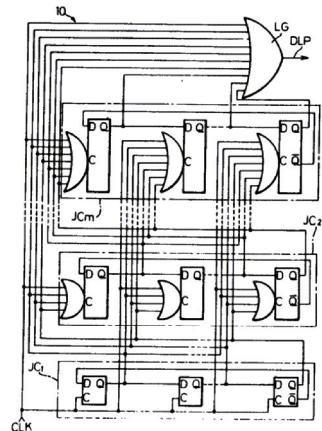

제13도는 본 발명의 3차 구조에 따른 카운터 회로의 기본 구조를 도시한 회로도,

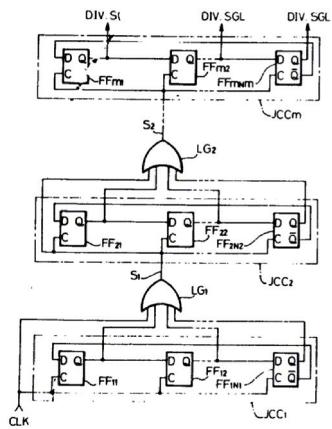

제14도는 본 발명의 4차 구조에 따른 분할 신호 발생 회로의 기본 구조를 도시한 회로도.

본 내용은 요부공개 건이므로 전문 내용을 수록하지 않았음

**(57) 청구의 범위****청구항 1**

(K-1) 차 단계 카운터내에 있는 플립플롭의 각 출력단(Q)에서의 신호가 K차 단계이상의 각 카운터내에 있는 플립플롭의 각 클럭입력단(C)에 동시에 입력되는 각각의 클럭입력단(C)에서 클럭신호(CLK)를 받는 각각의 플립프롭이 종속 결합으로 연결된 다수의 플립플롭(FF<sub>11</sub>-FF<sub>1N1</sub> FF<sub>21</sub>-FF<sub>2N2</sub>, ..., FF<sub>M1</sub>-FF<sub>MN1</sub>)을 포함하는 카운터 회로.

**청구항 2**

제1항에 있어서, 2단계의 각 카운터는 클럭신호와 이전 단계 또는 현 단계의 각 카운터내에서 플립플롭

에 대한 각 출력단으로부터의 신호를 동시에 받기 위한 게이트 수단( $G_{21}$   $G_{22}$ )을 포함하는 카운터 회로.

### 청구항 3

(K-1) 차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호가 K차 단계이상의 각 카운터내에 있는 플립플롭의 각 클럭입력단에 동시에 입력되고, 각 클럭입력단에서 클럭신호를 받는 각각의 플립플롭이 종속결합으로 연결된 다수의 플립플롭을 포함하는 M단계 존슨 타입카운터를 포함하는 카운터 회로, 클럭신호를 카운터회로 내에 플립플롭의 모든 출력단에서의 신호의 논리합을 발생시켜 M차 신호(DLP)로서의 결합을 출력하는 논리게이트(LG)를 포함하는 분할 신호발생 회로.

### 청구항 4

제3항에 있어서, 2차 단계의 각 카운터는 클럭신호와 이전 단계 또는 현 단계의 각 카운터내에서 플립플롭에 대한 각 출력단으로부터의 신호를 동시에 받기 위한 게이트 수단( $G_{21}$   $G_{22}$ )을 포함하는 카운터 회로.

### 청구항 5

종속 결합으로 연결된 다수의 플립플롭( $FF_{11}$ - $FF_{1N1}$   $FF_{21}$ - $FF_{2N2}$ , ...,  $FF_{m1}$ - $FF_{mNm}$ )을 포함하는 m단계의 존슨 타입 카운터(JCC<sub>1</sub>-JCC<sub>m</sub>), 클럭신호(CLK)가 1단계 카운터(JCC<sub>1</sub>)내에 있는 플립플롭의 각 클럭 입력단(C)에 동시에 입력되는 존슨 타입 카운터의 각 단계 사이에 연결된 (m-1) 논리 게이트(LG<sub>1</sub>-LG<sub>M-1</sub>), 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 출력단(Q)에서의 신호의 합이 1차 논리 게이트(LG<sub>1</sub>)에 발생되어 1차 신호(S<sub>1</sub>)로서 입력되고, 1차 신호를 2단계 카운터(JCC<sub>2</sub>)내에 있는 플립플롭의 각 클럭 입력단(C)에 동시에 입력되며, 클럭신호와 2단계 카운터내에 있는 플립플롭의 각 출력단(Q)에서의 신호의 합이 2차 논리 게이트(LG<sub>2</sub>)에 의해 발생되는 2차 신호(S<sub>2</sub>)로서 입력되고, 동일한 방법으로 (m-1)차 신호(S<sub>m-1</sub>)는 m차 단계 카운터(KJCC<sub>m</sub>)내에 있는 플립플롭의 각 클럭 입력단(C)에 동시에 입력되는 카운터 회로.

### 청구항 6

클럭신호가 1단계 카운터내에 있는 플립플롭의 각 출력단에 동시에 입력되는 존슨 타입 카운터의 각 단계사이에 연결된 (m-1)논리게이트와 종속결합으로 연결된 다수의 플립플롭을 포함하는 m단계의 존슨 타입 카운터를 포함하는 카운터 회로, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호는 논리합 1차 논리게이트에 의해 발생되어 1차 신호로서 출력되며, 1차 신호가 2단계 카운터 내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고, 1차 신호와 2단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 2차 논리게이트에 의해 발생되어 2차 신호로 입력되며, 동일한 방법으로 (m-1)차 신호는 m차 단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고, (m-1)차 신호와 m차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호(S<sub>m</sub>, DLP)로서 나타난 결과를 출력시키는 논리게이트(LG<sub>m</sub>)가 있는 카운터 회로를 포함하는 분할 신호 발생회로.

### 청구항 7

(K-1) 차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호가 K차 단계이상의 각 카운터내에 있는 플립플롭의 각 클럭입력단에 동시에 입력되는 각각의 입력단에서 클럭 신호를 받기 위한 각각의 플립플롭이 종속결합으로 연결된 다수의 플립플롭을 포함하는 m단계의 존슨 타입 카운터를 포함하는 카운터 회로, 클럭신호와 카운터 회로 내에 있는 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호(DLP)로서 나타난 결과를 출력시키는 논리게이트(LG), 클럭신호(CLK)에 반응하여 직렬 데이터(SK)를 입력하고 직렬 데이터를 다수 비트의 병렬 데이터를 변환시키기 위한 수단(11), 분할 신호 발생 회로로부터 m차 신호(DLP) 출력에 반응하여 병렬 데이터를 래칭하고 출력시키기 위한 수단(11), 분할 신호 발생 회로로부터 m차 신호(DLP) 출력에 반응하여 병렬데이터를 래칭하고 출력시키기 위한 수단(12)이 있는 분할 신호 발생 회로(10,20)를 포함하는 데이터 변환회로.

### 청구항 8

종속 결합을 연결된 다수의 플립플롭이 있는 m단계의 존슨 타입 카운터가 포함된 카운터 회로, 클럭신호가 1단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되는 존슨 타입 카운터의 각 단계 사이에 연결된 (m-1) 논리게이트, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 1차 논리 게이트에 의해 발생되어 1차 신호로서 출력되며, 1차 신호가 2단계 카운터에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고, 1차 신호와 2단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 2차 논리게이트에 의해 발생되어 2차 신호로서 출력되며, 동일한 방법으로 (m-1)차 신호가 m차 단계 카운터내에 있는 플립플롭의 각 출력단에 동시에 입력되고, (m-1)차 신호와 m차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호(DLP)로서 나타난 결과를 출력시키는 논리게이트(LG<sub>m</sub>), 클럭신호(CLK)에 반응하여 직렬 데이터(SK)를 입력하고 직렬데이터를 다수 비트의 병렬데이터로 변환시키기 위한 수단(10), 분할 신호 발생회로로부터 m차 신호(DLP) 출력에 반응하여 병렬데이터를 래칭하고 출력시키기 위한 수단(12)이 있는 분할 신호 발생 회로(10,20)를 포함하는 데이터 변환회로.

### 청구항 9

(K-1) 차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호가 K차 단계이상의 각 카운터내에 있는 플립플롭의 각 클럭입력단에 동시에 입력되는 각 클럭 입력단에서 클럭 신호를 받는 플립플롭이 종속결합으로 연결된 다수의 플립플롭을 포함하는 m단계의 존슨 타입 카운터를 포함하는 카운터 회로, 클럭신호와 카운터회로 내에 있는 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호(DLP)로서 나타난 결과를 출력시키는 논리게이트(LG), 분할 신호 발생회로로부터 m차 신호(DLP) 출력에 반응하여

수 비트의 병렬데이터(PD)를 입력하고 병렬 데이터를 클럭신호(CLK)에 반응하여 직렬데이터(SD)로 변환 시켜 변환된 직렬 데이터를 출력시키기 위한 수단(13)이 있는 분할 신호 발생회로(10,20)를 포함하는 데 이타 변환회로.

#### 청구항 10

클럭신호가 1단계 카운터내에 있는 플립플롭의 각 클럭입력단에 동시에 입력되는 존슨 타입 카운터의 각각의 단계 사이에 연결된 (m-1) 논리게이트와 종속결합으로 연결된 다수의 플립플롭을 포함하는 m단계의 존슨 타입 카운터를 포함하는 카운터 회로, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 클럭출력단에서의 신호의 논리합이 2차 논리게이트에 의해 발생되어 2차 신호로서 출력되며, 동일한 방법으로 (m-1)차 신호는 m차 단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고, (m-1)차 신호는 m차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호로서 나타나는 결과를 출력시키는 논리게이트(LG<sub>m</sub>), 분할신호 발생회로로부터 m차 신호(DLP) 출력에 반응하여 다수 비트의 병렬 데이터(PD)를 입력시키고 클럭 신호(CLK)에 반응하여 병렬 데이터를 직렬 데이터(SD)로 변환된 직렬 데이터를 출력시키기 위한 수단(13)이 있는 분할 신호 발생회로(10,20)를 포함하는 데이터 변환회로.

#### 청구항 11

각각의 클럭 입력단(C)에서 클럭신호(CLK)를 동시에 받으며 종속결합으로 연결된 다수의 플립플롭(FF<sub>1</sub>-FF<sub>N</sub>)을 포함하는 존슨 타입 카운터(JC), 클럭 신호와 카운터내에 있는 플립플롭의 각 출력단(Q, QX)에서의 신호의 논리합을 발생시키기 위한 게이트수단(GT)과, 클럭 신호와 각 플립플롭의 각 출력단에서의 신호가 게이트 수단에 입력되는 각각의 시간을 규제하기 위한 버퍼 수단(G, G<sub>1</sub>-G<sub>2</sub>)을 포함하는 존슨 타입 카운터와 최종단계 플립프롭(FF<sub>N</sub>)의 비변환 및 변환 출력이 1단계 플립플롭(FF<sub>1</sub>)의 데이터 변환 및 데이터 비변환 입력이 되며, 플립플롭의 각 차등신호 출력에 대한 동작 진폭 레벨이 다른 회로보다 적게 설정되는 카운터 회로.

#### 청구항 12

제11항에 있어서, 버퍼 수단이 위상을 정형화하기 위한 수단(G<sub>0</sub>)과 각각의 플립플롭으로부터 각각 적은 진폭의 차등 신호를 받고 게이트 수단내에서 논리 연산을 하기에 필요하고 충분한 진폭 레벨까지 차등 신호를 증폭하기 위한 수단(G<sub>1</sub>, G<sub>2</sub>)을 포함하는 카운터 회로.

#### 청구항 13

(K-1)차 단계카운터 내에 있는 플립플롭의 각 출력단(Q)에서의 신호가 K차 단계 이상의 각 카운터내에 있는 플립플로의 각 클럭 입력단에 동시에 입력되는 각각 클럭 입력단(C)에서 클럭 신호(CLK)를 받는 각각의 플립플롭이 종속결합으로 연결된 다수의 플립플롭(FF<sub>11</sub>, FF<sub>12</sub>, FF<sub>21</sub>, FF<sub>11</sub>)이 있는 m단계의 존슨 타입 카운터(JC, JC<sub>2</sub>)를 포함하는 카운터 회로, 클럭신호와 자체 카운터내에 있는 플립플롭의 각 출력단에서의 신호가 2단계 이상의 각 카운터내에 있는 플립플롭의 각 클럭 입력단에 입력되는 각각의 시간을 규제하기 위한 버퍼수단(G<sub>0</sub>, G<sub>1</sub>, G<sub>2</sub>)을 포함하는 1단계 존슨타입 카운터(JC), 최종단계 플립플롭(FF<sub>12</sub>)의 비변환 및 변환 출력이 1단계 플립플롭의 데이터 변환 및 데이터 비변환 입력단에 입력되며, 자체 카운터내에 있는 플립플롭의 각 차등 신호 출력에 대한 동작 진폭레벨이 다른 회로보다 적게 설정되는 것을 포함하는 분할 신호 발생회로.

#### 청구항 14

제13항에 있어서, 클럭신호와 카운터 회로내에 있는 모든 플립플롭의 각 출력단에서의 신호는 논리합을 발생시켜 m차 신호로서 나타나는 결과를 출력시키는 논리게이트(G)가 포함되는 분할 신호 발생회로.

#### 청구항 15

제14항에 있어서, 버퍼 수단은 위상 정형화를 위한 수단(G<sub>0</sub>)과 각 플립플롭으로부터 적은 진폭의 각 차등 신호를 받고 게이트 수단내에 있는 논리동작을 위해 필요하고 충분한 진폭 레벨까지 차등신호를 증폭하기 위한 수단(G<sub>1</sub>, G<sub>2</sub>)을 포함하는 신호분할 발생회로.

#### 청구항 16

제15항에 있어서, 2단계의 각 카운터가 이전 단계 또는 현단계의 각 카운터 내에 있는 플립플롭의 각 출력단으로부터의 신호와 클럭신호를 동시에 받기 위한 게이트 수단(G<sub>21</sub>, G<sub>22</sub>)을 포함하는 분할 신호 발생회로.

#### 청구항 17

클럭신호(CLK)가 1단계 카운터에 있는 플립플롭의 각 클럭 입력단(C)에 동시에 입력되는 존슨타입 카운터의 각 단계 사이에 연결된(m-1) 논리게이트(LG<sub>1</sub>)와 종속 결합으로 연결되 다수의 플립플롭(FF<sub>11</sub>, FF<sub>12</sub>, FF<sub>21</sub>, FF<sub>11</sub>)이 있는 m단계의 존슨 타입 카운터(JC, JCC<sub>2</sub>)를 포함하는 카운터 회로, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 클럭출력단에서의 신호의 논리합이 1차 논리게이트에 의하여 발생되어 1차 신호로서 출력되며, 1차 신호가 2단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고, 1차 신호와 2단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 2차 논리게이트에 의해 발생되어 2차 신호로서 출력되며, 동일한 방법으로 (m-1) 차 신호가 m차 단계 카운터내에 있는 플립플

룹의 각 클럭 입력단에 동시에 입력되고, 클럭신호와 자체 카운터내에 있는 각 플립플롭의 각 출력단에서의 신호가 1차 논리게이트에 입력되는 시간을 규제하기 위한 버퍼수단( $G_0, G_1, G_2$ )을 포함하는 1단계 존슨타입 카운터(JC), 최종단계 플립플롭(FF<sub>12</sub>)의 비변환 및 변환 출력이 1단계 플립플롭의 데이터 변환 및 데이터 비변환 입력단에 입력되며, 자체 카운터내에 있는 플립플롭의 각 차등 신호 출력의 동작 진폭레벨이 다른 회로보다 적게 설정되는 분할 신호 발생회로.

#### 청구항 18

제17항에 있어서, (m-1)차 신호와 m차 단계 카운터내에 있는 플립플롭의 각 출력단에의 신호의 논리합을 발생시켜 m차 신호로서 (DLP) 나타나는 결과를 출력시키는 논리게이트(LG<sub>2</sub>)를 포함하는 분할 신호 발생회로.

#### 청구항 19

제18항에 있어서, 버퍼 수단이 위상 정형화를 위한 수단( $G_0$ )과 각 플립플롭으로부터 작은 진폭의 각각의 차등신호를 받고 게이트 수단내에 있는 논리동작을 위해 필요하고 충분한 진폭레벨까지 차등신호를 증폭하기 위한 수단( $G_1, G_2$ )을 포함하는 분할 신호 발생회로.

#### 청구항 20

(K-1)차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호가 K차 단계이상의 각 카운터내에 있는 플립플롭의 각 클럭입력단에 동시에 입력되는 각각의 입력단에서 클럭 신호를 받는 플립플롭이 종속 결합으로 연결된 다수의 플립플롭이 있는 m단계의 존슨 타입 카운터를 포함하는 카운터 회로, 클럭신호와 카운터 회로내에 있는 모든 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호로서 나타나는 결과를 출력시키는 논리게이트, 클럭신호와 2단계 이상의 각 카운터내에 있는 플립플롭의 각 클럭 입력 단에 입력되는 각각의 시간을 규제하기 위한 버퍼 수단을 포함하는 1단계 존슨타입 카운터, 최종 단계의 비변환 및 변환 출력을 1단계 플립플롭의 데이터 변환 및 데이터 비변환 입력단에 입력시키고, 자체 카운터내에 있는 플립플롭의 각 차등 신호 출력의 동작 진폭레벨이 다른 회로보다 적게 설정되며, 클럭신호(CLK,DCLK)에 반응하여 직렬 데이터(SD)를 입력시키고 직렬데이터를 다스 비트의 병렬 데이터(OUT<sub>16</sub>-OUT<sub>1</sub>)로 변환시키기 위한 수단(FF<sub>101</sub>-FF<sub>116</sub>), 분할 신호 발생회로로부터 m차 신호(DLP) 출력에 반응하여 병렬 데이터를 래칭하고 출력시키기 위한 수단(FF<sub>201</sub>-FF<sub>216</sub>)이 있는 분할 신호 발생회로(10a, )를 포함하는 데이터 디멀티플렉서 회로.

#### 청구항 21

클럭신호가 1단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되는 존슨 타입 카운터의 각 단계 사이에 연결된 (m-1) 논리게이트와 종속 결합으로 연결된 다수의 플립플롭이 있는 m단계의 존슨 타입 카운터가 포함되는 카운터 회로, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 1차 논리게이트에 의해 발생되어 1차 신호로서 출력되며, 1차 신호가 2단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 2차 논리게이트에 의해 발생되어 2차 신호로서 출력되고, 동일한 방법으로, (m-1)차 신호가 m차 단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되며, (m-1)차 신호와 m차 단계 카운터내에 있는 플립플롭의 각 출력단에서의 논리합을 발생시켜 m 차 신호로서 나타나는 결과를 출력시키는 논리게이트, 클럭신호와 자체 카운터내에 있는 각각 플립플롭의 각 출력단에서의 신호가 1차 논리게이트에 입력되는 각각의 시간을 규제하기 위한 버퍼 수단을 포함하는 1단계 존슨 타입 카운터, 최종단계 플립플롭의 비변환 및 변환 출력이 1단계 플립플롭의 데이터 변환 및 데이터 비변환 입력단에 입력되고, 자체 카운터내에 있는 플립플롭의 각 차등신호 출력의 동작 진폭레벨이 다른 회로보다 적게 설정되고, 클럭신호(CLK,DCLK)에 반응하여 직렬데이터(SD)를 입력시키고 직렬데이터를 다수 비트의 병렬데이터(OUT<sub>16</sub>-OUT<sub>1</sub>)로 변환시키는 수단(FF<sub>101</sub>-FF<sub>116</sub>), 분할신호 발생회로로부터 m차 신호(DLP) 출력에 반응하여 병렬데이터를 래칭하고 출력시키기 위한 수단(FF<sub>201</sub>-FF<sub>216</sub>)이 있는 분할신호 발생회로를 포함하는 데이터 디멀티플렉서 회로.

#### 청구항 22

K단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호가 K차 단계 이상의 각 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되는 각각의 클럭 입력단에서 신호를 받는 각각의 플립플롭이 종속 결합으로 연결된 다수의 플립플롭이 있는 m단계의 존슨 타입 카운터를 포함하는 카운터 회로, 클럭신호와 카운터 회로내에 있는 모든 플립플롭의 각 출력단에서의 신호의 논리합을 발생시켜 m차 신호로서 나타나는 결과를 출력시키는 논리게이트, 클럭신호와 자체 카운터 내에 있는 각 플립플롭의 각 클럭 입력단에서의 신호가 2단계 이상의 각 카운터내에 있는 플립플롭의 각 클럭 입력단에 입력되는 각각의 시간을 규제하기 위한 버퍼 수단을 포함하는 1단계 존슨 타입 카운터, 최종단계 플립플롭의 비변환 및 변환 출력이 1단계 플립플롭의 데이터 변환 및 데이터 비변환 입력단에 입력되고, 자체 카운터내에 있는 플립플롭의 각 차등 신호 출력의 동작 진폭레벨이 다른 회로보다 적게 설정되며, 분할 신호 발생회로로부터 m차 신호(DLP) 출력에 반응하여 다수 비트의 병렬 데이터(D<sub>16</sub>-D<sub>1</sub>)를 입력시키고 클럭신호(CLK,DCLK)에 반응하여 병렬 데이터를 직렬데이터(OUT)로 변환된 직렬데이터를 출력시키기 위한 수단(SEL<sub>1</sub>-SEL<sub>16</sub>, FF<sub>302</sub>-FF<sub>316</sub>)이 있는 분할신호 발생회로(10a')가 포함되는 데이터 디멀티플렉서 회로.

#### 청구항 23

클럭신호가 1단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되는 존슨 타입 카운터의 각각의 단계 사이에 연결된 (m-1) 논리게이트와 종속 결합으로 연결된 다수의 플립플롭이 있는 m단계의

존슨 탑입 카운터를 포함하는 카운터 회로, 클럭신호와 1단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 1차 논리게이트에 의해 발생되어 1차 신호로서 출력되며, 1차 신호가 2단계 카운터내에 있는 플립플롭의 각 출력단에 동시에 입력되고, 1차 신호와 2단계 카운터내에 있는 플립플롭의 각 출력단에서의 신호의 논리합이 2차 논리게이트에 의해 발생되어 2차 신호로서 출력되며, 동일한 방법으로,  $(m-1)$ 차 시호가  $m$ 차 단계 카운터내에 있는 플립플롭의 각 클럭 입력단에 동시에 입력되고,  $(m-1)$ 차 신호와  $m$ 차 단계 카운터내에 있는 플립플롭의 각 출력단에서 논리합을 발생시켜  $m$ 차 신호로서 나타나는 결과를 출력시키는 논리게이트, 클럭신호와 자체 카운터내에 있는 각 플립플롭의 각 출력단에서의 신호가 1차 논리게이트에 입력되는 각각의 시간을 규제하기 위한 버퍼 수단을 포함하는 1단계 존슨 탑입 카운터, 최종단계 플립플롭의 비변환 및 변환 출력이 1단계 플립플롭의 데이터 변환 및 데이터 비변환 입력단에 입력되고, 자체 카운터내에 있는 플립플롭의 각 차등 신호 출력이 동작의 병렬 데이터( $D_{16}-D_1$ )를 입력시키고 클럭신호(CLK,DCLK)에 반응하여 병렬 데이터를 직렬데이터(OUT)로 변환시켜 변환된 직렬 데이터를 출력시키기 위한 수단(SEL<sub>1</sub>-SEL<sub>16</sub>, FF<sub>302</sub>-FF<sub>316</sub>)이 있는 분할신호 발생회로를 포함하는 데이터 디멀티플렉서 회로.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

## 도면

### 도면11

### 도면12

도면13

도면14