(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4618639号

(P4618639)

(45) 発行日 平成23年1月26日(2011.1.26)

(24) 登録日 平成22年11月5日(2010.11.5)

(51) Int.Cl.

F 1

H01L 27/14 (2006.01)

H01L 27/14

D

H01L 23/02 (2006.01)

H01L 23/02

F

H04N 5/369 (2011.01)

H04N 5/335 690

請求項の数 10 (全 14 頁)

(21) 出願番号

特願2005-45284 (P2005-45284)

(22) 出願日

平成17年2月22日(2005.2.22)

(65) 公開番号

特開2006-237051 (P2006-237051A)

(43) 公開日

平成18年9月7日(2006.9.7)

審査請求日

平成20年2月14日(2008.2.14)

(73) 特許権者 390022471

アオイ電子株式会社

香川県高松市香西南町455番地の1

(74) 代理人 100099173

弁理士 濵谷 孝

(72) 発明者 香西 克彦

香川県高松市香西南町455番地の1 ア

オイ電子株式会社内

審査官 恩田 春香

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体ウェハーに形成された複数の撮像用半導体素子の各受光部に保護膜を形成する工程と、

前記半導体ウェハーを撮像用半導体素子毎に分割する工程と、

前記分割された撮像用半導体素子を大判の回路基板へ実装する工程と、

前記各撮像用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の撮像用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研磨する工程と、

前記保護膜を除去する工程と、

前記撮像用半導体素子、前記研磨された樹脂上にカバーを貼り付ける工程と、

前記大判の回路基板を切断して個別の撮像用半導体装置に分割する工程と、

前記カバーを剥離する工程と

を有することを特徴とする撮像用半導体装置の製造方法。

## 【請求項 2】

前記請求項 1 に記載の撮像用半導体装置の製造方法で製造され、回路基板に実装された撮像用半導体素子と、該撮像用半導体素子の受光部上に樹脂パッケージの空洞部とを備えることを特徴とする撮像用半導体装置。

**【請求項 3】**

半導体ウェハーに形成された複数の撮像用半導体素子の各受光部に保護膜を形成する工程と、

前記半導体ウェハーを撮像用半導体素子毎に分割する工程と、

前記分割された撮像用半導体素子を大判の回路基板へ実装する工程と、

前記各撮像用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の撮像用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、

前記撮像用半導体素子、前記研摩された樹脂上に光学的に透明なカバー部材を貼り付ける工程と、

前記大判の回路基板を切断して個別の撮像用半導体装置に分割する工程と、

を有することを特徴とする撮像用半導体装置の製造方法。

**【請求項 4】**

前記光学的に透明なカバー部材は、ガラスでなることを特徴とする請求項 3 の撮像用半導体装置の製造方法。

**【請求項 5】**

前記請求項 3 又は請求項 4 に記載の撮像用半導体装置の製造方法で製造され、回路基板に実装された撮像用半導体素子と、該撮像用半導体素子の受光部上の樹脂パッケージの空洞部と、該空洞部を塞ぐカバーガラスとを備えることを特徴とする撮像用半導体装置。

**【請求項 6】**

半導体ウェハーに形成された複数の受光用半導体素子の各受光部に保護膜を形成する工程と、

前記半導体ウェハーを受光用半導体素子毎に分割する工程と、

前記分割された受光用半導体素子を大判の回路基板へ実装する工程と、

前記各受光用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の受光用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

前記保護膜を除去する工程と、

前記受光用半導体素子、前記研摩された樹脂上にカバーを貼り付ける工程と、

前記大判の回路基板を切断して個別の受光用半導体装置に分割する工程と、

を有することを特徴とする受光用半導体装置の製造方法。

**【請求項 7】**

前記請求項 6 に記載の受光用半導体装置の製造方法で製造され、回路基板に実装された受光用半導体素子と、該受光用半導体素子の受光部上の樹脂パッケージの空洞部とを備えることを特徴とする受光用半導体装置。

**【請求項 8】**

半導体ウェハーに形成された複数の受光用半導体素子の各受光部に保護膜を形成する工程と、

前記半導体ウェハーを受光用半導体素子毎に分割する工程と、

前記分割された受光用半導体素子を大判の回路基板へ実装する工程と、

前記各受光用半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、

前記保護膜、前記ワイヤ及び前記複数の受光用半導体素子全体を覆うように樹脂で封止する工程と、

前記保護膜の表面が露出するまで前記樹脂を研摩する工程と、

10

20

30

40

50

前記保護膜を除去する工程と、

前記受光用半導体素子、前記研磨された樹脂上に光学的に透明なカバー部材を貼り付ける工程と、

前記大判の回路基板を切断して個別の受光用半導体装置に分割する工程と、

を有することを特徴とする受光用半導体装置の製造方法。

【請求項 9】

前記光学的に透明なカバー部材は、ガラスでなることを特徴とする請求項 8 の受光用半導体装置の製造方法。

【請求項 10】

請求項 8 又は請求項 9 に記載の受光用半導体装置の製造方法で製造され、回路基板に実装された受光用半導体素子と、該受光用半導体素子の受光部上の樹脂パッケージの空洞部と、該空洞部を塞ぐカバーガラスとを備えることを特徴とする受光用半導体装置。 10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置の製造方法、特に、デジタルビデオカメラ、携帯電話等に実装して好適な光学モジュールに用いる撮像用半導体素子を備えた撮像用半導体装置や光ディスク装置に用いる光電変換素子を備えた光検出半導体装置の製造方法に関する。

【背景技術】

【0002】

近年、デジタルビデオカメラや携帯電話等に装填する光学モジュールは、高画素化、小型化が進んでおり、中でも携帯電話にカメラ機能が搭載され、その結果、レンズ、パッケージを含めた光学モジュールとしての小型化、薄型化の要求が高まっている。これに伴ってレンズを含めた小型化、薄型化を図った撮像装置が提案がなされている（特許文献 1、特許文献 2 参照）。

【0003】

【特許文献 1】特開 2000-269472 号公報

【特許文献 2】特開 2003-219284 号公報

【0004】

また、最近では光学モジュールが携帯電話、デジタルカメラ、PC カメラ等の民生機器や自動車の前後左右確認のために車体にカメラを搭載した自動車が登場してきている。 30

したがって、小型、薄型の要求に加え、耐環境性等の信頼性への要求も高まり、このような要求に応えるため、撮像用半導体素子を実装した次のような構造の光学モジュールが実施されている。

【0005】

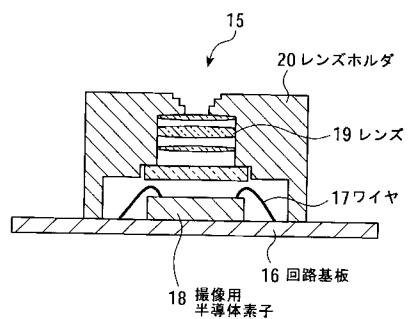

図 11 に示すように、光学モジュール 15 は、回路基板 16 上にワイヤ 17 で接続された撮像用半導体素子 18 を実装し、さらに回路基板 16 上にレンズ 19 が取り付けられたレンズホルダ 20 を取り付け、前記撮像用半導体素子 18 を封止している。

【0006】

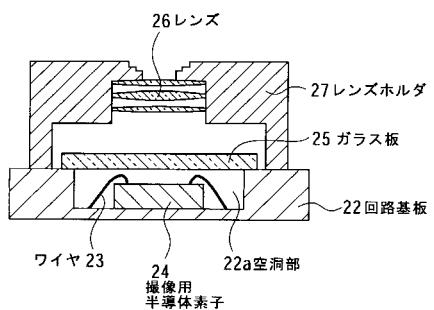

また、図 12 に示すように、セラミックスや樹脂を成型して作られた空洞部 22a を備えた回路基板 22 にワイヤ 23 でワイヤボンディングされた撮像用半導体素子 24 を実装し、前記空洞部 22a をガラス板 25 で封止し、さらにレンズ 26 が取り付けられたレンズホルダ 27 を前記空洞部 22a を囲むように取り付けた光学モジュールも実施されている。 40

【0007】

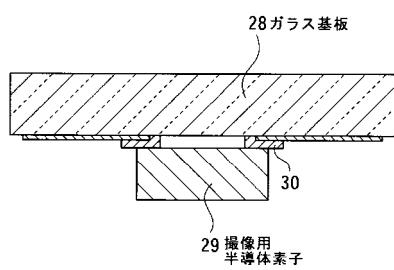

また、図 8 に示すように、ガラス基板 28 上の受光部とは反対側のパターニングされた面に撮像用半導体素子 29 をフリップチップボンディング 30 し、前記撮像用半導体素子 29 を樹脂封止（図示せず）した光学モジュールも実施されている。

【0008】

また、光ディスク装置に代表されるように、光ピックアップパッケージについても高密 50

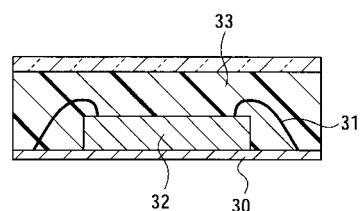

度記録媒体の読み取りができるパッケージの要求が高まっている。したがって、記録読み取りに使用する光の波長は短くなっている、図9に示すように、回路基板30に金ワイヤ31で接続された受光用半導体素子32を実装し、受光面側から透明な樹脂33で封止した樹脂封止型のパッケージが提案されているが、このパッケージでは樹脂が透明といえども光エネルギーによる樹脂の劣化によって透明度が低下し、光量の減衰が大きくなる。

また、樹脂封止の際入射側表面の樹脂の厚みを薄くする方法（特許文献3、特許文献4参照）、図10に示すように、回路基板34に実装した受光用半導体素子35の受光面側に空洞部36を形成して樹脂37で封止し、空洞部36をカバーガラス38で封止して光量の減衰を少なくした光ピックアップパッケージが提案されている。

#### 【0009】

10

【特許文献3】特開2003-17715号公報

【特許文献4】特開2003-273371号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

前記回路基板に利用する絶縁基板としてガラスエポキシ基板やセラミック基板が汎用されてきたが、これらの絶縁基板は発塵しやすく、ダイシング等の加工途中での塵埃の発生、光学モジュール完成後の振動による塵埃の発生等による異物の付着があり、歩留の向上に限界があった。また、レンズホルダーを組み付ける場合、半導体素子の受光部、受光部から光学レンズまでの距離がピントとなり、半導体素子の厚さのばらつき、実装時の接着剤の厚さのばらつき、レンズホルダの高さのばらつき等がピント合わせの精度を左右する。

また、半導体素子の厚みにも限界があり、半導体素子の厚みと絶縁基板の厚みが光学モジュールの総厚となるため、現状では光学モジュールに用いる半導体素子の薄型化にも限界がある。

#### 【0011】

20

ところで、前記ダイシングにより発生する塵埃の影響を避けるために、ダイシング中に固体撮像素子の表面に塵埃が付着しないようにした半導体装置の製造方法が提案されている。

該半導体装置の製造方法は、ダイシング時の固体撮像素子表面の傷付きや塵埃の付着を少なくするために、半導体ウェハに複数のCCDを形成した後、ダイシングにより半導体ウェハを個々のCCDに分割するに際し、半導体ウェハ表面にアクリル系樹脂材料である加工保護被膜を $1\text{ }\mu\text{m} \sim 3\text{ }\mu\text{m}$ の膜厚となるよう被着した後に回転ブレードでダイシングを行ない、ダイシング後に加工保護被膜をアルカリ水溶液又は有機溶剤で剥離、除去し、半導体ウェハを個々のCCDに分割するものである（特許文献5参照）。

#### 【0012】

30

【特許文献5】特開2003-273043号公報

#### 【0013】

また、他の例として、基材の一方の面上に、受光面を露出面側として複数個の固体撮像素子を所定間隔をあけて整列して接合する工程と、各々の固体撮像素子の露出面の受光領域を個片に形成された柔軟性を有する保護膜により被覆する工程と、保護膜を被着した固体撮像素子を基材とともに平坦な挾圧面を有する金型により挾圧し、金型の挾圧面と保護膜および隣接する固体撮像素子によって囲まれた空隙部分に封止材を充填して樹脂成形した後、固体撮像素子の受光面から保護膜を除去する工程と、成形された封止材を介して各固体撮像素子の露出する受光面を覆うように基材の全面にわたって透光板を接着する工程と、隣接する固体撮像素子間に沿って個片の半導体装置に切断する工程とを含み、固体撮像素子の受光面に異物が付着するのを防止するようにした半導体装置の製造方法が提案されている（特許文献6参照）。

#### 【0014】

40

【特許文献6】特開2003-332542号公報

#### 【0015】

50

前記特許文献 5 に記載の半導体装置の製造方法は、ダイシング時に発生する塵埃が半導体素子表面に付着するのを防止することができる。一方、製造された半導体素子が樹脂モールド等他の製造工程を経る際、半導体素子表面への塵埃の付着、汚染の除去までは解決されていない。

#### 【 0 0 1 6 】

また、特許文献 6 に記載の半導体装置の製造方法では、金型で固体撮像素子と保護膜を挟み型締めして、その空隙部分に樹脂を充填しているが、このように金型で挟み込むと保護膜が設けられても撮像素子表面に多大な荷重がかかる。このとき型締め圧を弱めると保護膜と金型の隙間に樹脂が回り込み、保護膜剥離後に樹脂バリが発生し、後工程において異物の原因となる。

10

#### 【 0 0 1 7 】

本発明は、前記各種問題点を総合的に解決できる半導体装置の製造方法を提案するものである。

#### 【課題を解決するための手段】

#### 【 0 0 1 8 】

第 1 に半導体素子の受光面への塵埃の付着を防止するという課題があるが、該防止策として(1)発塵の少ない材料の選択、(2)発塵させない加工方法、(3)工程内の異物付着の防止が考えられるが、(1)及び(2)の方法は有効な防止策であるが、現状では材料が制約され、また発塵させない物理的加工の知見に困難を伴う。

そこで、本願の発明では前記(3)の方法を採用し、撮像用半導体素子又は光電変換半導体素子などの受光用半導体素子(以下、半導体素子といふ。)が形成された半導体ウェハの状態からダイシング工程を経て空洞部を有する密閉状態に組み立てる直前まで半導体素子の表面を塵埃等の異物から保護し、製造中に異物が発生しても半導体素子の表面に異物が付着しない製造方法を提案するものである。

20

#### 【 0 0 1 9 】

第 2 の課題として、前記半導体素子を有する半導体装置の信頼性の問題があるが、多くの場合、光学モジュールは空洞部を有するため、電気的な引き出し線である金ワイヤ等の配線、半導体素子の表面等、多くの領域が外部にむき出しの状態となる。

金ワイヤ等の接続のため半導体素子の表面にアルミニウムなどの電極を設けているのが一般的であるが、樹脂パッケージ内への水分の侵入等によりむき出しの電極が腐食する可能性が高い。また広いむき出しのため異物を排除しなければならない領域が広くなる。

30

#### 【 0 0 2 0 】

そこで、本発明では、信頼性を確保するために、光学的に使用する領域を除き半導体素子の表面を樹脂で覆い、該半導体素子から電気的に引き出される金ワイヤ等の配線を外力や水分から遮断し、樹脂パッケージとしての信頼性を向上させるものである。後述する樹脂封止の工程で詳述する。

#### 【 0 0 2 1 】

また、前記空洞部を有する光学モジュールの場合、カバーガラスを取り付けるためには接続用のワイヤーループの高さに加えて間隙が必要となる。このとき間隙量はワイヤがむき出して保護されていないため外力に弱く、十分な距離をとる必要がある。

40

そこで、本発明では、組み立て時に樹脂パッケージを研磨して均一な厚みを確保するとともに、必要最低限の薄型パッケージにし、前記樹脂パッケージに比べて薄型化を図るもので、後述する。

#### 【 0 0 2 2 】

さらに、空洞部を有する構造の場合、ワイヤー引き出しに加えてカバーガラスの貼り付けしろのスペースが必要となりその分寸法が大きくならざるをえない。

これに対して、本発明では、ワイヤー引き出し部は樹脂で覆われているため、ワイヤー引き出し部と光学的に透明な部材、例えばガラス板の貼り付け部を立体的に共有し、それだけ樹脂パッケージを小型にすることができます。

#### 【 0 0 2 3 】

50

以上の課題を総合的に解決するために、本発明の半導体装置の製造方法は、半導体ウェハーに形成された複数の半導体素子の各受光部に保護膜を形成する工程と、前記半導体ウェハーを半導体素子毎に分割する工程と、前記分割された半導体素子を大判の回路基板へ実装する工程と、

前記各半導体素子と前記大判の回路基板の配線とをワイヤにてボンディングする工程と、前記保護膜、前記ワイヤ及び前記複数の半導体素子全体を覆うように樹脂で封止する工程と、前記保護膜の表面が露出するまで前記樹脂を研磨する工程と、

前記保護膜を除去する工程と、前記半導体素子、前記研磨された樹脂上にカバーを貼り付ける工程と、前記大判の回路基板を切断して個別の半導体装置に分割する工程と、

を有する。

10

#### 【発明の効果】

#### 【0024】

半導体装置が受光した画質を劣化させる塵埃、水分等の異物の侵入を妨げて受光部に異物が付着するのを防止することができる。また、樹脂パッケージを研磨にて均一に薄くすので、半導体装置の薄型化及び該半導体装置を用いた光学モジュールの小型化、薄型化が可能となる。

#### 【発明を実施するための最良の形態】

#### 【0025】

以下、本発明の撮像用半導体装置又は受光用半導体装置の製造方法の第1の実施の形態及び該製造方法で製造した半導体装置を説明する。

20

以下、撮像用半導体素子を備えた撮像用半導体装置を例に挙げながら説明するが、本発明の半導体装置の製造方法は、光ディスク装置に用いる受光用半導体装置の製造にも適用可能である。

#### 【0026】

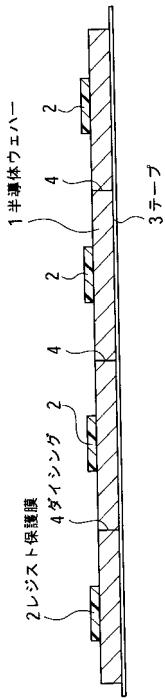

##### 〔工程1〕撮像用半導体素子の受光部への保護膜の形成

図1に示すように、撮像用半導体素子の受光部への保護膜の形成は、複数の撮像用半導体素子が形成された半導体ウェハー1の全面に均一にレジスト塗布機にて厚さ0.1mm以上のフォトレジストを塗布し、露光、現像及びエッチングにて撮像用半導体素子の受光部の領域のみフォトレジストにてレジスト保護膜2を形成する。

前記レジスト保護膜2の厚みは後述するワイヤボンディング時のワイヤループが十分隠れる程度の一定高さが必要である。ちなみに0.1mm以上あれば十分であり、後の工程で研磨にて樹脂パッケージの厚みを整えるため、厳密な膜厚管理は必要としない。

30

#### 【0027】

##### 〔工程2〕半導体ウェハーのダイシング

図1に示すように、前記半導体ウェハー1の裏面にテープ3を貼り付け、前記半導体ウェハー1を撮像用半導体素子毎に前記テープ3に達するまで回転ブレード等でダイシング4を行い、分割する。

この時、ダイシングすることで前記半導体ウェハー1のかす等の切削くずが発生するが、ダイシング前に前記レジスト保護膜2が施されているため、このような異物が前記レジスト保護膜2下の受光部まで回り込まず、異物付着の要因を排除することができる。

40

#### 【0028】

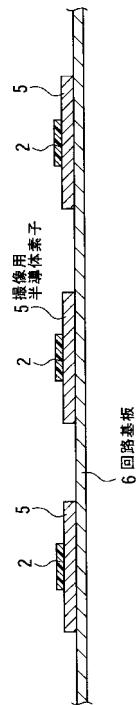

##### 〔工程3〕分割された撮像用半導体素子の大判の回路基板への実装

図2に示すように、個々に分割された撮像用半導体素子5を撮像用半導体素子5毎に配線された領域を有する大判の回路基板6上にそれぞれ実装する。

この実装は、前記ダイシング4で前記テープ3(図1)上に分割された各撮像用半導体素子5を1個ずつ吸着手段で吸着して前記大判の回路基板6上の実装場所に移動させて行う。

この時、撮像用半導体素子5の受光部の表面には前記レジスト保護膜2が施されているので、撮像用半導体素子5の表面を吸着しても傷や異物を付けることがなく、安定して吸着でき、前記テープ3(図1)から容易に剥離できる。

50

ここで、実装する大判の回路基板として用途にもよるが、リードフレーム、電鋳シート回路基板、ガラスエポキシ回路基板、フレキシブル回路基板等が使用でき、樹脂パッケージに適した基板であればマトリクス状に多数個の製品が取れるようにリードを配置したものを利用できる。

#### 【0029】

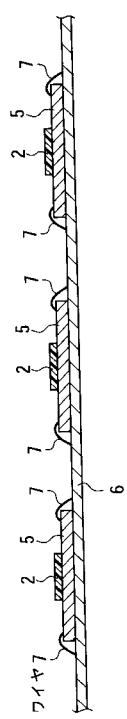

##### [工程4]撮像用半導体素子と回路基板の配線とのワイヤボンディング

ワイヤボンディングの前処理としてプラズマエッチングを必要に応じて行う。このプラズマエッチングは、撮像用半導体素子5のボンディングパッドやバンプ等の電極の表面の金属酸化物を除去するために行うものである。

図3に示すように、撮像用半導体素子5の電極(図示せず)と回路基板6の配線(図示せず)とのワイヤ7によるワイヤボンディングは低ループでボンディングするのが好適である。これは後述する樹脂パッケージの薄型化を図るために、後工程で樹脂パッケージを研磨するが、前記ワイヤ7のループが低いほど樹脂パッケージを薄く研磨できるからである。したがって、低ループにすれば前記研磨によって薄い樹脂パッケージを容易に得ることができる。

#### 【0030】

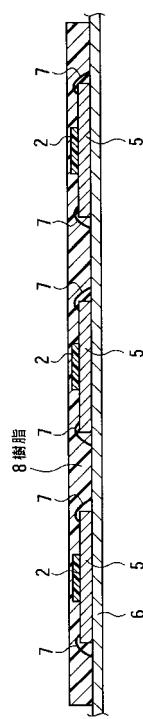

##### [工程5]樹脂パッケージの形成

図4に示すように、樹脂8にて前記レジスト保護膜2及びワイヤ7及び複数の撮像用半導体素子5全体を覆うように封止する。

この樹脂8による封止は、金型による型締めは大判の回路基板6を挟むことで封止が可能であるため、撮像用半導体素子5への荷重も分散し、また隣接する撮像用半導体素子間においてバリが発生することがない。

金型を用いる場合、例えばフィルムアシスト方式を用いても良い。例えば撮像用半導体素子の厚みが0.4mmの場合、半導体素子の厚み+0.2mm、つまり厚み0.6mmの金型を使用する。また、印刷方式やディスペンス方式で封止することもできる。

#### 【0031】

ここで後工程で光学的に透明な部材、例えばカバー用ガラスを貼り合わせるため、図5に示すように、該工程で隣接する半導体素子間の樹脂の上面にダイサーを利用して浅溝9をそれぞれ形成する。この浅溝9の形成は後の工程6の樹脂の研磨後にも良い。また、前記浅溝は省略しても良い。この浅溝9を設けることで後述するガラスカバー接着を行う接着剤を流し込むための溝となり、さらにダイシング用の位置決め用のマークとしても利用する。

#### 【0032】

##### [工程6]樹脂パッケージの研磨

図5に示すように、前記工程5で成形された樹脂8の表面全体を研磨機で研磨し、前記レジスト保護膜2の表面が完全に露出する所定の高さまで一様に研磨する。後に研磨を行った樹脂8にカバーガラスを貼り合わせるため、隣接する半導体素子間の樹脂部に前記浅溝9を必要に応じて形成する。

この樹脂研磨工程において、撮像用半導体素子5及びワイヤ7を完全に封止するような厚みまで樹脂8を研磨して薄くすることで、撮像用半導体装置の樹脂パッケージの薄型化を容易に実現することができる。

#### 【0033】

##### [工程7]レジスト保護膜の除去

各撮像用半導体素子5の受光面に設けられた前記レジスト保護膜2をエッチングにより除去し(図6)、除去後、純水で洗浄する。この工程ではレジスト保護膜2の除去後に純水で洗浄するため、レジスト保護膜2がなくても異物が付着することはない。また、仮に何らかの要因で異物が付着していても洗浄により除去することができる。

このレジスト保護膜2を設けることによって半導体ウエハーのダイシング工程から樹脂パッケージの研磨までの工程において、前記撮像用半導体素子5の受光面に異物や傷が付くのを防止することができる。このレジスト保護膜2の除去でできた空洞部10の高さは

10

20

30

40

50

、樹脂研磨後の厚みのみで決まるため、極めて低く形成でき、光学モジュールなどのレンズと撮像用半導体素子の距離を近接する構造にすることが可能となる。

#### 【0034】

##### [工程8] カバーガラスの貼り付け

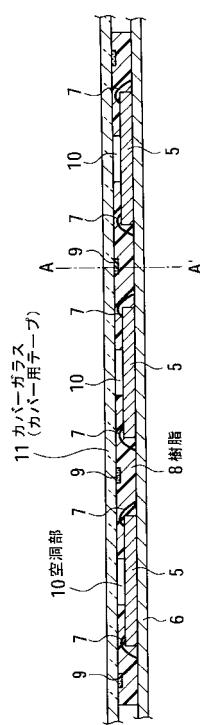

図6に示すように、前記工程7でレジスト保護膜2を除去した後、前記接着剤流し込み浅溝9内にUV接着剤等を流し込みし、光学的に透明で平坦な大判のカバーガラス11を一括で全体に貼り付けて、前記空洞部10内にある撮像用半導体素子5の受光部が密閉された撮像用半導体装置を形成する。これにより前記空洞部10に新たな異物の侵入を防止することができる。カバーガラスの貼り付けは、撮像用半導体素子5毎に個別に貼り付けても良い。

10

#### 【0035】

##### [工程9] 大判の回路基板のダイシング

前記カバーガラス11を一括貼り付けた後、大判の回路基板6とカバーガラス11を前記溝9の中央部を基準位置A-A'に採って前記回路基板6に向けてフルカットでダイシングし、個別の撮像用半導体装置に分割する。カバーガラスを撮像用半導体素子毎に個別に貼り付けた場合は、大判の回路基板6のみをダイシングして個別の撮像用半導体装置になるように分割する。このダイシング時、空洞部10はカバーガラス11で覆われているため、撮像用半導体素子5の受光面に異物が付着する事がない。

#### 【0036】

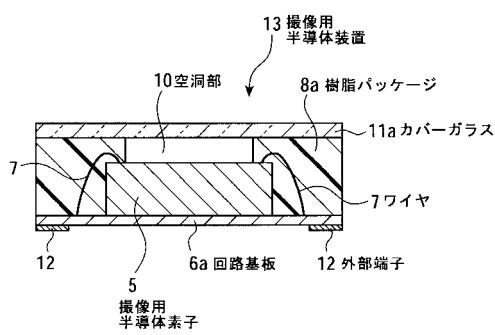

以上の工程を経て製造された撮像用半導体装置13を図7に示している。

20

完成した撮像用半導体装置13のワイヤボンディング部を含むワイヤ7全体が前記研摩された樹脂パッケージ8aで封止されているので、薄型化が可能な撮像用半導体装置が得られる。

また、回路基板6aの裏側に該回路基板6aのボンディングランドに繋がる外部端子12のパターンを予め形成しておくことで撮像用半導体装置13をフラットケーブルやプリント配線板に搭載して外部回路との接続を行うことができる。

#### 【0037】

図7に示すように、本発明の製造方法で製造された撮像用半導体装置13は、回路基板6a上に実装された撮像用半導体素子5、樹脂パッケージ8a、空洞部10及びカバーガラス11aを備えている。前記工程を経て製造されたので撮像用半導体素子5の受光部(カバーガラス側)表面には異物が付着する事がない。

30

#### 【0038】

また、前記空洞部10は前記レジスト保護膜2を除去した部分のみ残り、したがって前記空洞部10の高さは前記レジスト保護膜2の厚みのみで決まるため、前記空洞部10の高さを低くすることができ、撮像用半導体装置13を全体として従来の撮像用半導体装置よりも薄型に形成することができる。したがって、この撮像用半導体装置を光学モジュールに利用すると、従来の光学モジュールよりも小型化、薄型化が可能となる。

前記実施の形態では、前記空洞部を光学的に透明なカバーガラスで覆うようにしたが、光学モジュールを構成するレンズホルダー内に半導体装置を組み込むと、該カバーガラスは必ずしも必要としないので、以下、第2の実施の形態について説明する。

40

#### 【0039】

以下、本発明の第2の実施の形態について、前記第1の実施の形態の図を援用しながら説明する。

#### 【0040】

##### [工程1] 撮像用半導体素子の受光部への保護膜の形成

図1に示すように、撮像用半導体素子の表面への保護膜の形成は、複数の撮像用半導体素子が形成された半導体ウエハー1の全面に均一にレジスト塗布機にて厚さ0.1mm以上のフォトレジストを塗布し、露光、現像及びエッチングにて撮像用半導体素子の受光部の領域のみレジストにてレジスト保護膜2を形成する。

前記レジスト保護膜2の厚みは後述するワイヤボンディング時のワイヤループが十分隠

50

れる程度の一定高さが必要である。ちなみに 0.1 mm 以上あれば十分であり、後の工程で研磨にて樹脂パッケージの厚みを整えるため、厳密な膜厚管理は必要としない。

#### 【0041】

##### [工程2] 半導体ウエハーのダイシング

図1に示すように、前記半導体ウエハー1の裏面にテープ3を貼り付け、前記半導体ウエハー1を撮像用半導体素子毎に前記テープ3に達するまで回転ブレード等でダイシング4を行い、分割する。

#### 【0042】

##### [工程3] 分割された撮像用半導体素子の大判の回路基板への実装

図2に示すように、個々に分割された撮像用半導体素子5を撮像用半導体素子5毎に配線された領域を有する大判の回路基板6上にそれぞれ実装する。10

この実装は、前記ダイシング4で前記テープ3(図1)上に分割された各撮像用半導体素子5を1個ずつ吸着手段で吸着して前記大判の回路基板6上の実装場所に移動させて行う。

#### 【0043】

##### [工程4] 撮像用半導体素子と回路基板の配線とのワイヤボンディング

ワイヤボンディングの前処理としてプラズマエッチングを必要に応じて行う。このプラズマエッチングは、撮像用半導体素子5のボンディングパッドやバンプ等の電極の表面の金属酸化物を除去するために行うものである。

図3に示すように、撮像用半導体素子5の電極と回路基板6の配線とのワイヤ7によるワイヤボンディングは低ループで行う。20

#### 【0044】

##### [工程5] 樹脂パッケージの形成

図4に示すように、樹脂8にて前記レジスト保護膜2及びワイヤ7及び複数の撮像用半導体素子5全体を覆うように封止する。

#### 【0045】

##### [工程6] 樹脂パッケージの研磨

図5に示すように、前記工程5で成形された樹脂8の表面全体を研磨機で研磨し、前記レジスト保護膜2の表面が完全に露出する所定の高さまで一様に研磨する。

#### 【0046】

##### [工程7] レジスト保護膜の除去

各撮像用半導体素子5の受光部に設けられた前記レジスト保護膜2をエッチングにより除去し(図6)、除去後、前記撮像用半導体素子の表面を純水で洗浄する。

以上の工程までは、前記第1の実施の形態と同様である。また、以下の工程は、前記カバーガラスの貼り付けに代えてカバー用テープを貼り付ける工程となる。

#### 【0047】

##### [工程8] カバー用テープの貼り付け

図6に示すように、前記工程7でレジスト保護膜2を除去した後、前記第1の実施の形態におけるカバーガラスに代えて大判のカバー用テープ11を全体に貼り付け、撮像用半導体素子5の受光部を密閉し前記空洞部10を有する半導体装置を形成する。これにより前記中空洞10に新たな異物の侵入を防止することができる。このカバー用テープの貼り付けの工程では記浅溝9を省略することができる。40

#### 【0048】

##### [工程9] 大判の回路基板のダイシング

前記カバー用テープ11を一括貼り付けた後、大判の回路基板6と樹脂8を基準位置A-A'に採ってフルカットでダイシングし、個別の撮像用半導体装置に分割する。このダイシング時、空洞部10はカバー用テープ11で覆われているため、撮像用半導体素子5の受光部に異物が付着することができない。

#### 【0049】

図7に示すように、本発明の第2の実施の形態の製造方法で製造された半導体装置13

50

は、回路基板 6 a 上に実装された撮像半導体素子 5 、樹脂パッケージ 8 a 、空洞部 10 を備えている。前記工程を経て製造されたので撮像用半導体素子 5 の受光部の表面に異物が付着することがない。

この第 2 の実施の形態で製造された撮像用半導体装置は、空洞部 10 がカバーガラスで覆われていないが、前記カバー用テープを剥離して前記撮像用半導体装置を直接レンズホルダー内に組み込むことで撮像用半導体素子の受光部に異物が付着するのを防止できる。

#### 【 0 0 5 0 】

また、前記空洞部 10 は前記レジスト保護膜 2 を形成し除去した部分のみ残り、したがって前記空洞部 10 の高さは前記レジスト保護膜 2 の厚みでのみ決まるため、前記空洞部 10 の高さを低くすることができ、撮像用半導体装置 13 を全体として従来の撮像用半導体装置よりも薄型に形成することができる。したがって、この撮像用半導体装置を光学モジュールに利用すると、従来の光学モジュールよりも小型化、薄型化が可能となる。

10

前記各実施の形態では、半導体素子として撮像用半導体素子を例に挙げて説明したが、撮像用半導体素子に代えて、光ディスク装置の光ピックアップ等に利用する受光用半導体装置の製造にも適用することができる。

#### 【 図面の簡単な説明 】

#### 【 0 0 5 1 】

【 図 1 】本発明の半導体装置の製造方法の工程の説明図である。

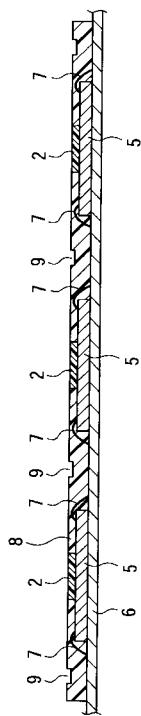

【 図 2 】本発明の半導体装置の製造方法の工程の説明図である。

【 図 3 】本発明の半導体装置の製造方法の工程の説明図である。

20

【 図 4 】本発明の半導体装置の製造方法の工程の説明図である。

【 図 5 】本発明の半導体装置の製造方法の工程の説明図である。

【 図 6 】本発明の半導体装置の製造方法の工程の説明図である。

【 図 7 】本発明の半導体装置の製造方法で製造された撮像用半導体装置の断面図である。

【 図 8 】従来の半導体装置の説明図である。

【 図 9 】従来の半導体装置の説明図である。

【 図 1 0 】従来の半導体装置の説明図である。

【 図 1 1 】従来の光学モジュールの説明図である。

【 図 1 2 】従来の光学モジュールの説明図である。

#### 【 符号の説明 】

30

#### 【 0 0 5 2 】

1 … 半導体ウェハー 2 … レジスト保護膜 5 … 半導体素子

6 … 大判の回路基板 8 … 研磨された樹脂 8 a … 樹脂パッケージ

10 … 空洞部 11 、 11 a … カバーガラス、カバー用テープ 13 … 半導体装置

【図1】

【図2】

【図3】

【図4】

【 四 5 】

【 义 6 】

【図7】

【図9】

〔 8 〕

【 10 】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 特開平7-221278(JP,A)

特開2003-332542(JP,A)

特開2003-219284(JP,A)

特開2006-186288(JP,A)

特開昭61-32535(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/14

H04N 5/335