## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-103634 (P2007-103634A)

(43) 公開日 平成19年4月19日 (2007.4.19)

| (51) Int.C1. |        |           | FI      |        |      | テーマコード (参考) |

|--------------|--------|-----------|---------|--------|------|-------------|

| HO1L         | 21/304 | (2006.01) | HO1L    | 21/304 | 622S | 3CO58       |

| G06F         | 17/50  | (2006.01) | GO6F    | 17/50  | 666S | 5BO46       |

| B24B         | 37/04  | (2006.01) | B 2 4 B | 37/04  | Z    |             |

| HO1L         | 21/00  | (2006.01) | HO1L    | 21/00  |      |             |

|                       |                                                        | 審査請求     | 未請求 請求項の数 9 OL (全 14 頁)                         |  |  |

|-----------------------|--------------------------------------------------------|----------|-------------------------------------------------|--|--|

| (21) 出願番号<br>(22) 出願日 | 特願2005-291004 (P2005-291004)<br>平成17年10月4日 (2005.10.4) | (71) 出願人 | 503121103<br>株式会社ルネサステクノロジ<br>東京都千代田区丸の内二丁目4番1号 |  |  |

|                       |                                                        | (74) 代理人 | 100080001<br>弁理士 筒井 大和                          |  |  |

|                       |                                                        | (72) 発明者 | 大嶽 敦<br>茨城県日立市大みか町七丁目1番1号 株<br>式会社日立製作所日立研究所内   |  |  |

|                       |                                                        | (72) 発明者 | 荒井 利行<br>東京都千代田区丸の内二丁目4番1号 株                    |  |  |

|                       |                                                        | (72) 発明者 | 式会社ルネサステクノロジ内<br>川崎 貴彦<br>東京都千代田区丸の内二丁目4番1号 株   |  |  |

|                       |                                                        |          | 式会社ルネサステクノロジ内<br>最終頁に続く                         |  |  |

(54) 【発明の名称】半導体デバイスの形状シミュレーション方法

## (57)【要約】

【課題】パターン上への膜堆積・エッチングなどのプロセスによる形状変化や、デバイス上に混在する異なる段差のパターンを考慮した具体的な C M P シミュレーション方法を提供する。

【解決手段】半導体デバイスの表面をCMPにより研磨した後の表面形状を予測するシミュレーション方法において、デバイスの設計CADパターンからパターン密度を計算する際に、パターンCADデータを予め加工するかもしくは計算したパターン密度データを加工することにより、表面形状をより正確に考慮したCMPシミュレーションを実施する。これにより、パターン形成後のプロセス(膜堆積、エッチングなど)によって変化したデバイス表面上の凹凸形状を考慮でき、また、複数の高さの異なる段差を含むデバイスについてCMPシミュレーションが可能となる。

【選択図】図10

20

30

40

50

#### 【特許請求の範囲】

### 【請求項1】

半導体デバイスの表面をCMPにより研磨した後の表面形状を予測する、コンピュータを用いた半導体デバイスの形状シミュレーション方法であって、

設計 C A D データから C M P 研磨前に堆積する膜の影響を考慮するため、設計 C A D データ中のパターンが占める割合を変化させて、 C M P 研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項2】

請求項1記載の半導体デバイスの形状シミュレーション方法において、

前記 C M P 研磨後の膜厚シミュレーションを実施する際には、設計 C A D データ中のパターン幅を増大もしくは減少させ、単位面積あたりのパターン幅を増大もしくは減少させたパターンの占める割合を求め、この割合を用いて C M P 研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項3】

請求項1または2記載の半導体デバイスの形状シミュレーション方法において、

前記設計CADデータ中には、高さの異なる二種類以上のパターンが含まれており、この二種類以上の異なる高さを考慮してCMP研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項4】

請求項3記載の半導体デバイスの形状シミュレーション方法において、

前記高さの異なる二種類以上のパターンには、 t 1 なる高さと t 2 ( t 1 > t 2 ) なる高さの二種類の異なるパターンが存在し、この二種類のパターンが同じ領域を占めることがない場合、 t 1 の高さを持つパターンもしくは t 1 のパターン上の堆積膜の占める面積の割合を 1 とし、 t 2 の高さを持つパターンもしくは t 2 のパターン上の堆積膜の占める面積の割合を 2 とした場合、新たにパターンが単位面積あたりに占める面積の割合を 1 + ( t 1 / t 2 ) 2 として求めることを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項5】

請求項3記載の半導体デバイスの形状シミュレーション方法において、

前記高さの異なる二種類以上のパターンには、 t 1 なる高さと t 2 ( t 1 > t 2 ) なる高さの二種類の異なるパターンが存在し、この t 1 なる高さを持つパターンと t 2 なる高さを持つパターンが重なる場合、重なった部分の高さを t 3 とし、重なった部分のパターンもしくは重なった部分のパターン上の堆積膜の占める面積の割合を 3 とした場合、新たにパターンが単位面積あたりに占める面積の割合を 3 + 1 ( t 2 / t 3 ) + 2 ( t 1 / t 3 ) として求めることを特徴とする半導体デバイスの形状シミュレーション方法

## 【請求項6】

請求項1~5のいずれか1項に記載の半導体デバイスの形状シミュレーション方法において、

前記CMP研磨後の膜厚シミュレーションを実施する際には、CMP前に堆積する酸化膜がオゾン・TEOS法もしくはこれに類するコンフォーマルな堆積形状を特徴とする方法により堆積された際、堆積したオゾン・TEOS膜もしくはこれに類する膜の堆積厚さをDとしたとき、( /4)Dだけ設計CADデータ中のパターン幅を増大させ、このパターン幅を増大させたCADデータから単位面積あたりのパターン幅を増大させたパターンの占める割合を求め、この割合を用いてCMP研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項7】

請求項 1 ~ 5 のいずれか 1 項に記載の半導体デバイスの形状シミュレーション方法において、

前記CMP研磨後の膜厚シミュレーションを実施する際には、CMP前に堆積する酸化

膜がHDP法により堆積された際、堆積したHDP膜の堆積厚さをDとしたとき、D/4~Dの値だけ設計CADデータ中のパターン幅を縮小させ、このパターン幅を縮小させたCADデータから単位面積あたりのパターン幅を縮小させたパターンの占める割合を求め、この割合を用いてCMP研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項8】

請求項1~7のいずれか1項に記載の半導体デバイスの形状シミュレーション方法において、

前記 C M P 研磨後の膜厚シミュレーションを実施する際には、設計 C A D データを用いて C M P 前に堆積する酸化膜もしくはその他の膜の体積を求め、さらに堆積後のエッチング処理によって変化した体積を求め、この体積を考慮して C M P 研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

#### 【請求項9】

請求項8記載の半導体デバイスの形状シミュレーション方法において、

堆積した酸化膜の厚さがTdであり、エッチング処理により減少した部分の厚さがTd‐Eであるとき、エッチング処理が施された部分が占める単位面積あたりの割合を E、エッチング処理が施されていない部分でかつパターン上に凸状に形成された堆積膜が占める単位面積あたりの割合を Nとするとき、新たに単位面積あたりのパターンの占める割合を N+ E(Td‐E)/Tdとして求め、このパターンの占める割合を用いてCMP研磨後の膜厚シミュレーションを実施することを特徴とする半導体デバイスの形状シミュレーション方法。

【発明の詳細な説明】

### 【技術分野】

### [ 0 0 0 1 ]

本発明は、半導体デバイスの製造技術に関し、特に、半導体デバイスの表面をCMP(Chemical Mechanical Polishing)により研磨した後の表面形状を予測するシミュレーション方法に適用して有効な技術に関する。

#### 【背景技術】

## [0002]

従来、半導体デバイスの表面をCMPにより研磨した後の表面形状を予測するシミュレーション方法に関する技術としては、単位面積あたりのパターンが占める割合を増大もしくは減少させて、堆積する膜の種類を考慮する技術がある(例えば、非特許文献1)。

【非特許文献1】Taber H.Smith,Simon J.Fang,Duane S.Boning,Greg B.Shinn,and Jerry A.Stefani,"A CMP Model Combining Density and Time Dependencies,"1999 Chemical Mechanical Polish for ULSI Multilevel Interconnection Conference(CMP-MIC),Santa Clara,Feb.1999

#### 【発明の開示】

【発明が解決しようとする課題】

#### [00003]

ところで、前記のような従来のシミュレーション方法に関する技術では、具体的な変更の手順については言及されておらず、また、同じデバイス上に存在する二種以上の高さを持つパターンの取り扱いを簡易に実施する手段についても言及されていない。

## [0004]

そこで、本発明の目的は、パターン上への膜堆積・エッチングなどのプロセスによる形状変化や、デバイス上に混在する異なる段差のパターンを考慮した具体的なCMPシミュレーション方法を提供することにある。

### [0005]

50

40

10

20

20

30

40

50

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

[0006]

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のと おりである。

[0007]

本発明は、酸化膜の堆積処理あるいはそれに引き続くエッチング処理などによりパターンが変化する影響、もしくはパターンの高さが二種類以上ある場合などにパターンの単位面積あたりの密度を算出し、CMPシミュレーションを実施することの課題を解決するものである。

[0008]

すなわち、本発明では、半導体デバイスの表面をCMP(Chemical Mechanical Polishing)により研磨した後の表面形状を予測するシミュレーション方法において、設計CADデータからCMP研磨前に堆積する膜の影響を考慮するため、設計CADデータ中のパターンが単位面積あたりに占める割合を変化させて、CMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計CADデータが得られた段階で堆積膜の形状を考慮したCMPシミュレーションが可能となる。

[0009]

好ましくは、上記において、設計 CAD データ中のパターン幅を増大もしくは減少させ、単位面積あたりのパターン幅を増大もしくは減少させたパターンの占める割合を求め、この割合を用いて CMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計 CAD データが得られた時点で膜の堆積の効果を考慮した CMPシミュレーションが可能となる。

[0010]

好ましくは、上記において、設計 CADデータ中に高さの異なる二種類以上のパターンが含まれており、この二種類以上の異なる高さを考慮して CMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計 CADデータが得られた段階で二種類以上の段差を持つ半導体デバイスの CMPシミュレーションが可能となる。

[0011]

また更に好ましくは、上記において、 t 1 なる高さと t 2 ( t 1 > t 2 ) なる高さの二種類の異なるパターンが存在し、二種類のパターンが同じ領域を占めることがない場合、 t 1 の高さを持つパターンもしくは t 1 のパターン上の堆積膜の占める面積の割合を 1 とし、 t 2 の高さを持つパターンもしくは t 2 のパターン上の堆積膜の占める面積の割合を 2 とした場合、新たにパターンが単位面積あたりに占める面積の割合を 1 + ( t 1 / t 2 ) 2 として求めることを特徴とする C M P 研磨後の膜厚シミュレーション方法が提供される。これにより、設計 C A D データが得られた段階で二種類以上の段差を持つ半導体デバイスの C M P シミュレーションが可能となる。

[ 0 0 1 2 ]

また更に好ましくは、上記において、 t 1 なる高さを持つパターンと t 2 なる高さを持つパターンが重なる場合、重なった部分の高さを t 3 とし、重なった部分のパターンもしくは重なった部分のパターン上の堆積膜の占める面積の割合を 3 とした場合、 3 + 1 ( t 2 / t 3 ) + 2 ( t 1 / t 3 ) として求めることを特徴とする C M P 研磨後の膜厚シミュレーション方法が提供される。これにより、設計 C A D データが得られた段階で二種類以上の段差を持つ半導体デバイスの C M P シミュレーションが可能となる。

[0013]

好ましくは、上記において、 C M P 前に堆積する酸化膜がオゾン - T E O S ( T e t r a e t h y l o r t h o s i l i c a t e ) 法もしくはこれに類するコンフォーマルな堆

20

30

40

50

積形状を特徴とする方法により堆積された際、堆積したオゾン・TEOS膜もしくはこれに類する膜の堆積厚さをDとしたとき、( /4)Dだけ設計CADデータ中のパターン幅を増大させ、このパターン幅を増大させたCADデータから単位面積あたりのパターン幅を増大させたパターンの占める割合を求め、この割合を用いてCMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計CADデータが得られた時点でオゾン・TEOS膜もしくはこれに類する膜の堆積の効果を考慮したCMPシミュレーションが可能となる。

#### [0014]

好ましくは、上記において、CMP前に堆積する酸化膜がHDP(High-Density-Plasma)法により堆積された際、堆積したHDP膜の堆積厚さをDとしたとき、D/4~Dだけ設計CADデータ中のパターン幅を縮小させ、このパターン幅を縮小させたCADデータから単位面積あたりのパターン幅を縮小させたパターンの占める割合を求め、この割合を用いてCMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計CADデータが得られた時点でHDP膜の堆積の効果を考慮したCMPシミュレーションが可能となる。

#### [0015]

好ましくは、上記において、設計CADデータを用いてCMP前に堆積する酸化膜もしくはその他の膜の体積を求め、さらに堆積後のエッチングその他の処理によって変化した体積を求め、この体積を考慮してCMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計CADデータが得られた時点で膜の堆積とエッチングの効果を考慮したCMPシミュレーションが可能となる。

#### [0016]

好ましくは、上記において、堆積した酸化膜の厚さがTdであり、エッチング処理により減少した部分の厚さがTd-Eであるとき、エッチング処理が施された部分が占める単位面積あたりの割合を E、エッチング処理が施されていない部分でかつパターン上に凸状に形成された堆積膜が占める単位面積あたりの割合を Nとするとき、新たに単位面積あたりのパターンの占める割合を N+ E(Td-E)/Tdとして求め、このパターンの占める割合を用いてCMP研磨後の膜厚シミュレーションを実施することを特徴とする方法が提供される。これにより、設計CADデータが得られた時点で膜の堆積とエッチングの効果を考慮したCMPシミュレーションが可能となる。

#### 【発明の効果】

### [0017]

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば以下のとおりである。

### [0018]

本発明によれば、パターン形成後のプロセス(膜堆積、エッチングなど)によって変化したデバイス表面上の凹凸形状を考慮でき、また、複数の高さの異なる段差を含むデバイスについて CMPシミュレーションが可能となる。

## 【発明を実施するための最良の形態】

#### [0019]

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の部材には原則として同一の符号を付し、その繰り返しの説明は省略する。

## [0020]

本発明の半導体デバイスの形状シミュレーション方法は、コンピュータを用いて、半導体デバイスの表面をCMPにより研磨した後の表面形状を予測する技術であり、各実施例を以下において順に説明する。

### [0021]

#### (実施例1)

本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1を、図1~図8

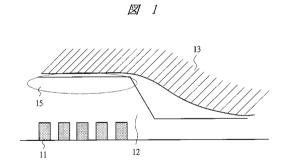

を用いて説明する。図1はCMPプロセスにおける研磨過程を説明するための、デバイスパターンの断面を示す説明図、図2および図3は局所的なパターン密度と平均化したパターン密度の概念を説明するための、デバイスパターンの上面を示す説明図、図4~図8はパターンの拡張処理を説明するための、デバイスパターンの上面を示す説明図である。

#### [0022]

まず、図1を用いて、CMPプロセスにおける研磨過程について説明する。CMPプロセスにおいては、研磨パッド13をデバイスの凸パターン15に押し当てて回転させ、デバイス表面上に存在する凸部分を研磨し、平坦化する。酸化膜CMPプロセスの場合、この凸パターン15は酸化膜でパターン11上に堆積された酸化膜12によって形成されている。従って、図1の通り、凸パターン15は必ずしもパターン11と一致しない。この際、研磨パッド13はデバイス表面上に存在する凸パターン15の影響を受けて変形を起こす。研磨パッド13は凸パターン15に接触するが、研磨パッド13の変形のために注目している凸パターン15上だけに応力が集中せずに、凸パターン15から遠方に向かってたわむ。

### [0023]

この影響を考慮したシミュレーションを実行するため、通常は応力応答関数と呼ばれる関数によって局所的なパターン密度を平均化し、この平均化したパターン密度 を求めることが行われる。ここで、局所的なパターン密度とは単位面積あたりに存在する凸パターン15の占める割合のことである。通常、上記単位面積は数  $\mu$  m × 数  $\mu$  m の領域が占める面積であり、本実施例では25 $\mu$  m × 25 $\mu$  m ( = 625 $\mu$  m <sup>2</sup>) である。局所的なパターン密度 を求めるには、チップ(通常1辺数 m m サイズの長方形もしくは正方形、数 m m :1~15 m m 程度)を上記で述べたような例えば25 $\mu$  m × 25 $\mu$  m の領域に分割し、各分割領域での凸パターンが占める割合を求める。

#### [0024]

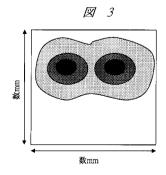

図 2 、図 3 を用いて、局所的なパターン密度 と平均化したパターン密度 の概念を説明する。図 2 において、黒い部分のパターン 2 1 は凸パターンの局所的なパターン密度が80%を占めていることを示す。図 2 を平均化処理すると、図 3 のようにパターン 2 1 の輪郭がぼやけて密度の高い部分(灰色の濃い部分)と低い部分(灰色の薄い部分)の分布が発生することが分かる。このようにして、平均化したパターン密度 のチップ内分布を求めることができる。

### [0025]

平均化したパターン密度 'を用いたCMPシミュレーション手法については現在までに多くの論文(例えば、前記非特許文献 1 など)が書かれているので、ここでは詳述しない。

### [0026]

以上までで述べたとおり、図1においてチップ上に存在するパターン11の密度をそのまま求めたのでは酸化膜12の堆積を考慮したシミュレーションを実施することができず、酸化膜12の堆積した後の凸パターン15の密度を求める必要がある。設計CADデータのレベルではパターン11の情報しか含まれていないので、設計CADデータから酸化膜堆積後の凸パターン密度を求める方法について以下に述べる。

## [ 0 0 2 7 ]

図1を見ると、パターン11の上に酸化膜12が覆いかぶさり、元々離れて存在していたパターン11の上に形成された凸パターン15は一つの大きな領域となっていることが分かる。ここで、図4のような単一のパターンを考えた場合に、パターンを だけ周囲に向かって拡張させる(図5)。これにより、図6のような元のパターン(図4)よりも大きなパターンが得られる。図7のように 以内のスペースで、隣接する複数のパターンが存在する場合、上記に述べたようなパターンの拡張を実施すると図8のような連続した大きな凸パターン領域が得られる。このようなパターンの拡張処理は、市販されている多くのLSI設計ツールの機能として備わっており、容易に実施することができる。

### [0028]

50

40

20

30

40

50

以上のようにして、本実施例によれば、元の設計 CADデータを加工することにより、酸化膜堆積などのパターン形成後のプロセスによって生じる凸パターン領域を考慮した CMPシミュレーションが可能となる。

#### [0029]

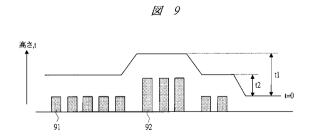

(実施例2)

本発明の半導体デバイスの形状シミュレーション方法にかかる実施例2を、図9を用いて説明する。図9は2種類以上の高さのパターンが同一のチップ上に存在する場合を説明するための、デバイスパターンの断面を示す説明図である。

[0030]

上記実施例1では、パターンの高さが1種類のみの例について説明したが、本実施例では2種類以上の高さのパターンが同一のチップ上に存在する場合について以下に説明する

[0031]

図9を用いて、二つの高さの異なるパターン91,92が形成された1つのチップの場合を説明する。それぞれのパターンの上には酸化膜が形成されており、酸化膜形成後のパターン高さはそれぞれ、高い方がt1、低い方がt2となっている。ここでは、パターンが存在しない部分の高さを基準、すなわちゼロとする。また、それぞれ二つの高さを持つパターンは互いに重なることはないものとする。この場合の局所的なパターン密度は、次の式を用いて求める。

[0032]

$= 1 + (t1/t2) 2 \cdot \cdot \cdot (1)$

式(1)における 1 は高さ t 1 の領域が単位面積あたりに占める割合、 2 は高さ t 2 の領域が単位面積あたりに占める割合である。式(1)で求めた から 'を求め、シミュレーションを実施することで、二つの段差を持つ場合の研磨後段差の評価が可能となる。なお、シミュレーションで必要になる初期段差としては t 2 の値を用いる。

[0033]

以上のようにして、本実施例によれば、二つの高さが異なるパターンが存在するチップのCMPシミュレーションが可能となる。

[0034]

(実施例3)

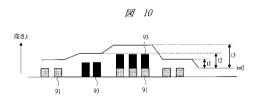

本発明の半導体デバイスの形状シミュレーション方法にかかる実施例3を、図10を用いて説明する。図10は二つの高さの異なるパターンが重なり合う場合を説明するための、デバイスパターンの断面を示す説明図である。

[0035]

上記実施例 2 では、二つの高さの異なるパターンが重なり合わない場合について説明したが、本実施例では二つの高さの異なるパターンが重なり合う場合について以下に説明する。

[0036]

図10を用いて、二つの高さの異なるパターン91,93が形成され、一部でパターン91とパターン93が重なり合う構造を持つチップの場合を説明する。また、パターン91同士は重なり合うことが無く、またパターン93同士も重なり合うことはないものとする。この場合、パターン91とパターン93が重なり合う領域の高さはt3(=t1+t2)となる。3つの高さの違うパターンを含む領域の局所的なパターン密度 は次のようにして求める。

[0037]

$= 3 + 1(t2/t3) + 2(t1/t3) \cdot \cdot \cdot (2)$

式(2)における 1 は高さ t 1 の領域が単位面積あたりに占める割合、 2 は高さ t 2 の領域が単位面積あたりに占める割合、 3 は高さ t 3 の領域が単位面積あたりに占める割合である。式(2)で求めた から 'を求め、シミュレーションを実施することで二つの段差を持つ場合の研磨後段差の評価が可能となる。なお、シミュレーションで必要に

20

30

40

50

なる初期段差としてはt3の値を用いる。

[0038]

以上のようにして、本実施例によれば、二つの高さが異なるパターンが混在し、かつ重なり合う構造のチップにおいてCMPシミュレーションが可能となる。

(8)

[0039]

また、本実施例において、パターン91同士が重なり合う場合、およびパターン93同士が重なり合う場合においては、次のような取り扱いをすればよい。また、ここで最も高くなる場所はパターン93同士が重なり合う場所であり、高さがt5となるものとする。ここで、局所的なパターン密度 は次のようにして求める。また、パターン91同士が重なり合う場所の高さはt4とする。

[0040]

= 5 + 1 (t2/t5) + 2 (t1/t5)

+ 3 (t3/t5) + 4 (t3/t4) · · · (3)

式(3)における 5 はパターン 9 3 同士が重なり合う場所が単位面積あたりに占める割合であり、 4 はパターン 9 1 同士が重なり合う場所が単位面積あたりに占める割合である。

[0041]

以上のようにして、本実施例によれば、二つの高さが異なるパターンが混在し、かつ重なり合う構造のチップにおいてCMPシミュレーションが可能となる。

[0042]

(実施例4)

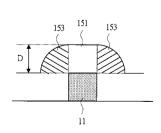

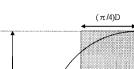

本発明の半導体デバイスの形状シミュレーション方法にかかる実施例4を、図11および図12を用いて説明する。図11および図12はパターン上にオゾン・TEOS法やPSG法などで形成された酸化膜を堆積した場合を説明するための、デバイスパターンの断面を示す説明図である。

[0043]

本実施例では、パターン上にオゾン・TEOS(TetraEthylOrthoSilicate)法やPSG(Phosphosilicate Glass)法などで形成された酸化膜を堆積した場合について、図11、図12を用いて以下に説明する。

[0044]

オゾン・TEOS法で形成した酸化膜151は、図11のように元々存在するパターン11に対してコンフォーマルに堆積する性質がある。このため、膜厚をDとした場合に、図11にハッチングで示した領域153がパターンから見て四分円状になる。この四分円状の領域153を拡大して図示したものが図12である。四分円であるから領域153の断面積は(1/4) D²である。ここで、この四分円の領域153と同じ面積で高さDとなる長方形の短辺の長さを求めると( / 4)Dとなる。コンフォーマルに堆積する酸化膜によって( / 4)Dだけパターンの幅が広くなると仮定すれば、図5における の値を( / 4)Dとしてパターン密度を求めればよいことになる。

[0045]

以上のようにして、本実施例によれば、オゾン・TEOS法やPSG法などの酸化膜による堆積の効果を考慮したシミュレーションが可能となる。

[0046]

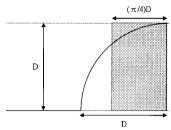

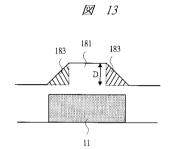

(実施例5)

本発明の半導体デバイスの形状シミュレーション方法にかかる実施例 5 を、図 1 3 および図 1 4 を用いて説明する。図 1 3 および図 1 4 はパターン上にHDP法やこれに類する方法で形成された酸化膜を堆積した場合を説明するための、デバイスパターンの断面を示す説明図である。

[0047]

本実施例では、パターン上にHDP(High Density Plasma)法やこれに類する方法で形成された酸化膜を堆積した場合について、図13、図14を用いて

以下に説明する。

#### [0048]

HDP法で形成した酸化膜181は、図13のように元々存在するパターン11の端部が三角形状に切り取られた形状となる。このため、膜厚をDとした場合に、図13にハッチングで示した領域183がパターンから見て三角形になる。この三角形の領域183を拡大して図示したものが図14である。この三角形は通常のHDPプロセスの場合、二等辺直角三角形となる。この三角形の断面積は(1/2)D²である。ここで、この三角形の領域183と同じ面積で高さDとなる長方形の短辺の長さを求めるとD/2となる。HDP膜によってD/2だけパターンの幅が広くなると仮定すれば、図5におけるの値を-D/2としてパターン密度を求めればよいことになる。ただし、HDP膜の場合、実測との適合性を高めるためにの値を-D/4~-Dとしても良い。

[0049]

以上のように、本実施例によれば、HDP法やこれに類する方法によって堆積した酸化膜の効果を考慮したシミュレーションが可能となる。

[0050]

(実施例6)

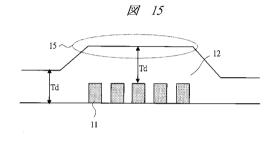

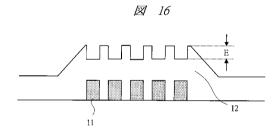

本発明の半導体デバイスの形状シミュレーション方法にかかる実施例6を、図15および図16を用いて説明する。図15および図16はパターン上の酸化膜をエッチングした場合を説明するための、デバイスパターンの断面を示す説明図である。

[0051]

本実施例では、パターン上の酸化膜をエッチングした場合について、図15、図16を 用いて以下に説明する。

[0052]

図15は、パターン11の上に酸化膜12を形成した後の断面形状の概略図を示したものである。ここで、堆積した酸化膜12の厚さはTd[nm]であり、凸パターン15がパターン11上に形成される。また、図16は、図15で形成された酸化膜12をエッチングにより凸パターン15の一部だけを掘り下げたものである。エッチングにより掘り下げる深さはE[nm]である。ここで、図16における局所的なパターン密度 を次のように表現することにする。

[ 0 0 5 3 ]

$= N + E(Td - E) / Td \cdot \cdot \cdot (4)$

式(4)における Nはエッチングされていない凸パターンの単位面積あたりの割合であり、 Eはエッチングされている領域の単位面積あたりの割合である。上記の取り扱いにより、エッチングされた部分の体積を考慮したパターン密度 を求めることができる。この を応力応答関数により平均化して を求めれば、CMPシミュレーションに利用することができる。

[0054]

以上のように、本実施例によれば、パターン上の酸化膜をエッチングした場合について もCMPシミュレーションを実施することが可能となる。

[0055]

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【産業上の利用可能性】

[0056]

本発明は、半導体デバイスの製造技術に関し、特に、半導体デバイスの表面をCMPにより研磨した後の表面形状を予測するシミュレーション方法に適用して有効である。

【図面の簡単な説明】

[0057]

【図1】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1において

10

20

30

40

20

30

40

50

、 C M P プロセスにおける研磨過程を説明するための、デバイスパターンの断面を示す説明図である。

- 【図2】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1において、局所的なパターン密度と平均化したパターン密度の概念を説明するための、デバイスパターンの上面を示す説明図(1)である。

- 【図3】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1において、局所的なパターン密度と平均化したパターン密度の概念を説明するための、デバイスパターンの上面を示す説明図(2)である。

- 【図4】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1において、パターンの拡張処理を説明するための、デバイスパターンの上面を示す説明図(1)である。

- 【図 5 】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例 1 において、パターンの拡張処理を説明するための、デバイスパターンの上面を示す説明図( 2 )である。

- 【 図 6 】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例 1 において、パターンの拡張処理を説明するための、デバイスパターンの上面を示す説明図( 3 )である。

- 【図7】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1において、パターンの拡張処理を説明するための、デバイスパターンの上面を示す説明図(4)である。

- 【図8】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例1において、パターンの拡張処理を説明するための、デバイスパターンの上面を示す説明図(5)である。

- 【図9】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例2において、2種類以上の高さのパターンが同一のチップ上に存在する場合を説明するための、デバイスパターンの断面を示す説明図である。

- 【図10】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例3において、二つの高さの異なるパターンが重なり合う場合を説明するための、デバイスパターンの断面を示す説明図である。

- 【図11】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例4において、パターン上にオゾン・TEOS法やPSG法などで形成された酸化膜を堆積した場合を説明するための、デバイスパターンの断面を示す説明図(1)である。

- 【図12】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例4において、パターン上にオゾン・TEOS法やPSG法などで形成された酸化膜を堆積した場合を説明するための、デバイスパターンの断面を示す説明図(2)である。

- 【図13】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例5において、パターン上にHDP法やこれに類する方法で形成された酸化膜を堆積した場合を説明するための、デバイスパターンの断面を示す説明図(1)である。

- 【図14】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例 5 において、パターン上にHDP法やこれに類する方法で形成された酸化膜を堆積した場合を説明するための、デバイスパターンの断面を示す説明図(2)である。

- 【図15】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例6において、パターン上の酸化膜をエッチングした場合を説明するための、デバイスパターンの断面を示す説明図(1)である。

- 【図16】本発明の半導体デバイスの形状シミュレーション方法にかかる実施例6において、パターン上の酸化膜をエッチングした場合を説明するための、デバイスパターンの断面を示す説明図(2)である。

## 【符号の説明】

[0058]

1 1 ... パターン、 1 2 ... 酸化膜、 1 3 ... 研磨パッド、 1 5 ... 凸パターン、 2 1 ... パター

ン、 9 1 ... パターン、 9 2 ... パターン、 9 3 ... パターン、 1 5 1 ... 酸化膜、 1 5 3 ... 領域 、 1 8 1 ... 酸化膜、 1 8 3 ... 領域。

【図1】

【図2】

【図3】

【図4】

# 【図6】

【図5】

【図7】

【図8】

【図10】

【図9】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

## フロントページの続き

F ターム(参考) 3C058 AA07 BA02 BA09 BB06 BB09 BC03 CB01 CB03 DA12 DA17 5B046 AA08 JA04