(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(21) 출원번호 10-2003-0057245 (65) 공개번호 10-2005-0019453

(22) 출원일자 2003년08월19일 (43) 공개일자 2005년03월03일

(73) 특허권자 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 박윤식

경기도 용인시 기흥읍 신갈리 158번지 양현마을 풍립아파트 304동 702호

심사관 : 이인용

(54) 단일의 기준 저항기를 이용하여 종결 회로 및 오프-체구동 회로의 임피던스를 제어하는 장치

요약

본 발명에 따른 반도체 집적 회로 장치는 외부 기준 저항기에 연결되며, 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생하는 임피던스 제어 회로를 포함한다. 입력 회로는 입력 신호 전송 라인을 통해 외부 신호를 입력받고, 입력된 신호를 내부 회로로 출력한다. 종결 회로는 임피던스 제어 코드들 중 적어도 하나에 응답하여 입력 신호 전송 라인을 종결시킨다. 출력 회로는 내부 회로로부터 출력되는 신호에 따라 출력 신호 전송 라인을 구동하며, 임피던스가 임피던스 제어 코드들에 따라 가변된다.

대표도

도 1

## 명세서

## 도면의 간단한 설명

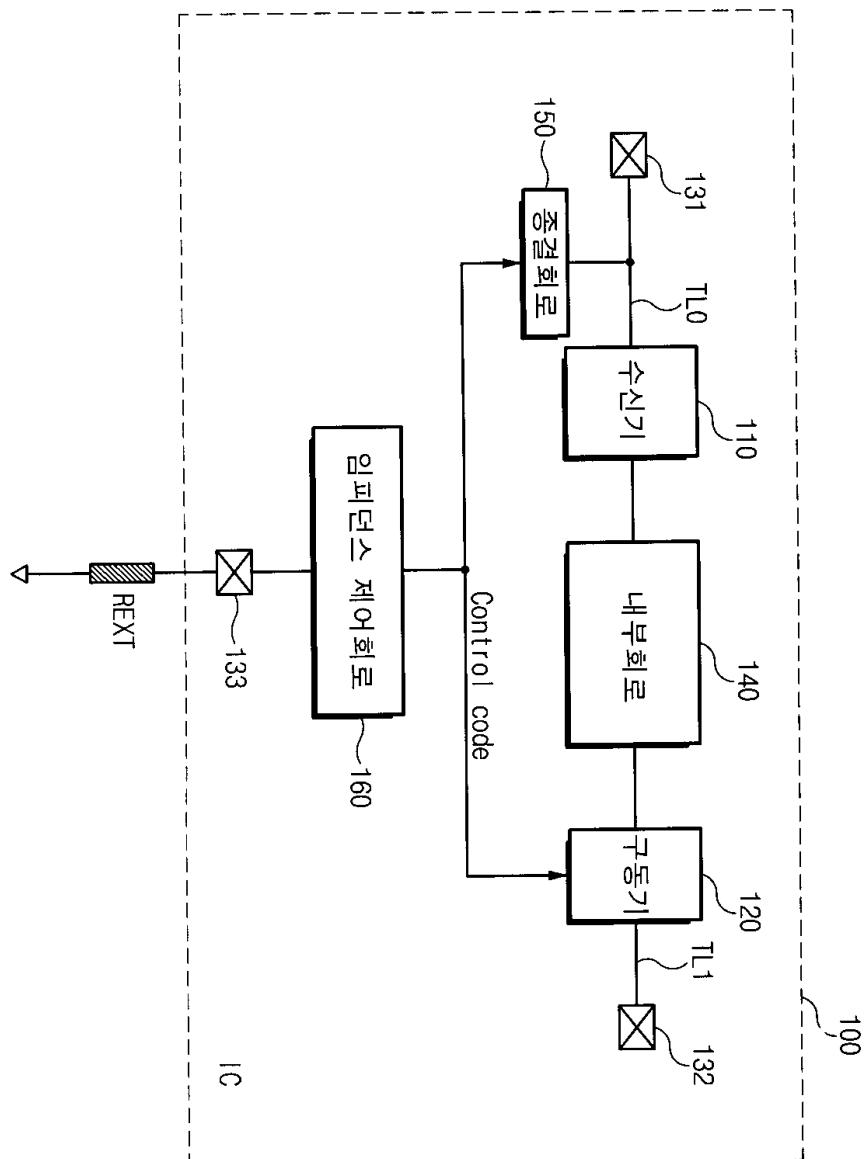

도 1은 본 발명에 따른 반도체 집적 회로 장치를 보여주는 블록도;

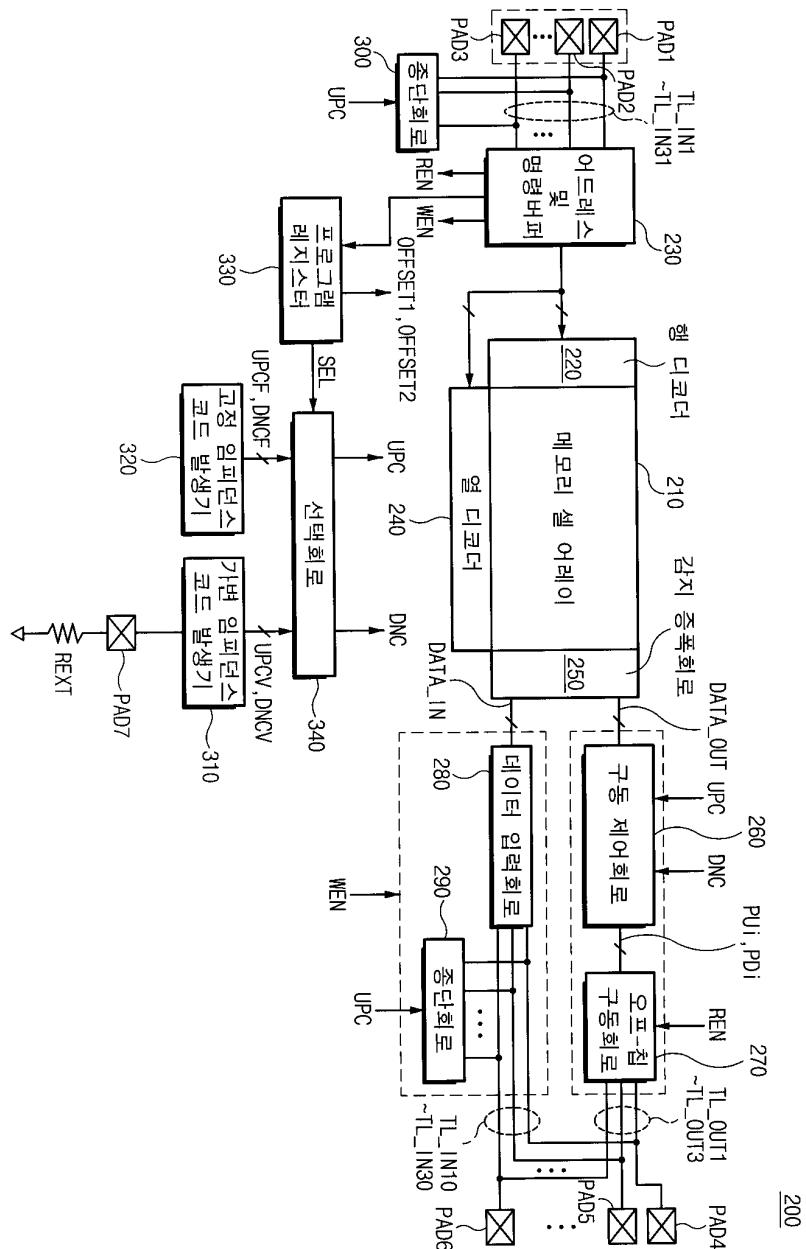

도 2는 본 발명에 따른 반도체 메모리 장치를 보여주는 블록도;

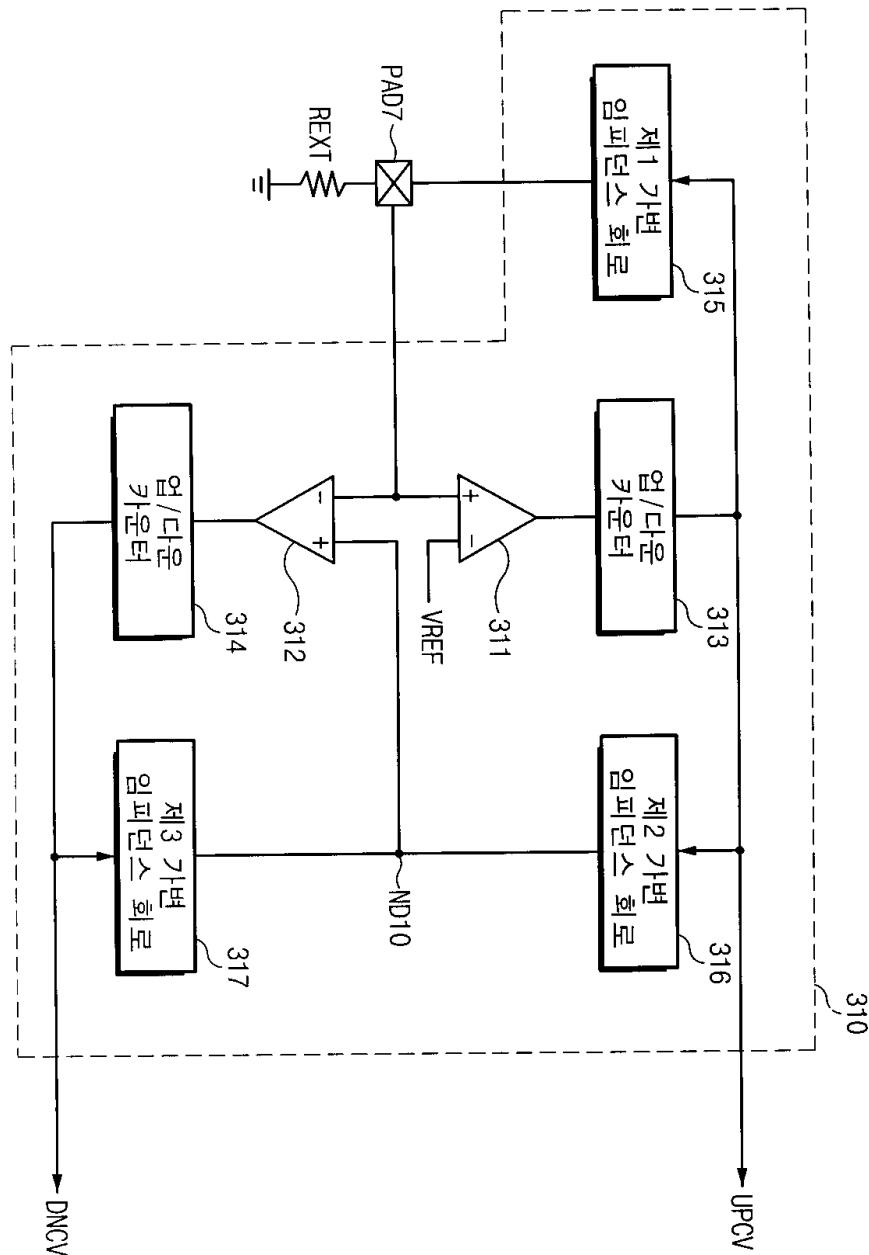

도 3은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 가변 임피던스 코드 발생회로를 보여주는 블록도;

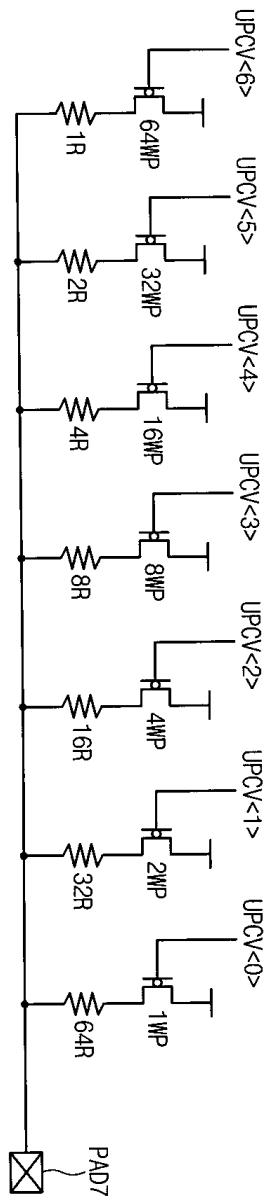

도 4a 및 도 4b는 본 발명의 바람직한 실시예에 따른 도 3에 도시된 가변 임피던스 회로들을 보여주는 회로도들;

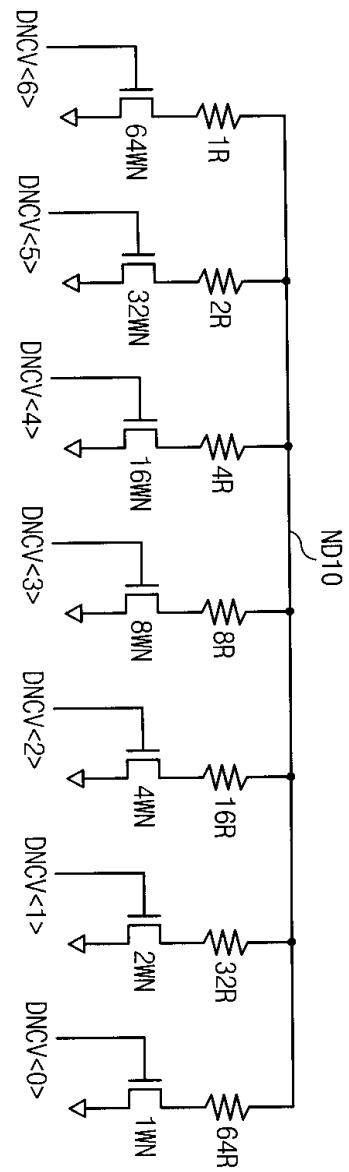

도 5는 본 발명의 바람직한 실시예에 따른 도 2에 도시된 고정 임피던스 코드 발생 회로를 보여주는 회로도;

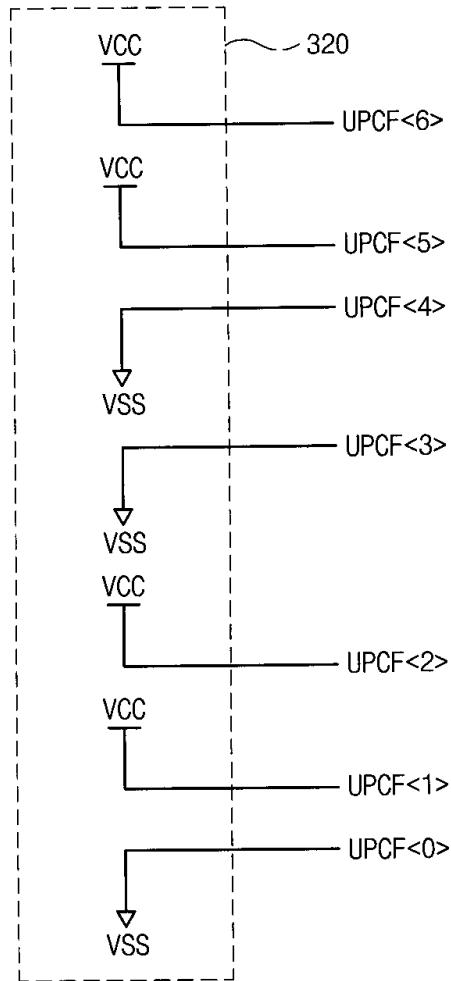

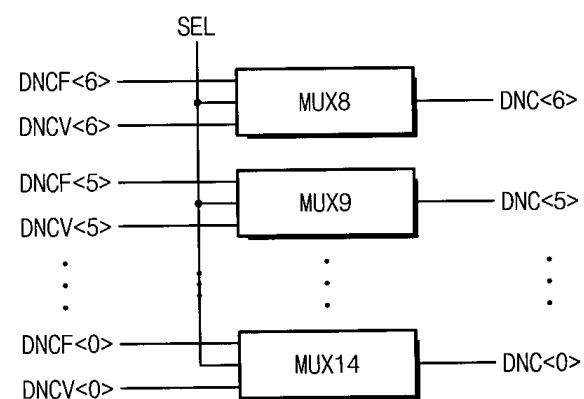

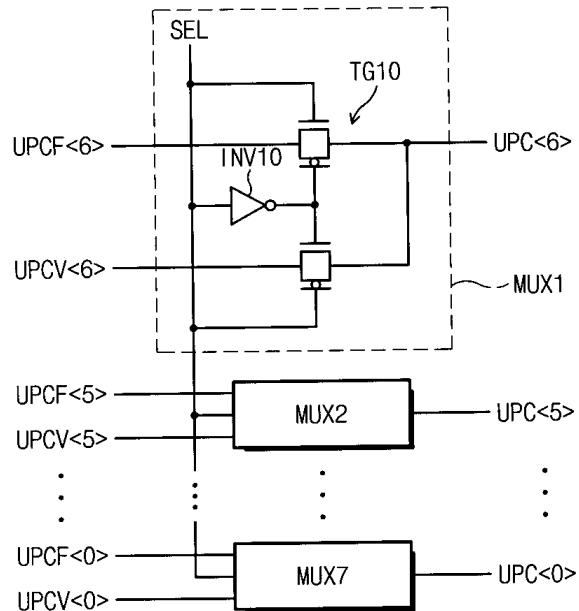

도 6은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 선택 회로를 보여주는 블록도;

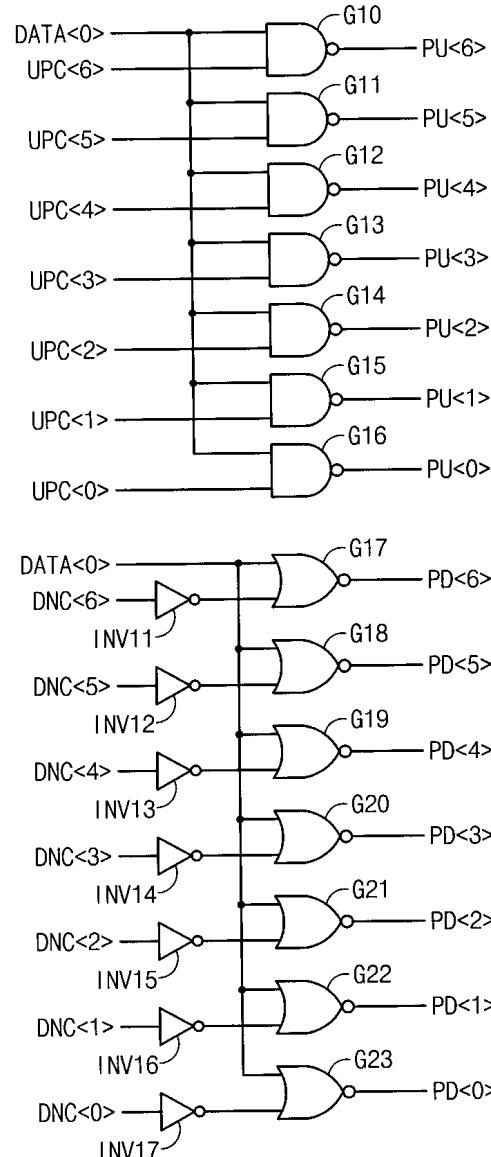

도 7은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 구동 제어 회로를 보여주는 회로도;

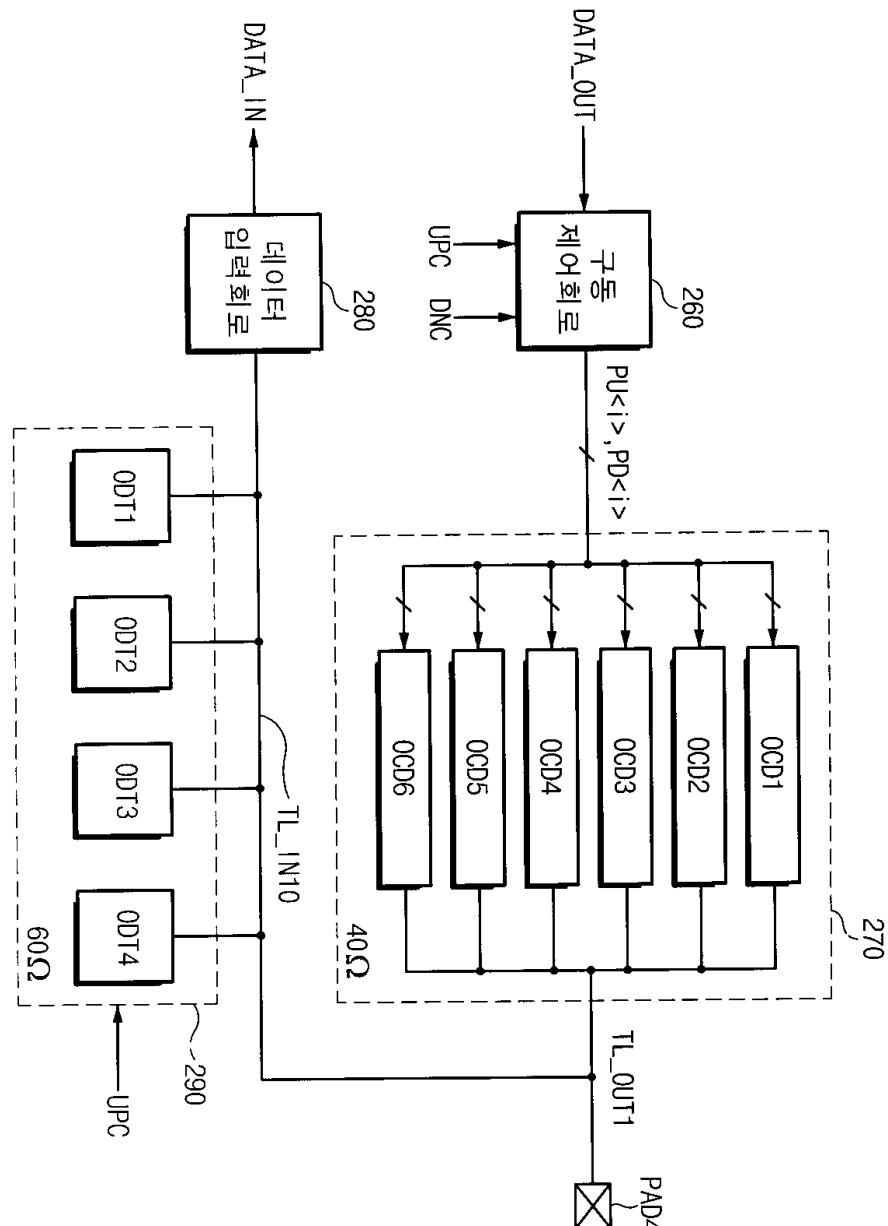

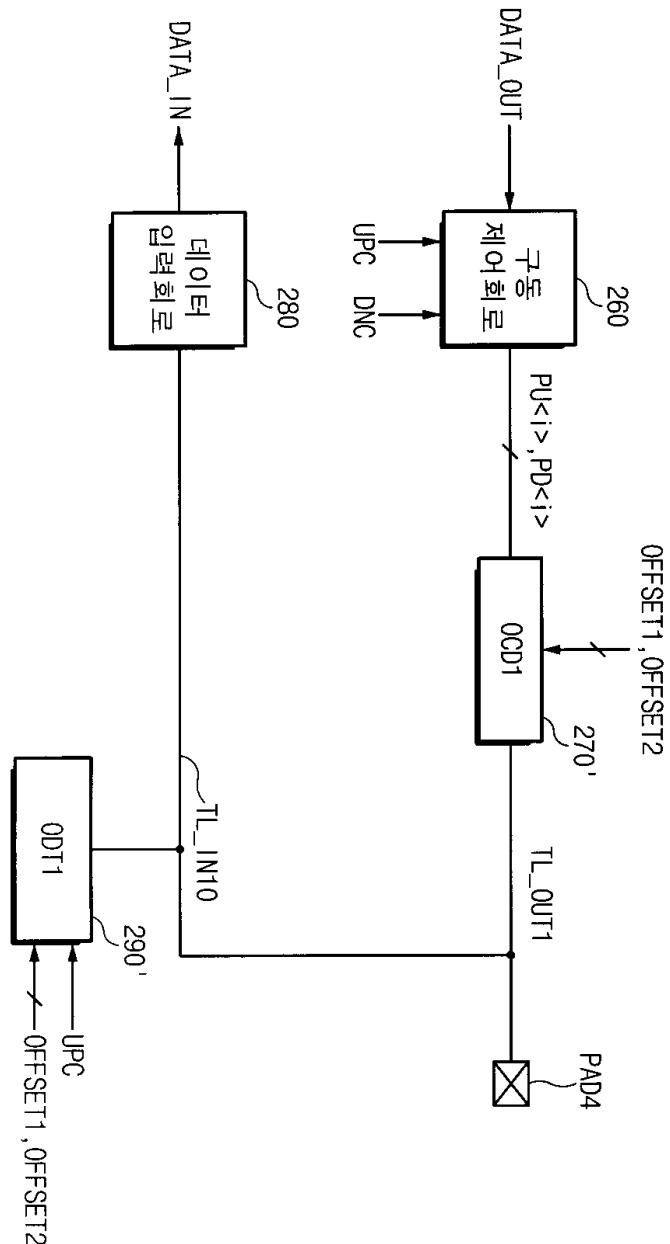

도 8은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 오프-칩 구동 회로 및 종결 회로를 보여주는 블록도;

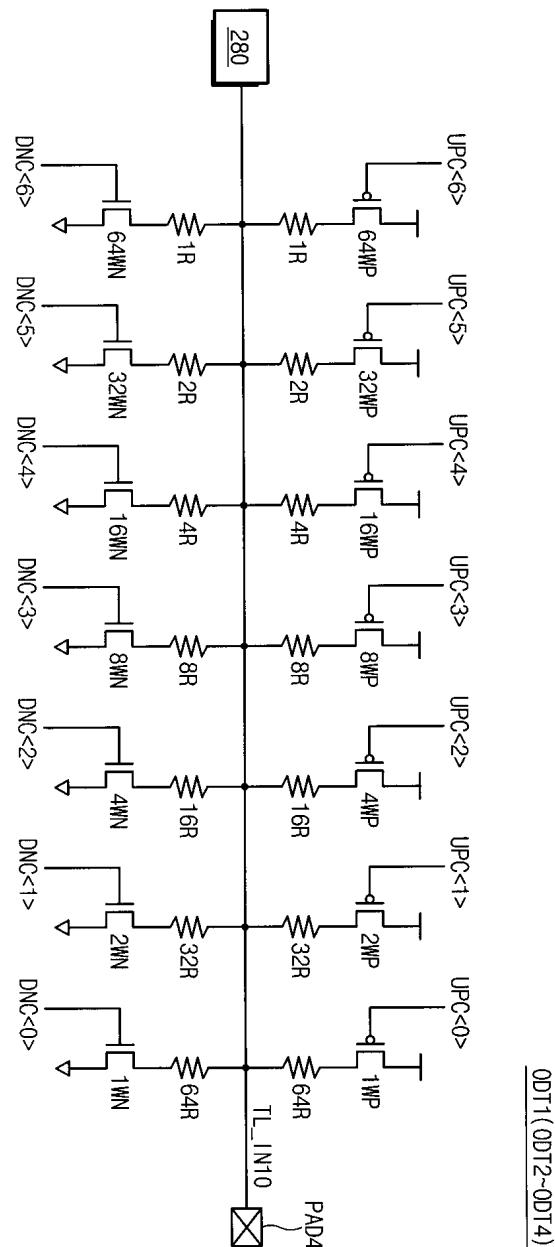

도 9는 본 발명의 바람직한 실시예에 따른 도 8에 도시된 오프-칩 구동 블록을 보여주는 회로도;

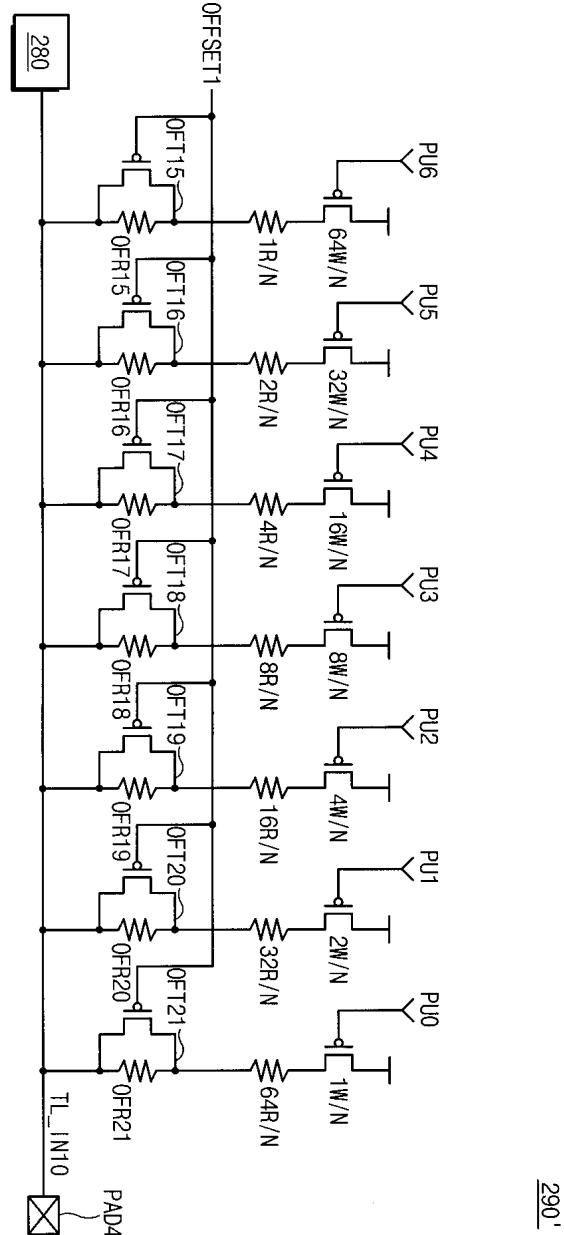

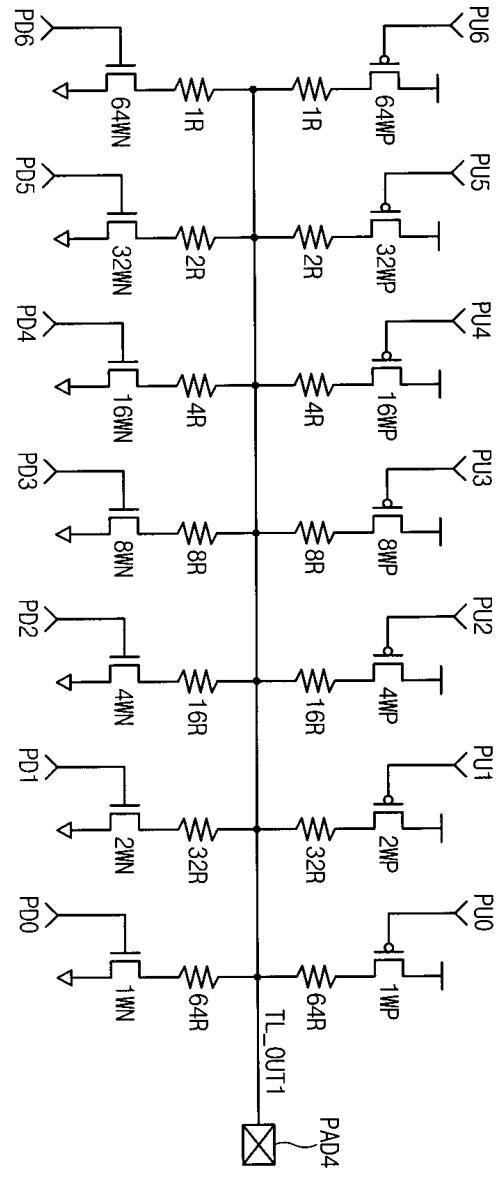

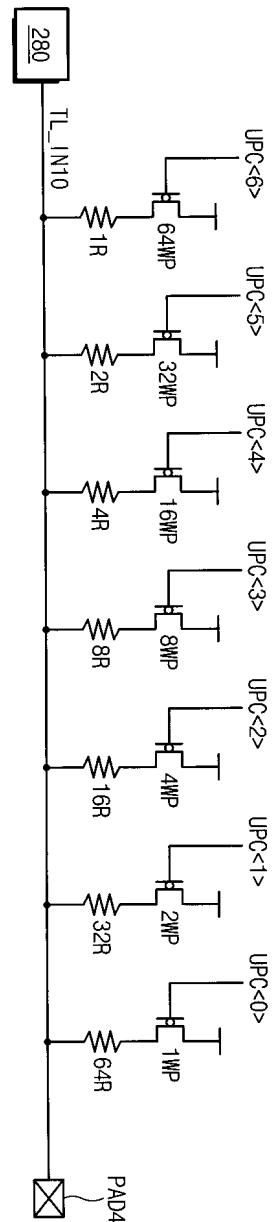

도 10은 본 발명의 바람직한 실시예에 따른 도 8에 도시된 종단 블록을 보여주는 회로도;

도 11은 본 발명의 다른 실시예에 따른 도 8에 도시된 종단 블록을 보여주는 회로도;

도 12는 본 발명의 다른 실시예에 따른 도 2에 도시된 오프-칩 구동 회로 및 종결 회로를 보여주는 블록도;

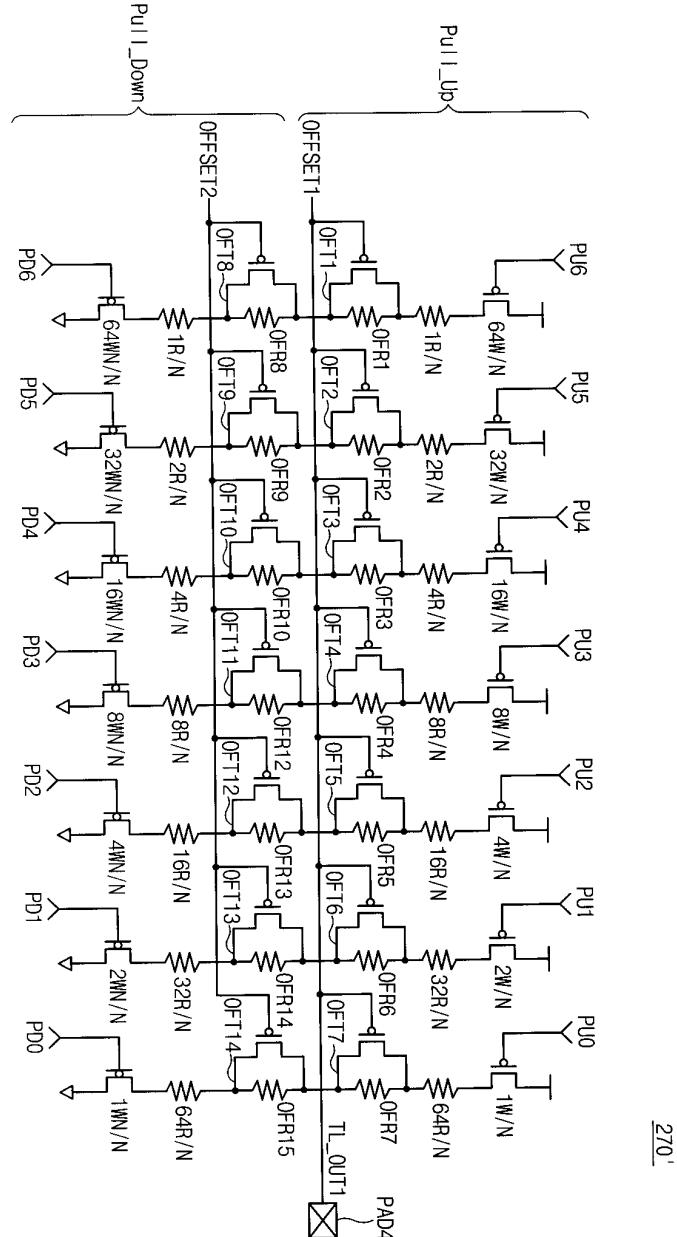

도 13은 본 발명의 바람직한 실시예에 따른 도 12에 도시된 오프-칩 구동 회로를 보여주는 회로도; 그리고

도 14는 본 발명의 바람직한 실시예에 따른 도 12에 도시된 종결 회로를 보여주는 회로도이다.

\* 도면의 주요 부분에 대한 부호 설명 \*

100 : 반도체 집적 회로 장치 110 : 수신기

120 : 구동기 140 : 내부 회로

150 : 종결 회로 160 : 임피던스 제어 회로

200 : 반도체 메모리 장치 210 : 메모리 셀 어레이

220 : 행 디코더 회로 230 : 어드레스 및 명령 버퍼 회로

240 : 열 디코더 회로 250 : 감지 증폭 회로

260 : 구동 제어 회로 270 : 오프-칩 구동 회로

280 : 데이터 입력 회로 290, 300 : 종결 회로

310 : 가변 임피던스 코드 발생 회로 320 : 고정 임피던스 코드 발생 회로

330 : 프로그램 레지스터 340 : 선택 회로

### **발명의 상세한 설명**

#### **발명의 목적**

#### **발명이 속하는 기술 및 그 분야의 종래기술**

본 발명은 반도체 집적 회로 장치에 관한 것으로, 좀 더 구체적으로는 프로그램 가능한 버스 종결 회로 (programmable bus termination circuit) 및 프로그램 가능한 임피던스 출력 구동 회로 (programmable impedance output driver circuit)를 포함하는 반도체 집적 회로 장치에 관한 것이다.

더블 데이터 레이트 (double data rate: DDR) 메모리를 포함한 고속 집적 회로 장치를 설계함에 있어서, 이전 버전의 집적 회로 장치와 대비하여 볼 때 데이터/어드레스/제어 신호의 입력 및 출력과 관련된 AC 특성이 매우 중요해지고 있다. AC 특성은 집적 회로 장치 또는 집적 회로 장치를 제어하기 위한 컨트롤러 자체의 문제에 기인하기보다는 두 개 또는 그 이상의 장치들을 연결하는 채널의 특성에 기인한다. 그러므로, 채널 특성 (channel characteristic)을 고려하여 고속 집적 회로 장치를 설계하는 것이 무엇보다 중요하다.

채널 특성을 향상시키기 위한 다양한 노력들이 진행되어 오고 있다. 그러한 노력들의 일환으로서, 프로그램 가능한 임피던스 온-다이 종결 회로 및 오프-칩 구동 회로가 제안되어 오고 있다. 예시적인 온-다이 종결 회로 및 오프-칩 구동 회로가 U.S. Patent No. 5,666,078에 "PROGRAMMABLE IMPEDANCE OUTPUT DRIVER"라는 제목으로, U.S. Patent No. 5,955,894에 "METHOD FOR CONTROLLING THE IMPEDANCE OF A DRIVER CIRCUIT"라는 제목으로, U.S. Patent No. 6,157,206에 "ON-CHIP TERMINATION"라는 제목으로, 그리고 대한민국특허번호 제10-0332455호에 "반도체 장치의 가변 임피던스 콘트롤 회로 및 오프 칩 구동 회로와 가변 임피던스 콘트롤 방법"이라는 제목으로 각각 기재되어 있다.

잘 알려진 바와 같이, 온-다이 종결 회로 및 오프-칩 구동 회로의 임피던스는 서로 상이한 값들을 갖도록 조정된다. 예를 들면, 온-다이 종결 회로의 임피던스는  $60\Omega$ 의 임피던스를 갖도록 대응하는 제어 회로에 의해서 조정되고, 오프-칩 구동 회로의 임피던스는  $40\Omega$ 의 임피던스를 갖도록 대응하는 제어 회로에 의해서 조정된다. 즉, 앞서 언급된 특허들에서 알 수 있듯이, 온-다이 종결 회로 및 오프-칩 구동 회로의 임피던스를 제어하기 위해서는 대응하는 임피던스 제어 회로들 및 외부 기준 저항기들이 개별적으로 사용되고 있다.

하지만, 이러한 임피던스 제어 방식을 통해 채널 특성을 향상시키고자 하는 경우, 칩 사이즈 뿐만 아니라 편수가 필연적으로 증가하며, 이는 반도체 집적 회로 장치를 설계하는 데 부담이 된다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 하나의 외부 기준 저항기를 이용하여 종결 회로 및 오프-칩 구동 회로를 제어할 수 있는 임피던스 제어 구조와 그것을 포함한 반도체 집적 회로 장치를 제공하는 것이다.

### 발명의 구성 및 작용

상술한 제반 목적을 달성하기 위한 본 발명의 특징에 따르면, 반도체 집적 회로 장치는 임피던스 제어 회로, 입력 회로, 출력 회로 그리고 종결 회로를 포함한다. 임피던스 제어 회로는 외부 기준 저항기에 연결되며, 상기 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생한다. 입력 회로는 입력 신호 전송 라인을 통해 외부 신호를 입력받고, 상기 입력된 신호를 내부 회로로 출력한다. 종결 회로는 상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 신호 전송 라인을 종결시킨다. 출력 회로는 상기 내부 회로로부터 출력되는 신호에 따라 출력 신호 전송 라인을 구동하며, 임피던스가 상기 임피던스 제어 코드들에 따라 가변된다.

이 실시예에 있어서, 상기 종결 회로는 상기 입력 신호 전송 라인에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들 중 어느 하나에 의해서 제어된다. 또는, 상기 종결 회로는 상기 입력 신호 전송 라인에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들에 의해서 제어된다. 상기 구동 회로는 상기 출력 신호 전송 라인에 병렬 연결된 복수 개의 구동기들을 포함하며, 상기 구동기들 각각의 임피던스는 상기 임피던스 제어 코드들에 따라 조정된다.

이 실시예에 있어서, 상기 임피던스 제어 회로는 상기 외부 기준 저항기와 연결되는 패드와; 상기 패드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 임피던스 제어 코드들 중 제 1 임피던스 제어 코드에 의해서 제어되는 제 1 가변 임피던스 회로와; 상기 패드의 전압을 기준 전압과 비교하는 제 1 비교기와; 상기 제 1 비교기의 출력에 응답하여 상기 제 1 임피던스 제어 코드를 발생하는 제 1 업/다운 카운터와; 내부 노드에 연결되며, 상기 외부가변 저항기와 동일한 임피던스를 갖도록 상기 제 1 임피던스 제어 코드에 의해서 제어되는 제 2 가변 임피던스 회로와; 상기 내부 노드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 임피던스 제어 코드들 중 제 2 임피던스 제어 코드에 의해서 제어되는 제 3 가변 임피던스 회로와; 상기 내부 노드의 전압과 상기 패드의 전압을 비교하는 제 2 비교기와; 그리고 상기 제 2 비교기의 출력에 응답하여 상기 제 2 임피던스 제어 코드를 발생하는 제 2 업/다운 카운터를 포함한다.

본 발명의 다른 특징에 따르면, 반도체 메모리 장치는 행들과 열들로 배열된 메모리 셀들의 어레이와; 메모리 셀들로부터/에 데이터를 읽고/쓰는 감지 증폭 회로와; 고정 임피던스 제어 코드들을 발생하는 제 1 코드 발생 회로와; 외부 기준 저항기에 연결되며, 상기 외부 기준 저항기의 임피던스에 따라 가변되는 가변 임피던스 제어 코드들을 발생하는 제 2 코드 발생 회로와; 코드 선택 신호에 응답하여 상기 고정 임피던스 제어 코드들 또는 상기 가변 임피던스 제어 코드들을 선택하는 선택 회로와; 상기 감지 증폭 회로로부터 출력되는 데이터 및 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들에 응답하여 풀업 및 풀다운 제어 신호들을 발생하는 구동 제어 회로와; 읽기 동작 동안 상기 풀업 및 풀다운 제어 신호들에 응답하여 데이터 전송 라인들을 구동하며, 임피던스가 상기 풀업 및 풀다운 제어 신호들에 의해서 가변되는 오프-칩 구동 회로와; 쓰기 동작 동안 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 데이터 전송 라인들을 종결시키는 제 1 종결 회로를 포함한다.

이 실시예에 있어서, 반도체 메모리 장치는 입력 전송 라인들을 통해 입력되는 어드레스 및 제어 신호들을 입력받는 입력 버퍼 회로와; 상기 입력 버퍼 회로로부터 출력되는 행 어드레스에 응답하여 상기 행들을 선택하는 행 디코더 회로와; 상기 입력 버퍼 회로로부터 출력되는 열 어드레스에 응답하여 상기 열들을 선택하는 열 디코더 회로와; 그리고 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 전송 라인들을 종결시키는 제 2 종결 회로를 더 포함한다.

이 실시예에 있어서, 상기 제 2 코드 발생 회로는 상기 외부 기준 저항기와 연결되는 패드와; 상기 패드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 가변 임피던스 제어 코드들 중 제 1 가변 임피던스 제어 코드에 의해서 제어되는 제 1 가변 임피던스 회로와; 상기 패드의 전압을 기준 전압과 비교하는 제 1 비교기와; 상기 제 1 비교기의 출력에 응답하여 상기 제 1 가변 임피던스 제어 코드를 발생하는 제 1 업/다운 카운터와; 내부 노드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 제 1 가변 임피던스 제어 코드에 의해서 제어되는 제 2 가변 임피던스 회로와; 상기 내부 노드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 가변 임피던스 제어 코드들 중 제 2 가변 임피던스 제어 코드에 의해서 제어되는 제 3 가변 임피던스 회로와; 상기 내부 노드의 전압과 상기 패드의 전압을 비교하는 제 2 비교기와; 그리고 상기 제 2 비교기의 출력에 응답하여 상기 제 2 가변 임피던스 제어 코드를 발생하는 제 2 업/다운 카운터를 포함한다.

본 발명의 또 다른 특징에 따르면, 반도체 집적 회로 장치는 입력 신호 전송 라인을 통해 외부 신호를 입력받고, 상기 입력된 신호를 내부 회로로 출력하는 입력 회로와; 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생하는 임피던스 제어 회로와; 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 신호 전송 라인을 종결시키는 종결 회로와; 그리고 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 내부 회로로부터 출력되는 신호에 따라 출력 신호 전송 라인을 구동하되, 임피던스가 상기 임피던스 제어 코드들에 따라 가변되는 출력 회로를 포함하며, 상기 종결 회로 및 상기 출력 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 임피던스 제어 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는다.

본 발명의 또 다른 특징에 따르면, 반도체 메모리 장치는 행들과 열들로 배열된 메모리 셀들의 어레이와; 메모리 셀들로부터/에 데이터를 읽고/쓰는 감지 증폭 회로와; 고정 임피던스 제어 코드들을 발생하는 제 1 코드 발생 회로와; 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 외부 기준 저항기의 임피던스에 따라 가변되는 가변 임피던스 제어 코드들을 발생하는 제 2 코드 발생 회로와; 코드 선택 신호에 응답하여 상기 고정 임피던스 제어 코드들 또는 상기 가변 임피던스 제어 코드들을 선택하는 선택 회로와; 상기 감지 증폭 회로로부터 출력되는 데이터 및 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들에 응답하여 풀업 및 풀다운 제어 신호들을 발생하는 구동 제어 회로와; 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 읽기 동작 동안 상기 풀업 및 풀다운 제어 신호들에 응답하여 데이터 전송 라인들을 구동하되, 임피던스가 상기 풀업 및 풀다운 제어 신호들에 의해서 가변되는 오프-칩 구동 회로와; 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 쓰기 동작 동안 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 데이터 전송 라인들을 종결시키는 제 1 종결 회로를 포함하며, 상기 제 1 종결 회로 및 상기 출력 회로의 이진 가중치 트랜지스터들 및 이중 가중치 저항기들은 상기 제 2 코드 발생 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는다.

이 실시예에 있어서, 반도체 메모리 장치는 입력 전송 라인들을 통해 입력되는 어드레스 및 제어 신호들을 입력받는 입력 버퍼 회로와; 상기 입력 버퍼 회로로부터 출력되는 행 어드레스에 응답하여 상기 행들을 선택하는 행 디코더 회로와; 상기 입력 버퍼 회로로부터 출력되는 열 어드레스에 응답하여 상기 열들을 선택하는 열 디코더 회로와; 그리고 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 전송 라인들을 종결시키는 제 2 종결 회로를 더 포함한다.

본 발명의 또 다른 특징에 따르면, 반도체 메모리 장치는 행들과 열들로 배열된 메모리 셀들의 어레이와; 메모리 셀들로부터/에 데이터를 읽고/쓰는 감지 증폭 회로와; 외부 기준 저항기에 연결되며, 상기 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생하는 코드 발생 회로와; 상기 감지 증폭 회로로부터 출력되는 데이터 및 임피던스 제어 코드들에 응답하여 풀업 및 풀다운 제어 신호들을 발생하는 구동 제어 회로와; 읽기 동작 동안 상기 풀업 및 풀다운 제어 신호들에 응답하여 데이터 전송 라인들을 구동하며, 임피던스가 상기 풀업 및 풀다운 제어 신호들에 의해서 가변되는 오프-칩 구동 회로와; 그리고 쓰기 동작 동안 상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 데이터 전송 라인들을 종결시키는 종결 회로를 포함한다.

본 발명의 바람직한 실시예들이 참조 도면들에 의거하여 이하 상세히 설명될 것이다.

도 1은 본 발명에 따른 반도체 집적 회로 장치를 보여주는 블록도이다. 도 1을 참조하면, 본 발명의 반도체 집적 회로 장치(100)는 다른 집적 회로 장치와 통신하도록 수신기(receiver)(110)와 구동기(driver)(120)를 포함한다. 수신기(110)는 신호 전송 라인(TL0)을 통해 패드(131)에 연결되며, 외부에서 패드(131)로 전송되는 신호(예를 들면, 제어 신호들 또는 어드레스 신호들)를 입력받는다. 구동기(120)는 신호 전송 라인(TL1)을 통해 패드(132)에 연결되며, 내부 회로(140)로부터 출력되는 신호(예를 들면, 데이터)에 따라 신호 전송 라인(TL1)을 구동한다.

신호 전송 라인(TL0)에는 종결 회로(termination circuit)(150)가 연결되며, 비록 도면에는 도시되지 않았지만, 패드(131)는 외부의 전송 라인을 통해 다른 집적 회로 장치와 연결될 것이다. 종결 회로(150)는 외부 전송 라인(미도시됨)과 수신기(110) 사이의 임피던스 불일치(impedance mismatch)로 인한 신호 반사를 줄일 수 있도록 신호 전송 라인(TL0)을 종결시킨다. 임피던스 제어 회로(impedance control circuit)(160)는 외부 기준 저항기(REXT)와 연결된 패드(133)에 연결되며, 외부 기준 저항기(REXT)의 임피던스에 따라 가변되는 제어 코드를 생성한다. 종결 회로(150) 및 구동기(120)는 임피던스 제어 회로(160)에서 생성된 제어 코드에 의해서 동시에 제어된다. 따라서, 임피던스 제어 회로(160)는 외부 기준 저항기(REXT)의 임피던스에 따라 종결 회로(150)의 임피던스 뿐만 아니라 구동기(120)의 임피던스를 동시에 가변적으로 제어한다.

본 발명에 따른 반도체 집적 회로 장치(100)는 하나의 외부 기준 저항기(REXT)를 이용한 임피던스 제어 회로(160)에서 생성된 제어 코드에 따라 종결 회로(150)의 임피던스 및 구동기(120)의 임피던스가 동시에 제어되도록 구현된다.

본 발명에 따른 가변 임피던스 제어 구조가 반도체 집적 회로 장치로서 반도체 메모리 장치를 이용하여 이하 상세히 설명될 것이다. 비록 본 발명에 따른 가변 임피던스 제어 구조가 반도체 메모리 장치를 이용하여 설명되지만, 본 발명에 따른 가변 임피던스 제어 구조가 여기에 기재된 반도체 메모리 장치에 국한되지 않음은 이 분야의 통상적인 지식을 습득한 자에게 자명하다. 예를 들면, 본 발명에 따른 가변 임피던스 제어 구조는 높은 주파수 영역에서 동작하는 전자 장치들에 적용될 수 있다.

도 2는 본 발명에 따른 반도체 메모리 장치를 보여주는 블록도이다. 본 발명에 따른 반도체 메모리 장치는 채널 특성에 민감한 고주파 메모리로, 예를 들면, 더블 데이터 레이트(double data rate: DDR) 메모리이다. 하지만, 본 발명에 따른 반도체 메모리 장치가 DDR 메모리에 국한되지 않음은 자명하다.

도 2를 참조하면, 본 발명의 반도체 메모리 장치(200)는 데이터 정보를 저장하기 위한 메모리 셀 어레이(210)를 포함하며, 비록 도면에는 도시되지 않았지만, 메모리 셀 어레이(210)는 행들(또는 워드 라인들)과 열들(또는 비트 라인들)의 매트릭스 형태로 배열된 메모리 셀들을 포함한다. 행 디코더 회로(row decoder circuit)(220)는 어드레스 및 명령 버퍼 회로(address and command buffer circuit)(230)로부터 출력되는 행 어드레스에 따라 메모리 셀 어레이(210)의 행들을 선택한다. 열 디코더 회로(column decoder circuit)(240)는 어드레스 및 명령 버퍼 회로(230)로부터 출력되는 열 어드레스에 따라 메모리 셀 어레이(210)의 열들을 선택한다. 감지 증폭 회로(sense amplifier circuit)(250)는 읽기 동작시 메모리 셀 어레이(210)로부터 데이터를 읽고 쓰기 동작시 메모리 셀 어레이(210)에 데이터를 쓴다.

구동 제어 회로(260)는 감지 증폭 회로(250)로부터 출력되는 데이터를 입력받고, 임피던스 제어 코드들(UPC, DNC)에 응답하여 풀업 및 풀다운 제어 신호들(PDi, PUi)을 발생한다. 오프-칩 구동 회로(270)는 구동 제어 회로(260)로부터 출력되는 풀업 및 풀다운 제어 신호들(PDi, PUi)에 응답하여 출력 신호 전송 라인들(TL\_OUT1-TL\_OUT3)을 구동한다. 출력 신호 전송 라인들(TL\_OUT1-TL\_OUT3)은 대응하는 패드들(PAD4-PAD6)에 각각 연결된다. 오프-칩 구동 회로(270)의 임피던스는 풀업 및 풀다운 제어 신호들(PUi, PDi)의 선택적인 활성화에 따라 가변될 것이다. 이는 이후 상세히 설명될 것이다. 데이터 입력 회로(280)는 입력 신호 전송 라인들(TL\_IN10-TL\_IN30)을 통해 대응하는 패드들(PAD4-PAD6)에 각각 연결되며, 패드들(PAD4-PAD6)에 인가되는 데이터를 감지 증폭 회로(250)로 전송한다. 입력 신호 전송

라인들 (TL\_IN10-TL\_IN30)에는 종결 회로 (termination circuit) (290)가 연결되어 있다. 종결 회로 (290)는 임피던스 제어 코드 (UPC) 또는 임피던스 제어 코드들 (UPC, DNC)에 응답하여 동작하며, 외부 전송 라인 (미도시됨)과 수신기로서 데이터 입력 회로 (280) 사이의 임피던스 불일치로 인한 신호 반사를 줄일 수 있도록 입력 신호 전송 라인들 (TL\_IN10-TL\_IN30)을 종결시킨다.

이 실시예에 있어서, 구동 제어 회로 (260) 및 오프-칩 구동 회로 (270)는 읽기 동작을 나타내는 제어 신호 (REN)의 활성화시에 동작하며, 데이터 입력 회로 (280) 및 종결 회로 (290)는 쓰기 동작을 나타내는 제어 신호 (WEN)의 활성화시에 동작한다.

계속해서 도 2를 참조하면, 어드레스 및 명령 버퍼 회로 (230)는 입력 신호 전송 라인들 (TL\_IN11-TL\_IN31)을 통해 패드들 (PAD1-PAD3)에 각각 연결되어 있다. 어드레스 및 명령 버퍼 회로 (230)는 입력 신호 전송 라인들 (TL\_IN11-TL\_IN31)을 통해 외부로부터 정해진 타이밍에 따라 어드레스 및 제어 명령을 입력받는다. 입력 어드레스 중 행 어드레스는 행 디코더 회로 (220)로 전달되고, 열 어드레스는 열 디코더 회로 (240)로 전달된다. 입력 신호 전송 라인들 (TL\_IN11-TL\_IN31)에는 종결 회로 (300)가 연결되어 있다. 종결 회로 (300)는 임피던스 제어 코드 (UPC) 또는 임피던스 제어 코드들 (UPC, DNC)에 응답하여 동작하며, 외부 전송 라인 (미도시됨)과 수신기로서 어드레스 및 명령 버퍼 회로 (230) 사이의 임피던스 불일치로 인한 신호 반사를 줄일 수 있도록 입력 신호 전송 라인들 (TL\_IN11-TL\_IN31)을 종결시킨다.

도 2에 도시된 바와 같이, 패드 (PAD7)에는 외부 기준 저항기 (REXT) 및 가변 임피던스 코드 발생 회로 (variable impedance code generator circuit) (310)가 연결되어 있다. 가변 임피던스 코드 발생 회로 (310)는 외부 기준 저항기 (REXT)의 임피던스에 따라 가변되는 가변 임피던스 제어 코드들 (UPCV, DNCV)을 발생한다. 고정 임피던스 코드 발생기 (320)는 외부 기준 저항기 (REXT)의 임피던스와 관계없이 고정된 임피던스 제어 코드들 (UPCF, DNCF)을 발생한다. 이는 이후 상세히 설명될 것이다. 프로그램 레지스터 (programmable register) (330)는 외부로부터의 명령에 따라 프로그램 가능하도록 구성되며, 프로그램 값에 따라 코드 선택 신호 (SEL) 및 오프셋 선택 신호들 (OFFSET1, OFFSET2)을 발생한다. 예를 들면, 프로그램 레지스터 (330)는 이 분야에 잘 알려진 모드 레지스터 세트 (mode register set: MRS)으로 구현될 수 있다. 또는, 프로그램 레지스터 (330)가 다른 로직 회로를 이용하여 구현될 수 있음을 이 분야의 통상적인 지식을 습득한 자들에게 자명하다. 선택 회로 (340)는 코드 선택 신호 (SEL)에 응답하여 가변 임피던스 코드 발생 회로 (310)의 가변 임피던스 제어 코드들 (UPCV, DNCV) 또는 고정 임피던스 코드 발생 회로 (320)의 고정 임피던스 제어 코드들 (UPCF, DNCF)을 임피던스 제어 코드들 (UPC, DNC)로서 선택한다. 선택된 제어 코드들 (UPC, DNC)은 구동 제어 회로 (260) 및 종결 회로들 (290, 300)에 전달된다.

이상의 설명으로부터 알 수 있듯이, 종결 회로들 (290, 300)의 임피던스는 선택된 제어 코드들 (UPC, DNC)에 의해서 가변됨과 동시에 오프-칩 구동 회로 (270)의 임피던스 역시 선택된 제어 코드들 (UPC, DNC)에 따라 제어된다. 결과적으로, 하나의 외부 기준 저항기 (REXT) 및 하나의 임피던스 코드 발생기 (310)를 이용하여 종결 회로들 (290, 300)의 임피던스 및 오프-칩 구동 회로 (270)의 임피던스를 동시에 조정하는 것이 가능하다.

도 3은 도 2에 도시된 가변 임피던스 코드 발생 회로의 바람직한 실시예이다. 도 3을 참조하면, 본 발명에 따른 가변 임피던스 코드 발생 회로 (310)는 제 1 및 제 2 비교기들 (first and second comparators) (311, 312), 제 1 및 제 2 카운터들 (first and second counters) (313, 314), 그리고 가변 임피던스 회로들 (variable impedance circuits) (315, 316, 317)을 포함한다.

제 1 비교기 (311)는 패드 (PAD7)의 전압이 소정의 기준 전압 (VREF) (예를 들면, VDDQ/2)보다 높은 지의 여부를 검출한다. 제 1 카운터 (313)는 제 1 비교기 (311)의 출력에 응답하여 가변 임피던스 제어 코드 (UPCV)을 발생한다. 제 1 및 제 2 가변 임피던스 회로들 (315, 316) 각각의 임피던스는 제 1 카운터 (313)로부터 출력되는 가변 임피던스 제어 코드 (UPCV)에 의해서 가변된다. 이러한 동작은 패드 (PAD7)의 전압이 기준 전압 (VREF)이 될 때까지 반복적으로 수행될 것이다. 이와 동시에, 제 2 비교기 (312)는 내부 노드 (ND10)의 전압이 패드 (PAD7)의 전압보다 높은 지의 여부를 검출한다. 제 2 카운터 (314)는 제 2 비교기 (312)의 출력에 응답하여 가변 임피던스 제어 코드 (DNCV)를 발생한다. 제 3 가변 임피던스 회로 (317)의 임피던스는 제 2 카운터 (314)로부터 출력되는 임피던스 제어 코드 (DNCV)에 의해서 가변된다. 이러한 동작은 내부 노드 (ND10)의 전압이 패드 (PAD7)의 전압이 될 때까지 반복적으로 수행될 것이다.

예를 들면, 외부 기준 저항기 (REXT)가  $240\Omega$ 이라고 가정하면, 가변 임피던스 회로들 (315, 316, 317) 각각은 비교기들 (311, 312)과 카운터들 (313, 314)을 통해  $240\Omega$ 의 임피던스를 갖도록 제어될 것이다.

이 실시예에 있어서, 제 1 및 제 2 카운터들 (313, 314)은 7-비트 업/다운 카운터 (7-bit up/down counter)이다. 이 경우, 가변 임피던스 제어 코드들 (UPCV, DNCV) 각각은 7-비트 코드이다. 하지만, 본 발명에 따른 제어 코드들 (UPCV, DNCV)이 이에 제한되지 않음은 이 분야의 통상적인 지식을 습득한 자들에게 자명하다.

도 4a 및 도 4b는 도 3에 도시된 가변 임피던스 회로들의 실시예들을 보여주는 회로도들이다. 먼저, 가변 임피던스 회로 (315)를 보여주는 도 4a를 참조하면, 가변 임피던스 회로 (315)는 가변 임피던스 제어 코드 신호들 (UPCV<6>-UPCV<0>)에 각각 대응하는 쌍들의 PMOS 트랜지스터 및 저항기를 포함한다. 각 쌍의 PMOS 트랜지스터 및 저항기는 전원 전압과 패드 (PAD7) 사이에 직렬로 연결되어 있다. 가변 임피던스 회로 (315)의 PMOS 트랜지스터들 (1WP-64WP)은 이진 가중치 트랜지스터들 (binary-weighted transistors)이고, 가변 임피던스 회로 (315)의 저항기들 (1R-64R)은 이진 가중치 저항기들 (binary-weighted resistors)이다. 가변 임피던스 제어 코드 신호들 (UPCV<6>-UPCV<0>)의 선택적인 활성화에 따라 이진 가중치 트랜지스터들이 선택적으로 활성화되며, 그 결과 가변 임피던스 회로 (315)는 외부 기준 저항기 (REXT)와 동일한 임피던스를 갖는다. 비록 도면에는 도시되지 않았지만, 가변 임피던스 회로 (316) 역시 도 4a에 도시된 것과 실질적으로 동일하게 구성되며, 그것에 대한 설명은 그러므로 생략된다.

가변 임피던스 회로 (317)를 보여주는 도 4b를 참조하면, 가변 임피던스 회로 (317)는 가변 임피던스 제어 코드 신호들 (DNCV<6>-DNCV<0>)에 각각 대응하는 쌍들의 NMOS 트랜지스터 및 저항기를 포함한다. 각 쌍의 NMOS 트랜지스터 및 저항기는 내부 노드 (ND10)와 접지 전압 사이에 직렬로 연결되어 있다. 가변 임피던스 회로 (317)의 NMOS 트랜지스터들 (1WN-64WN)은 이진 가중치 트랜지스터들 (binary-weighted transistors)이고, 가변 임피던스 회로 (317)의 저항기들 (1R-64R)은 이진 가중치 저항기들 (binary-weighted resistors)이다. 가변 임피던스 제어 코드 신호들 (DNCV<6>-DNCV<0>)의 선택적인 활성화에 따라 이진 가중치 트랜지스터들이 선택적으로 활성화되며, 그 결과 가변 임피던스 회로 (317)는 외부 기준 저항기 (REXT)와 동일한 임피던스를 갖는다.

도 5는 본 발명의 바람직한 실시예에 따라 도 2에 도시된 고정 임피던스 코드 발생 회로 (320)를 보여주는 회로도이다.

도 5를 참조하면, 본 발명에 따른 고정 임피던스 코드 발생 회로 (320)는 정해진 값에 따라 고정 임피던스 제어 코드 신호들 (UPCF<0>-UPCF<6>)이 전원 전압 (VCC)과 접지 전압 (VSS)에 선택적으로 연결되도록 구성된다. 비록 도면에는 도시되지 않았지만, 고정 임피던스 코드 발생 회로 (320)는 고정 임피던스 제어 코드 (UPCF)가 외부 데이터에 의해서 프로그램되도록 구성될 수 있다. 고정 임피던스 코드 발생 회로 (320)는 도 4에 도시된 것과 동일한 방식으로 또는 앞서 언급된 프로그램 방식으로 고정 임피던스 제어 코드 (DNCF)를 발생할 것이다. 또는 임피던스 제어 코드 (UPCF)는 동일한 코드 값을 갖도록 임피던스 제어 코드 (DNCF)로서 사용될 수 있다.

도 6은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 선택 회로 (340)를 보여주는 블록도이다.

도 6을 참조하면, 본 발명의 선택 회로 (340)는 복수 개의, 예를 들면, 14개의 2:1 멀티플렉서들 (MUX1-MUX14)로 구성된다. 멀티플렉서 (MUX1)는 인버터 (INV10)와 전달 게이트 (TG10)로 구성되며, 도면에 도시된 바와 같이 연결되어 있다. 나머지 멀티플렉서들 (MUX2-MUX14)은 멀티플렉서 (MUX1)와 동일하게 구성된다. 멀티플렉서 (MUX1)은 가변 임피던스 코드 발생 회로 (310)로부터 출력되는 대응하는 가변 임피던스 제어 코드 신호 (UPCV<6>)와 고정 임피던스 코드 발생 회로 (320)로부터 출력되는 대응하는 고정 임피던스 제어 코드 신호 (UPCF<6>)을 입력받고, 코드 선택 신호 (SEL)에 응답하여 입력 신호들 중 하나를 선택한다. 나머지 멀티플렉서들 (MUX2-MUX7) 역시 멀티플렉서 (MUX1)와 동일한 방식으로 동작한다. 멀티플렉서 (MUX8)은 가변 임피던스 코드 발생 회로 (310)로부터 출력되는 대응하는 가변 임피던스 제어 코드 신호 (DNCV<6>)와 고정 임피던스 코드 발생 회로 (320)로부터 출력되는 대응하는 고정 임피던스 제어 코드 신호 (DNCF<6>)을 입력받고, 코드 선택 신호 (SEL)에 응답하여 입력 신호들 중 하나를 선택한다. 나머지 멀티플렉서들 (MUX9-MUX14) 역시 멀티플렉서 (MUX8)과 동일한 방식으로 동작한다.

코드 선택 신호 (SEL)가 로우 레벨일 때, 선택 회로 (340)는 가변 임피던스 코드 발생 회로 (310)로부터 출력되는 가변 임피던스 제어 코드들 (UPCV, DNCV)을 선택한다. 코드 선택 신호 (SEL)가 하이 레벨일 때, 선택 회로 (340)는 고정 임피던스 코드 발생 회로 (320)로부터 출력되는 고정 임피던스 제어 코드들 (UPCF, DNCF)을 선택한다.

도 7은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 구동 제어 회로 (260)를 보여주는 회로도이다.

도 7을 참조하면, 본 발명의 구동 제어 회로 (260)는 도 2의 선택 회로 (340)로부터 출력되는 임피던스 제어 코드들 (UPC, DNC) 및 도 2의 감지 증폭 회로 (250)로부터 출력되는 데이터 (DATA\_OUT)을 입력받고, 풀업 및 풀다운 제어 신호들 (PU<6>-PU<0>, PD<6>-PD<0>)을 발생한다. 구동 제어 회로 (260)는, 예를 들면, 7개의 NAND 게이트들 (G10-G16), 7개의 NOR 게이트들 (G17-G23), 7개의 인버터들 (INV11-INV17)을 포함하며, 도면에 도시된 바와 같이 연결되어 있다.

데이터 (DATA\_OUT)가 '1'일 때, NAND 게이트들 (G10-G16)의 출력 신호들 (PU<6>-PU<0>)의 로직 상태들은 가변 임피던스 제어 코드 신호들 (UPC<6>-UPC<0>)의 값들에 따라 결정된다. 예를 들면, 가변 임피던스 제어 코드 (UPC)가 "1010101"일 때, 풀업 제어 신호들 (PU<6>, PU<4>, PU<2>, PU<0>)은 각각 로우 레벨이 되고 풀업 제어 신호들 (PU<5>, PU<3>, PU<1>)은 각각 하이 레벨이 된다. 데이터 (DATA\_OUT)가 '1'일 때, NOR 게이트들 (G17-G23)의 출력 신호들 (PD<6>-PD<0>)은 가변 임피던스 제어 코드 (DNC)에 관계없이 모두 로우 레벨이 된다.

데이터 (DATA\_OUT)가 '0'일 때, NOR 게이트들 (G17-G23)의 출력 신호들 (PD<6>-PD<0>)의 로직 상태들은 가변 임피던스 제어 코드 신호들 (DNC<6>-DNC<0>)의 값들에 따라 결정된다. 예를 들면, 가변 임피던스 제어 코드 (DNC)가 "1010101"일 때, 풀다운 제어 신호들 (PD<6>, PD<4>, PD<2>, PD<0>)은 각각 하이 레벨이 되고 풀다운 제어 신호들 (PD<5>, PU<3>, PU<1>)은 각각 로우 레벨이 된다. 데이터 (DATA\_OUT)가 '0'일 때, NAND 게이트들 (G10-G16)의 출력 신호들 (PU<6>-PU<0>)은 가변 임피던스 제어 코드 (UPC)에 관계없이 모두 하이 레벨이 된다.

이상의 설명으로부터 알 수 있듯이, 풀업 제어 신호들 (PU<6>-PU<0>)은 데이터 (DATA\_OUT)가 '1'일 때 가변 임피던스 제어 코드 (UPC)에 따라 선택적으로 활성화되며, 풀다운 제어 신호들 (PD<6>-PD<0>)은 데이터 (DATA\_OUT)가 '0'일 때 가변 임피던스 제어 코드 (DNC)에 따라 선택적으로 활성화된다. 풀업 제어 신호들 (PU<6>-PU<0>)은 풀다운 제어 신호들 (PD<6>-PD<0>)과 배타적으로 활성화된다.

도 8은 본 발명의 바람직한 실시예에 따른 도 2에 도시된 오프-칩 구동 회로 (270) 및 종결 회로 (290)를 보여주는 블록도이다. 도 8에는 단지 하나의 패드 (PAD4)에 관련된 구성 요소들이 도시되어 있지만, 나머지 패드들 (PAD5-PAD6) 각각과 관련된 구성 요소들이 도 8에 도시된 것과 실질적으로 동일하게 구성될 것이다.

도 8을 참조하면, 오프-칩 구동 회로 (270)는 패드 (PAD4)에 병렬 연결된 복수 개의, 예를 들면, 6개의 오프-칩 구동 블록들 (OCD1-OCD6)을 포함한다. 오프-칩 구동 블록들 (OCD1-OCD6) 각각은 구동 제어 회로 (260)에서 출력되는 풀업 및 풀다운 제어 신호들 (PUI<sub>i</sub>, PDI<sub>i</sub>) ( $i=0-6$ )에 응답하여 패드 (PAD4) (또는 출력 신호 전송 라인 (TL\_OUT1))을 구동한다. 오프-칩 구동 블록들 (OCD1-OCD6) 각각은 도 9에 도시된 바와 같이 연결된 이진 가중치 트랜지스터들 및 이진 가중치 저항기들로 구성된다. 가변 임피던스 코드 발생 회로 (310)에서, 앞서 설명된 바와 같이, 기준 전압 (VREF)과 패드 (PAD7)의 전압이 일치할 때 가변 임피던스 회로 (315)는 외부 기준 저항기 (REXT)와 동일한 임피던스를 갖는다. 풀업 제어 신호들 (PU<6>-PU<0>) 또는 풀다운 제어 신호들 (PD<6>-PD<0>)이 가변 임피던스 제어 코드들에 따라 선택적으로 활성화되기 때문에, 오프-칩 구동 블록들 (OCD1-OCD6) 각각은 외부 기준 저항기 (REXT)와 동일한 임피던스를 갖는다. 예를 들면, 240Ω의 외부 기준 저항기 (REXT)가 사용될 때, 오프-칩 구동 블록들 (OCD1-OCD6) 각각은 임피던스 제어 코드들에 따라 240Ω의 임피던스를 갖는다. 6개의 오프-칩 구동 블록들 (OCD1-OCD6)이 각 패드에 병렬 연결되어 있기 때문에, 각 패드 (또는 각 출력 신호 전송 라인)은 40Ω의 임피던스를 갖는 오프-칩 구동 회로 (270)에 의해서 구동될 것이다.

다시 도 8을 참조하면, 종결 회로 (290)는 패드 (PAD4) 또는 입력 신호 전송 라인 (TL\_IN10)에 병렬 연결된 4개의 종단 블록들 (ODT1-ODT4)을 포함한다. 종단 블록들 (ODT1-ODT4) 각각은 임피던스 제어 신호 (UPC)에 응답하여 입력 신호 전송 라인 (TL\_IN10)을 종결시킨다. 종단 블록들 (ODT1-ODT4) 각각은 도 10에 도시된 바와 같이 연결된 이진 가중치 트랜지스터들 및 이진 가중치 저항기들로 구성된다. 가변 임피던스 코드 발생 회로 (310)에서, 앞서 설명된 바와 같이, 기준 전압 (VREF)과 패드 (PAD7)의 전압이 일치할 때 가변 임피던스 회로 (315)는 외부 기준 저항기 (REXT)와 동일한 임피던스를 갖는다. 임피던스 제어 코드 신호들 (UPC<6>-UPC<0>)은 가변 임피던스 제어 코드 신호들과 동일하기 때문에, 종단 블록들 (ODT1-ODT4) 각각은 외부 기준 저항기 (REXT)와 동일한 임피던스를 갖는다. 예를 들면, 240Ω의 외부 기준 저항기 (REXT)가 사용될 때, 종단 블록들 (ODT1-ODT4) 각각은 임피던스 제어 코드 (UPC)에 따라 240Ω의 임피던스를 갖는다. 4개의 종단 블록들 (ODT1-ODT4)이 각 패드에 병렬 연결되어 있기 때문에, 각 패드 (또는 각 입력 신호 전송 라인)은 60Ω의 임피던스를 갖는 종결 회로 (290)에 의해서 구동될 것이다.

도 8에 도시된 종결 회로 (290)는 도 2의 선택 회로 (340)로부터 출력되는 임피던스 제어 코드 (UPC)에 의해서 제어되도록 구성되어 있다. 하지만, 종결 회로 (290)는, 도 11에 도시된 바와 같이, 선택 회로 (340)로부터 출력되는 임피던스 제어 코드들 (UPC, DNC)에 의해서 제어되도록 구성될 수 있다. 본 발명에 따른 종결 회로 (290)가 이에 국한되지 않음은 이 분

야의 통상적인 지식을 습득한 자들에게 자명하다. 입력 신호 전송 라인들 (TL\_IN11-TL\_IN31)을 종결시키기 위한 도 2의 종결 회로 (300)는, 비록 도면에는 도시되지 않았지만, 도 8, 도 10 및 도 11에 도시된 것과 동일하게 구성됨은 이 분야의 통상적인 지식을 습득한 자들에게 자명하다. 따라서, 도 2의 종결 회로 (300)에 대한 설명은 여기서 생략될 것이다.

본 발명에 따른 반도체 메모리 장치의 종결 회로 및 오프-칩 구동 회로의 임피던스를 제어하는 동작이 참조 도면들에 의거하여 이하 상세히 설명될 것이다.

고정 임피던스 제어 코드들 (UPCF, DNCF) 또는 가변 임피던스 제어 코드들 (UPCV, DNCV)을 선택하기 위해서 프로그램 레지스터 (330)가 프로그램될 것이다. 이 실시예에 있어서, 프로그램 레지스터 (330)는 가변 임피던스 제어 코드들이 선택되도록 프로그램될 것이다. 이러한 가정에 따르면, 프로그램 레지스터 (330)는 로우 레벨의 코드 선택 신호 (SEL)를 발생한다. 이는 선택 회로 (340)가 가변 임피던스 코드 발생 회로 (310)의 출력 (UPCV, DNCV)이 선택되게 한다. 가변 임피던스 코드 발생 회로 (310)는 패드 (PAD7)에 연결된 외부 기준 저항기 (REXT)의 임피던스에 따라 가변되는 가변 임피던스 제어 코드들 (UPCV, DNCV)을 발생한다. 그렇게 발생된 가변 임피던스 제어 코드들은 선택 회로 (340)를 통해 종결 회로들 (300, 290) 및 구동 제어 회로 (260)로 전달된다. 종결 회로들 (340)에는 임피던스 제어 코드 (UPC)만이 인가될 수도 있고 임피던스 제어 코드들 (UPC, DNC)이 모두 인가될 수도 있다.

종결 회로 (300)는 임피던스 제어 코드 (UPC)에 응답하여 입력 신호 전송 라인들 (TL\_IN11-TL\_IN31)을 종결시킨다. 종결 회로 (290)는 쓰기 동작시 임피던스 제어 코드 (UPC)에 응답하여 입력 신호 전송 라인들 (TL\_IN10-TL\_IN30)을 종결시킨다. 이때, 종결 회로들 (290, 300)은 동일한 임피던스를 가지며, 예를 들면, 240Ω의 외부 기준 저항기 (REXT)가 패드 (PAD7)에 연결될 때 종결 회로들 (290, 300) 각각은 60Ω의 임피던스를 갖는다. 왜냐하면, 앞서 설명된 바와 같이, 종결 회로들 (290, 300) 각각의 4개의 종단 블록들 (ODT1-ODT4)이 대응하는 패드 (또는 입력 신호 전송 라인)에 병렬 연결되고 종단 블록들 (ODT1-ODT4) 각각이 외부 기준 저항기 (REXT)와 동일한 임피던스 (예를 들면, 240Ω)를 갖도록 동일한 임피던스 제어 코드에 제어되기 때문이다.

이와 동시에, 선택 회로 (340)에 의해서 선택된 임피던스 제어 코드들 (UPC, DNC)은 구동 제어 회로 (260)에 전달된다. 구동 제어 회로 (260)는, 읽기 동작시, 감지 증폭 회로 (250)로부터의 데이터 (DATA\_OUT)에 따라 풀업 또는 풀다운 제어 신호들 (PUi 또는 PDi) ( $i=0-6$ )을 발생하며, 풀업 또는 풀다운 제어 신호들은 임피던스 제어 코드들 (UPC, DNC)과 동일한 코드값을 갖는다. 240Ω의 외부 기준 저항기 (REXT)가 패드 (PAD7)에 연결될 때 오프-칩 구동 회로 (270)는 40Ω의 임피던스를 갖는다. 왜냐하면, 앞서 설명된 바와 같이, 오프-칩 구동 회로를 구성하는 6개의 오프-칩 구동 블록들 (OCD1-OCD6)이 대응하는 패드 (또는 출력 신호 전송 라인)에 병렬 연결되고 오프-칩 구동 블록들 (OCD1-OCD6) 각각이 외부 기준 저항기 (REXT)와 동일한 임피던스 (예를 들면, 240Ω)를 갖도록 동일한 풀업 또는 풀다운 제어 신호들에 의해서 제어되기 때문이다.

읽기 동작시 종결 회로 (300) 및 오프-칩 구동 회로 (270)는 요구되는 임피던스를 갖도록 선택된 임피던스 제어 코드들 (UPC, DNC)에 의해서 동시에 제어된다. 마찬가지로, 쓰기 동작시 종결 회로들 (290, 300)은 요구되는 임피던스를 갖도록 선택된 임피던스 제어 코드들 (UPC, DNC)에 의해서 제어된다. 다시 말해서, 종결 회로들 (290, 300)의 임피던스는 선택된 임피던스 제어 코드들 (UPC, DNC)에 의해서 가변됨과 동시에 오프-칩 구동 회로 (270)의 임피던스 역시 선택된 제어 코드들 (UPC, DNC)에 따라 제어된다. 결과적으로, 하나의 외부 기준 저항기 (REXT) 및 하나의 임피던스 코드 발생기 (310 또는 320)를 이용하여 종결 회로들 (290, 300)의 임피던스 및 오프-칩 구동 회로 (270)의 임피던스를 동시에 조정하는 것이 가능하다.

도 12는 도 2에 도시된 오프-칩 구동 회로 (270) 및 종결 회로 (290)의 다른 실시예를 보여주는 블록도이다.

도 8에 도시된 것과 달리, 도 12에 도시된 오프-칩 구동 회로 (270')는 단지 하나의 오프-칩 구동 블록 (OCD1)을 이용하여 구현되며, 오프-칩 구동 회로 (270')의 임피던스는 오프셋 선택 신호들 (OFFSET0, OFFSET1)에 따라 미세하게 조정될 수 있다. 좀 더 구체적으로 설명하면, 도 13을 참조하면, 오프-칩 구동 회로 (270')는 풀업부 (PULL\_UP)와 풀다운부 (PULL\_DOWN)로 구성된다. 풀업부 (PULL\_UP)는 도면에 도시된 바와 같이 연결된 이진 가중치 트랜지스터들 (64WP/N-1WP/N) 및 이진 가중치 저항기들 (1R/N-64R/N)을 포함한다. 40Ω의 임피던스를 갖는 오프-칩 구동 회로 (270')를 구현하기 위해서, 이진 가중치 트랜지스터들 (64WP/N-1WP/N)은 도 8에 도시된 이진 가중치 트랜지스터들을 1/N으로 선형적으로 축소하여 형성된 것이며, 이진 가중치 저항기들 (1R/N-64R/N)은 도 8에 도시된 이진 가중치 저항기들을 1/N으로 선형적으로 축소하여 형성된 것이다. 이진 가중치 트랜지스터들 (64WP/N-1WP/N)은 대응하는 풀업 제어 신호들 (PU<6>-PU<0>)에 의해서 각각 제어되며, 그 결과 40Ω의 임피던스를 갖는 오프-칩 구동 회로 (270')를 통해 패드 (PAD4)가 구동될 것이다.

풀업부 (PULL\_UP)는 도면에 도시된 바와 같이 연결된 오프셋 저항기들 (OFR1-OFR7) 및 오프셋 트랜지스터들 (OFT1-OFT7)을 더 포함하며, 오프셋 트랜지스터들 (OFT1-OFT7)은 오프셋 선택 신호 (OFFSET1)에 의해서 공통으로 제어된다. 오프셋 선택 신호 (OFFSET1)가 활성화되는 지의 여부에 따라 풀업부 (PULL\_UP)의 임피던스가 조정될 수 있다. 오프셋 트랜지스터들 (OFT1-OFT7)은 동일한 값을 갖도록 또는 이진 가중치를 갖도록 구현될 수 있다. 마찬가지로, 오프셋 저항기들 (OFR1-OFR7)은 동일한 값을 갖도록 또는 이진 가중치를 갖도록 구현될 수 있다.

마찬가지로, 풀다운부 (PULL\_DOWN)는 도면에 도시된 바와 같이 연결된 이진 가중치 트랜지스터들 (64WN/N-1WN/N) 및 이진 가중치 저항기들 (1R/N-64R/N)을 포함한다.  $60\Omega$ 의 임피던스를 갖는 오프-칩 구동 회로 (270')를 구현하기 위해서, 이진 가중치 트랜지스터들 (64WN/N-1WN/N)은 도 8에 도시된 이진 가중치 트랜지스터들을 1/N으로 선형적으로 축소하여 형성된 것이며, 이진 가중치 저항기들 (1R/N-64R/N)은 도 8에 도시된 이진 가중치 저항기들을 1/N으로 선형적으로 축소하여 형성된 것이다. 이진 가중치 트랜지스터들 (64WN/N-1WN/N)은 대응하는 풀다운 제어 신호들 (PD<6>-PD<0>)에 의해서 각각 제어되며,  $60\Omega$ 의 임피던스를 갖는 오프-칩 구동 회로 (270')를 통해 패드 (PAD4)가 구동될 것이다.

풀다운부 (PULL\_DOWN)는 도면에 도시된 바와 같이 연결된 오프셋 저항기들 (OFR8-OFR14) 및 오프셋 트랜지스터들 (OFT8-OFT14)을 더 포함하며, 오프셋 트랜지스터들 (OFT8-OFT14)은 오프셋 선택 신호 (OFFSET2)에 의해서 공통으로 제어된다. 오프셋 선택 신호 (OFFSET2)가 활성화되는 지의 여부에 따라 풀다운부 (PULL\_DOWN)의 임피던스가 조정될 수 있다. 오프셋 트랜지스터들 (OFT8-OFT14)은 동일한 값을 갖도록 또는 이진 가중치를 갖도록 구현될 수 있다. 마찬가지로, 오프셋 저항기들 (OFR8-OFR14)은 동일한 값을 갖도록 또는 이진 가중치를 갖도록 구현될 수 있다.

다시 도 12를 참조하면, 도 8에 도시된 것과 달리, 도 12에 도시된 종결 회로 (290')는 단지 하나의 종단 블록 (ODT1)을 이용하여 구현되며, 종결 회로 (290')의 임피던스는 오프셋 선택 신호들 (OFFSET1, OFFSET2)에 따라 미세하게 조정될 수 있다. 좀 더 구체적으로 설명하면, 도 14를 참조하면, 종결 회로 (290')는 도면에 도시된 바와 같이 연결된 이진 가중치 트랜지스터들 (64WP/N-1WP/N) 및 이진 가중치 저항기들 (1R/N-64R/N)을 포함한다.  $40\Omega$ 의 임피던스를 갖는 종결 회로 (290')를 구현하기 위해서, 이진 가중치 트랜지스터들 (64WP/N-1WP/N)은 도 8에 도시된 이진 가중치 트랜지스터들을 1/N으로 선형적으로 축소하여 형성된 것이며, 이진 가중치 저항기들 (1R/N-64R/N)은 도 8에 도시된 이진 가중치 저항기들을 1/N으로 선형적으로 축소하여 형성된 것이다. 이진 가중치 트랜지스터들 (64WP/N-1WP/N)은 대응하는 풀업 제어 신호들 (PU<6>-PU<0>)에 의해서 각각 제어되며, 그 결과  $60\Omega$ 의 임피던스를 갖는 종결 회로 (290')를 통해 입력 신호 전송 라인 (TL\_IN10)이 종결된다.

종결 회로 (290')는 도면에 도시된 바와 같이 연결된 오프셋 저항기들 (OFR15-OFR21) 및 오프셋 트랜지스터들 (OFT15-OFT21)을 더 포함하며, 오프셋 트랜지스터들 (OFT15-OFT21)은 오프셋 선택 신호 (OFFSET1)에 의해서 공통으로 제어된다. 오프셋 선택 신호 (OFFSET1)가 활성화되는 지의 여부에 따라 종결 회로 (290')의 임피던스가 조정될 수 있다. 오프셋 트랜지스터들 (OFT15-OFT21)은 동일한 값을 갖도록 또는 이진 가중치를 갖도록 구현될 수 있다. 마찬가지로, 오프셋 저항기들 (OFR15-OFR21)은 동일한 값을 갖도록 또는 이진 가중치를 갖도록 구현될 수 있다.

비록 도면에는 도시되지 않았지만, 도 2에 도시된 종결 회로 (300) 역시 도 14에 도시된 것과 동일하게 구현될 수 있다.

이상에서, 본 발명에 따른 회로의 구성 및 동작을 상기한 설명 및 도면에 따라 도시하였지만, 이는 예를 들어 설명한 것에 불과하며 본 발명의 기술적 사상 및 범위를 벗어나지 않는 범위 내에서 다양한 변화 및 변경이 가능함은 물론이다.

### 발명의 효과

상술한 바와 같이, 하나의 외부 기준 저항기 및 하나의 임피던스 코드 발생기를 이용하여 종결 회로들의 임피던스 및 오프-칩 구동 회로의 임피던스를 동시에 조정하는 것이 가능하다.

### (57) 청구의 범위

#### 청구항 1.

외부 기준 저항기에 연결되며, 상기 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생하는 임피던스 제어 회로와;

입력 신호 전송 라인을 통해 외부 신호를 입력받고, 상기 입력된 신호를 내부 회로로 출력하는 입력 회로와;

상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 신호 전송 라인을 종결시키는 종결 회로와; 그리고

상기 내부 회로로부터 출력되는 신호에 따라 출력 신호 전송 라인을 구동하며, 임피던스가 상기 임피던스 제어 코드들에 따라 가변되는 출력 회로를 포함하는 반도체 집적 회로 장치.

## 청구항 2.

제 1 항에 있어서,

상기 종결 회로는 상기 입력 신호 전송 라인에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들 중 어느 하나에 의해서 제어되는 반도체 집적 회로 장치.

## 청구항 3.

제 1 항에 있어서,

상기 종결 회로는 상기 입력 신호 전송 라인에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들에 의해서 제어되는 반도체 집적 회로 장치.

## 청구항 4.

제 1 항에 있어서,

상기 출력 회로는 상기 출력 신호 전송 라인에 병렬 연결된 복수 개의 구동기들을 포함하며, 상기 구동기들 각각의 임피던스는 상기 임피던스 제어 코드들에 따라 조정되는 반도체 집적 회로 장치.

## 청구항 5.

제 1 항에 있어서,

상기 임피던스 제어 회로는

상기 외부 기준 저항기와 연결되는 패드와;

상기 패드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 임피던스 제어 코드들 중 제 1 임피던스 제어 코드에 의해서 제어되는 제 1 가변 임피던스 회로와;

상기 패드의 전압을 기준 전압과 비교하는 제 1 비교기와;

상기 제 1 비교기의 출력에 응답하여 상기 제 1 임피던스 제어 코드를 발생하는 제 1 업/다운 카운터와;

내부 노드에 연결되며, 상기 외부가변 저항기와 동일한 임피던스를 갖도록 상기 제 1 임피던스 제어 코드에 의해서 제어되는 제 2 가변 임피던스 회로와;

상기 내부 노드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 임피던스 제어 코드들 중 제 2 임피던스 제어 코드에 의해서 제어되는 제 3 가변 임피던스 회로와;

상기 내부 노드의 전압과 상기 패드의 전압을 비교하는 제 2 비교기와; 그리고

상기 제 2 비교기의 출력에 응답하여 상기 제 2 임피던스 제어 코드를 발생하는 제 2 업/다운 카운터를 포함하는 반도체 집적 회로 장치.

## 청구항 6.

제 5 항에 있어서,

상기 제 1 내지 제 3 가변 임피던스 회로들 각각은 이진 가중치 저항기들과 이진 가중치 트랜지스터들을 포함하는 반도체 집적 회로 장치.

## 청구항 7.

제 6 항에 있어서,

상기 종결 회로는 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 종결 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 제 1 내지 제 3 가변 임피던스 회로들 각각의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 집적 회로 장치.

## 청구항 8.

제 1 항에 있어서,

상기 임피던스 제어 회로는 선택 신호에 응답하여 상기 외부 기준 저항기의 임피던스에 관계없이 일정하게 유지되는 상기 임피던스 제어 코드들을 발생하는 반도체 집적 회로 장치.

## 청구항 9.

제 6 항에 있어서,

상기 출력 회로는 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 출력 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 제 1 내지 제 3 가변 임피던스 회로들 각각의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 집적 회로 장치.

## 청구항 10.

행들과 열들로 배열된 메모리 셀들의 어레이와;

메모리 셀들로부터/에 데이터를 읽고/쓰는 감지 증폭 회로와;

고정 임피던스 제어 코드들을 발생하는 제 1 코드 발생 회로와;

외부 기준 저항기에 연결되며, 상기 외부 기준 저항기의 임피던스에 따라 가변되는 가변 임피던스 제어 코드들을 발생하는 제 2 코드 발생 회로와;

코드 선택 신호에 응답하여 상기 고정 임피던스 제어 코드들 또는 상기 가변 임피던스 제어 코드들을 선택하는 선택 회로와;

상기 감지 증폭 회로로부터 출력되는 데이터 및 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들에 응답하여 풀업 및 풀다운 제어 신호들을 발생하는 구동 제어 회로와;

읽기 동작 동안 상기 풀업 및 풀다운 제어 신호들에 응답하여 데이터 전송 라인들을 구동하며, 임피던스가 상기 풀업 및 풀다운 제어 신호들에 의해서 가변되는 오프-칩 구동 회로와;

쓰기 동작 동안 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 데이터 전송 라인들을 종결시키는 제 1 종결 회로를 포함하는 반도체 메모리 장치.

### **청구항 11.**

제 10 항에 있어서,

상기 쓰기 동작 동안 상기 데이터 전송 라인들 상의 데이터를 상기 감지 증폭 회로로 전달하는 데이터 입력 회로를 더 포함하는 반도체 메모리 장치.

### **청구항 12.**

제 10 항에 있어서,

상기 제 1 종결 회로는 상기 데이터 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 어느 하나에 의해서 제어되는 반도체 메모리 장치.

### **청구항 13.**

제 10 항에 있어서,

상기 제 1 종결 회로는 상기 데이터 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들에 의해서 제어되는 반도체 메모리 장치.

### **청구항 14.**

제 10 항에 있어서,

상기 오프-칩 구동 회로는 상기 데이터 전송 라인들 각각에 병렬 연결된 복수 개의 구동기들을 포함하며, 상기 구동기들 각각의 임피던스는 상기 풀업 및 풀다운 제어 신호들에 의해서 조정되는 반도체 메모리 장치.

### **청구항 15.**

제 10 항에 있어서,

입력 전송 라인들을 통해 입력되는 어드레스 및 제어 신호들을 입력받는 입력 버퍼 회로와;

상기 입력 버퍼 회로로부터 출력되는 행 어드레스에 응답하여 상기 행들을 선택하는 행 디코더 회로와;

상기 입력 버퍼 회로로부터 출력되는 열 어드레스에 응답하여 상기 열들을 선택하는 열 디코더 회로와; 그리고

상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 전송 라인들을 종결시키는 제 2 종결 회로를 더 포함하는 반도체 메모리 장치.

### 청구항 16.

제 15 항에 있어서,

상기 제 2 종결 회로는 상기 입력 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 어느 하나에 의해서 제어되는 반도체 메모리 장치.

### 청구항 17.

제 15 항에 있어서,

상기 제 2 종결 회로는 상기 입력 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들에 의해서 제어되는 반도체 메모리 장치.

### 청구항 18.

제 15 항에 있어서,

상기 제 2 코드 발생 회로는

상기 외부 기준 저항기와 연결되는 패드와;

상기 패드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 가변 임피던스 제어 코드들 중 제 1 가변 임피던스 제어 코드에 의해서 제어되는 제 1 가변 임피던스 회로와;

상기 패드의 전압을 기준 전압과 비교하는 제 1 비교기와;

상기 제 1 비교기의 출력에 응답하여 상기 제 1 가변 임피던스 제어 코드를 발생하는 제 1 업/다운 카운터와;

내부 노드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 제 1 가변 임피던스 제어 코드에 의해서 제어되는 제 2 가변 임피던스 회로와;

상기 내부 노드에 연결되며, 상기 외부 기준 저항기와 동일한 임피던스를 갖도록 상기 가변 임피던스 제어 코드들 중 제 2 가변 임피던스 제어 코드에 의해서 제어되는 제 3 가변 임피던스 회로와;

상기 내부 노드의 전압과 상기 패드의 전압을 비교하는 제 2 비교기와; 그리고

상기 제 2 비교기의 출력에 응답하여 상기 제 2 가변 임피던스 제어 코드를 발생하는 제 2 업/다운 카운터를 포함하는 반도체 메모리 장치.

### 청구항 19.

제 18 항에 있어서,

상기 제 1 내지 제 3 가변 임피던스 회로들 각각은 이진 가중치 트랜지스터들 및 이진 가중치 저항기들로 구성되는 반도체 메모리 장치.

### 청구항 20.

제 19 항에 있어서,

상기 제 1 종결 회로는 이진 가중치 트랜지스터들 및 이진 가중치 저항기들로 구성되며, 상기 제 1 종결 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 제 1 내지 제 3 가변 임피던스 회로들 각각의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 메모리 장치.

### 청구항 21.

제 19 항에 있어서,

상기 제 2 종결 회로는 이진 가중치 트랜지스터들 및 이진 가중치 저항기들로 구성되며, 상기 제 2 종결 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 제 1 내지 제 3 가변 임피던스 회로들 각각의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 메모리 장치.

### 청구항 22.

제 15 항에 있어서,

제어 신호들에 응답하여 오프셋 선택 신호들와 상기 코드 선택 신호를 발생하는 선택 신호 발생 회로를 더 포함하는 반도체 메모리 장치.

### 청구항 23.

제 22 항에 있어서,

상기 오프-칩 구동 회로의 임피던스와 상기 제 1 및 제 2 종결 회로들의 임피던스는 상기 오프셋 선택 신호들에 의해서 가변되는 반도체 메모리 장치.

### 청구항 24.

제 22 항에 있어서,

상기 선택 신호 발생 회로는 모드 레지스터 세트 (MRS)인 반도체 메모리 장치.

### 청구항 25.

입력 신호 전송 라인을 통해 외부 신호를 입력받고, 상기 입력된 신호를 내부 회로로 출력하는 입력 회로와;

이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생하는 임피던스 제어 회로와;

이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 신호 전송 라인을 종결시키는 종결 회로와; 그리고

이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 내부 회로로부터 출력되는 신호에 따라 출력 신호 전송 라인을 구동하되, 임피던스가 상기 임피던스 제어 코드들에 따라 가변되는 출력 회로를 포함하며,

상기 종결 회로 및 상기 출력 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 임피던스 제어 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 집적 회로 장치.

## 청구항 26.

행들과 열들로 배열된 메모리 셀들의 어레이와;

메모리 셀들로부터/에 데이터를 읽고/쓰는 감지 증폭 회로와;

고정 임피던스 제어 코드들을 발생하는 제 1 코드 발생 회로와;

이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 외부 기준 저항기의 임피던스에 따라 가변되는 가변 임피던스 제어 코드들을 발생하는 제 2 코드 발생 회로와;

코드 선택 신호에 응답하여 상기 고정 임피던스 제어 코드들 또는 상기 가변 임피던스 제어 코드들을 선택하는 선택 회로 와;

상기 감지 증폭 회로로부터 출력되는 데이터 및 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들에 응답하여 풀업 및 풀다운 제어 신호들을 발생하는 구동 제어 회로와;

이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 읽기 동작 동안 상기 풀업 및 풀다운 제어 신호들에 응답하여 데이터 전송 라인들을 구동하되, 임피던스가 상기 풀업 및 풀다운 제어 신호들에 의해서 가변되는 오프-칩 구동 회로 와;

이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 쓰기 동작 동안 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 데이터 전송 라인들을 종결시키는 제 1 종결 회로를 포함 하며,

상기 제 1 종결 회로 및 상기 출력 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 제 2 코드 발생 회로 의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 메모리 장치.

## 청구항 27.

제 26 항에 있어서,

입력 전송 라인들을 통해 입력되는 어드레스 및 제어 신호들을 입력받는 입력 버퍼 회로와;

상기 입력 버퍼 회로로부터 출력되는 행 어드레스에 응답하여 상기 행들을 선택하는 행 디코더 회로와;

상기 입력 버퍼 회로로부터 출력되는 열 어드레스에 응답하여 상기 열들을 선택하는 열 디코더 회로와; 그리고 이진 가중치 트랜지스터들 및 이진 가중치 저항기들을 포함하며, 상기 선택 회로에 의해서 선택된 고정 또는 가변 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 전송 라인들을 종결시키는 제 2 종결 회로를 더 포함하는 반도체 메모리 장치.

### 청구항 28.

제 27 항에 있어서,

상기 제 2 종결 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들은 상기 제 2 코드 발생 회로의 이진 가중치 트랜지스터들 및 이진 가중치 저항기들의 선형적으로 축소된 크기 및 저항값을 갖는 반도체 메모리 장치.

### 청구항 29.

행들과 열들로 배열된 메모리 셀들의 어레이와;

메모리 셀들로부터/에 데이터를 읽고/쓰는 감지 증폭 회로와;

외부 기준 저항기에 연결되며, 상기 외부 기준 저항기의 임피던스에 따라 가변되는 임피던스 제어 코드들을 발생하는 코드 발생 회로와;

상기 감지 증폭 회로로부터 출력되는 데이터 및 임피던스 제어 코드들에 응답하여 풀업 및 풀다운 제어 신호들을 발생하는 구동 제어 회로와;

읽기 동작 동안 상기 풀업 및 풀다운 제어 신호들에 응답하여 데이터 전송 라인들을 구동하며, 임피던스가 상기 풀업 및 풀다운 제어 신호들에 의해서 가변되는 오프-칩 구동 회로와; 그리고

쓰기 동작 동안 상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 데이터 전송 라인들을 종결시키는 제 1 종결 회로를 포함하는 반도체 메모리 장치.

### 청구항 30.

제 29 항에 있어서,

상기 쓰기 동작 동안 상기 데이터 전송 라인들 상의 데이터를 상기 감지 증폭 회로로 전달하는 데이터 입력 회로를 더 포함하는 반도체 메모리 장치.

### 청구항 31.

제 29 항에 있어서,

상기 제 1 종결 회로는 상기 데이터 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들 중 어느 하나에 의해서 제어되는 반도체 메모리 장치.

### 청구항 32.

제 29 항에 있어서,

상기 제 1 종결 회로는 상기 데이터 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들에 의해서 제어되는 반도체 메모리 장치.

### 청구항 33.

제 29 항에 있어서,

상기 오프-칩 구동 회로는 상기 데이터 전송 라인들 각각에 병렬 연결된 복수 개의 구동기들을 포함하며, 상기 구동기들 각각의 임피던스는 상기 풀업 및 풀다운 제어 신호들에 의해서 조정되는 반도체 메모리 장치.

### 청구항 34.

제 29 항에 있어서,

입력 전송 라인들을 통해 입력되는 어드레스 및 제어 신호들을 입력받는 입력 버퍼 회로와;

상기 입력 버퍼 회로로부터 출력되는 행 어드레스에 응답하여 상기 행들을 선택하는 행 디코더 회로와;

상기 입력 버퍼 회로로부터 출력되는 열 어드레스에 응답하여 상기 열들을 선택하는 열 디코더 회로와; 그리고

상기 임피던스 제어 코드들 중 적어도 하나에 응답하여 상기 입력 전송 라인들을 종결시키는 제 2 종결 회로를 더 포함하는 반도체 메모리 장치.

### 청구항 35.

제 34 항에 있어서,

상기 제 2 종결 회로는 상기 입력 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들 중 어느 하나에 의해서 제어되는 반도체 메모리 장치.

### 청구항 36.

제 34 항에 있어서,

상기 제 2 종결 회로는 상기 입력 전송 라인들 각각에 병렬 연결된 복수 개의 종결 회로들을 포함하며, 상기 종결 회로들 각각은 상기 임피던스 제어 코드들에 의해서 제어되는 반도체 메모리 장치.

도면

도면1

도면2

도면3

도면4a

315

도면4b

317

도면5

## 도면6

340

## 도면7

260

도면8

도면9

0CD1(0CD2~0CD6)

도면10

0DT1(0DT2~0DT4)

도면11

도면12

도면13

270'

도면14