(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2023-83384

(P2023-83384A)

(43)公開日 令和5年6月15日(2023.6.15)

## (51)国際特許分類

|        |                  |        |       |         |

|--------|------------------|--------|-------|---------|

| H 01 L | 29/786 (2006.01) | H 01 L | 29/78 | 6 1 6 S |

| H 01 L | 21/336 (2006.01) | H 01 L | 29/78 | 6 2 6 C |

| H 10 B | 12/00 (2023.01)  | H 10 B | 12/00 | 6 1 5   |

| H 01 L | 29/41 (2006.01)  | H 10 B | 12/00 | 6 7 1 C |

| H 01 L | 29/417 (2006.01) | H 01 L | 29/44 | S       |

審査請求 有 請求項の数 3 O L (全32頁) 最終頁に続く

(21)出願番号 特願2023-64667(P2023-64667)

(22)出願日 令和5年4月12日(2023.4.12)

(62)分割の表示 特願2021-164004(P2021-164004)

)の分割

原出願日 平成20年3月11日(2008.3.11)

(31)優先権主張番号 特願2007-78067(P2007-78067)

(32)優先日 平成19年3月26日(2007.3.26)

(33)優先権主張国・地域又は機関

日本国(JP)

(71)出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

山崎 舜平

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

須澤 英臣

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

笹川 慎也

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

倉田 求

神奈川県厚木市長谷398番地 株式会

社半導体エネルギー研究所内

## (54)【発明の名称】 半導体装置

## (57)【要約】

【課題】コンタクトホール形成時のエッチングの制御を容易に行う半導体装置を作製する技術を提案する。

【解決手段】少なくとも絶縁表面上に形成された半導体層と、半導体層上に形成された第1の絶縁層と、第1の絶縁層上に形成されたゲート電極と、ゲート電極上に形成された第2の絶縁層と、を有し、少なくとも半導体層及び第2の絶縁層に開口部が形成されて絶縁表面が部分的に露出されており、開口部を介して第2の絶縁層上に形成された導電層と、を有する。なお、ここで導電層は半導体層に形成された開口の側面において半導体層と電気的に接続している。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

絶縁表面上に形成された半導体層と、

前記半導体層上に形成された第1の絶縁層と、

前記第1の絶縁層上に形成されたゲート電極と、

前記ゲート電極上に形成された第2の絶縁層と、

少なくとも前記半導体層及び前記第2の絶縁層に形成された、前記絶縁表面に達する開口部を介して前記第2の絶縁層上に形成された導電層と、を有する半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

10

## 【0001】

本発明は、半導体装置及びその作製方法に関する。なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を示す。

## 【背景技術】

## 【0002】

近年、ガラス等の絶縁表面を有する基板上に薄膜トランジスタ(TFT)を形成し、当該薄膜トランジスタをスイッチング素子等として利用する半導体装置の作製が盛んに行われている。当該薄膜トランジスタは、絶縁表面を有する基板上にCVD法、フォトリソグラフィ工程等を用いて島状の半導体膜を形成し、当該島状の半導体膜の一部をトランジスタのチャネル形成領域として利用するように設けられている(例えば特許文献1)。

20

## 【0003】

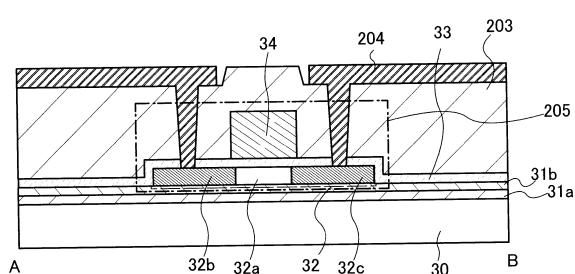

薄膜トランジスタの断面の模式図を図21に示す。図21に示すように、薄膜トランジスタは、基板30上に、下地膜として機能する絶縁層31が形成され、絶縁層31上に、チャネル形成領域32a、ソース領域及びドレイン領域として機能する不純物領域32b、32cを有する半導体層32が形成され、半導体層32及び絶縁層31上にゲート絶縁層として機能する絶縁層33が形成され、絶縁層33上にゲート電極として機能する導電層34が形成され、導電層34上に絶縁層203が形成され、絶縁層203上に不純物領域32b、32cと電気的に接続する配線204が形成されている。

## 【先行技術文献】

## 【特許文献】

30

## 【0004】

## 【特許文献1】特開平08-018055号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

図21の構造では、配線をソース領域又はドレイン領域の表面と電気的に接続させるため、開口部の底部にはソース領域又はドレイン領域となる半導体層を形成する必要が考えられていた。そのため絶縁層に開口部を設ける際のエッチングの制御が困難であった。これは半導体層を50nm以下の薄膜で形成する場合に特に顕著な問題である。

## 【0006】

40

本願発明はこのような課題を解決するための技術であり、コンタクトホール形成時のエッチングの制御を容易に行うことができる半導体装置を作製する技術を提案する。

## 【課題を解決するための手段】

## 【0007】

本発明の半導体装置は、少なくとも絶縁表面上に形成された半導体層と、半導体層上に形成された第1の絶縁層と、第1の絶縁層上に形成されたゲート電極と、ゲート電極上に形成された第2の絶縁層と、を有し、少なくとも半導体層及び第2の絶縁層に開口部が形成されて絶縁表面が部分的に露出されており、開口部を介して第2の絶縁層上に形成された導電層と、を有する。なお、ここで導電層は半導体層に形成されたコンタクトホールの側面において半導体層と電気的に接続している。また、半導体層の表面の一部が露出するよ

50

うにコンタクトホールを形成してもよい。つまり、半導体層に形成された開口の上面積は、第2の絶縁層に形成された開口の上面積に比べて小さく形成されており、導電層と半導体層とが、半導体層に形成されたコンタクトホールの側面及び半導体層の表面において電気的に接続されていてもよい。

【0008】

本発明の半導体装置は、絶縁表面上に半導体層を形成し、半導体層上に第1の絶縁層を形成し、第1の絶縁層上にゲート電極を形成し、ゲート電極上に第2の絶縁層を形成し、少なくとも前記半導体層及び前記第2の絶縁層に、前記絶縁表面を部分的に露出する開口部を形成し、開口部を介して絶縁表面及び前記第2の絶縁層上に導電層を形成することにより作製することができる。

10

【0009】

また、本発明の半導体装置は、基板上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に半導体層を形成し、半導体層上に第3の絶縁層を形成し、第3の絶縁層上にゲート電極を形成し、ゲート電極上に第4の絶縁層を形成し、少なくとも第2の絶縁層、半導体層及び第4の絶縁層に、第1の絶縁層表面を部分的に露出する開口部を形成し、開口部を介して前記第1の絶縁層表面及び第4の絶縁層上に導電層を形成することにより作製することができる。

【0010】

また、本発明の半導体装置は、基板上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に半導体層を形成し、半導体層上に第3の絶縁層を形成し、第3の絶縁層上にゲート電極を形成し、ゲート電極上に第4の絶縁層を形成し、第4の絶縁層上にレジストを形成し、レジストをマスクとして少なくとも第4の絶縁層に、半導体層表面を部分的に露出する第1の開口部を形成し、レジストをマスクとして少なくとも前記第2の絶縁層、半導体層及び第4の絶縁層をエッチングして、第1の絶縁層表面及び半導体層表面を部分的に露出する第2の開口部を形成し、第2の開口部を介して第1の絶縁層表面、半導体層表面、及び第4の絶縁層上に導電層を形成することにより作製することができる。なお、第1の開口部は、ウェットエッチングにより形成し、第2の開口部はドライエッチングにより形成することができる。

20

【0011】

また、本発明の半導体装置は、基板上に第1の絶縁層を形成し、第1の絶縁層上に第2の絶縁層を形成し、第2の絶縁層上に半導体層を形成し、半導体層上に第3の絶縁層を形成し、第3の絶縁層上にゲート電極を形成し、ゲート電極上に第4の絶縁層を形成し、第4の絶縁層上にレジストを形成し、レジストをマスクとして少なくとも第4の絶縁層に、半導体層表面を部分的に露出する第1の開口部を形成し、レジストをエッチングして前記レジストを後退させ、レジストをマスクとして少なくとも第2の絶縁層、半導体層及び第4の絶縁層をエッチングして、第1の絶縁層表面及び半導体層表面を部分的に露出する第2の開口部を形成し、第2の開口部を介して第1の絶縁層表面、半導体層表面、及び第4の絶縁層上に導電層を形成することにより作製することができる。なお、第1の開口部及び第2の開口部はドライエッチングにより形成することができる。

30

【発明の効果】

【0012】

本発明において、半導体膜の表面でエッチングを止める必要がないため、コンタクトホール形成時のエッチングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。

40

【図面の簡単な説明】

【0013】

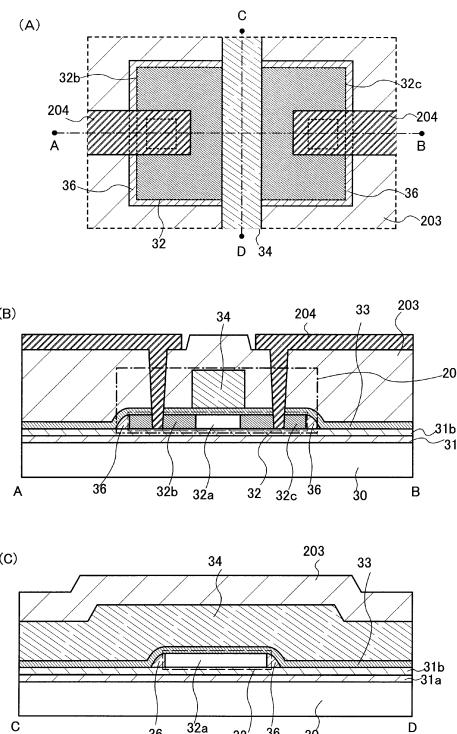

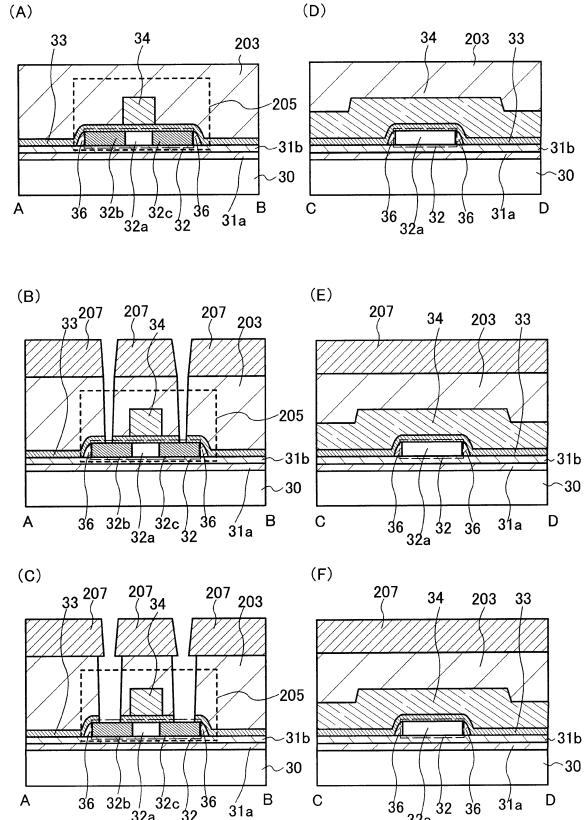

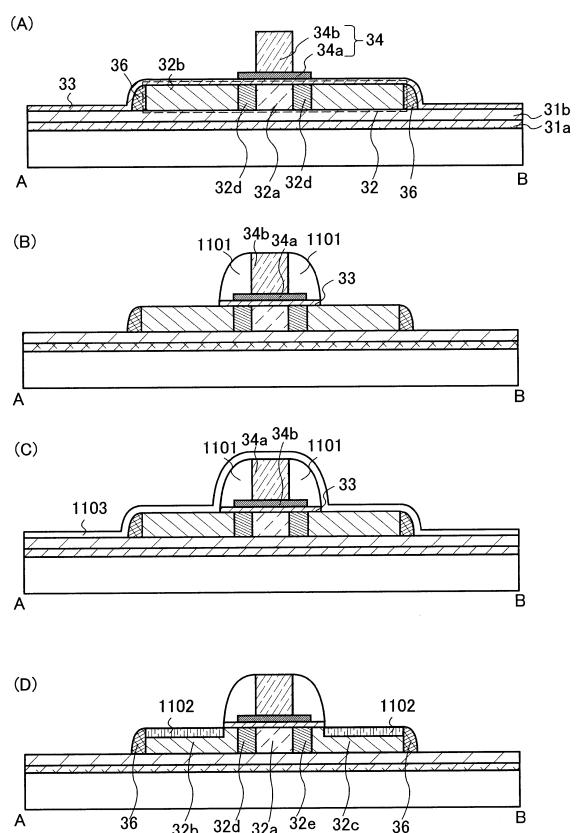

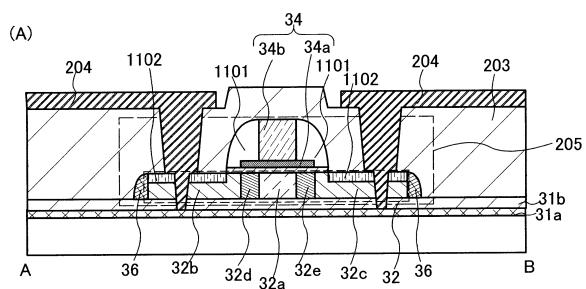

【図1】本発明の半導体装置の構成を説明する上面図及び断面図。

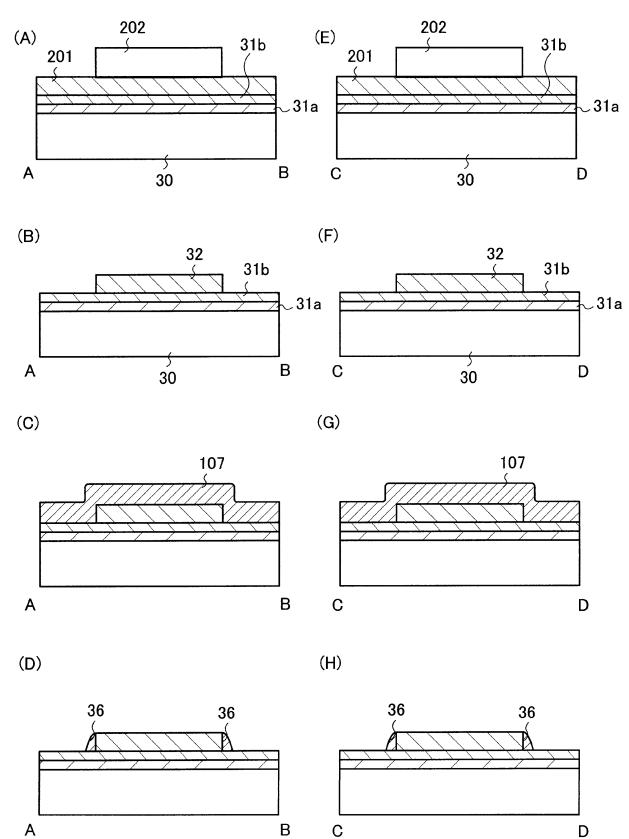

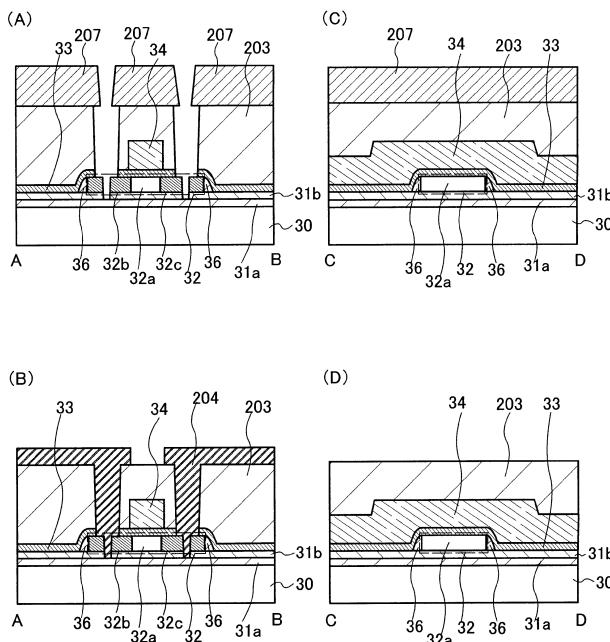

【図2】本発明の半導体装置の作製工程を説明する断面図。

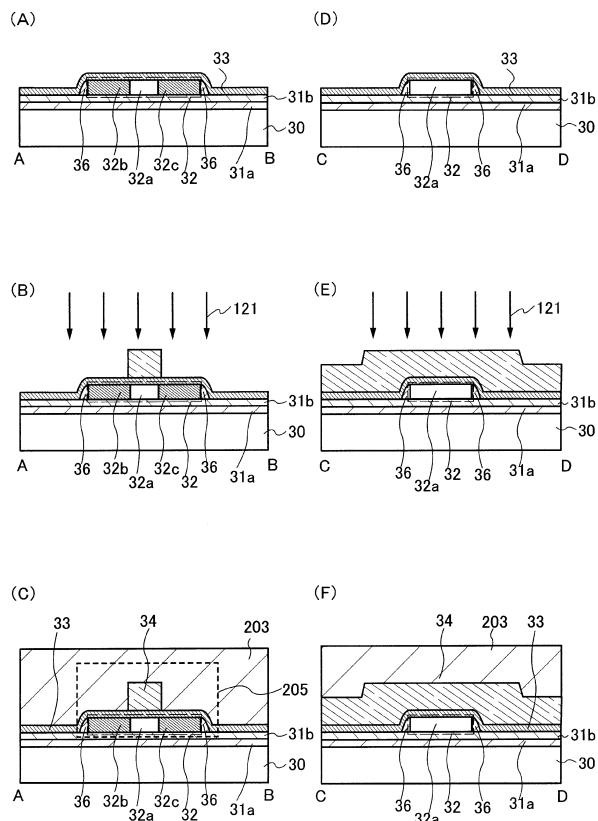

【図3】本発明の半導体装置の作製工程を説明する断面図。

50

【図4】本発明の半導体装置の作製工程を説明する断面図。

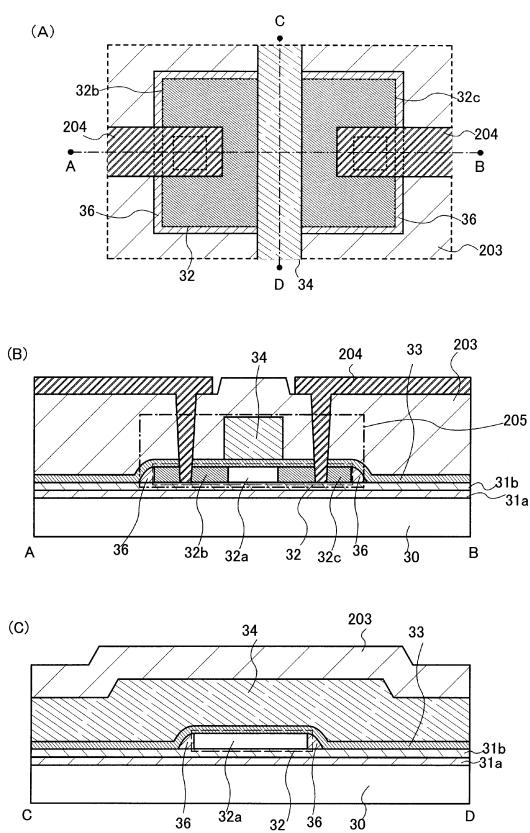

【図5】本発明の半導体装置の構成を説明する上面図及び断面図。

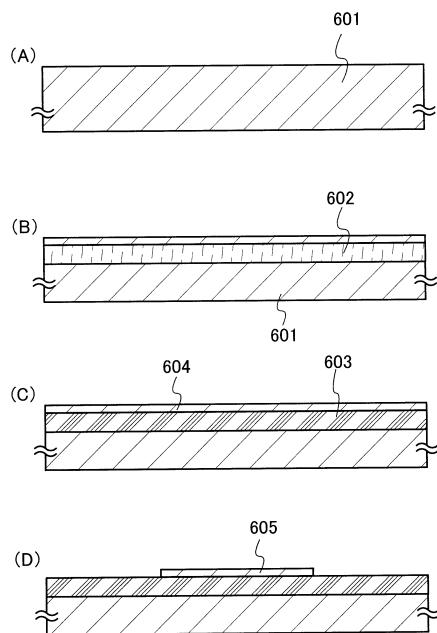

【図6】本発明の半導体装置の作製工程を説明する断面図。

【図7】本発明の半導体装置の構成を説明する上面図及び断面図。

【図8】本発明の半導体装置の作製工程を説明する断面図。

【図9】本発明の半導体装置の作製工程を説明する断面図。

【図10】本発明の半導体装置の作製工程を説明する断面図。

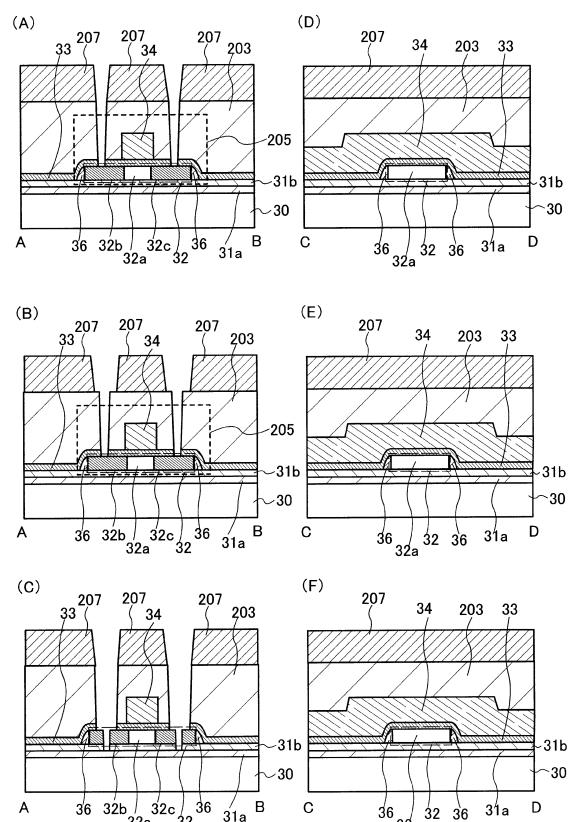

【図11】本発明の半導体装置の構成を説明する上面図及び断面図。

【図12】本発明の半導体装置の作製工程を説明する断面図。

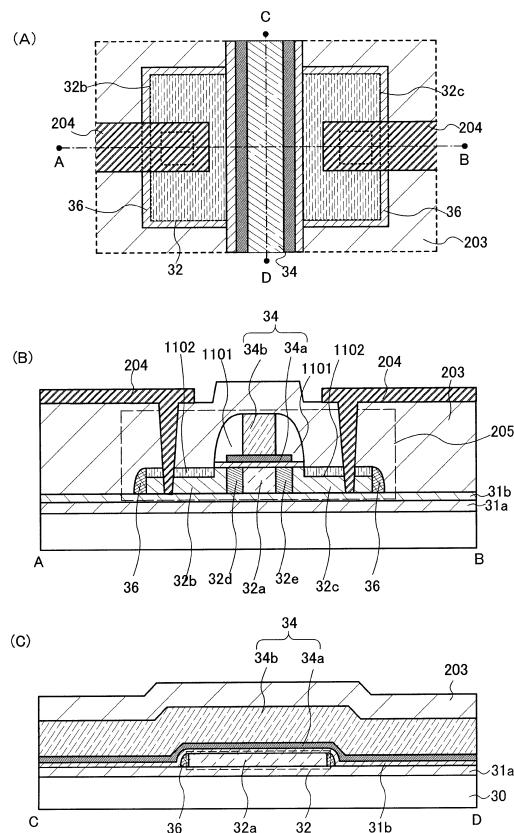

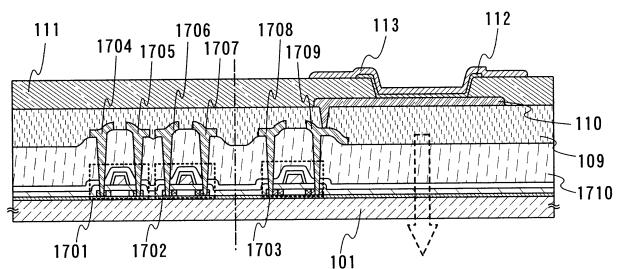

【図13】本発明の半導体装置の構成を説明する断面図。

【図14】本発明の半導体装置の構成を説明する断面図。

【図15】本発明の半導体装置の構成を説明する断面図。

【図16】本発明の半導体装置の作製工程を説明する断面図。

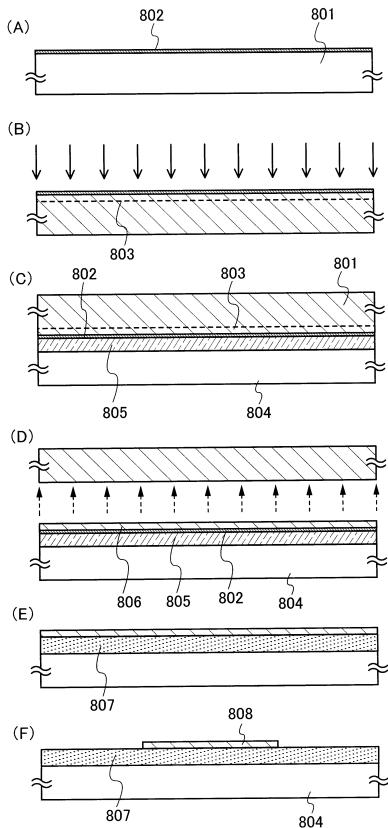

【図17】本発明の半導体装置の作製工程を説明する断面図。

【図18】本発明の半導体装置の構成を説明する断面図。

【図19】本発明の半導体装置の構成を説明する断面図。

【図20】本発明の半導体装置の構成を説明する上面図と断面図。

【図21】従来の半導体装置の構成を説明する断面図。

## 【発明を実施するための形態】

## 【0014】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる場合がある。

## 【0015】

## (実施の形態1)

本実施の形態では、コンタクトホール形成時のエッチングの制御を容易に行うことができる半導体装置の構造及び作製方法について説明する。

## 【0016】

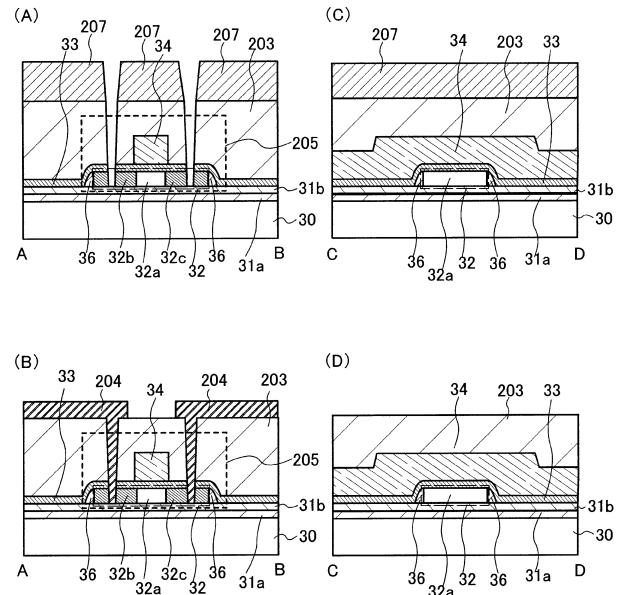

図1は本発明に係る半導体装置の主要な構成を説明するための上面図及び断面図である。図1(A)は、特に薄膜トランジスタの上面図を示し、図1(B)は図1(A)のAとBとを結ぶ破線における断面図を示し、図1(C)は図1(A)のCとDとを結ぶ破線における断面図を示している。

## 【0017】

本実施の形態に示す半導体装置は、基板30上に絶縁層31を介して島状に設けられた半導体層32と、半導体層32上に形成されたゲート絶縁層33と、半導体層32の上方にゲート絶縁層33を介して設けられたゲート電極として機能する導電層34と、を含む薄膜トランジスタ205と、ゲート絶縁層33及び導電層34を覆って設けられた絶縁層203と、絶縁層203上に設けられたソース電極又はドレイン電極として機能する導電層204とを有している(図1(A)～(C))。なお、半導体層32は、チャネル形成領域32aとソース領域又はドレイン領域として機能する不純物領域32b、32cとに加えて、半導体層32の端部、ここでは導電層34の下方のチャネル形成領域32aに接した部分に形成された絶縁層36とを有している。

## 【0018】

本実施の形態に示す半導体装置は、絶縁層203及び半導体層32の不純物領域32b、32cをエッチングして、絶縁層31bに達するコンタクトホール(開口部ともいう)を形成し、該コンタクトホールを充填するように導電層204を形成している。つまり、本実施の形態において、導電層204と不純物領域32b、32cとは、不純物領域32b、32cに形成されたコンタクトホールの側面において電気的に接続されている。

10

20

30

40

50

## 【 0 0 1 9 】

本実施の形態において、半導体層の表面でエッティングを止める必要がないため、コンタクトホール形成時のエッティングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。

## 【 0 0 2 0 】

ここで、半導体層の端部に形成された絶縁層 3 6 は必ずしも形成する必要はないが、半導体層 3 2 の端部とゲート電極として機能する導電層 3 4 が短絡してリーク電流が流れるのを防止するために設けることが好ましい。従って、絶縁層 3 6 を設ける場合、少なくとも半導体層 3 2 のチャネル形成領域 3 2 a の側面（露出している部分）に形成されればよい。ただし、それ以外の部分に形成されていてももちろん構わない。なお、本実施の形態において、絶縁層 3 6 はゲート絶縁層 3 3 の下側（基板側）の領域にゲート絶縁層 3 3 と接して形成されている。

## 【 0 0 2 1 】

次に、図 1 に示した半導体装置の作製方法の一例について図面を参照して説明する。なお、図 1 ( A ) の A と B とを結ぶ破線での断面における作製工程を図 2 ( A ) ~ ( D ) 、図 3 ( A ) ~ ( C ) 、図 4 ( A ) ~ ( B ) を用いて、図 1 ( A ) の C と D とを結ぶ破線での断面における作製工程を図 2 ( E ) ~ ( H ) 、図 3 ( D ) ~ ( F ) 、図 4 ( C ) ~ ( D ) を用いて説明する。

## 【 0 0 2 2 】

まず、基板 3 0 上に絶縁層 3 1 を形成する（図 2 ( A ) 、( E ) ）。本実施の形態では、絶縁層 3 1 は、基板 3 0 上に形成された第 1 の絶縁層 3 1 a 及び第 1 の絶縁層 3 1 a 上に形成された第 2 の絶縁層 3 1 b の 2 層構造とする。

## 【 0 0 2 3 】

基板 3 0 は、ガラス基板、石英基板、金属基板（例えばセラミック基板またはステンレス基板など）、Si 基板等の半導体基板などを用いることができる。また、他にもプラスチック基板として、ポリエチレンテレフタレート（P E T）、ポリエチレンナフタレート（P E N）、ポリエーテルサルファン（P E S）、アクリルなどの基板を選択することもできる。

## 【 0 0 2 4 】

絶縁層 3 1 は、例えば、C V D 法やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン（Si O<sub>x</sub> N<sub>y</sub>）（x > y > 0）、窒化酸化シリコン（Si N<sub>x</sub> O<sub>y</sub>）（x > y > 0）等の絶縁材料を用いて形成することができる。例えば、第 1 の絶縁層 3 1 a として窒化酸化シリコン膜を形成し、第 2 の絶縁層 3 1 b として酸化窒化シリコン膜を形成するとよい。また、第 1 の絶縁層 3 1 a として窒化シリコン膜を形成し、第 2 の絶縁層 3 1 b として酸化シリコン膜を形成してもよい。絶縁層 3 1 を設けることにより基板 3 0 からアルカリ金属などの不純物が拡散して、上に形成される素子の汚染を防ぐことができる。

## 【 0 0 2 5 】

続いて、絶縁層 3 1 上に半導体膜 2 0 1 を形成する。半導体膜 2 0 1 は、非晶質半導体膜又は結晶質半導体膜で形成することができる。結晶性半導体膜としては、絶縁層 3 1 上に形成した非晶質半導体膜を熱処理やレーザー光の照射によって結晶化させたものなどを用いることができる。なお、半導体材料としては、シリコンが好ましく、その他にシリコンゲルマニウム半導体等を用いることもできる。

## 【 0 0 2 6 】

半導体膜 2 0 1 は、1 0 n m ~ 2 0 0 n m 、好ましくは 1 0 n m ~ 5 0 n m 程度、更に好ましくは 1 0 n m ~ 3 0 n m 程度の膜厚で形成するとよい。なお、5 0 n m 以下の半導体膜を形成する場合、5 0 n m 以上の膜厚で半導体膜を形成した後で、半導体膜の表面をドライエッティング処理することにより 1 0 n m ~ 5 0 n m 程度の膜厚の半導体膜を形成してもよい。このときのエッティングの際のエッティングガスとしては、C l 2 、B C l 3 、S i

10

20

30

40

50

C<sub>1</sub>4等の塩素系のガス、C<sub>F</sub>4、N<sub>F</sub>3、S<sub>F</sub>6、C<sub>H</sub>F<sub>3</sub>、等のフッ素系のガス、又はフッ素系ガスにO<sub>2</sub>ガス、H<sub>2</sub>ガス、HeやAr等の不活性ガスを適宜加えた混合ガス等を用いることができる。なお、ドライエッチングの前に、半導体膜表面を希フッ酸処理して半導体表面に形成される自然酸化膜を除去し、その後半導体膜表面をオゾン水などで処理して半導体膜表面に酸化膜を形成しておいてもよい。

#### 【0027】

半導体膜201を50nm以下程度の薄膜で形成することにより、半導体膜表面に形成されるゲート絶縁層の被覆不良を低減することができる。また、半導体膜を薄膜で形成することにより、TFTをより小型化することができる。また、TFTのしきい値電圧を制御するためにチャネル形成領域への不純物元素のドープ量を増加させた場合でも、半導体膜を薄膜で形成することにより完全空乏型のTFTを作製しやすくなるため、良好なS値の状態でしきい値電圧が制御されたTFTを作製することができる。

#### 【0028】

また、非結晶半導体膜をレーザー光の照射によって結晶化若しくは再結晶化した膜を半導体膜201として用いる場合、レーザー光の光源としてLD励起の連続発振(CW)レーザー(YVO<sub>4</sub>、第2高調波(波長532nm))を用いることができる。特に第2高調波に限定する必要はないが、第2高調波はエネルギー効率の点で、さらに高次の高調波より優れている。CWレーザーを半導体膜に照射すると、連続的に半導体膜にエネルギーが与えられるため、一旦半導体膜を溶融状態にすると、溶融状態を継続させることができる。さらに、CWレーザーを走査することによって半導体膜の固液界面を移動させ、この移動の方向に沿って一方向に長い結晶粒を形成することができる。また、固体レーザーを用いるのは、気体レーザー等と比較して、出力の安定性が高く、安定した処理が見込まれるためである。なお、CWレーザーに限らず、繰り返し周波数が10MHz以上のパルスレーザーを用いることも可能である。繰り返し周波数が高いパルスレーザーを用いると、半導体膜が溶融してから固化するまでの時間よりもレーザーのパルス間隔が短ければ、常に半導体膜を溶融状態にとどめることができ、固液界面の移動により一方向に長い結晶粒で構成される半導体膜を形成することができる。その他のCWレーザー及び繰り返し周波数が10MHz以上のパルスレーザーを使用することもできる。例えば、気体レーザーとしては、Arレーザー、Krレーザー、CO<sub>2</sub>レーザー等がある。固体レーザーとして、YAGレーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、KGWレーザー、KYWレーザー、アレキサンンドライトレーザー、Ti:サファイアレーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、YVO<sub>4</sub>レーザー等がある。また、YAGレーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、YVO<sub>4</sub>レーザーなどのセラミックスレーザーがある。金属蒸気レーザーとしてはヘリウムカドミウムレーザ等が挙げられる。また、レーザー発振器において、レーザー光をTEM<sub>00</sub>(シングル横モード)で発振して射出すると、被照射面において得られる線状のビームスポットのエネルギー均一性を上げることができるので好ましい。その他にも、パルス発振のエキシマレーザーを用いても良い。

#### 【0029】

次に、半導体膜201上にレジスト202を選択的に形成する(図2(A)、(E))。そして、レジスト202をマスクとして半導体膜201をドライエッチングして、島状の半導体層32を形成する(図2(B)、(F))。なお、レジスト202は、エッチングの際のマスクとして用いるものであり、ポジ型のフォトレジストやネガ型のフォトレジスト等を適宜選択して用いることができる。

#### 【0030】

なお、ドライエッチングのときのエッチングガスとしては、C<sub>F</sub>4、N<sub>F</sub>3、S<sub>F</sub>6、C<sub>H</sub>F<sub>3</sub>等のフッ素系のガス、又は該フッ素系ガスにO<sub>2</sub>ガス、H<sub>2</sub>ガス、HeやAr等の不活性ガスを適宜加えた混合ガス等を用いることができる。好ましくは、C<sub>F</sub>4とO<sub>2</sub>との混合ガス、S<sub>F</sub>6とO<sub>2</sub>との混合ガス、C<sub>H</sub>F<sub>3</sub>とHeとの混合ガス、又はC<sub>F</sub>4とH<sub>2</sub>との混合ガスを用いるといい。また、エッチングはドライエッチングに限らずウェットエッチングで行ってもよい。その場合、半導体膜201に対してTM<sub>AH</sub>(tetra

10

20

30

40

50

methylammonium hydroxide、テトラメチルアンモニウムヒドロキシド)に代表される有機アルカリ系水溶液を用いたウェットエッティングを行うことにより島状の半導体層32を形成することができる。なお、エッティング液としてTMAH等を用いた場合、半導体膜201のみが選択的にエッティングされるため、下地の絶縁層31にダメージを与えずにエッティングすることができる。このように、絶縁表面に形成された半導体層を島状に分離形成することで、同一基板上に複数の薄膜トランジスタと周辺回路を形成した場合に、それぞれの素子を分離をすることができます。

#### 【0031】

また、半導体層32は、端部が垂直形状となるように形成してもよいし、端部がテープ形状となるように形成してもよい。半導体層32の端部の形状は、エッティング条件等を変化させることにより、適宜選択することができる。好ましくは、半導体層32の端部をテープ角が45°以上95°未満、より好ましくはテープ角が60°以上95°未満となるように形成するとよい。半導体層32の端部を垂直に近い形状とすることで寄生チャネルを低減することができる。

#### 【0032】

続いて、半導体層32上に形成されたレジスト202を除去する。

#### 【0033】

次に、半導体層32を覆うように絶縁層107(以下、第3の絶縁層107ともいう)を形成する(図2(C)、(G))。第3の絶縁層107は、CVD法やスパッタリング法を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、SiOF、SiOC、DLC、ポーラスシリカ等の材料を用いて形成することができる。

#### 【0034】

また、第3の絶縁層107は、半導体層32の端部を十分に被覆できる膜厚で形成する。第3の絶縁層107の膜厚は、下層に形成される半導体層32の膜厚の1.5倍乃至3倍の範囲の厚さで形成するのが好ましい。

#### 【0035】

次に、第3の絶縁層107を、垂直方向を主体とした異方性エッティングを行うことにより選択的にエッティングし、半導体層32の側面と接する絶縁層36(以下、第4の絶縁層36ともいう)を形成する(図2(D)、(H))。

#### 【0036】

第3の絶縁層107を、垂直方向を主体として異方性のエッティングを行っていくと、半導体層32の一表面上および絶縁層31b上に形成されている第3の絶縁層107から徐々にエッティングされていく。なお、半導体層32の一表面上及び絶縁層31b上には、ほぼ同じ膜厚の第3の絶縁層107が形成されている。よって、半導体層106の一表面が露出したところでエッティングを停止させることにより、半導体層32の側面と接する領域及びその付近のみに第3の絶縁層107を残すことができる。残存する第3の絶縁層107は、第4の絶縁層36に相当する。なお、半導体層32の端部を垂直形状に近い形状としておくことで、半導体層32の側面と接する領域及びその付近のみに第3の絶縁層107を残すことが容易になる。つまり、第4の絶縁層36を容易に形成することができる。

#### 【0037】

第3の絶縁層107のエッティング方法は、垂直方向を主体とした異方性エッティングを行えるものであれば特に限定されない。例えば、反応性イオンエッティング(RIE: Reactive Ion Etching)を利用することができる。また、反応性イオンエッティングは、プラズマ発生法により、平行平板方式、マグネットロン方式、2周波方式、ERC方式、ヘリコン方式、ICP方式などに分類される。このとき用いるエッティングガスは、第3の絶縁層107と、それ以外の層(半導体層32)とでエッティング選択比が取れるものを選択すればよい。絶縁膜を選択的にエッティングする際には、例えば、CHF3、CF4、C4F8、C2F6、NF3等のフッ素系のガスを用いることができる。その他、ヘリウム(He)、アルゴン(Arg)、キセノン(Xe)などの不活性ガス、又はO2ガス、H2ガスを適宜加えてよい。

10

20

30

40

50

## 【 0 0 3 8 】

第4の絶縁層36の形状は、薄膜を形成する材料、エッティング条件等を適宜選択することにより変更することができる。本実施の形態では、第4の絶縁層36は、底面（絶縁層31bと接する面）からの垂直方向の高さが半導体層32と略一致するように形成している。また、第4の絶縁層36は、半導体層の側面と接しない面を湾曲状に形成している。具体的には、任意の曲率を有し、接する半導体層32の側面に対して凸形状に湾曲するように形成している。もちろん、本発明は特に限定されず、第4の絶縁層36は丸みを帯びた形状でなく、角を有する形状としてもよい。好ましくは、第4の絶縁層36のコーナー部を緩やかな形状とすると、上層に積層される層（ここでは、絶縁層33）の被覆性を良好にすることができる。なお、エッティング条件は、エッティングガスの種類、各ガスの流量比の他、基板を載置した電極に印加される電力量、基板が載置した電極の電極温度、チャンバー内圧力等を示す。

## 【 0 0 3 9 】

次に、半導体層32及び第4の絶縁層36上に絶縁層33（以下、第5の絶縁層33ともいう）を形成する（図3（A）、（D））。第5の絶縁層33は、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化アルミニウム等の材料を用いて形成する。また、第5の絶縁層33は、これらの材料のうち1つ又は複数を用いて、単層構造又は積層構造で形成する。第5の絶縁層33は、膜厚1nm乃至50nm、好ましくは膜厚1nm乃至20nm、より好ましくは1nm乃至10nmの範囲で形成する。

## 【 0 0 4 0 】

なお、絶縁層36の形成方法は本実施の形態に示すものに限られるものではなく、半導体層32の端部をウェット酸化又は酸素を含む雰囲気下でプラズマ処理することにより形成してもよい。その場合、半導体層32上に絶縁層33を形成した後、半導体層32の端部を覆う絶縁層33を除去し、半導体層32の露出した部分にプラズマ処理又はウェット酸化することにより絶縁層36を形成することが好ましい。

## 【 0 0 4 1 】

なお、ウェット酸化の場合、オゾンを含む水溶液、過酸化水素を含む水溶液、硫酸を含む水溶液、ヨウ素酸を含む水溶液、又は硝酸を含む水溶液を用いて半導体層32の表面を処理することにより、半導体層32の露出している部分に形成された酸化膜を絶縁層36として用いることができる。オゾンを含む水溶液、過酸化水素を含む水溶液、前記硫酸を含む水溶液、前記ヨウ素酸を含む水溶液、又は前記硝酸を含む水溶液は、酢酸又はしゅう酸を含んでいてもよい。

## 【 0 0 4 2 】

また、酸素を含む雰囲気下として例えば、酸素（O<sub>2</sub>）と希ガス（He、Ne、Ar、Kr、Xeの少なくとも一つを含む）との混合ガス雰囲気下、酸素と水素（H<sub>2</sub>）と希ガスとの混合ガス雰囲気下、一酸化二窒素と希ガスとの混合ガス雰囲気下、または一酸化二窒素と水素と希ガスとの混合ガス雰囲気下で行うことができる。例えば、酸素（O<sub>2</sub>）、水素（H<sub>2</sub>）とアルゴン（Ar）との混合ガスを用いることができる。その場合の流量は、酸素を0.1～100sccm、水素を0.1～100sccm、アルゴンを100～5000sccmとすればよい。なお、酸素：水素：アルゴン=1：1：100の比率で混合ガスを導入することが好ましい。例えば、酸素を5sccm、水素を5sccm、アルゴンを500sccmとして導入すればよい。

## 【 0 0 4 3 】

また、窒素を含む雰囲気下として例えば、窒素（N<sub>2</sub>）と希ガス（He、Ne、Ar、Kr、Xeの少なくとも一つを含む）との混合ガス雰囲気下、窒素と水素と希ガスとの混合ガス雰囲気下、またはアンモニア（NH<sub>3</sub>）と希ガスとの混合ガス雰囲気下で行うことができる。

## 【 0 0 4 4 】

なお、プラズマ処理は、上記ガスの雰囲気中において、電子密度が1×10<sup>11</sup>cm<sup>-3</sup>

10

20

30

40

50

以上であり、電子温度が1.5eV以下のプラズマを用いて行う。より詳しくいうと、電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上 $1 \times 10^{13} \text{ cm}^{-3}$ 以下で、電子温度が0.5eV以上1.5eV以下のプラズマで行う。上記プラズマはプラズマの電子密度が高密度であり、基板30上に形成された被処理物（ここでは、半導体層32）付近での電子温度が低いため、被処理物に対するプラズマによる損傷を防止することができる。また、プラズマの電子密度が $1 \times 10^{11} \text{ cm}^{-3}$ 以上と高密度であるため、プラズマ処理を用いて、被照射物を酸化または窒化することによって形成される酸化膜または窒化膜は、CVD法やスパッタ法等により形成された膜と比較して膜厚等が均一性に優れ、且つ緻密な膜を形成することができる。また、プラズマの電子温度が1.5eV以下と低いため、従来のプラズマ処理や熱酸化法と比較して低い温度で酸化または窒化処理を行うことができる。例えば、ガラス基板の歪点よりも100度以上低い温度でプラズマ処理を行っても十分に酸化を行うことができる。また、プラズマを形成するための周波数としては、マイクロ波（2.45GHz）等の高周波を用いることができる。

10

20

## 【0045】

次に、ゲート絶縁層33上にゲート電極として機能する導電層34を形成する（図3（B）（E））。ここでは、導電層34は単層で形成した例を示しているが、もちろん導電性材料を2層又は3層以上の積層で設けた構造としてもよい。なお、ここでは図示しないが、導電層34は、ゲート絶縁層33上を覆って形成された導電層を選択的にエッチングすることにより形成することができる。

20

30

40

## 【0046】

また、導電層34は、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等から選択された元素またはこれらの元素を主成分とする合金材料若しくは化合物材料で形成することができる。また、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。例えば、導電層34を第1の導電膜と第2の導電膜との積層構造とする場合、第1の導電膜として窒化タンタルを用い、第2の導電膜としてタンゲステンを用いて形成するとよい。なお、この組み合わせに限られず、導電層34を積層して形成する場合には、上記材料を自由に組み合わせて設けることができる。

30

40

## 【0047】

続いて、導電層34をマスクとして半導体層32に不純物元素121を導入することによって、半導体層32に不純物領域32b、32c及び不純物元素121が導入されないチャネル形成領域32aを形成する（図3（B）（E））。なお、ここでは、導電層34を島状の半導体層32を横断するように形成した後に不純物元素を導入するため、導電層34に覆われていない半導体層32の領域に不純物が導入されて不純物領域32b、32cが形成され、導電層34に覆われた半導体層32の領域には不純物元素121が導入されないチャネル形成領域32aが形成される。

30

40

## 【0048】

ここで、不純物元素121としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いることができる。n型を示す不純物元素としては、リン（P）やヒ素（As）等を用いることができる。p型を示す不純物元素としては、ボロン（B）やアルミニウム（Al）やガリウム（Ga）等を用いることができる。例えば、不純物元素121として、リン（P）を $1 \times 10^{18} \sim 1 \times 10^{21} \text{ cm}^{-3}$ の濃度で含まれるように半導体層32に導入し、n型を示す不純物領域32b、32cを形成すればよい。なお、チャネル形成領域32aとソース領域又はドレイン領域である不純物領域32b、32cとの間に、ソース領域又はドレイン領域である不純物領域32b、32cより低濃度に不純物が添加された低濃度不純物領域（LDD領域）を形成してもよい。低濃度不純物領域を設けることにより、ドレイン端の電界を緩和して、書き込み及び消去の繰り返しによる劣化を抑制することができる。

30

40

## 【0049】

また、チャネル形成領域32a中に、不純物領域32b、32cに添加した不純物とは逆

50

の導電型を有する不純物元素（例えばn型TFTに対してはボロン）を添加してもよい。チャネル形成領域32a中に逆導電型の不純物を添加することにより、TFTのしきい値電圧を制御することができる。なお、この不純物元素はゲート電極を介してドープすることによって添加してもよいし、ゲート電極形成前に予め添加しておいてもよい。

#### 【0050】

次に、導電層34、ゲート絶縁層33を覆うように絶縁層203を形成する（図3（C）（F））。続いて、絶縁層203上に選択的にレジスト207を形成する。

#### 【0051】

その後、ドライエッチングにより絶縁層203、ゲート絶縁層33、及び半導体層32にコンタクトホールを形成する（図4（A）、（C））。次に、絶縁層203上にソース電極又はドレイン電極として機能する導電層204を選択的に形成する（図4（B）、（D））。ここで、導電層204は、絶縁層203、ゲート絶縁層33、及び半導体層32に形成されたコンタクトホールを充填するように形成されている。従って、導電層204とソース領域又はドレイン領域として機能する不純物領域32b、32cとは、不純物領域32b、32cに形成されたコンタクトホールの側面において電気的に接続されるように設けられている。

#### 【0052】

ここで、絶縁層203は、CVD法やスパッタリング法等で形成した、酸化シリコン、酸化窒化シリコン（ $\text{SiO}_{xNy}$ ）（ $x > y > 0$ ）、窒化酸化シリコン（ $\text{SiN}_{xOy}$ ）（ $x > y > 0$ ）などを用いることができる。また、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、エポキシ等の有機材料、またはシロキサン樹脂等のシロキサン材料、オキサゾール樹脂などからなる単層または積層構造で設けることができる。なお、シロキサン材料とは、 $\text{Si-O-Si}$ 結合を含む材料に相当する。シロキサンは、シリコン（ $\text{Si}$ ）と酸素（ $O$ ）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、芳香族炭化水素）が用いられる。置換基として、フルオロ基を用いることもできる。オキサゾール樹脂は、例えば、感光性ポリベンゾオキサゾール等である。感光性ポリベンゾオキサゾールは、誘電率が低く（常温1MHzで誘電率2.9）、耐熱性が高く（示差熱熱重量同時測定（TG/DTA：Thermogravimetry-Differential Thermal Analysis）で昇温5/minで熱分解温度550）、吸水率が低い（常温24時間で0.3%）材料である。オキサゾール樹脂は、ポリイミド等の比誘電率（3.2~3.4程度）と比較すると、比誘電率が低いため（2.9程度）、寄生容量の発生を抑制し、高速動作を行うことができる。ここでは、絶縁層203として、CVD法で形成した酸化シリコン、酸化窒化シリコン（ $\text{SiO}_{xNy}$ ）（ $x > y > 0$ ）又は窒化酸化シリコン（ $\text{SiN}_{xOy}$ ）（ $x > y > 0$ ）を単層又は積層して形成する。また、さらに、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル、エポキシ等の有機材料、シロキサン樹脂等のシロキサン材料、又はオキサゾール樹脂を積層して形成してもよい。

#### 【0053】

また、導電層204は、アルミニウム、タンクスチン、チタン、タンタル、モリブデン、ニッケル、ネオジムから選ばれた一種の元素または当該元素を複数含む合金からなる単層構造または積層構造を用いることができる。例えば、当該元素を複数含む合金からなる導電膜として、チタンを含有したアルミニウム合金、ネオジムを含有したアルミニウム合金などで形成することができる。また、積層構造で設ける場合、例えば、アルミニウム層若しくは前記したようなアルミニウム合金層を、チタン層で挟んで積層させた構造としても良い。

#### 【0054】

以上の工程により、薄膜トランジスタ205を含む半導体装置を作製することができる。

#### 【0055】

本実施の形態において、半導体膜の表面でエッチングを止める必要がないため、コンタク

10

20

30

40

50

トホール形成時のエッティングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるため、特性の劣化が抑えられた半導体装置を容易に作製することができる。

#### 【 0 0 5 6 】

また、半導体層のチャネル形成領域の端部に選択的に厚く絶縁層を設けてもよい。そうすることで、半導体層のチャネル形成領域の端部における電界集中を緩和することができる。従って、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

#### 【 0 0 5 7 】

(実施の形態 2 )

10

本実施の形態では、図 1 とは異なる半導体装置の構成及び作製方法について説明する。

#### 【 0 0 5 8 】

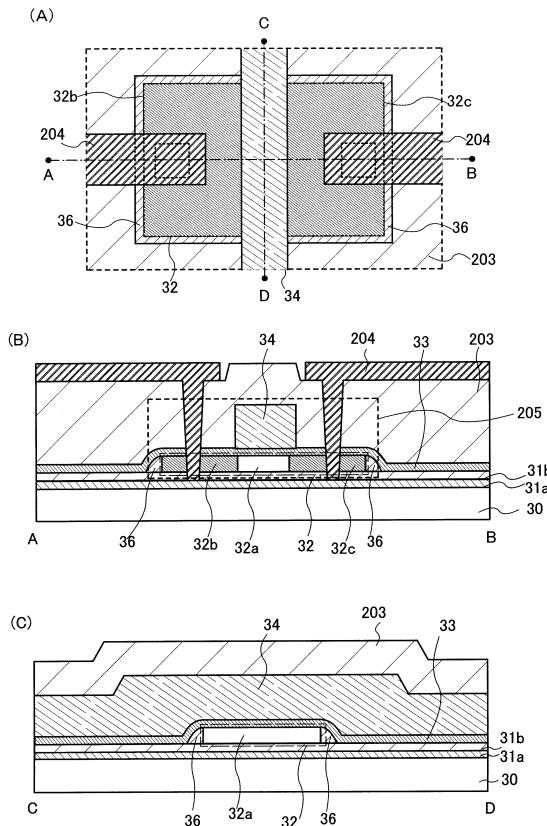

図 5 は本実施の形態に係る半導体装置の構成を説明するための上面図及び断面図である。図 5 ( A ) は、薄膜トランジスタの上面図を示し、図 5 ( B ) は図 5 ( A ) の A と B とを結ぶ破線における断面図を示し、図 5 ( C ) は図 5 ( A ) の C と D とを結ぶ破線における断面図を示している。

#### 【 0 0 5 9 】

本実施の形態に示す半導体装置は、基板 3 0 上に絶縁層 3 1 を介して島状に設けられた半導体層 3 2 と、半導体層 3 2 上に形成されたゲート絶縁層 3 3 と、半導体層 3 2 の上方にゲート絶縁層 3 3 を介して設けられたゲート電極として機能する導電層 3 4 と、を含む薄膜トランジスタ 2 0 5 と、ゲート絶縁層 3 3 及び導電層 3 4 を覆って設けられた絶縁層 2 0 3 と、絶縁層 2 0 3 上に設けられたソース電極又はドレイン電極として機能する導電層 2 0 4 とを有している(図 5 ( A ) ~ ( C ) )。なお、半導体層 3 2 は、チャネル形成領域 3 2 a とソース領域又はドレイン領域として機能する不純物領域 3 2 b 、 3 2 c とに加えて、半導体層 3 2 の端部、ここでは導電層 3 4 の下方のチャネル形成領域 3 2 a に接した部分に形成された絶縁層 3 6 とを有している。なお、チャネル形成領域 3 2 a 中に、不純物領域 3 2 b 、 3 2 c に添加した不純物とは逆の導電型の不純物が添加されていてよい。

#### 【 0 0 6 0 】

本実施の形態に示す半導体装置は、絶縁層 2 0 3 及び半導体層 3 2 の不純物領域 3 2 b 、 3 2 c 、絶縁層 3 1 b をエッティングして、絶縁層 3 1 a に達するコンタクトホールを形成し、該コンタクトホールを充填するように導電層 2 0 4 を形成している。つまり、本実施の形態において、導電層 2 0 4 と不純物領域 3 2 b 、 3 2 c とは、不純物領域 3 2 b 、 3 2 c に形成されたコンタクトホールの側面において電気的に接続されている。

#### 【 0 0 6 1 】

次に、図 5 ( A ) の A と B とを結ぶ破線での断面における作製工程を図 6 ( A ) ~ ( B ) を用いて、図 5 ( A ) の C と D とを結ぶ破線での断面における作製工程を図 6 ( C ) ~ ( D ) を用いて説明する。

#### 【 0 0 6 2 】

まず、実施の形態 1 と同様に、基板 3 0 上に絶縁層 3 1 a 、 3 1 b を形成し、絶縁層 3 1 b 上に半導体層 3 2 、絶縁層 3 6 及びゲート絶縁層 3 3 を形成し、ゲート絶縁層 3 3 上にゲート電極として機能する導電層 3 4 を形成し、導電層 3 4 上に絶縁層 2 0 3 を形成する(図 6 ( A ) 、 ( C ) )。ここで、絶縁層 2 0 3 上にはレジスト 2 0 7 が形成されている。

#### 【 0 0 6 3 】

続いて、レジスト 2 0 7 をマスクとして絶縁層 2 0 3 、ゲート絶縁層 3 3 、半導体層 3 2 、及び絶縁層 3 1 b をエッティングして、絶縁層 3 1 a に達するコンタクトホールを形成する(図 6 ( B ) 、 ( D ) )。

#### 【 0 0 6 4 】

続いて、レジスト 2 0 7 を除去する。以降の工程は、実施の形態 1 と同様にコンタクトホ

20

30

40

50

ールを充填するように導電層 204 を形成することによって図 5 に示す半導体装置を作製することができる。

【 0 0 6 5 】

本実施の形態において、半導体膜の表面でエッティングを止める必要がないため、コンタクトホール形成時のエッティングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。

【 0 0 6 6 】

また、半導体層のチャネル形成領域の端部に選択的に厚く絶縁層を設けてもよい。そうすることで、半導体層のチャネル形成領域の端部における電界集中を緩和することができる。従って、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。

10

【 0 0 6 7 】

( 実施の形態 3 )

本実施の形態では、図 1 又は図 5 とは異なる半導体装置の構成及び作製方法について説明する。

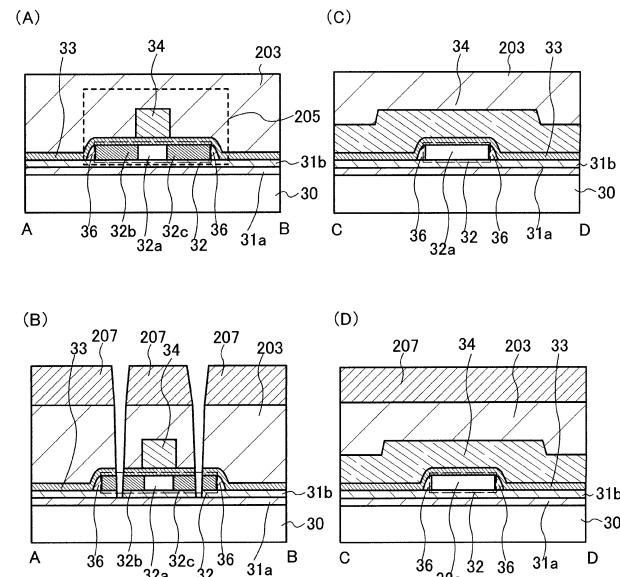

【 0 0 6 8 】

図 7 は本実施の形態に係る半導体装置の構成を説明するための上面図及び断面図である。図 7 ( A ) は、薄膜トランジスタの上面図を示し、図 7 ( B ) は図 7 ( A ) の A と B とを結ぶ破線における断面図を示し、図 7 ( C ) は図 7 ( A ) の C と D とを結ぶ破線における断面図を示している。

20

【 0 0 6 9 】

本実施の形態の半導体装置は図 7 に示すように、図 5 に示す構成と導電層 204 が充填されるコンタクトホールの形状が異なっている。つまり、本実施の形態に示す半導体装置において、絶縁層 203 、半導体層 32 の不純物領域 32b 、 32c 、絶縁層 31b をエッティングして形成された絶縁層 31a に達するコンタクトホールは、半導体層 32 の表面の一部 ( 不純物領域 32b 、 32c ) も露出するように形成されている。従って、本実施の形態において、導電層 204 と不純物領域 32b 、 32c とは、不純物領域 32b 、 32c に形成されたコンタクトホールの側面及び不純物領域 32b 、 32c の表面において電気的に接続されている。なお、本実施の形態において、絶縁層 31b にもコンタクトホールを形成しているが、絶縁層 31b にはコンタクトホールを形成せず、絶縁層 31b の表面が露出するようにコンタクトホールを形成してもよい。

30

【 0 0 7 0 】

次に、図 7 ( A ) の A と B とを結ぶ破線での断面における作製工程を図 8 ( A ) ~ ( C ) 、図 9 ( A ) ~ ( B ) を用いて、図 7 ( A ) の C と D とを結ぶ破線での断面における作製工程を図 8 ( D ) ~ ( F ) 、図 9 ( C ) ~ ( D ) を用いて説明する。

30

【 0 0 7 1 】

まず、実施の形態 1 と同様に、基板 30 上に絶縁層 31a 、 31b を形成し、絶縁層 31b 上に半導体層 32 、絶縁層 36 及びゲート絶縁層 33 を形成し、ゲート絶縁層 33 上にゲート電極として機能する導電層 34 を形成し、導電層 34 上に絶縁層 203 を形成する ( 図 8 ( A ) 、 ( D ) ) 。ここで、絶縁層 203 上にはレジスト 207 が形成されている。

40

【 0 0 7 2 】

次に、レジスト 207 をマスクとして絶縁層 203 、ゲート絶縁層 33 をドライエッティングして、半導体層 32 に達するコンタクトホールを形成する ( 図 8 ( B ) 、 ( E ) ) 。

【 0 0 7 3 】

次に、レジスト 207 をマスクとして、絶縁層 203 、ゲート絶縁層 33 をウェットエッティングして、絶縁層 203 、ゲート絶縁層 33 を外側に後退させる。

【 0 0 7 4 】

次に、レジスト 207 をマスクとして半導体層 32 及び絶縁層 31b をドライエッティング

50

して、絶縁層 3 1 a に達するコンタクトホールを形成する。これにより、不純物領域 3 2 b、3 2 c の側面及び不純物領域 3 2 b、3 2 c の表面の一部が露出するコンタクトホールを形成することができる。

【 0 0 7 5 】

以降の工程は、実施の形態 1 又は実施の形態 2 と同様にコンタクトホールを充填するように導電層 2 0 4 を形成することによって図 7 に示す半導体装置を作製することができる。

【 0 0 7 6 】

次に、図 8 ~ 9 に示した方法とは異なる作製方法について図 10 を用いて説明する。図 7 ( A ) の A と B とを結ぶ破線での断面における作製工程を図 10 ( A ) ~ ( C ) を用いて、図 7 ( A ) の C と D とを結ぶ破線での断面における作製工程を図 10 ( D ) ~ ( F ) を用いて説明する。10

【 0 0 7 7 】

まず、図 8 ( B )、( E ) と同様に、基板 3 0 上に絶縁層 3 1 a、3 1 b を形成し、絶縁層 3 1 b 上に半導体層 3 2 、絶縁層 3 6 及びゲート絶縁層 3 3 を形成し、ゲート絶縁層 3 3 上にゲート電極として機能する導電層 3 4 を形成し、導電層 3 4 上に絶縁層 2 0 3 を形成し、絶縁層 2 0 3 上に形成されたレジスト 2 0 7 をマスクとして絶縁層 2 0 3 及びゲート絶縁層 3 3 をドライエッチングしてコンタクトホールを形成する ( 図 10 ( A )、( D ) )。

【 0 0 7 8 】

次に、レジスト 2 0 7 をドライエッチングしてレジスト 2 0 7 を外側に後退させる ( 図 10 ( B )、( E ) )。次に、レジスト 2 0 7 をマスクとして、絶縁層 2 0 3 、ゲート絶縁層 3 3 、半導体層 3 2 、絶縁層 3 1 b をドライエッチングして、絶縁層 3 1 a を露出させるコンタクトホールを形成する ( 図 10 ( C )、( F ) )。これにより、不純物領域 3 2 b、3 2 c の側面及び不純物領域 3 2 b、3 2 c の表面の一部が露出するコンタクトホールを形成することができる。20

【 0 0 7 9 】

以降の工程は、実施の形態 1 と同様にコンタクトホールを充填するように導電層 2 0 4 を形成することによって図 7 に示す半導体装置を作製することができる。

【 0 0 8 0 】

本実施の形態において、半導体膜の表面でエッチングを止める必要がないため、コンタクトホール形成時のエッチングの制御を容易に行うことができる。また、絶縁層 2 0 3 と半導体層 3 2 とによって段差が形成されるため、コンタクトホールの側面における導電層 2 0 4 の被覆性が向上し、導電層 2 0 4 の膜厚のばらつきや導電層 2 0 4 の断線を防止することができ、コンタクト抵抗のばらつきを抑えることが可能となる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。30

【 0 0 8 1 】

また、半導体層のチャネル形成領域の端部に選択的に厚く絶縁層を設けてもよい。そうすることで、半導体層のチャネル形成領域の端部における電界集中を緩和することができる。従って、ゲートリーク不良を低減し、ゲート電極の耐圧を向上させることが可能となる。40

【 0 0 8 2 】

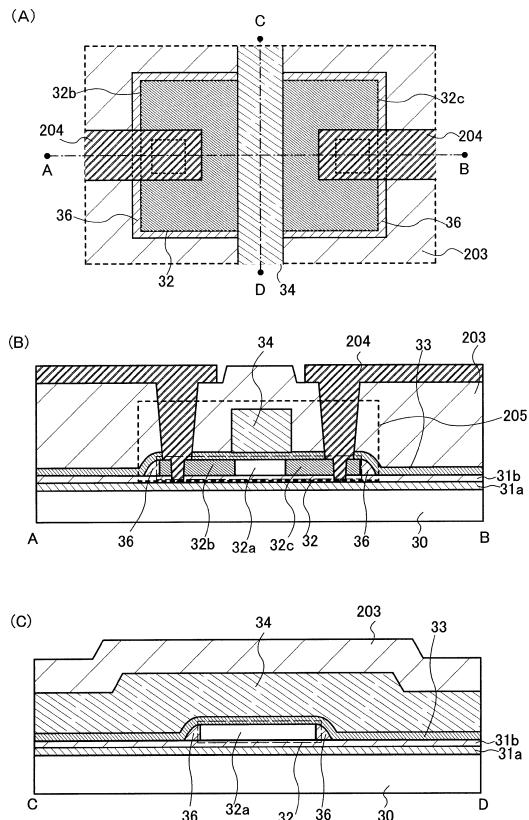

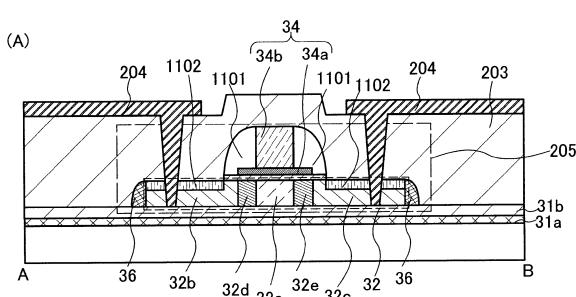

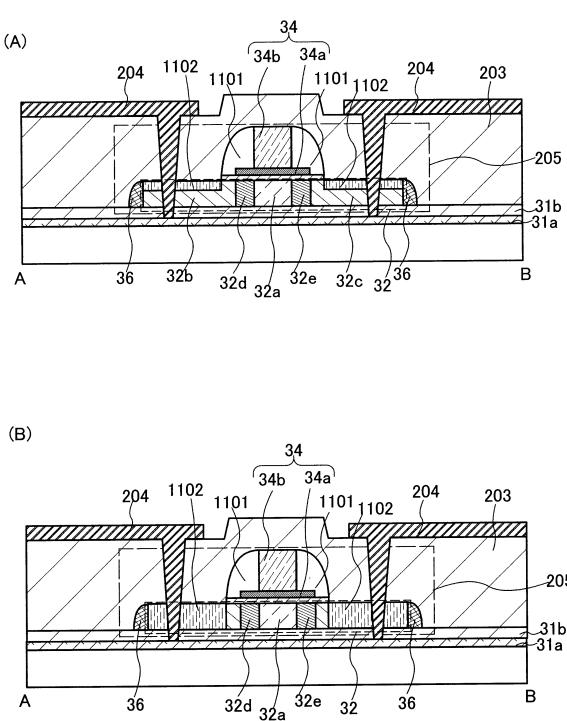

( 実施の形態 4 )

本発明に係る半導体装置は、実施の形態 1 ~ 3 に示した構成に限らず様々な形状をとることができる。本実施の形態では、半導体層を部分的にシリサイド化させた薄膜トランジスタの構成及び作製方法について説明する。図 11 に本実施の形態の半導体装置の構成を示す。図 11 ( A ) は上面図であり、図 11 ( B ) は図 11 ( A ) の破線 A B での断面図を示し、図 11 ( C ) は図 11 ( A ) の破線 C D での断面図を示す。

【 0 0 8 3 】

本実施の形態の半導体装置は、図11に示すように図1に示す構成に加えて半導体層32の表面の一部にシリサイド領域1102が形成されている。また、ゲート電極として機能する導電層34は、第1の導電層34aと第2の導電層34bとの積層構造で形成されており、導電層34の側壁に絶縁層（サイドウォール絶縁層ともいう）1101が形成されている。さらに、ソース領域又はドレイン領域として機能する不純物領域（高濃度不純物領域ともいう）32b、32cとチャネル形成領域32aとの間に、不純物領域32b、32cよりも低濃度に不純物が添加された領域（低濃度不純物領域ともいう）32d、32eが形成されている。

#### 【0084】

次に、図11に示す半導体装置の作製方法を説明する。

10

#### 【0085】

まず、実施の形態1と同様に、基板30上に絶縁層31a、31bを形成し、絶縁層31b上に半導体層32、絶縁層36及びゲート絶縁層33を形成し、ゲート絶縁層33上にゲート電極として機能する第1の導電層34a、第2の導電層34bを形成する（図12（A））。次に、導電層34bをマスクとした第1の濃度の一導電型を付与する不純物元素を添加した後、導電層34a及び導電層34bをマスクとした第2の濃度の不純物元素の添加を行って、自己整合的に一対の高濃度不純物領域32b、32cと、一対の低濃度不純物領域32d、32eと、チャネル形成領域32aを形成する。ここで、第1の濃度の不純物元素及び第2の濃度の不純物元素は、同じ導電型の不純物元素を添加し、例えばp型を付与する不純物元素であるボロン（B）、アルミニウム（Al）、ガリウム（Ga）、n型を付与する不純物元素であるリン（P）、ヒ素（As）等を添加することができる。

20

#### 【0086】

なお、チャネル形成領域32aにトランジスタの閾値電圧を制御するための一導電型を付与する不純物元素を添加してもよい。チャネル形成領域32aに対する不純物元素の添加は、導電層34を形成する前に行うことができる。また、一導電型を付与する不純物元素を添加した後、熱処理を行って添加した不純物元素を活性化してもよい。熱処理は、レーザビームの照射、又はRTA若しくはファーネスアニール炉を用いて行うことができ、400乃至700、好ましくは500乃至650の温度範囲で行えばよい。また、熱処理は窒素雰囲気下で行うことが好ましい。

30

#### 【0087】

次に、導電層34a及び導電層34bの側面と接するサイドウォール絶縁層1101を形成する（図12（B））。

#### 【0088】

サイドウォール絶縁層1101は、導電層34a及び導電層34b上に絶縁層を形成し、当該絶縁層を垂直方向を主体とした異方性エッチングにより選択的にエッチングすることにより形成することができる。例えば、CVD法やスパッタリング法により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の無機材料、有機樹脂などの有機材料を用いて単層構造又は積層構造の絶縁層を形成し、当該絶縁層を選択的にエッチングして形成することができる。サイドウォール絶縁層1101は、後にシリサイド領域を形成する際のシリサイド用マスクとして用いる。また、ここでは、サイドウォール絶縁層1101は、導電層34a、34bの側面と接しない面を湾曲状に形成している。なお、サイドウォール絶縁層1101は、ゲート電極を形成する導電層34a及び導電層34bの側面を完全に覆うように形成されている。

40

#### 【0089】

また、本実施の形態において、サイドウォール絶縁層1101を形成する際のエッチングにより下層の絶縁層33もエッチングして、半導体層32の一部を選択的に露出させていく。具体的にはサイドウォール絶縁層1101と重ならない領域の高濃度不純物領域32b、32cを露出させる。なお、エッチング条件によっては高濃度不純物領域32b、32cの上層もエッチングされて膜厚が減少する（膜減りといわれる）ことがある。

50

## 【0090】

次に、半導体層32の露出した面上に金属層1103を形成する(図12(C))。

## 【0091】

金属層1103は、少なくとも露出させた半導体層32上に形成すればよい。つまり、半導体層32においてサイドウォール絶縁層1101と重ならない領域に形成する。本実施の形態では、金属層1103は半導体層32の露出した面のみではなくサイドウォール絶縁層1101や導電層34も覆うように形成する。金属層1103は、半導体層と反応してシリサイドを形成する材料を用いて形成する。例えば、ニッケル(Ni)、チタン(Ti)、コバルト(Co)、又は白金(Pl)等の金属元素、又は当該金属元素を含む合金材料を用いることができる。金属層1103は、これらの材料を用いてスパッタリング法、蒸着法、めっき法等により形成する。なお、金属層1103の膜厚は、形成したいシリサイド領域の膜厚により適宜選択する必要がある。本実施の形態では、金属層1103として、膜厚10nmのニッケル層を形成する。なお、金属層1103を形成する際に、露出させた半導体層32上に自然酸化膜が形成されている場合は、自然酸化膜を除去してから金属層1103を形成するとよい。

10

## 【0092】

次に、半導体層32の一部にシリサイド領域1102を形成する(図12(D))。

## 【0093】

シリサイド領域1102は、熱処理を行うことにより、半導体層32及び金属層1103が接する領域が反応して形成される。また、シリサイド領域1102は、金属層1103が接する領域の半導体層32の一部がシリサイド化して形成される。このとき、半導体層32に形成された高濃度不純物領域32b、32cは、その一部がシリサイド化されて領域が減少する。なお、高濃度不純物領域の一部にシリサイド領域が形成されるともいえる。例えば、金属層1103としてニッケルを形成した場合はシリサイド領域1102としてニッケルシリサイドが形成される。同様に、金属層1103としてチタン、コバルト、又は白金を形成した場合は、それぞれシリサイド領域1102としてチタンシリサイド、コバルトシリサイド、白金シリサイドが形成される。

20

## 【0094】

熱処理は、RTA又はファーネスアニール炉を用いて行うことができる。具体的には、300乃至700の温度範囲で、10秒乃至1時間、好ましくは20秒乃至30分の範囲で行うとよい。本実施の形態では、55030秒の熱処理を行って、ニッケルシリサイドでなるシリサイド領域1102を形成する。

30

## 【0095】

図12(D)では、シリサイド領域1102を、半導体層32においてチャネル形成領域32aが形成されている領域の膜厚未満となるように形成する。つまり、サイドウォール絶縁層1101と重ならない領域の半導体層32において、該領域における半導体層32の絶縁層31bと接する側に高濃度不純物32b、32cが形成され、高濃度不純物32b、32cの上層に接してシリサイド領域1102が形成される。

## 【0096】

なお、シリサイド領域1102の形状、膜厚等は、反応させる金属層1103の膜厚、熱処理の温度、熱処理の時間等を適宜制御することにより、選択することができる。例えば、図13(B)に示すように、サイドウォール絶縁層1101と重ならない領域の半導体層32において、該領域における半導体層32の一部又は全体に、上面から下面までの全体をシリサイド化したシリサイド領域1102を形成してもよい。ここで上面とは半導体層32においてシリサイド化のための金属層が形成される面側であり、下面とは絶縁層31bと接する面側である。なお、上面から下面までの全体をシリサイド化する場合、サイドウォール絶縁層1101の下には高濃度不純物領域が形成されるようにする。なお、本発明は特に限定されず、シリサイド領域の一部が、サイドウォール絶縁層1101下の半導体層32(但し、チャネル形成領域32aは除く)まで形成されていてもよい。

40

## 【0097】

50

なお、半導体層 3 2 と金属層 1 1 0 3 とを反応させた後に未反応の金属層が残存する場合は未反応の金属層を除去する。ここでは、図示しないが絶縁層 3 6 、サイドウォール絶縁層 1 1 0 1 、導電層 3 4 b 及び絶縁層 3 1 b 上に形成された金属層 1 1 0 3 を除去する。また、形成されたシリサイド領域 1 1 0 2 上に未反応の金属層が残存する場合は、その残存する金属層も除去する。未反応の金属層除去は、ウェットエッチングやドライエッチングを用いることができる。このとき、エッチングガス又はエッチング溶液としては、未反応の金属層と他の層（例えば、絶縁層 3 6 、サイドウォール絶縁層 1 1 0 1 、導電層 3 4 b 、絶縁層 3 1 b 及びシリサイド領域 1 1 0 2 ）とのエッチング選択比が十分にとれるものを用いる。つまり、金属層に対するエッチングレートが高く、他の層に対するエッチングレートが低いものを用いればよい。例えば、金属層 1 1 0 3 としてニッケルを用いて形成した場合、塩酸（HCl）、硝酸（HNO<sub>3</sub>）及び純水（H<sub>2</sub>O）の混合溶液を用いたウェットエッチングにより除去することができる。例えば、溶液の混合比は、HCl : HNO<sub>3</sub> : H<sub>2</sub>O = 3 : 2 : 1 とすることができます。

10

#### 【0098】

なお、本実施の形態において、半導体層 3 2 端部の側面と接して絶縁層 3 6 が形成されているため、未反応の金属層をエッチング除去する際に、半導体層 3 2 の側面がエッチングされるのを防ぐことができる。

20

#### 【0099】

なお、シリサイド領域を形成する場合には、シリサイド領域及びゲート電極を形成する導電層とが接しないようにする必要がある。これは、シリサイド領域及びゲート電極が接してしまうと、ゲート電極と、ソース領域又はドレイン領域がショートしてスイッチング特性（オンオフ比）が取れなくなり、半導体装置として動作することができなくなるからである。したがって、本実施の形態では、ゲート電極を形成する導電層 3 4 a 、 3 4 b の幅をゲート絶縁層として機能する絶縁層 3 3 よりも狭くし、サイドウォール絶縁層 1 1 0 1 の端部を絶縁層 3 3 の端部と略一致するようにする。

20

#### 【0100】

次に、基板 3 0 上に設けられた絶縁層や導電層等を覆うように絶縁層 2 0 3 を形成する（図 1 3 ( A )）。

#### 【0101】

以降の工程は、実施の形態 1 と同様に絶縁層 2 0 3 及び半導体層 3 2 に、絶縁層 3 1 b に達するコンタクトホールを形成し、コンタクトホールを充填するように導電層 2 0 4 を形成することにより、図 1 1 又は図 1 3 ( A ) に示す半導体装置を作製することができる。

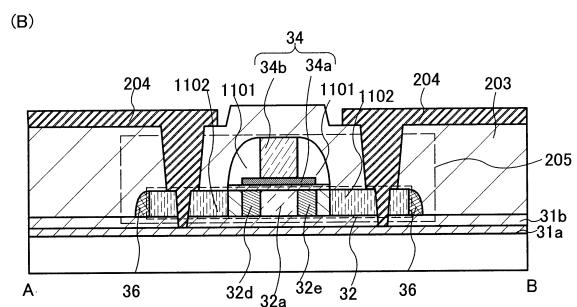

30

#### 【0102】

本実施の形態の半導体装置は、図 1 1 ~ 図 1 3 に示すものに限られず、図 1 4 ~ 図 1 5 に示すような形状としてもよい。

#### 【0103】

図 1 4 ( A ) に示す半導体装置は、図 1 3 ( A ) に示す構成と導電層 2 0 4 が充填されるコンタクトホールの形状が異なっている。つまり、図 1 4 ( A ) に示す半導体装置において、導電層 2 0 4 が充填されるコンタクトホールは、絶縁層 2 0 3 、半導体層 3 2 の不純物領域 3 2 b 、 3 2 c 、絶縁層 3 1 b をエッチングして形成された絶縁層 3 1 a に達するように形成されている。従って、本実施の形態において、導電層 2 0 4 と不純物領域 3 2 b 、 3 2 c とは、不純物領域 3 2 b 、 3 2 c に形成されたコンタクトホールの側面において電気的に接続されている。図 1 4 ( A ) に示すコンタクトホールは、実施の形態 3 と同様に行うことにより形成することができる。なお、図 1 4 ( A ) に示すものに限られず、図 1 4 ( B ) に示すように半導体層 3 2 の一部又は全体に、上面から下面までの全体をシリサイド化したシリサイド領域 1 1 0 2 を形成してもよい。

40

#### 【0104】

また、図 1 5 ( A ) に示す半導体装置は、図 1 3 ( A ) に示す構成と導電層 2 0 4 が充填されるコンタクトホールの形状が異なっている。つまり、本実施の形態に示す半導体装置において、絶縁層 2 0 3 、半導体層 3 2 の不純物領域 3 2 b 、 3 2 c 、絶縁層 3 1 b を工

50

ッチングして形成された絶縁層 3 1 a に達するコンタクトホールは、半導体層 3 2 の表面の一部（不純物領域 3 2 b、3 1 c）も露出するように形成されている。従って、本実施の形態において、導電層 2 0 4 と不純物領域 3 2 b、3 2 c とは、不純物領域 3 2 b、3 2 c に形成されたコンタクトホールの側面及び不純物領域 3 2 b、3 2 c の表面において電気的に接続されている。なお、本実施の形態において、絶縁層 3 1 b にもコンタクトホールを形成しているが、絶縁層 3 1 b にはコンタクトホールを形成せず、絶縁層 3 1 b の表面が露出するようにコンタクトホールを形成してもよい。図 15 (A) に示すコンタクトホールは、実施の形態 3 と同様に行うことにより形成することができる。なお、図 15 (A) に示すものに限らず、図 15 (B) に示すように半導体層 3 2 の一部又は全体に、上面から下面までの全体をシリサイド化したシリサイド領域 1 1 0 2 を形成してもよい。

10

#### 【 0 1 0 5 】

本実施の形態において、半導体膜の表面でエッチングを止める必要がないため、コンタクトホール形成時のエッチングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるため、特性の劣化が抑えられた半導体装置を容易に作製することができる。

#### 【 0 1 0 6 】

##### ( 実施の形態 5 )

実施の形態 1 ~ 4 で説明した半導体装置は、単結晶シリコン基板上に酸化シリコンでなる酸化膜を形成し、酸化膜上に形成された単結晶半導体薄膜を活性層として用いることができる。本実施の形態では、S I M O X と呼ばれる S O I 技術を用いた半導体装置について説明する。

20

#### 【 0 1 0 7 】

まず、単結晶シリコン層の形成材料となる単結晶シリコン基板 6 0 1 を用意する（図 16 (A)）。ここでは P 型の単結晶シリコン基板を用いる場合を説明するが N 型の単結晶シリコン基板であってもよい。もちろん、単結晶シリコンゲルマニウム基板を用いることもできる。

#### 【 0 1 0 8 】

続いて、単結晶シリコン基板 6 0 1 に対して酸素イオンを添加し、所定の深さに酸素含有層 6 0 2 を形成する（図 16 (B)）。酸素イオンは、例えば  $1 \times 1 0 1 8 \text{ atoms/cm}^2$  程度のドーズ量で添加すれば良い。なお、酸素含有層 6 0 2 が形成される深さ（単結晶シリコン基板 6 0 1 の主表面と酸素含有層 6 0 2 との間の距離）は、後に形成される T F T の活性層として機能する単結晶シリコン層の膜厚となる。

30

#### 【 0 1 0 9 】

次に、800 ~ 1200 の温度で熱処理を行い、酸素含有層 6 0 2 を埋め込み絶縁層 6 0 3 に変化させる。酸素含有層 6 0 2 の深さ方向の幅は、イオン添加時の酸素イオンの分布で決まっている。酸素イオンの濃度が単結晶シリコン基板 6 0 1 から酸素含有層 6 0 2 に向かって減少していくため、単結晶シリコン基板 6 0 1 と埋め込み絶縁層 6 0 3 との界面は不明確であるが、この熱処理工程により単結晶シリコン基板 6 0 1 と埋め込み絶縁層 6 0 3 との界面は明確なものとなる（図 16 (B)、(C)）。

40

#### 【 0 1 1 0 】

この埋め込み絶縁層 6 0 3 の膜厚は 10 ~ 500 nm（代表的には 20 ~ 50 nm）とする。本実施の形態では、単結晶シリコン基板 6 0 1 と埋め込み絶縁層 6 0 3 の界面が安定に接合されているため、20 ~ 50 nm といった薄い埋め込み絶縁層を形成することができる。

#### 【 0 1 1 1 】

こうして埋め込み絶縁層 6 0 3 が形成されると、埋め込み絶縁層 6 0 3 の上には部分的に単結晶シリコン基板の一部が残存し、単結晶シリコン層 6 0 4 が形成される。なお、単結晶シリコン層 6 0 4 の膜厚は 10 ~ 200 nm（好ましくは 10 ~ 50 nm、更に好ましくは 10 nm ~ 30 nm）となる様に、酸素含有層 6 0 2 が形成される深さを調節すれば

50

よい。

【0112】

次に、単結晶シリコン層604上に選択的にレジストを形成して、単結晶シリコン層604を選択的にエッティングすることにより、後に形成されるTFTの活性層となる島状の単結晶シリコン層605を形成する。なお、本実施の形態では一つの島状の単結晶シリコン層しか記載していないが、同一基板上に複数個が形成されていてもよい。(図16(D))

【0113】

以降の工程は、実施の形態1～4と同様に行うことにより、本発明に係る半導体装置を作製することができる。

【0114】

本実施の形態に係る半導体装置は、半導体膜の表面でエッティングを止める必要がないため、コンタクトホール形成時のエッティングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。また、本実施の形態に係る半導体装置は、活性層として単結晶半導体層を用いるため、更に特性を向上させることができる。

【0115】

(実施の形態6)

本実施の形態では、単結晶シリコン基板上に酸化シリコンでなる酸化膜を形成し、酸化膜上に形成された単結晶半導体薄膜を活性層として用いる半導体装置について説明する。本実施の形態では、Smart-Cut法を用いて形成されるSOI基板を用いた半導体装置について説明する。

【0116】

まず、単結晶シリコン層の形成材料となる単結晶シリコン基板801を用意する。ここではP型の単結晶シリコン基板を用いる場合を説明するがN型の単結晶シリコン基板であってもよい。もちろん、単結晶シリコンゲルマニウム基板を用いることもできる。

【0117】

次いで熱酸化処理を行い、その主表面(素子形成面に相当する)に酸化シリコン膜802を形成する。膜厚は実施者が適宜決定すれば良いが、10～500nm(代表的には20～50nm)とすれば良い。この酸化シリコン膜802は後にSOI基板の埋め込み絶縁層の一部として機能する(図17(A))。

【0118】

次に、単結晶シリコン基板801の主表面側から酸化シリコン膜802を通して水素イオンを添加して水素含有層803を形成する(図17(B))。なお、水素含有層803が形成される深さ(単結晶シリコン基板801の主表面と水素含有層803との間の距離)は、後にTFTの活性層として機能する単結晶シリコン層の膜厚となる。例えば、単結晶シリコン基板801の主表面と水素含有層803との間に50nm厚の単結晶シリコン層が残る様に、イオンインプランテーション法を用いて水素イオンを $1 \times 10^{16} \sim 1 \times 10^{17}$ atoms/cm<sup>2</sup>のドーズ量で添加することができる。

【0119】

次に、単結晶シリコン基板801と支持基板とを貼り合わせる。本実施の形態では支持基板として単結晶シリコン基板804を用い、その表面には貼り合わせ用の酸化シリコン膜805を設けておく(図17(C))。なお、単結晶シリコン基板804のかわりに、FZ法で形成されたシリコン基板、多結晶シリコン基板等を用いてもよい。また、石英基板、セラミックス基板、結晶化ガラス基板などの高耐熱性基板を用いてもよい。

【0120】

この時、貼り合わせ界面は親水性の高い酸化シリコン膜同士となるので、両表面に含まれた水分の反応により接着される。

【0121】

10

20

30

40

50

次に、400～600（例えば500）の熱処理（第1熱処理）を行う。この熱処理により水素含有層803では微小空孔の体積変化が起こり、水素含有層803に沿って破断面が発生する。これにより単結晶シリコン基板801は分断され、支持基板の上には酸化シリコン膜802と単結晶シリコン層806が残される（図17（D））。

【0122】

次に、第2熱処理工程として1050～1150（例えば1100）の温度範囲でファーネスアニール工程を行う。この工程では貼り合わせ界面において、Si-O-Si結合の応力緩和が起こり、貼り合わせ界面が安定化する。即ち、単結晶シリコン層806を支持基板上に完全に接着させるための工程となる。こうして貼り合わせ界面が安定化することで埋め込み絶縁層807が形成される（図17（E））。なお、本実施の形態では、水素含有層803を形成し、水素含有層803に沿って破断面を発生させて薄膜の単結晶シリコン層806を形成しているが、これに限られるものではなく、水素含有層803を設けずに単結晶シリコン基板801を研磨することにより薄膜の単結晶シリコン層806を形成してもよい。

10

【0123】

次に、単結晶シリコン層806の表面を平坦化する処理を行ってもよい。平坦化にはCMP（ケミカルメカニカルポリッシング）と呼ばれる研磨工程や還元雰囲気中で高温（900～1200程度）のファーネスアニール処理を行えば良い。

【0124】

最終的な単結晶シリコン層806の膜厚は10～200nm（好ましくは10～50nm、更に好ましくは10nm～30nm）とすれば良い。

20

【0125】

次に、単結晶シリコン層806上に選択的にレジストを形成して、単結晶シリコン層806を選択的にエッチングすることにより、後に形成されるTFTの活性層となる島状の単結晶シリコン層808を形成する。なお、本実施の形態では一つの島状の単結晶シリコン層しか記載していないが、同一基板上に複数の島状の単結晶シリコン層が形成されていてもよい。（図17（F））

【0126】

以降の工程は、実施の形態1～4と同様に行うことにより、本発明に係る半導体装置を作製することができる。

30

【0127】

本実施の形態に係る半導体装置は、半導体膜の表面でエッチングを止める必要がないため、コンタクトホール形成時のエッチングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。また、本実施の形態に係る半導体装置は、活性層として単結晶半導体層を用いるため、更に特性を向上させることができる。

【0128】

（実施の形態7）

本実施の形態では、実施の形態1で説明した半導体装置とエレクトロルミネッセンス素子（以下、「EL素子」ともいう。）を有する表示装置（EL表示装置）を作製する方法について説明する。なお、本実施の形態において用いることが可能な半導体装置は実施の形態1に示すものに限られず、実施の形態2～6で説明した半導体装置を用いてもよい。

40

【0129】

本実施の形態では、エレクトロルミネッセンス素子からの光を第1の電極110側から取り出す構造にするため、透光性を有する膜を用いて第1の電極110を形成する。本実施の形態では、酸化珪素を含む酸化インジウムスズ（ITO）を第1の電極110として用いる。

【0130】

まず、図18に示すように、実施の形態1と同様にTFT1701～1703と、TFT

50

1701～1703を覆う絶縁層1710と、TFT1701～1703のソース領域又はドレイン領域と電気的に接続する配線1704～1709を形成する。次に、配線1704～1709を覆うように絶縁層109を形成し、絶縁層109上に配線1709と電気的に接続する第1の電極110を形成する。次に、第1の電極110の端部及び絶縁層109を覆うように絶縁膜111(バンク、隔壁、障壁、土手などとも呼ばれる。)を形成する。

#### 【0131】

絶縁膜111としては、酸化珪素、窒化珪素、酸化窒化珪素、酸化アルミニウム、窒化アルミニウム、酸窒化アルミニウムその他の無機絶縁性材料、又はアクリル酸、メタクリル酸及びこれらの誘導体、又はポリイミド(polyimide)、芳香族ポリアミド、ポリベンゾイミダゾール(polybenzimidazole)などの耐熱性高分子、又は珪素、酸素、水素からなる化合物のうちSi-O-Si結合を含む無機シロキサン、珪素に結合されている水素がメチルやフェニルのような有機基に置換された有機シロキサン系の絶縁性材料を用いることができる。アクリル、ポリイミド等の感光性、非感光性の材料を用いて形成してもよい。本実施の形態では、感光性ポリイミドを用いて、平坦な領域で膜厚が1.5μmとなるように絶縁膜111を形成する。

#### 【0132】

また、絶縁膜111は曲率半径が連続的に変化する形状が好ましく、絶縁膜111上に形成される電界発光層112(有機化合物を含む層)、第2の電極113の被覆性を向上させることができる。

#### 【0133】

また、信頼性をさらに向上させるために、電界発光層112を形成する前に第1の電極110及び絶縁膜111に対して、高密度プラズマ装置を用いて窒化処理又は酸化処理を行うとよい。第1の電極110を高密度プラズマ装置を用いて窒化又は酸化することで、電極の表面改質の際のプラズマダメージが少なく、より欠陥の少ない表面を得ることができるので、本実施の形態の発光素子による表示は高精細で表示ムラが少ない。さらに、絶縁膜111を窒化した場合、絶縁膜111の表面が改質され、絶縁膜内部への水分の吸収を抑えることができる。また、絶縁膜111を酸化した場合、膜が強固になり、有機ガスの放出を抑えることができる。本実施の形態では、高密度プラズマ装置を用いることでプラズマダメージの少ない処理を行うことが可能である。ここで、絶縁膜111表面に対して、酸化処理を行うか、窒化処理を行うかは絶縁膜の材料及び効果を考えて適宜選択すればよい。

#### 【0134】

次に、第1の電極110上に電界発光層112を形成する。なお、図18では1画素しか図示していないが、本実施の形態では赤(R)、緑(G)、青(B)の各色に対応した電界発光層を作り分けている。本実施の形態では電界発光層112として、赤(R)、緑(G)、青(B)の発光を示す材料を、蒸着マスクを用いた蒸着法によって、それぞれ選択的に形成する。赤色(R)、緑色(G)、青色(B)の発光を示す材料は、蒸着マスクを用いた蒸着法によってそれぞれ選択的に形成する方法や、液滴吐出法により形成することができる。液滴吐出法の場合、マスクを用いずにRGBの塗り分けを行うことができるという利点がある。本実施の形態では、赤(R)、緑(G)、青(B)の発光を示す材料を蒸着法によってそれぞれ形成する。

#### 【0135】

なお、ELの蒸着前に、不活性ガスを主成分とし、酸素の濃度が5%以下且つ水の濃度が1%以下とする雰囲気で加熱処理を行い、水分などを除去することが好ましい。本実施の形態では、300℃で1時間加熱処理を行う。

#### 【0136】

次に、電界発光層112の上に導電膜からなる第2の電極113を形成する。第2の電極113としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれらの合金MgAg、MgIn、AlLi、CaF<sub>2</sub>、または窒化カルシウム)を用いればよい。こ

10

20

30

40

50

うして第1の電極110、電界発光層112及び第2の電極113からなる発光素子が形成される。

#### 【0137】

図18に示す表示装置において、発光素子から発した光は、基板101と第1の電極110の間に形成された膜を透過して第1の電極110側から矢印の方向に射出される。

#### 【0138】

また、第2の電極113を覆うようにしてパッシベーション膜を設けることは有効である。パッシベーション膜としては、窒化珪素、酸化珪素、酸化窒化珪素(SiON)、窒化酸化珪素(SiNO)、窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイヤモンドライクカーボン(DLC)、窒素含有炭素膜(CN)を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層を用いることができる。また、シリコン(Si)と酸素(O)との結合で骨格構造が構成されるシロキサンを用いてもよい。シロキサンは、置換基として少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。また、置換基としてフルオロ基、又は少なくとも水素を含む有機基とフルオロ基とを用いてもよい。

#### 【0139】

この際、カバレッジの良い膜をパッシベーション膜として用いることが好ましく、炭素膜、特にDLC膜を用いることは有効である。DLC膜は室温から100以下の温度範囲で成膜可能であるため、耐熱性の低い電界発光層112の上方にも容易に成膜することができる。また、DLC膜は酸素に対するブロッキング効果が高く、電界発光層112の酸化を抑制することができる。そのため、この後に続く封止工程を行う間に電界発光層112が酸化するといった問題を防止することができる。

#### 【0140】

次に、発光素子が形成された基板101と、封止基板とをシール材によって固着し、発光素子を封止する。断面からの水分の侵入がシール材によって遮断されるので、発光素子の劣化が防止でき、表示装置の信頼性が向上する。なお、シール材で囲まれた領域には充填材を充填してもよく、窒素雰囲気下で封止することによって、窒素等を封入してもよい。また充填材は、液状の状態で滴下し、表示装置内に充填することもできる。本実施の形態は、下面射出型のため、透光性を有する充填材を使用する必要はないが、充填材を透過して光を取り出す構造の場合は、透光性を有する材料を用いて充填材を形成する必要がある。充填材の一例としては、可視光硬化、紫外線硬化または熱硬化のエポキシ樹脂が挙げられる。以上の工程において、発光素子を有する表示装置が完成する。

#### 【0141】

また、素子の水分による劣化を防ぐためにEL表示パネル内に乾燥剤を設置することが好ましい。本実施の形態では、画素領域を取り囲むように封止基板に形成された凹部に乾燥剤を設置し、薄型化を妨げない構成とする。また、ゲート配線層に対応する領域にも乾燥剤を設置することにより吸水面積を広く取ることができ、吸水効果が高い。また、直接発光しないゲート配線層上に乾燥剤を形成しているので、光取り出し効率を低下させることもない。

#### 【0142】

なお、発光素子を封止する処理とは、発光素子を水分から保護するための処理であり、カバー材で機械的に封入する方法、熱硬化性樹脂又は紫外光硬化性樹脂で封入する方法、金属酸化物や窒化物等のバリア能力が高い薄膜により封止する方法のいずれかを用いる。封止基板又はカバー材としては、ガラス、セラミックス、プラスチックもしくは金属を用いることができるが、カバー材側に光を放射させる場合は透光性でなければならない。また、カバー材と上記発光素子が形成された基板とは熱硬化性樹脂又は紫外光硬化性樹脂等のシール材を用いて貼り合わせられ、熱処理又は紫外光照射処理によって樹脂を硬化させて密閉空間を形成する。この密閉空間の中に酸化バリウムに代表される吸湿材を設けることも有効である。この吸湿材は、シール材の上に接して設けても良いし、発光素子よりの光

10

20

30

40

50

を妨げないような、隔壁の上や周辺部に設けても良い。さらに、カバー材と発光素子の形成された基板との空間を熱硬化性樹脂若しくは紫外光硬化性樹脂で充填することも可能である。この場合、熱硬化性樹脂若しくは紫外光硬化性樹脂の中に酸化バリウムに代表される吸湿材を添加しておくことは有効である。

【0143】

本実施の形態で示すTFT1701～1703は実施の形態1～6のいずれかの方法で作製されており、半導体膜の表面でエッティングを止める必要がないため、コンタクトホール形成時のエッティングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。従って、特性のよいEL表示装置を容易に作製することができる。

【0144】

(実施の形態8)

本実施の形態では、実施の形態1で作製した半導体装置を用いて、透過型液晶表示装置を作製する方法について説明する。もちろん、実施の形態2～6で作製した半導体装置を用いることもできる。

【0145】

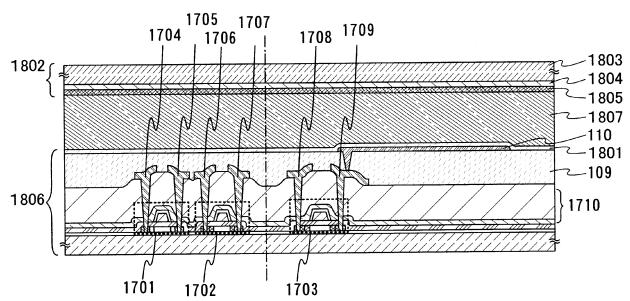

まず、実施の形態1と同様にTFT1701～1703と、TFT1701～1703を覆う絶縁層1710と、TFT1701～1703のソース領域又はドレイン領域と電気的に接続する配線1704～1709を形成する(図19)。次に、配線1704～1709を覆うように絶縁層109を形成し、絶縁層109上に配線1709と電気的に接続する第1の電極110を形成する。本実施の形態では、第1の電極110の材料として、酸化珪素を含む酸化インジウムスズ(ITSO)を用いる。次に、図19に示すように、絶縁層109及び第1の電極110上に配向膜1801を形成する。本実施の形態では、配向膜1801にポリイミドを用いた。次に対向基板1802を用意する。対向基板1802は、ガラス基板1803、透明導電膜からなる対向電極1804、配向膜1805などで構成される。

【0146】

次に、上記工程により得たTFT基板1806と対向基板1802とをシール材を介して貼り合わせる。ここで、両基板の間隔を一定に保つために、配向膜1801と配向膜1805との間にスペーサを設けても良い。その後、両基板の間に液晶1807を注入し、封止材によって封止することで図19に示すような透過型液晶表示装置が完成する。

【0147】

なお、本実施の形態においては透過型の液晶表示装置について説明したが、本発明の液晶表示装置はこれに限定されない。第1の電極110として反射性を有する電極を用いたり、第1の電極110の上面又は下面に反射膜を設けることで、反射型液晶表示装置に用いることができる。また、半透過型液晶表示装置に用いてもよい。

【0148】

本実施の形態で示すTFT1701～1703は実施の形態1～6のいずれかの方法で作製されており、半導体膜の表面でエッティングを止める必要がないため、コンタクトホール形成時のエッティングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。従って、特性のよい液晶表示装置を容易に作製することができる。

【0149】

(実施の形態9)

本実施の形態では、実施の形態1～6で説明した薄膜トランジスタ、記憶素子およびアンテナを含む本発明の半導体装置の作製方法について、図面を参照して説明する。

【0150】

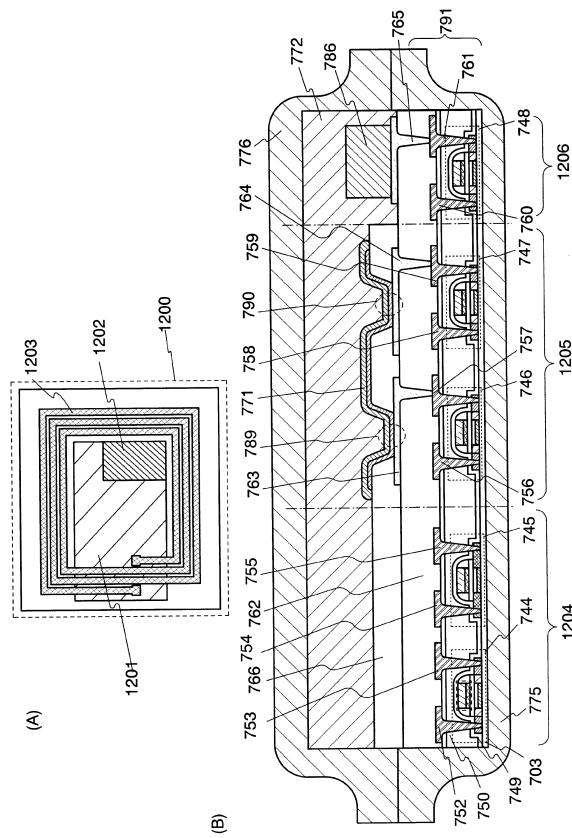

本実施の形態で示す半導体装置を図20に示す。なお、図20(A)は本実施の形態で示

10

20

30

40

50

す半導体装置の上面構造の一例を示し、図20(A)の断面構造の一部を図20(B)に示している。

【0151】

本実施の形態において、半導体装置1200は集積回路部1201、メモリ部1202、アンテナ1203を有している(図20(A))。なお、図20(B)において、領域1204は図20(A)の集積回路部1201の断面構造の一部に対応し、領域1205は図20(A)のメモリ部1202の断面構造の一部に対応し、領域1206は図20(A)のアンテナ1203の断面構造の一部に対応している。

【0152】

本実施の形態の半導体装置は、図20(B)に示すように第1の基体775上に絶縁層703を介して設けられた薄膜トランジスタ(TFT)744～748と、薄膜トランジスタ744～748上に設けられた絶縁膜750と、当該絶縁膜750上に設けられたソース電極又はドレイン電極として機能する導電膜752～761とを有する。また、絶縁膜750及び導電膜752～761上に設けられた絶縁膜762と、絶縁膜762上に設けられた導電膜763～765と、絶縁膜762及び導電膜763～764の一部を覆うように設けられた絶縁膜766と、絶縁膜766上に設けられた記憶素子部789、790と、導電膜765上に設けられたアンテナとして機能する導電層786と、絶縁膜766、導電膜771及びアンテナとして機能する導電層786を覆うように設けられた絶縁膜772と、絶縁膜772上に設けられた第2の基体776を有している。なお、第1の基体775及び第2の基体776とによって、半導体装置の集積回路部1201、メモリ部1202、アンテナ1203は封止されている。

【0153】

本実施の形態で示す薄膜トランジスタ744～748は実施の形態1～6のいずれかの方法で作製されており、半導体膜の表面でエッチングを止める必要がないため、コンタクトホール形成時のエッチングの制御を容易に行うことができる。また、半導体層に形成されたコンタクトホールの側面においてソース電極又はドレイン電極と電気的な接続をとることができるために、特性の劣化が抑えられた半導体装置を容易に作製することができる。従って、特性のよい無線通信可能な半導体装置を容易に作製することができる。

【符号の説明】

【0154】

- 30 基板

- 31 絶縁層

- 32 半導体層

- 33 ゲート絶縁層

- 34 導電層

- 36 絶縁層

- 203 絶縁層

- 204 導電層

- 205 薄膜トランジスタ

- 32a チャネル形成領域

- 32b 不純物領域

- 32c 不純物領域

30

40

50

## 【図面】

## 【図1】

## 【図2】

10

20

30

40

50

【図3】

【図4】

10

20

30

40

【図5】

【図6】

50

【 四 7 】

【 四 8 】

【図9】

【 図 1 0 】

【図11】

【図12】

【図13】

【図14】

10

20

30

40

50

【図15】

【図16】

10

20

30

40

50

【図17】

【図18】

10

20

30

40

50

【図19】

【図20】

10

20

30

40

50

【図21】

**【手続補正書】**

【提出日】令和5年5月11日(2023.5.11)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

基板上に位置し、且つ窒化シリコンを有する第1の絶縁層と、

前記第1の絶縁層上に位置する領域を有し、且つ酸化シリコンを有する第2の絶縁層と、

前記第2の絶縁層の上面と接する領域を有し、且つトランジスタのチャネル形成領域を有する半導体膜と、

前記半導体膜の上面と接する領域を有し、且つ酸化シリコンを有する第3の絶縁層と、

前記第3の絶縁層上に位置し、且つ前記トランジスタのゲート電極として機能する領域を有する第1の導電層と、

前記第1の導電層上に位置する領域を有し且つ酸化シリコン、酸化窒化シリコン又は窒化酸化シリコンを有する第4の絶縁層と、

前記第4の絶縁層上に位置する領域を有する第2の導電層と、を有し、

少なくとも前記第4の絶縁層と、前記第3の絶縁層と、前記半導体膜と、を貫通する一のコンタクトホールを有し、

前記第2の導電層は、前記コンタクトホールの内側において、前記半導体膜と接する領域を有し、

断面視において、前記第2の導電層の下面是、前記コンタクトホールの内側に位置し且つ前記半導体膜の下面よりも前記基板側に位置する領域を有し、

前記コンタクトホールの内側における前記半導体膜の端面は、前記基板の上面に対して第1の傾斜角で傾斜する領域を有し、

前記コンタクトホールの内側における前記第2の絶縁層の端面は、前記基板の上面に対して前記第1の傾斜角で傾斜する領域を有し、

前記第1の傾斜角は、90°未満である、半導体装置。

**【請求項2】**

基板上に位置し、且つ窒化シリコンを有する第1の絶縁層と、

前記第1の絶縁層上に位置する領域を有し、且つ酸化シリコンを有する第2の絶縁層と、

前記第2の絶縁層の上面と接する領域を有し、且つトランジスタのチャネル形成領域を有する半導体膜と、

前記半導体膜の上面と接する領域を有し、且つ酸化シリコンを有する第3の絶縁層と、

前記第3の絶縁層上に位置し、且つ前記トランジスタのゲート電極として機能する領域を有する第1の導電層と、

前記第1の導電層上に位置する領域を有し且つ酸化シリコン、酸化窒化シリコン又は窒化酸化シリコンを有する第4の絶縁層と、

前記第4の絶縁層上に位置する領域を有する第2の導電層と、を有し、

少なくとも前記第4の絶縁層と、前記第3の絶縁層と、前記半導体膜と、を貫通する一のコンタクトホールを有し、

前記第2の導電層は、前記コンタクトホールの内側において、前記半導体膜と接する領域を有し、

断面視において、前記第2の導電層の下面是、前記コンタクトホールの内側に位置し且つ前記半導体膜の下面よりも前記基板側に位置する領域を有し、

前記コンタクトホールの内側における前記半導体膜の端面は、前記基板の上面に対して第1の傾斜角で傾斜する領域を有し、

前記コンタクトホールの内側における前記第2の絶縁層の端面は、前記基板の上面に対し

10

20

30

40

50

て前記第1の傾斜角で傾斜する領域を有し、

前記第1の傾斜角は、90°未満であり、

前記コンタクトホールの内側において、前記半導体膜の上端部は、前記第3の絶縁層と接する領域を有する、半導体装置。

【請求項3】

請求項1又は2において、

前記第4の絶縁層は、積層構造を有する、半導体装置。

10

20

30

40

50

---

フロントページの続き

(51)国際特許分類

F I

H 01 L

29/50

M