## ITALIAN PATENT OFFICE

Document No.

102012902087549A1

**Publication Date**

20140327

**Applicant**

STMICROELECTRONICS S.R.L.

## Title

INTERFACCIA DI RACCOLTA DI ENERGIA CON EFFICIENZA MIGLIORATA, METODO PER OPERARE L'INTERFACCIA DI RACCOLTA DI ENERGIA, E SISTEMA DI RACCOLTA DI ENERGIA COMPRENDENTE L'INTERFACCIA DI RACCOLTA DI ENERGIA

## DESCRIZIONE

del brevetto per invenzione industriale dal titolo: "INTERFACCIA DI RACCOLTA DI ENERGIA CON EFFICIENZA MIGLIORATA, METODO PER OPERARE L'INTERFACCIA DI RACCOLTA DI ENERGIA, E SISTEMA DI RACCOLTA DI ENERGIA COMPRENDENTE L'INTERFACCIA DI RACCOLTA DI ENERGIA"

di STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

Inventori: RAMORINI Stefano, GASPARINI Alessandro, CATTANI Alberto

\* \* \*

La presente invenzione è relativa ad una interfaccia di raccolta di energia con efficienza migliorata, ad un metodo per operare l'interfaccia di raccolta di energia, e ad un sistema di raccolta di energia comprendente l'interfaccia di raccolta di energia. In particolare è relativa ad una interfaccia di raccolta di energia includente un circuito rettificatore.

La presente invenzione è inoltre relativa ad un apparecchio (ad esempio un veicolo o una calzatura) comprendente il sistema di raccolta di energia.

Come noto, sistemi per la raccolta di energia (anche noti come sistemi di "energy harvesting" o "energy scavenging") da fonti energetiche ambientali hanno suscitato e suscitano notevole interesse in svariati campi

della tecnologia. Tipicamente, i sistemi di raccolta di energia sono atti a raccogliere ("harvest"), accumulare ("store"), e trasferire energia generata da sorgenti meccaniche ad un generico carico di tipo elettrico.

Vibrazioni a bassa frequenza, come ad esempio vibrazioni meccaniche di disturbo in sistemi con parti in movimento possono essere una valida sorgente di energia. L'energia meccanica è convertita, da uno o più opportuni trasduttori (ad esempio dispositivi piezoelettrici o elettromagnetici) in energia elettrica, che può essere utilizzata per alimentare un carico elettrico. In questo modo, il carico elettrico non necessita di batterie o altri sistemi di alimentazione ingombranti e scarsamente resistenti a stress meccanici.

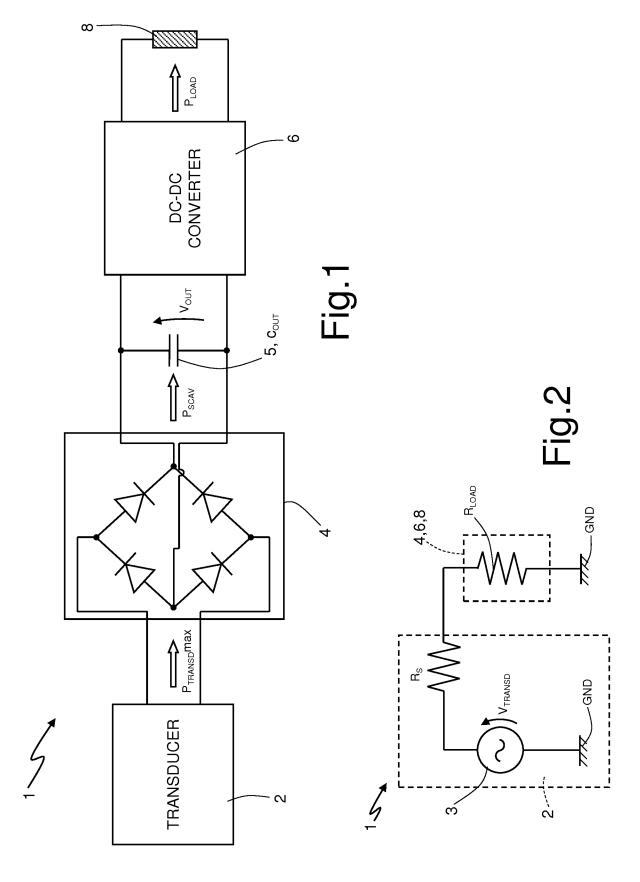

La figura 1 mostra, in forma schematica mediante blocchi funzionali, un sistema di raccolta di energia di tipo noto.

Il sistema di raccolta di energia ("energy harvesting system") 1 di figura 1 comprende un trasduttore 2, ad esempio di tipo elettromagnetico o piezoelettrico, soggetto durante l'uso a vibrazioni meccaniche ambientali e configurato per convertire energia meccanica in energia elettrica, tipicamente in tensioni AC (corrente alternata); un'interfaccia di raccolta ("scavenging interface") 4, ad esempio comprendente un circuito rettificatore a ponte di

(anche noto come ponte di Gretz), configurata per ricevere in ingresso il segnale in AC generato trasduttore 2 e fornire in uscita un segnale DC per caricare un (corrente continua) condensatore collegato sull'uscita del circuito rettificatore 4; e un convertitore DC-DC 6, collegato al condensatore 5 per ricevere in ingresso l'energia elettrica immagazzinata dal condensatore 5 e fornirla ad un carico elettrico 8. condensatore 5 ha dunque la funzione di elemento immagazzinamento di energia, che viene resa disponibile, al carico elettrico quando richiesto, 8 per il funzionamento di quest'ultimo.

L'efficienza globale  $\eta_{\text{TOT}}$  del sistema di raccolta di energia 1 è data dalla formula (1):

$$\eta_{\text{TOT}} = \eta_{\text{TRASD}} \cdot \eta_{\text{SCAV}} \cdot \eta_{\text{DCDC}} \tag{1}$$

l'efficienza dove  $\eta_{\mathrm{TRASD}}$ è del trasduttore 2, indicativa della quantità di energia disponibile nell'ambiente effettivamente convertita, dal trasduttore 2, in energia elettrica;  $\eta_{ ext{SCAV}}$  è l'efficienza dell'interfaccia di raccolta 4, indicativa dell'energia consumata dall'interfaccia di raccolta 4 e del fattore di accoppiamento  $\eta_{\text{COUPLE}}$  tra trasduttore 2 ed interfaccia di raccolta 4 (indicativo dell'adattamento di impedenza tra trasduttore 2 ed interfaccia di raccolta 4); e  $\eta_{DCDC}$  è l'efficienza del convertitore DC-DC 6.

Come noto, al fine di fornire al carico la massima potenza disponibile, l'impedenza del carico dovrebbe essere uguale a quella della sorgente. Come mostrato in figura 2, il trasduttore 2 può essere schematizzato, in questo contesto, come un generatore di tensione 3 provvisto di una propria resistenza  $R_{\rm S}$ . La massima potenza  $P_{\rm TRASD}^{\rm MAX}$  che il trasduttore 2 può fornire in uscita può essere definita come:

$$P_{\text{TRASD}}^{\text{MAX}} = V_{\text{TRASD}}^2 / 4R_{\text{S}}$$

se  $R_{\text{LOAD}} = R_{\text{S}}$  (2)

dove  $V_{TRASD}$  è la tensione fornita dal generatore di tensione equivalente; e  $R_{LOAD}$  è la resistenza elettrica equivalente sull'uscita del trasduttore 2 (o, analogamente, vista in ingresso all'interfaccia di raccolta 4), che tiene in dovuta considerazione la resistenza equivalente dell'interfaccia di raccolta 4, del convertitore DC-DC 6 e del carico 8.

A causa del disaccoppiamento d'impedenza ( $R_{LOAD} \neq R_S$ ), la potenza in ingresso all'interfaccia di raccolta 4 è inferiore alla potenza massima disponibile  $P_{TRASD}^{MAX}$ .

La potenza  $P_{\text{SCAV}}$  è fornita in uscita dall'interfaccia di raccolta ed è data dalla formula (3):

$$P_{SCAV} = \eta_{TRASD} \cdot \eta_{SCAV} \cdot P_{TRASD}^{MAX}$$

(3)

La potenza richiesta al convertitore DC-DC 6 per alimentare il carico elettrico 8 è data dalla seguente formula (4):

dove  $P_{DCDC}$  è la potenza ricevuta in ingresso dal convertitore DC-DC 8, in questo caso coincidente con  $P_{SCAV}$ , e  $P_{LOAD}$  è la potenza richiesta dal carico elettrico.

L'efficienza del sistema 1 di figura 1 è fortemente dipendente dal segnale generato dal trasduttore 2. L'efficienza scende rapidamente al valore zero (cioè il sistema 1 non è in grado di raccogliere energia ambientale) quando l'ampiezza del segnale del trasduttore 2 (segnale  $V_{\text{TRASD}}$ ) assume un valore inferiore, in valore assoluto, a  $V_{OUT}+2V_{TH}$  , dove  $V_{OUT}$  è la tensione accumulata sul condensatore 5, e  $V_{\text{TH D}}$  è la tensione di soglia dei diodi che formano l'interfaccia di raccolta 4. Come consequenza di questo, la massima energia che può essere immagazzinata 5 è nel condensatore limitata al valore  $E_{\text{max}} = 0.5 \cdot C_{\text{OUT}} \cdot (V_{\text{TRASD}}^{\text{MAX}} - 2V_{\text{TH D}})^2$ . Se l'ampiezza del segnale  $V_{\text{TRASD}}$ del trasduttore 2 è inferiore al doppio della tensione di soglia V<sub>TH D</sub> dei diodi del rettificatore dell'interfaccia di raccolta 4 (cioè  $V_{TRASD}$ <2 $V_{TH\ D}$ ), allora l'efficienza del sistema 1 è zero, la tensione accumulata sul condensatore di uscita 5 è nulla, l'energia ambientale non viene raccolta e il carico elettrico 8 non viene alimentato.

Scopo della presente invenzione è quello di fornire una interfaccia di raccolta di energia con efficienza migliorata, un metodo per operare l'interfaccia di raccolta

di energia, un sistema di raccolta di energia comprendente l'interfaccia di raccolta di energia, e un apparecchio comprendente il sistema di raccolta di energia che consentano di superare i succitati problemi e svantaggi, ed in particolare che abbiano elevata efficienza.

Secondo la presente invenzione vengono pertanto forniti ("provided") una interfaccia di raccolta di energia con efficienza migliorata, un metodo per operare l'interfaccia di raccolta di energia, un sistema di raccolta di energia comprendente l'interfaccia di raccolta di energia, e un apparecchio comprendente il sistema di raccolta di energia, come definiti nelle rivendicazioni allegate.

Per una migliore comprensione della presente invenzione, ne vengono ora descritte forme di realizzazione preferite, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

- la figura 1 mostra un sistema di raccolta di energia secondo una forma di realizzazione nota;

- la figura 2 mostra un circuito equivalente al sistema di raccolta di energia di figura 1;

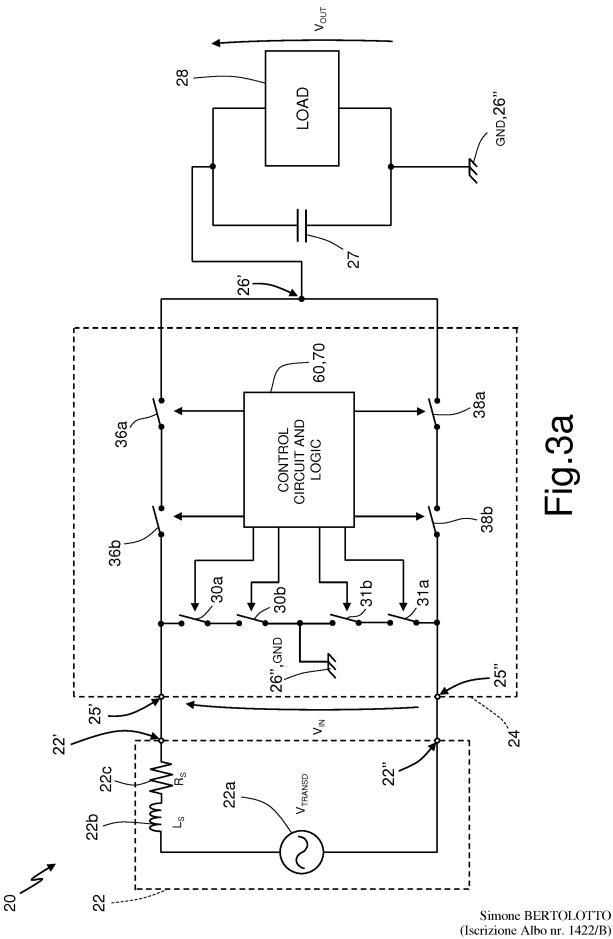

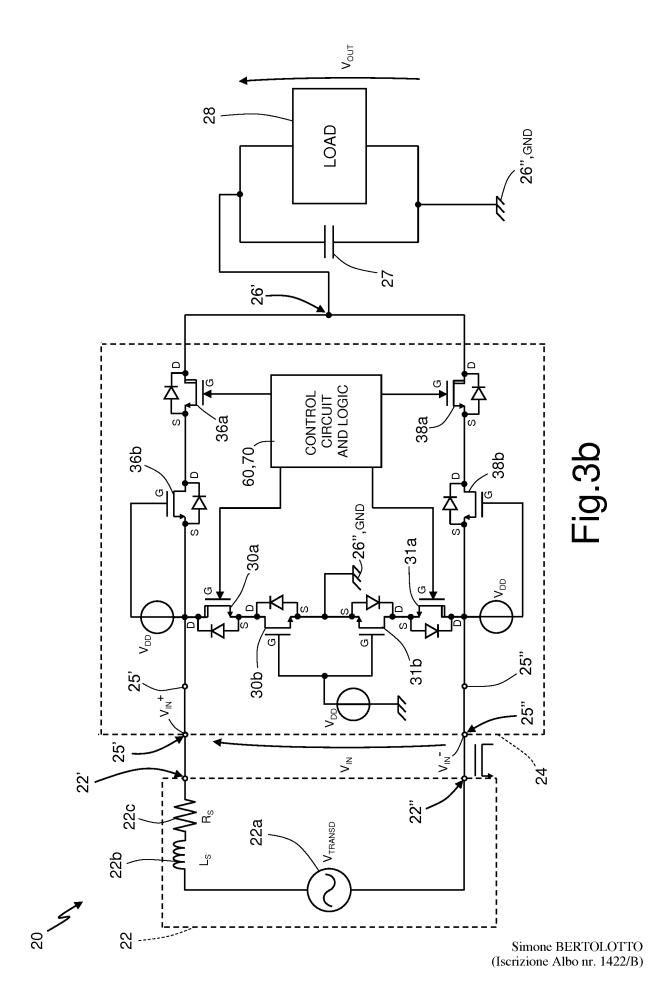

- le figure 3a e 3b mostrano un sistema di raccolta di energia comprendente un circuito di interfaccia di raccolta operabile secondo le fasi del metodo di figura 13, secondo rispettive forme di realizzazione della presente

## invenzione;

- le figure 4a e 4b mostrano il sistema di raccolta di energia di figura 3a o 3b in rispettive condizioni operative, temporalmente successive tra loro;

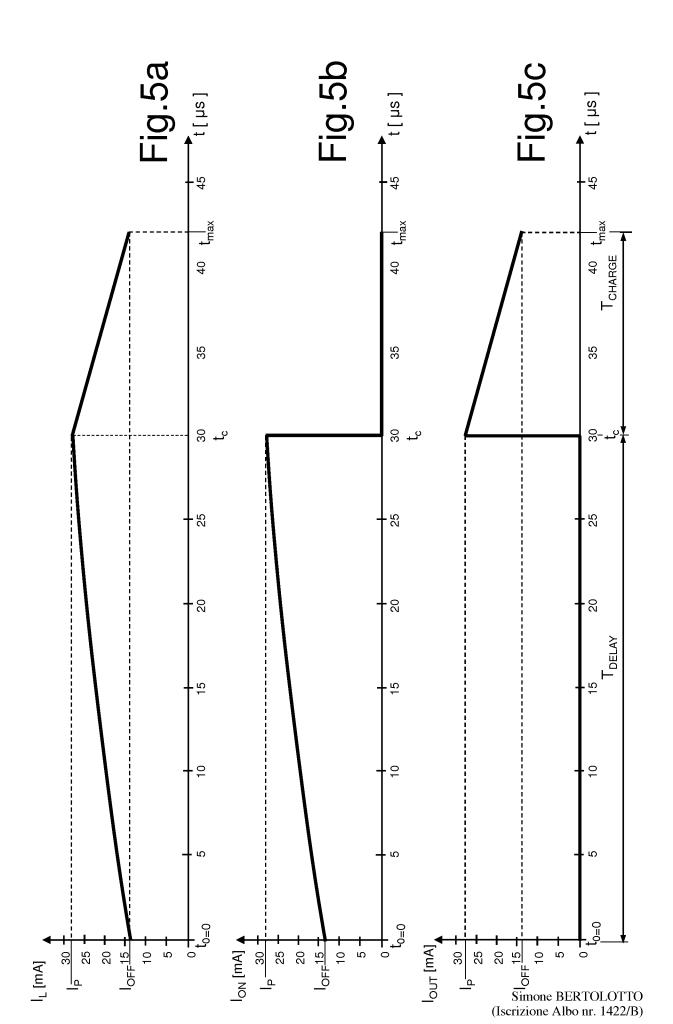

- le figure 5a-5c mostrano, utilizzando una stessa scala temporale, l'andamento nel tempo di segnali di corrente del sistema di raccolta di energia di figura 3a o 3b nelle condizioni operative delle figure 4a e 4b;

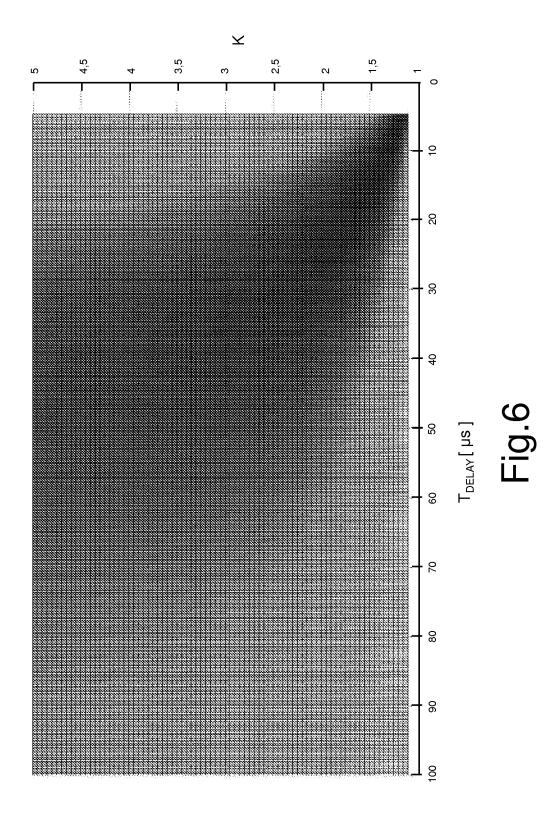

- la figura 6 mostra l'andamento del fattore di accoppiamento tra il trasduttore e il circuito di interfaccia di raccolta di figura 3a o 3b, al variare di parametri operativi;

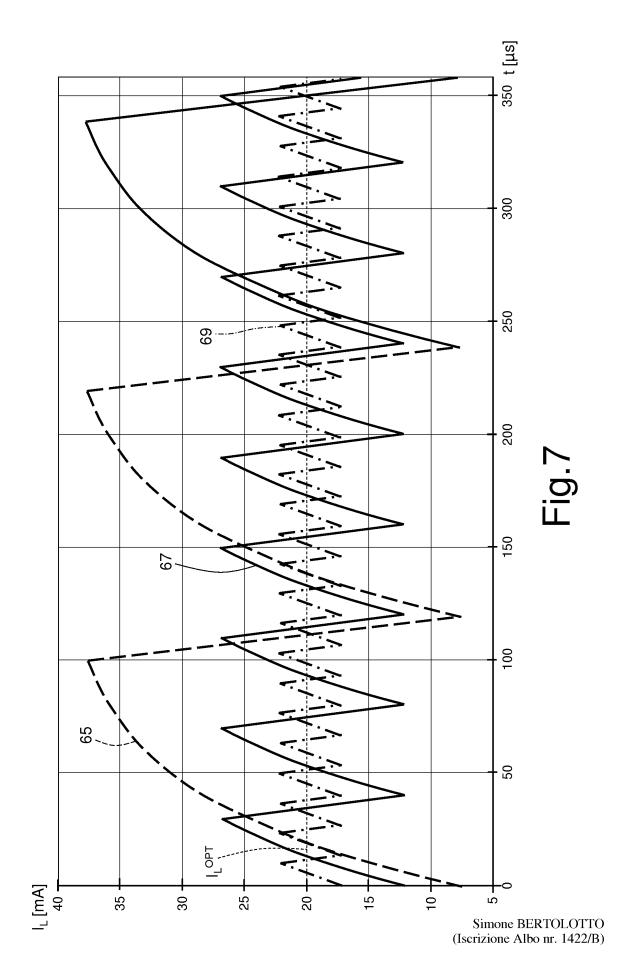

- la figura 7 mostra profili di accumulo/scarica di corrente nel sistema di raccolta di energia nelle condizioni operative della figura 4a e 4b;

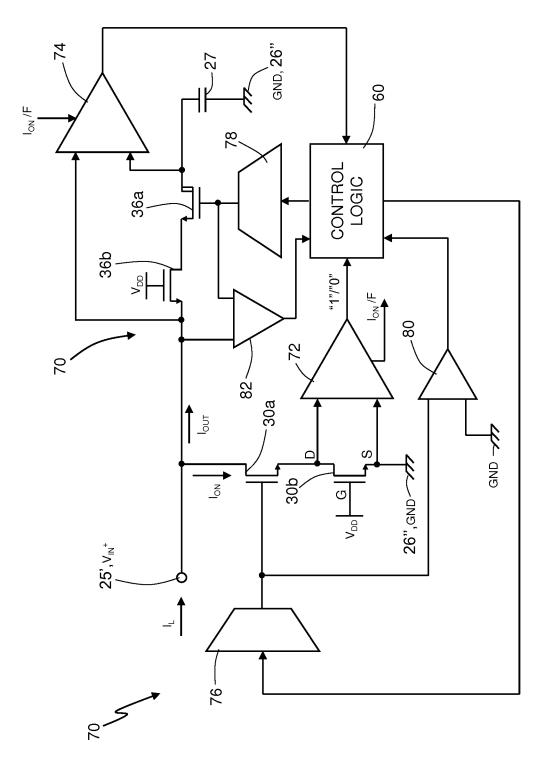

- la figura 8 mostra un circuito di gestione e controllo del circuito di interfaccia di raccolta di figura 3a o 3b utilizzabile per semionde positive del segnale di ingresso al circuito di interfaccia di raccolta;

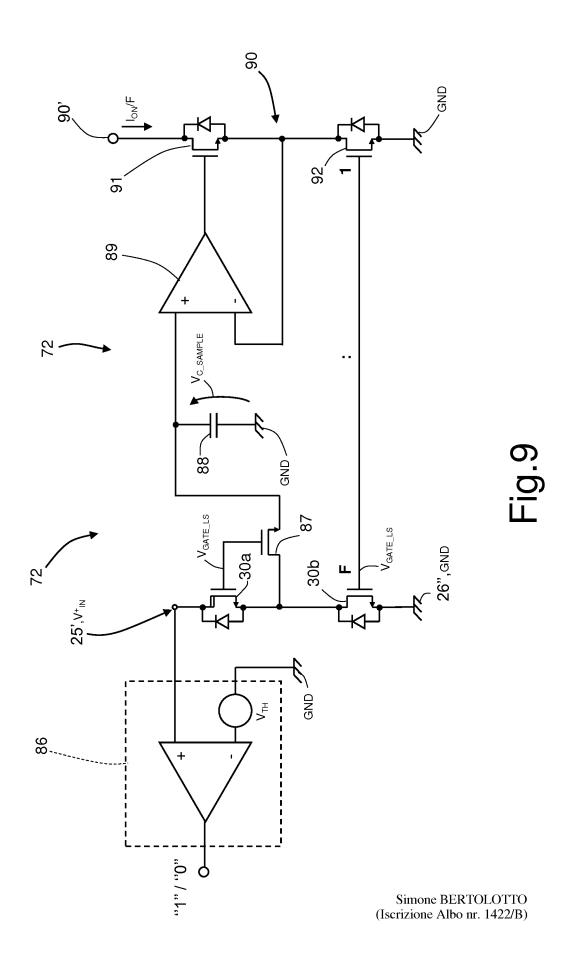

- la figura 9 mostra, con maggior dettaglio, una porzione del circuito di gestione e controllo di figura 8;

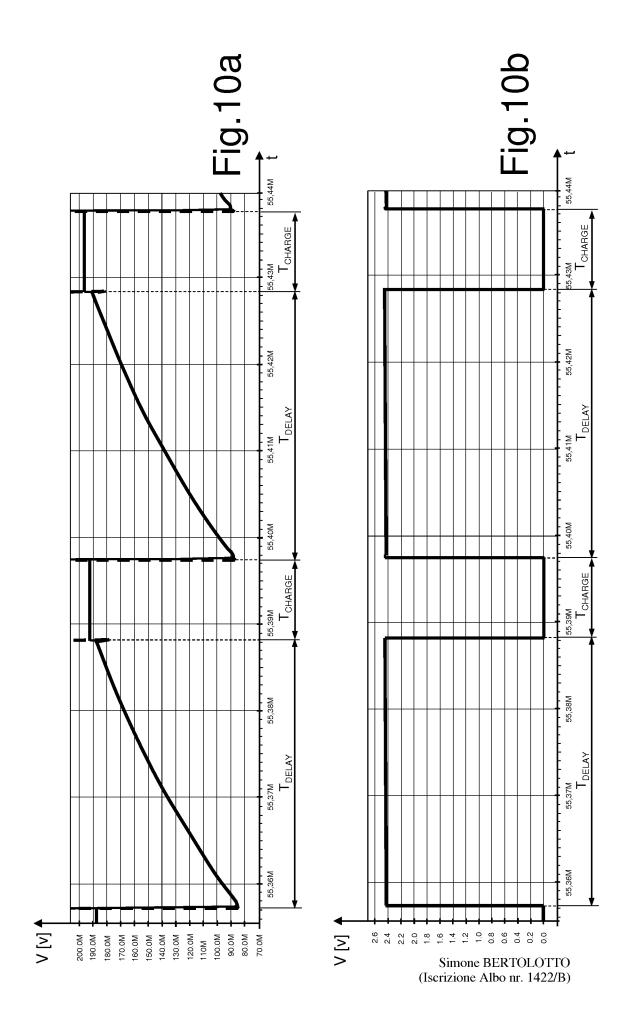

- le figure 10a e 10b mostrano, utilizzando una stessa scala temporale, l'andamento nel tempo di segnali di corrente nel circuito di figura 9, in particolare per mostrare una fase di passaggio tra la condizione operativa

di figura 4a e la condizione operativa di figura 4b;

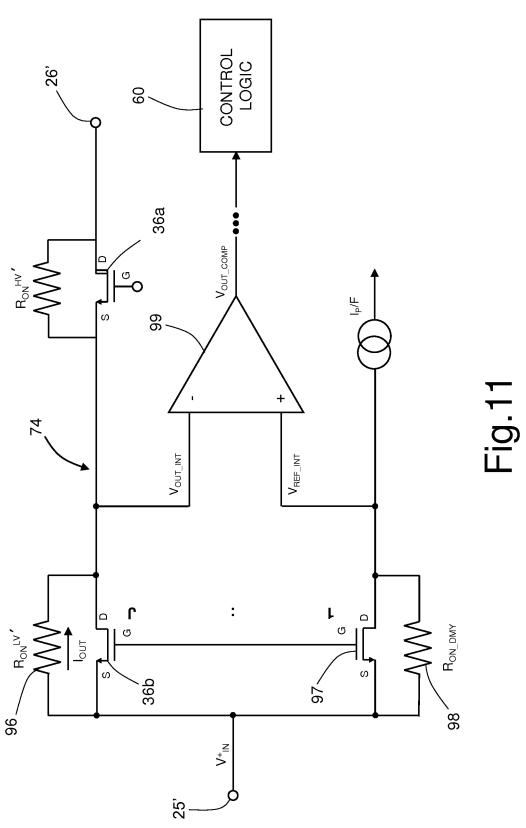

- la figura 11 mostra, con maggior dettaglio, una porzione ulteriore del circuito di gestione e controllo di figura 8;

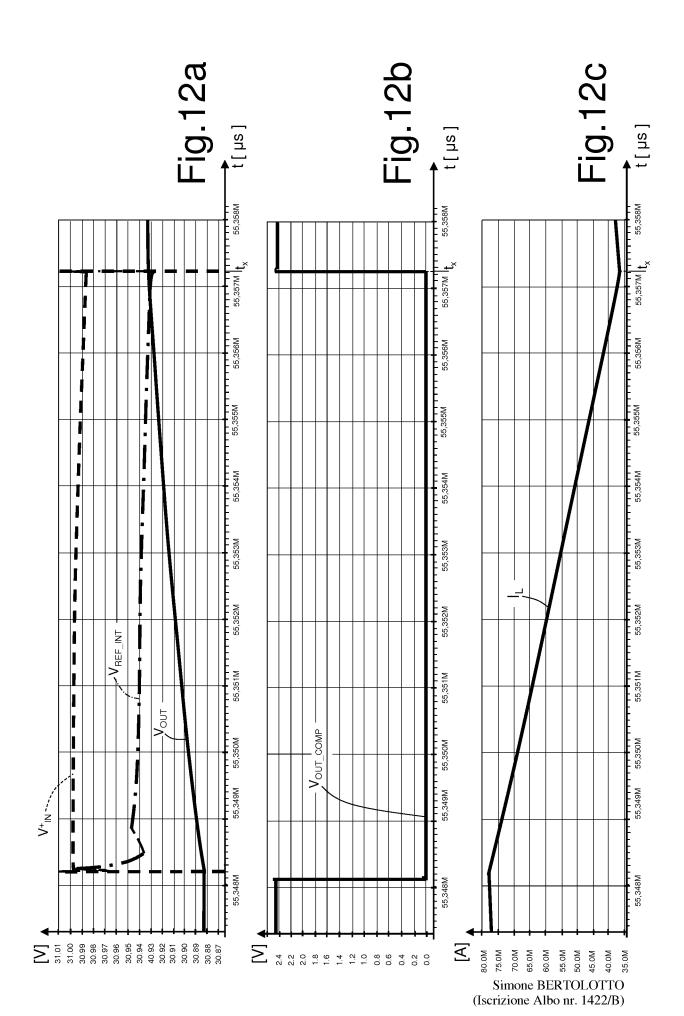

- le figure 12a-12c mostrano, utilizzando una stessa scala temporale, l'andamento nel tempo di segnali di corrente nel circuito di figura 11;

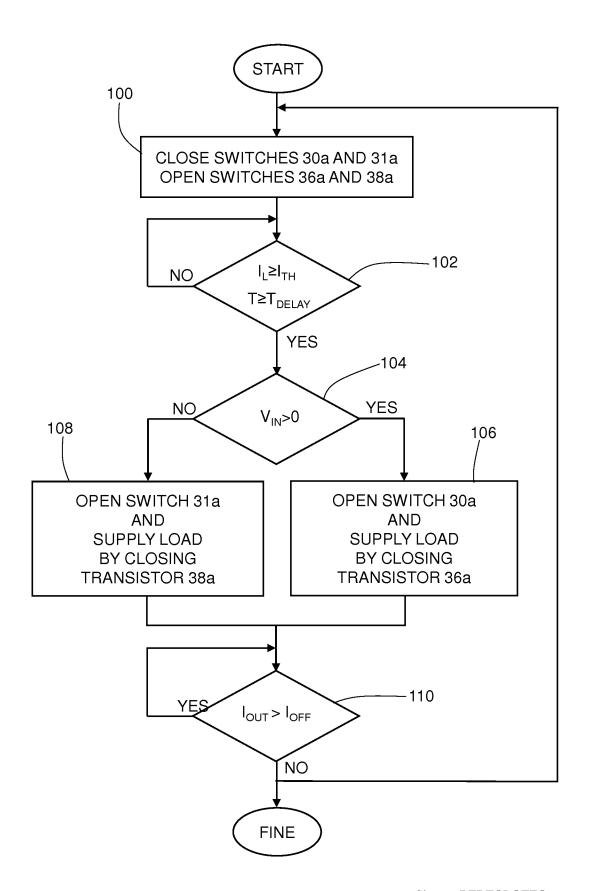

- la figura 13 mostra, mediante diagramma di flusso, fasi di un metodo per operare il sistema di raccolta di energia di figura 3a o 3b, secondo una forma di realizzazione della presente invenzione;

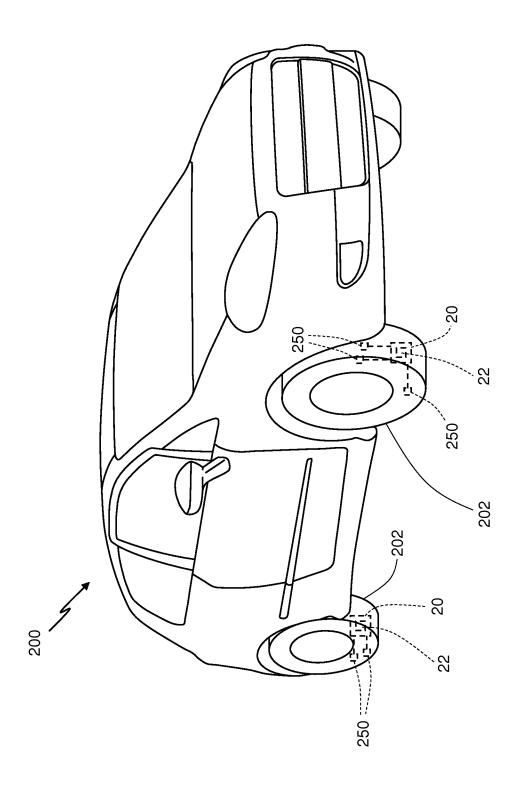

- la figura 14 mostra un veicolo comprendente il sistema di raccolta di energia di figura 3a o 3b; e

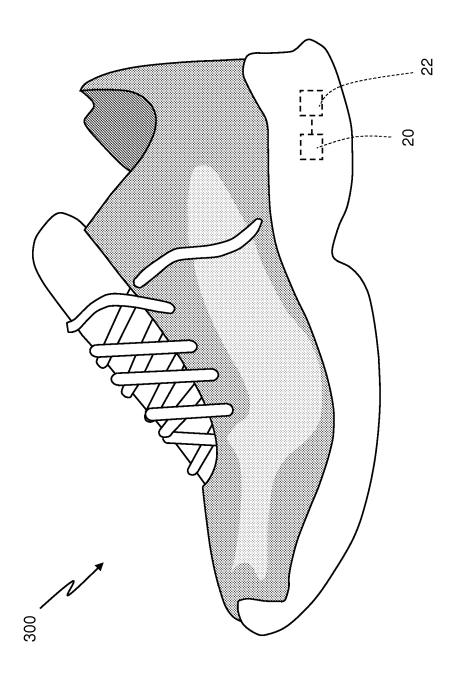

- la figura 15 mostra una calzatura comprendente il sistema di raccolta di energia di figura 3a o 3b.

L'interfaccia di raccolta di energia scavenging interface") (in particolare avente la configurazione di un circuito rettificatore) secondo la presente invenzione è collegabile tra una sorgente segnale di ingresso (in particolare, un segnale di tensione carico elettrico variabile) ed un (con l'eventuale interposizione di un convertitore DC-DC atto a fornire al carico elettrico un segnale di tensione avente un livello di tensione accettato dal carico elettrico). L'interfaccia di raccolta di energia comprende, secondo una forma di

realizzazione della presente invenzione, un primo e terzo interruttore, posti in serie, connessi tra il terminale di ingresso dell'interfaccia e un terminale di dell'interfaccia posto a tensione costante. L'interfaccia comprende inoltre un secondo e quarto interruttore, posti in serie, connessi tra il terminale di dell'interfaccia e il terminale di uscita dell'interfaccia su cui viene raccolta l'energia. L'interfaccia di raccolta di energia comprende inoltre una logica di controllo, accoppiata ai terminali di controllo del primo e del secondo interruttore, configurata per aprire/chiudere il primo e il secondo interruttore mediante un opportuno segnale di controllo.

L'interfaccia di raccolta di energia comprende inoltre ulteriori terzo e quarto interruttore, ciascuno avente un terminale di controllo, e collegati in serie al primo e, rispettivamente, secondo interruttore.

Sull'uscita dell'interfaccia di raccolta di energia è presente un condensatore, per accumulare la potenza trasferita in uscita dell'interfaccia di raccolta. In parallelo al condensatore può essere presente un carico elettrico, che viene alimentato mediante l'energia accumulata nel condensatore. Come già detto, tra il condensatore e il carico elettrico può essere interposto un convertitore DC-DC, di tipo buck, o boost, o buck/boost.

In una prima condizione operativa, il primo e il terzo interruttore sono chiusi e l'interfaccia di raccolta di energia accumula energia elettrica in un elemento di accumulo accoppiato al primo e al terzo interruttore; il secondo interruttore è invece aperto così che il condensatore non viene caricato.

In una seconda condizione operativa, l'elemento di accumulo viene elettricamente accoppiato al condensatore aprendo il primo interruttore e chiudendo il secondo interruttore; il condensatore viene caricato mediante l'energia elettrica precedentemente accumulata durante la prima condizione operativa.

Il passaggio dalla prima alla seconda condizione operativa, e viceversa, è ciclico.

L'interfaccia di raccolta di energia secondo la presente invenzione è descritta in dettaglio con riferimento ad una sua applicazione, in particolare come circuito rettificatore di un sistema di raccolta di energia ("energy harvesting system") disposto tra una sorgente di tensione ed un elemento di accumulo e/o un carico elettrico.

Secondo un aspetto della presente invenzione, l'interfaccia di raccolta di energia comprende inoltre un dispositivo misuratore e generatore di corrente accoppiato a terminali di conduzione del terzo interruttore per

rilevare la corrente che scorre, in uso, attraverso il terzo interruttore (e, consequentemente, anche attraverso interruttore). Il il primo dispositivo misuratore generatore di corrente è inoltre configurato per generare una copia scalata della corrente che scorre attraverso il terzo interruttore. In particolare la generazione della copia scalata della corrente è ottenuta pilotando un ulteriore interruttore con fattore geometrico W/L ridotto di una quantità F rispetto al fattore geometrico W/L del interruttore. La corrente che scorre in tale interruttore con fattore W/L scalato della quantità F è dunque F-volte minore della corrente che scorre nel primo e nel terzo transistore durante la prima condizione operativa.

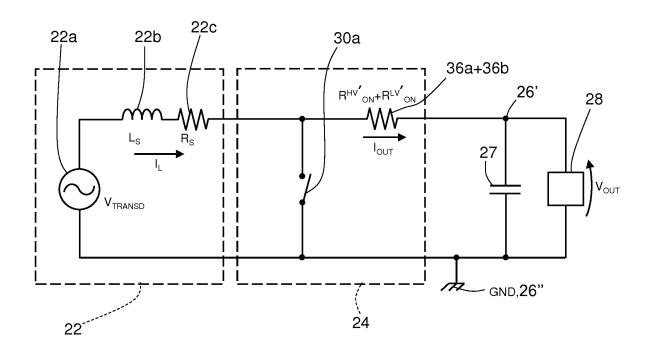

La figura 3a mostra un sistema di raccolta di energia 20 comprendente un circuito rettificatore 24, secondo una forma di realizzazione della presente invenzione.

In generale, il sistema di raccolta di energia 20 comprende un trasduttore 22 (analogo al trasduttore 2 di figura 1) includente propri terminali di uscita 22', 22"; il circuito rettificatore 24, includente un primo e un secondo terminale di ingresso 25', 25", elettricamente accoppiati, rispettivamente, ai terminali di uscita 22', 22" del trasduttore 22, e un primo e un secondo terminale di uscita 26', 26"; e un elemento di accumulo 27, ad

esempio un condensatore, collegato tra il primo e il secondo terminale di uscita 26', 26" del circuito rettificatore 24, e configurato per accumulare carica elettrica fornita in uscita dal circuito rettificatore 24. Il secondo terminale di uscita 26" è, secondo una forma di realizzazione della presente invenzione, un terminale a tensione di riferimento, ad esempio a tensione di terra GND, ad esempio pari a circa 0V. Altre tensioni di riferimento possono essere utilizzate.

Il trasduttore 22 è, ad esempio, un trasduttore elettromagnetico, ed è schematizzato in modo da includere un generatore di tensione 22a, atto a fornire una tensione  $V_{\text{TRASD}}$ , un induttore 22b (tipico del trasduttore elettromagnetico) avente induttanza  $L_{\text{S}}$ , ed un resistore 22c avente resistenza  $R_{\text{S}}$ , collegato in serie all'induttore 22b.

Sull'uscita del circuito rettificatore 24, in parallelo all'elemento di accumulo 27, è collegabile un carico elettrico 28, atto ad essere alimentato dalla carica immagazzinata nell'elemento di accumulo 27 o mediante un convertitore, ad esempio DC-DC (non mostrato in figura), se il carico elettrico richiede un valore di tensione diverso da quello generato in uscita dal circuito rettificatore 24.

Tra il primo terminale di ingresso 25' e il secondo terminale di uscita 26" del circuito rettificatore 24 sono collegati, in serie tra loro, un interruttore per alta

tensione 30a (nel seguito interruttore HV) e un interruttore per bassa tensione 30b (nel seguito interruttore LV), in particolare di tipo controllato in tensione. Gli interruttori 30a e 30b sono, ad esempio, transistori a effetto di campo (FET) a canale N.

L'interruttore HV 30a è un dispositivo in grado di sostenere elevate tensioni ("high voltages"). Secondo una forma di realizzazione, l'interruttore HV 30a è un transistore DMOS atto ad operare con tensioni gate-drain ( $V_{GD}$ ) e drain-source ( $V_{DS}$ ) nell'intervallo 30-50 V, ad esempio pari a 40 V.

L'interruttore LV 30b è un dispositivo per basse tensioni ("low voltages"). Secondo una forma di realizzazione, l'interruttore HV 30a è un transistore CMOS tensioni atto ad operare con gate-source  $(V_{GS})$ nell'intervallo 1-5 V, in particolare 2.5-3.6 V, ad esempio pari a 3.3 V. Altre tecnologie per transistori a bassa tensione prevedono tensioni operative leggermente più alte, ad esempio dell'ordine di 4-5 V.

In generale, dato un valore di tensione massimo tollerato ( $V_{max\_th}$ ) in corrispondenza del primo terminale di uscita 26' (dipendente, ad esempio dalle caratteristiche del condensatore 27 e/o del carico 28), con il termine "elevate tensioni" si intendono tensioni gate-drain ( $V_{GD}$ ) e drainsource ( $V_{DS}$ ) del rispettivo transistore prossime, ma non

superiori, a tale valore di tensione massimo tollerato  $(V_{max\_th})$ . La "bassa tensione" è invece riferita a tensioni gate-source  $V_{GS}$  del rispettivo transistore.

Risulta evidente che i valori indicati sono indicativi di una possibile forma di realizzazione, e variano in rapporto alla tecnologia utilizzata per i transistori e all'applicazione specifica della presente invenzione.

Tra il primo terminale di ingresso 25' e il primo terminale di uscita 26' sono collegati, in serie tra loro, un interruttore per bassa tensione (LV) 36b e un interruttore per alta tensione (HV) 36a, in particolare di tipo controllato in tensione. Anche gli interruttori 36b e 36a sono, ad esempio, transistori FET a canale N. In particolare, l'interruttore HV 36a è dello stesso tipo dell'interruttore HV 30a, in grado di sostenere elevate tensioni, mentre l'interruttore LV 36b è dello stesso tipo dell'interruttore LV 30b, per basse tensioni.

L'interruttore HV 36a ha la funzione di garantire elevate tensioni al terminale di uscita 26" del circuito rettificatore 24

Inoltre, il circuito rettificatore 24 comprende ulteriori interruttori per alta tensione (HV) 31a e per bassa tensione (LV) 31b, collegati in serie tra loro, e elettricamente accoppiati tra il secondo terminale di ingresso 25" e il secondo terminale di uscita 26" del

circuito rettificatore 24; ed interruttori per alta tensione (HV) 38a e per bassa tensione (LV) 38b, collegati in serie tra loro e collegati tra il secondo terminale di ingresso 25" e il primo terminale di uscita 26'.

Gli interruttori 31a e 31b sono analoghi (e speculari da un punto di vista circuitale) agli interruttori 30a e 30b, e tali che l'interruttore HV 31a è un dispositivo in grado di sostenere elevate tensioni gate-drain e drainsource (ad esempio 30-50V, in particolare 40 V), mentre l'interruttore LV 31b è un dispositivo per basse tensioni, ad esempio un CMOS, in grado di sostenere basse tensioni gate-source (ad esempio 1-5 V, in particolare 2.5-3.6V, ancora più in particolare 3.3 V). Altre tecnologie per transistori a bassa tensione prevedono tensioni operative leggermente più alte, ad esempio dell'ordine di 4-5 V.

Gli interruttori 38a e 38b sono analoghi (e speculari da un punto di vista circuitale) agli interruttori 36a e 36b rispettivamente, e tali che l'interruttore HV 38a è un dispositivo in grado di sostenere elevate tensioni, mentre l'interruttore LV 38b è un dispositivo per basse tensioni, in analogia a quanto già descritto con riferimento agli interruttori 36a e 36b rispettivamente.

Per semplicità di descrizione ci si riferirà nel seguito interruttori per alta tensione (HV) 30a, 36a, 31a, 38a come, rispettivamente, transistori per alta tensione

(HV)30a, 36a, 31a, 38a senza per questo perdere di generalità; e agli interruttori per bassa tensione 30b, , 36b , 31b, 38b come, rispettivamente, transistori per bassa tensione (LV) 30b, 36b, 31b, 38b, senza per questo perdere di generalità.

Allo stesso modo, con il termine "transistore chiuso" ci si riferirà nel seguito ad un transistore polarizzato in modo tale da consentire la conduzione di corrente elettrica tra i suoi terminali di sorgente e pozzo, cioè configurato per comportarsi come un interruttore chiuso; e con il termine "transistore aperto" ci si riferirà nel seguito ad un transistore polarizzato in modo tale da non consentire la conduzione di corrente elettrica tra i suoi terminali di sorgente e pozzo, cioè configurato per comportarsi come un interruttore aperto o interdetto.

La figura 3b mostra il sistema di raccolta di energia 20 di figura 3a in cui gli interruttori sono stati sostituiti da rispettivi transistori. Ciascun transistore è inoltre rappresentato con il proprio diodo interno (diodo parassita).

Con riferimento alla figura 3b, il terminale di pozzo D del transistore HV 30a è collegato al primo terminale di ingresso 25' del circuito rettificatore 24, mentre il terminale di sorgente S del transistore HV 30a è collegato al terminale di pozzo D del transistore LV 30b; il

terminale di sorgente S del transistore LV 30b è invece collegato al secondo terminale di uscita 26" del circuito rettificatore 24. In questo modo, i transistori 30a e 30b sono effettivamente collegati in serie tra loro tra l'ingresso 25' e l'uscita 26" del circuito rettificatore 24.

Il terminale di pozzo D del transistore HV 36a è collegato al primo terminale di uscita 26' del circuito rettificatore 24, e il terminale di sorgente S del transistore HV 36a è collegato al terminale di pozzo D del transistore LV 36b; il terminale di sorgente S del transistore LV è collegato al primo terminale di ingresso 25' del circuito rettificatore 24. In questo modo, i transistori HV 36a e LV 36b sono effettivamente collegati in serie tra loro tra l'ingresso 25' e l'uscita 26' del circuito rettificatore 24.

Per quanto riguarda i transistori HV 31a e LV 31b, questi sono collegati tra il secondo terminale di ingresso 25" e il secondo terminale di uscita 26" del circuito rettificatore 24 così che il terminale di sorgente S del transistore LV 31b è collegato al secondo terminale di uscita 26", il terminale di pozzo D del transistore HV 31a è collegato al secondo terminale di ingresso 25", e i restanti terminali di pozzo D del transistore LV 31b e sorgente S del transistore HV 31a sono collegati tra loro.

I transistori HV 38a e LV 38b sono collegati tra il secondo terminale di ingresso 25" e il primo terminale di uscita 26', in modo tale che il terminale di sorgente S del transistore LV 38b è collegato al secondo terminale di ingresso 25", il terminale di pozzo D del transistore HV 38a è collegato al primo terminale di uscita 26', e i restanti terminali di pozzo D del transistore LV 38b e sorgente S del transistore HV 38a sono collegati tra loro.

Durante semi-cicli positivi della tensione di ingresso  $V_{\rm IN}$ , la rettificazione di tensione è effettuata pilotando opportunamente i transistori HV 30a e 36a, mantenendo i transistori LV 30b e 36b in stato chiuso. In questa fase, i i transistori 31a, 31b, ee 38b sono in stato aperto chiuso, mentre il transistore 38a è in stato aperto. Viceversa, durante semi-cicli negativi della tensione di ingresso  $V_{\rm IN}$ , la rettificazione di tensione è effettuata pilotando opportunamente i transistori HV 31a e 38a, mantenendo i transistori 31b e 38b in stato chiuso. In questa fase, i transistori 30a, 30b, e 36b sono mantenuti in stato aperto chiuso, mentre il transistore 36a è aperto.

Per operare il circuito rettificatore 24, secondo una forma di realizzazione della presente invenzione, il circuito rettificatore 24 comprende inoltre un circuito ed una logica di controllo, indicati in figura 3a o 3b con i numeri di riferimento 60 e 70, e meglio descritti con

riferimento alle figure 8 e 9. Inoltre, la logica di controllo 60 implementa le fasi di metodo di figura 13.

In uso, ad esempio per tensioni positive di  $V_{\rm IN}$ , i transistori HV 30a e LV 30b vengono tenuti chiusi per almeno un intervallo temporale  $T_{DELAY}$  in modo da accumulare nell'induttore 22b (situazione energia mostrata schematicamente in figura 4a). Durante questa fase, per garantire un accumulo dell'energia nell'induttore 22b in assenza di trasferimento di energia sul condensatore 27, almeno uno tra i transistori 36a e 36b (ad esempio il solo 36a) viene mantenuto transistore HV in stato aperto (secondo una forma di realizzazione, il transistore 36b è sempre mantenuto in stato chiuso). Il transistore 31a è controllato in stato chiuso, il transistore 31b è mantenuto in stato chiuso, e il transistore 38a è controllato in stato aperto.

Quindi, trascorso l'intervallo temporale  $T_{\text{DELAY}}$  e raggiunto un valore di soglia minimo  $I_{\text{TH}}$  per l'energia accumulata nell'induttore 22b, almeno uno tra i transistori 30a e 30b (ad esempio il solo transistore HV 30a) viene aperto e i transistori 36a e 36b vengono chiusi in modo da trasferire l'energia accumulata nell'induttore 22b verso il condensatore 27/carico 28. Questa situazione è mostrata schematicamente in figura 4b.

Il segnale di ingresso  $V_{\rm IN}$  è, come detto, un segnale variabile, cioè avente polarità variabile nel tempo. Per polarità negative di  $V_{\rm IN}$ , quanto descritto con riferimento alle figure 4a e 4b è comunque valido controllando in modo analogo i transistori 31a, 31b, 38a e 38b. Le fasi di controllo di questi transistori non sono qui riportate per brevità, ma sono apparenti al tecnico esperto ("skilled technician"), sulla base di quanto finora descritto.

Secondo una forma di realizzazione della presente invenzione, in entrambe le condizioni operative delle figure 4a e 4b, per polarità positive della tensione di ingresso  $V_{IN}$ , i transistori LV 30b e 36b sono sempre mantenuti chiusi, e la logica di controllo 60 comanda in stato aperto/chiuso i soli transistori HV 30a e 36a; analogamente, per polarità negative della tensione di ingresso  $V_{\mathrm{IN}}$ , la logica di controllo 60 comanda in stato aperto/chiuso i soli transistori HV 31a e 38a, mentre i transistori LV 31b e 38b sono sempre mantenuti chiusi. Questa situazione è rappresentata schematicamente in figura 3b mostrando generatori di tensione, atti a generare una tensione VDD, accoppiati ai terminali di controllo G dei transistori LV 30b, 31b, 36b, e 38b. La tensione  $V_{DD}$  ha valore tale da controllare in stato chiuso i transistori LV 30b, 31b, 36b, e 38b.

Risulta evidente che, secondo una diversa forma di realizzazione, la logica di controllo 60 può comandare attivamente in stato aperto/chiuso entrambi i transistori 36a e 36b, ed entrambi i transistori 38a e 38b, senza per questo interferire con le fasi di carica dell'induttore 22b e alimentazione del condensatore 27/carico 28 precedentemente descritte.

Durante la fase di figura 4b, in cui la corrente accumulata nell'induttore 22b viene trasferita in uscita sull'elemento di accumulo 27 mediante i transistori 36a e 36b (o in alternativa i transistori 38a e 38b, a seconda della polarità della tensione di ingresso  $V_{\rm IN}$ ), si osserva un incremento della tensione di uscita  $V_{\rm OUT}$ .

Nel seguito, il funzionamento del rettificatore 24 è meglio descritto facendo riferimento ad un modello circuitale valido per una polarità (in particolare la polarità positiva) del segnale di ingresso  $V_{\rm IN}$ , per maggior semplicità e chiarezza di descrizione. Come detto, quanto descritto è comunque immediatamente applicabile al controllo dei transistori 31a, 31b, 38a, 38b nel caso di polarità negativa del segnale di ingresso  $V_{\rm IN}$ .

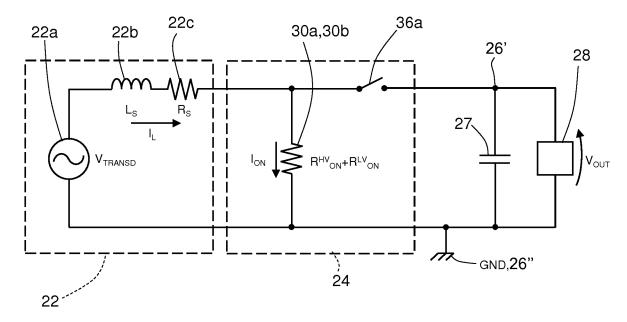

La figura 4a mostra un circuito equivalente al circuito di figura 3a o 3b, per semionde positive della tensione di ingresso  $V_{\rm IN}.$  Il transistore HV 36a è aperto e il transistore LV 36b chiuso. I transistori 30a e 30b sono

chiusi. In questa condizione operativa i transistori 30a e 30b sono idealmente sostituiti da rispettivi resistori aventi resistenza  $R^{HV}_{ON}$  e, rispettivamente,  $R^{LV}_{ON}$  (resistenza dei transistori 30a e 30b in stato acceso - "on-state resistance").

La corrente  $I_L$  che scorre nell'induttore 22b è pari alla corrente  $I_{ON}$  che percorre i transistori 30a e 30b in stato acceso. Il valore della corrente  $I_L$  cresce fino a raggiungere un valore massimo, o valore di picco,  $I_P$  (si veda il grafico di figura 5a).

La curva di  $I_L$  ha un andamento nel tempo dato da:

$$I_{L} = I_{ON} = \frac{V_{TRASD}}{R_{S}} \left( 1 - e^{-\frac{t}{\tau}} \right) - I_{OFF} \cdot e^{-\frac{t}{\tau}}$$

La corrente  $I_{\text{ON}}$  raggiunge il valore di picco  $I_{\text{p}}$  al tempo  $t=t_{\text{c}}=T_{\text{DELAY}}.$  Per semplicità, si suppone che l'istante di partenza  $t_0$  sia pari a 0  $\mu s$ .

Trascorso l'intervallo temporale  $T_{\text{DELAY}}$ , e posto che la corrente  $I_{\text{L}}$  che scorre nell'induttore 22b ha raggiunto un valore uguale al, o maggiore del, valore di soglia  $I_{\text{TH}}$ , si passa alla condizione operativa schematizzata in figura 4b.

L'intervallo temporale  $T_{\text{DELAY}}$  è l'intervallo intercorrente tra l'istante di chiusura del transistore HV 30a (al tempo  $t_0$ ) e l'istante di apertura del transistore HV 30a e chiusura del transistore 36a (al tempo  $t_c$ ). Risulta evidente che, prima della chiusura del transistore

HV 36a è opportuno aprire il transistore HV 30a, in modo da evitare fenomeni di conduzione incrociata ("cross conduction") e dissipazione di potenza dal condensatore di uscita 27 verso massa GND.

Il valore di corrente di soglia  $I_{TH}$  è scelto in base ai valori di picco di corrente Ip che si raggiungono, e/o sulla base dell'applicazione del circuito rettificatore 24. valori dipendono dalle caratteristiche del trasduttore 22 e dalle sollecitazioni ambientali a cui il trasduttore 22 è sottoposto. In particolare, il valore di corrente di soglia  $I_{TH}$  è scelto molto minore del valore di picco Ip che si prevede di raggiungere nell'applicazione in cui il circuito rettificatore 24 è utilizzato. Ad esempio, supponendo di raggiungere valori di picco Ip di circa 150 mA, la soglia  $I_{TH}$  può essere scelta compresa tra circa 5-10 mA. Si fa notare che la scelta di una corrente di soglia  $I_{\text{TH}}$  troppo vicina al valore di picco  $I_{\text{p}}$  comporta una bassa efficienza. Infatti, secondo quanto descritto, trasferita corrente in uscita solo al superamento della soglia  $I_{TH}$ ; tutte le porzioni di segnale  $V_{TRASD}$  che generano una corrente con valore di picco  $I_p < I_{TH}$  non danno contributo di carica trasferito in uscita.

Con riferimento alla figura 4b, al tempo  $t_{\text{c}}$ , il transistore HV 30a viene aperto e il transistore HV 36a chiuso (come detto, preferibilmente rispettando un

intervallo di guardia per evitare cross conduction); la corrente  $I_L$  che fluisce dall'induttore 22b verso l'uscita 26' del rettificatore 24 è la corrente  $I_{OUT}$  che carica il condensatore 27. In questa fase, la corrente nell'induttore 22b decresce con una pendenza costante, fino a raggiungere il valore predefinito  $I_{OFF}$  (al tempo  $t_{max}$ , si veda nuovamente la figura 5a), secondo la relazione:

$$\frac{dI_L}{dT} = \frac{V_{OUT} + \left(R_S + R_{ON}^{HV} + R_{ON}^{LV}\right) \cdot \frac{I_p + I_{OFF}}{2} - V_{TRASD}}{L_S}$$

dove  $R^{HV}_{ON}$ ' e

$R^{\text{LV}}_{\text{ON}}$ , sono, rispettivamente, i valori di resistenza in stato acceso dei transistori 36a e 36b.

Posto che  $I_{\text{OFF}}$  è un valore costante, dato da  $I_{\text{p}}/K$ , con K costante maggiore di 1 (scelta come spiegato in seguito), si ottiene la seguente formula per il valore di picco  $I_{\text{P}}$ :

$$I_{p} = \frac{V_{TRASD}}{R_{S}} \cdot \frac{\left(1 - e^{-\frac{T_{DELAY}}{\tau}}\right)}{1 - \frac{1}{K} e^{\frac{T_{DELAY}}{\tau}}}$$

La figura 5a mostra l'andamento della corrente  $I_L$  nel tempo t ( $\mu$ s). La curva della corrente  $I_L$  raggiunge il valore di picco  $I_P$  all'istante temporale  $t_c$ , in cui il transistore HV 30a viene aperto (si veda la figura 5b) e il transistore HV 36a chiuso.

Quindi, tra  $t_c$  e  $t_{max}$  (intervallo temporale  $T_{CHARGE}$ ) la corrente  $I_L$  decresce fino a raggiungere il valore  $I_{OFF}=I_p/K$ .

La figura 5b mostra, utilizzando la stessa scala temporale della figura 5a, l'andamento della corrente  $I_{\text{ON}}$  che scorre attraverso il transistore HV 30a durante la fase di figura 4a di carica dell'induttore 22b. Nell'intervallo temporale  $t_0$ - $t_c$  la corrente  $I_{\text{ON}}$  segue lo stesso andamento della corrente  $I_{\text{L}}$ ; all'istante temporale  $t_c$ , il transistore HV 30a viene aperto e la corrente  $I_{\text{ON}}$ , di conseguenza, scende a zero ("drops to zero").

La figura 5c mostra, utilizzando la stessa scala temporale delle figure 5a e 5b, l'andamento della corrente di uscita  $I_{\text{OUT}}$ . La corrente  $I_{\text{OUT}}$  si mantiene ad un valore nullo nell'intervallo temporale  $t_0$ - $t_c$ , per raggiungere il valore di picco  $I_P$  all'istante temporale  $t_c$  in cui il condensatore 27 viene accoppiato elettricamente all'induttore 22b. Quindi, tra  $t_c$  e  $t_{\text{max}}$  (entro l'intervallo temporale  $T_{\text{CHARGE}}$ ), l'energia immagazzinata nell'induttore 22b alimenta e carica il condensatore 27.

L'intervallo temporale T<sub>CHARGE</sub> è dato da:

$$T_{CHARGE} = L_{S} \cdot \frac{I_{p} - I_{OFF}}{V_{OUT} + \left(R_{S} + R^{\text{t}_{ON}^{HV}} + R^{\text{t}_{ON}^{LV}}\right) \cdot \frac{I_{p} + I_{OFF}}{2} - V_{TRASD}}$$

Al tempo  $t_{\text{max}}$ , in cui la corrente che fluisce verso il condensatore 27 raggiunge il valore di soglia  $I_{\text{OFF}}$ , il

transistore HV 36a viene aperto, e il transistore HV 30a viene chiuso, così che l'induttore 22b si carica nuovamente, in analogia a quanto già descritto. Le fasi di carica e scarica dell'induttore 22b (e, di conseguenza, di alimentazione del condensatore 27/carico 28) si ripetono in modo ciclico.

L'integrale della curva di  $I_{OUT}$  (figura 5c) tra il tempo  $t_c$  e il tempo  $t_{max}$  indica la carica  $Q_{CYCLE}$  trasferita tra l'ingresso e l'uscita del rettificatore 24 nel tempo fine di massimizzare l'efficienza Al di trasferimento di carica tra ingresso e uscita rettificatore 24, è opportuno massimizzare il valore della potenza P<sub>CYCLE</sub> trasferita in uscita dal circuito rettificatore 24 in ciascun ciclo di carica/scarica dell'induttore 22b. La potenza  $P_{CYCLE}$  è definita come P<sub>CYCLE</sub>=V<sub>OUT</sub>·I<sub>CYCLE</sub>, dove I<sub>CYCLE</sub> è data da I<sub>CYCLE</sub>=Q<sub>CYCLE</sub>/T<sub>CYCLE</sub>, essendo  $T_{CYCLE}$  l'intervallo temporale intercorrente tra  $t_0$  e  $t_{max}$  ( $T_{CYCLE} = T_{DELAY} + T_{CHARGE}$ ).

La richiedente ha verificato che  $P_{\text{CYCLE}}$  è dato dalla seguente relazione (dove  $I_{\text{ON}}$  assume il valore di picco  $I_{\text{p}}$ ):

$$P_{CYCLE} = \frac{\frac{I_{ON} + I_{OFF}}{2} \cdot T_{CHARGE}}{T_{DELAY} + T_{CHARGE}} \cdot V_{OUT}$$

Dalle precedenti relazione si può notare come la potenza  $P_{\text{CYCLE}}$  è funzione dei parametri di progetto  $T_{\text{DELAY}}$  e K, e delle variabili esterne  $V_{\text{TRASD}}$  (tensione del trasduttore, non predicibile) e  $V_{\text{OUT}}$  (tensione sul condensatore 27, anch'essa non predicibile). Massimizzare il valore di  $P_{\text{CYCLE}}$  significa dunque trovare i valori di  $T_{\text{DELAY}}$  e K ottimi, tali per cui la curva di  $P_{\text{CYCLE}}$  raggiunge un valore massimo, o prossimo al valore massimo, o un valore ottimo definibile a seconda della particolare applicazione ed esigenze di progetto.

La curva di  $P_{\text{CYCLE}}$  raggiunge un valore ottimo quando l'uscita del trasduttore 22 e l'ingresso del circuito rettificatore 24 mostrano la stessa impedenza (sono, cioè, adattate). La migliore efficienza di accoppiamento  $\eta_{\text{COUPLE}}$  tra il trasduttore 22 e il circuito rettificatore 24 è data da  $P_{\text{CYCLE}}^{\text{OPT}}/P_{\text{TRASD}}^{\text{MAX}}$ , dove  $P_{\text{CYCLE}}^{\text{OPT}}$  è il valore di  $P_{\text{CYCLE}}$  calcolato con  $T_{\text{DELAY}}$  e K ottimi, e  $P_{\text{TRASD}}^{\text{MAX}}$  è dato da  $(V_{\text{TRASD}})^2/4R_{\text{S}}$ .

L'ottimizzazione del valore di  $P_{CYCLE}$  consente di ottenere un valore ottimo dell'intervallo temporale  $T_{DELAY}$  e del fattore K (e viceversa) in funzione del valore di  $V_{TRASD}$  e  $V_{OUT}$ . Tuttavia, la richiedente ha verificato che la dipendenza di  $T_{DELAY}$  da  $V_{TRASD}$  e  $V_{OUT}$  è irrilevante a fini pratici, e il valore di efficienza di accoppiamento  $\eta_{COUPLE}$

si attesta a valori superiori al 95% per valori di  $V_{\text{TRASD}}$  e  $V_{\text{OUT}}$  di interesse pratico.

La figura 6 mostra l'andamento dell'efficienza di accoppiamento  $\eta_{\text{COUPLE}}$  al variare dei valori  $T_{\text{DELAY}}$  e K. Il grafico di figura 6 è facilmente ottenibile a partire dall'espressione di  $P_{\text{CYCLE}}$  variando i parametri  $T_{\text{DELAY}}$  e K (fissando i valori delle variabili esterne  $V_{\text{TRASD}}$  e  $V_{\text{OUT}}$ ). A ciascun valore di  $\eta_{\text{COUPLE}}$  corrisponde una coppia di valori  $T_{\text{DELAY}}$  e K. È dunque possibile ricavare in modo automatico la coppia di valori  $T_{\text{DELAY}}$  e K ottimi per ottenere un desiderato valore di efficienza di accoppiamento  $\eta_{\text{COUPLE}}$ . Nel grafico di figura 6, le zone più scure sono quelle in cui il valore di efficienza di accoppiamento  $\eta_{\text{COUPLE}}$  è maggiore; viceversa, le zone più chiare sono quelle in cui il valore di efficienza di accoppiamento  $\eta_{\text{COUPLE}}$  è più bassa (bassi valori di  $T_{\text{DELAY}}$  e elevati valori di K, o alti valori di  $T_{\text{DELAY}}$  e bassi valori di K).

La figura 7 mostra profili di corrente  $I_L$  nell'induttore 22b al variare dei valori scelti per  $T_{DELAY}$  e K, e con riferimento ad un valore di corrente ideale ottimo  $I_L^{OPT}$  (condizione di carico adattato in cui l'efficienza di accoppiamento è massima).

In particolare, la curva 65 mostra l'andamento ciclico, nel tempo t, del profili di corrente  $I_L$  per elevati valori di  $T_{DELAY}$  e K (ad esempio  $T_{DELAY}$ =100 $\mu$ s e K=5).

In questo caso si ha il vantaggio che la frequenza apertura/chiusura dei transistori HV 30a e 36a (0 transistori HV 31a e 38a) è bassa; questo si traduce in un da ridotto consumo di energia parte del circuito durante l'uso. Tuttavia, i valori rettificatore 24 corrente di picco Ip raggiunti dalla corrente IL secondo la curva 65 sono elevati e l'adattamento di impedenza tra trasduttore 22 e circuito rettificatore 24 non è ottimale, causando una efficienza di accoppiamento relativamente bassa ( $\eta_{COUPLE} \approx 72.3\%$ ).

La curva 67 mostra l'andamento ciclico, nel tempo t, del profili di corrente  $I_L$  per valori medi di  $T_{DELAY}$  e K (ad esempio  $T_{DELAY}$ =30 $\mu$ s e K=2.25). In questo caso, la frequenza di apertura/chiusura dei transistori HV 30a e 36a (o transistori HV 31a e 38a) è maggiore rispetto al caso della curva 65, ma si ha il vantaggio che i valori di corrente di picco sono minori rispetto al caso della curva 65 e l'efficienza di accoppiamento è elevata ( $\eta_{COUPLE} \approx 96.5\%$ ).

Infine, la curva 69 mostra l'andamento ciclico, nel tempo t, del profili di corrente  $I_L$  per piccoli valori di  $T_{\text{DELAY}}$  e K (ad esempio  $T_{\text{DELAY}}$ =10 $\mu$ s e K=1.3). In questo caso, l'efficienza di accoppiamento  $\eta_{\text{COUPLE}}$  è ancora maggiore rispetto al caso della curva 67 (circa 99.5%), ma con lo svantaggio che la frequenza di controllo dei transistori HV 30a e 36a (o transistori HV 31a e 38a) è eccessivamente

elevata, causando un eccessivo consumo di corrente da parte del circuito rettificatore 24, con conseguente riduzione del fattore di efficienza  $\eta_{\text{SCAV}}$  non sufficientemente compensata dall'incremento del valore di efficienza di accoppiamento  $\eta_{\text{COUPLE}}$ .

Ai fini dell'applicazione del circuito rettificatore 24 come interfaccia di raccolta di energia in un sistema di raccolta di energia ambientale, una scelta di compromesso, quale ad esempio quella della curva 67, è preferibile. Risulta evidente che altri ambiti applicativi della presente invenzione possono portare ad una scelta diversa dei valori di  $T_{DELAY}$  e K (e in generale con  $K\geq 1$ ).

La figura 8 mostra, mediante blocchi funzionali, un circuito di controllo 70 per comandare il transistore HV 30a e il transistore HV 36a al fine di implementare le condizioni operative delle figure 4a e 4b. Il circuito di controllo 70 opera, in particolare, per semionde positive  $(V_{\rm IN}^{+})$  del segnale di ingresso  $V_{\rm IN}$ . Il transistore LV 36b è polarizzato con tensione porta-sorgente  $(V_{\rm GS})$  pari a  $V_{\rm DD}$ , mentre il transistore LV 30b è polarizzato a tensione costante  $V_{\rm DD}$ , in modo tale da essere mantenuti sempre nello stato acceso. Il valore della tensione  $V_{\rm DD}$  è dunque scelto sulla base delle caratteristiche dei transistori 30b e 36b, in modo tale da controllarli in stato acceso.

Al fine di operare il transistore HV 31a e il transistore HV 38a per semionde negative del segnale di ingresso  $V_{\rm IN}$ , si utilizza una architettura circuitale analoga a quella mostrata per il circuito di controllo 70 (non mostrata in dettaglio in figura 8).

In maggior dettaglio, il circuito di controllo 70 comprende un primo rilevatore di corrente 72, accoppiato tra il terminale di sorgente S e il terminale di pozzo D del transistore LV 30b, per rilevare (durante la fase di figura 4a) quando la corrente  $I_{\rm ON}$  che scorre attraverso il transistore LV 30b (e, conseguentemente, anche attraverso il transistore HV 30a) supera la soglia  $I_{\rm TH}$ . Inoltre, il rilevatore di corrente 72 ha anche la funzione di generare, nella fase della figura 4a, una copia scalata della corrente che scorre nel transistore LV 30b, come meglio illustrato in seguito.

La figura 9 mostra in maggior dettaglio il primo rilevatore di corrente 72, secondo una forma di realizzazione. Con riferimento a tale figura 9, una prima porzione del rilevatore di corrente 72 comprende un comparatore 86 configurato per ricevere in ingresso i segnali di tensione presenti al terminale di sorgente S e al terminale di pozzo D del transistore LV 30b e generare in uscita un segnale digitale che assume livello logico basso quando  $I_{\text{ON}} > I_{\text{TH}}$  e livello logico alto quando  $I_{\text{ON}} > I_{\text{TH}}$  (o

viceversa). Il segnale in uscita dal comparatore 86 è fornito alla logica di controllo 60 che, quando è trascorso l'intervallo temporale TDELAY, apre il transistore HV 30a.

La durata dell'intervallo temporale  $T_{DELAY}$ , a seconda dell'ampiezza del segnale  $V_{TRASD}$  del trasduttore 22a, può essere determinato o dalla logica di controllo 60 o dal comparatore 86 appartenente al rilevatore di corrente 72.

In questo ultimo caso, il segnale in uscita dal comparatore 86 assume livello logico alto quando  $I_{ON} \ge I_{TH}$  e  $t \ge T_{DELAY}$ , e la logica di controllo 60 apre il transistore HV 30a in corrispondenza del fronte di salita del segnale digitale generato dal comparatore 86.

Una seconda porzione del rilevatore di corrente 72 comprende un anello con retroazione negativa includente un amplificatore 89 che controlla la corrente che scorre su un ramo di uscita 90 del rilevatore di corrente 72 agendo sul terminale di controllo di un transistore 91 appartenente al ramo di uscita 90 (cioè aprendo/chiudendo il transistore 91). La retroazione negativa assicura che la tensione all'ingresso invertente dell'amplificatore 89 sia sempre pari alla tensione presente all'ingresso non invertente dell'amplificatore 89. Il ramo di uscita 90 comprende inoltre un ulteriore transistore 92 avente dimensioni (intese come rapporto W/L) ridotte di un fattore F rispetto

alle rispettive dimensioni (intese come rapporto W/L) del transistore LV 36b.

Durante l'uso, scorre sempre corrente nel ramo di uscita 90. Nella fase di figura 4a la corrente è variabile e pari ad  $I_{\text{ON}}/F$ , mentre nella fase di figura 4b la corrente è costante e pari a  $I_{\text{P}}/F$ . Il dimensionamento del transistore 92 garantisce che la corrente che scorre nel ramo di uscita 90 sia una frazione 1/F della corrente  $I_{\text{ON}}$  (o del suo valore di picco  $I_{\text{P}}$ , come detto).

Tornando alla figura 8, il circuito di controllo 70 comprende inoltre un secondo rilevatore di corrente 74, accoppiato al terminale di sorgente S e al terminale di pozzo D del transistore LV 36b. Il secondo rilevatore di corrente 74 è analogo al primo rilevatore di corrente 72 ed è configurato per rilevare il valore di corrente che scorre attraverso il transistore LV 36b (e, di consequenza, attraverso il transistore HV 36a) durante la fase operativa di figura 4b. In particolare, il secondo rilevatore di corrente 74 collabora con la logica di controllo 60 al fine di rilevare se la corrente  $I_{\text{OUT}}$  raggiunge il valore minimo previsto  $I_{OFF}=I_P/K$ . Il segnale di uscita del secondo rilevatore di corrente 74, indicativo del valore di corrente  $I_{OUT}$ , è fornito in ingresso alla logica di controllo 60.

Il secondo rilevatore di corrente 74 riceve in ingresso la corrente  $I_{\text{ON}}/F$  (generata dal primo rilevatore di corrente 72, come precedentemente descritto), e commuta quando la corrente  $I_{\text{OUT}}$  raggiunge il valore minimo previsto dato da  $I_{\text{OFF}}=I_{\text{P}}/K$ .

Il circuito di controllo 70 comprende inoltre un primo dispositivo di pilotaggio 76 ed un secondo dispositivo di pilotaggio 78, accoppiati, rispettivamente, tra la logica controllo 60 e il terminale di controllo G transistore HV 30a e del transistore HV 36a. Il primo dispositivo di pilotaggio 76 e il secondo dispositivo di pilotaggio 78 sono, di per se, di tipo noto, e sono atti a controllare in apertura/chiusura i transistori 30a, 36a sulla base di un segnale di comando ricevuto dalla logica di controllo 60. In particolare, nella condizione operativa di figura 4a, la logica di controllo 60 comanda, tramite il primo dispositivo di pilotaggio 76, il transistore HV 30a in stato chiuso e, tramite il secondo dispositivo di pilotaggio 78, il transistore HV 36a in stato aperto. Quando, sulla base del segnale generato in uscita dal primo rilevatore di corrente 72, la logica di controllo 60 rileva che la corrente  $I_L=I_{ON}$  ha raggiunto (e/o superato) il valore di soglia  $I_{TH}$ , ed il tempo  $T_{DELAY}$  è trascorso, la logica di controllo 60 comanda, tramite il primo dispositivo di pilotaggio 76, il transistore HV 30a in stato aperto e,

tramite il secondo dispositivo di pilotaggio 78, il transistore HV 36a in stato chiuso. Quindi, la logica di controllo 60 monitora, sulla base del segnale ricevuto dal secondo rilevatore di corrente 74, il valore della corrente  $I_{\text{OUT}}$  per controllare il passaggio dalla condizione operativa corrente (di alimentazione del carico, figura 4b) alla condizione operativa di accumulo di energia nell'induttore 22b (figura 4a), non appena la corrente  $I_{\text{OUT}}$  raggiunge il valore  $I_{\text{OFF}}$ .

Il circuito di controllo 70 comprende inoltre un secondo rilevatore di tensione 80, un primo rispettivamente accoppiati tra il terminale di controllo G e sorgente S del transistore HV 30a e del transistore HV 36a. Il primo rilevatore di tensione 80 rileva la tensione presente tra il terminale di controllo G del transistore HV 30a e il terminale di sorgente S del transistore LV 30b (in questo caso, corrispondente al terminale di riferimento GND) e genera un segnale di uscita indicativo di tale tensione. Ιl segnale di uscita generato dal rilevatore di tensione 80 è fornito alla logica controllo 60. Analogamente, il secondo rilevatore di tensione 82 rileva la tensione presente tra il terminale di controllo G del transistore HV 36a e il terminale sorgente S del transistore LV 36b (in questo caso, corrispondente al nodo di ingresso 25') e genera un segnale di uscita indicativo di tale tensione. Sulla base dei segnali ricevuti dal primo e dal secondo rilevatore di tensione 80, 82, la logica di controllo 60 conosce lo stato acceso/spento dei transistori HV 30a e 36a, e controlla il passaggio dalla condizione operativa di figura 4a alla condizione operativa di figura 4b (e viceversa) inserendo opportuni tempi morti tra l'apertura (chiusura) del transistore HV 30a e la chiusura (apertura) del transistore HV 36a. Si evitano così fenomeni di conduzione incrociata e collegamento diretto tra il primo terminale di uscita 26' (a cui è accoppiato il condensatore 27/carico28) e il terminale a riferimento di terra GND.

Quanto qui descritto, sia da un punto di vista circuitale che di metodo per operare il circuito di controllo 70, è applicabile, in modo corrispondente ed evidente per il tecnico esperto ("skilled technician"), ai transistori HV 31a e 38a, che vengono operati per la rettificazione di semionde negative della tensione  $V_{TRASD}$  (i transistori LV 31b e 38b vengono mantenuti sempre accesi, in analogia a quanto descritto per i transistori LV 30b e 36b).

La figura 9 mostra, secondo una forma di realizzazione della presente invenzione, il primo rilevatore di corrente 72. Secondo la forma di realizzazione di figura 9, il primo rilevatore di corrente 72 comprende inoltre mezzi atti a

memorizzare il valore di picco  $I_p$  della corrente  $I_{ON}$  che attraversa, in uso, il transistore HV 30a. La figura 9 mostra inoltre, accoppiato al primo rilevatore di corrente 72, un comparatore 86 il cui segnale di uscita è indicativo, per la logica di controllo 60, se la corrente  $I_L=I_{ON}$  raggiunge (o supera) il valore di soglia impostato  $I_{TH}$ .

Il comparatore 86 è configurato per ricevere, in ingresso al terminale non invertente, il segnale di tensione presente al terminale di ingresso 25' del circuito rettificatore 24 (segnale  $V_{IN}^+$ ), e, in ingresso al terminale invertente, un segnale di tensione di soglia  $V_{TH}$  tale per cui  $V_{TH}=I_{TH}\cdot(R^{HV}_{ON}+R^{LV}_{ON})$ , dove, come già detto,  $R^{HV}_{ON}$  è la resistenza in stato acceso del transistore HV 30a e  $R^{LV}_{ON}$  è la resistenza in stato acceso del transistore LV 30b. Quando la tensione al terminale di ingresso 25' supera la soglia  $V_{TH}$ , l'uscita del comparatore 86 cambia stato, segnalando l'avvenuto superamento della soglia (e dunque indicando che  $I_L=I_{ON}\geq I_{TH}$ ).

Il primo rilevatore di corrente 72 comprende inoltre un transistore 87 avente un terminale di pozzo comune al terminale di pozzo del transistore LV 30b, e il terminale di sorgente accoppiato ad un condensatore 88 (il secondo terminale del condensatore 88 è collegato a tensione di riferimento GND). Il terminale di controllo G del

transistore 87 è collegato al terminale di controllo G del transistore HV 30a. In questo modo, il transistore HV 30a e il transistore 87 sono controllati in stato aperto/chiuso da uno stesso segnale  $V_{\text{GATE LS}}$ .

Durante l'intervallo temporale  $T_{\text{DELAY}}$  (situazione di figura 4a), il transistore HV 30a è chiuso (il segnale  $V_{\text{GATE\_LS}}$  ha valore alto e controlla in stato chiuso il transistore HV 30a). Allo stesso modo, anche il transistore 87, è chiuso. Il condensatore 88 viene pertanto caricato alla tensione presente al primo terminale di ingresso 25' del circuito rettificatore 24 (in figura 9 la tensione ai capi del condensatore 88 è indicata come  $V_{\text{C\_SAMPLE}}$ ).

Il primo rilevatore di corrente 72 comprende inoltre un ulteriore comparatore 89 ed un ramo 90 includente un transistore 91 e un transistore 92 collegati in serie tra loro tra un terminale 90' ed il terminale di riferimento GND. In particolare, il transistore 91 ha il proprio terminale di sorgente accoppiato al terminale di pozzo del transistore 92; inoltre, il transistore 92 ha il proprio terminale di controllo G collegato ad un terminale di alimentazione a tensione costante  $V_{DD}$ . Si noti che il transistore 92 è un transistore a bassa tensione ("low voltage"), ad esempio un CMOS. In particolare, il transistore 92 è atto ad operare con tensioni gate-source nell'intervallo 1-5 V, in particolare 2.5V-3.6 V, ad

esempio pari a 3.3 V. Altre tecnologie per transistori a bassa tensione prevedono tensioni operative leggermente più alte, ad esempio dell'ordine di 4-5 V. In particolare, il transistore 92 è dello stesso tipo del transistore LV 30b, ma è dimensionato in modo tale che il transistore 92 ha dimensioni (misurate in termini di fattore di forma W/L larghezza/lunghezza -) F-volte ridotte rispetto al transistore LV 30b ed è atto a condurre una corrente Fvolte inferiore rispetto al valore assunto da  $I_{\text{ON}}$  (corrente fluisce attraverso il transistore LV 30b). transistore LV 30b ed il transistore 92 hanno inoltre i rispettivi terminali di controllo connessi tra loro polarizzati alla tensione VDD. La retroazione negativa, realizzata mediante il comparatore 89 e il transistore 91, assicura che le tensioni di pozzo dei transistori 30b e 92 siano identiche; pertanto, la corrente che attraverso il transistore 92 assume pertanto valori pari al valore di  $I_{\text{ON}}$  scalati del fattore F (quando  $I_{\text{ON}}$  raggiunge il valore di picco  $I_p$  tale corrente sarà pari a  $I_p/F$ ). Si genera così una copia scalata del fattore F della corrente di picco I<sub>P</sub>. Poiché entrambi i transistori 30b e 92 sono transistori (es., CMOS) a bassa tensione (low voltage) essi forniscono ottime proprietà di adattamento ("matching"), così che il fattore F è minimamente influenzato da problemi di "mismatch" tra i transistori 30b e 92 (come invece lo

sarebbe nel caso in cui i transistor 30b e 92 fossero transistori ad alta tensione). Questo consente di ottenere una copia scalata della corrente di picco  $I_P$  stabile e con valore riproducibile.

Il comparatore 89 è collegato al terminale di sorgente del transistore 87 e, quando il transistore 87 è chiuso, esso riceve in ingresso (al terminale non invertente) la tensione del terminale di pozzo del transistore LV 30b, e in ingresso (al terminale invertente) il segnale presente in corrispondenza dei terminali di pozzo del transistore 92 e sorgente del transistore 91; l'uscita del comparatore 89 è accoppiata al terminale di controllo G del transistore 91. Il transistore 91 è sempre chiuso; il comparatore 89 polarizza il terminale di controllo del transistore 91 in modo che sul ramo 90 scorra la corrente  $I_{\rm ON}/F$ , come desiderato.

Il feedback negativo fornito dal comparatore 89 assicura che il segnale in ingresso al terminale non invertente del comparatore 89 e il segnale in ingresso al terminale invertente del comparatore 89 siano uguali, così che il transistore LV 30b e il transistore 92 abbiano lo stessa tensione sorgente-pozzo e sorgente-gate.

Quando il transistore HV 30a è aperto, anche il transistore 87 è aperto, e il condensatore 88 è in stato "floating", assicurando, durante l'intervallo di tempo

$T_{\text{CHARGE}}$ , una corrente di valore praticamente costante attraverso il transistore 92, e pari al valore  $I_P/F$ . Infatti, durante la fase di alimentazione del condensatore 27/carico 28, il condensatore 88 assicura il mantenimento della tensione  $V_{C\_SAMPLE}$  ai suoi capi, garantendo un segnale di ingresso sostanzialmente costante (a meno delle perdite del condensatore 88) all'ingresso non invertente del comparatore 89. Questo consente di mantenere inalterata la generazione della corrente  $I_{ON}/F$  sul ramo di uscita 90 del primo rilevatore di corrente 72 durante la fase di figura 4b (in questa fase, la corrente  $I_{ON}$  ha raggiunto il valore di picco  $I_P$ , e pertanto nel ramo di uscita 90 del primo rilevatore di corrente 72 scorre una corrente  $I_P/F$ ).

La figura 10a mostra graficamente l'andamento nel tempo della tensione sul terminale di pozzo del transistore LV 30b e del segnale di tensione  $V_{C\_SAMPLE}$  ai capi del condensatore 88. Questi segnali hanno lo stesso andamento e sono sovrapposti tra loro in figura 10a. La figura 10b mostra l'andamento nel tempo del segnale  $V_{GATE\_LS}$  applicato ai terminali di controllo del transistore HV 30a e del transistore 87.

Al termine di  $T_{CHARGE}$  la tensione  $V_{C\_SAMPLE}$  scende al valore  $I_{OFF} \cdot (R^{HV}_{ON} + R^{LV}_{ON})$  dove  $R^{HV}_{ON}$  e  $R^{LV}_{ON}$  sono, rispettivamente, le resistenze dei transistori HV 30a e LV 30b in stato acceso.

La figura 11 mostra, in maggior dettaglio, il secondo rilevatore di corrente 74. Il secondo rilevatore di corrente 74 di figura 11 comprende un transistore 97, avente un terminale di sorgente S collegato al primo terminale di ingresso 25' del circuito rettificatore 24, un terminale di controllo G collegato al terminale di controllo G del transistore LV 36b, e un terminale di pozzo D. In parallelo al transistore 97 è mostrato un resistore 98 rappresentativo della resistenza elettrica in stato acceso  $R_{\text{ON\_DMY}}$  del transistore 97. Analogamente, anche il transistore LV 36b e il transistore HV 36a sono mostrati con la propria rispettiva resistenza elettrica in stato acceso  $R_{\text{ON}}^{\text{LV}}$  e  $R_{\text{ON}}^{\text{HV}}$  collegata in parallelo (resistori 96 e 95).

Il secondo rilevatore di corrente 74 comprende inoltre un comparatore 99, avente un terminale invertente collegato tra il terminale di pozzo del transistore LV 36b e il terminale di sorgente del transistore HV 36a (per ricevere un segnale di uscita intermedio  $V_{\text{OUT\_INT}}$ ), ed un terminale non invertente collegato al terminale di pozzo del transistore 97 (per ricevere un segnale di riferimento intermedio  $V_{\text{REF INT}}$ ).

Il transistore 97 è una replica, scalata di un fattore J, del transistore LV 36b. Pertanto, i transistori 36b e 97 sono dimensionati in modo tale che il transistore 97 ha

dimensioni (misurate in termini di fattore di forma W/L - larghezza/lunghezza -) J-volte ridotte rispetto al transistore LV 36b ed è atto a condurre una corrente F-volte inferiore rispetto al valore assunto da  $I_{ON}$  (cioè  $I_{ON}/F$ ) durante la fase di figura 4a, e una corrente F-volte inferiore rispetto al valore di picco  $I_P$  (cioè  $I_P/F$ ) durante la fase di figura 4b.

Il segnale di tensione intermedio  $V_{\text{REF\_INT}}$  in ingresso al comparatore 99 (al terminale non invertente) è dato da (al tempo  $t_{\text{c}}$  di figura 5c):

$$V_{REF}INT = V_{IN}^+ - J \cdot R_{ONDMY} \cdot I_p / F$$

.

Il segnale di tensione  $V_{\text{OUT\_INT}}$  in ingresso al comparatore 99 (al terminale invertente) è dato da:

$$V_{\text{OUT}} = V_{\text{IN}}^+ - R^{\text{LV}}_{\text{ON}} \cdot I_{\text{OUT}}$$

dove  $I_{\text{OUT}}$  è la corrente che fluisce attraverso i transistori 36b e 36a quando sono in stato acceso.

Ne consegue che, poiché la condizione che determina il cambiamento dell'uscita del comparatore 99 è  $V_{\text{REF\_INT}} = V_{\text{OUT\_INT}}$ , il valore di  $I_{\text{OUT}}$  a cui si ha un cambiamento di uscita del comparatore 99 è proprio il valore di corrente  $I_{\text{OFF}}$  precedentemente introdotto. Pertanto, posto che  $I_{\text{OUT}} = I_{\text{OFF}}$ , si ottiene  $I_{\text{OFF}} = J/F \cdot I_p$ , e, definendo K = F/J, si ricava la condizione precedentemente indicata ( $I_{\text{OFF}} = I_p/K$ ) che determina la soglia di passaggio dalla condizione operativa di figura 4b alla condizione operativa di figura 4a.

Si fa notare che Poiché entrambi i transistori 36b e 97 sono transistori (es., CMOS) a bassa tensione (low voltage) dello stesso tipo e dunque essi garantiscono ottime proprietà di adattamento ("matching"), tali per cui il fattore J è minimamente influenzato da problemi di "mismatch" tra i transistori 36b e 97 (come invece lo sarebbe nel caso in cui entrambi i transistori fossero transistori ad alta tensione). Stabilizzare J attorno ad un valore desiderato corrisponde a stabilizzare il valore di K attorno al valore scelto. Inoltre, poiché anche il fattore F è stabile, il parametro K risulta avere uno spread minimo intorno al valore scelto e desiderato.

Le figure 12a-12c mostrano, utilizzando una stessa scala temporale, l'andamento dei segnali  ${\rm V_{IN}}^+$ ,  ${\rm V_{REF\_INT}}$ ,  ${\rm V_{OUT}}$  (figura 12a); l'andamento del segnale  ${\rm V_{OUT\_COMP}}$  generato in uscita dal comparatore 99 (figura 12b); e l'andamento del segnale di corrente  ${\rm I_L}$  (figura 12c).

Con riferimento alla figura 12a, si nota che in corrispondenza di un fronte di salita (ideale) del segnale di ingresso  $V_{\rm IN}^+$  corrisponde una progressiva discesa del segnale  $V_{\rm REF\_INT}$  ed una corrispondente progressiva salita del segnale  $V_{\rm OUT}$ . Quindi, con ulteriore riferimento alla figura 12b, quando  $V_{\rm REF\_INT}=V_{\rm OUT}$  (istante temporale  $t_x$ ), l'uscita  $V_{\rm OUT\_COMP}$  del comparatore 99 cambia stato e passa da uno stato a valore basso ad uno stato a valore alto. Il

cambiamento di stato è riconosciuto dalla logica di controllo 60, che controlla opportunamente gli interruttori (transistori) HV 30a e 36a come precedentemente descritto.

La figura 12c mostra la corrente  $I_L$ , in particolare durante l'intervallo temporale  $T_{CHARGE}$  (condizione operativa di figura 4b). La corrente  $I_L = I_{OUT}$  decresce da un valore massimo  $I_P$  ad un valore minimo  $I_{OFF}$ , alimentando il condensatore 27/carico 28.

Quanto precedentemente descritto è valido, in modo del tutto equivalente, per il controllo degli interruttori (transistori) HV 31a e 38a, per polarità negative della tensione di ingresso  $V_{\rm IN}$ .

La logica di controllo 60 implementa il metodo di controllo dei transistori HV 30a, 36a, 31a, e 38a precedentemente descritto e mostrato in modo schematico in figura 13, mediante diagramma di flusso.

Con riferimento alla figura 13, fase 100, i transistori HV 30a e 31a vengono chiusi. I transistori HV 36a e 38 invece, vengono aperti. Si considera, nel seguito della descrizione, che i transistori LV 30b, 31b, 36b e 38b siano sempre in stato chiuso (situazione di figura 3b).

In questo modo, l'induttore 22b viene caricato tramite la corrente  $I_L = I_{ON}$  che scorre attraverso i transistori HV 30a e 31a.

Il valore di corrente  $I_L = I_{ON}$  viene monitorato (fase 102) per rilevare se essa raggiunge (o supera) il valore di soglia  $I_{TH}$  richiesto. Allo stesso tempo, la logica di controllo 60 monitora l'intervallo temporale  $T_{DELAY}$ . In questo caso, il tempo  $t_0$  di inizio dell'intervallo temporale  $T_{DELAY}$  corrisponde all'istante di chiusura dei transistori HV 30a, 31a, secondo la fase 100.

Nel caso in cui la corrente  $I_L$  non abbia raggiunto la soglia  $I_{TH}$  o non sia trascorso il tempo  $T_{DELAY}$  (uscita NO dalla fase 102), si attende che entrambe queste condizioni siano soddisfatte e la logica di controllo 60 mantiene il sistema 20 negli stati 100, 102 fintantoché la condizione  $I_L \!\! \geq \! I_{TH}$  viene soddisfatta. Viceversa (uscita SI dalla fase 102), si passa alla successiva fase 104.

Durante la fase 104 si verifica se la tensione di ingresso  $V_{\rm IN}$  ha polarità positiva o negativa. Questa operazione può essere effettuata mediante il comparatore 86, che riceve in ingresso il segnale  $V_{\rm IN}^+$ .

Come già detto, un circuito equivalente a quello mostrato in figura 9 è accoppiato (in modo non mostrato in figura) al transistore HV 31a, ed utilizzato in modo analogo per verificare se la tensione di ingresso  $V_{\rm IN}$  ha polarità negativa.

Nel caso in cui la tensione di ingresso  $V_{\text{IN}}$  ha polarità positiva, si passa alla fase 106 (uscita SI dalla

fase 104), in cui i transistori HV 30a (ed eventualmente LV 30b) vengono aperti, alimentando il condensatore 27/carico 28 tramite i transistori HV 36a e LV 36b.

Nel caso in cui la tensione di ingresso  $V_{\rm IN}$  ha polarità negativa, si passa invece alla fase 108 (uscita NO dalla fase 104), in cui il condensatore 27/carico 28 è alimentato tramite i transistori LV 38b e HV 38a.

L'uscita dalle fasi 106 e 108 porta alla fase 110, in la logica di controllo 60 monitora il valore di corrente  $I_{\text{OUT}}$  che fluisce attraverso il transistore LV 36b (o il transistore LV 38b, a seconda della polarità della tensione di ingresso V<sub>IN</sub>) verso l'uscita del rettificatore 24, per rilevare se la corrente  $I_{\text{OUT}}$  assume un valore pari a I<sub>OFF</sub>. Fintantoché I<sub>OUT</sub>>I<sub>OFF</sub>, la logica di controllo 60 mantiene il sistema 20 nella fase di caricamento del condensatore 27/alimentazione del carico 28. Quando  $I_{OUT}=I_{OFF}$ , si torna alla fase 100. Le fasi 100-104 sono eseguite, come descritto con riferimento alle figure 5a-5c, in un intervallo temporale pari ad almeno TDELAY fintantoché la corrente nell'induttore raggiunge la soglia I<sub>TH</sub> mentre le fasi 106-110 sono eseguite in un intervallo temporale pari a  $T_{CHARGE}$ .

La logica di controllo 60 è, ad esempio, un microcontrollore, configurato per pilotare i transistori HV

30a, 31a, 36a e 38a al fine di eseguire le fasi del metodo di figura 13.

La figura 14 mostra un veicolo 200 comprendente il sistema di raccolta di energia 20 di figura 3. Il veicolo 200 è, in particolare, una automobile. Risulta evidente tuttavia, che il sistema di raccolta di energia 20 può essere utilizzato in qualsiasi veicolo 200 o in sistemi o apparecchi ("apparatuses") diversi da un veicolo. In particolare il sistema di raccolta di energia 20 può trovare applicazione in generici sistemi in cui sia desiderabile raccogliere ("harvest"), immagazzinare, ed utilizzare energia ambientale, in particolare mediante conversione di energia meccanica in energia elettrica.

Con riferimento alla figura 14, il veicolo 200 comprende uno o più trasduttori 22 accoppiati in modo noto ad una porzione del veicolo 200 soggetta a stress meccanici e/o vibrazioni, per convertire tali stress meccanici e/o vibrazioni in corrente elettrica.

Il sistema di raccolta di energia 20 è collegato ad uno o più carichi elettrici 28a, ..., 28n, ad esempio tramite interposizione di un convertitore DC-DC. In particolare, secondo una applicazione della presente invenzione, i carichi elettrici 28a, ..., 28n comprendono sensori TPM 250 ("tyre parameters monitoring") per il monitoraggio di parametri di pneumatici 202. In questo

caso, i sensori TPM 250 sono accoppiati ad una porzione interna degli pneumatici 202 del veicolo 200. Analogamente, trasduttori 22 anche (ad esempio, di elettromagnetico, o piezoelettrico) sono accoppiati ad una porzione interna degli pneumatici 202. La sollecitazione dei trasduttori 22 durante la marcia del veicolo 200 causa la produzione di un segnale di corrente elettrica/tensione uscita dal trasduttore 22 mediante conversione in dell'energia meccanica in energia elettrica. L'energia elettrica così prodotta è immagazzinata, precedentemente descritto, nell'elemento di accumulo 27 e fornita, tramite il convertitore DC-DC eventualmente presente, ai sensori TPM 250.

Secondo una forma di realizzazione della presente invenzione, il sistema di raccolta di energia 20, comprendente uno o più trasduttori, e i sensori TPM 250, vengono incollati all'interno di uno o più pneumatici 202. L'urto dello pneumatico 202 sul terreno durante il moto del veicolo 200 consente la produzione di energia elettrica.

Alternativamente a quanto mostrato in figura 14, il sistema di raccolta di energia 20, può essere disposto in qualsiasi altra porzione del veicolo 200, e/o utilizzato per alimentare un carico elettrico diverso dai o ulteriore ai sensori TPM 250.

Un'altra possibile applicazione del sistema di raccolta di energia 20 è la generazione di energia elettrica sfruttando l'energia meccanica prodotta da un individuo durante una camminata o una corsa. In questo caso, il sistema di raccolta di energia 20 è disposto all'interno delle scarpe 300 di tale individuo (ad esempio, all'interno della suola) come mostrato schematicamente in figura 15. Nei sistemi rivolti al fitness, ove risulta particolarmente interessante contare i passi, è utile recuperare energia dalle vibrazioni indotte dalla passeggiata/corsa per poter alimentare senza l'uso batteria sensori di accelerazione e/o trasmettitori RFID in grado di comunicare con telefoni cellulari, dispositivi di riproduzione di musica, o con qualsiasi altro apparecchio interessato ad un informazione sui passi percorsi.

Da un esame delle caratteristiche del trovato realizzato secondo la presente invenzione sono evidenti i vantaggi che essa consente di ottenere.

In particolare, il parametro K ha valore altamente riproducibile (spread minimo), così da aumentare il rendimento, la robustezza e l'efficienza del sistema 20, minimizzando il mismatch tra le polarità positive e negative del segnale del trasduttore ed evitando fenomeni di inversione del flusso di corrente dal condensatore 27

verso i terminali di ingresso 25', 25" del circuito rettificatore 24.

Inoltre, poiché la durata dell'intervallo temporale  $T_{\text{DELAY}}$  è (tipicamente) costante, il rettificatore 24 opera a duty cycle del segnale di apertura/chiusura del primo e del secondo interruttore 30, 31 costante; questo consente di ottenere valori di efficienza  $\eta_{\text{SCAV}}$  (efficienza del rettificatore 24, avente la funzione di interfaccia di raccolta del sistema 20) particolarmente elevati (la richiedente ha verificato valori di efficienza superiori al 95% indipendentemente dai valori assunti da  $V_{\text{TRASD}}$  e  $V_{\text{OUT}}$ ).

L'efficienza di raccolta è altresì elevata anche quando l'ampiezza del segnale  $V_{TRASD}$  del trasduttore 22 è inferiore al valore di tensione immagazzinata nel condensatore 27, superando una limitazione dell'architettura di rettificazione a ponte di diodi.

Inoltre, poiché nel caso di trasduttore 22 di tipo elettromagnetico il rettificatore 24 sfrutta l'induttore 22b proprio del trasduttore 22, l'efficienza di raccolta è elevata anche quando l'ampiezza del segnale del trasduttore è bassa. Si supera in questo modo la limitazione imposta dai rettificatori a ponte di diodi che richiedono una tensione del trasduttore  $V_{TRASD}$  maggiore di  $2V_{TH\_D}$ , con  $V_{TH\_D}$  tensione di soglia dei diodi del rettificatore.

Utilizzando una tecnologia HV ("high voltage") per il condensatore 27 e per l'interfaccia di raccolta è possibile immagazzinare elevate tensioni, e quindi elevata energia, nel condensatore, aumentando di conseguenza l'autonomia di funzionamento dei sensori TPM 250.

Il metodo descritto, che prevede la scelta di valore ottimo di TDELAY e di K, consente di implementare un controllo attivo (del valor medio e dei "ripple") della corrente fornita dal trasduttore, e consente di ottenere un adattamento di impedenza ottimo tra il trasduttore 22 e l'interfaccia di raccolta 24. Ouesto assicura efficienza n<sub>SCAV</sub> dell'interfaccia di raccolta 24b elevata indipendentemente dalla velocità di rotazione dei pneumatici 202 e dalle condizioni di immagazzinamento dell'energia nel condensatore 27.

Inoltre, come detto, il valore dell'intervallo  $T_{\text{DELAY}}$  può essere variato a seconda della particolare applicazione in cui il rettificatore 24 opera. Il rettificatore 24 trova quindi impiego in sistemi diversi dal sistema di raccolta di energia 20, basati su trasduttori elettromagnetici di qualsiasi tipo.

Inoltre, il circuito rettificatore 24 può essere utilizzato con trasduttori di altro tipo, mediante interposizione di un opportuno circuito tra il trasduttore

e il circuito rettificatore atto a fornire ("provide") un accumulatore di energia analogo all'induttore 22b.

Inoltre, il rettificatore 24 secondo la presente invenzione e il sistema di raccolta di energia 20 sono di tipo completamente integrato, e pertanto richiedono minimo spazio di installazione.

Infine, il recupero di energia ambientale avviene anche quando il segnale del trasduttore è inferiore al valore di tensione accumulato sul condensatore di uscita, cosa che non è possibile utilizzando un'interfaccia a ponte di diodi di tipo noto come mostrato in figura 1. Secondo la presente invenzione, l'interfaccia di raccolta 24 è dunque in grado di recuperare energia anche quando la potenza fornita dal trasduttore è molto bassa.

Risulta infine chiaro che a quanto qui descritto ed illustrato possono essere apportate modifiche e varianti senza per questo uscire dall'ambito di protezione della presente invenzione, come definito nelle rivendicazioni allegate.

In particolare, secondo una forma di realizzazione della presente invenzione, il circuito rettificatore 24 può comprendere un numero di transistori diverso da quanto descritto. Ad esempio, il circuito rettificatore 24 può essere un rettificatore a mezza onda ("half-wave rectifier"), comprendente solo gli interruttori che operano

per polarità positive del segnale di ingresso VIN (cioè gli interruttori 30a, 30b, 36a, e 36b) o solo gli interruttori che operano per polarità negative del segnale di ingresso interruttori 31a, 31b, 38a, (cioè gli L'utilizzo di un rettificatore half-wave può vantaggioso nel caso in cui il segnale di ingresso V<sub>IN</sub> sia di tipo noto e comprendente solo semionde positive (o negative). Il suo utilizzo è tuttavia sconsigliato, (anche se possibile) in sistemi di raccolta di energia in quanto parte del segnale di ingresso andrebbe perso, a scapito dell'efficienza del sistema nel suo complesso.

Inoltre, le condizioni t> $T_{\text{DELAY}}$  e  $I_{\text{L}}$ > $I_{\text{TH}}$  espresse con riferimento alla condizione operativa di figura 4a non sono sempre entrambe necessarie. In particolare, per segnali di tensione generati da trasduttori 22 di tipo noto il valore di tensione raggiunge sempre picchi tali da consentire il superamento della soglia  $I_{\text{TH}}$  entro il tempo  $T_{\text{DELAY}}$ . Inoltre, una scelta opportuna di  $T_{\text{DELAY}}$  garantisce sempre, a fini pratici, il raggiungimento di una soglia minima accettabile  $I_{\text{TH}}$ .

Inoltre, possono essere presenti una pluralità di trasduttori 22, tutti dello stesso tipo o di tipo diverso tra loro, indifferentemente. Ad esempio, il/i trasduttore/i possono essere scelti nel gruppo comprendente: trasduttori elettrochimici (atti a convertire energia chimica in un

segnale elettrico), elettromeccanici (atti a convertire energia meccanica in un segnale elettrico), elettroacustici (atti a convertire variazioni di pressione in un segnale elettrico), elettromagnetici (atti a convertire un campo magnetico in un segnale elettrico), fotoelettrici (atti a convertire energia luminosa in un segnale elettrico), elettrostatici, termoelettrici, piezoelettrici, termoacustici, termomagnetici, termoionici.

## RIVENDICAZIONI

1. Interfaccia di raccolta di energia ("Energy scavenging interface") (24) avente un primo e un secondo terminale di ingresso (25', 25") collegabili ad un primo elemento di accumulo (22b), ed un primo e un secondo terminale di uscita (26', 26") collegabili ad un secondo elemento di accumulo (27), in cui il primo e il secondo terminale di ingresso (25', 25") sono atti a ricevere un segnale elettrico di ingresso ( $V_{\rm IN}$ ), e il primo e il secondo terminale di uscita sono atti a fornire al secondo elemento di accumulo un segnale di uscita ( $I_{\rm OUT}$ ,  $V_{\rm OUT}$ ),

l'interfaccia di raccolta di energia (24) comprendendo un primo e un secondo interruttore (30a, 30b; 31a, 31b) collegati in serie tra loro, tra il primo terminale di ingresso (25'; 25") ed il secondo terminale di uscita (26"); un terzo e un quarto interruttore (36a, 36b; 38a, 38b), collegati in serie tra loro, tra il primo terminale di ingresso (25'; 25") e il primo terminale di uscita (26');

e una logica di controllo (60, 70) configurata per:

- operare il primo e il secondo interruttore (30a, 30b; 31a, 31b) in uno stato chiuso e il terzo interruttore (36a; 38a) in uno stato aperto per un primo intervallo temporale avente almeno una prima durata temporale ( $T_{DELAY}$ ) in cui il primo elemento di accumulo (22b) accumula carica

elettrica;

- acquisire una copia scalata ( $I_p/K$ ) di un valore di picco ( $I_p$ ) della corrente elettrica accumulata nell'elemento di accumulo (22b) durante il primo intervallo temporale ( $T_{DELAY}$ );

- operare il primo interruttore (30a; 31a) in uno stato aperto e il terzo e il quarto interruttore (36a, 36b; 38a, 38b) in uno stato chiuso generando il segnale di uscita che alimenta ("supplies") il secondo elemento di accumulo;

- mantenere il primo interruttore (30a; 31a) nello stato aperto e il terzo e il quarto interruttore (36a, 36b; 38a, 38b) nello stato chiuso fintantoché ("as long as") il valore in corrente del segnale di uscita ( $I_{\text{OUT}}$ ) è maggiore del valore di detta copia scalata ( $I_{\text{p}}/K$ ) del valore di picco.

- 2. Interfaccia di raccolta di energia secondo la rivendicazione 1, comprendente inoltre un primo dispositivo rilevatore di segnale elettrico (72), accoppiato a terminali di conduzione del secondo interruttore (30b; 31b), configurato per rilevare, durante il primo intervallo temporale, se la corrente elettrica nell'elemento di accumulo (22b) raggiunge un valore di soglia ( $I_{TH}$ ),

la logica di controllo (60, 70) essendo inoltre configurata per mantenere il primo e il secondo

interruttore (30a, 30b; 31a, 31b) in stato chiuso e il terzo interruttore (36a; 38a) in stato aperto fintantoché la carica elettrica accumulata nell'elemento di accumulo (22b) raggiunge il primo valore di soglia ( $I_{TH}$ ).

- 3. Interfaccia di raccolta di energia secondo la rivendicazione 1 o 2, comprendente inoltre: