(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-120718

(P2006-120718A)

(43) 公開日 平成18年5月11日(2006.5.11)

| (51) Int.C1.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>HO1L 27/092 (2006.01)</b>  | HO1L 27/08 | 321D 4M104  |

| <b>HO1L 21/8238 (2006.01)</b> | HO1L 21/28 | 301R 5F048  |

| <b>HO1L 21/28 (2006.01)</b>   | HO1L 29/78 | 301G 5F140  |

| <b>HO1L 29/78 (2006.01)</b>   | HO1L 29/58 | G           |

| <b>HO1L 29/423 (2006.01)</b>  |            |             |

審査請求 有 請求項の数 6 O L (全 11 頁) 最終頁に続く

|           |                              |          |           |

|-----------|------------------------------|----------|-----------|

| (21) 出願番号 | 特願2004-304584 (P2004-304584) | (71) 出願人 | 000003078 |

| (22) 出願日  | 平成16年10月19日 (2004.10.19)     |          | 株式会社東芝    |

|          |           |

|----------|-----------|

| (74) 代理人 | 100075812 |

|          | 弁理士 吉武 賢次 |

| (74) 代理人 | 100088889 |

|          | 弁理士 橋谷 英俊 |

| (74) 代理人 | 100082991 |

|          | 弁理士 佐藤 泰和 |

| (74) 代理人 | 100096921 |

|          | 弁理士 吉元 弘  |

| (74) 代理人 | 100103263 |

|          | 弁理士 川崎 康  |

最終頁に続く

(54) 【発明の名称】半導体装置およびその製造方法

## (57) 【要約】

【課題】 シリコン基板上に形成されるトランジスタの導電型によらず、移動度を向上させる。

【解決手段】 半導体装置は、シリコン基板1上にPMOSトランジスタ2と、NMOSトランジスタ3とを備えている。いずれのトランジスタも、シリコン基板1上に形成されるゲート絶縁膜4と、このゲート絶縁膜4上に形成されるゲート電極5a, 5bとを有する。ゲート電極5a, 5bは例えばタングステン(W)で形成されている。PMOSトランジスタ2のゲート電極5aとNMOSトランジスタ3のゲート電極5bとに、互いに異なる応力を持たせる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

シリコン基板上に絶縁層を介して形成される金属を含む導電層を備え、前記導電層は、不純物を注入して形成され他の領域とは異なる応力を持つ応力変化領域を有することを特徴とする半導体装置。

**【請求項 2】**

シリコン基板上に形成される絶縁層と、前記絶縁層上に形成される第1導電層と、前記第1導電層上に形成される金属を含む第2導電層と、を備え、前記第2導電層は、不純物を注入して形成され他の領域とは異なる応力を持つ応力変化領域を有することを特徴とする半導体装置。 10

**【請求項 3】**

前記第1および第2導電層はゲート電極の少なくとも一部を構成しており、前記第1導電層は、前記ゲート電極の仕事関数を決定し、前記第2導電層は、前記ゲート電極の下方の前記シリコン基板内に形成されるチャネル領域の応力を制御することを特徴とする請求項2に記載の半導体装置。

**【請求項 4】**

前記第1および第2導電層の間に形成されるバリア層を備え、前記第1導電層は、ポリシリコン層であることを特徴とする請求項2に記載の半導体装置。 20

**【請求項 5】**

シリコン基板上に絶縁層を介して、金属を含む導電層を形成し、前記導電層の一部に、不純物を注入して、他の領域とは異なる応力を持つ応力変化領域を形成することを特徴とする半導体装置の製造方法。

**【請求項 6】**

シリコン基板上に絶縁層を形成し、前記絶縁層上に第1導電層を形成し、前記第1導電層上に、金属を含む第2導電層を形成し、前記第2導電層は、不純物を注入して形成され他の領域とは異なる応力を持つ応力変化領域を有することを特徴とする半導体装置の製造方法。 30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、シリコン基板上に絶縁層を介して導電層を形成する半導体装置およびその製造方法に関する。

**【背景技術】****【0002】**

半導体集積回路の微細化が進むにつれて、従来のポリシリコン電極に変わって、ゲート空乏層のない金属材料からなるゲート電極が用いられるようになった。シリコン半導体の駆動力を向上させる手法として、チャネル部分に応力を加えて歪ませて移動度を向上させ、トランジスタの駆動電流の増加を図ることができる（特許文献1参照）。 40

**【0003】**

しかしながら、金属材料からなるゲート電極が本来持つ応力は、圧縮応力と引っ張り応力のいずれか一方だけであり、PMOSトランジスタとNMOSトランジスタのいずれか一方しか移動度を向上させることができず、移動度が向上するトランジスタとは異なるトランジスタについては、逆に移動度が低下するおそれもあった。

**【特許文献1】特開2002-93921公報****【発明の開示】****【発明が解決しようとする課題】****【0004】**

本発明は、シリコン基板上に形成されるトランジスタの導電型によらず、移動度を向上させることができる半導体装置およびその製造方法を提供する。

【課題を解決するための手段】

【0005】

本発明の一態様によれば、シリコン基板上に絶縁層を介して形成される金属を含む導電層を備え、前記導電層は、不純物を注入して形成され他の領域とは異なる応力を持つ応力変化領域を有する。

【0006】

また、本発明の一態様によれば、シリコン基板上に形成される絶縁層と、前記絶縁層上に形成される第1導電層と、前記第1導電層上に形成される金属を含む第2導電層と、を備え、前記第2導電層は、不純物を注入して形成され他の領域とは異なる応力を持つ応力変化領域を有する。

【発明の効果】

【0007】

本発明によれば、導電層の一部のみの応力を変化させるため、圧縮応力と引っ張り応力の両方の特性を持つことができ、PMOSトランジスタとNMOSトランジスタのいずれであっても、移動度を向上させることができる。

【発明を実施するための最良の形態】

【0008】

以下、図面を参照しながら、本発明の一実施形態について説明する。

【0009】

(第1の実施形態)

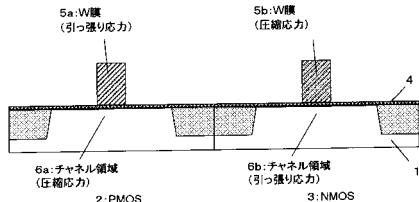

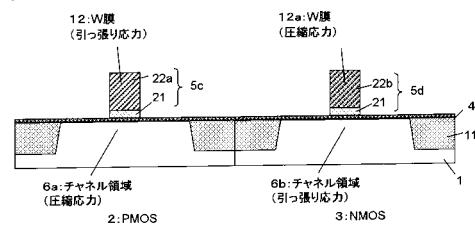

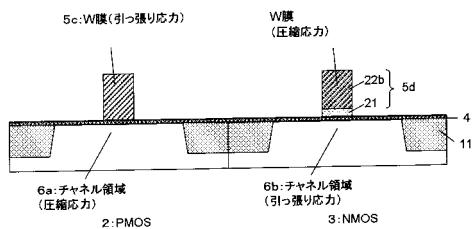

図1は本発明の第1の実施形態による半導体装置の断面構造を示す断面図である。図1の半導体装置は、シリコン基板1上に隣接して形成されるPMOSトランジスタ2と、NMOSトランジスタ3とを備えている。いずれのトランジスタも、シリコン基板1上に形成されるゲート絶縁膜4と、このゲート絶縁膜4上に形成されるゲート電極5a, 5bとを有する。ゲート電極5a, 5bは例えばタンゲステン(W)で形成されている。

【0010】

PMOSトランジスタ2のゲート電極5aは引っ張り応力を持つのに対して、NMOSトランジスタ3のゲート電極5bは圧縮応力を持っている。チャネル領域6a, 6bには、ゲート電極5a, 5bとは逆の応力が働くため、PMOSトランジスタ2のチャネル領域6aは圧縮応力を持ち、NMOSトランジスタ3のチャネル領域6bは引っ張り応力を持つ。

【0011】

PMOSトランジスタ2は、そのチャネル領域6aが圧縮応力を持つ方が移動度がより向上する。同様に、NMOSトランジスタ3は、そのチャネル領域6bが引っ張り応力を持つ方が移動度がより向上する。これにより、図1の半導体装置は、PMOSトランジスタ2とNMOSトランジスタ3の双方とも、移動度を向上できる。

【0012】

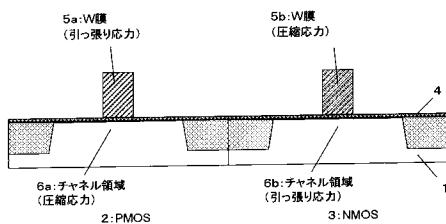

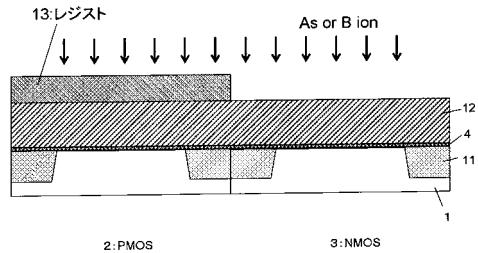

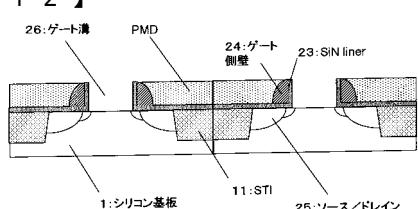

図2～図4は図1の半導体装置の製造工程の一例を示す断面図である。以下、これらの図を用いて、図1の半導体装置の製造工程を順に説明する。まず、シリコン基板1上に、バッファ膜を介して、マスクとなるシリコン窒化膜を堆積する。次に、レジストを用いたパターン転写法により、シリコン窒化膜、バッファ膜およびシリコン基板1を所定の深さまでエッチングする。

【0013】

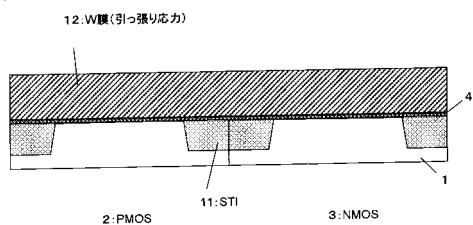

次に、レジストを除去した後、全面にシリコン酸化膜を堆積し、表面をCMP(Chemical Mechanical Polishing)等で平坦化する。次に、シリコン窒化膜とバッファ膜を除去して素子分離(STI: Sharrow Trench Isolation)11を形成する(図2)。

【0014】

次に、基板全面にゲート絶縁膜4を形成する(図2)。ゲート絶縁膜4の厚さは例えば3nm以下である。ゲート絶縁膜4として、例えばシリコン基板1を熱酸化して熱酸化膜を

形成してもよい。あるいは、窒化させて酸窒化膜や窒化膜を形成してもよい。あるいは、表面処理を行った後に、ハフニウム酸化膜やハフニウムシリケート等の高誘電体膜を形成してもよい。

【0015】

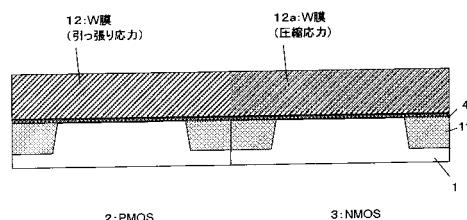

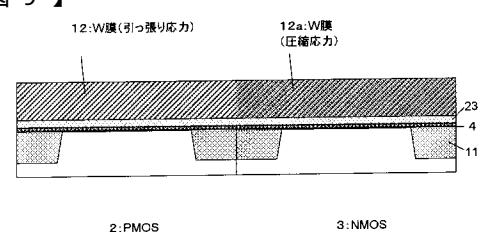

次に、ゲート絶縁膜4上に電極用の金属層を形成する。例えば、引っ張り応力(tensile stress)を持つタンゲステン(W)膜12を形成する(図2)。膜厚は例えば約100nmとする。

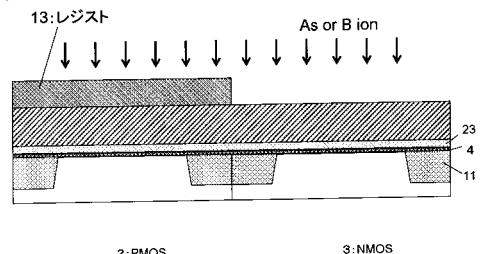

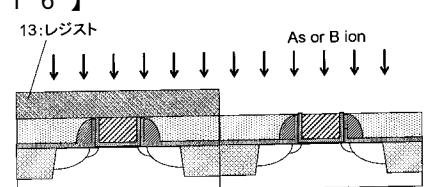

【0016】

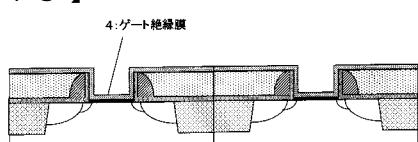

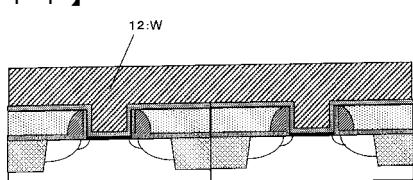

次に、レジスト13等により、引っ張り応力を持続させる領域をマスクする(図3)。例えば、PMOSトランジスタ2の形成領域をレジスト13で覆い、NMOSトランジスタ3の形成領域のタンゲステン膜12を露出させる。そして、タンゲステン膜12にヒ素(As)やボロン(B)等の不純物イオンを注入する。不純物イオンを注入したタンゲステン膜12aは、引っ張り応力が解放されて応力が無視できる大きさになるか、あるいは圧縮応力(compressive stress)を持つ領域に変化する(図4)。

【0017】

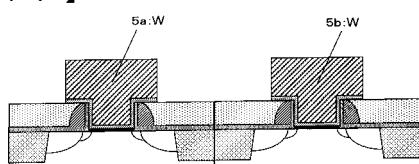

次に、パターニングとRIE等の異方性エッチングとを用いて、タンゲステン膜12, 12aを加工してゲート電極5a, 5bを形成する(図1)。ゲート電極5a, 5bの幅は、約10nmの微細パターンから約10μm以上の幅広パターンまで、必要に応じて決定される。

【0018】

引っ張り応力を持つタンゲステン膜12からなるPMOSトランジスタ2のゲート電極5aに対向配置されるチャネル表面は圧縮応力を持ち、圧縮応力を持つタンゲステン膜12aからなるNMOSトランジスタ3のゲート電極5bに対向配置されるチャネル表面は引っ張り応力を持つ。

【0019】

図1の構造が形成されると、公知の手法で、エクステンション拡散層の形成、ゲート電極5a, 5bの側壁の形成、ソース/ドレイン拡散層の形成などを行う。その後、基板全面に層間膜を形成した後、コンタクトプロセスにより配線を形成し、トランジスタを完成させる。

【0020】

このように、第1の実施形態では、PMOSトランジスタ2のゲート電極5aとNMOSトランジスタ3のゲート電極5bとに、互いに異なる応力を持たせるため、PMOSトランジスタ2のチャネル表面とNMOSトランジスタ3のチャネル表面の応力も互いに逆になる。したがって、両トランジスタとも、応力により移動度を向上させることができ、トランジスタの駆動電流を増大できる。

【0021】

(第2の実施形態)

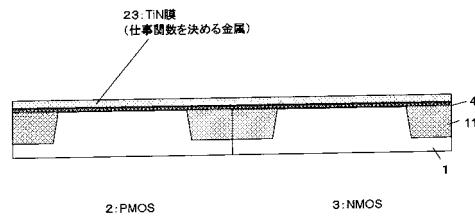

上述した第1の実施形態は、ゲート電極がタンゲステン膜のみからなる単層構造であるため、トランジスタの閾値電圧等の電気特性も、タンゲステン膜の性質に依存することになる。より詳細には、閾値等の電気特性は、ゲート絶縁膜4に接する金属の仕事関数に依存する。そこで、第2の実施形態では、ゲート電極を積層構造にして、電気特性を決める金属層と、応力を決める金属層とを別個に設ける。

【0022】

図5は本発明の第2の実施形態による半導体装置の断面構造を示す断面図である。図5の半導体装置は、ゲート電極5c, 5dの構造が図1の半導体装置のゲート電極5a, 5bと異なる。図5のゲート電極5c, 5dは、2層構造になっており、ゲート絶縁膜4上に形成される第1金属層21と、第1金属層21上に形成される第2金属層22a, 22bとを有する。

【0023】

第1金属層21は、ゲート絶縁膜4に接しており、トランジスタの電気特性を決定する

10

20

30

40

50

。第1金属層21は例えば窒化チタン(TiN)で形成され、その膜厚は約5nmである。第2金属層22a, 22bは、チャネル表面の応力を決定するものであり、第1の実施形態と同様にタンゲステンで形成され、その膜厚は約100nmである。

#### 【0024】

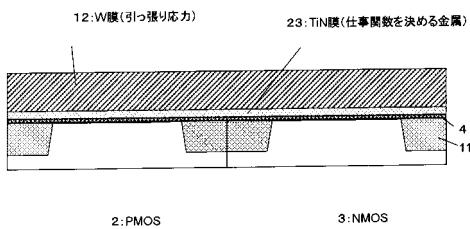

図6～図9は図5の半導体装置の製造工程の一例を示す断面図である。以下、これらの図を用いて、図5の半導体装置の製造工程を順に説明する。シリコン基板1上にゲート絶縁膜4を形成した後、例えばTiN23を約5nm形成し(図6)、その上面に例えばタンゲステン(W)12を約100nm積層する(図7)。

#### 【0025】

その後の工程は第1の実施形態とほとんど同じである。簡単に説明すると、PMOSトランジスタ2の形成領域をレジスト13でマスクして、NMOSトランジスタ3の形成領域にヒ素(As)やボロン(B)イオンを注入して、NMOSトランジスタ3の形成領域のタンゲステン膜12の引っ張り応力を解放するか、圧縮応力を持たせる(図8)。

#### 【0026】

その後、レジスト13を剥離し(図9)、タンゲステン膜12を加工してゲート電極5c, 5dを形成する(図5)。

#### 【0027】

上述したように、第1金属層21をTiNにした場合、トランジスタ2, 3の電気特性はTiNの特性により決定される。より具体的には、ゲート電極5c, 5dの仕事関数はTiNの仕事関数に依存し、第2金属層22a, 22bの材料が何であれ、トランジスタ2, 3の閾値等の電気特性には影響しない。このため、トランジスタ2, 3の電気特性とチャネル表面の応力を別個に制御することができる。

#### 【0028】

上記の説明では、トランジスタ2, 3の電気特性を決定する第1金属層21の上面に、チャネル表面の応力を決定する第2金属層22a, 22bを配置したが、第1金属層21と第2金属層22a, 22bが互いに反応する場合には、第1金属層21と第2金属層22a, 22bの間に、反応防止膜を介挿するのが望ましい。

#### 【0029】

第2の実施形態の場合も、図5の断面構造が得られた後、公知の手法で、エクステンション拡散層の形成、ゲート電極5c, 5d側壁の形成、ソース/ドレイン拡散層の形成を行う。その後、全面に層間膜を形成した後、コンタクトプロセスにより、配線層を形成して、トランジスタを完成させる。

#### 【0030】

なお、第1金属層21は、NMOSトランジスタ3とPMOSトランジスタ2で互いに別個の金属を用いて、いわゆるデュアルメタル電極を採用してもよい。具体的には、例えば、PMOSトランジスタ2の第1金属層21としてPtSiを用い、NMOSトランジスタ3の第1金属層21としてTiCを用いてもよい。また、ゲート電極5c, 5dは、3層以上の積層膜で形成してもよい。あるいは、PMOSトランジスタ2とNMOSトランジスタ3のうち一方を積層構造にし、他方を単層構造にしてもよい。

#### 【0031】

図10はPMOSトランジスタ2のゲート電極5cを単層構造にして、NMOSトランジスタ3のゲート電極5dを2層構造にした半導体装置の一例を示す断面図である。図10において、NMOSトランジスタ3のゲート電極5dは、図5のゲート電極5dと同様に、ゲート絶縁膜4上に形成される第1金属層21と、第1金属層21上に形成される第2金属層22bとを有する。

#### 【0032】

このように、第2の実施形態では、トランジスタ2, 3の電気特性を決定する第1金属層21と、トランジスタ2, 3のチャネル表面の応力を決定する第2金属層22a, 22bとでゲート電極5c, 5dを形成するため、トランジスタの電気特性とチャネル表面の応力を互いに独立に制御でき、電気特性に優れてかつ移動度の高いトランジスタを形成

10

20

30

40

50

できる。

【0033】

(第3の実施形態)

第3の実施形態はダマシンプロセスを用いて半導体装置を製造するものである。

【0034】

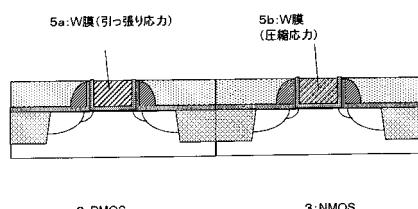

図11は本発明の第3の実施形態による半導体装置の断面構造を示す断面図である。図11の半導体装置は、ダマシンプロセスにて作製されたPMOSトランジスタ2とNMOSトランジスタ3とを備えている。

【0035】

PMOSトランジスタ2のゲート電極5aとNMOSトランジスタ3のゲート電極5bはそれぞれ、基板上に形成されたゲート溝の周囲に、例えばタンゲステン(W)を用いて形成されている。PMOSトランジスタ2のゲート電極5aは引っ張り応力を持ち、NMOSトランジスタ3のゲート電極5bは圧縮応力を持つ。

【0036】

図12～図16は図11の半導体装置の製造工程の一例を示す断面図である。以下、これらの図を用いて、図11の半導体装置の製造工程を順に説明する。まず、第1の実施形態と同様に、シリコン基板1上に素子領域と素子分離領域(STI)11を形成した後、バッファ膜としてシリコン酸化膜を全面に形成する。

【0037】

次に、ダミーゲート膜として、ポリシリコンおよびシリコン窒化膜23を基板全面に形成する。次に、レジストを用いて異方性エッチングを行い、ダミーゲート電極を形成する。次に、既知の手法により、エクステンション拡散層領域を形成した後、側壁24をゲート電極5a, 5bの周りに形成する。次に、ソース/ドレインの拡散層を形成するために不純物イオンを注入する。そして、不純物イオンの活性化を行うことにより、ソース/ドレイン領域25が形成される。必要に応じて、シリサイド膜をソース/ドレイン領域25に形成する。

【0038】

次に、基板全面に例えシリコン酸化膜を堆積した後、CMP法またはエッチバック法により、堆積させたシリコン酸化膜をエッチングして平坦化し、ダミーゲート膜の上面を露出させる。

【0039】

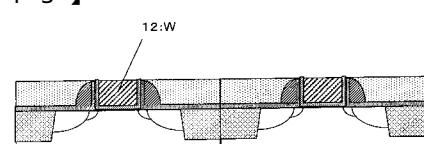

次に、シリコン窒化膜とシリコン酸化膜をエッチングし、バッファ酸化膜を希フッ酸溶液で除去してシリコン基板1を露出させ、これにより、ゲート電極5a, 5bを形成するためのゲート溝26が形成される(図12)。

【0040】

次に、ゲート溝26の内部を含めて基板上面にレジストマスク等によりゲート絶縁膜4を形成する(図13)。例えば、シリコン基板1を酸化してもよいし、基板全面に高誘電体膜を堆積してもよい。

【0041】

次に、ゲート絶縁膜4の上面に、ゲート電極5a, 5bとなる金属層(例えは、引っ張り応力を持つタンゲステン)12を形成する(図14)。次に、基板上面をCMP等により平坦化して、ゲート溝26外のタンゲステンと、ゲート絶縁膜4を除去する(図15)。

【0042】

次に、第1の実施形態と同様に、引っ張り応力を持たせる領域(PMOSトランジスタ2の形成領域)をレジスト13でマスクし、NMOSトランジスタ3の形成領域にヒ素(As)やボロン(B)等の不純物イオンを注入する(図16)。これにより、NMOSトランジスタ3の形成領域は、引っ張り応力が解放されて、応力が無視できる大きさになるか、あるいは圧縮応力を持つようになる(図11)。

【0043】

図11～図16では、単層構造のゲート電極5a, 5bを形成する例を説明したが、第

10

20

30

40

50

2 の実施形態と同様に積層構造のゲート電極 5 a , 5 b を形成してもよい。また、ゲート電極 5 a , 5 b は、図 17 に示すように T 字型のゲート電極 5 a , 5 b を形成してもよい。図 17 のゲート電極 5 a , 5 b は、図 14 の工程の後、パターニングと RIE によりタンゲステン膜 12 を加工して形成する。

## 【0044】

この後、通常のトランジスタと同様に、層間膜とコンタクトが順に形成される。

## 【0045】

このように、第 3 の実施形態では、ダマシンプロセスで PMOS トランジスタ 2 と NMOS トランジスタ 3 を形成する際にも、両トランジスタのゲート電極 5 a , 5 b の応力を互いに逆になり、トランジスタの種類によらず、移動度を向上させることができる。

10

## 【0046】

## (第 4 の実施形態)

第 4 の実施形態は、ゲート電極 5 a , 5 b を積層構造にして、応力に影響する金属層をゲート電極 5 a , 5 b の上層に形成するものである。

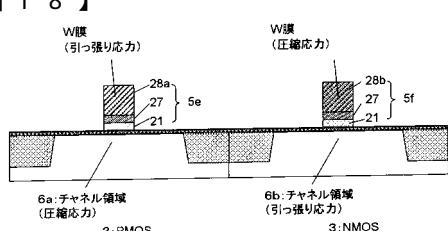

## 【0047】

図 18 は本発明の第 4 の実施形態による半導体装置の断面構造を示す断面図である。図 18 の半導体装置は、PMOS トランジスタ 2 と NMOS トランジスタ 3 を備え、両トランジスタとも 3 層構造からなるゲート電極 5 e , 5 f を有する。ゲート電極 5 e , 5 f は、ゲート絶縁膜 4 上に形成されるポリシリコン層 21 と、ポリシリコン層 21 上に形成されるバリア層 27 と、バリア層 27 上に形成されるタンゲステン膜 28 a , 28 b とを有する。

20

## 【0048】

PMOS トランジスタ 2 のゲート電極 5 e の材料であるタンゲステン膜は引っ張り応力を持つのに対し、NMOS トランジスタ 3 のゲート電極 5 f の材料であるタンゲステン膜は圧縮応力を持つ。

## 【0049】

以下、図 18 の半導体装置の製造工程について簡単に説明する。シリコン基板 1 上に素子領域と素子分離領域 11 を形成する。基板上面にゲート絶縁膜 4 を形成し、このゲート絶縁膜 4 上にポリシリコン層 21 を形成する。その後、ポリシリコン層 21 に不純物イオンを注入する。あるいは、不純物イオンを含むポリシリコン層 21 を予めゲート絶縁膜 4 上に形成してもよい。次に、熱工程により不純物イオンを活性化し、基板上面にバリア層 27 として窒化タンゲステン (WN) を形成し、その上面にタンゲステン膜 12 を形成する。

30

## 【0050】

その後、第 1 ~ 第 3 の実施形態と同様に、PMOS トランジスタ 2 の形成領域をレジストでマスクし、NMOS トランジスタ 3 の形成領域にヒ素 (As) やボロン (B) 等の不純物イオンを注入して、応力を緩和するか、圧縮応力を持たせる。

## 【0051】

その後、第 1 ~ 第 3 の実施形態と同様に、ゲート電極 5 e , 5 f を加工成形し、公知の手法で、エクステンション拡散層の形成、ゲート側壁の形成、およびソース / ドレイン拡散層の形成を行い、基板全面に層間膜を形成した後、コンタクトプロセスにより配線層を形成し、トランジスタを完成させる。

40

## 【0052】

ポリシリコン層 21 は、ゲート電極 5 e , 5 f の仕事関数を決定するためのものであり、これにより、トランジスタのしきい値電圧等の電気特性が決定される。

## 【0053】

このように、第 4 の実施形態では、ゲート電極 5 e , 5 f の下層にポリシリコン層を形成するため、トランジスタの電気特性を制御することができる。また、ゲート電極 5 e , 5 f の上層には応力制御用のタンゲステン膜 12 を形成するため、PMOS トランジスタ 2 と NMOS トランジスタ 3 でチャネル表面の応力を互いに逆にすることができ、両トランジスタともに移動度を向上できる。

50

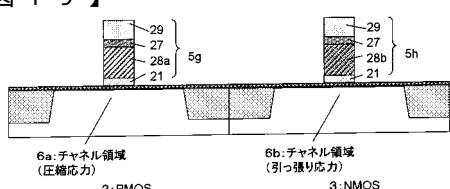

## 【0054】

図19は図18の変形例を示す断面図である。図19のゲート電極5g, 5hは、タンゲステン膜28a, 28bの上面にバリア層27を介してシリサイド層29が形成されている。ゲート電極5g, 5hの最上層にシリサイド層29を形成することにより、ゲート電極5g, 5h全体の抵抗を下げることができる。

## 【0055】

本発明は、上述した各実施形態に限定されるものではなく、本発明の要旨を逸脱しない範囲で種々に変形して実施することができる。例えば、基板はシリコン基板1に限定されず、絶縁膜上にシリコン活性層を形成したSOI基板にも用いることができる。また、基板の面方位によって移動度が異なるが、本発明は特に面方位を限定しない。

10

## 【0056】

また、本発明は、平面型のトランジスタだけでなく、Fin型などのチャネルゲート電極5g, 5h部分が立体構造のトランジスタにも適用可能である。

## 【0057】

上述した実施形態では、応力を解放させるイオン注入をゲート電極加工前に行つたが、ゲート電極加工後に行ってもよい。応力を解放させる工程として、イオン注入に加えて、熱工程を行ってもよい。

## 【0058】

応力を持つ金属としてタンゲステンを例に挙げたが、TiSi等のシリサイドでもよい。また、注入する不純物イオンは、ヒ素(As)やボロン(B)に限らない。例えば、ゲルマニウム(Ge)やインジウム(In)などの各種不純物イオンが適用可能である。

20

## 【0059】

電気特性に影響する金属として、TiNの例を挙げたが、その他の金属(Ti, Zr, Hf, Ta, W)の窒化物(TiN, ZrN, HfN, Ta<sub>2</sub>N, WN)や、臭化物(TiB<sub>2</sub>, ZrB<sub>2</sub>, HfB<sub>2</sub>, TaB<sub>2</sub>, MoB<sub>2</sub>, WB)や、硅化物や、シリサイド(PtSi, WSi)などを用いてもよい。

## 【0060】

また、ゲート絶縁膜4は、酸化膜やハフニウム(Hf)以外に、高誘電体やその酸化物、酸窒化物やシリケートなどを用いてもよい。

## 【図面の簡単な説明】

## 【0061】

30

【図1】本発明の第1の実施形態による半導体装置の断面構造を示す断面図。

【図2】図1の半導体装置の製造工程の一例を示す断面図。

【図3】図2に続く工程断面図。

【図4】図3に続く工程断面図。

【図5】本発明の第2の実施形態による半導体装置の断面構造を示す断面図。

【図6】図5の半導体装置の製造工程の一例を示す断面図。

【図7】図6に続く工程断面図。

【図8】図7に続く工程断面図。

【図9】図8に続く工程断面図。

【図10】PMOSトランジスタ2のゲート電極5cを単層構造にして、NMOSトランジスタ3のゲート電極5dを2層構造にした半導体装置の一例を示す断面図。

40

【図11】本発明の第3の実施形態による半導体装置の断面構造を示す断面図。

【図12】図11の半導体装置の製造工程の一例を示す断面図。

【図13】図12に続く工程断面図。

【図14】図13に続く工程断面図。

【図15】図14に続く工程断面図。

【図16】図15に続く工程断面図。

【図17】T字型のゲート電極を形成する例を示す断面図。

【図18】本発明の第4の実施形態による半導体装置の断面構造を示す断面図。

【図19】図18の変形例を示す断面図。

50

## 【符号の説明】

## 【0062】

- 1 シリコン基板

2 PMOSトランジスタ

3 NMOSトランジスタ

4 ゲート絶縁膜

5a, 5b, 5c, 5d, 5e, 5f, 5g, 5h ゲート電極

6a, 6b チャネル領域

21 第1金属層

22a, 22b 第2金属層

27 バリア層

28a, 28b タングステン膜

10

【図1】

【図4】

【図2】

【図5】

【図3】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

## フロントページの続き

(51) Int.Cl.

**H 01 L 29/49**

F I

テーマコード(参考)

(2006.01)

(72)発明者 齋 藤 友 博

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

F ターム(参考) 4M104 AA01 BB01 BB13 BB14 BB17 BB18 BB22 BB28 BB29 BB30

BB32 BB34 BB36 BB39 CC05 DD03 DD66 DD77 FF13 GG09

GG10

5F048 AA08 AC03 BA01 BB05 BB06 BB09 BB10 BB11 BB12 BB13

BC06 BE03 BG13 DA23

5F140 AA01 AB03 AC28 BA01 BD07 BD09 BD11 BD13 BE07 BE08

BF01 BF04 BF06 BF07 BF08 BF10 BF11 BF17 BF20 BF21

BF27 BF38 BF42 BG04 BG08 BG36 BG38 BG40 BH14 BJ01

BJ08 BK02 BK13 BK21 CB04 CE07