(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4822572号

(P4822572)

(45) 発行日 平成23年11月24日(2011.11.24)

(24) 登録日 平成23年9月16日(2011.9.16)

(51) Int.Cl.

F 1

G 11 C 11/4074 (2006.01)

G 11 C 11/34 354 F

G 11 C 11/4076 (2006.01)

G 11 C 11/34 354 C

請求項の数 2 (全 19 頁)

(21) 出願番号

特願平11-248580

(22) 出願日

平成11年9月2日(1999.9.2)

(65) 公開番号

特開2001-76484(P2001-76484A)

(43) 公開日

平成13年3月23日(2001.3.23)

審査請求日

平成18年8月3日(2006.8.3)

(73) 特許権者 302062931

ルネサスエレクトロニクス株式会社

神奈川県川崎市中原区下沼部1753番地

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100109162

弁理士 酒井 将行

(74) 代理人 100111246

弁理士 荒川 伸夫

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリセルアレイを含む内部回路と、

第1電圧供給ノード(N A)と、

第2電圧供給ノード(N B)と、

第3電圧供給ノード(N C)と、

前記第1電圧供給ノードから受ける動作電圧と前記第2電圧供給ノードから受ける動作電圧とに基づき動作し、前記内部回路の動作タイミングを決定する内部クロックを発生する同期回路と、

前記第1電圧供給ノードと前記第3電圧供給ノードとに電圧を供給する第1電源と、

前記第1電源から前記第3電圧供給ノードに電圧を供給する降圧回路と、

前記内部回路と前記第2電圧供給ノードとに前記第1電源より低い電圧を供給する第2電源と、

前記第1電圧供給ノードの電圧および前記第2電圧供給ノードの電圧を安定化させる電圧安定化回路とを備え、

前記内部回路は、前記第3電圧供給ノードから動作電圧を受け、

前記電圧安定化回路は、

前記第1電圧供給ノードの電圧の変化を検出する検出回路と、

前記検出回路の出力に応じて、前記第1電源から前記第1電圧供給ノードに電圧を供給する回路と、

10

20

前記第2電源と前記第1電圧供給ノードとの間に設けられ、クロックイネーブル信号がHレベルの間、前記第1電圧供給ノードから前記第2電源にダミー電流を流すダミー電流発生回路と、

前記第2電圧供給ノードと前記第2電源との間のインピーダンスを高くする高インピーダンス素子と、

前記第1電圧供給ノードと前記第2電圧供給ノードとの間に設けられ、前記第1電圧供給ノードの電圧と前記第2電圧供給ノードの電圧とを同方向に変化させる電圧変化回路とを含む、半導体記憶装置。

#### 【請求項2】

前記ダミー電流発生回路は、

10

前記第1電圧供給ノードと前記第2電源との間に設けられるトランジスタを含む、請求項1に記載の半導体記憶装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この発明は、半導体記憶装置に関し、より特定的には、安定した電源を供給することができる構成を有する半導体記憶装置に関する。

##### 【0002】

##### 【従来の技術】

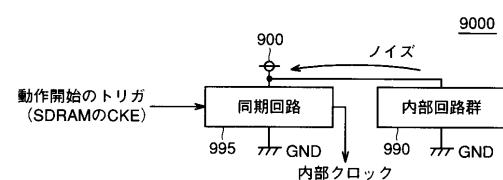

従来の半導体記憶装置の構成について、図20を用いて説明する。図20に示される半導体記憶装置9000は、メモリセルを含む内部回路群990と内部クロックを発生する同期回路995とを備える。同期回路995は、動作開始のトリガに応じて駆動し、内部回路群990における動作タイミングを決定する内部クロックを発生する。同期回路995は、たとえばPLL回路等から構成される。

20

##### 【0003】

図20に示されるように、同期回路995と内部回路群990とは、電源900を共有しており、同期回路995および内部回路群990はともに、電源900から受ける電源電圧と接地電圧GNDとを動作電圧として動作する。

##### 【0004】

##### 【発明が解決しようとする課題】

30

ところで、同期回路995が高精度な同期動作を行なうためには、動作電圧の安定が必要とされる。

##### 【0005】

しかしながら、内部回路群が動作すると電流消費に伴いノイズが発生し、電源電圧が揺れてしまう。したがって、従来の半導体記憶装置9000の構成では、内部動作に伴い、内部クロックの精度が損われるという問題があった。

##### 【0006】

また、内部回路群に不良があると、同様に電源電圧や信号電圧が揺れてしまう。したがって、同一チップ内の回路のみならず、同一配線で接続される他の装置に対しても内部回路群の不良に伴う影響を抑える必要がある。

40

##### 【0007】

したがって、本発明は係る問題を解決するためになされたものでありその目的は、安定した電源電圧を供給することにより高周波動作時においても動作マージンの大きい半導体記憶装置を提供することにある。

##### 【0008】

また、本発明のさらなる目的は、不良による影響を抑えて、同一配線で接続される機器の安定した動作を保証することができる半導体記憶装置を提供することにある。

##### 【0009】

##### 【課題を解決するための手段】

この発明の一つの局面に従う半導体記憶装置は、メモリセルアレイを含む内部回路と、

50

第1電圧供給ノードと、第2電圧供給ノードと、第3電圧供給ノードと、第1電圧供給ノードから受ける動作電圧と第2電圧供給ノードから受ける動作電圧に基づき動作し、内部回路の動作タイミングを決定する内部クロックを発生する同期回路と、第1電圧供給ノードと第3電圧供給ノードとに電圧を供給する第1電源と、第1電源から第3電圧供給ノードに電圧を供給する降圧回路と、内部回路と第2電圧供給ノードとに第1電源より低い電圧を供給する第2電源と、第1電圧供給ノードの電圧および第2電圧供給ノードの電圧を安定化させる電圧安定化回路とを備える。内部回路は、第3電圧供給ノードからの動作電圧を受ける。 電圧安定化回路は、第1電圧供給ノードの電圧の変化を検出する検出回路と、検出回路の出力に応じて、第1電源から第1電圧供給ノードに電圧を供給する回路と、第2電源と第1電圧供給ノードとの間に設けられ、クロックイネーブル信号がHレベルの間、第1電圧供給ノードから第2電源にダミー電流を流すダミー電流発生回路と、第2電圧供給ノードと第2電源との間のインピーダンスを高くする高インピーダンス素子と、第1電圧供給ノードと第2電圧供給ノードとの間に設けられ、第1電圧供給ノードの電圧と第2電圧供給ノードの電圧とを同方向に変化させる電圧変化回路とを含む。

10

### 【0013】

好ましくは、ダミー電流発生回路は、第1電圧供給ノードと第2電源との間に設けられるトランジスタを含む。

### 【0021】

#### 【発明の実施の形態】

以下、本発明に係る構成について図を用いて説明する。なお、同一または相当部分には同一記号を付しその説明を省略する。

20

### 【0022】

#### [実施の形態1]

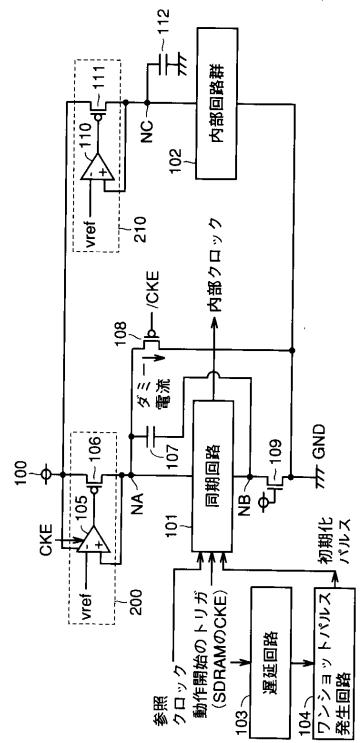

本発明の実施の形態1に係る半導体記憶装置の構成について、図1を用いて説明する。図1は、高精度の内部クロックを発生させるための回路構成を示している。図1に示される半導体記憶装置は、同期回路101、内部回路群102、遅回路103およびワンショットパルス発生回路104を備える。

### 【0023】

同期回路101は、PLL回路(Phase lock loop)、DLL回路(Delay lock loop)等で構成される。同期回路101は、動作開始のトリガ(SDRAMにおけるチップ活性化時にHレベルになるクロックイネーブル信号CKE)により起動し、初期化パルスにより初期化された後に参照クロック(たとえば、外部クロック)に応じて内部クロックを発生する。

30

### 【0024】

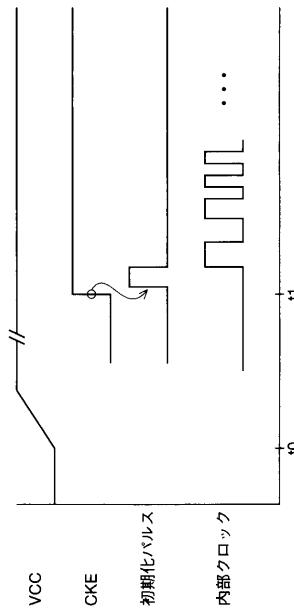

遅延回路103は、動作開始のトリガを遅延して出力する。ワンショットパルス発生回路104は、遅延回路103の出力に応答してワンショットの初期化パルスを発生する。図2に示されるように、電源電圧VCCが時刻t0においてLレベルからHレベルに立上がりると、動作開始のトリガとなるクロックイネーブル信号CKEが時刻t1においてHレベルに立上がる。これを受け、1ショットの初期化パルスが発生する。初期化パルスの投入後から、同期回路101における同期動作が始まり、内部クロックが発生する。

40

### 【0025】

図1を参照して、同期回路101と内部回路群102とは、電源100と接地電源(接地電圧)GNDとの間に配置されている。簡単のため、電源100については、電源側と、接地電源については、GND側と記す。内部回路群102は、メモリセルアレイ、メモリセルアレイの動作を制御する回路、または入出力バッファ等で構成される。

### 【0026】

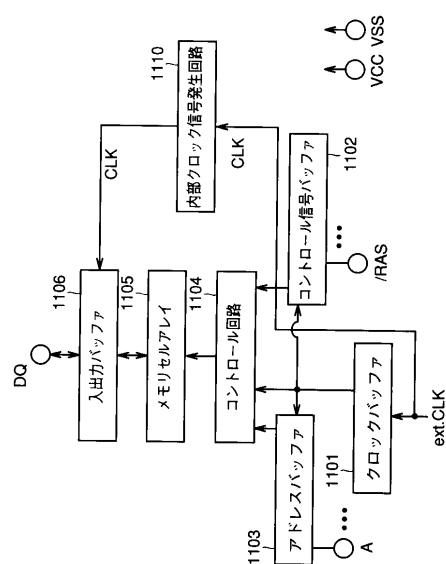

同期回路101と内部回路群102との対応関係の一例を、図18を用いて説明する。

図18に示されるSDRAMは、外部クロックext.CLKを取り込み内部クロックを出力するクロックバッファ1101、クロックバッファ1101の出力に基づき外部制御信号(たとえば、ロウアドレスストローブ信号/RAS等)を取込むコントロール信号バッ

50

ファ 1 1 0 2、クロックバッファ 1 1 0 1 の出力に基づきアドレス信号 A を取込むアドレスバッファ 1 1 0 3、クロックバッファ 1 1 0 1 の出力に基づき、コントロール信号バッファ 1 1 0 2 の出力およびアドレスバッファ 1 0 3 の出力に応じてメモリセルを選択するコントロール回路 1 1 0 4、複数のメモリセルを含むメモリセルアレイ 1 1 0 5、データ入出力ピン D Q と接続され、選択されたメモリセルからデータを読み出し、または選択されたメモリセルへ書込むデータを外部から受ける入出力バッファ 1 1 0 6、および外部クロックを受けて所望の位相で H / L を繰返す内部クロック C L K を発生する内部クロック信号発生回路 1 1 1 0 を備える。記号 V C C、V S S は、電源ピンを表わしている。入出力バッファ 1 1 0 6 は、内部クロック C L K を基準に動作する。内部クロック信号発生回路 1 1 1 0 は、P L L 回路またはD L L 回路で構成される。図 1 に示す同期回路 1 0 1 は、たとえば、内部クロック信号発生回路 1 1 1 0 に対応している。10

#### 【 0 0 2 7 】

図 1 を参照して、同期回路 1 0 1 の電源側（電圧供給ノード N A ）には、差動アンプ 1 0 5 と P M O S トランジスタ 1 0 6 とを含む V D C 回路（V D C : voltage down converter ; 電圧降下回路）2 0 0 を配置する。V D C 回路 2 0 0 を介して、ノード N A から同期回路 1 0 1 に内部電圧を供給する。

#### 【 0 0 2 8 】

P M O S トランジスタ 1 0 6 は、電源 1 0 0 とノード N A との間に接続される。差動アンプ 1 0 5 の正の入力端子は、ノード N A と接続され、負の入力端子には基準電圧 v r e f を供給する。差動アンプ 1 0 5 は、クロックイネーブル信号 C K E に応答して活性化し、電源 1 0 0 から供給される電圧に基づき動作する。P M O S トランジスタ 1 0 6 は、差動アンプ 1 0 5 の出力に応じて導通する。20

#### 【 0 0 2 9 】

同期回路 1 0 1 の G N D 側（電圧供給ノード N B ）には、インピーダンスを発生させるための N M O S トランジスタ 1 0 9 を配置する。N M O S トランジスタ 1 0 9 は、接地電源 G N D とノード N B との間に接続され、ゲートに電源電圧が供給されている。

#### 【 0 0 3 0 】

ノード N A とノード N B との間には、同期回路 1 0 1 に供給される電圧を安定化するために容量 1 0 7 を配置する。容量 1 0 7 は、平行平板容量、M O S 容量、接合容量、もしくは D R A M に対応するメモリセル容量等が考えられる。30

#### 【 0 0 3 1 】

ノード N A と接地電源 G N D との間には、ダミー電流を流すための P M O S トランジスタ 1 0 8 を配置する。P M O S トランジスタ 1 0 8 は、クロックイネーブル信号を反転した反転クロックイネーブル信号 / C K E に応じて導通する。

#### 【 0 0 3 2 】

内部回路群 1 0 2 の電源側（電圧供給ノード N C ）には、差動アンプ 1 1 0 と P M O S トランジスタ 1 1 1 とを含む V D C 回路 2 1 0 を配置する。V D C 回路 2 1 0 を介して、ノード N C から内部回路群 1 0 2 に内部電圧を供給する。

#### 【 0 0 3 3 】

P M O S トランジスタ 1 1 1 は、電源 1 0 0 とノード N C との間に接続される。差動アンプ 1 1 0 の正の入力端子は、ノード N C と接続され、負の入力端子には、基準電圧 v r e f を供給する。P M O S トランジスタ 1 1 1 は、差動アンプ 1 1 0 の出力に応じて導通する。ノード N C と接地電源 G N D との間には、容量 1 1 2 を配置する。40

#### 【 0 0 3 4 】

このように、電源側に V D C 回路 2 0 0、2 1 0 を配置することにより、電圧供給ノード N A の電圧が、内部回路群 1 0 2 の動作に伴い発生するノイズに連動して振動することを防止する。これにより、同期回路 1 0 1 に対して安定した電圧供給を行なうことが可能となる。

#### 【 0 0 3 5 】

ノード N A にノイズがのった場合であっても、同期回路 1 0 1 の電源側と G N D 側との間50

に配置された容量 107 のカップリング効果で、ノード N A の電圧とノード N B の電圧とを同方向に変化させることができる。すなわち、同期回路 101 の動作電圧（ノード N A と N B との間の電圧）が一定に保たれることになる。

#### 【0036】

さらに、ダミー電流を流すための経路（PMOS ランジスタ 108 の存在）を設けることにより、ノード N A の電圧を発生するための差動アンプ 105 の動作が安定する。ノイズに対して差動アンプ 105 が安定した動作を行なうことが可能となる。

#### 【0037】

同期回路 101 は、クロックイネーブル信号 CKE が H レベルになるチップ活性期間に動作する。このため、クロックイネーブル信号 CKE に応じてダミー電流を流し、クロックイネーブル信号 CKE が L レベルの間（パワーダウン時）には、ダミー電流をカットして消費電流の低減化を図る。このため、PMOS ランジスタ 8 のゲート電極には、反転クロックイネーブル信号 / CKE を供給する。10

#### 【0038】

GND 側にも同様にノイズがのること考えられる。このため、オン状態の NMOS ランジスタ 109 を配置する。このようなオン抵抗を利用することにより、ノイズがノード N B にのることを防止する。NMOS ランジスタ 109 により、ノード N B のインピーダンスを高くなる。これにより、容量 107 によるカップリング効果が生じる。

#### 【0039】

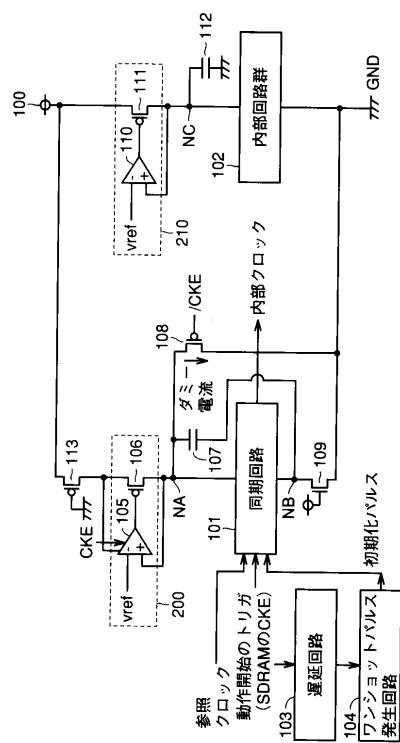

本発明の実施の形態 1 における他の構成例について、図 3 を用いて説明する。図 3 に示す構成では、電源 100 と VDC 回路 200 との間に配置される、ゲート電極に接地電圧 GND を受ける PMOS ランジスタ 113 を含む。20

#### 【0040】

VDC 回路 200 に電圧を供給する電源 100 に対して、PMOS ランジスタ 113 のオン抵抗を利用したフィルタを配置する。一方、VDC 回路 200 は、同期回路 101 用の電源に対するフィルタとしての役割を果たしている。

#### 【0041】

これにより、電源 100 とノード N A との間に 2 つのフィルタがシリアルに配置される構成となる。この結果、高周波動作時のノイズはもとより、広い周波数領域でのノイズをカットすることが可能となる。30

#### 【0042】

##### [実施の形態 2 ]

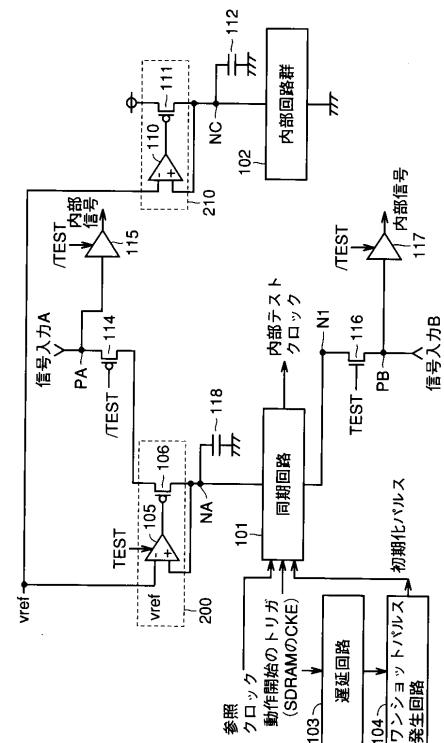

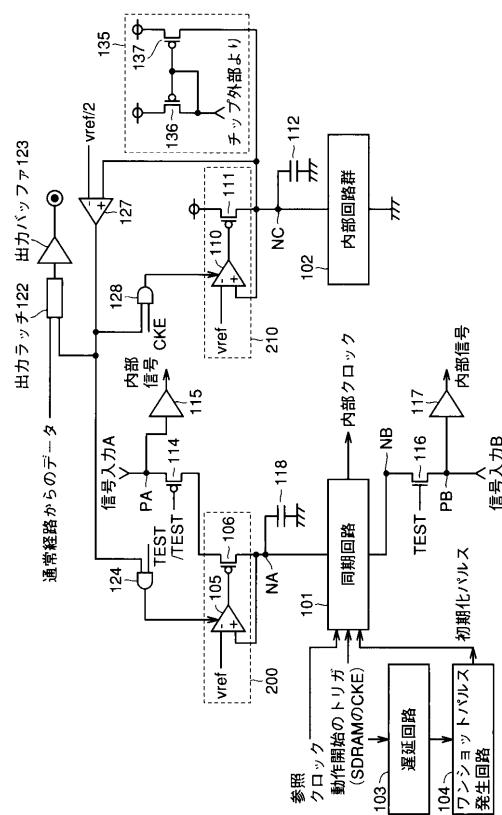

本発明の実施の形態 2 における半導体記憶装置の構成について、図 4 を用いて説明する。チップをパッケージングした後においては、テスト系回路に対して新たな電源を供給するための入力ピンを別途設けることが困難である。そこで、本発明の実施の形態 2 においては、通常使用のピン（テストモード以外で使用するピン）をテスト系回路の電源ピンとする。なお、本発明の実施の形態 2 における同期回路 101 は、DLL 回路等で構成され、同期回路 101 の出力する内部クロックが、テストモードにのみ使用される（以下、同期回路 101 の出力を、内部テストクロックと記す）。

#### 【0043】

同期回路 101 の電源側には、VDC 回路 200、容量 118 および PMOS ランジスタ 114 を配置する。本発明の実施の形態 2 においては、VDC 回路 200 に含まれる差動アンプ 105 は、テストモード信号 TEST に応じて動作する。PMOS ランジスタ 106 は、ノード N A と PMOS ランジスタ 114 の一方の導通端子との間に接続される。容量 118 は、ノード N A と接地電圧 GND との間に接続される。40

#### 【0044】

PMOS ランジスタ 114 は、信号 A を受ける信号入力ピン PA と PMOS ランジスタ 106 との間に接続される。PMOS ランジスタ 114 は、テストモード信号 TEST を反転したテストモード信号 / TEST に応じて導通する。

#### 【0045】

10

20

30

40

50

同期回路 101 の GND 側には、PMOS トランジスタ 116 を配置する。NMOS トランジスタ 116 は、ノード NB と信号入力ピン PB との間に接続され、テストモード信号 TEST に応じて導通する。

#### 【0046】

図4に示す構成においては、同期回路 101 は、テストモード信号 TEST がHレベル(ある特定のテストモード)になると動作し、内部テストクロックを出力する。

#### 【0047】

信号入力ピン PA に対して設けられる回路 115 は、テストモード信号 / TEST に応じて信号 A を取込み、内部信号を出力する。信号入力ピン PB に対して設けられる回路 117 は、テストモード信号 / TEST に応じて信号 B を取込み、内部信号を出力する。内部回路群 102 は、通常動作モードでは、当該内部信号に応じて動作する。なお、内部回路群 102 に対する電源構成は、実施の形態 1 で説明したとおりである。10

#### 【0048】

信号入力ピン PA には、通常モードでは、通常の内部信号系(回路 115)に対する信号 A を与え、テストモードでは、電源電圧レベルの信号 A を与える。信号入力ピン PB には、通常モードでは、通常の内部信号系(回路 117)に対する信号 B を与え、テストモードでは、接地電圧レベルの信号 B を与える。

#### 【0049】

これにより、信号入力ピン PA、PB を、テスト系回路である同期回路 101 の電源ピンとして使用できる。この際、内部信号については、必要であれば、内部で発生させる。または、当該テストモードにおいては使用しない内部信号に対応するピンを電源ピンとして使用する。20

#### 【0050】

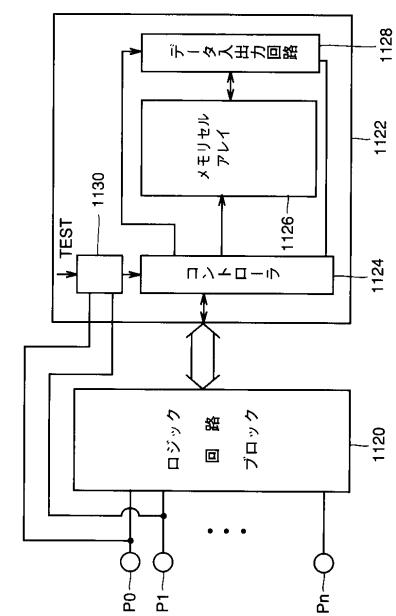

同期回路 101 と内部回路群 102 との対応関係の一例を、図19を用いて説明する。図19に示される半導体記憶装置は、外部との電気的インターフェイスを取るロジック回路ブロック 1120 と、当該ロジック回路ブロック 1120 と信号の送受信を行なうメモリセルアレイ 1126 を含むメモリコア部 1122 とが同一基板上に形成されている。ロジック回路ブロック 1120 は、複数の外部ピン P0 ~ Pn を介して図示しない装置と信号の送受信を行なう。メモリコア部 1122 は、メモリセルアレイ 1126、データ入出力回路 1128、ロジック回路ブロック 1120 から受ける信号に基づき、メモリセルアレイ 1126 およびデータ入出力回路 1128 の動作を制御するコントローラ 1124、および内部クロック信号発生回路 1130 を備える。内部クロック信号発生回路 1130 は、テストモードにおいて内部テストクロックを発生する。たとえば、コントローラ 1124 やデータ入出力回路 1128 は、テストモードにおいては、当該内部クロック信号発生回路 1130 の出力する内部テストクロックを基準に動作する。30

#### 【0051】

メモリセルアレイ 1126 に対するテストモードにおいては、ロジック回路ブロック 1120 側への信号入力が不要になる。たとえば、一旦データを書込んだ後であれば、データを入力するピンは不要になる。この際、ロジック回路ブロック 1120 側の信号供給は停止できる。そこで、通常モードにおいてロジック回路ブロック 1120 の回路動作に使用する信号入力ピン P0、P1 を、テストモードではメモリコア部 1122 に含まれる内部テストクロックを発生させる内部クロック信号発生回路 1130 の電源ピンとして使用する。40

#### 【0052】

なお、同期回路 101 に対する電源構成は、同期回路 101 のみならずテストモードにのみ動作させるあらゆるテスト系回路に対して適用できる。

#### 【0053】

このように、テストモードで使用しない通常使用ピンをテスト系回路の電源ピンとして、テスト系回路における電源ピンを専用化することができる。この結果、テスト系回路の動作が安定するため、特に同期回路においては、高精度な同期動作が実現されること50

になる。

**【0054】**

[実施の形態3]

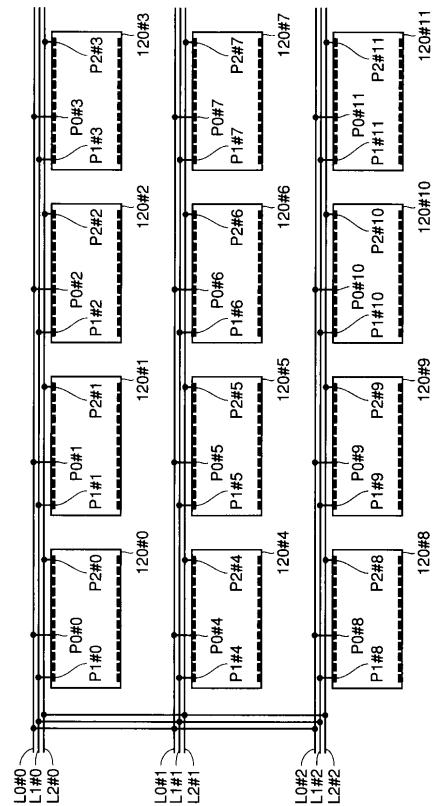

同一ボードに搭載した複数個の半導体記憶装置を同時にテストする並列テストについて説明する。図5は、複数のチップを同一ボード上に搭載してテストする並列テストについて説明するための概略図である。記号L0\_0～L0\_2は信号線を、記号L1\_0～L1\_2、L2\_0～L2\_2は電源線をそれぞれ示している。

**【0055】**

複数のチップを同一ボード上に搭載して並列テストを行なう場合、複数のチップは、電源や信号（ロウアドレスストローブ信号RAS等）を共有する。図5においては、代表的に、複数のチップ120\_0～120\_11が、信号線と電源線とを共有する場合を示している。

10

**【0056】**

信号線L0\_0～L0\_2は互いに結合関係にあり、同一の信号を各チップに伝送する。電源線L1\_0～L1\_2は、互いに結合状態にあり、同レベルの電圧を各チップに供給する。同じく、電源線L2\_0～L2\_2は、互いに結合関係にあり、同レベルの電圧を各チップに供給する。

**【0057】**

このような並列テストにおいて、一部のチップに欠陥が存在した場合、当該チップから信号線や電源線に流れ込むリーク電流のために、共有する電源線の電圧が低下し、または共有する信号線の電圧レベルが低下する。このような電圧レベルの変化は、テスト結果に影響を及ぼしてしまう。すなわち、正確な試験を行なうことができなくなる。

20

**【0058】**

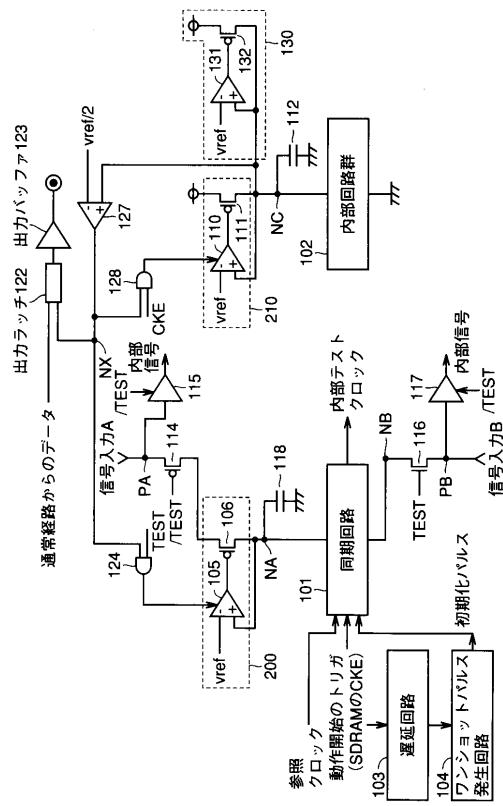

そこで、図6に示されるように、各チップごとに異常電流（リーク電流）の発生に対する処置を行なうための回路を設ける。ここで、図6に示される本発明の実施の形態3における回路構成について説明する。

**【0059】**

ノードNCの電圧と所定の電圧（図6においては、vref/2）とを比較する比較器127を配置する。VDC回路210の差動アンプ110は、比較器127の出力ノードNXとクロックイネーブル信号CKEとを受けるAND回路128の出力に応じて動作させる。

30

**【0060】**

ノードNCには、VDC回路130を配置する。VDC回路130は、差動アンプ131とPMOSトランジスタ132とを含む。差動アンプ131の正の入力端子はノードNCと接続され、負の入力端子には基準電圧vrefを供給する。PMOSトランジスタ132は、電源とノードNCとの間に接続され、差動アンプ131の出力に応じて導通する。VDC回路130は、予め、内部回路群102に供給できる電流量を制限できるように構成されている。

**【0061】**

VDC回路200の差動アンプ105は、ノードNXとテストモード信号TESTとを受けるAND回路124の出力に応じて動作させる。

40

**【0062】**

図5に示す配置で、複数個の図6に示すチップに対して並列テストを実施する際には、まず待機時に、VDC回路130をオンし、通常動作用のVDC回路200、210をオフしておく。なお、ここでいう待機時とは、並列テスト開始後であってチップ活性化前を意味する。

**【0063】**

チップが正常な場合、VDC回路130は内部電圧を正常に供給できる。したがって、ノードNCの電圧と所定の電圧vref/2との比較により、ノードNXがHレベルになる。この結果、チップを活性化すると、通常動作用のVDC回路210がオンする。また、

50

特定のテストモードに入ると (TESTがHレベル)、VDC回路200がオンして同期回路101が起動する。

#### 【0064】

ところが、内部回路群102に不良がありリーク電流が発生すると、VDC回路130は当該リーク電流を補うだけの電流を供給できない。したがって、ノードNCの電圧が低下する。ノードNCの電圧と所定の電圧 $v_{ref}/2$ との比較により、ノードNXの電圧がLレベルになる。すなわち、リーク電流の発生が検出される。

#### 【0065】

リーク電流が検出された場合には、チップを活性化しても、VDC回路210はオンせず、内部回路群102は起動しない。また、特定のテストモードに入っても (TESTがHレベル)、VDC回路200がオンせず同期回路101が起動しない。

10

#### 【0066】

したがって、並列テストの際、不良チップについては、VDC回路210とVDC回路200とがオフする。これにより、電源線や信号線を共有する他のチップにリーク電流の発生による影響を防止することができる。

#### 【0067】

リーク電流の発生の有無を外部に出力する場合には、通常の径路から受けるデータ(メモリセルから読出したデータ)と、リーク電流の発生の有無(比較器127の出力)を示すノードNXの信号とをラッチするように出力ラッチ122を構成する。これにより、出力ラッチ122のデータを受ける出力バッファ123を介して、リーク電流の発生の有無が外部に出力される。

20

#### 【0068】

比較器127における判定レベルを $v_{ref}/2$ として説明したが、当該レベルはこれに限られず任意に設定することが可能である。比較器127での判定レベル用の電圧は、外部から入力してもよいし、内部において任意のレベルを発生してもよい。

#### 【0069】

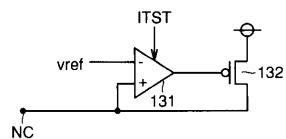

なお、VDC回路130の構成は、図6に示されたものに限らず、図7に示す構成であつてもよい。図7では、VDC回路130に代わりに、PMOSトランジスタ136および137を含むVDC回路135を配置する。PMOSトランジスタ136は、電源とチップ外部からの入力を受けるノードとの間に接続され、PMOSトランジスタ137は、電源とノードNCとの間に接続される。PMOSトランジスタ136および137のゲートは、チップ外部からの信号を受ける。PMOSトランジスタ136および137は、カレントミラー回路を構成している。このように構成することにより、リーク電流をチェックするためのチェック電流値を外部入力により替えることが可能となる。

30

#### 【0070】

図6および図7におけるVDC回路130、135は、リーク電流検出のため専用に設ける。なお、チップ上に存在する通常のスタンバイ用の小電流供給用のVDC回路を、リーク電流検出のために流用することも可能である。

#### 【0071】

図8にスタンバイ用の小電流供給用のVDC回路を利用した一例を示す。図8に示す回路は、ノードNCに差動アンプ131と、回路141、144とを含む。

40

#### 【0072】

回路141は、外部から設定切替信号に応じて導通するPMOSトランジスタ142、および差動アンプ131の出力に応じて導通するPMOSトランジスタ143を含む。PMOSトランジスタ142およびPMOSトランジスタ143は、電源とノードNCとの間に直列に接続される。

#### 【0073】

回路144は、外部から設定切替信号に応じて導通するPMOSトランジスタ145、および差動アンプ131の出力に応じて導通するPMOSトランジスタ146を含む。PMOSトランジスタ145およびPMOSトランジスタ146は、電源とノードNCとの間

50

に直列に接続される。

**【0074】**

設定切替信号に応じて、回路141、144を選択的に起動させることで、ノードN Cへの供給能力を切替える。

**【0075】**

リーク電流が発生すると、内部電圧を保持するための電流供給が不足し、内部電圧が低下する。このときの内部電圧の変化は、図9に示すように、あるチェック電流値を境に急激に変化する。したがって、当該チェック電流値を適切に設定することにより不良チップを容易に検出することが可能となる。

**【0076】**

なお、上述した構成では、待機時に検出された内部電圧の低下により、チップ活性化時（特定のタイミング）においてもV D C回路200、210が動作しないように構成している。しかし、これ限定されず、所定のテストモードにおいて当該検出を行ない、この検出結果をラッチし、これに従ってチップ活性化時にV D C回路をオンさせないように構成してもよい。

**【0077】**

たとえば、図10に示すように、差動アンプ131を特定のテストモードを指定するテストモード信号I T S Tに応じて動作させる。ここでテストモードとは、並列テストでのテストモードとは別に、電流チェック用のテストするためのモードを意味する。

**【0078】**

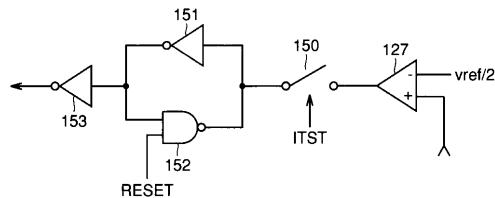

また、図11は、比較器127の出力をラッチするための回路構成を示す図である。図11に示す構成では、比較器127に対して、スイッチ150、インバータ151、N A N D回路152およびインバータ153を配置する。スイッチ150は、テストモード信号I T S Tに応じてオンし、インバータ151およびN A N D回路152から構成されるラッチ回路と比較器127の出力とを接続する。ラッチ回路を構成するN A N D回路152は、リセット信号R E S E Tに応じてリセットされる。インバータ153は、ラッチ回路の出力を反転する。インバータ153の出力に応じて、V D C回路に含まれる差動アンプを動作させるようとする。

**【0079】**

このように本発明の実施の形態3における半導体記憶装置によれば、不良チップのリーク電流を検出し、リーク電流の流出を防止することができる。このため、特に、並列テストにおいて同一チップ上に配置される他のチップの動作が保証される。

**【0080】**

**[実施の形態4]**

本発明の実施の形態4による半導体記憶装置の概要について図12～図15を用いて説明する。なお、以下の説明において、先頭に記号“／”が付された信号は、当該“／”を付さない信号を反転した信号であるものとする。

**【0081】**

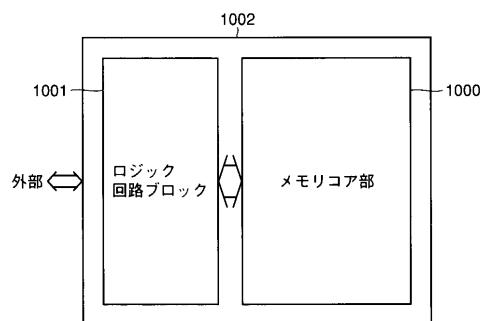

図12に示されるように、本発明の実施の形態4における半導体記憶装置は、D R A M（ダイナミックランダムアクセスメモリ）を含むメモリコア部1000とロジック回路ブロック1001とを備える。メモリコア部1000とロジック回路ブロック1001とは、同一チップ1002上に形成される。なお、図示しないが、S R A M、ゲートアレイ、F P G A、不揮発性R A M、R O M等も搭載される。

**【0082】**

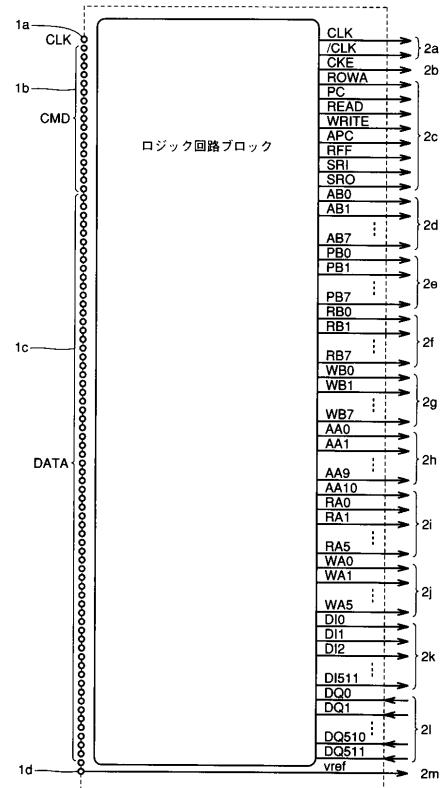

図13に示されるように、ロジック回路ブロック1001とメモリコア部1000とは、接続ノード2a～2mを介して信号の送受信を行なう。ロジック回路ブロック1001からD R A Mに対して、コマンド、アドレス、データが送信され、これに従って、D R A M側からロジック回路ブロック1001にデータが送信される。

**【0083】**

ロジック回路ブロック1001は、ピン1aから外部クロック信号C L Kを、ピン1bか

10

20

30

40

50

らコマンドCMDを、ピン1dから基準電圧vrefを受ける。また、ピン1cを用いてデータDATAの入出力を行なう。

#### 【0084】

ロジック回路ブロック1001は、入力信号に論理処理を施し、メモリコア部1000に対応する信号を出力する。なお、ピン1dで受ける基準電圧vrefは、そのままノード2mに出力される。

#### 【0085】

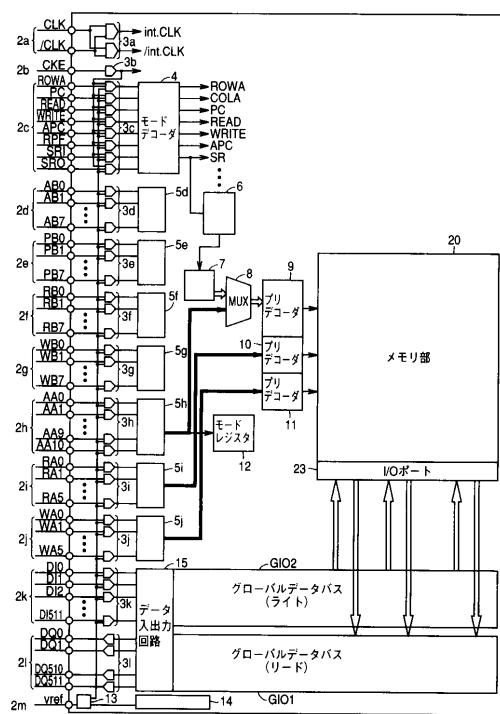

図14に示されるように、メモリコア部1000には、接続ノード2a～2kを介して以下に示す信号が供給される。ノード2aから、クロック信号CLK、/CLKが供給される。ノード2bから、クロックイネーブル信号CKEが供給される。ノード2cからは、制御信号である、ワード線の活性化を示す信号ROWA、ワード線のリセット(プリチャージ)に関連する信号PC、コラム系回路のリード動作に関連する信号READ、コラム系回路のライト動作に関連する信号WRITE、オートプリチャージ動作を指示する信号APC、リフレッシュ動作に関連する信号REF、ならびにセルフリフレッシュモードに関する信号SRIおよびSWOが供給される。10

#### 【0086】

最大で信号ROWA、信号PC、信号READ、信号WRITEの合計4コマンドを同時に発することが可能である。

#### 【0087】

ノード2dから、アクトバンク信号AB0～AB7が供給される。アクトバンク信号は、ロウ系およびコラム系のそれぞれのアクセスにおいて、アクセス対象となるバンクを指定する。ノード2eから、プリチャージバンク信号PB0～PB7が供給される。ノード2fから、リードバンク信号RB0～RB7が供給され、ノード2gから、ライトバンク信号WB0～WB7が供給される。20

#### 【0088】

ノード2hから、アクトアドレス信号AA0～AA10が供給され、ノード2iから、リードアドレス信号RA0～RA5が供給され、ノード2jから、ライトアドレス信号WA0～WA5が供給される。

#### 【0089】

ノード2kからは、入力データDI0～DI511が供給される。なお、メモリコア部1000から出力される出力データDQ0～DQ511は、ノード2lを介してロジック回路ブロック1001に送信される。30

#### 【0090】

メモリコア部1000は、バッファ3a～3l、モードデコーダ4、アクトバンクラッチ5d、プリチャージバンクラッチ5e、リードバンクラッチ5f、ライトバンクラッチ5g、ロウアドレスラッチ5h、リードアドレスラッチ5i、ライトアドレスラッチ5j、セルフリフレッシュタイマ6、リフレッシュアドレスカウンタ7、マルチプレクサ8、プリデコーダ9、10、11、モードレジスタ12、基準電圧制御回路13および同期回路14を含む。

#### 【0091】

バッファ3aは、クロック信号CLK、/CLKを受けて内部クロック信号int.CLK、/int.CLKを出力する。バッファ3c～3kのそれぞれは、基準電圧制御回路13から基準電圧vrefの供給を受ける。バッファ3bは、クロックイネーブル信号CKEを受ける。バッファ3cは、バッファ3bの出力に応じて動作し、ノード2cで受けた制御信号を取込む。モードデコーダ4は、バッファ3cの出力を受けて、内部制御信号(信号ROWA、信号COLA、信号PC、信号READ、信号WRITE、信号APCおよび信号SR等)を出力する。40

#### 【0092】

アクトバンクラッチ5dは、バッファ3dを介してアクトバンク信号AB0～AB7をラッチする。プリチャージバンクラッチ5eは、バッファ3eを介して、プリチャージバン50

ク信号 P B 0 ~ P B 7 をラッチする。リードバンククラッチ 5 f は、バッファ 3 f を介して、リードバンク信号 R B 0 ~ R B 7 をラッチする。ライトバンククラッチ 5 g は、バッファ 3 g を介してライトバンク信号 W B 0 ~ W B 7 をラッチする。ロウアドレスラッチ 5 h は、バッファ 3 h を介してアクトアドレス信号 A A 0 ~ A A 1 0 をラッチする。リードアドレスラッチ 5 i は、バッファ 3 i を介してリードアドレス信号 R A 0 ~ R A 5 をラッチする。ライトアドレスラッチ 5 j は、バッファ 3 j を介してライトアドレス信号 W A 0 ~ W A 5 をラッチする。

#### 【 0 0 9 3 】

バッファ 3 k は、入力データ D I 0 ~ D I 5 1 1 を取込む。バッファ 3 l は、データ入出力回路 1 5 から出力されるデータを取り込み、ノード 2 1 に出力する。

10

#### 【 0 0 9 4 】

セルフリフレッシュタイム 6 は、モードデコーダ 4 から出力される信号 S R を受けて動作を開始する。リフレッシュアドレスカウンタ 7 はセルフリフレッシュタイム 6 の指示に従い、リフレッシュ動作を行なうためのアドレスを発生する。マルチプレクサ 8 は、通常動作ではロウアドレスラッチ 5 h の出力を、セルフリフレッシュ動作ではリフレッシュアドレスカウンタ 7 の出力を出力する。プリデコーダ 9 は、マルチプレクサ 8 から受けるロウアドレスをデコードする。プリデコーダ 1 0 は、リードアドレスラッチ 5 i から受けるコラムアドレスをデコードする。プリデコーダ 1 1 は、ライトアドレスラッチ 5 j から受けるコラムアドレスをデコードする。モードレジスタ 1 2 は、ロウアドレスラッチ 5 h の出力に応じて、所定の動作モードに対応する情報を（たとえば、バースト長に対応するデータ等）を保持する。

20

#### 【 0 0 9 5 】

グローバルデータバス G I O 1 は、メモリ部 2 0 から読出されるデータをデータ入出力回路 1 5 に伝送する。グローバルデータバス G I O 2 は、データ入出力回路 1 5 で受ける入力データをメモリ部 2 0 に伝送する。

#### 【 0 0 9 6 】

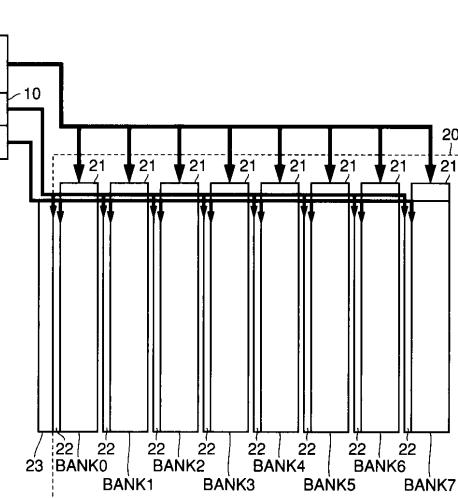

メモリ部 2 0 は、図 1 5 に示されるように、バンク B A N K 0 ~ B A N K 7 に分割されている。各バンクは、行列状に配置される複数のメモリセルと、行に対応して配置された複数のワード線と、列に対応して配置される複数のビット線とを含む。メモリセルは、情報を電荷の形で蓄積するメモリセルキャパシタと、ゲート電極が対応するワード線と接続され、一方の導通端子が対応するビット線と接続され、他方の導通端子がメモリセルキャパシタと接続されるメモリセルトランジスタとで構成される。

30

#### 【 0 0 9 7 】

バンクのそれぞれに対して、ロウデコーダ 2 1 およびコラムデコーダ 2 2 を配置する。ロウデコーダ 2 1 は、プリデコーダ 9 の出力に応答して対応するロウ方向の選択を行なう。コラムデコーダ 2 2 は、プリデコーダ 1 0 および 1 1 の出力に応答して、対応するコラム方向の選択を行なう。

#### 【 0 0 9 8 】

バンク B A N K 0 ~ B A N K 7 は、I / O ポート 2 3 を介してグローバルデータバス G I O 1 、G I O 2 とデータの受渡しを行なう。

40

#### 【 0 0 9 9 】

各バンクは、バンクアドレスにより制御される。バンクアドレスは、それぞれのコマンドに対応して存在する。たとえば、信号 R O W A とアクトバンク信号 A B n ( n = 0 ~ 7 ) とにより、対応するバンクのワード線が活性化される。信号 P C とプリチャージバンク信号 P B n ( n = 0 ~ 7 ) とにより、対応するバンクのワード線がリセットされる。信号 R E A D とリードバンク信号 R B n ( n = 0 ~ 7 ) とにより、対応するバンクのセンスアンプからデータがリードされる。また、信号 W R I T E とライトバンク信号 W B n ( n = 0 ~ 7 ) とにより、対応するバンクのセンスアンプにデータがライトされる。

#### 【 0 1 0 0 】

ここで、基準電圧制御回路 1 3 と同期回路 1 4 との関係を説明する。同期回路 1 4 は、P

50

L L 回路等で構成されている。同期回路 1 4 は、テストモードにおいて内部テストクロックを発生する。

#### 【 0 1 0 1 】

メモリコア部 1 0 0 0 は、テストモードにおいては、たとえば、バッファ 3 a の出力する内部クロック int . CLK に代わり当該内部テストクロックを基準に動作する。または、一部の回路（データ入出力回路 1 5 ）が、内部クロック int . CLK に代わり当該内部テストクロックを基準に動作する。

#### 【 0 1 0 2 】

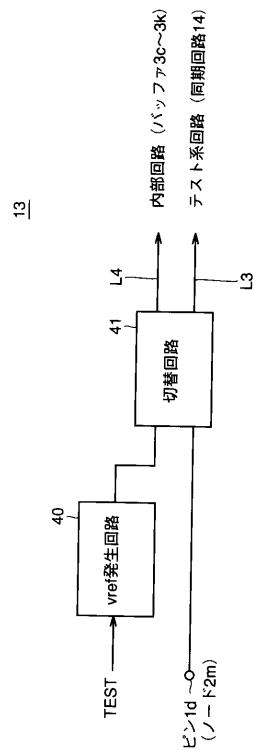

図 1 6 に示されるように、基準電圧制御回路 1 3 は、 vref 発生回路 4 0 と切替回路 4 1 とを含む。 vref 発生回路 4 0 は、テストモード信号 TEST に応じて基準電圧を発生する。

10

#### 【 0 1 0 3 】

テストモードにおいては、切替回路 4 1 は、ピン 1 d （ノード 2 m ）と同期回路 1 4 に電圧を供給するための電源線 L 3 とを接続し、バッファ 3 c ~ 3 k に基準電圧を供給する内部 vref 配線 L 4 と vref 発生回路 4 0 の出力ノードとを電気的に接続する。通常モードにおいては、切替回路 4 1 は、ピン 1 d と内部 vref 配線 L 4 とを電気的に接続する。

#### 【 0 1 0 4 】

通常モードにおいては、ピン 1 d （外部）から入力される基準電圧 vref が入力バッファ 3 c ~ 3 k のスレッショルド電圧を決定する。この際、テスト系回路である同期回路 1 4 は停止状態にある。テストモードにおいては、ピン 1 d は、同期回路 1 4 に電源電圧を供給するためのピンとして使用する。この際、バッファに対しては、内部で発生した基準電圧を供給する。

20

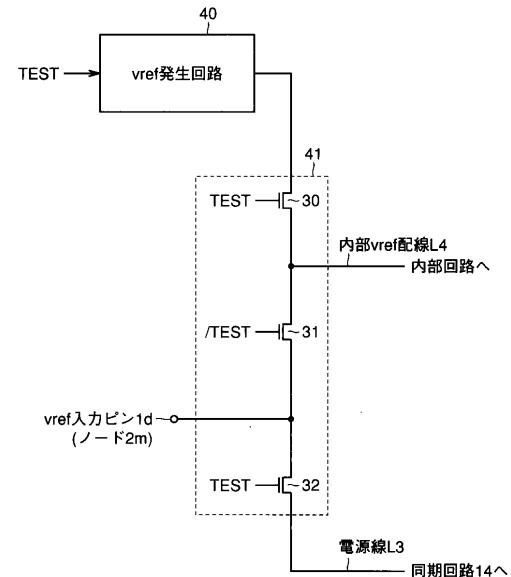

#### 【 0 1 0 5 】

基準電圧制御回路 1 3 の具体例を図 1 7 を用いて説明する。切替回路 4 1 は、 NMOS ドバイア二極管 3 0 、 3 1 および 3 2 で構成する。 NMOS ドバイア二極管 3 0 および 3 2 のそれぞれ、ゲートにテストモード信号 TEST を受け、 NMOS ドバイア二極管 3 1 は、ゲートにテストモード信号 /TEST を受ける。

#### 【 0 1 0 6 】

NMOS ドバイア二極管 3 0 は、内部 vref 配線 L 4 と vref 発生回路 4 0 の出力ノードとの間に配置する。 NMOS ドバイア二極管 3 2 は、ピン 1 d （ノード 2 m ）と電源線 L 3 との間に配置する。 NMOS ドバイア二極管 3 1 は、ピン 1 d （ノード 2 m ）と内部 vref 配線 L 4 との間に配置する。 vref 発生回路 4 0 は、テストモード信号 TEST に応じて、所定の基準電圧を発生する。

30

#### 【 0 1 0 7 】

内部 vref 配線 L 4 の電圧は、テストモード信号 TEST が H レベルになると、 vref 発生回路 4 0 の出力する信号に応じて変化し、テストモード信号 TEST が L レベルになる通常モードでは、ピン 1 d で受ける基準電圧 vref に応じて変化する。

#### 【 0 1 0 8 】

電源線 L 3 の電圧は、テストモード信号 TEST が H レベルになると、ピン 1 d で受ける電圧に応じて変化する。

40

#### 【 0 1 0 9 】

このように構成することにより、テスト系回路（同期回路）に対する電源電圧供給のための入力ピンを別途確保することなく、通常時に使用するピン 1 d を電源電圧を供給するためのピンとして使用することができる。この結果、テスト系回路に対し、安定した電源を供給することが可能となる。

#### 【 0 1 1 0 】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される

50

。

### 【0111】

#### 【発明の効果】

このように、この発明の実施の形態に係る半導体記憶装置によれば、同期回路と内部回路とが同一電源を使用する場合であっても、電源ノイズを取除き同期回路に安定した動作電圧を供給する回路を配置することにより、高精度な同期動作が保証される。

### 【0112】

また、この発明の実施の形態に係る半導体記憶装置によれば、同期回路に内部電圧を供給する電源側とGND側との間にダミー電流を流す。これにより、電源側に配置した動作電圧の変化を検出する検出回路（差動アンプ）の動作が安定する。

10

### 【0113】

また、この発明の実施の形態に係る半導体記憶装置によれば、GND側に高インピーダンス成分を配置することにより、接地電圧にノイズがのることを防止する。

### 【0114】

また、この発明の実施の形態に係る半導体記憶装置によれば、電源側とGND側とを同方向に変化させることにより、同期回路の動作電圧を一定に保つことが可能となる。

### 【0115】

また、この発明の実施の形態に係る半導体記憶装置によれば、電源と同期回路との間にフィルタをシリアルに接続することになる。この結果、より安定した動作電圧を同期回路に供給することができる。

20

### 【0116】

さらに、この発明の実施の形態に係る半導体記憶装置によれば、内部回路に発生する異常電流（リーク電流）を検出して、ピンと内部回路とを非接続にする。これにより、リーク電流による外部装置への影響を抑えることができる。

### 【0117】

この発明の実施の形態に係る半導体記憶装置によれば、リーク電流の検出結果に基づき、動作電圧の供給を停止することができる。これにより、同一の電源線を使用する他のチップの動作を保証することができる。

### 【0118】

さらに、この発明の実施の形態に係る半導体記憶装置によれば、通常モードで使用するピンをテストモードにおける同期回路の電源ピンとして使用する。たとえば、複数のチップが同一の信号線や電源線により、同一の信号や電圧供給を受けている場合において、いずれか1のチップにおいてリーク電流が発生した場合には、不良チップに含まれる回路の起動を停止させることにより、信号線または電源線の電圧レベルの低下を防止することができる。

30

### 【0119】

この発明の実施の形態に係る半導体記憶装置によれば、電源側とGND側にそれぞれ電圧を供給するための制御回路を設ける。これにより、テストモードにおいて、同期回路に動作電圧を安定して供給することができる。

### 【0120】

40

この発明の実施の形態に係る半導体記憶装置によれば、テストモードにおいては、通常使用ピンから受ける信号に代わって内部で発生した信号を用いることにより、ピンから受ける入力を電源電圧として同期回路に供給することができる。

#### 【図面の簡単な説明】

【図1】 本発明の実施の形態1における半導体記憶装置の主要部の構成について説明するための図である。

【図2】 同期回路101の動作を説明するためのタイミングチャートである。

【図3】 本発明の実施の形態1における半導体記憶装置の主要部の他の構成例について説明するための図である。

【図4】 本発明の実施の形態2における半導体記憶装置の主要部の構成について説明す

50

るための図である。

【図5】複数のチップを同一ボード上に搭載してテストする並列テストについて説明するための概略図である。

【図6】本発明の実施の形態3における半導体記憶装置の主要部の構成について説明するための図である。

【図7】本発明の実施の形態3における半導体記憶装置の主要部の他の構成例について説明するための図である。

【図8】リーク電流検出用の回路の他の構成例について説明するための図である。

【図9】正常チップおよび不良チップのそれぞれにおける、チェック電流と内部電圧との関係を示す図である。 10

【図10】リーク電流検出用の回路の他の構成例を示す図である。

【図11】比較器127の出力をラッチするための回路構成を示す図である。

【図12】本発明の実施の形態4における半導体記憶装置について説明するための図である。 20

【図13】図12に示すロジック回路ブロック1001について説明するための図である。

【図14】図12に示すメモリコア部1000の構成の一例を示す図である。

【図15】メモリ部20の構成について説明するための図である。

【図16】基準電圧制御回路13の構成の概要を示す図である。

【図17】基準電圧制御回路13の構成の一例を示す図である。 20

【図18】同期回路101と内部回路群102との対応関係の一例を示す図である。

【図19】同期回路101と内部回路群102との対応関係の一例を示す図である。

【図20】従来の半導体記憶装置における電源について説明するための図である。

【符号の説明】

1a～1d 外部端子、2a～2m 入力ピン、3a～3l バッファ、4 モードデコーダ、6 セルフリフレッシュタイム、7 リフレッシュアドレスカウンタ、8 マルチプレクサ、9, 10, 11 プリデコーダ、12 モードレジスタ、13 基準電圧制御回路、14 同期回路、15 データ入出力回路、20 メモリ部、21 ロウデコーダ、22 コラムデコーダ、23 I/Oポート、40 vref発生回路、41 切替回路、130, 200, 210 VDC回路、101 同期回路、102 内部回路群、103 遅延回路、104 ワンショットパルス発生回路、107 容量、106, 108, 111 PMOSトランジスタ、109 NMOSトランジスタ、100 電源、105, 110 差動アンプ、1000 メモリコア部、1001 ロジック回路ブロック。 30

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図 16】

【図 17】

【図 18】

【図 19】

【図 20】

---

フロントページの続き

(74)代理人 100124523

弁理士 佐々木 真人

(74)代理人 100098316

弁理士 野田 久登

(72)発明者 大石 司

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

(72)発明者 濑戸川 潤

東京都千代田区丸の内二丁目2番3号 三菱電機株式会社内

審査官 堀田 和義

(56)参考文献 特開2000-124797(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/4074