(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7344904号

(P7344904)

(45)発行日 令和5年9月14日(2023.9.14)

(24)登録日 令和5年9月6日(2023.9.6)

(51)国際特許分類

G 1 1 C 11/405 (2006.01)

F I

G 1 1 C 11/405

請求項の数 4 (全47頁)

(21)出願番号 特願2020-560634(P2020-560634)

(86)(22)出願日 令和1年11月20日(2019.11.20)

(86)国際出願番号 PCT/IB2019/059955

(87)国際公開番号 WO2020/128676

(87)国際公開日 令和2年6月25日(2020.6.25)

審査請求日 令和4年10月6日(2022.10.6)

(31)優先権主張番号 特願2018-239486(P2018-239486)

(32)優先日 平成30年12月21日(2018.12.21)

(33)優先権主張国・地域又は機関

日本国(JP)

特許法第30条第2項適用 [刊行物名] international ELECTRON DEVICES meeting 2018 TECHNICAL DIGEST, 312-315 発行年月日 平成30年12月1日

[集会名] 2018 IEEE International 最終頁に続く

(73)特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 大貫 達也

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

加藤 清

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

山崎 舜平

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 後藤 彰

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

ソース又はドレインの一方が、データを読み出すための第1配線に電気的に接続された第1トランジスタと、

ソース又はドレインの一方が、前記第1トランジスタのゲートに電気的に接続され、ソース又はドレインの他方が前記データを書き込むための第2配線に電気的に接続された第2トランジスタと、

ソース又はドレインの一方が、前記第1トランジスタのゲートに電気的に接続され、ソース又はドレインの他方が前記データに応じた電荷を保持するためのキャパシタに電気的に接続された第3トランジスタと、を有し、

前記第3トランジスタは、チャネル形成領域に金属酸化物を有し、

前記第2トランジスタ及び前記第3トランジスタを介して、前記キャパシタの一方の電極に前記データに応じた電位が与えられた後、前記第2トランジスタよりも前記第3トランジスタの方が先に非導通状態となる、半導体装置。

## 【請求項2】

請求項1において、

前記第2トランジスタは、チャネル形成領域に金属酸化物を有する、半導体装置。

## 【請求項3】

請求項1または請求項2において、

前記第1トランジスタは、チャネル形成領域にシリコンを有する、半導体装置。

## 【請求項 4】

請求項 1 乃至 請求項 3 のいずれか一において、

前記第 1 配線は、前記第 2 配線と同じ配線である半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本明細書は、半導体装置、並びにその動作方法等について説明する。

## 【0002】

本明細書において、半導体装置とは、半導体特性を利用した装置であり、半導体素子（トランジスタ、ダイオード、フォトダイオード等）を含む回路、同回路を有する装置等をいう。また、半導体特性を利用することで機能しうる装置全般をいう。例えば、集積回路、集積回路を備えたチップや、パッケージにチップを収納した電子部品は半導体装置の一例である。また、記憶装置、表示装置、発光装置、照明装置及び電子機器等は、それ自体が半導体装置であり、半導体装置を有している場合がある。

10

## 【背景技術】

## 【0003】

トランジスタに適用可能な半導体として金属酸化物が注目されている。“IGZO”、“イグゾー”などと呼ばれる In - Ga - Zn 酸化物は、多元系金属酸化物の代表的なものである。IGZOに関する研究において、単結晶でも非晶質でもない、CAAC (c - a x i s a l i g n e d c r y s t a l l i n e) 構造、および nc (n a n o c r y s t a l l i n e) 構造が見出された（例えば、非特許文献 1）。

20

## 【0004】

チャネル形成領域に金属酸化物半導体を有するトランジスタ（以下、「酸化物半導体トランジスタ」、または「OSトランジスタ」と呼ぶ場合がある。）は、極小オフ電流であることが報告されている（例えば、非特許文献 1、2）。OSトランジスタが用いられた様々な半導体装置が作製されている（例えば、非特許文献 3、4）。OSトランジスタの製造プロセスは、従来の Siトランジスタとの CMOS プロセスに組み込むことができ、OSトランジスタは Siトランジスタに積層することが可能である（例えば、非特許文献 4）。

30

## 【先行技術文献】

## 【非特許文献】

## 【0005】

【文献】 S. Yamazaki et al., “Properties of crystalline In - Ga - Zn - oxide semiconductor and its transistor characteristics,” Jpn. J. Appl. Phys., vol. 53, 04ED18 (2014).

K. Kato et al., “Evaluation of Off - State Current Characteristics of Transistor Using Oxide Semiconductor Material, Indium - Gallium - Zinc Oxide,” Jpn. J. Appl. Phys., vol. 51, 021201 (2012).

40

S. Amano et al., “Low Power LC Display Using In - Ga - Zn - Oxide TFTs Based on Variable Frame Frequency,” SID Symp. Dig. Papers, vol. 41, pp. 626 - 629 (2010).

T. Ishizu et al., “Embedded Oxide Semiconductor Memories: A Key Enabler for Low - Power ULSI,” ECS Tran., vol. 79, pp. 149 - 156 (2017).

## 【発明の概要】

## 【発明が解決しようとする課題】

50

**【0006】**

本発明の一形態の課題は、極小オフ電流を利用した記憶装置として機能する半導体装置において、データの長時間の保持といった信頼性に優れた半導体装置を提供すること、又は低消費電力化に優れた半導体装置を提供することである。

**【0007】**

複数の課題の記載は、互いの課題の存在を妨げるものではない。本発明の一形態は、例示した全ての課題を解決する必要はない。また、列記した以外の課題が、本明細書の記載から、自ずと明らかとなり、このような課題も、本発明の一形態の課題となり得る。

**【課題を解決するための手段】****【0008】**

本発明の一態様は、ソース又はドレインの一方が、データを読み出すための第1配線に電気的に接続された第1トランジスタと、ソース又はドレインの一方が、前記第1トランジスタのゲートに電気的に接続され、ソース又はドレインの他方が前記データを書き込むための第2配線に電気的に接続された第2トランジスタと、ソース又はドレインの一方が、前記第1トランジスタのゲートに電気的に接続され、ソース又はドレインの他方が前記データに応じた電荷を保持するためのキャパシタに電気的に接続された第3トランジスタと、を有し、前記第3トランジスタは、チャネル形成領域に金属酸化物を有する、半導体装置である。

**【0009】**

本発明の一態様において、前記第2トランジスタは、チャネル形成領域に金属酸化物を有する、半導体装置が好ましい。

**【0010】**

本発明の一態様において、前記第1トランジスタは、チャネル形成領域にシリコンを有する、半導体装置が好ましい。

**【0011】**

本発明の一態様において、前記第1配線は、前記第2配線と同じ配線である半導体装置が好ましい。

**【0012】**

本発明の一態様は、上記記載の半導体装置と、筐体と、を有する電子機器である。

**【0013】**

本発明の一態様は、上記記載の半導体装置の動作方法であり、前記第2トランジスタおよび前記第3トランジスタを導通状態とするデータ書き込み動作と、前記第3トランジスタを非導通状態とするデータ保持動作と、前記第2のトランジスタを非導通状態とし、且つ前記第3のトランジスタを導通状態とするデータ読み出し動作と、を含む半導体装置の動作方法である。

**【0014】**

なおその他の本発明の一態様については、以下で述べる実施の形態における説明、及び図面に記載されている。

**【発明の効果】****【0015】**

本発明の一形態によって、極小オフ電流を利用した記憶装置として機能する半導体装置において、データの長時間の保持といった信頼性に優れた半導体装置を提供すること、又は低消費電力化に優れた半導体装置を提供することができる。

**【0016】**

複数の効果の記載は、他の効果の存在を妨げるものではない。また、本発明の一形態は、必ずしも、例示した効果の全てを有する必要はない。また、本発明の一形態について、上記以外の課題、効果、および新規な特徴については、本明細書の記載および図面から自ずと明らかになるものである。

**【図面の簡単な説明】****【0017】**

10

20

30

40

50

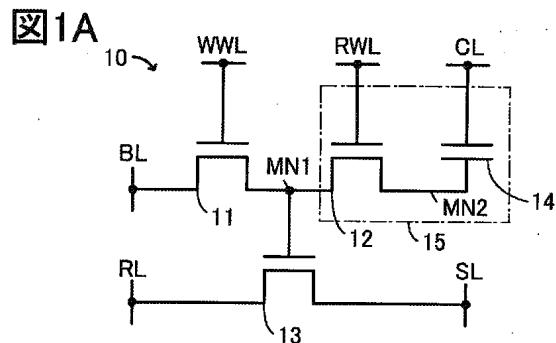

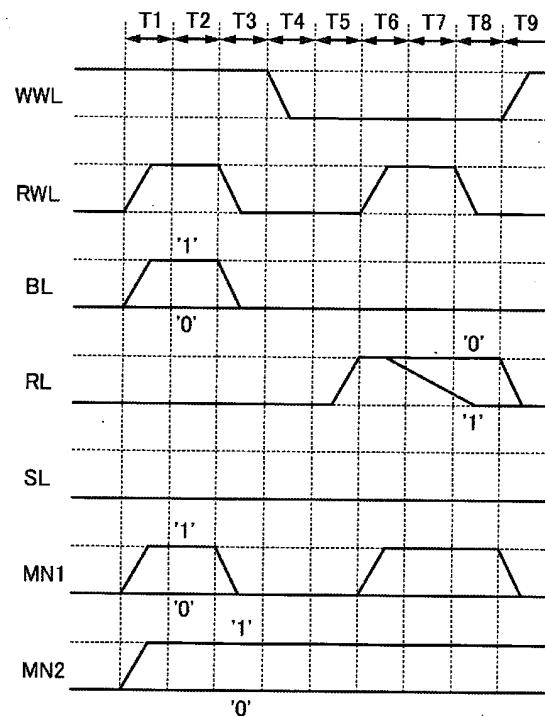

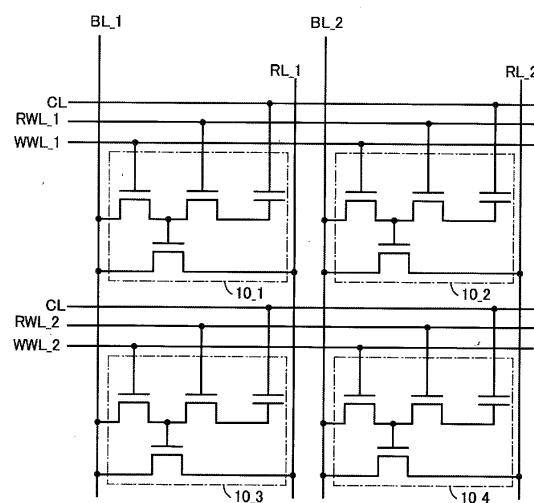

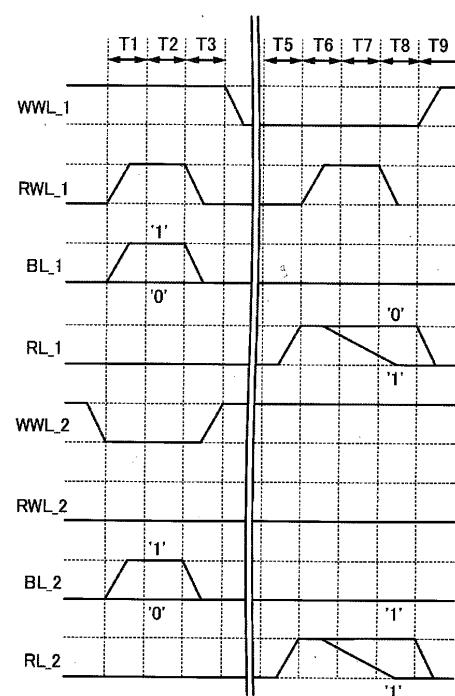

図1A、図1Bは半導体装置の構成例を示す回路図およびタイミングチャートである。

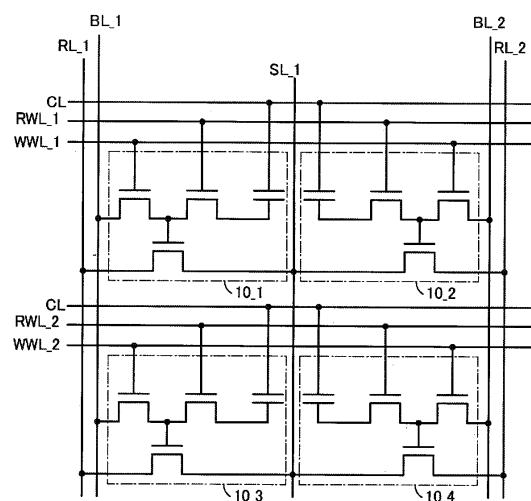

図2A、図2Bは半導体装置の構成例を示す回路図である。

図3A、図3Bは半導体装置の構成例を示す回路図である。

図4A、図4Bは半導体装置の構成例を示す回路図である。

図5A、図5Bは半導体装置の構成例を示す回路図である。

図6は半導体装置の構成例を示す回路図である。

図7A、図7Bは半導体装置の構成例を示す回路図である。

図8A、図8Bは半導体装置の構成例を示す回路図である。

図9A、図9B、図9Cは半導体装置の構成例を示す回路図である。

図10は半導体装置の構成例を示す回路図である。

10

図11は半導体装置の動作例を示すタイミングチャートである。

図12は半導体装置の構成例を示す回路図である。

図13は半導体装置の動作例を示すタイミングチャートである。

図14は半導体装置の構成例を示す回路図である。

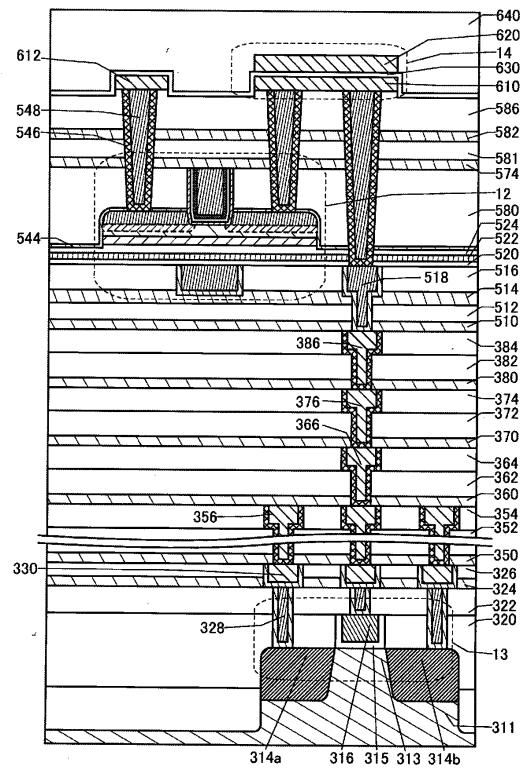

図15は半導体装置の構成例を説明する断面模式図である。

図16は半導体装置の構成例を説明する断面模式図である。

図17A、図17B、図17Cはトランジスタの構成例を説明する断面模式図である。

図18A、図18Bはトランジスタの構成例を説明する断面模式図である。

図19は半導体装置の構成例を説明する断面模式図である。

図20は記憶装置の構成例を示すプロック図である。

20

図21はメモリセルアレイの構成例を示すプロック図である。

図22A、図22Bは電子部品の一例を説明する図である。

図23は電子機器の例を示す図である。

【発明を実施するための形態】

【0018】

以下に、本発明の実施の形態を説明する。ただし、本発明の一形態は、以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明の一形態は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0019】

30

なお本明細書等において、「第1」、「第2」、「第3」という序数詞は、構成要素の混同を避けるために付したものである。従って、構成要素の数を限定するものではない。また、構成要素の順序を限定するものではない。また例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素が、他の実施の形態、あるいは特許請求の範囲において「第2」に言及された構成要素とすることもありうる。また例えば、本明細書等の実施の形態の一において「第1」に言及された構成要素を、他の実施の形態、あるいは特許請求の範囲において省略することもありうる。

【0020】

図面において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

40

【0021】

本明細書において、例えば、電源電位VDDを、電位VDD、VDD等と省略して記載する場合がある。これは、他の構成要素（例えば、信号、電圧、回路、素子、電極、配線等）についても同様である。

【0022】

また、複数の要素に同じ符号を用いる場合、特に、それらを区別する必要があるときには、符号に“\_1”、“\_2”、“[n]”、“[m, n]”等の識別用の符号を付記して記載する場合がある。例えば、2番目の配線GLを配線GL[2]と記載する。

【0023】

50

(実施の形態 1)

本発明の一態様である半導体装置、および半導体装置の動作方法の構成例について、図1乃至図14を参照して説明する。

【0024】

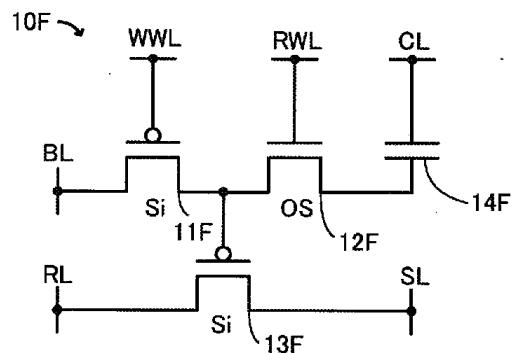

図1Aには、半導体装置の回路図の一例について示す。図1Aに示す半導体装置10は、トランジスタ11、トランジスタ12、トランジスタ13、およびキャパシタ14を有する。

【0025】

トランジスタ11のゲートは、配線WWLに接続される。トランジスタ11のソース又はドレインの一方は、トランジスタ13のゲート、およびトランジスタ12のソース又はドレインの一方に接続される。トランジスタ11のソース又はドレインの他方は、配線BLに接続される。なお図1A中および本明細書中の説明において、トランジスタ11のソース又はドレインの一方、トランジスタ13のゲート、およびトランジスタ12のソース又はドレインの一方が接続されるノードを、ノードMN1という。

10

【0026】

トランジスタ12のゲートは、配線RWLに接続される。トランジスタ12のソース又はドレインの他方は、キャパシタ14の一方の電極に接続される。キャパシタ14の他方の電極は、配線CLに接続される。なお図1A中および本明細書中の説明において、トランジスタ12のソース又はドレインの他方、およびキャパシタ14の一方の電極が接続されるノードを、ノードMN2という。なお配線CLは固定電位が与えられる配線である。

20

【0027】

なおキャパシタ14の静電容量値（ノードMN2の容量値）は、トランジスタ13のゲート容量（ノードMN1の容量値）より大きい構成とすることが好ましい。図1Aの構成では、半導体装置10からデータを読み出す際、ノードMN2からノードMN1にデータを書き戻してデータを読み出す構成となる。そのため、ノードMN1の容量値をノードMN2の容量値より小さくしておくことで、データを書き戻す際に要する電荷量を低減することができる。

【0028】

トランジスタ13のソース又はドレインの一方は、配線RLに接続される。トランジスタ13のソース又はドレインの他方は、配線SLに接続される。

30

【0029】

トランジスタ12は、ノードMN1の電圧を、配線RWLに与えられる電圧に応じて、ノードMN2に伝えるか否かを制御する機能を有する。またトランジスタ12は、配線RWLに与えられる電圧に応じて、ノードMN2に与えられる電圧をキャパシタ14に保持する機能を有する。トランジスタ12は、配線RWLに与えられる電圧に応じて導通状態または非導通状態（オンまたはオフともいう）が切り替えられるスイッチとして機能させることができる。

【0030】

トランジスタ12として、チャネル形成領域に酸化物半導体を有するトランジスタ（以下、OSトランジスタという）で構成されることが好ましい。本発明の一態様の構成では、OSトランジスタを有する記憶素子を用いる構成とすることで、オフ時にソースとドレイン間を流れるリーク電流（以下、オフ電流）が極めて低いことを利用して、所望の電圧を記憶素子に保持させることができる。

40

【0031】

トランジスタ12は、チャネル形成領域が酸化物半導体を有するトランジスタ（以下、OSトランジスタという）で構成されることが好ましい。本発明の一態様の構成では、OSトランジスタをトランジスタ12に用いる構成とすることで、非導通状態（オフ）時にソースとドレイン間を流れるリーク電流（以下、オフ電流）が極めて低いことを利用して、半導体装置10に書き込まれるデータに応じた電荷をキャパシタ14に保持させることができる。つまり、トランジスタ12およびキャパシタ14で構成される電荷保持回路1

50

5において、半導体装置10に書き込んだデータを長時間保持することができる。

【0032】

加えてOSトランジスタを用いた電荷保持回路15では、電荷の充電又は放電することによってデータの書き換えおよび読み出しが可能となるため、実質的に無制限回のデータの書き込みおよび読み出しが可能である。OSトランジスタを用いた電荷保持回路15は、磁気メモリあるいは抵抗変化型メモリなどのように原子レベルでの構造変化を伴わないため、書き換え耐性に優れている。またOSトランジスタを用いた電荷保持回路15は、フラッシュメモリのように繰り返し書き換え動作でも電子捕獲中心の増加による不安定性が認められない。

【0033】

またOSトランジスタを用いた電荷保持回路15は、チャネル形成領域がシリコンを有するトランジスタ（以下、Siトランジスタ）を用いた回路上などに自由に配置可能であるため、集積化を容易に行うことができる。またOSトランジスタは、Siトランジスタと同様の製造装置を用いて作製することが可能であるため、低コストで作製可能である。

【0034】

またOSトランジスタは、ゲート電極、ソース電極およびドレイン電極に加えて、バックゲート電極を含むと、4端子の半導体素子とすることができます。ゲート電極またはバックゲート電極に与える電圧に応じて、ソースとドレインとの間を流れる信号の入出力が独立制御可能な電気回路網で構成することができる。そのため、LSIと同一思考で回路設計を行うことができる。加えてOSトランジスタは、高温環境下において、Siトランジスタよりも優れた電気特性を有する。具体的には、125以上150以下といった高温下においてもオン電流とオフ電流の比が大きいため、良好なスイッチング動作を行うことができる。

【0035】

なおSiトランジスタに用いる材料としては、単結晶シリコン及び非単結晶シリコン（例えば、多結晶シリコン等）を用いることができる。Siトランジスタに単結晶シリコンを用いる場合、オン時にソースとドレインとの間を流れる電流（オン電流ともいう）を大きくすることができる。なお半導体層の材料としてはシリコンの他、ゲルマニウム（Ge）などの半導体、GaAs、InP、SiC、ZnSe、GaN、SiGeなどのような化合物半導体も用いることができる。

【0036】

トランジスタ11は、配線BLに与えられるデータに応じた電圧を、配線WWLに与えられる電圧に応じて、ノードMN1に伝えるか否かを制御する機能を有する。トランジスタ11は、配線WWLに与えられる電圧に応じて導通状態または非導通状態（オンまたはオフともいう）が切り替えられるスイッチとして機能させることができる。

【0037】

なお、スイッチとしてSiトランジスタを用いる場合、トランジスタの「導通状態」とは、トランジスタのソース電極とドレイン電極が電気的に短絡されているとみなせる状態をいう。また、トランジスタの「非導通状態」とは、トランジスタのソース電極とドレイン電極が電気的に遮断されているとみなせる状態をいう。

【0038】

配線BLに与えられるデータは、データ'1'、又はデータ'0'の二値のデータとして表すことができる。データ'1'、又はデータ'0'は、電位の高低によって書き込まれる信号である。データ'1'は、ノードMN2に保持された後、ノードMN2からノードMN1に電荷分配されることでトランジスタ12にデータを読み出し可能な程度に電流を流すための電位である。データ'0'は、ノードMN2に保持された後、ノードMN2からノードMN1に電荷分配された際にトランジスタ12に電流を流さないための電位である。

【0039】

トランジスタ13は、ノードMN1の電位に応じて、ソース電極とドレイン電極との間を流れる電流量を制御する機能を有する。配線RLは、プリチャージ回路によって電荷が

10

20

30

40

50

与えられ（プリチャージされ）た後、トランジスタ 13 を流れる電流量に応じて電位が変動する配線である。配線 S L は、ノード MN 1 の電位に応じて、トランジスタ 13 に流れる電流量を制御するための電位が与えられる配線である。

【 0 0 4 0 】

図 1 A の構成とすることで、電荷の充電又は放電することによってデータの書き換えおよび読み出しが可能となるため、実質的に無制限回のデータの書き込みおよび読み出しが可能である。データの読み出し時において、保持した電荷を放電すること、いわゆる破壊読み出しすることなくデータを読み出すことができるため、データリフレッシュに要する電荷の充電および放電の分の消費電力を低減することができる。

【 0 0 4 1 】

また図 1 A の構成とすることで、ノード MN 1 の容量値がノード MN 2 の容量値より小さくなるため、データを書き戻す際に要する電荷量を低減することができる。そのため、保持した電荷を静電容量の大きい配線等に放電することなく、データを読み出すことができる。またノード MN 2 の容量値を大きくすることで、データの長時間の保持といった信頼性に優れた半導体装置とすることができる。

【 0 0 4 2 】

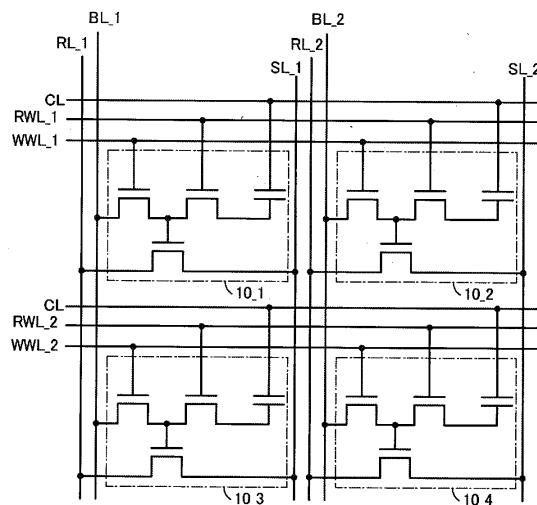

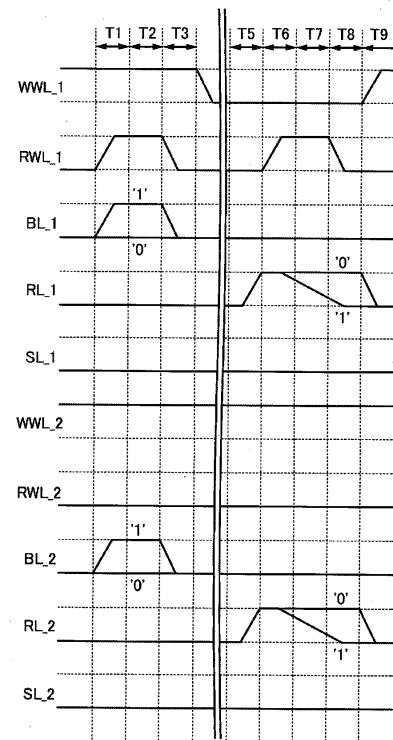

図 1 B には、図 1 A の半導体装置の動作例を説明するためにタイミングチャートを示す。図 1 B では、配線 WW L、配線 RW L、配線 BL、配線 RL、配線 SL、ノード MN 1 およびノード MN 2 におけるデータの書き込み及び読み出しに応じた電位の変動を模式的に図示している。図 1 B では、期間 T 1 乃至 T 9 に分けて図示しており、期間 T 1 乃至 T 3 がデータ書き込み期間、期間 T 4 がデータ保持期間、期間 T 5 乃至期間 T 9 がデータ読み出し期間に相当する。また図 1 B では、データを '1'、'0' の信号と図示している。また半導体装置 10 の動作例の説明において、トランジスタの導通状態または非導通状態を制御する信号が与えられる配線の電位を H レベルまたは L レベルの電位として説明する。

【 0 0 4 3 】

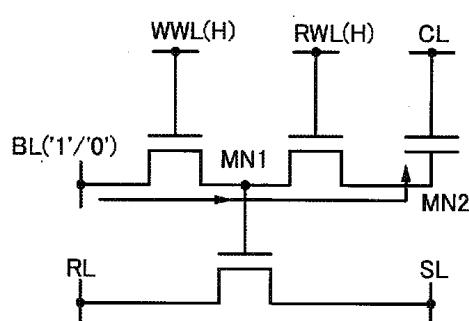

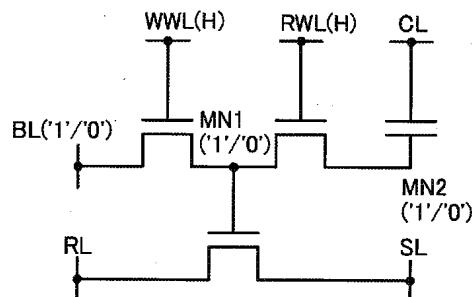

また図 2 乃至図 6 では、図 1 B の期間 T 1 乃至 T 9 における半導体装置 10 の動作を模式的に説明するための図である。なお図 2 乃至図 6 において、実線矢印は、配線またはノードの間で入出力される信号の流れを模式的に表している。また図 2 乃至図 6 において、回路図における理解を容易にするため、非導通状態のトランジスタにバツ印を付している。

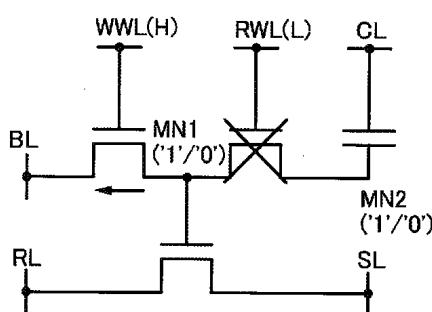

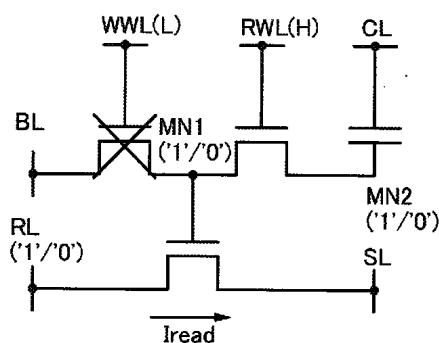

【 0 0 4 4 】

図 1 B の期間 T 1 は、データ書き込み動作を行う期間である。図 2 A に図示するように、配線 WW L を H レベル、配線 RW L を H レベルとし、トランジスタ 11 およびトランジスタ 12 を導通状態とする。配線 BL ではデータ '1'、'0' に応じた電位が与えられ、当該電位がノード MN 1 およびノード MN 2 に与えられる。配線 RL および配線 SL は同電位とし、トランジスタ 13 に電流は流れない。

【 0 0 4 5 】

図 1 B の期間 T 2 は、データ書き込み動作を行う期間である。図 2 B に図示するように。ノード MN 1 およびノード MN 2 の電位が、データ '1'、'0' に応じた電位となる。

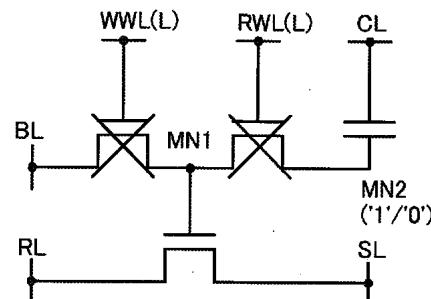

【 0 0 4 6 】

図 1 B の期間 T 3 は、データ書き込み動作を行う期間である。図 3 A に図示するように。配線 WW L を H レベル、配線 RW L を L レベルとし、トランジスタ 11 を導通状態、トランジスタ 12 を非導通状態とする。ノード MN 2 ではデータ '1'、'0' に応じた電位が保持される。ノード MN 1 ではデータ '1'、'0' に応じた電位が配線 BL に放電され、やがて L レベルの電位となる。

【 0 0 4 7 】

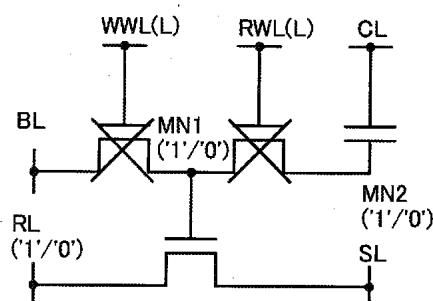

図 1 B の期間 T 4 は、データ保持を行う期間である。図 3 B に図示するように。配線 WL を L レベル、配線 RW L を L レベルとし、トランジスタ 11 を非導通状態、トランジスタ 12 を非導通状態とする。ノード MN 2 ではデータ '1'、'0' に応じた電位が保持される。ノード MN 1 では期間 T 3 の電位、つまり L レベルが保持される。ノード MN 2 の電位は、トランジスタ 11 及びトランジスタ 12 を共に非導通状態とすることで、配線 BL 50

に対して放電しにくくすることができる。

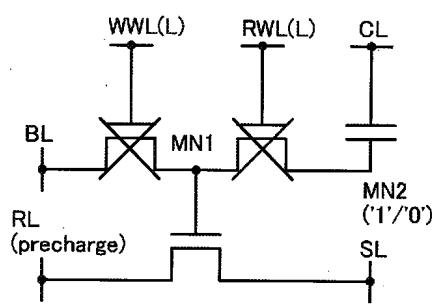

【0048】

図1Bの期間T5は、データ読み出し動作を行う期間である。図4Aに図示するように。配線WWLをLレベル、配線RWLをLレベルとし、トランジスタ11を非導通状態、トランジスタ12を非導通状態とする。配線RLは、所定の電位、例えばHレベルの電位にプリチャージする(図中、prechargeと図示)。

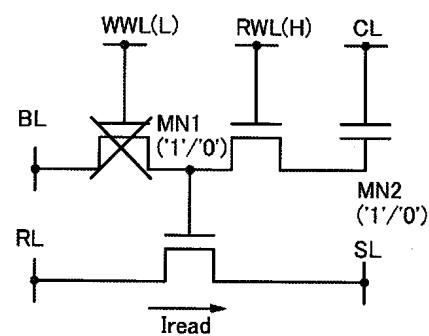

【0049】

図1Bの期間T6は、データ読み出し動作を行う期間である。図4Bに図示するように。配線WWLをLレベル、配線RWLをHレベルとし、トランジスタ11を非導通状態、トランジスタ12を導通状態とする。ノードMN2に保持された電荷がノードMN1に分配され、ノードMN1およびノードMN2がデータ'1'、'0'に応じた電位となる。ノードMN1の容量値は、ノードMN2の容量値と比べて小さいため、電荷の分配に応じた電位の変動を小さくすることができる。トランジスタ13では、ノードMN1の電位、つまり電荷保持回路15に保持されたデータ'1'、'0'に応じて、電流Ireadが流れる。電流Ireadは、ノードMN1の電位がHレベルつまりデータ'1'であれば大きく、ノードMN1の電位がLレベルつまりデータ'0'であれば小さい。そのため、データ'1'であれば、プリチャージされた配線RLの電位の変動が大きく、データ'0'であれば、プリチャージされた配線RLの電位の変動が小さくなる。期間T5でプリチャージされた配線RLは、電流Ireadの大小に応じて、電位が変動する。

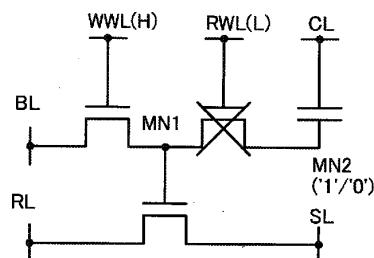

【0050】

図1Bの期間T7は、データ読み出し動作を行う期間である。図5Aに図示するように。トランジスタ13では、ノードMN1の電位に応じて、電流Ireadが流れる。ノードMN1のデータがデータ'1'、つまりHレベルの電位であれば電流Ireadが大きい。そのため、プリチャージされた配線RLの電位の変動が大きい。逆に、ノードMN1のデータがデータ'0'、つまりLレベルの電位であれば電流Ireadが小さい(配線RLはLレベルに変化する)。そのため、プリチャージされた配線RLの電位の変動が小さい(配線RLはHレベルのまま)。そのため、半導体装置10に書き込まれたデータは、配線RLに読み出すことができる。

【0051】

図1Bの期間T8は、データ読み出し動作を行う期間である。図5Bに図示するように。配線WWLをLレベル、配線RWLをLレベルとし、トランジスタ11を非導通状態、トランジスタ12を非導通状態とする。ノードMN1およびノードMN2の電位が、データ'1'、'0'に応じた電位となる。

【0052】

図1Bの期間T9は、データ読み出し動作を行う期間である。図6に図示するように。配線WWLをHレベル、配線RWLをLレベルとし、トランジスタ11を導通状態、トランジスタ12を非導通状態とする。ノードMN2ではデータ'1'、'0'に応じた電位が保持される。ノードMN1ではデータ'1'、'0'に応じた電位が配線BLに放電される。ノードMN1では配線BLの電位、つまりLレベルとなる。トランジスタ13では、電流Ireadが流れなくなる。

【0053】

図1Aの構成において、図1B、図2乃至図6の動作方法とすることで、電荷の充電又は放電することによってデータの書き換えおよび読み出しが可能となるため、実質的に無制限回のデータの書き込みおよび読み出しが可能である。データの読み出し時ににおいて、保持した電荷を放電すること、いわゆる破壊読み出しそれなくデータ読み出すことができるため、データリフレッシュに要する電荷の充電および放電の分の消費電力を低減することができる。

【0054】

また図1Aの構成において、図1B、図2乃至図6の動作方法とすることで、ノードMN1の容量値がノードMN2の容量値より小さいため、データを書き戻す際に要する電荷

10

20

30

40

50

量を低減することができる。そのため、保持した電荷を静電容量の大きい配線等に放電することなく、データを読み出すことができる。またノードM N 2 の容量値を大きくすることで、データの長時間の保持といった信頼性に優れた半導体装置とすることができます。

【0055】

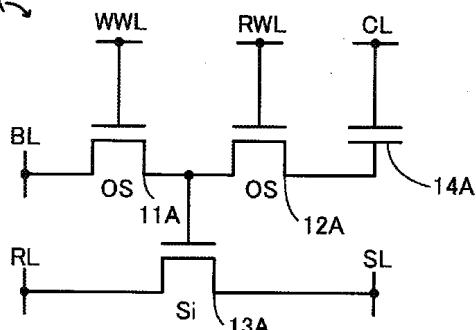

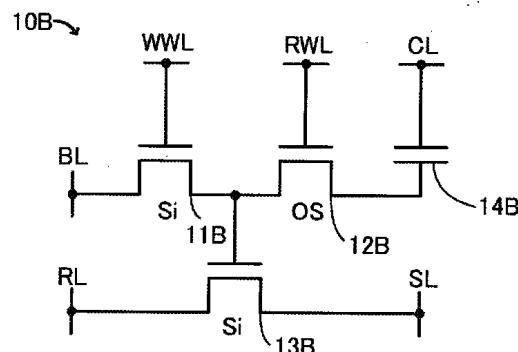

なおトランジスタ11は、トランジスタ12と同様に、OSトランジスタとすることができます。OSトランジスタは、Siトランジスタを用いた回路上などに自由に配置可能であるため、集積化を容易に行うことができる。またOSトランジスタは、Siトランジスタと同様の製造装置を用いて作製することが可能であるため、低コストで作製可能である。図7Aにおいて半導体装置10Aが有するトランジスタ11Aおよびトランジスタ12Aは、OSトランジスタであることを明示するために、OSの符号を合わせて付している。またトランジスタ13Aは、Siトランジスタであることを明示するために、Siの符号を合わせて付している。

10

【0056】

なおトランジスタ11は、トランジスタ13と同様に、Siトランジスタとすることができます。図7Bにおいて半導体装置10Bが有するトランジスタ12Bは、OSトランジスタであることを明示するために、OSの符号を合わせて付している。またトランジスタ11Bおよびトランジスタ13Bは、Siトランジスタであることを明示するために、Siの符号を合わせて付している。

【0057】

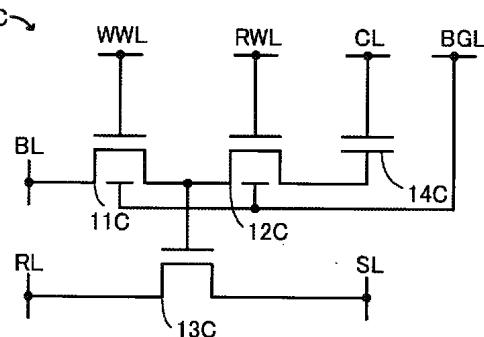

図7Aにおいて、半導体装置10Aが有するトランジスタ11Aおよび12Aは、バックゲート電極がないトップゲート構造またはボトムゲート構造のトランジスタとして図示したが、トランジスタ11Aおよび12Aの構造はこれに限らない。例えば、図8Aに図示する半導体装置10Cのように、バックゲート電極線BGLに接続されたバックゲート電極を有するトランジスタ11Cおよびトランジスタ12Cとしてもよい。トランジスタ13CはSiトランジスタである。図8Aの構成とすることで、トランジスタ11Cおよびトランジスタ12Cのしきい値電圧などの電気特性を外部より制御しやすくすることができる。

20

【0058】

あるいは図8Bに図示する半導体装置10Dのように、ゲート電極に接続されたバックゲート電極を有するトランジスタ11Dおよびトランジスタ12Dとしてもよい。トランジスタ13DはSiトランジスタである。図8Bの構成とすることで、トランジスタ11Dおよびトランジスタ12Dを流れる電流を増やすことができる。

30

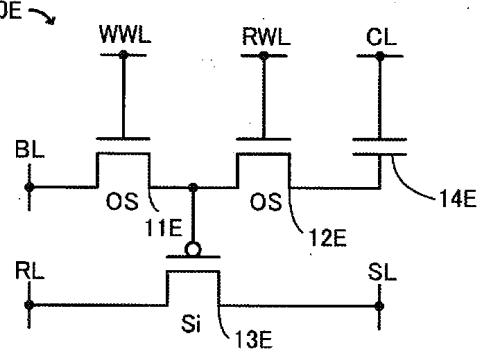

【0059】

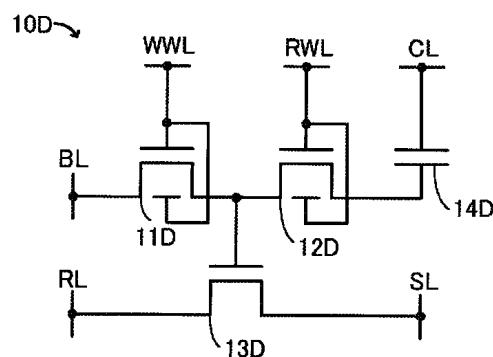

図7Aにおいて、半導体装置10Aが有するトランジスタ13Aは、nチャネル型のトランジスタとして図示したが、トランジスタ13Aの導電型はこれに限らない。例えば、図9Aに図示する半導体装置10Eのように、pチャネル型のトランジスタ13Eとすることができます。トランジスタ11Eおよびトランジスタ12Eはnチャネル型のOSトランジスタである。

【0060】

図7Bにおいて、半導体装置10Bが有するトランジスタ11Bおよびトランジスタ13Bは、nチャネル型のトランジスタとして図示したが、トランジスタ11Bおよびトランジスタ13Bの導電型はこれに限らない。例えば、図9Bに図示する半導体装置10Fのように、pチャネル型のトランジスタ11Fおよび13Fとすることができます。トランジスタ12Fはnチャネル型のOSトランジスタである。

40

【0061】

図7Bにおいて、半導体装置10Bが有するトランジスタ11Bおよびトランジスタ13Bは、同じ導電型のトランジスタとして図示したが、トランジスタ11Bおよびトランジスタ13Bの導電型は別々でもよい。例えば、図9Cに図示する半導体装置10Gのように、nチャネル型のトランジスタ11Gと、pチャネル型のトランジスタ13Gとすることができます。トランジスタ12Gはnチャネル型のOSトランジスタである。

50

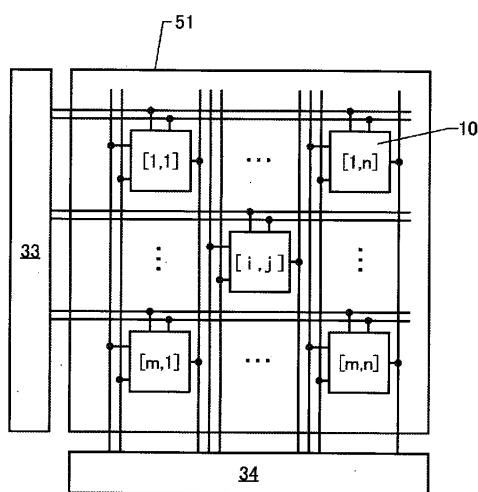

**【 0 0 6 2 】**

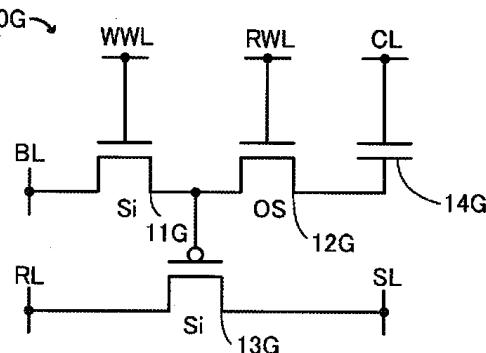

なお半導体装置 10 は、マトリクス状に配置することができる。図 10 には、図 1 A の半導体装置 10 を 2 行 2 列のマトリクス状に配置する場合の構成例を図示している。図 10 において、半導体装置 10 は、半導体装置 10\_1 乃至 10\_4 として図示している。また図 10 では、各半導体装置 10\_1 乃至 10\_4 に接続される配線として、配線 R WL\_1、RWL\_2、配線 WWL\_1、WWL\_2、配線 RL\_1、RL\_2、配線 BL\_1、BL\_2、および配線 SL\_1、SL\_2 を図示している。

**【 0 0 6 3 】**

図 11 には、図 10 に図示する構成における動作例を説明するためのタイミングチャート図を示す。なお図 11 に示すタイミングチャートの詳細については、図 1 B と重複するため、説明を省略する。

10

**【 0 0 6 4 】**

なお図 10 の構成において、異なる配線同士の機能を共通化して、配線数を削減する構成とすることができます。一例として図 12 では、図 10 における配線 RL\_1、RL\_2 と配線 SL\_1、SL\_2 との機能を兼ね備えるよう動作させることで、配線 SL\_1、SL\_2 を省略する構成例を図示している。つまり配線 RL は、配線 SL と同じ配線であるとして動作させることで、配線数を削減することができる。

**【 0 0 6 5 】**

図 13 には、図 12 に図示する構成における動作例を説明するためのタイミングチャート図を示す。なお図 13 に示すタイミングチャートが図 11 に示すタイミングチャートと異なる点としては、1 行目の半導体装置へのデータ書き込み動作の際、その他の行、例えば 2 行目の配線 WWL\_2 を L レベルとしておく点が異なる。当該構成とすることで、データ書き込み時にトランジスタ 13 を流れる電流を抑制することができる。なおその他の期間のタイミングチャートの詳細については、図 1 B と重複するため、説明を省略する。

20

**【 0 0 6 6 】**

また図 12 とは別の例として、図 14 では、図 10 における配線 SL\_1 と SL\_2 との機能を兼ね備えるよう動作させることで、配線 SL\_2 を省略する構成例を図示している。つまり配線 SL は、複数の半導体装置間で共有させることで、配線数を削減することができる。

**【 0 0 6 7 】**

30

以上説明した実施の形態で説明した構成では、電荷の充電又は放電することによってデータの書き換えおよび読み出しが可能となるため、実質的に無制限回のデータの書き込みおよび読み出しが可能である。データの読み出し時において、保持した電荷を放電すること、いわゆる破壊読み出しすることなくデータ読み出すことができるため、データリフレッシュに要する電荷の充電および放電の分の消費電力を低減することができる。

**【 0 0 6 8 】**

また以上説明した実施の形態で説明した構成では、ノード MN 1 の容量値がノード MN 2 の容量値より小さいため、データを書き戻す際に要する電荷量を低減することができる。そのため、保持した電荷を静電容量の大きい配線等に放電することなく、データを読み出すことができる。またノード MN 2 の容量値を大きくすることで、データの長時間の保持といった信頼性に優れた半導体装置とすることができます。

40

**【 0 0 6 9 】****( 実施の形態 2 )**

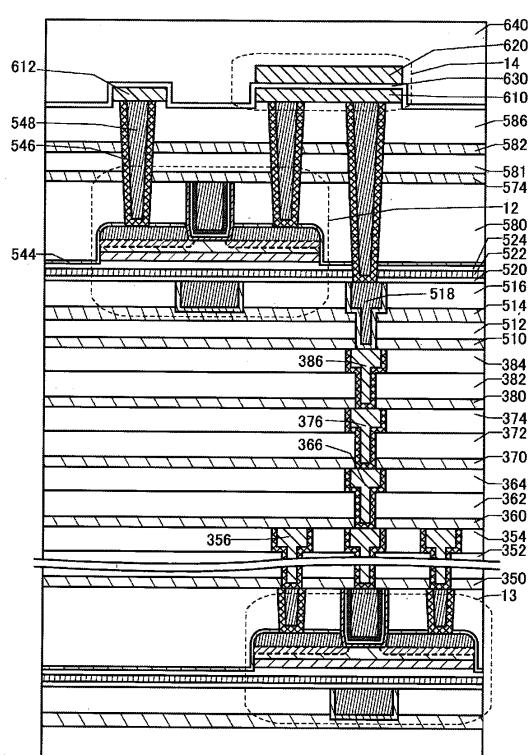

本実施の形態では、上記実施の形態で説明した半導体装置の断面構成例について、図面を用いて説明する。

**【 0 0 7 0 】**

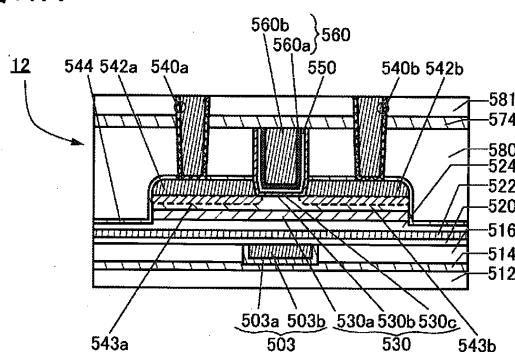

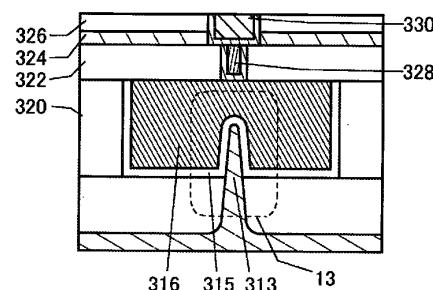

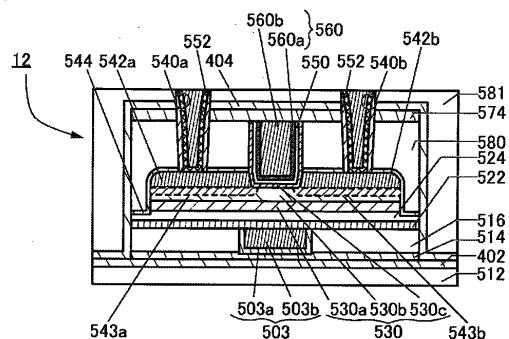

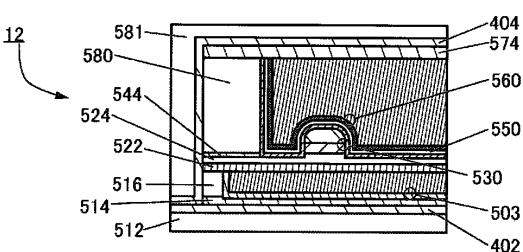

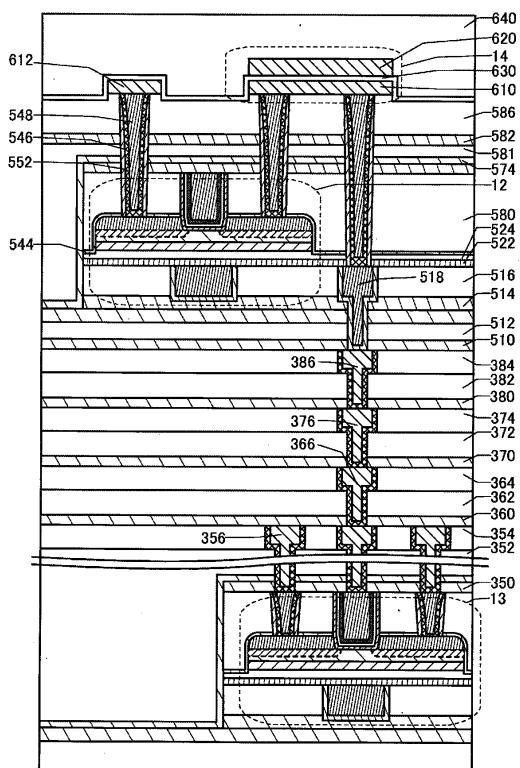

図 15 に示す半導体装置は、トランジスタ 13 と、トランジスタ 12 と、キャパシタ 14 と、を有している。図 17 A はトランジスタ 12 のチャネル長方向の断面図であり、図 17 B はトランジスタ 12 のチャネル幅方向の断面図であり、図 17 C はトランジスタ 13 のチャネル幅方向の断面図である。

50

## 【0071】

トランジスタ12は、OSトランジスタである。トランジスタ12は、オフ電流が小さい。このため、半導体装置の消費電力を低減することができる。

## 【0072】

本実施の形態で説明する半導体装置は、図15に示すようにトランジスタ13、トランジスタ12、及びキャパシタ14を有する。トランジスタ12はトランジスタ13の上方に設けられ、キャパシタ14はトランジスタ13、及びトランジスタ12の上方に設けられている。

## 【0073】

トランジスタ13は、基板311上に設けられ、導電体316、絶縁体315、基板311の一部からなる半導体領域313、ソース領域又はドレイン領域として機能する低抵抗領域314a、及び低抵抗領域314bを有する。

10

## 【0074】

トランジスタ13は、図17Cに示すように、半導体領域313の上面、及びチャネル幅方向の側面が絶縁体315を介して導電体316に覆われている。このように、トランジスタ13をFin型とすることにより、実効上のチャネル幅が増大する。これにより、トランジスタ13のオン特性を向上させることができる。また、ゲート電極の電界の寄与を高くすることができるため、トランジスタ13のオフ特性を向上させることができる。

## 【0075】

なお、トランジスタ13は、pチャネル型、あるいはnチャネル型のいずれでもよい。

20

## 【0076】

半導体領域313のチャネルが形成される領域及びその近傍の領域、並びにソース領域又はドレイン領域となる低抵抗領域314a及び低抵抗領域314b等において、シリコン系半導体等の半導体を含むことが好ましく、単結晶シリコンを含むことが好ましい。又は、Ge(ゲルマニウム)、SiGe(シリコンゲルマニウム)、GaAs(ガリウムヒ素)、GaAlAs(ガリウムアルミニウムヒ素)等を有する材料で形成してもよい。結晶格子に応力を与え、格子間隔を変化させることで有効質量を制御したシリコンを用いた構成としてもよい。又はGaAsとGaAlAs等を用いることで、トランジスタ13をHEMT(High Electron Mobility Transistor)としてもよい。

30

## 【0077】

低抵抗領域314a、及び低抵抗領域314bは、半導体領域313に適用される半導体材料に加え、ヒ素、リン等のn型の導電性を付与する元素、又はホウ素等のp型の導電性を付与する元素を含む。

## 【0078】

ゲート電極として機能する導電体316は、ヒ素、リン等のn型の導電性を付与する元素、もしくはホウ素等のp型の導電性を付与する元素を含むシリコン等の半導体材料、金属材料、合金材料、又は金属酸化物材料等の導電性材料を用いることができる。

## 【0079】

なお、導電体の材料によって仕事関数が決まるため、当該導電体の材料を選択することで、トランジスタのしきい値電圧を調整することができる。具体的には、導電体に窒化チタンや窒化タンタル等の材料を用いることが好ましい。さらに導電性と埋め込み性を両立するために導電体にタンクスチンやアルミニウム等の金属材料を積層として用いることが好ましく、特にタンクスチンを用いることが耐熱性の点で好ましい。

40

## 【0080】

なお、図15に示すトランジスタ13は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。例えば、半導体装置をOSトランジスタのみの単極性回路とする場合、図16に示すとおり、トランジスタ13の構成を、OSトランジスタであるトランジスタ12と同様の構成にすればよい。なお、トランジスタ12の詳細については後述する。

50

## 【0081】

本明細書等において、単極性回路とは、例えば全てのトランジスタが同極性のトランジスタである回路を示す。例えば、全てのトランジスタがnチャネル型トランジスタである回路は、単極性回路であることができる。

## 【0082】

トランジスタ13を覆って、絶縁体320、絶縁体322、絶縁体324、及び絶縁体326が順に積層して設けられている。

## 【0083】

絶縁体320、絶縁体322、絶縁体324、及び絶縁体326として、例えば、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、酸化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、窒化アルミニウム等を用いればよい。

10

## 【0084】

なお、本明細書等において、酸化窒化シリコンとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化シリコンとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。また、本明細書等において、酸化窒化アルミニウムとは、その組成として窒素よりも酸素の含有量が多い材料を指し、窒化酸化アルミニウムとは、その組成として、酸素よりも窒素の含有量が多い材料を示す。

## 【0085】

絶縁体322は、その下方に設けられるトランジスタ13等によって生じる段差を平坦化する平坦化膜としての機能を有していてもよい。例えば、絶縁体322の上面は、平坦性を高めるために化学機械研磨(CMP)法等を用いた平坦化処理により平坦化されてもよい。

20

## 【0086】

また、絶縁体324には、基板311、又はトランジスタ13等から、トランジスタ12が設けられる領域に、水素や不純物が拡散しないようなバリア性を有する膜を用いることが好ましい。

## 【0087】

水素に対するバリア性を有する膜の一例として、例えば、CVD法で形成した窒化シリコンを用いることができる。ここで、トランジスタ12等の酸化物半導体を有する半導体素子に水素が拡散することで、当該半導体素子の特性が低下する場合がある。したがって、トランジスタ12と、トランジスタ13との間に、水素の拡散を抑制する膜を用いることが好ましい。水素の拡散を抑制する膜とは、具体的には、水素の脱離量が少ない膜とする。

30

## 【0088】

水素の脱離量は、例えば、昇温脱離ガス分析法(TDS)等を用いて分析することができる。例えば、絶縁体324の水素の脱離量は、TDS分析において、膜の表面温度が50から500の範囲において、水素原子に換算した脱離量が、絶縁体324の面積当たりに換算して、 $10 \times 10^{15} \text{ atoms/cm}^2$ 以下、好ましくは $5 \times 10^{15} \text{ atoms/cm}^2$ 以下であればよい。

40

## 【0089】

なお、絶縁体326は、絶縁体324よりも誘電率が低いことが好ましい。例えば、絶縁体326の比誘電率は4未満が好ましく、3未満がより好ましい。また例えば、絶縁体326の比誘電率は、絶縁体324の比誘電率の0.7倍以下が好ましく、0.6倍以下がより好ましい。誘電率が低い材料を層間膜として、配線間に生じる寄生容量を低減することができる。

## 【0090】

また、絶縁体320、絶縁体322、絶縁体324、及び絶縁体326にはキャパシタ14、又はトランジスタ12と接続する導電体328、及び導電体330等が埋め込まれている。なお、導電体328、及び導電体330は、プラグ又は配線としての機能を有する。また、プラグ又は配線としての機能を有する導電体は、複数の構造をまとめて同一の

50

符号を付与する場合がある。また、本明細書等において、配線と、配線と接続するプラグとが一体物であってもよい。すなわち、導電体の一部が配線として機能する場合、及び導電体の一部がプラグとして機能する場合もある。

【0091】

各プラグ、及び配線（導電体328、導電体330等）の材料としては、金属材料、合金材料、金属窒化物材料、又は金属酸化物材料等の導電性材料を、単層又は積層して用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデン等の高融点材料を用いることが好ましく、タンゲステンを用いることが好ましい。又は、アルミニウムや銅等の低抵抗導電性材料で形成することが好ましい。低抵抗導電性材料を用いることで配線抵抗を低くすることができる。

10

【0092】

絶縁体326、及び導電体330上に、配線層を設けてもよい。例えば、図15において、絶縁体350、絶縁体352、及び絶縁体354が順に積層して設けられている。また、絶縁体350、絶縁体352、及び絶縁体354には、導電体356が形成されている。導電体356は、トランジスタ13と接続するプラグ、又は配線としての機能を有する。なお導電体356は、導電体328、又は導電体330と同様の材料を用いて設けることができる。

【0093】

なお、例えば、絶縁体350は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体356は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体350に設けられる開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ13とトランジスタ12とは、バリア層により分離することができ、トランジスタ13からトランジスタ12への水素の拡散を抑制することができる。

20

【0094】

なお、水素に対するバリア性を有する導電体としては、例えば、窒化タンタル等を用いるとよい。また、窒化タンタルと導電性が高いタンゲステンを積層することで、配線としての導電性を保持したまま、トランジスタ13からの水素の拡散を抑制することができる。この場合、水素に対するバリア性を有する窒化タンタル層が、水素に対するバリア性を有する絶縁体350と接する構造であることが好ましい。

30

【0095】

絶縁体354、及び導電体356上に、配線層を設けてもよい。例えば、図15において、絶縁体360、絶縁体362、及び絶縁体364が順に積層して設けられている。また、絶縁体360、絶縁体362、及び絶縁体364には、導電体366が形成されている。導電体366は、プラグ又は配線としての機能を有する。なお導電体366は、導電体328、又は導電体330と同様の材料を用いて設けることができる。

【0096】

なお、例えば、絶縁体360は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体366は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体360に設けられる開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ13とトランジスタ12とは、バリア層により分離することができ、トランジスタ13からトランジスタ12への水素の拡散を抑制することができる。

40

【0097】

絶縁体364、及び導電体366上に、配線層を設けてもよい。例えば、図15において、絶縁体370、絶縁体372、及び絶縁体374が順に積層して設けられている。また、絶縁体370、絶縁体372、及び絶縁体374には、導電体376が形成されている。導電体376は、プラグ又は配線としての機能を有する。なお導電体376は、導電体328、又は導電体330と同様の材料を用いて設けることができる。

【0098】

50

なお、例えば、絶縁体370は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体376は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体370に設けられる開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ13とトランジスタ12とは、バリア層により分離することができ、トランジスタ13からトランジスタ12への水素の拡散を抑制することができる。

【0099】

絶縁体374、及び導電体376上に、配線層を設けてもよい。例えば、図15において、絶縁体380、絶縁体382、及び絶縁体384が順に積層して設けられている。また、絶縁体380、絶縁体382、及び絶縁体384には、導電体386が形成されている。導電体386は、プラグ又は配線としての機能を有する。なお導電体386は、導電体328、又は導電体330と同様の材料を用いて設けることができる。

10

【0100】

なお、例えば、絶縁体380は、絶縁体324と同様に、水素に対するバリア性を有する絶縁体を用いることが好ましい。また、導電体386は、水素に対するバリア性を有する導電体を含むことが好ましい。特に、水素に対するバリア性を有する絶縁体380に設けられる開口部に、水素に対するバリア性を有する導電体が形成される。当該構成により、トランジスタ13とトランジスタ12とは、バリア層により分離することができ、トランジスタ13からトランジスタ12への水素の拡散を抑制することができる。

20

【0101】

上記において、導電体356を含む配線層、導電体366を含む配線層、導電体376を含む配線層、及び導電体386を含む配線層、について説明したが、本実施の形態に係る半導体装置はこれに限られるものではない。導電体356を含む配線層と同様の配線層を3層以下にしてもよいし、導電体356を含む配線層と同様の配線層を5層以上にしてよい。

【0102】

絶縁体384上には絶縁体510、絶縁体512、絶縁体514、及び絶縁体516が、順に積層して設けられている。絶縁体510、絶縁体512、絶縁体514、及び絶縁体516のいずれかは、酸素や水素に対してバリア性のある物質を用いることが好ましい。

30

【0103】

例えば、絶縁体510及び絶縁体514には、基板311等から、又はトランジスタ13を設ける領域等からトランジスタ12を設ける領域に、水素や不純物が拡散しないようなバリア性を有する膜を用いることが好ましい。したがって、絶縁体324と同様の材料を用いることが好ましい。

【0104】

水素に対するバリア性を有する膜の一例として、CVD法で形成した窒化シリコンを用いることができる。ここで、トランジスタ12等の酸化物半導体を有する半導体素子に水素が拡散することで、当該半導体素子の特性が低下する場合がある。したがって、トランジスタ12と、トランジスタ13との間に、水素の拡散を抑制する膜を用いることが好ましい。水素の拡散を抑制する膜とは、具体的には、水素の脱離量が少ない膜である。

40

【0105】

また、水素に対するバリア性を有する膜として、例えば、絶縁体510、及び絶縁体514には、酸化アルミニウム、酸化ハフニウム、酸化タンタル等の金属酸化物を用いることが好ましい。

【0106】

特に、酸化アルミニウムは、酸素と、トランジスタの電気特性の変動要因となる水素、水分等の不純物と、の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウムは、トランジスタの作製工程中及び作製後において、水素、水分等の不純物のトランジスタ12への混入を防止することができる。また、トランジスタ12を構成する金属酸化物からの酸素の放出を抑制することができる。そのため、トランジスタ12に

50

対する保護膜として用いることに適している。

【0107】

また、例えば、絶縁体512、及び絶縁体516には、絶縁体320と同様の材料を用いることができる。また、これらの絶縁体に、比較的誘電率が低い材料を適用することでき、配線間に生じる寄生容量を低減することができる。例えば、絶縁体512、及び絶縁体516として、酸化シリコン膜や酸化窒化シリコン膜等を用いることができる。

【0108】

また、絶縁体510、絶縁体512、絶縁体514、及び絶縁体516には、導電体518、及びトランジスタ12を構成する導電体（例えば、導電体503）等が埋め込まれている。なお、導電体518は、キャパシタ14、又はトランジスタ13と接続するプラグ、又は配線としての機能を有する。導電体518は、導電体328、又は導電体330と同様の材料を用いて設けることができる。

10

【0109】

特に、絶縁体510、及び絶縁体514と接する領域の導電体518は、酸素、水素、及び水に対するバリア性を有する導電体であることが好ましい。当該構成により、トランジスタ13とトランジスタ12とは、酸素、水素、及び水に対するバリア性を有する層で分離することができ、トランジスタ13からトランジスタ12への水素の拡散を抑制することができる。

【0110】

絶縁体516の上方には、トランジスタ12が設けられている。

20

【0111】

図17A、図17Bに示すように、トランジスタ12は、絶縁体514及び絶縁体516に埋め込まれるように配置された導電体503と、絶縁体516及び導電体503の上に配置された絶縁体520と、絶縁体520の上に配置された絶縁体522と、絶縁体522の上に配置された絶縁体524と、絶縁体524の上に配置された酸化物530aと、酸化物530aの上に配置された酸化物530bと、酸化物530b上に互いに離れて配置された導電体542a及び導電体542bと、導電体542a及び導電体542b上に配置され、導電体542aと導電体542bの間に重畠して開口が形成された絶縁体580と、開口の底面及び側面に配置された酸化物530cと、酸化物530cの形成面に配置された絶縁体550と、絶縁体550の形成面に配置された導電体560と、を有する。

30

【0112】

また、図17A、図17Bに示すように、酸化物530a、酸化物530b、導電体542a、及び導電体542bと、絶縁体580との間に絶縁体544を配置することが好ましい。また、図17A、図17Bに示すように、導電体560は、絶縁体550の内側に設けられた導電体560aと、導電体560aの内側に埋め込まれるように設けられた導電体560bと、を有することが好ましい。また、図17A、図17Bに示すように、絶縁体580、導電体560、及び絶縁体550の上に絶縁体574が配置されることが好ましい。

30

【0113】

なお、以下において、酸化物530a、酸化物530b、及び酸化物530cをまとめて酸化物530という場合がある。

【0114】

なお、トランジスタ12では、チャネルが形成される領域と、その近傍において、酸化物530a、酸化物530b、及び酸化物530cの3層を積層する構成について示しているが、本発明はこれに限られるものではない。例えば、酸化物530bの単層、酸化物530bと酸化物530aの2層構造、酸化物530bと酸化物530cの2層構造、又は4層以上の積層構造を設ける構成にしてもよい。また、トランジスタ12では、導電体560を2層の積層構造として示しているが、本発明はこれに限られるものではない。例えば、導電体560が単層構造であってもよいし、3層以上の積層構造であってもよい。

50

また、図15、図16、図17A、図17Bに示すトランジスタ12は一例であり、その構造に限定されず、回路構成や駆動方法に応じて適切なトランジスタを用いればよい。

#### 【0115】

ここで、導電体560は、トランジスタ12のゲート電極として機能し、導電体542a及び導電体542bは、それぞれソース電極又はドレイン電極として機能する。上記のように、導電体560は、絶縁体580の開口、及び導電体542aと導電体542bに挟まれた領域に埋め込まれるように形成される。導電体560、導電体542a、及び導電体542bの配置は、絶縁体580の開口に対して自己整合的に選択される。つまり、トランジスタ12において、ゲート電極を、ソース電極とドレイン電極の間に自己整合的に配置させることができる。よって、導電体560を位置合わせのマージンを設けることなく形成することができるので、トランジスタ12の占有面積の縮小を図ることができる。これにより、半導体装置の微細化、高集積化を図ることができる。

#### 【0116】

さらに、導電体560が、導電体542aと導電体542bの間の領域に自己整合的に形成されるので、導電体560は、導電体542a又は導電体542bと重畠する領域を有さない。これにより、導電体560と、導電体542a及び導電体542bと、の間に形成される寄生容量を低減することができる。よって、トランジスタ12のスイッチング速度が向上し、高い周波数特性を有することができる。

#### 【0117】

導電体560は、第1のゲート（トップゲートともいう）電極として機能する場合がある。また、導電体503は、第2のゲート（ボトムゲートともいう）電極として機能する場合がある。その場合、導電体503に印加する電位を、導電体560に印加する電位と連動させず、独立して変化させることで、トランジスタ12のしきい値電圧を制御することができる。特に、導電体503に負の電位を印加することにより、トランジスタ12のしきい値電圧を0Vより大きくし、オフ電流を低減することができる。したがって、導電体503に負の電位を印加したほうが、印加しない場合よりも、導電体560に印加する電位が0Vのときのドレイン電流を小さくすることができる。

#### 【0118】

導電体503は、酸化物530、及び導電体560と重なる領域を有するように配置する。これにより、導電体560、及び導電体503に電位を印加した場合、導電体560から生じる電界と、導電体503から生じる電界と、がつながり、酸化物530に形成されるチャネル形成領域を覆うことができる。本明細書等において、第1のゲート電極、及び第2のゲート電極の電界によってチャネル形成領域を電気的に取り囲むトランジスタの構造を、surrounded channel (s-channel) 構造という。

#### 【0119】

また、導電体503は、導電体518と同様の構成であり、絶縁体514及び絶縁体516の開口の内壁に接して導電体503aが形成され、さらに内側に導電体503bが形成されている。なお、トランジスタ12では、導電体503a及び導電体503bを積層する構成について示しているが、本発明はこれに限られるものではない。例えば、導電体503は、単層、又は3層以上の積層構造として設ける構成にしてもよい。

#### 【0120】

ここで、導電体503aは、水素原子、水素分子、水分子、銅原子等の不純物の拡散を抑制する機能を有する（上記不純物が透過しにくい。）導電性材料を用いることが好ましい。又は、酸素（例えば、酸素原子、酸素分子等の少なくと一）の拡散を抑制する機能を有する（上記酸素が透過しにくい。）導電性材料を用いることが好ましい。なお、本明細書等において、不純物、又は酸素の拡散を抑制する機能とは、上記不純物、又は上記酸素のいずれか一、又は全ての拡散を抑制する機能とする。

#### 【0121】

例えば、導電体503aが酸素の拡散を抑制する機能を有することにより、導電体503bが酸化して導電率が低下することを抑制することができる。

10

20

30

40

50

## 【0122】

また、導電体503が配線の機能を兼ねる場合、導電体503bは、タングステン、銅、又はアルミニウムを主成分とする、導電性が高い導電性材料を用いることが好ましい。その場合、導電体503aは、必ずしも設けなくともよい。なお、導電体503bを単層で図示したが、積層構造としてもよく、例えば、チタン又は窒化チタンと上記導電性材料との積層としてもよい。

## 【0123】

絶縁体520、絶縁体522、及び絶縁体524は、第2のゲート絶縁膜としての機能を有する。

## 【0124】

ここで、酸化物530と接する絶縁体524は、化学量論的組成を満たす酸素よりも多くの酸素を含む絶縁体を用いることが好ましい。つまり、絶縁体524には、過剰酸素領域が形成されていることが好ましい。このような過剰酸素を含む絶縁体を酸化物530に接して設けることにより、酸化物530中の酸素欠損を低減し、トランジスタ12の信頼性を向上させることができる。

10

## 【0125】

過剰酸素領域を有する絶縁体として、具体的には、加熱により一部の酸素が脱離する酸化物材料を用いることが好ましい。加熱により酸素を脱離する酸化物とは、TDS (Thermal Desorption Spectroscopy) 分析にて、酸素原子に換算しての酸素の脱離量が  $1.0 \times 10^{18}$  atoms/cm<sup>3</sup> 以上、好ましくは  $1.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以上、さらに好ましくは  $2.0 \times 10^{19}$  atoms/cm<sup>3</sup> 以上、又は  $3.0 \times 10^{20}$  atoms/cm<sup>3</sup> 以上である酸化物膜である。なお、上記TDS分析時における膜の表面温度としては 100 以上 700 以下、又は 100 以上 400 以下の範囲が好ましい。

20

## 【0126】

また、上記過剰酸素領域を有する絶縁体と、酸化物530と、を接して加熱処理、マイクロ波処理、又はRF処理のいずれか一又は複数の処理を行ってもよい。当該処理を行うことで、酸化物530中の水、又は水素を除去することができる。例えば、酸化物530において、VOHの結合が切断される反応が起きる、別言すると「VOH → V + OH」という反応が起きることにより、脱水素化することができる。このとき発生した水素の一部は、酸素と結合してH<sub>2</sub>Oとして、酸化物530、又は酸化物530近傍の絶縁体から除去される場合がある。また、水素の一部は、導電体542に拡散又は捕獲(ゲッタリングともいう)される場合がある。

30

## 【0127】

また、上記マイクロ波処理は、例えば、高密度プラズマを発生させる電源を有する装置、又は、基板側にRFを印加する電源を有する装置を用いると好適である。例えば、酸素を含むガスを用い、且つ高密度プラズマを用いることにより、高密度の酸素ラジカルを生成することができる。また、基板側にRFを印加することで、高密度プラズマによって生成された酸素ラジカルを、効率よく酸化物530、又は酸化物530近傍の絶縁体中に導入することができる。また、上記マイクロ波処理は、圧力を 133 Pa 以上、好ましくは 200 Pa 以上、さらに好ましくは 400 Pa 以上とすればよい。また、マイクロ波処理を行う装置内に導入するガスとしては、例えば酸素及びアルゴンを用い、酸素流量比(O<sub>2</sub> / (O<sub>2</sub> + Ar)) は 50% 以下、好ましくは 10% 以上 30% 以下とするといい。

40

## 【0128】

また、トランジスタ12の作製工程において、酸化物530の表面が露出した状態で加熱処理を行うと好適である。当該加熱処理は、例えば、100 以上 450 以下、より好ましくは 350 以上 400 以下で行えばよい。なお、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気、又は酸化性ガスを 10 ppm 以上、1% 以上、もしくは 10% 以上含む雰囲気で行う。例えば、加熱処理は酸素雰囲気で行うことが好ましい。これにより、酸化物530に酸素を供給して、酸素欠損(VO)の低減を図ることができる。また

50

、加熱処理は減圧状態で行ってもよい。又は、加熱処理は、窒素ガスもしくは不活性ガスの雰囲気で加熱処理した後に、脱離した酸素を補うために、酸化性ガスを10 ppm以上、1%以上、又は10%以上含む雰囲気で行ってもよい。又は、酸化性ガスを10 ppm以上、1%以上、又は10%以上含む雰囲気で加熱処理した後に、連続して窒素ガスもしくは不活性ガスの雰囲気で加熱処理を行ってもよい。

#### 【0129】

なお、酸化物530に加酸素化処理を行うことで、酸化物530中の酸素欠損を、供給された酸素により修復させる、別言すると「 $V_0 + O \rightarrow V_2O_5$ 」という反応を促進させることができる。

さらに、酸化物530中に残存した水素と、酸化物530に供給された酸素と、が反応することで、当該水素を $H_2O$ として除去する（脱水化する）ことができる。これにより、酸化物530中に残存していた水素が酸素欠損に再結合して $V_0H$ が形成されるのを抑制することができる。

10

#### 【0130】

また、絶縁体524が過剰酸素領域を有する場合、絶縁体522は、酸素（例えば、酸素原子、酸素分子等）の拡散を抑制する機能を有する（上記酸素が透過しにくい）ことが好ましい。

#### 【0131】

絶縁体522が、酸素や不純物の拡散を抑制する機能を有することで、酸化物530が有する酸素が絶縁体520側へ拡散することなく、好ましい。また、導電体503が、絶縁体524や酸化物530が有する酸素と反応することを抑制することができる。

20

#### 【0132】

絶縁体522は、例えば、酸化アルミニウム、酸化ハフニウム、アルミニウム及びハフニウムを含む酸化物（ハフニウムアルミネート）、酸化タンタル、酸化ジルコニウム、チタン酸ジルコン酸鉛（PZT）、チタン酸ストロンチウム（SrTiO<sub>3</sub>）、又は（Ba, Sr）TiO<sub>3</sub>（BST）等のいわゆるhigh-k材料を含む絶縁体を単層又は積層で用いることが好ましい。トランジスタの微細化、及び高集積化が進むと、ゲート絶縁膜の薄膜化により、リーク電流等の問題が生じる場合がある。ゲート絶縁膜として機能する絶縁体にhigh-k材料を用いることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位の低減が可能となる。

30

#### 【0133】

特に、不純物、及び酸素等の拡散を抑制する機能を有する（上記酸素が透過しにくい）絶縁性材料であるアルミニウム、ハフニウムの一方又は双方の酸化物を含む絶縁体を用いるとよい。アルミニウム、ハフニウムの一方又は双方の酸化物を含む絶縁体として、酸化アルミニウム、酸化ハフニウム、又はアルミニウム及びハフニウムを含む酸化物（ハフニウムアルミネート）等を用いることが好ましい。このような材料を用いて絶縁体522を形成した場合、絶縁体522は、酸化物530からの酸素の放出や、トランジスタ12の周辺部から酸化物530への水素等の不純物の混入を抑制する層として機能する。

#### 【0134】

又は、これらの絶縁体に、例えば、酸化アルミニウム、酸化ビスマス、酸化ゲルマニウム、酸化ニオブ、酸化シリコン、酸化チタン、酸化タンゲステン、酸化イットリウム、酸化ジルコニウムを添加してもよい。又はこれらの絶縁体を窒化処理してもよい。上記の絶縁体に酸化シリコン、酸化窒化シリコン、又は窒化シリコンを積層して用いてもよい。

40

#### 【0135】

また、絶縁体520は、熱的に安定していることが好ましい。例えば、酸化シリコン及び酸化窒化シリコンは、熱的に安定であるため好適である。また、high-k材料の絶縁体を酸化シリコン、又は酸化窒化シリコンと組み合わせることで、熱的に安定かつ比誘電率の高い積層構造の絶縁体520を得ることができる。

#### 【0136】

なお、図17A、図17Bのトランジスタ12では、3層の積層構造からなる第2のゲ

50

ート絶縁膜として、絶縁体 520、絶縁体 522、及び絶縁体 524が図示されているが、第2のゲート絶縁膜は、単層、2層、又は4層以上の積層構造を有していてもよい。その場合、同じ材料からなる積層構造に限定されず、異なる材料からなる積層構造でもよい。

#### 【0137】

トランジスタ12は、チャネル形成領域を含む酸化物530に、酸化物半導体として機能する金属酸化物を用いることが好ましい。例えば、酸化物530として、In-M-Zn酸化物（元素Mは、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タンゲステン、又はマグネシウム等から選ばれた一種、又は複数種）等の金属酸化物を用いるとよい。特に、酸化物530として適用できるIn-M-Zn酸化物は、CAAC-OS(C-Aligned Crystal Oxide Semiconductor)、CAC-OS(Cloud-Aligned Composite Oxide Semiconductor)であることが好ましい。また、酸化物530として、In-Ga酸化物、In-Zn酸化物を用いてもよい。CAAC-OS及びCAC-OSについては後述する。なお、トランジスタ12のオン電流を高めたい場合においては、酸化物530にIn-Zn酸化物を用いると好適である。酸化物530にIn-Zn酸化物を用いる場合、例えば、酸化物530aにIn-Zn酸化物を用い、酸化物530bおよび酸化物530cにIn-M-Zn酸化物を用い、酸化物530bおよび酸化物530cのいずれか一方にIn-Zn酸化物を用いる積層構造などが挙げられる。

#### 【0138】

また、トランジスタ12には、キャリア濃度の低い金属酸化物を用いることが好ましい。金属酸化物のキャリア濃度を低くする場合においては、金属酸化物中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性又は実質的に高純度真性という。なお、金属酸化物中の不純物としては、例えば、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

#### 【0139】

特に、金属酸化物に含まれる水素は、金属原子と結合する酸素と反応して水になるため、金属酸化物中に酸素欠損を形成する場合がある。また、酸化物530中の酸素欠損に水素が入った場合、酸素欠損と水素とが結合しVOHを形成する場合がある。VOHはドナーとして機能し、キャリアである電子が生成されることがある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成する場合がある。したがって、水素が多く含まれている金属酸化物を用いたトランジスタは、ノーマリーオン特性となりやすい。また、金属酸化物中の水素は、熱、電界等のストレスによって動きやすいため、金属酸化物に多くの水素が含まれると、トランジスタの信頼性が悪化する懼れもある。本発明の一態様においては、酸化物530中のVOHをできる限り低減し、高純度真性又は実質的に高純度真性にすることが好ましい。このように、VOHが十分低減された金属酸化物を得るには、金属酸化物中の水分、水素等の不純物を除去すること（脱水、脱水素化処理と記載する場合がある。）と、金属酸化物に酸素を供給して酸素欠損を補填すること（加酸素化処理と記載する場合がある。）が重要である。VOH等の不純物が十分に低減された金属酸化物をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

#### 【0140】

酸素欠損に水素が入った欠陥は、金属酸化物のドナーとして機能しうる。しかしながら、当該欠陥を定量的に評価することは困難である。そこで、金属酸化物においては、ドナー濃度ではなく、キャリア濃度で評価される場合がある。よって、本明細書等では、金属酸化物のパラメータとして、ドナー濃度ではなく、電界が印加されない状態を想定したキャリア濃度を用いる場合がある。つまり、本明細書等に記載の「キャリア濃度」は、「ド

10

20

30

40

50

ナー濃度」と言い換えることができる場合がある。

【0141】

よって、金属酸化物を酸化物530に用いる場合、金属酸化物中の水素はできる限り低減されていることが好ましい。具体的には、金属酸化物において、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られる水素濃度を、 $1 \times 10^{20}$  atoms/cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms/cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms/cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{18}$  atoms/cm<sup>3</sup>未満とする。水素等の不純物が十分に低減された金属酸化物をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

10

【0142】

また、酸化物530に金属酸化物を用いる場合、チャネル形成領域の金属酸化物のキャリア濃度は、 $1 \times 10^{18}$  cm<sup>-3</sup>以下であることが好ましく、 $1 \times 10^{17}$  cm<sup>-3</sup>未満であることがより好ましく、 $1 \times 10^{16}$  cm<sup>-3</sup>未満であることがさらに好ましく、 $1 \times 10^{13}$  cm<sup>-3</sup>未満であることがさらに好ましく、 $1 \times 10^{12}$  cm<sup>-3</sup>未満であることがさらに好ましい。なお、チャネル形成領域の金属酸化物のキャリア濃度の下限値については、特に限定は無いが、例えば、 $1 \times 10^{-9}$  cm<sup>-3</sup>とすることができる。

【0143】

また、酸化物530に金属酸化物を用いる場合、導電体542(導電体542a、及び導電体542b)と酸化物530とが接することで、酸化物530中の酸素が導電体542へ拡散し、導電体542が酸化する場合がある。導電体542が酸化することで、導電体542の導電率が低下する蓋然性が高い。なお、酸化物530中の酸素が導電体542へ拡散することを、導電体542が酸化物530中の酸素を吸収する、と言い換えることができる。

20

【0144】

また、酸化物530中の酸素が導電体542(導電体542a、及び導電体542b)へ拡散することで、導電体542aと酸化物530bとの間、及び導電体542bと酸化物530bとの間に異層が形成される場合がある。当該異層は、導電体542よりも酸素を多く含むため、当該異層は絶縁性を有すると推定される。このとき、導電体542と、当該異層と、酸化物530bとの3層構造は、金属-絶縁体-半導体からなる3層構造とみなすことができ、MIS(Metal-Insulator-Semiconductor)構造という、又はMIS構造を主としたダイオード接合構造という場合がある。

30

【0145】

なお、上記異層は、導電体542と酸化物530bとの間に形成されることに限られない。例えば、異層が、導電体542と酸化物530cとの間に形成される場合がある。又は、導電体542と酸化物530bとの間、及び導電体542と酸化物530cとの間に形成される場合がある。

【0146】

また、酸化物530においてチャネル形成領域として機能する金属酸化物は、バンドギャップが2eV以上、好ましくは2.5eV以上のものを用いることが好ましい。このように、バンドギャップの大きい金属酸化物を用いることで、トランジスタのオフ電流を低減することができる。

40

【0147】

酸化物530は、酸化物530b下に酸化物530aを有することで、酸化物530aよりも下方に形成された構造物から、酸化物530bへ不純物が拡散することを抑制することができる。また、酸化物530b上に酸化物530cを有することで、酸化物530cよりも上方に形成された構造物から、酸化物530bへ不純物が拡散することを抑制することができる。

【0148】

なお、酸化物530は、各金属原子の原子数比が異なる複数の酸化物層の積層構造を有

50

することが好ましい。具体的には、酸化物 530a に用いる金属酸化物において、構成元素中の元素 M の原子数比が、酸化物 530b に用いる金属酸化物における、構成元素中の元素 M の原子数比より大きいことが好ましい。また、酸化物 530a に用いる金属酸化物において、In に対する元素 M の原子数比が、酸化物 530b に用いる金属酸化物における、In に対する元素 M の原子数比より大きいことが好ましい。また、酸化物 530b に用いる金属酸化物において、元素 M に対する In の原子数比が、酸化物 530a に用いる金属酸化物における、元素 M に対する In の原子数比より大きいことが好ましい。また、酸化物 530c は、酸化物 530a 又は酸化物 530b に用いることができる金属酸化物を用いることができる。

## 【0149】

10

具体的には、酸化物 530a として、In : Ga : Zn = 1 : 3 : 4 [原子数比]、または 1 : 1 : 0.5 [原子数比] の金属酸化物を用いればよい。また、酸化物 530b として、In : Ga : Zn = 4 : 2 : 3 [原子数比]、または 1 : 1 : 1 [原子数比] の金属酸化物を用いればよい。また、酸化物 530c として、In : Ga : Zn = 1 : 3 : 4 [原子数比]、Ga : Zn = 2 : 1 [原子数比]、または Ga : Zn = 2 : 5 [原子数比] の金属酸化物を用いればよい。また、酸化物 530c を積層構造とする場合の具体例としては、In : Ga : Zn = 4 : 2 : 3 [原子数比] と、In : Ga : Zn = 1 : 3 : 4 [原子数比] との積層構造、Ga : Zn = 2 : 1 [原子数比] と、In : Ga : Zn = 4 : 2 : 3 [原子数比] との積層構造、Ga : Zn = 2 : 5 [原子数比] と、In : Ga : Zn = 4 : 2 : 3 [原子数比] との積層構造、酸化ガリウムと、In : Ga : Zn = 4 : 2 : 3 [原子数比] との積層構造などが挙げられる。

20

## 【0150】

また、酸化物 530a 及び酸化物 530c の伝導帯下端のエネルギーが、酸化物 530b の伝導帯下端のエネルギーより高くなることが好ましい。また、言い換えると、酸化物 530a 及び酸化物 530c の電子親和力が、酸化物 530b の電子親和力より小さいことが好ましい。

## 【0151】

30

ここで、酸化物 530a、酸化物 530b、及び酸化物 530c の接合部において、伝導帯下端のエネルギー準位はなだらかに変化する。換言すると、酸化物 530a、酸化物 530b、及び酸化物 530c の接合部における伝導帯下端のエネルギー準位は、連続的に変化又は連続接合するともいうことができる。このようにするために、酸化物 530a と酸化物 530b との界面、及び酸化物 530b と酸化物 530c との界面において形成される混合層の欠陥準位密度を低くするとよい。

## 【0152】

具体的には、酸化物 530a と酸化物 530b、及び酸化物 530b と酸化物 530c が、酸素以外に共通の元素を有する（主成分とする）ことで、欠陥準位密度が低い混合層を形成することができる。例えば、酸化物 530b が In - Ga - Zn 酸化物の場合、酸化物 530a 及び酸化物 530c として、In - Ga - Zn 酸化物、Ga - Zn 酸化物、酸化ガリウム等を用いるとよい。

## 【0153】

40

このとき、キャリアの主たる経路は酸化物 530b となる。酸化物 530a、及び酸化物 530c を上述の構成とすることで、酸化物 530a と酸化物 530b との界面、及び酸化物 530b と酸化物 530c との界面における欠陥準位密度を低くすることができる。そのため、界面散乱によるキャリア伝導への影響が小さくなり、トランジスタ 12 は高いイオン電流を得られる。

## 【0154】

なお、酸化物 530 に用いることができる半導体材料は、上述の金属酸化物に限られない。酸化物 530 として、バンドギャップを有する半導体材料（ゼロギャップ半導体ではない半導体材料）を用いてもよい。例えば、シリコンなどの単体元素の半導体、ヒ化ガリウムなどの化合物半導体、半導体として機能する層状物質（原子層物質、2 次元材料など

50

ともいう。)などを半導体材料に用いることが好ましい。特に、半導体として機能する層状物質を半導体材料に用いると好適である。

【0155】

ここで、本明細書等において、層状物質とは、層状の結晶構造を有する材料群の総称である。層状の結晶構造は、共有結合やイオン結合によって形成される層が、ファンデルワールス力のような、共有結合やイオン結合よりも弱い結合を介して積層している構造である。層状物質は、単位層内における電気伝導性が高く、つまり、2次元電気伝導性が高い。半導体として機能し、かつ、2次元電気伝導性の高い材料をチャネル形成領域に用いることで、オン電流の大きいトランジスタを提供することができる。

【0156】

層状物質として、グラフェン、シリセン、カルコゲン化物などがある。カルコゲン化物は、カルコゲンを含む化合物である。また、カルコゲンは、第16族に属する元素の総称であり、酸素、硫黄、セレン、テルル、ポロニウム、リバモリウムが含まれる。また、カルコゲン化物として、遷移金属カルコゲナイト、13族カルコゲナイトなどが挙げられる。

【0157】

酸化物530として、例えば、半導体として機能する遷移金属カルコゲナイトを用いることが好ましい。酸化物530として適用可能な遷移金属カルコゲナイトとして、具体的には、硫化モリブデン(代表的にはMoS<sub>2</sub>)、セレン化モリブデン(代表的にはMoSe<sub>2</sub>)、モリブデンテルル(代表的にはMoTe<sub>2</sub>)、硫化タンクス滕(代表的にはWS<sub>2</sub>)、セレン化タンクス滕(代表的にはWSe<sub>2</sub>)、タンクス滕テルル(代表的にはWT<sub>2</sub>)、硫化ハフニウム(代表的にはHfS<sub>2</sub>)、セレン化ハフニウム(代表的にはHfSe<sub>2</sub>)、硫化ジルコニウム(代表的にはZrS<sub>2</sub>)、セレン化ジルコニウム(代表的にはZrSe<sub>2</sub>)などが挙げられる。

【0158】

酸化物530b上には、ソース電極、及びドレイン電極として機能する導電体542a、及び導電体542bが設けられる。導電体542a、及び導電体542bとしては、アルミニウム、クロム、銅、銀、金、白金、タンタル、ニッケル、チタン、モリブデン、タンクス滕、ハフニウム、バナジウム、ニオブ、マンガン、マグネシウム、ジルコニウム、ベリリウム、インジウム、ルテニウム、イリジウム、ストロンチウム、ランタンから選ばれた金属元素、又は上述した金属元素を成分とする合金か、上述した金属元素を組み合わせた合金等を用いることが好ましい。例えば、窒化タンタル、窒化チタン、タンクス滕、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物等を用いることが好ましい。また、窒化タンタル、窒化チタン、チタンとアルミニウムを含む窒化物、タンタルとアルミニウムを含む窒化物、酸化ルテニウム、窒化ルテニウム、ストロンチウムとルテニウムを含む酸化物、ランタンとニッケルを含む酸化物は、酸化しにくい導電性材料、又は酸素を吸収しても導電性を維持する材料であるため好ましい。更に、窒化タンタル等の金属窒化物膜は、水素又は酸素に対するバリア性があるため好ましい。

【0159】

また、図17では、導電体542a、及び導電体542bを単層構造として示したが、2層以上の積層構造としてもよい。例えば、窒化タンタル膜とタンクス滕膜を積層するといよい。また、チタン膜とアルミニウム膜を積層してもよい。また、タンクス滕膜上にアルミニウム膜を積層する二層構造、銅-マグネシウム-アルミニウム合金膜上に銅膜を積層する二層構造、チタン膜上に銅膜を積層する二層構造、タンクス滕膜上に銅膜を積層する二層構造としてもよい。

【0160】

また、チタン膜又は窒化チタン膜と、そのチタン膜又は窒化チタン膜上に重ねてアルミニウム膜又は銅膜を積層し、さらにその上にチタン膜又は窒化チタン膜を形成する三層構造、モリブデン膜又は窒化モリブデン膜と、そのモリブデン膜又は窒化モリブデン膜上に

10

20

30

40

50

重ねてアルミニウム膜又は銅膜を積層し、さらにその上にモリブデン膜又は窒化モリブデン膜を形成する三層構造等がある。なお、酸化インジウム、酸化錫又は酸化亜鉛を含む透明導電材料を用いてもよい。

【0161】

また、図17Aに示すように、酸化物530の、導電体542a(導電体542b)との界面とその近傍には、低抵抗領域として領域543a、及び領域543bが形成される場合がある。このとき、領域543aはソース領域又はドレイン領域の一方として機能し、領域543bはソース領域又はドレイン領域の他方として機能する。また、領域543aと領域543bに挟まれる領域にチャネル形成領域が形成される。

【0162】

酸化物530と接するように上記導電体542a(導電体542b)を設けることで、領域543a(領域543b)の酸素濃度が低減する場合がある。また、領域543a(領域543b)に導電体542a(導電体542b)に含まれる金属と、酸化物530の成分とを含む金属化合物層が形成される場合がある。このような場合、領域543a(領域543b)のキャリア濃度が増加し、領域543a(領域543b)は、低抵抗領域となる。

10

【0163】

絶縁体544は、導電体542a、及び導電体542bを覆うように設けられ、導電体542a、及び導電体542bの酸化を抑制する。このとき、絶縁体544は、酸化物530の側面を覆い、絶縁体524と接するように設けられてもよい。

20

【0164】

絶縁体544として、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タンクスチン、チタン、タンタル、ニッケル、ゲルマニウム、ネオジム、ランタン、マグネシウム等から選ばれた一種、又は二種以上が含まれた金属酸化物を用いることができる。また、絶縁体544として、窒化酸化シリコン又は窒化シリコン等も用いることができる。

【0165】

特に、絶縁体544として、アルミニウム、又はハフニウムの一方又は双方の酸化物を含む絶縁体である、酸化アルミニウム、酸化ハフニウム、又はアルミニウム及びハフニウムを含む酸化物(ハフニウムアルミネート)等を用いることが好ましい。特に、ハフニウムアルミネートは、酸化ハフニウム膜よりも耐熱性が高い。そのため、後の工程での熱処理において、結晶化しにくいため好ましい。なお、導電体542a、及び導電体542bが耐酸化性を有する材料、又は酸素を吸収しても著しく導電性が低下しない場合、絶縁体544は必須の構成ではない。求めるトランジスタ特性により適宜設計すればよい。

30

【0166】

絶縁体544を有することで、絶縁体580に含まれる水、及び水素等の不純物が、酸化物530c及び絶縁体550を介して酸化物530bに拡散することを抑制することができる。また、絶縁体580が有する過剰酸素により、導電体560が酸化することを抑制することができる。

【0167】

絶縁体550は、第1のゲート絶縁膜として機能する。絶縁体550は、酸化物530cの内側(上面、及び側面)と接するように配置することが好ましい。絶縁体550は、上述した絶縁体524と同様に、過剰に酸素を含み、かつ加熱により酸素が放出される絶縁体を用いて形成することが好ましい。

40

【0168】

具体的には、過剰酸素を有する酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素、及び窒素を添加した酸化シリコン、空孔を有する酸化シリコンを用いることができる。特に、酸化シリコン、及び酸化窒化シリコンは熱に対し安定であるため好ましい。

【0169】

50

加熱により酸素が放出される絶縁体を、絶縁体 550 として酸化物 530c の上面に接して設けることにより、酸化物 530c を通じて、絶縁体 550 から酸化物 530b のチャネル形成領域に効果的に酸素を供給することができる。また、絶縁体 524 と同様に、絶縁体 550 中の水又は水素等の不純物濃度が低減されていることが好ましい。絶縁体 550 の膜厚は、1 nm 以上 20 nm 以下とすることが好ましい。

#### 【0170】

また、絶縁体 550 が有する過剰酸素を効率的に酸化物 530 へ供給するために、絶縁体 550 と導電体 560 との間に金属酸化物を設けてもよい。当該金属酸化物は、絶縁体 550 から導電体 560 への酸素拡散を抑制する機能を有することが好ましい。酸素の拡散を抑制する機能を有する金属酸化物を設けることで、絶縁体 550 から導電体 560 への過剰酸素の拡散が抑制される。つまり、酸化物 530 へ供給する過剰酸素量の減少を抑制することができる。また、過剰酸素による導電体 560 の酸化を抑制することができる。当該金属酸化物としては、絶縁体 544 に用いることができる材料を用いればよい。

10

#### 【0171】

なお、絶縁体 550 は、第 2 のゲート絶縁膜と同様に、積層構造としてもよい。トランジスタの微細化、及び高集積化が進むと、ゲート絶縁膜の薄膜化により、リーク電流等の問題が生じる場合がある。このため、ゲート絶縁膜として機能する絶縁体を、high-k 材料と、熱的に安定している材料との積層構造とすることで、物理膜厚を保ちながら、トランジスタ動作時のゲート電位を低減することが可能となる。また、熱的に安定かつ比誘電率の高い積層構造とすることができます。

20

#### 【0172】

第 1 のゲート電極として機能する導電体 560 は、図 17A、図 17B では 2 層構造として示しているが、単層構造でもよいし、3 層以上の積層構造であってもよい。

#### 【0173】

導電体 560a は、水素原子、水素分子、水分子、窒素原子、窒素分子、酸化窒素分子 (N<sub>2</sub>O、NO、NO<sub>2</sub> 等)、銅原子等の不純物の拡散を抑制する機能を有する導電性材料を用いることが好ましい。又は、酸素 (例えば、酸素原子、酸素分子等の少なくとも一) の拡散を抑制する機能を有する導電性材料を用いることが好ましい。導電体 560a が酸素の拡散を抑制する機能を有することで、絶縁体 550 に含まれる酸素により導電体 560b が酸化して導電率が低下することを抑制することができる。酸素の拡散を抑制する機能を有する導電性材料としては、例えば、タンタル、窒化タンタル、ルテニウム、又は酸化ルテニウム等を用いることが好ましい。また、導電体 560a として、酸化物 530 に適用できる酸化物半導体を用いることができる。その場合、導電体 560b をスパッタリング法で成膜することで、導電体 560a の電気抵抗値を低下させて導電体にことができる。これを O<sub>C</sub> (Oxide Conductor) 電極といふことができる。

30

#### 【0174】

また、導電体 560b は、タンゲステン、銅、又はアルミニウムを主成分とする導電性材料を用いることが好ましい。また、導電体 560b は、配線としても機能するため、導電性が高い導電体を用いることが好ましい。例えば、タンゲステン、銅、又はアルミニウムを主成分とする導電性材料を用いることができる。また、導電体 560b は積層構造としてもよく、例えば、チタン又は窒化チタンと上記導電性材料との積層構造としてもよい。

40

#### 【0175】

絶縁体 580 は、絶縁体 544 を介して、導電体 542a、及び導電体 542b 上に設けられる。絶縁体 580 は、過剰酸素領域を有することが好ましい。例えば、絶縁体 580 として、酸化シリコン、酸化窒化シリコン、窒化酸化シリコン、窒化シリコン、フッ素を添加した酸化シリコン、炭素を添加した酸化シリコン、炭素、及び窒素を添加した酸化シリコン、空孔を有する酸化シリコン、又は樹脂等を有することが好ましい。特に、酸化シリコン、及び酸化窒化シリコンは、熱的に安定であるため好ましい。特に、酸化シリコン、及び空孔を有する酸化シリコンは、後の工程で容易に過剰酸素領域を形成することができるため好ましい。

50

## 【0176】

絶縁体580は、過剰酸素領域を有することが好ましい。加熱により酸素が放出される絶縁体580を、酸化物530cと接する領域を有するように設けることで、絶縁体580中の酸素を、酸化物530cを通じて、酸化物530a及び酸化物530bへと効率良く供給することができる。なお、絶縁体580中の水又は水素等の不純物濃度が低減されていることが好ましい。

## 【0177】

絶縁体580の開口は、導電体542aと導電体542bの間の領域に重畳して形成される。これにより、導電体560は、絶縁体580の開口、及び導電体542aと導電体542bに挟まれた領域に埋め込まれるように形成される。

10

## 【0178】

半導体装置を微細化するに当たり、ゲート長を短くすることが求められるが、導電体560の導電性が下がらないようにする必要がある。そのために導電体560の膜厚を大きくすると、導電体560はアスペクト比が高い形状となりうる。本実施の形態では、導電体560を絶縁体580の開口に埋め込むように設けるため、導電体560をアスペクト比の高い形状にしても、工程中に導電体560を倒壊させることなく導電体560を形成することができる。

## 【0179】

絶縁体574は、絶縁体580の上面、導電体560の上面、及び絶縁体550の上面に接して設けられることが好ましい。絶縁体574をスパッタリング法で成膜することで、絶縁体550、及び絶縁体580へ過剰酸素領域を設けることができる。これにより、当該過剰酸素領域から、酸化物530中に酸素を供給することができる。

20

## 【0180】

例えば、絶縁体574として、ハフニウム、アルミニウム、ガリウム、イットリウム、ジルコニウム、タンクステン、チタン、タンタル、ニッケル、ゲルマニウム、又はマグネシウム等から選ばれた一種、又は二種以上が含まれた金属酸化物を用いることができる。

## 【0181】

特に、酸化アルミニウムはバリア性が高く、0.5nm以上3.0nm以下の薄膜であっても、水素、及び窒素の拡散を抑制することができる。したがって、スパッタリング法で成膜した酸化アルミニウムは、酸素供給源であるとともに、水素等の不純物のバリア膜としての機能も有することができる。

30

## 【0182】

また、絶縁体574の上に、層間膜として機能する絶縁体581を設けることが好ましい。絶縁体581は、絶縁体524等と同様に、膜中の水又は水素等の不純物濃度が低減されていることが好ましい。

## 【0183】

また、絶縁体581、絶縁体574、絶縁体580、及び絶縁体544に形成された開口に、導電体540a、及び導電体540bを配置する。導電体540a及び導電体540bは、導電体560を挟んで対向して設ける。導電体540a及び導電体540bは、後述する導電体546、及び導電体548と同様の構成である。

40

## 【0184】

絶縁体581上には、絶縁体582が設けられている。絶縁体582は、酸素や水素に対してバリア性のある物質を用いることが好ましい。したがって、絶縁体582には、絶縁体514と同様の材料を用いることができる。例えば、絶縁体582には、酸化アルミニウム、酸化ハフニウム、酸化タンタル等の金属酸化物を用いることが好ましい。

## 【0185】

特に、酸化アルミニウムは、酸素、及びトランジスタの電気特性の変動要因となる水素、水分等の不純物、の両方に対して膜を透過させない遮断効果が高い。したがって、酸化アルミニウムは、トランジスタの作製工程中及び作製後において、水素、水分等の不純物のトランジスタ12への混入を防止することができる。また、トランジスタ12を構成す

50

る酸化物からの酸素の放出を抑制することができる。そのため、トランジスタ12に対する保護膜として用いることに適している。

【0186】

また、絶縁体582上には、絶縁体586が設けられている。絶縁体586は、絶縁体320と同様の材料を用いることができる。また、これらの絶縁体に、比較的誘電率が低い材料を適用することで、配線間に生じる寄生容量を低減することができる。例えば、絶縁体586として、酸化シリコン膜や酸化窒化シリコン膜等を用いることができる。

【0187】

また、絶縁体520、絶縁体522、絶縁体524、絶縁体544、絶縁体580、絶縁体574、絶縁体581、絶縁体582、及び絶縁体586には、導電体546、及び導電体548等が埋め込まれている。

10

【0188】

導電体546、及び導電体548は、キャパシタ14、トランジスタ12、又はトランジスタ13と接続するプラグ、又は配線としての機能を有する。導電体546、及び導電体548は、導電体328、又は導電体330と同様の材料を用いて設けることができる。

【0189】

なお、トランジスタ12の形成後、トランジスタ12を囲むように開口を形成し、当該開口を覆うように、水素、又は水に対するバリア性が高い絶縁体を形成してもよい。上述のバリア性の高い絶縁体でトランジスタ12を包み込むことで、外部から水分、及び水素が侵入することを防止することができる。又は、複数のトランジスタ12をまとめて、水素、又は水に対するバリア性が高い絶縁体で包み込んでもよい。なお、トランジスタ12を囲むように開口を形成する場合、例えば、絶縁体514又は絶縁体522に達する開口を形成し、絶縁体514又は絶縁体522に接するように上述のバリア性の高い絶縁体を形成すると、トランジスタ12の作製工程の一部を兼ねられるため好適である。なお、水素、又は水に対するバリア性が高い絶縁体としては、例えば、絶縁体522と同様の材料を用いればよい。

20

【0190】

続いて、トランジスタ12の上方には、キャパシタ14が設けられている。キャパシタ14は、導電体610、導電体620、及び絶縁体630を有する。

30

【0191】

また、導電体546、及び導電体548上に、導電体612を設けてよい。導電体612は、トランジスタ12と接続するプラグ、又は配線としての機能を有する。導電体610は、キャパシタ14の電極としての機能を有する。なお、導電体612、及び導電体610は、同時に形成することができる。

【0192】

導電体612、及び導電体610には、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウムから選ばれた元素を含む金属膜、又は上述した元素を成分とする金属窒化物膜（窒化タンタル膜、窒化チタン膜、窒化モリブデン膜、窒化タングステン膜）等を用いることができる。又は、インジウム錫酸化物、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物等の導電性材料を適用することもできる。

40

【0193】

図15では、導電体612、及び導電体610は単層構造を示したが、当該構成に限定されず、2層以上の積層構造でもよい。例えば、バリア性を有する導電体と導電性が高い導電体との間に、バリア性を有する導電体、及び導電性が高い導電体に対して密着性が高い導電体を形成してもよい。

【0194】

絶縁体630を介して導電体610と重畳するように、導電体620を設ける。なお、

50

導電体 620 は、金属材料、合金材料、又は金属酸化物材料等の導電性材料を用いることができる。耐熱性と導電性を両立するタンゲステンやモリブデン等の高融点材料を用いることが好ましく、特にタンゲステンを用いることが好ましい。また、導電体等の他の構造と同時に形成する場合は、低抵抗金属材料である Cu (銅) や Al (アルミニウム) 等を用いればよい。

【0195】

導電体 620、及び絶縁体 630 上には、絶縁体 640 が設けられている。絶縁体 640 は、絶縁体 320 と同様の材料を用いて設けることができる。また、絶縁体 640 は、その下方の凹凸形状を被覆する平坦化膜として機能してもよい。

【0196】

本構造を用いることで、酸化物半導体を有するトランジスタを用いた半導体装置において、微細化又は高集積化を図ることができる。

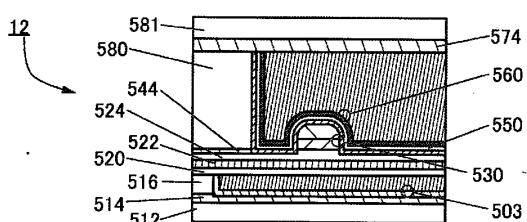

【0197】

図 18A、図 18B は、図 17A、図 17B に示すトランジスタ 12 の変形例である。図 17A はトランジスタ 12 のチャネル長方向の断面図であり、図 17B はトランジスタ 12 のチャネル幅方向の断面図である。なお、図 18A、図 18B に示す構成は、トランジスタ 13 等、本発明の一態様の半導体装置が有する他のトランジスタにも適用することができる。

【0198】

図 18A は、トランジスタ 12 のチャネル長方向の断面図であり、図 18B は、トランジスタ 12 のチャネル幅方向の断面図である。図 18A、図 18B に示すトランジスタ 12 は、絶縁体 402 及び絶縁体 404 を有する点が、図 17A、図 17B に示すトランジスタ 12 と異なる。また、導電体 540a の側面に接して絶縁体 552 が設けられ、導電体 540b の側面に接して絶縁体 552 が設けられる点が、図 17A、図 17B に示すトランジスタ 12 と異なる。さらに、絶縁体 520 を有さない点が、図 17A、図 17B に示すトランジスタ 12 と異なる。

【0199】

図 18A、図 18B に示すトランジスタ 12 は、絶縁体 512 上に絶縁体 402 が設けられる。また、絶縁体 574 上、及び絶縁体 402 上に絶縁体 404 が設けられる。

【0200】

図 18A、図 18B に示すトランジスタ 12 では、絶縁体 514、絶縁体 516、絶縁体 522、絶縁体 524、絶縁体 544、絶縁体 580、及び絶縁体 574 がパターニングされており、絶縁体 404 がこれらを覆う構造になっている。つまり、絶縁体 404 は、絶縁体 574 の上面、絶縁体 574 の側面、絶縁体 580 の側面、絶縁体 544 の側面、絶縁体 524 の側面、絶縁体 522 の側面、絶縁体 516 の側面、絶縁体 514 の側面、絶縁体 402 の上面とそれぞれ接する。これにより、酸化物 530 等は、絶縁体 404 と絶縁体 402 によって外部から隔離される。

【0201】

絶縁体 402 及び絶縁体 404 は、水素 (例えば、水素原子、水素分子などの少なくとも一) 又は水分子の拡散を抑制する機能が高いことが好ましい。例えば、絶縁体 402 及び絶縁体 404 として、水素バリア性が高い材料である、窒化シリコン又は窒化酸化シリコンを用いることが好ましい。これにより、酸化物 530 に水素等が拡散することを抑制することができるので、トランジスタ 12 の特性が低下することを抑制することができる。よって、本発明の一態様の半導体装置の信頼性を高めることができる。

【0202】

絶縁体 552 は、絶縁体 581、絶縁体 404、絶縁体 574、絶縁体 580、及び絶縁体 544 に接して設けられる。絶縁体 552 は、水素又は水分子の拡散を抑制する機能を有することが好ましい。たとえば、絶縁体 552 として、水素バリア性が高い材料である、窒化シリコン、酸化アルミニウム、又は窒化酸化シリコン等の絶縁体を用いることが好ましい。特に、窒化シリコンは水素バリア性が高い材料であるので、絶縁体 552 とし

10

20

30

40

50

て用いると好適である。絶縁体 552 として水素バリア性が高い材料を用いることにより、水又は水素等の不純物が、絶縁体 580 等から導電体 540a 及び導電体 540b を通じて酸化物 530 に拡散することを抑制することができる。また、絶縁体 580 に含まれる酸素が導電体 540a 及び導電体 540b に吸収されることを抑制することができる。以上により、本発明の一態様の半導体装置の信頼性を高めることができる。

【0203】

図 19 は、トランジスタ 12 及びトランジスタ 13 を図 18A、図 18B に示す構成とした場合における、半導体装置の構成例を示す断面図である。導電体 546 の側面に、絶縁体 552 が設けられている。

【0204】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することができる。

10

【0205】

(実施の形態 3)

本実施の形態では、上記の実施の形態で説明した OS トランジスタに用いることができる金属酸化物である CAC - OS、及び CAAC - OS の構成について説明する。なお、本明細書等において、CAC は機能、又は材料の構成の一例を表し、CAAC は結晶構造の一例を表す。

【0206】

<金属酸化物の構成>

CAC - OS 又は CAC - metal oxide とは、材料の一部では導電性の機能と、材料の一部では絶縁性の機能とを有し、材料の全体では半導体としての機能を有する。なお、CAC - OS 又は CAC - metal oxide を、トランジスタの活性層に用いる場合、導電性の機能は、キャリアとなる電子（又はホール）を流す機能であり、絶縁性の機能は、キャリアとなる電子を流さない機能である。導電性の機能と、絶縁性の機能とを、それぞれ相補的に作用させることで、スイッチングさせる機能（On / Off させる機能）を CAC - OS 又は CAC - metal oxide に付与することができる。CAC - OS 又は CAC - metal oxide において、それぞれの機能を分離させることで、双方の機能を最大限に高めることができる。

20

【0207】

また、CAC - OS 又は CAC - metal oxide は、導電性領域、及び絶縁性領域を有する。導電性領域は、上述の導電性の機能を有し、絶縁性領域は、上述の絶縁性の機能を有する。また、材料中において、導電性領域と、絶縁性領域とは、ナノ粒子レベルで分離している場合がある。また、導電性領域と、絶縁性領域とは、それぞれ材料中に偏在する場合がある。また、導電性領域は、周辺がばけてクラウド状に連結して観察される場合がある。

30

【0208】

また、CAC - OS 又は CAC - metal oxide において、導電性領域と、絶縁性領域とは、それぞれ 0.5 nm 以上 10 nm 以下、好ましくは 0.5 nm 以上 3 nm 以下のサイズで材料中に分散している場合がある。

40

【0209】

また、CAC - OS 又は CAC - metal oxide は、異なるバンドギャップを有する成分により構成される。例えば、CAC - OS 又は CAC - metal oxide は、絶縁性領域に起因するワイドギャップを有する成分と、導電性領域に起因するナローギャップを有する成分と、により構成される。当該構成の場合、キャリアを流す際に、ナローギャップを有する成分において、主にキャリアが流れる。また、ナローギャップを有する成分が、ワイドギャップを有する成分に相補的に作用し、ナローギャップを有する成分に連動してワイドギャップを有する成分にもキャリアが流れる。このため、上記 CAC - OS 又は CAC - metal oxide をトランジスタのチャネル形成領域に用いる場合、トランジスタのオン状態において高い電流駆動力、つまり大きなオン電流、及び

50

高い電界効果移動度を得ることができる。

【0210】

すなわち、C A A C - O S 又はC A A C - m e t a l o x i d e は、マトリックス複合材 (m a t r i x c o m p o s i t e) 、又は金属マトリックス複合材 (m e t a l m a t r i x c o m p o s i t e) と呼称することもできる。

【0211】

<金属酸化物の構造>

酸化物半導体は、単結晶酸化物半導体と、それ以外の非単結晶酸化物半導体と、に分けられる。非単結晶酸化物半導体としては、例えば、C A A C - O S 、多結晶酸化物半導体、n c - O S (n a n o c r y s t a l l i n e o x i d e s e m i c o n d u c t o r) 、擬似非晶質酸化物半導体 (a - l i k e O S : a m o r p h o u s - l i k e o x i d e s e m i c o n d u c t o r) 及び非晶質酸化物半導体等がある。

10

【0212】

C A A C - O S は、c 軸配向性を有し、かつa - b 面方向において複数のナノ結晶が連結し、歪みを有した結晶構造となっている。なお、歪みとは、複数のナノ結晶が連結する領域において、格子配列の揃った領域と、別の格子配列の揃った領域と、の間で格子配列の向きが変化している箇所を指す。

【0213】

ナノ結晶は、六角形を基本とするが、正六角形状とは限らず、非正六角形状である場合がある。また、歪みにおいて、五角形、及び七角形等の格子配列を有する場合がある。なお、C A A C - O S において、歪み近傍においても、明確な結晶粒界 (グレインバウンダリーともいう) を確認することはできない。即ち、格子配列の歪みによって、結晶粒界の形成が抑制されていることがわかる。これは、C A A C - O S が、a - b 面方向において酸素原子の配列が稠密でないことや、金属元素が置換することで原子間の結合距離が変化すること等によって、歪みを許容することができるためと考えられる。

20

【0214】

また、C A A C - O S は、インジウム、及び酸素を有する層 (以下、I n 層) と、元素M、亜鉛、及び酸素を有する層 (以下、(M, Z n ) 層) とが積層した、層状の結晶構造 (層状構造ともいう) を有する傾向がある。なお、インジウムと元素Mは、互いに置換可能であり、(M, Z n ) 層の元素Mがインジウムと置換した場合、(I n , M, Z n ) 層と表すこともできる。また、I n 層のインジウムが元素Mと置換した場合、(I n , M) 層と表すこともできる。

30

【0215】

C A A C - O S は結晶性の高い酸化物半導体である。一方、C A A C - O S は、明確な結晶粒界を確認することはできないため、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。また、酸化物半導体の結晶性は不純物の混入や欠陥の生成等によって低下する場合があるため、C A A C - O S は不純物や欠陥 (酸素欠損等) の少ない酸化物半導体ともいえる。したがって、C A A C - O S を有する酸化物半導体は、物理的性質が安定する。そのため、C A A C - O S を有する酸化物半導体は熱に強く、信頼性が高い。また、C A A C - O S は、製造工程における高い温度 (所謂サーマルバジェット) に対しても安定である。したがって、O S トランジスタにC A A C - O S を用いると、製造工程の自由度を広げることが可能となる。

40

【0216】

n c - O S は、微小な領域 (例えば、1 n m 以上 1 0 n m 以下の領域、特に 1 n m 以上 3 n m 以下の領域) において原子配列に周期性を有する。また、n c - O S は、異なるナノ結晶間で結晶方位に規則性が見られない。そのため、膜全体で配向性が見られない。したがって、n c - O S は、分析方法によっては、a - l i k e O S や非晶質酸化物半導体と区別が付かない場合がある。

【0217】

a - l i k e O S は、n c - O S と非晶質酸化物半導体との間の構造を有する酸化物

50

半導体である。a - l i k e O Sは、鬆又は低密度領域を有する。即ち、a - l i k e O Sは、n c - O S及びC A A C - O Sと比べて、結晶性が低い。

【0218】

酸化物半導体は、多様な構造をとり、それぞれが異なる特性を有する。本発明の一態様の酸化物半導体は、非晶質酸化物半導体、多結晶酸化物半導体、a - l i k e O S、n c - O S、C A A C - O Sのうち、二種以上を有していてもよい。

【0219】

<酸化物半導体を有するトランジスタ>

続いて、上記酸化物半導体をトランジスタに用いる場合について説明する。

【0220】

上記酸化物半導体をトランジスタに用いることで、高い電界効果移動度のトランジスタを実現することができる。また、信頼性の高いトランジスタを実現することができる。

10

【0221】

また、トランジスタには、キャリア濃度の低い酸化物半導体を用いることが好ましい。酸化物半導体膜のキャリア濃度を低くする場合においては、酸化物半導体膜中の不純物濃度を低くし、欠陥準位密度を低くすればよい。本明細書等において、不純物濃度が低く、欠陥準位密度の低いことを高純度真性又は実質的に高純度真性と言う。

【0222】

また、高純度真性又は実質的に高純度真性である酸化物半導体膜は、欠陥準位密度が低いため、トラップ準位密度も低くなる場合がある。

20

【0223】

また、酸化物半導体のトラップ準位に捕獲された電荷は、消失するまでに要する時間が長く、あたかも固定電荷のように振る舞うことがある。そのため、トラップ準位密度の高い酸化物半導体にチャネル形成領域が形成されるトランジスタは、電気特性が不安定となる場合がある。

【0224】

したがって、トランジスタの電気特性を安定にするためには、酸化物半導体中の不純物濃度を低減することが有効である。また、酸化物半導体中の不純物濃度を低減するためには、近接する膜中の不純物濃度も低減することが好ましい。不純物としては、水素、窒素、アルカリ金属、アルカリ土類金属、鉄、ニッケル、シリコン等がある。

30

【0225】

<不純物>

ここで、酸化物半導体中における各不純物の影響について説明する。

【0226】

酸化物半導体において、第14族元素の一つであるシリコンや炭素が含まれると、酸化物半導体において欠陥準位が形成される。このため、酸化物半導体におけるシリコンや炭素の濃度と、酸化物半導体との界面近傍のシリコンや炭素の濃度（二次イオン質量分析法（S I M S : S e c o n d a r y I o n M a s s S p e c t r o m e t r y ）により得られる濃度）を、 $2 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{17}$  atoms / cm<sup>3</sup>以下とする。

40

【0227】

また、酸化物半導体にアルカリ金属又はアルカリ土類金属が含まれると、欠陥準位を形成し、キャリアを生成する場合がある。したがって、アルカリ金属又はアルカリ土類金属が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中のアルカリ金属又はアルカリ土類金属の濃度を低減することが好ましい。具体的には、S I M S により得られる酸化物半導体中のアルカリ金属又はアルカリ土類金属の濃度を、 $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、好ましくは $2 \times 10^{16}$  atoms / cm<sup>3</sup>以下にする。

【0228】

また、酸化物半導体において、窒素が含まれると、キャリアである電子が生じ、キャリ

50

ア濃度が増加し、n型化しやすい。この結果、窒素が含まれている酸化物半導体を半導体に用いたトランジスタはノーマリーオン特性となりやすい。したがって、該酸化物半導体において、窒素はできる限り低減されていることが好ましい、例えば、酸化物半導体中の窒素濃度は、S I M Sにおいて、 $5 \times 10^{19}$  atoms / cm<sup>3</sup>未満、好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>以下、より好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>以下、さらに好ましくは $5 \times 10^{17}$  atoms / cm<sup>3</sup>以下とする。

【0229】

また、酸化物半導体に含まれる水素は、金属原子と結合する酸素と反応して水になるため、酸素欠損を形成する場合がある。該酸素欠損に水素が入ることで、キャリアである電子が生成される場合がある。また、水素の一部が金属原子と結合する酸素と結合して、キャリアである電子を生成することがある。したがって、水素が含まれている酸化物半導体を用いたトランジスタはノーマリーオン特性となりやすい。このため、酸化物半導体中の水素はできる限り低減されていることが好ましい。具体的には、酸化物半導体において、S I M Sにより得られる水素濃度を、 $1 \times 10^{20}$  atoms / cm<sup>3</sup>未満、好ましくは $1 \times 10^{19}$  atoms / cm<sup>3</sup>未満、より好ましくは $5 \times 10^{18}$  atoms / cm<sup>3</sup>未満、さらに好ましくは $1 \times 10^{18}$  atoms / cm<sup>3</sup>未満とする。

【0230】

不純物が十分に低減された酸化物半導体をトランジスタのチャネル形成領域に用いることで、安定した電気特性を付与することができる。

【0231】

本実施の形態は、他の実施の形態等に記載した構成と適宜組み合わせて実施することが可能である。

【0232】

(実施の形態4)

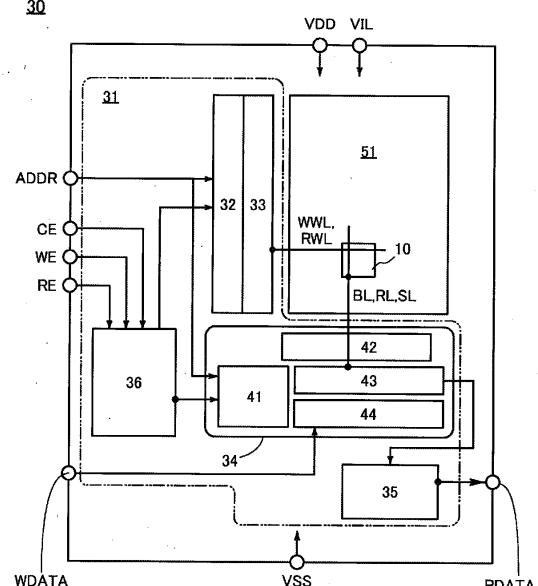

本実施の形態では、実施の形態1に記載の半導体装置10を用いた記憶装置について説明する。

【0233】

<記憶装置>

図20は、記憶装置の構成例を示すブロック図である。記憶装置30は、周辺回路31、およびセルアレイ51を有する。周辺回路31は、ローデコーダ32、ワード線ドライバ回路33、ビット線ドライバ回路34、出力回路35、コントロールロジック回路36を有する。

【0234】

ワード線ドライバ回路33は、配線WLに電位を供給する機能を有する。ビット線ドライバ回路34は、カラムデコーダ41、プリチャージ回路42、增幅回路43、および書き込み回路44を有する。プリチャージ回路42は、配線RLなどをプリチャージする機能を有する。增幅回路43は、配線RLから読み出されたデータ信号を増幅する機能を有する。なお、配線WWL、配線RWL、配線SL、配線BL、および配線RLは、上記実施の形態1で説明したように、セルアレイ51が有するメモリセルとして機能する半導体装置10に接続されている配線である。増幅されたデータ信号は、出力回路35を介して、デジタルのデータ信号RDATAとして記憶装置30の外部に出力される。

【0235】

記憶装置30には、外部から電源電圧として低電源電圧(VSS)、周辺回路31用の高電源電圧(VDD)、セルアレイ51用の高電源電圧(VIL)が供給される。

【0236】

また、記憶装置30には、制御信号(CE、WE、RE)、アドレス信号ADDR、データ信号WDATAが外部から入力される。アドレス信号ADDRは、ローデコーダ32およびカラムデコーダ41に入力され、WDATAは書き込み回路44に入力される。

【0237】

コントロールロジック回路36は、外部からの入力信号(CE、WE、RE)を処理し

10

20

30

40

50

て、ローデコーダ 32、カラムデコーダ 41 の制御信号を生成する。CE は、チップイネーブル信号であり、WE は、書き込みイネーブル信号であり、RE は、読み出シイネーブル信号である。コントロールロジック回路 36 が処理する信号は、これに限定されるものではなく、必要に応じて、他の制御信号を入力すればよい。

【0238】

なお、上述の各回路あるいは各信号は、必要に応じて、適宜、取捨することができる。

【0239】

セルアレイ 51 を構成するトランジスタにOSトランジスタを適用することができる。また、周辺回路 31 を構成するトランジスタにOSトランジスタを適用することができる。セルアレイ 51 と周辺回路 31 を、OSトランジスタを用いて形成することで、セルアレイ 51 と周辺回路 31 を、同一の製造工程で作製することが可能になり、製造コストを 10 低く抑えることができる。

【0240】

(セルアレイの構成例)

図 21 にセルアレイ 51 の詳細を記載する。セルアレイ 51 は、一列に m (m は 1 以上の整数である。) 個、一行に n (n は 1 以上の整数である。) 個、計  $m \times n$  個のメモリセルとして機能する半導体装置 10 を有し、半導体装置 10 は、図 10、図 12、及び図 14 で例示したように、行列状に配置されている。図 21 では、半導体装置 10 のアドレスも併せて表記しており、[1, 1]、[m, 1]、[i, j]、[1, n]、[m, n] (i は、1 以上 m 以下の整数であり、j は、1 以上 n 以下の整数である。) のアドレスに位置している半導体装置 10 を図示している。なお、セルアレイ 51 とワード線ドライバ回路 33 とを接続している配線の数は、半導体装置 10 の構成、一列中に含まれる半導体装置 10 の数などによって決まる。また、セルアレイ 51 とビット線ドライバ回路 34 とを接続している配線の数は、半導体装置 10 の構成、一行中に含まれる半導体装置 10 の数などによって決まる。 20

【0241】

半導体装置 10 の構成とすることで、電荷の充電又は放電することによってデータの書き換えおよび読み出しが可能となるため、実質的に無制限回のデータの書き込みおよび読み出しが可能である。データの読み出し時において、保持した電荷を放電すること、いわゆる破壊読み出しすることなくデータ読み出すことができるため、データリフレッシュに要する電荷の充電および放電の分の消費電力を低減することができる。 30

【0242】

また半導体装置 10 の構成とすることで、データを書き戻す際に要する電荷量を低減することができる。そのため、保持した電荷を静電容量の大きい配線等に放電することなく、データを読み出すことができる。またデータの長時間の保持といった信頼性に優れた半導体装置とすることができる。

【0243】

(実施の形態 5)

本実施の形態は、上記実施の形態に示す記憶装置などが組み込まれた電子部品および電子機器の一例を示す。 40

【0244】

<電子部品>

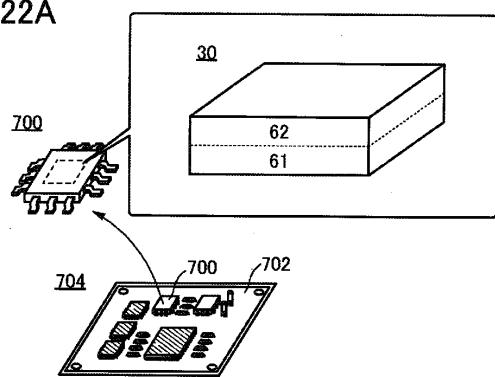

まず、記憶装置 300 が組み込まれた電子部品の例を、図 22A、図 22B を用いて説明を行う。

【0245】

図 22A に電子部品 700 および電子部品 700 が実装された基板 (実装基板 704) の斜視図を示す。図 22A に示す電子部品 700 は I C チップであり、リードおよび回路部を有する。電子部品 700 は、例えばプリント基板 702 に実装される。このような I C チップが複数組み合わされて、それぞれがプリント基板 702 上で電気的に接続されることで実装基板 704 が完成する。 50

## 【0246】

電子部品700の回路部として、上記実施の形態に示した記憶装置30が設けられている。図22Aでは、電子部品700のパッケージにQFP(Quad Flat Pack age)を適用しているが、パッケージの態様はこれに限定されない。記憶装置はSiトランジスタが設けられた層61とOSトランジスタが設けられた層62とが積層されている。

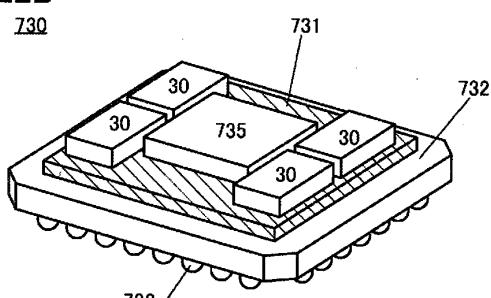

## 【0247】

図22Bに電子部品730の斜視図を示す。電子部品730は、SiP(System in package)またはMCM(Multi Chip Module)の一例である。電子部品730は、パッケージ基板732(プリント基板)上にインターポーラ731が設けられ、インターポーラ731上に半導体装置735、および複数の記憶装置30が設けられている。

10

## 【0248】

電子部品730では、記憶装置30を広帯域メモリ(HBM: High Bandwidth Memory)として用いる例を示している。また、半導体装置735には、CPU(Central Processing Unit)、GPU(Graphic Processing Unit)、FPGA(Field Programmable Gate Array)などの集積回路(半導体装置)を用いることができる。

## 【0249】

パッケージ基板732は、セラミック基板、プラスチック基板、またはガラスエポキシ基板などを用いることができる。インターポーラ731には、シリコンインターポーラ、樹脂インターポーラなどを用いることができる。

20

## 【0250】

インターポーラ731は、複数の配線を有し、端子ピッチの異なる複数の集積回路を電気的に接続する機能を有する。複数の配線は、単層または多層で設けられる。また、インターポーラ731は、インターポーラ731上に設けられた集積回路をパッケージ基板732に設けられた電極と電気的に接続する機能を有する。これらのことから、インターポーラを「再配線基板」または「中間基板」と呼ぶ場合がある。また、インターポーラ731に貫通電極を設けて、当該貫通電極を用いて集積回路とパッケージ基板732を電気的に接続する場合もある。また、シリコンインターポーラでは、貫通電極として、TSV(Through Silicon Via)を用いることも出来る。

30

## 【0251】

インターポーラ731としてシリコンインターポーラを用いることが好ましい。シリコンインターポーラでは能動素子を設ける必要が無いため、集積回路よりも低コストで作製することができる。一方で、シリコンインターポーラの配線形成は半導体プロセスで行なうことができるため、樹脂インターポーラでは難しい微細配線の形成が容易である。

## 【0252】

HBMでは、広いメモリバンド幅を実現するために多くの配線を接続する必要がある。このため、HBMを実装するインターポーラには、微細かつ高密度の配線形成が求められる。よって、HBMを実装するインターポーラには、シリコンインターポーラを用いることが好ましい。

40

## 【0253】

また、シリコンインターポーラを用いたSiPやMCMなどでは、集積回路とインターポーラ間の膨張係数の違いによる信頼性の低下が生じにくい。また、シリコンインターポーラは表面の平坦性が高いため、シリコンインターポーラ上に設ける集積回路とシリコンインターポーラ間の接続不良が生じにくい。特に、インターポーラ上に複数の集積回路を横に並べて配置する2.5Dパッケージ(2.5次元実装)では、シリコンインターポーラを用いることが好ましい。

## 【0254】

また、電子部品730と重ねてヒートシンク(放熱板)を設けてもよい。ヒートシンク

50

を設ける場合は、インターポーザ 731 上に設ける集積回路の高さを揃えることが好ましい。例えば、本実施の形態に示す電子部品 730 では、記憶装置 30 と半導体装置 735 の高さを揃えることが好ましい。

【0255】

電子部品 730 を他の基板に実装するため、パッケージ基板 732 の底部に電極 733 を設けてもよい。図 22B では、電極 733 を半田ボールで形成する例を示している。パッケージ基板 732 の底部に半田ボールをマトリクス状に設けることで、BGA (Ball Grid Array) 実装を実現できる。また、電極 733 を導電性のピンで形成してもよい。パッケージ基板 732 の底部に導電性のピンをマトリクス状に設けることで、PGA (Pin Grid Array) 実装を実現できる。

10

【0256】

電子部品 730 は、BGA および PGA に限らず様々な実装方法を用いて他の基板に実装することができる。例えば、SPGA (Staggered Pin Grid Array)、LGA (Land Grid Array)、QFP (Quad Flat Package)、QFJ (Quad Flat J-leaded package)、または QFN (Quad Flat Non-leaded package) などの実装方法を用いることができる。

【0257】

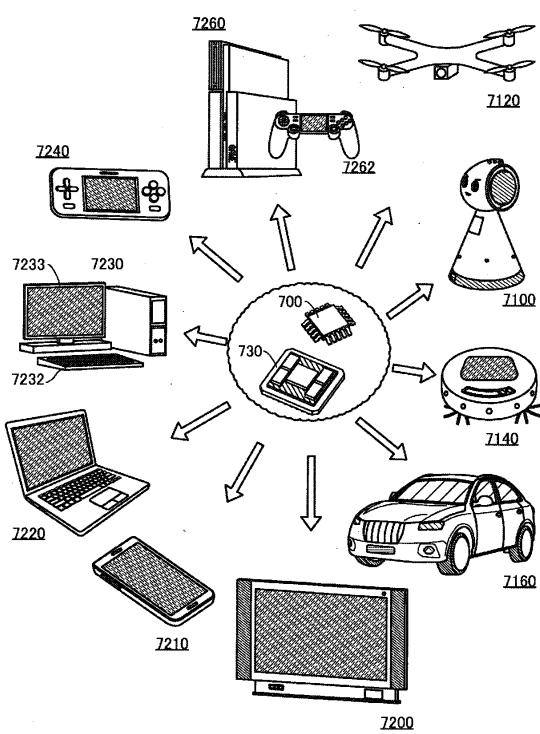

<電子機器>

次に、上記電子部品を備えた電子機器の例について図 23 を用いて説明を行う。

20

【0258】

ロボット 7100 は、照度センサ、マイクロフォン、カメラ、スピーカ、ディスプレイ、各種センサ（赤外線センサ、超音波センサ、加速度センサ、ピエゾセンサ、光センサ、ジャイロセンサなど）、および移動機構などを備える。電子部品 730 はプロセッサなどを有し、これら周辺機器を制御する機能を有する。例えば、電子部品 700 はセンサで取得されたデータを記憶する機能を有する。

【0259】

マイクロフォンは、使用者の音声および環境音などの音響信号を検知する機能を有する。また、スピーカは、音声および警告音などのオーディオ信号を発する機能を有する。ロボット 7100 は、マイクロフォンを介して入力されたオーディオ信号を解析し、必要なオーディオ信号をスピーカから発することができる。ロボット 7100 において、は、マイクロフォン、およびスピーカを用いて、使用者とコミュニケーションをとることが可能である。

30

【0260】

カメラは、ロボット 7100 の周囲を撮像する機能を有する。また、ロボット 7100 は、移動機構を用いて移動する機能を有する。ロボット 7100 は、カメラを用いて周囲の画像を撮像し、画像を解析して移動する際の障害物の有無などを察知することができる。

【0261】

飛行体 7120 は、プロペラ、カメラ、およびバッテリなどを有し、自律して飛行する機能を有する。電子部品 730 はこれら周辺機器を制御する機能を有する。

40

【0262】

例えば、カメラで撮影した画像データは、電子部品 700 に記憶される。電子部品 730 は、画像データを解析し、移動する際の障害物の有無などを察知することができる。また、電子部品 730 によってバッテリの蓄電容量の変化から、バッテリ残量を推定することができる。

【0263】

掃除ロボット 7140 は、上面に配置されたディスプレイ、側面に配置された複数のカメラ、ブラシ、操作ボタン、各種センサなどを有する。図示されていないが、掃除ロボット 7140 には、タイヤ、吸い込み口等が備えられている。掃除ロボット 7140 は自走し、ゴミを検知し、下面に設けられた吸い込み口からゴミを吸引することができる。

50

## 【0264】

例えば、電子部品730は、カメラが撮影した画像を解析し、壁、家具または段差などの障害物の有無を判断することができる。また、画像解析により、配線などブラシに絡まりそうな物体を検知した場合は、ブラシの回転を止めることができる。

## 【0265】

自動車7160は、エンジン、タイヤ、ブレーキ、操舵装置、カメラなどを有する。例えば、電子部品730は、ナビゲーション情報、速度、エンジンの状態、ギアの選択状態、ブレーキの使用頻度などのデータに基づいて、自動車7160の走行状態を最適化するための制御を行う。例えば、カメラで撮影した画像データは電子部品700に記憶される。

## 【0266】

電子部品700および/または電子部品730は、TV装置7200（テレビジョン受像装置）、スマートフォン7210、PC（パーソナルコンピュータ）7220、7230、ゲーム機7240、ゲーム機7260等に組み込むことができる。

## 【0267】

例えば、TV装置7200に内蔵された電子部品730は画像エンジンとして機能させることができる。例えば、電子部品730は、ノイズ除去、解像度アップコンバージョンなどの画像処理を行う。

## 【0268】

スマートフォン7210は、携帯情報端末の一例である。スマートフォン7210は、マイクロフォン、カメラ、スピーカ、各種センサ、および表示部を有する。電子部品730によってこれら周辺機器が制御される。

10

20

## 【0269】

PC7220、PC7230はそれぞれノート型PC、据え置き型PCの例である。PC7230には、キーボード7232、およびモニタ装置7233が無線または有線により接続可能である。ゲーム機7240は携帯型ゲーム機の例である。ゲーム機7260は据え置き型ゲーム機の例である。ゲーム機7260には、無線または有線でコントローラ7262が接続されている。コントローラ7262に、電子部品700および/または電子部品730を組み込むこともできる。

## 【0270】

本実施の形態は、他の実施の形態などに記載した構成と適宜組み合わせて実施することが可能である。

30

## 【0271】

（本明細書等の記載に関する付記）

以上の実施の形態、及び実施の形態における各構成の説明について、以下に付記する。

## 【0272】

各実施の形態に示す構成は、他の実施の形態あるいは実施例に示す構成と適宜組み合わせて、本発明の一態様とすることができます。また、1つの実施の形態の中に、複数の構成例が示される場合は、構成例を適宜組み合わせることが可能である。

## 【0273】

なお、ある一つの実施の形態の中で述べる内容（一部の内容でもよい）は、その実施の形態で述べる別の内容（一部の内容でもよい）、及び/又は、一つ若しくは複数の別の実施の形態で述べる内容（一部の内容でもよい）に対して、適用、組み合わせ、又は置き換えなどを行うことが出来る。

40

## 【0274】

なお、実施の形態の中で述べる内容とは、各々の実施の形態において、様々な図を用いて述べる内容、又は明細書に記載される文章を用いて述べる内容のことである。

## 【0275】

なお、ある一つの実施の形態において述べる図（一部でもよい）は、その図の別の部分、その実施の形態において述べる別の図（一部でもよい）、及び/又は、一つ若しくは複数の別の実施の形態において述べる図（一部でもよい）に対して、組み合わせることによ

50

り、さらに多くの図を構成させることが出来る。

【0276】

また本明細書等において、ブロック図では、構成要素を機能毎に分類し、互いに独立したブロックとして示している。しかしながら実際の回路等においては、構成要素を機能毎に切り分けることが難しく、一つの回路に複数の機能が係わる場合や、複数の回路にわたって一つの機能が関わる場合があり得る。そのため、ブロック図のブロックは、明細書で説明した構成要素に限定されず、状況に応じて適切に言い換えることができる。

【0277】

また、図面において、大きさ、層の厚さ、又は領域は、説明の便宜上任意の大きさに示したものである。よって、必ずしもそのスケールに限定されない。なお図面は明確性を期すために模式的に示したものであり、図面に示す形状又は値などに限定されない。例えば、ノイズによる信号、電圧、若しくは電流のばらつき、又は、タイミングのずれによる信号、電圧、若しくは電流のばらつきなどを含むことが可能である。

10

【0278】

また、図面等において図示する構成要素の位置関係は、相対的である。従って、図面を参照して構成要素を説明する場合、位置関係を示す「上に」、「下に」等の語句は便宜的に用いられる場合がある。構成要素の位置関係は、本明細書の記載内容に限定されず、状況に応じて適切に言い換えることができる。

【0279】

本明細書等において、トランジスタの接続関係を説明する際、「ソース又はドレインの一方」（又は第1電極、又は第1端子）、ソースとドレインとの他方を「ソース又はドレインの他方」（又は第2電極、又は第2端子）という表記を用いる。これは、トランジスタのソースとドレインは、トランジスタの構造又は動作条件等によって変わるものである。なおトランジスタのソースとドレインの呼称については、ソース（ドレイン）端子や、ソース（ドレイン）電極等、状況に応じて適切に言い換えることができる。

20

【0280】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

30

【0281】

また、本明細書等において、電圧と電位は、適宜言い換えることができる。電圧は、基準となる電位からの電位差のことであり、例えば基準となる電位をグラウンド電圧（接地電圧）とすると、電圧を電位に言い換えることができる。グラウンド電位は必ずしも0Vを意味するとは限らない。なお電位は相対的なものであり、基準となる電位によっては、配線等に与える電位を変化させる場合がある。

【0282】

また本明細書等において、ノードは、回路構成やデバイス構造等に応じて、端子、配線、電極、導電層、導電体、不純物領域等と言い換えることが可能である。また、端子、配線等をノードと言い換えることが可能である。

40

【0283】

本明細書等において、AとBとが接続されている、とは、AとBとが電気的に接続されているものをいう。ここで、AとBとが電気的に接続されているとは、AとBとの間で対象物（スイッチ、トランジスタ素子、またはダイオード等の素子、あるいは当該素子および配線を含む回路等を指す）が存在する場合にAとBとの電気信号の伝達が可能である接続をいう。なおAとBとが電気的に接続されている場合には、AとBとが直接接続されている場合を含む。ここで、AとBとが直接接続されているとは、上記対象物を介することなく、AとBとの間で配線（または電極）等を介してAとBとの電気信号の伝達が可能である接続をいう。換言すれば、直接接続とは、等価回路で表した際に同じ回路図として見なせる接続をいう。

50

## 【0284】

本明細書等において、スイッチとは、導通状態（オン状態）、または、非導通状態（オフ状態）になり、電流を流すか流さないかを制御する機能を有するものをいう。または、スイッチとは、電流を流す経路を選択して切り替える機能を有するものをいう。

## 【0285】

本明細書等において、チャネル長とは、例えば、トランジスタの上面図において、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲートとが重なる領域、またはチャネルが形成される領域における、ソースとドレインとの間の距離をいう。

## 【0286】

本明細書等において、チャネル幅とは、例えば、半導体（またはトランジスタがオン状態のときに半導体の中で電流の流れる部分）とゲート電極とが重なる領域、またはチャネルが形成される領域における、ソースとドレインとが向かい合っている部分の長さをいう。

## 【0287】

なお本明細書等において、「膜」、「層」などの語句は、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を、「導電膜」という用語に変更することが可能な場合がある。または、例えば、「絶縁膜」という用語を、「絶縁層」という用語に変更することが可能な場合がある。

## 【符号の説明】

## 【0288】

B L \_ 1 : 配線、M N 1 : ノード、M N 2 : ノード、R L \_ 1 : 配線、R W L \_ 1 : 配線、S L \_ 1 : 配線、S L \_ 2 : 配線、T 1 : 期間、T 2 : 期間、T 3 : 期間、T 4 : 期間、T 5 : 期間、T 6 : 期間、T 7 : 期間、T 8 : 期間、T 9 : 期間、W W L \_ 1 : 配線、W W L \_ 2 : 配線、1 0 : 半導体装置、1 0 \_ 1 : 半導体装置、1 0 \_ 4 : 半導体装置、1 0 A : 半導体装置、1 0 B : 半導体装置、1 0 C : 半導体装置、1 0 D : 半導体装置、1 0 E : 半導体装置、1 0 F : 半導体装置、1 0 G : 半導体装置、1 1 : トランジスタ、1 1 A : トランジスタ、1 1 B : トランジスタ、1 1 C : トランジスタ、1 1 D : トランジスタ、1 1 E : トランジスタ、1 1 F : トランジスタ、1 1 G : トランジスタ、1 2 : トランジスタ、1 2 A : トランジスタ、1 2 B : トランジスタ、1 2 C : トランジスタ、1 2 D : トランジスタ、1 2 E : トランジスタ、1 2 F : トランジスタ、1 2 G : トランジスタ、1 3 : トランジスタ、1 3 A : トランジスタ、1 3 B : トランジスタ、1 3 C : トランジスタ、1 3 D : トランジスタ、1 3 E : トランジスタ、1 3 G : トランジスタ、1 4 : キャパシタ、1 5 : 電荷保持回路、3 0 : 記憶装置、3 1 : 周辺回路、3 2 : ポーデコーダ、3 3 : ワード線ドライバ回路、3 4 : ビット線ドライバ回路、3 5 : 出力回路、3 6 : コントロールロジック回路、4 1 : カラムデコーダ、4 2 : プリチャージ回路、4 3 : 増幅回路、4 4 : 回路、5 1 : セルアレイ、6 1 : 層、6 2 : 層、3 0 0 : 記憶装置、3 1 1 : 基板、3 1 3 : 半導体領域、3 1 4 a : 低抵抗領域、3 1 4 b : 低抵抗領域、3 1 5 : 絶縁体、3 1 6 : 導電体、3 2 0 : 絶縁体、3 2 2 : 絶縁体、3 2 4 : 絶縁体、3 2 6 : 絶縁体、3 2 8 : 導電体、3 3 0 : 導電体、3 5 0 : 絶縁体、3 5 2 : 絶縁体、3 5 4 : 絶縁体、3 5 6 : 導電体、3 6 0 : 絶縁体、3 6 2 : 絶縁体、3 6 4 : 絶縁体、3 6 6 : 導電体、3 7 0 : 絶縁体、3 7 2 : 絶縁体、3 7 4 : 絶縁体、3 7 6 : 導電体、3 8 0 : 絶縁体、3 8 2 : 絶縁体、3 8 4 : 絶縁体、3 8 6 : 導電体、4 0 2 : 絶縁体、4 0 4 : 絶縁体、5 0 3 : 導電体、5 0 3 a : 導電体、5 0 3 b : 導電体、5 1 0 : 絶縁体、5 1 2 : 絶縁体、5 1 4 : 絶縁体、5 1 6 : 絶縁体、5 1 8 : 導電体、5 2 0 : 絶縁体、5 2 2 : 絶縁体、5 2 4 : 絶縁体、5 3 0 : 酸化物、5 3 0 a : 酸化物、5 3 0 b : 酸化物、5 3 0 c : 酸化物、5 4 0 a : 導電体、5 4 0 b : 導電体、5 4 2 : 導電体、5 4 2 a : 導電体、5 4 2 b : 導電体、5 4 3 a : 領域、5 4 3 b : 領域、5 4 4 : 絶縁体、5 4 6 : 導電体、5 4 8 : 導電体、5 5 0 : 絶縁体、5 5 2 : 絶縁体、5 6 0 : 導電体、5 6 0 a : 導電体、5 6 0 b : 導電体、5 7 4 : 絶縁体、5 8 0 : 絶縁体、5 8 1 : 絶縁体、5 8 2 : 絶縁体、5 8 6 : 絶縁体、6 1 0 : 導電体、6 1 2 : 導電体、6 2 0

10

20

30

40

50

：導電体、630：絶縁体、640：絶縁体、700：電子部品、702：プリント基板、704：実装基板、730：電子部品、731：インターポーラ、732：パッケージ基板、733：電極、735：半導体装置、7100：ロボット、7120：飛行体、7140：掃除ロボット、7160：自動車、7200：TV装置、7210：スマートフォン、7220：PC、7230：PC、7232：キーボード、7233：モニタ装置、7240：ゲーム機、7260：ゲーム機、7262：コントローラ

## 【図面】

【図1A】

【図1B】

【図1B】

10

20

30

【図2A】

【図2A】

I1

【図2B】

【図2B】

I2

40

50

【図 3 A】

図3A

I3

【図 3 B】

図3B

I4

10

【図 4 A】

図4A

I5

【図 4 B】

図4B

I6

20

30

40

50

【図 5 A】

図5A

I7

【図 5 B】

図5B

I8

10

【図 6】

図6

I9

【図 7 A】

図7A

10A

20

30

40

50

【図 7 B】

図7B

【図 8 A】

図8A

10

【図 8 B】

図8B

【図 9 A】

図9A

20

30

40

50

【図 9 B】

図9B

【図 9 C】

図9C

10

【図 10】

図10

【図 11】

図11

20

30

40

50

【図12】

図12

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17A】

図17A

10

20

【図17B】

図17B

【図17C】

図17C

30

40

50

【図18A】

図18A

【図18B】

図18B

10

【図19】

図19

【図20】

図20

20

30

40

50

【図21】

図21

10

20

【図22A】

図22A

30

【図22B】

図22B

【図23】

図23

40

50

---

フロントページの続き

al Electron Devices Meeting 開催日 平成30年12月1日 - 5日

(56)参考文献 特開2007-115335 (JP, A)

国際公開第2013/146039 (WO, A1)

特開2012-256818 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

G 11 C 11/405