(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0051562

(43) 공개일자 2012년05월22일

(51) 국제특허분류(Int. Cl.)

*H03K 19/0185* (2006.01) *G06F 13/00*

(2006.01)

(21) 출원번호 10-2011-0005020

(22) 출원일자 2011년01월18일

심사청구일자 없음

(30) 우선권주장

61/412,952 2010년11월12일 미국(US)

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

구자천

서울특별시 강남구 선릉로 221, 102동 506호 (도곡동, 도곡렉슬아파트)

임경록

경기도 수원시 영통구 영통로 111, 동수원엘지빌리지3차 303동 1102호 (망포동)

(74) 대리인

권혁수, 송윤호, 오세준

전체 청구항 수 : 총 22 항

(54) 발명의 명칭 레벨 변환기, 그것을 포함하는 시스템-온-칩, 그리고 그것을 포함하는 멀티미디어 장치

### (57) 요 약

본 발명은 레벨 변환기에 관한 것이다. 본 발명의 레벨 변환기는, 입력 노드를 통해 수신되는 제 1 전압 도메인의 입력 클록에 응답하여 제 2 전압 도메인의 출력 클록을 발생하는 제 1 및 제 2 전압 변환 회로들을 포함하고, 제 1 및 제 2 전압 변환 회로들은 동일한 구조를 가지며, 입력 노드 및 출력 노드 사이에 병렬 연결된다.

대 표 도 - 도1

## 특허청구의 범위

### 청구항 1

입력 노드;

상기 입력 노드를 통해 수신되는 제 1 전압 도메인의 입력 클록에 응답하여 제 2 전압 도메인의 출력 클록을 발생하도록 구성되는 제 1 및 제 2 전압 변환 회로들; 그리고

상기 출력 클록을 출력하는 출력 노드를 포함하고,

상기 제 1 및 제 2 전압 변환 회로들은 동일한 구조를 가지며, 상기 입력 노드 및 출력 노드 사이에 병렬 연결되는 레벨 변환기.

### 청구항 2

제 1 항에 있어서,

상기 제 1 전압 변환 회로는 상기 제 2 전압 도메인에서 동작하는 적어도 두 개의 인버터들을 포함하는 레벨 변환기.

### 청구항 3

제 1 항에 있어서,

상기 제 2 전압 변환 회로는 상기 제 1 전압 도메인에서 동작하는 적어도 하나의 인버터와 상기 제 2 전압 도메인에서 동작하는 적어도 하나의 인버터를 포함하는 레벨 변환기.

### 청구항 4

제 3 항에 있어서,

상기 제 2 전압 도메인에서 동작하는 적어도 하나의 인버터는 상기 제 1 전압 도메인에서 동작하는 적어도 하나의 인버터의 출력을 수신하도록 구성되는 레벨 변환기.

### 청구항 5

제 1 항에 있어서,

상기 제 1 전압 변환 회로는 상기 입력 노드의 전압에 따라 제 2 전압 또는 접지 전압을 출력하는 제 1 인버터 및 상기 제 1 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 출력 노드로 출력하는 제 2 인버터를 포함하고,

상기 제 2 전압 변환 회로는 상기 입력 노드의 전압에 따라 상기 제 1 전압 또는 접지 전압을 출력하는 제 3 인버터 및 상기 제 3 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 상기 출력 노드로 출력하는 제 4 인버터를 포함하는 레벨 변환기.

### 청구항 6

제 5 항에 있어서,

상기 제 1 내지 제 4 인버터들은 씨모스(CMOS) 인버터들인 레벨 변환기.

### 청구항 7

제 1 전압 도메인의 제 1 클록을 발생하도록 구성되는 위상 고정 루프;

상기 제 1 클록에 응답하여 동작하는 주변 블록, 오디오 블록, 디스플레이 블록, 그래픽 블록, 이미지 프로세싱 블록, 그리고 코덱 블록;

상기 제 1 클록에 기반하여, 제 2 전압 도메인의 제 2 클록을 발생하는 레벨 변환기; 그리고

상기 제 2 클록에 응답하여 동작하는 프로세서를 포함하고,

상기 레벨 변환기는 입력 노드 및 출력 노드 사이에 병렬 연결되며 동일한 구조를 갖는 제 1 및 제 2 전압 변환 회로들을 포함하는 시스템-온-칩(SOC, System-On-Chip).

### 청구항 8

제 7 항에 있어서,

상기 제 1 전압 변환 회로는 상기 제 2 전압 도메인에서 동작하며 직렬 연결된 제 1 및 제 2 인버터들을 포함하고,

상기 제 2 전압 변환 회로는 상기 제 1 전압 도메인에서 동작하는 제 3 인버터, 그리고 상기 제 2 전압 도메인에서 상기 제 3 인버터의 출력에 응답하여 동작하는 제 4 인버터를 포함하는 시스템-온-칩.

### 청구항 9

제 7 항에 있어서,

상기 제 2 전압 도메인의 전압 레벨은 상기 제 1 전압 도메인의 전압 레벨보다 높은 시스템-온-칩.

### 청구항 10

프로세서;

상기 프로세서의 동작 메모리;

상기 프로세서의 제어에 따라 외부와 통신하도록 구성되는 모뎀;

상기 프로세서의 제어에 따라 데이터를 저장하도록 구성되는 저장부;

외부의 신호를 감지하여 상기 프로세서에 전달하도록 구성되는 사용자 인터페이스;

상기 프로세서의 제어에 따라, 디스플레이부를 통해 영상을 표시하도록 구성되는 디스플레이 제어부;

상기 프로세서의 제어에 따라, 스피커를 통해 소리를 출력하도록 구성되는 사운드 제어부;

상기 프로세서의 제어에 따라 인코딩 및 디코딩을 수행하는 코덱부;

발진기의 출력에 따라 클록을 발생하도록 구성되는 클록 발생부;

상기 클록에 동기되는 제 1 전압 도메인의 제 1 클록을 발생하는 위상 고정 루프; 그리고

상기 제 1 클록에 응답하여 제 2 전압 도메인의 제 2 클록을 발생하도록 구성되는 레벨 변환기를 포함하고,

상기 프로세서는 상기 제 2 클록에 응답하여 동작하고,

상기 레벨 변환기는 입력 노드 및 출력 노드 사이에 병렬 연결되며 동일한 구조를 갖는 제 1 및 제 2 전압 변환 회로들을 포함하는 멀티미디어 장치.

### 청구항 11

제 10 항에 있어서,

상기 레벨 변환기는,

상기 입력 노드의 전압에 따라 상기 제 2 전압 도메인의 제 2 전압 또는 접지 전압을 출력하는 제 1 인버터;

상기 제 1 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 출력 노드로 출력하는 제 2 인버터;

상기 입력 노드의 전압에 따라 상기 제 1 전압 도메인의 제 1 전압 또는 접지 전압을 출력하는 제 3 인버터; 그리고

상기 제 3 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 상기 출력 노드로 출력하는 제 4 인버터를 포함하는 멀티미디어 장치.

### 청구항 12

제 10 항에 있어서,

상기 프로세서, 동작 메모리, 디스플레이 제어부, 사운드 제어부, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 동작 메모리, 디스플레이 제어부, 사운드 제어부, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

### 청구항 13

제 10 항에 있어서,

상기 프로세서의 제어에 따라, 카메라로부터 획득되는 이미지 데이터를 처리하도록 구성되는 이미지 프로세싱부를 더 포함하는 멀티미디어 장치.

### 청구항 14

제 13 항에 있어서,

상기 프로세서, 디스플레이 제어부, 사운드 제어부, 이미지 프로세싱부, 동작 메모리, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 디스플레이 제어부, 사운드 제어부, 이미지 프로세싱부, 동작 메모리, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

### 청구항 15

제 13 항에 있어서,

상기 프로세서, 디스플레이 제어부, 사운드 제어부, 모뎀, 이미지 프로세싱부, 동작 메모리, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 디스플레이 제어부, 사운드 제어부, 모뎀, 이미지 프로세싱부, 동작 메모리, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

### 청구항 16

제 13 항에 있어서,

상기 프로세서, 디스플레이 제어부, 사운드 제어부, 동작 메모리, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 디스플레이 제어부, 사운드 제어부, 동작 메모리, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

### 청구항 17

제 13 항에 있어서,

상기 프로세서, 디스플레이 제어부, 사운드 제어부, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 디스플레이 제어부, 사운드 제어부, 그리고 동작 메모리는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

### 청구항 18

제 13 항에 있어서,

상기 프로세서, 디스플레이 제어부, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 디스플레이 제어부, 그리고 동작 메모리는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

**청구항 19**

제 13 항에 있어서,

상기 프로세서, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 동작 메모리는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

**청구항 20**

제 13 항에 있어서,

상기 프로세서, 사운드 제어부, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고,

상기 사운드 제어부 및 동작 메모리는 상기 제 1 클록에 응답하여 동작하는 멀티미디어 장치.

**청구항 21**

제 10 항에 있어서,

상기 프로세서, 동작 메모리, 모뎀, 저장부, 사용자 인터페이스, 디스플레이 제어부, 디스플레이부, 사운드 제어부, 스피커, 발진기, 클록 발생부, 카메라, 이미지 프로세싱부, 코덱부, 그리고 위상 고정 루프는 모바일 장치를 구성하는 멀티미디어 장치.

**청구항 22**

제 10 항에 있어서,

상기 프로세서, 동작 메모리, 모뎀, 저장부, 사용자 인터페이스, 디스플레이 제어부, 디스플레이부, 사운드 제어부, 스피커, 발진기, 클록 발생부, 카메라, 이미지 프로세싱부, 코덱부, 그리고 위상 고정 루프는 스마트 텔레비전(Smart Television)을 구성하는 멀티미디어 장치.

**명세서****기술 분야**

[0001]

본 발명은 전자 회로에 관한 것으로, 더 상세하게는 레벨 변환기, 그것을 포함하는 시스템-온-칩, 그리고 그것을 포함하는 멀티미디어 장치에 관한 것이다.

**배경기술**

[0002]

레벨 변환기(level shifter)는 제 1 전압 도메인의 신호를 수신하고, 제 1 전압과 다른 제 2 전압 도메인의 신호를 출력하는 소자이다. 서로 다른 전압들을 사용하는 전압 도메인들 사이에서 레벨 변환기가 사용된다.

[0003]

시스템-온-칩(SOC, System-On-Chip)은 복수의 아이피들(IP, Intellectual Property) 및 프로세서를 포함한다. 프로세서는 아이피들(IP)보다 빠른 동작 속도를 갖는다. 프로세서의 동작 성능을 향상시키기 위하여, 프로세서에 공급되는 클록의 전압 레벨은 아이피들(IP)에 공급되는 클록의 전압 레벨보다 높게 설정될 수 있다. 프로세서에 공급되는 클록의 전압 레벨을 상승시키기 위하여, 시스템-온-칩(SOC)에서 레벨변환기가 사용될 수 있다.

**발명의 내용****해결하려는 과제**

[0004]

본 발명의 목적은 향상된 신뢰성을 갖는 레벨 변환기, 그것을 포함하는 시스템-온-칩, 그리고 그것을 포함하는 멀티미디어 장치를 제공하는 데에 있다.

**과제의 해결 수단**

[0005]

본 발명의 실시 예에 따른 레벨 변환기는, 입력 노드; 상기 입력 노드를 통해 수신되는 제 1 전압 도메인의 입력 클록에 응답하여 제 2 전압 도메인의 출력 클록을 발생하도록 구성되는 제 1 및 제 2 전압 변환 회로들;

그리고 상기 출력 클록을 출력하는 출력 노드를 포함하고, 상기 제 1 및 제 2 전압 변환 회로들은 동일한 구조를 가지며, 상기 입력 노드 및 출력 노드 사이에 병렬 연결된다.

[0006] 실시 예로서, 상기 제 1 전압 변환 회로는 상기 제 2 전압 도메인에서 동작하는 적어도 두 개의 인버터들을 포함한다.

[0007] 실시 예로서, 상기 제 2 전압 변환 회로는 상기 제 1 전압 도메인에서 동작하는 적어도 하나의 인버터와 상기 제 2 전압 도메인에서 동작하는 적어도 하나의 인버터를 포함한다.

[0008] 실시 예로서, 상기 제 2 전압 도메인에서 동작하는 적어도 하나의 인버터는 상기 제 1 전압 도메인에서 동작하는 적어도 하나의 인버터의 출력을 수신하도록 구성된다.

[0009] 실시 예로서, 상기 제 1 전압 변환 회로는 상기 입력 노드의 전압에 따라 제 2 전압 또는 접지 전압을 출력하는 제 1 인버터 및 상기 제 1 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 출력 노드로 출력하는 제 2 인버터를 포함하고, 상기 제 2 전압 변환 회로는 상기 입력 노드의 전압에 따라 상기 제 1 전압 또는 접지 전압을 출력하는 제 3 인버터 및 상기 제 3 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 상기 출력 노드로 출력하는 제 4 인버터를 포함한다.

[0010] 실시 예로서, 상기 제 1 내지 제 4 인버터들은 씨모스(CMOS) 인버터들이다.

[0011] 본 발명의 실시 예에 따른 시스템-온-칩은, 제 1 전압 도메인의 제 1 클록을 발생하도록 구성되는 위상 고정 루프; 상기 제 1 클록에 응답하여 동작하는 주변 블록, 오디오 블록, 디스플레이 블록, 그래픽 블록, 이미지 프로세싱 블록, 그리고 코덱 블록; 상기 제 1 클록에 기반하여, 제 2 전압 도메인의 제 2 클록을 발생하는 레벨 변환기; 그리고 상기 제 2 클록에 응답하여 동작하는 프로세서를 포함하고, 상기 레벨 변환기는 입력 노드 및 출력 노드 사이에 병렬 연결되며 동일한 구조를 갖는 제 1 및 제 2 전압 변환 회로들을 포함한다.

[0012] 실시 예로서, 상기 제 1 전압 변환 회로는 상기 제 2 전압 도메인에서 동작하며 직렬 연결된 제 1 및 제 2 인버터들을 포함하고, 상기 제 2 전압 변환 회로는 상기 제 1 전압 도메인에서 동작하는 제 3 인버터, 그리고 상기 제 2 전압 도메인에서 상기 제 3 인버터의 출력에 응답하여 동작하는 제 4 인버터를 포함한다.

[0013] 실시 예로서, 상기 제 2 전압 도메인의 전압 레벨은 상기 제 1 전압 도메인의 전압 레벨보다 높다.

[0014] 본 발명의 실시 예에 따른 멀티미디어 장치는, 프로세서; 상기 프로세서의 동작 메모리; 상기 프로세서의 제어에 따라 외부와 통신하도록 구성되는 모뎀; 상기 프로세서의 제어에 따라 데이터를 저장하도록 구성되는 저장부; 외부의 신호를 감지하여 상기 프로세서에 전달하도록 구성되는 사용자 인터페이스; 상기 프로세서의 제어에 따라, 디스플레이부를 통해 영상을 표시하도록 구성되는 디스플레이 제어부; 상기 프로세서의 제어에 따라, 스피커를 통해 소리를 출력하도록 구성되는 사운드 제어부; 상기 프로세서의 제어에 따라 인코딩 및 디코딩을 수행하는 코덱부; 발진기의 출력에 따라 클록을 발생하도록 구성되는 클록 발생부; 상기 클록에 동기되는 제 1 전압 도메인의 제 1 클록을 발생하는 위상 고정 루프; 그리고 상기 제 1 클록에 응답하여 제 2 전압 도메인의 제 2 클록을 발생하도록 구성되는 레벨 변환기를 포함하고, 상기 프로세서는 상기 제 2 클록에 응답하여 동작하고, 상기 레벨 변환기는 입력 노드 및 출력 노드 사이에 병렬 연결되며 동일한 구조를 갖는 제 1 및 제 2 전압 변환 회로들을 포함한다.

[0015] 실시 예로서, 상기 입력 노드의 전압에 따라 상기 제 2 전압 도메인의 제 2 전압 또는 접지 전압을 출력하는 제 1 인버터; 상기 제 1 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 출력 노드로 출력하는 제 2 인버터; 상기 입력 노드의 전압에 따라 상기 제 1 전압 도메인의 제 1 전압 또는 접지 전압을 출력하는 제 3 인버터; 그리고 상기 제 3 인버터의 출력에 따라 상기 제 2 전압 또는 접지 전압을 상기 출력 노드로 출력하는 제 4 인버터를 포함한다.

[0016] 실시 예로서, 상기 프로세서, 동작 메모리, 디스플레이 제어부, 사운드 제어부, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 동작 메모리, 디스플레이 제어부, 사운드 제어부, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작한다.

[0017] 실시 예로서, 상기 프로세서의 제어에 따라, 카메라로부터 획득되는 이미지 데이터를 처리하도록 구성되는 이미지 프로세싱부를 더 포함한다.

[0018] 실시 예로서, 상기 프로세서, 디스플레이 제어부, 사운드 제어부, 이미지 프로세싱부, 동작 메모리, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 디스플레이 제어부, 사운드

제어부, 이미지 프로세싱부, 동작 메모리, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작한다.

[0019] 실시 예로서, 상기 프로세서, 디스플레이 제어부, 사운드 제어부, 모뎀, 이미지 프로세싱부, 동작 메모리, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 디스플레이 제어부, 사운드 제어부, 모뎀, 이미지 프로세싱부, 동작 메모리, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작한다.

[0020] 실시 예로서, 상기 프로세서, 디스플레이 제어부, 사운드 제어부, 동작 메모리, 코덱부, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 디스플레이 제어부, 사운드 제어부, 동작 메모리, 그리고 코덱부는 상기 제 1 클록에 응답하여 동작한다.

[0021] 실시 예로서, 상기 프로세서, 디스플레이 제어부, 사운드 제어부, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 디스플레이 제어부, 사운드 제어부, 그리고 동작 메모리는 상기 제 1 클록에 응답하여 동작한다.

[0022] 실시 예로서, 상기 프로세서, 디스플레이 제어부, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 디스플레이 제어부, 그리고 동작 메모리는 상기 제 1 클록에 응답하여 동작한다.

[0023] 실시 예로서, 상기 프로세서, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 동작 메모리는 상기 제 1 클록에 응답하여 동작한다.

[0024] 실시 예로서, 상기 프로세서, 사운드 제어부, 동작 메모리, 그리고 위상 고정 루프는 시스템-온-칩(System-On-Chip)을 구성하고, 상기 사운드 제어부 및 동작 메모리는 상기 제 1 클록에 응답하여 동작한다.

[0025] 실시 예로서, 상기 프로세서, 동작 메모리, 모뎀, 저장부, 사용자 인터페이스, 디스플레이 제어부, 디스플레이 이부, 사운드 제어부, 스피커, 발진기, 클록 발생부, 카메라, 이미지 프로세싱부, 코덱부, 그리고 위상 고정 루프는 모바일 장치를 구성한다.

[0026] 실시 예로서, 상기 프로세서, 동작 메모리, 모뎀, 저장부, 사용자 인터페이스, 디스플레이 제어부, 디스플레이 이부, 사운드 제어부, 스피커, 발진기, 클록 발생부, 카메라, 이미지 프로세싱부, 코덱부, 그리고 위상 고정 루프는 스마트 텔레비전(Smart Television)을 구성한다.

### 발명의 효과

[0027] 본 발명에 의하면, 레벨 변환기의 출력 클록의 고레벨 구간의 폭과 저레벨 구간의 폭이 평준화된다. 따라서, 향상된 신뢰성을 갖는 레벨 변환기, 그것을 포함하는 시스템-온-칩, 그리고 그것을 포함하는 멀티미디어 장치가 제공된다.

### 도면의 간단한 설명

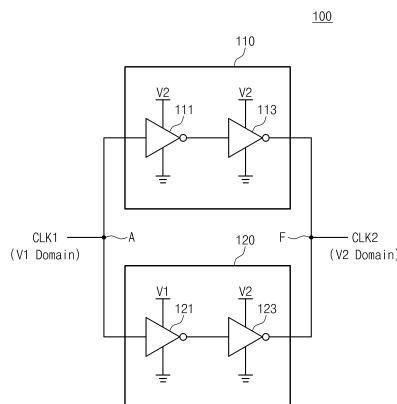

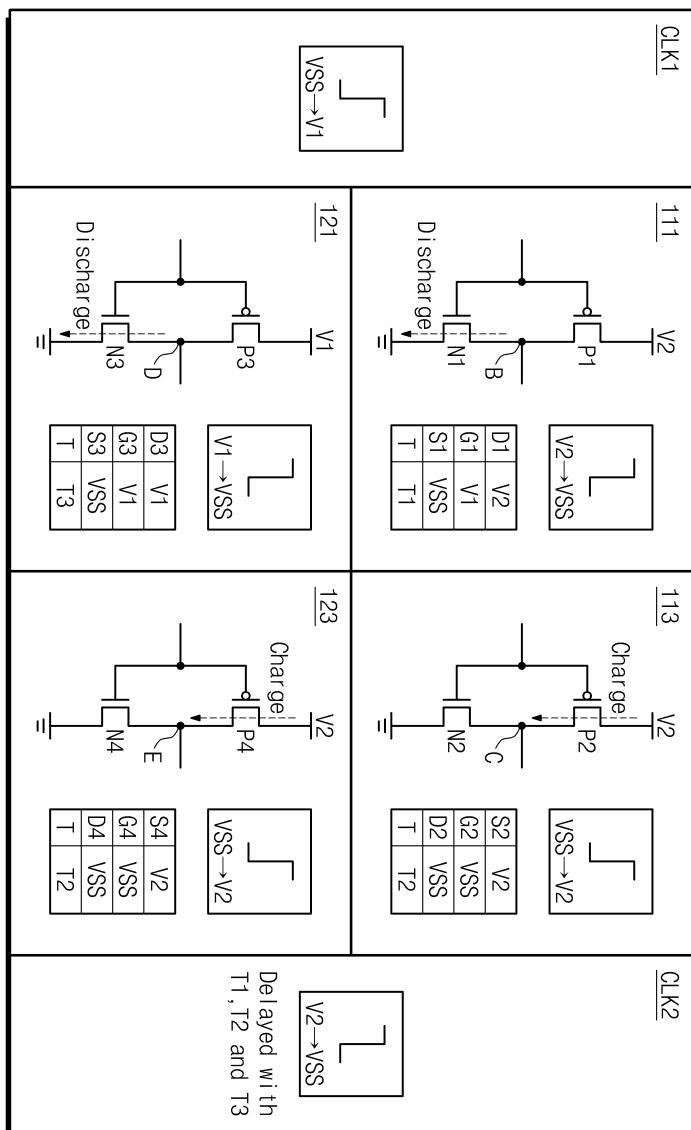

[0028] 도 1은 본 발명의 실시 예에 따른 레벨 변환기를 보여주는 블록도이다.

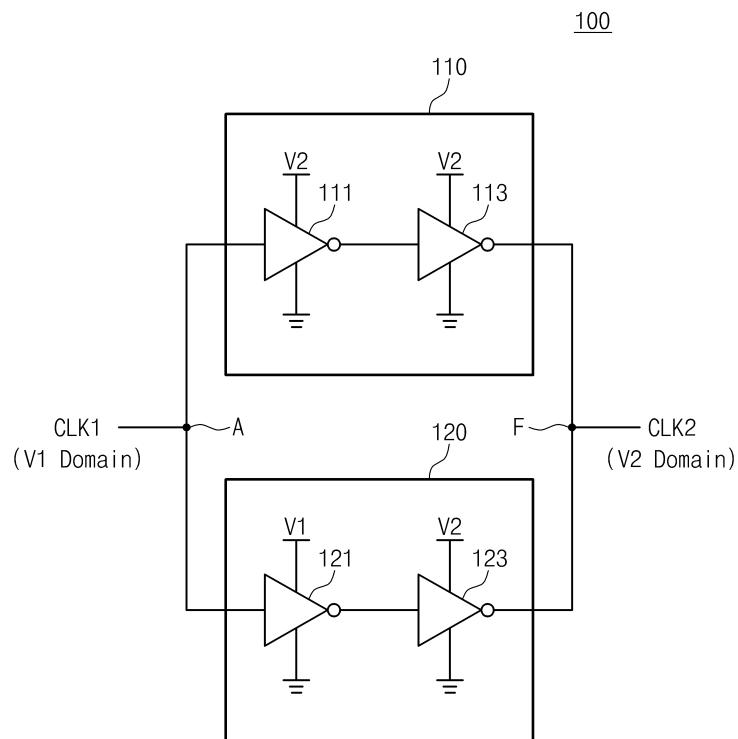

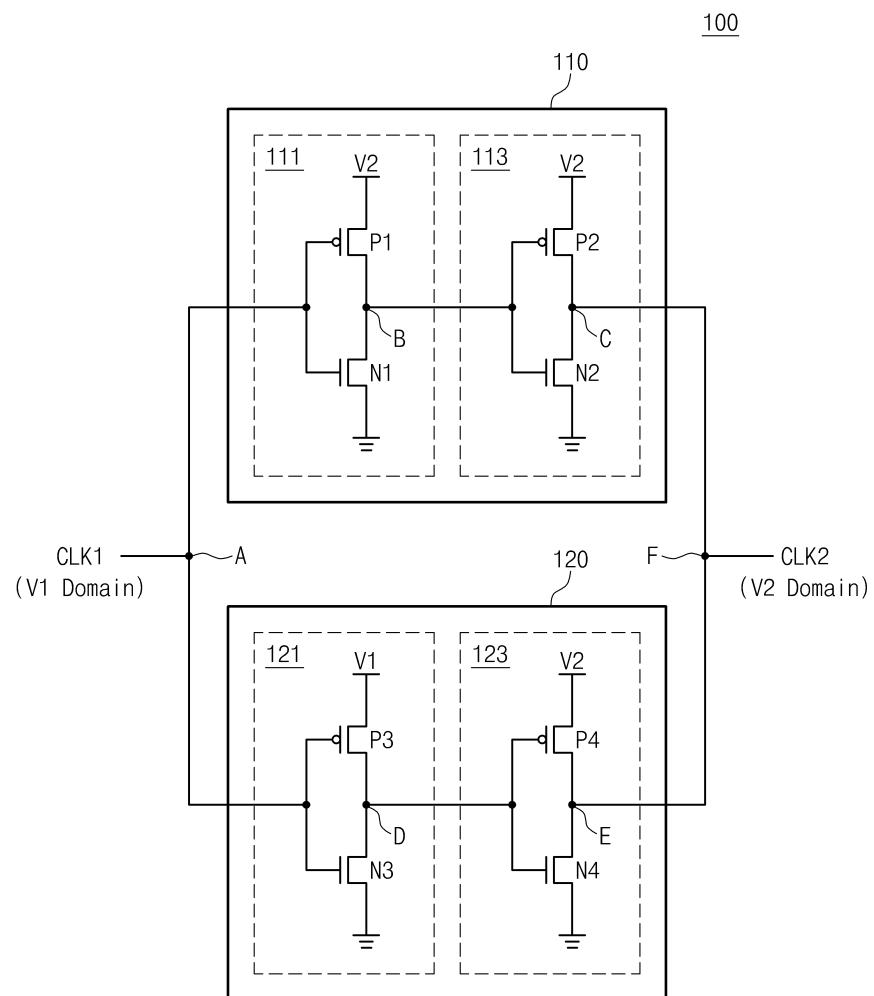

도 2는 본 발명의 실시 예에 따른 레벨 변환기를 보여주는 회로도이다.

도 3은 제 1 클록이 상승할 때, 도 2를 참조하여 설명된 제 1 내지 제 4 인버터들의 동작들을 보여주는 도면이다.

도 4는 제 1 클록이 하강할 때, 도 2를 참조하여 설명된 제 1 내지 제 4 인버터들의 동작들을 보여주는 도면이다.

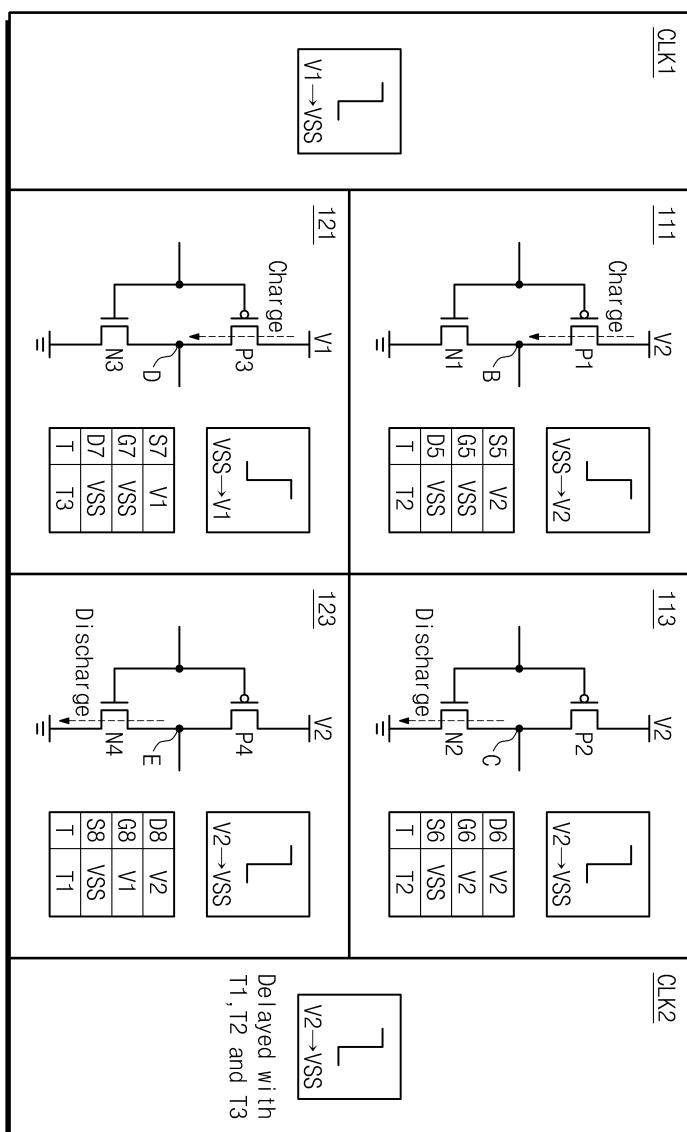

도 5는 도 1 내지 도 4를 참조하여 설명된 레벨 변환기의 입력 클록 및 출력 클록을 보여주는 타이밍도이다.

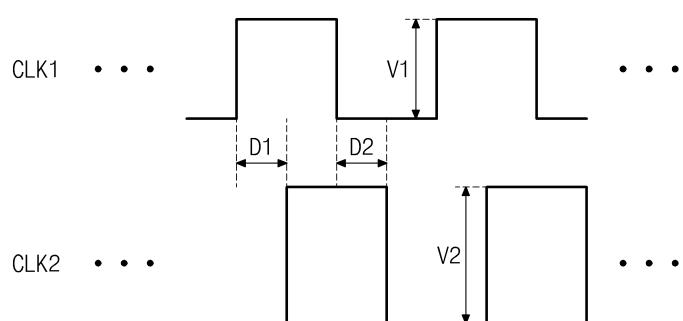

도 6은 도 1 내지 도 5를 참조하여 설명된 레벨 변환기를 포함하는 시스템-온-칩을 보여주는 블록도이다.

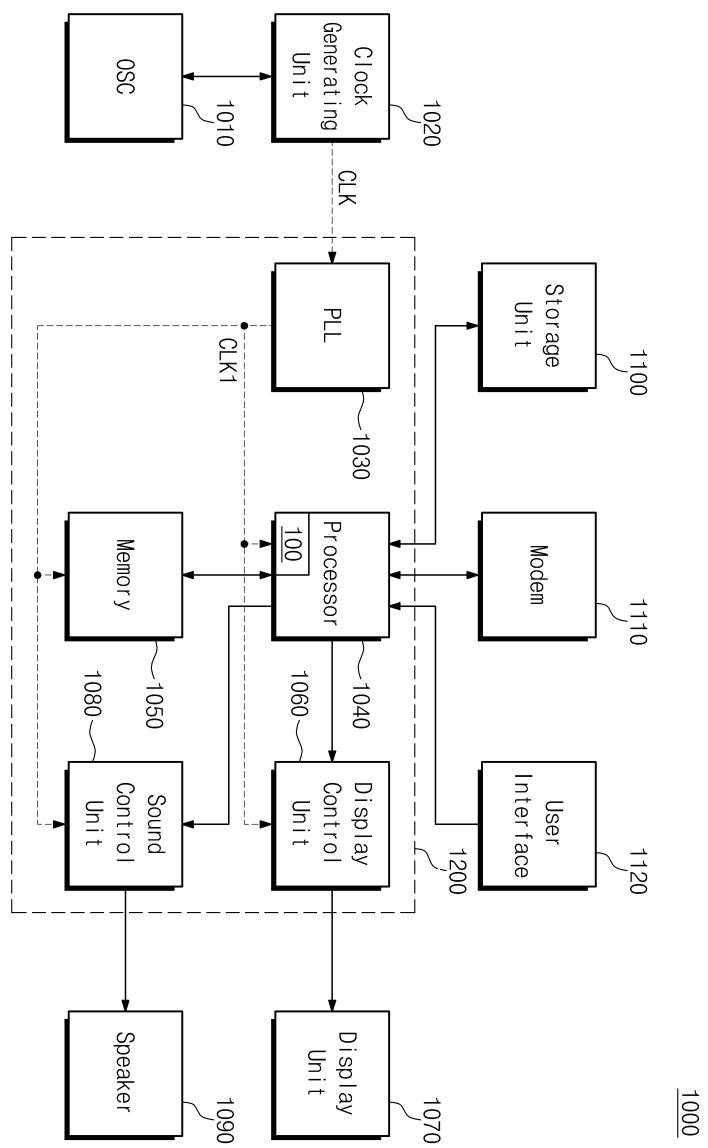

도 7은 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 1 예를 보여주는 블록도이다.

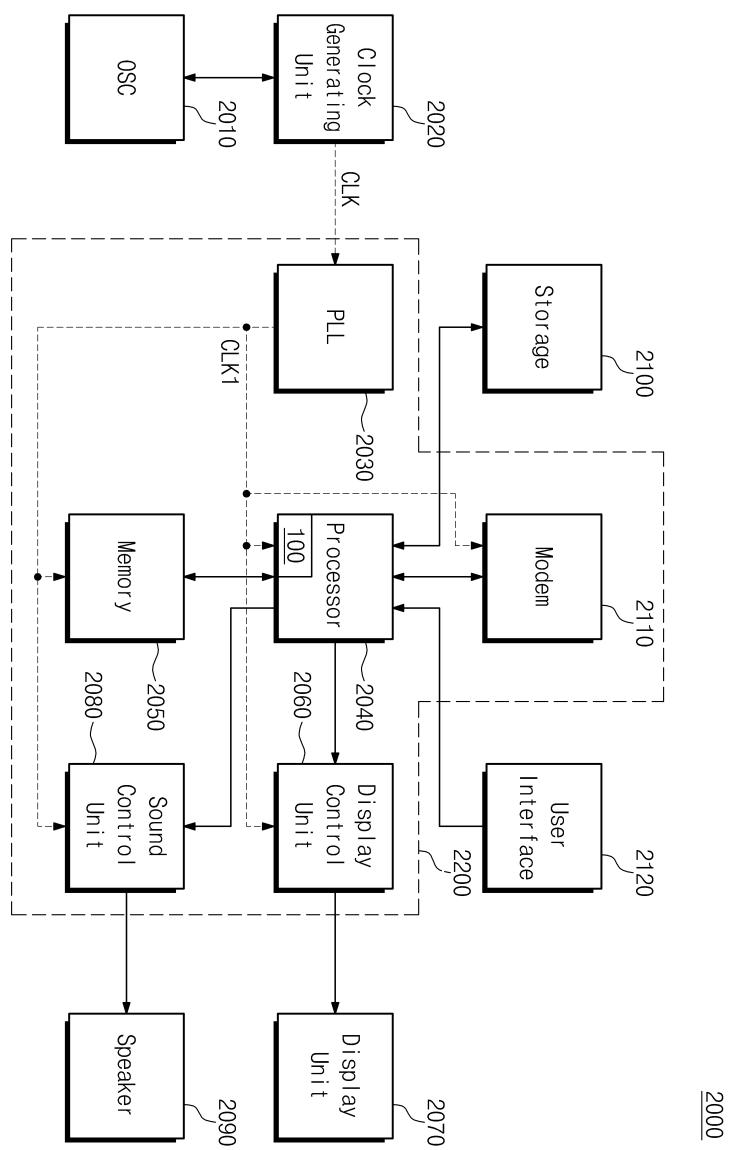

도 8은 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 2 예를 보여주는 블록도이다.

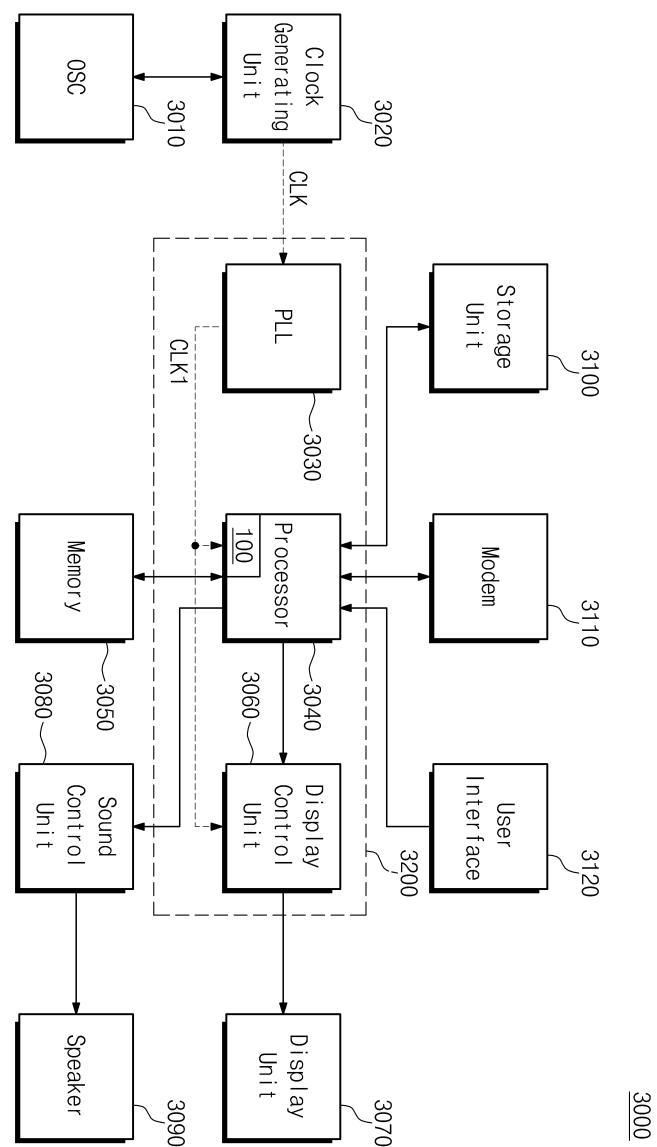

도 9는 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 3 예를 보여주는 블록도이다.

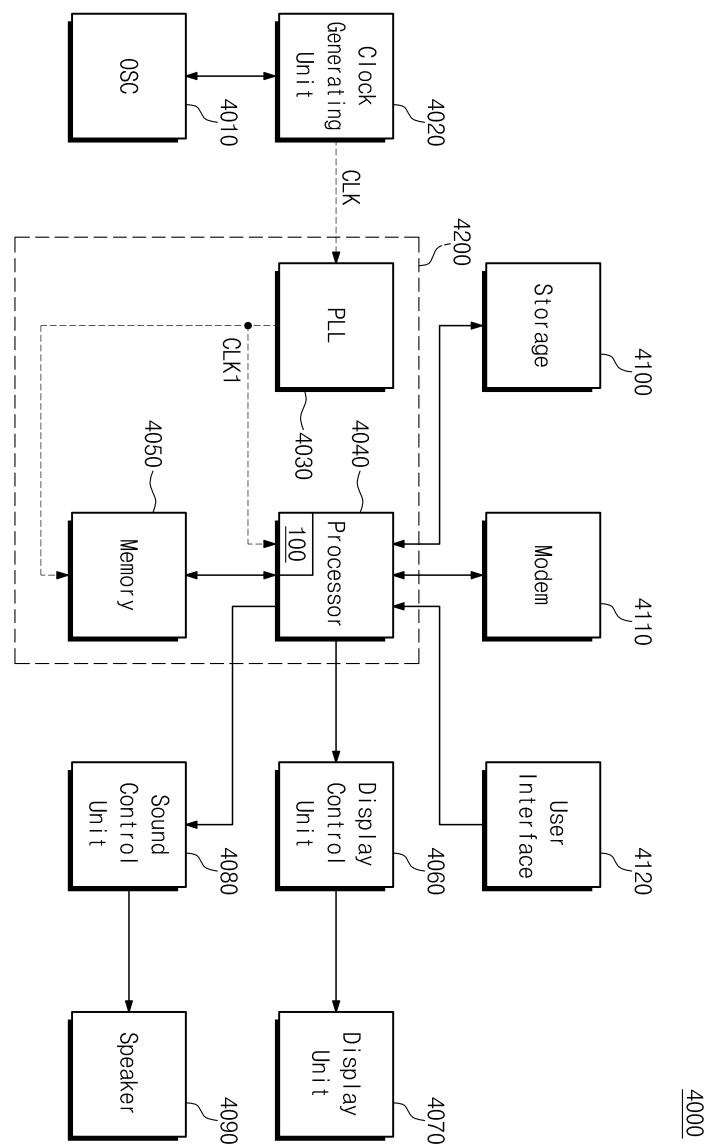

도 10은 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 4 예를 보여주는 블록도이다.

도 11은 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 5 예를 보여주는 블록도이다.

도 12는 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 6 예를 보여주는 블록도이다.

도 13은 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 7 예를 보여주는 블록도이다.

도 14는 본 발명의 실시 예에 따른 레벨 변환기를 포함하는 멀티미디어 장치의 제 8 예를 보여주는 블록도이다.

도 15는 본 발명의 실시 예에 따른 스마트 폰을 보여주는 도면이다.

도 16은 본 발명의 실시 예에 따른 태블릿 컴퓨터를 보여주는 도면이다.

도 17은 본 발명의 실시 예에 따른 모바일 컴퓨터를 보여주는 도면이다.

도 18은 본 발명의 실시 예에 따른 컴퓨터를 보여주는 도면이다.

도 19는 본 발명의 실시 예에 따른 텔레비전을 보여주는 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0029]

이하에서, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 실시 예를 첨부된 도면을 참조하여 설명하기로 한다.

[0030]

도 1은 본 발명의 실시 예에 따른 레벨 변환기(100)를 보여주는 블록도이다. 도 1을 참조하면, 레벨 변환기(100)는 제 1 전압 변환 회로(110) 및 제 2 전압 변환 회로(120)를 포함한다. 제 1 및 제 2 전압 변환 회로들(110, 120)은 입력 노드(A) 및 출력 노드(F) 사이에 병렬 연결된다.

[0031]

제 1 전압 변환 회로(110)는 입력 노드(A)를 통해 제 1 전압(V1)에 대응하는 제 1 전압 도메인의 제 1 클록(CLK1)을 수신한다. 제 1 클록(CLK1)은 제 1 전압(V1)의 스윙(swing) 폭을 가질 수 있다. 제 1 전압 변환 회로(110)는 수신된 제 1 클록(CLK1)에 기반하여, 제 2 전압(V2)에 대응하는 제 2 전압 도메인의 신호를 발생한다. 제 2 클록(CLK2)은 제 2 전압(V2)의 스윙 폭을 가질 수 있다.

[0032]

제 1 전압 변환 회로(110)는 제 1 및 제 2 인버터들(111, 113)을 포함한다. 제 1 인버터(111)는 제 1 클록(CLK1)에 응답하여 제 2 전압(V2) 및 접지 전압(VSS) 중 하나를 출력하도록 구성된다. 제 2 인버터(113)는 제 1 인버터(111)의 출력에 응답하여 제 2 전압(V2) 및 접지 전압(VSS) 중 하나를 출력하도록 구성된다. 즉, 제 2 인버터(113)는 제 1 클록(CLK1)에 동기되는 제 2 전압 도메인의 신호를 출력한다.

[0033]

제 2 전압 변환 회로(120)는 입력 노드(A)를 통해 제 1 전압 도메인의 제 1 클록(CLK1)을 수신한다. 제 1 전압 변환 회로(110)는 수신된 제 1 클록(CLK1)에 기반하여 제 2 전압 도메인의 신호를 발생한다.

[0034]

제 2 전압 변환 회로(120)는 제 1 전압 변환 회로(110)와 동일한 구조를 갖는다. 제 2 전압 변환 회로(120)는 제 3 및 제 4 인버터들(121, 123)을 포함한다. 제 3 인버터(121)는 제 1 클록(CLK1)에 응답하여 제 1 전압(V1) 및 접지 전압(VSS) 중 하나를 출력하도록 구성된다. 제 4 인버터(123)는 제 3 인버터(121)의 출력에 응답하여 제 2 전압(V2) 및 접지 전압(VSS) 중 하나를 출력하도록 구성된다. 즉, 제 4 인버터(123)는 제 1 클록(CLK1)에 동기되는 제 2 전압 도메인의 신호를 출력한다.

[0035]

제 1 및 제 2 전압 변환 회로들(110, 120)은 출력 노드(F)에서 혼합된다. 제 1 전압 변환 회로(110)는 제 1 클록(CLK1)에 동기되는 제 2 전압 도메인의 신호를 출력한다. 제 2 전압 변환 회로(120) 또한 제 1 클록(CLK1)에 동기되는 제 2 전압 도메인의 신호를 출력한다. 즉, 출력 노드(F)에서, 제 1 클록(CLK1)에 동기되는 제 2 전압 도메인의 신호가 생성된다. 출력 노드(F)의 신호는 제 2 전압 도메인의 제 2 클록(CLK2)으로 출력된다.

[0036]

도 2는 본 발명의 실시 예에 따른 레벨 변환기(100)를 보여주는 회로도이다. 예시적으로, 도 1을 참조하여 설명된 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 내부 회로들이 도시되어 있다. 예시적으로, 제 1 내지

제 4 인버터들(111, 113, 121, 123) 각각은 씨모스(CMOS) 인버터들일 수 있다. 그러나, 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 내부 회로들은 도 2에 도시된 회로들에 한정되지 않는다.

[0037] 도 1 및 도 2를 참조하면, 제 1 인버터(111)는 제 1 PMOS 트랜지스터(P1) 및 제 1 NMOS 트랜지스터(N1)를 포함한다. 제 1 PMOS 트랜지스터(P1)의 게이트는 입력 노드(A)에 연결된다. 제 1 PMOS 트랜지스터(P1)의 일단에 제 2 전압(V2)이 공급되고, 타단은 출력 노드(B)에 연결된다. 제 1 NMOS 트랜지스터(N1)의 게이트는 입력 노드(A)에 연결된다. 제 1 NMOS 트랜지스터(N1)의 일단은 접지 노드에 연결되고, 타단은 출력 노드(B)에 연결된다.

[0038] 제 2 인버터(113)는 제 1 인버터(111)와 동일한 구조를 갖는다. 제 2 인버터(113)는 제 2 PMOS 트랜지스터(P2) 및 제 2 NMOS 트랜지스터(N2)를 포함한다. 제 2 PMOS 트랜지스터(P2)의 게이트는 제 1 인버터(111)의 출력 노드(B)에 연결된다. 제 2 PMOS 트랜지스터(P2)의 일단에 제 2 전압(V2)이 공급되고, 타단은 출력 노드(C)에 연결된다. 제 2 NMOS 트랜지스터(N2)의 게이트는 제 1 인버터(111)의 출력 노드(B)에 연결된다. 제 2 NMOS 트랜지스터(N2)의 일단은 접지 노드에 연결되고, 타단은 출력 노드(C)에 연결된다.

[0039] 제 3 인버터(121)는 제 1 인버터(111)와 동일한 구조를 갖는다. 제 3 인버터(121)는 제 3 PMOS 트랜지스터(P3) 및 제 3 NMOS 트랜지스터(N3)를 포함한다. 제 3 PMOS 트랜지스터(P3)의 게이트는 입력 노드(A)에 연결된다. 제 3 PMOS 트랜지스터(P3)의 일단에 제 1 전압(V1)이 공급되고, 타단은 출력 노드(D)에 연결된다. 제 3 NMOS 트랜지스터(N3)의 게이트는 입력 노드(A)에 연결된다. 제 3 NMOS 트랜지스터(N3)의 일단은 접지 노드에 연결되고, 타단은 출력 노드(D)에 연결된다.

[0040] 제 4 인버터(123)는 제 1 인버터(111)와 동일한 구조를 갖는다. 제 4 인버터(123)는 제 4 PMOS 트랜지스터(P4) 및 제 4 NMOS 트랜지스터(N4)를 포함한다. 제 4 PMOS 트랜지스터(P4)의 게이트는 제 3 인버터(121)의 출력 노드(D)에 연결된다. 제 4 PMOS 트랜지스터(P4)의 일단에 제 2 전압(V2)이 공급되고, 타단은 출력 노드(E)에 연결된다. 제 4 NMOS 트랜지스터(N4)의 게이트는 제 3 인버터(121)의 출력 노드(D)에 연결된다. 제 4 NMOS 트랜지스터(N4)의 일단은 접지 노드에 연결되고, 타단은 출력 노드(E)에 연결된다.

[0041] 도 3은 제 1 클록(CLK1)이 상승할 때, 도 2를 참조하여 설명된 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 동작들을 보여주는 도면이다. 도 2 및 도 3을 참조하면, 제 1 클록(CLK1)은 접지 전압(VSS)으로부터 제 1 전압(V1)으로 상승한다. 제 1 클록(CLK1)이 제 1 전압(V1)일 때, 제 1 인버터(111)의 제 1 PMOS 트랜지스터(P1)는 턴 오프 되고, 제 1 NMOS 트랜지스터(N1)는 턴 온 된다. 즉, 제 1 인버터(111)의 출력 노드(B)는 접지 노드와 연결된다.

[0042] 제 1 클록(CLK1)이 접지 전압(VSS)일 때, 제 1 인버터(111)의 출력 노드(B)에 제 1 PMOS 트랜지스터(P1)를 통해 제 2 전압(V2)이 공급된다. 따라서, 제 1 클록(CLK1)이 접지 전압(VSS)으로부터 제 1 전압(V1)으로 상승할 때, 제 1 인버터(111)의 출력 노드(B)의 전압은 제 2 전압(V2)으로부터 접지 전압(VSS)으로 방전된다.

[0043] 구체적으로, 제 1 NMOS 트랜지스터(N1)의 드레인(D1)에 제 2 전압(V2)이 인가되고, 게이트(G1)에 제 1 전압(V1)이 인가되고, 그리고 소스(S1)에 접지 전압(VSS)이 인가된 상태에서, 제 1 NMOS 트랜지스터(N1)의 채널을 통해 출력 노드(B)의 전압이 방전된다. 이때, 제 1 인버터(111)의 출력 노드(B)의 전압이 접지 전압(VSS)으로 방전되는데 소요되는 시간은 제 1 시간(T1)일 수 있다. 제 1 시간(T1)은 제 1 인버터(111)의 출력 노드(B)의 전압이 제 1 클록(CLK1)의 상승 에지(rising edge)에 동기되어 하강할 때까지의 지연 시간일 수 있다.

[0044] 제 1 인버터(111)의 출력 전압이 접지 전압(VSS)일 때, 제 2 인버터(113)의 제 2 NMOS 트랜지스터(N2)는 턴 오프 되고, 제 2 PMOS 트랜지스터(P2)는 턴 온 된다. 즉, 제 2 인버터(113)의 출력 노드(C)에 제 2 전압(V2)이 공급된다.

[0045] 제 1 인버터(111)의 출력 전압이 제 2 전압(V2)일 때, 제 2 인버터(113)의 출력 노드(C)에 제 2 NMOS 트랜지스터(N2)를 통해 접지 전압(VSS)이 공급된다. 따라서, 제 1 인버터(111)의 출력 전압이 제 2 전압(V2)으로부터 접지 전압(VSS)으로 하강할 때, 제 2 인버터(113)의 출력 노드(C)의 전압은 접지 전압(VSS)으로부터 제 2 전압(V2)으로 충전된다.

[0046] 구체적으로, 제 2 PMOS 트랜지스터(P2)의 소스(S2)에 제 2 전압(V2)이 인가되고, 게이트(G2)에 접지 전압(VSS)이 인가되고, 그리고 드레인(D2)에 접지 전압(VSS)이 인가된 상태에서, 제 2 PMOS 트랜지스터(P2)의 채널을 통해 출력 노드(C)의 전압이 충전된다. 이때, 제 2 인버터(113)의 출력 노드(C)의 전압이 제 2 전압(V2)으로 충전되는데 소요되는 시간은 제 2 시간(T2)일 수 있다. 제 2 시간(T2)은 제 2 인버터(113)의 출력 노드(C)의 전압이 제 1 인버터(111)의 출력 전압의 하강 에지(falling edge)에 동기되어 상승할 때까지의 지연

시간일 수 있다.

[0047] 제 1 클록(CLK1)은 접지 전압(VSS)으로부터 제 1 전압(V1)으로 상승한다. 제 1 클록(CLK1)이 제 1 전압(V1)일 때, 제 3 인버터(121)의 제 3 PMOS 트랜지스터(P1)는 턴 오프 되고, 제 3 NMOS 트랜지스터(N3)는 턴 온 된다. 즉, 제 3 인버터(121)의 출력 노드(D)에 접지 전압(VSS)이 공급된다.

[0048] 제 1 클록(CLK1)이 접지 전압(VSS)일 때, 제 3 인버터(121)의 출력 노드(D)에 제 3 PMOS 트랜지스터(P3)를 통해 제 1 전압(V1)이 공급된다. 따라서, 제 1 클록(CLK1)이 접지 전압(VSS)으로부터 제 1 전압(V1)으로 상승할 때, 제 3 인버터(121)의 출력 노드(D)의 전압은 제 1 전압(V1)으로부터 접지 전압(VSS)으로 방전된다.

[0049] 구체적으로, 제 3 NMOS 트랜지스터(N3)의 드레인(D3)에 제 1 전압(V1)이 인가되고, 게이트(G3)에 제 1 전압(V1)이 인가되고, 그리고 소스(S3)에 접지 전압(VSS)이 인가된 상태에서, 제 3 NMOS 트랜지스터(N3)의 채널을 통해 출력 노드(D)의 전압이 방전된다. 이때, 제 3 인버터(121)의 출력 노드(D)의 전압은 접지 전압(VSS)으로 방전되는데 소요되는 시간은 제 3 시간(T3)일 수 있다. 제 3 시간(T3)은 제 3 인버터(121)의 출력 노드(D)의 전압이 제 1 클록(CLK1)의 상승 에지(falling edge)에 동기되어 하강할 때까지의 지연 시간일 수 있다.

[0050] 제 3 인버터(121)의 출력이 접지 전압(VSS)일 때, 제 4 인버터(123)의 제 4 NMOS 트랜지스터(N4)는 턴 오프 되고, 제 4 PMOS 트랜지스터(P4)는 턴 온 된다. 즉, 제 4 인버터(123)의 출력 노드(E)에 제 2 전압(V2)이 공급된다.

[0051] 제 3 인버터(121)의 출력 전압이 제 1 전압(V1)일 때, 제 4 인버터(123)의 출력 노드(E)에 제 4 NMOS 트랜지스터(N4)를 통해 접지 전압(VSS)이 공급된다. 따라서, 제 3 인버터(121)의 출력 전압이 제 1 전압(V1)으로부터 접지 전압(VSS)으로 하강할 때, 제 4 인버터(123)의 출력 노드(E)의 전압은 접지 전압(VSS)으로부터 제 2 전압(V2)으로 충전된다.

[0052] 구체적으로, 제 4 PMOS 트랜지스터(P4)의 소스(S4)에 제 2 전압(V2)이 인가되고, 게이트(G4)에 접지 전압(VSS)이 인가되고, 그리고 드레인(D4)에 접지 전압(VSS)이 인가된 상태에서, 제 4 PMOS 트랜지스터(P4)의 채널을 통해 출력 노드(E)의 전압이 충전된다. 이때, 제 4 인버터(123)의 제 4 PMOS 트랜지스터(P4)의 바이어스 조건은 제 2 인버터(113)의 제 2 PMOS 트랜지스터(P2)의 바이어스 조건과 동일하다. 따라서, 제 4 인버터(123)의 출력 노드(E)의 전압이 제 2 전압(V2)으로 충전되는데 소요되는 시간은 제 2 시간(T2)일 수 있다. 제 2 시간(T2)은 제 4 인버터(123)의 출력 노드(E)의 전압이 제 3 인버터(121)의 출력 전압의 하강 에지에 동기되어 상승할 때까지의 지연 시간일 수 있다.

[0053] 도 4는 제 1 클록(CLK1)이 하강할 때, 도 2를 참조하여 설명된 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 동작들을 보여주는 도면이다. 도 2 및 도 4를 참조하면, 제 1 클록(CLK1)은 제 1 전압(V1)으로부터 접지 전압(VSS)으로 하강한다. 제 1 클록(CLK1)이 접지 전압(VSS)일 때, 제 1 인버터(111)의 제 1 NMOS 트랜지스터(N1)는 턴 오프 되고, 제 1 PMOS 트랜지스터(P1)는 턴 온 된다. 즉, 제 1 인버터(111)의 출력 노드(B)에 제 2 전압(V2)이 공급된다.

[0054] 제 1 클록(CLK1)이 제 1 전압(V1)일 때, 제 1 인버터(111)의 출력 노드(B)에 제 1 NMOS 트랜지스터(N1)를 통해 접지 전압(VSS)이 공급된다. 따라서, 제 1 클록(CLK1)이 제 1 전압(V1)으로부터 접지 전압(VSS)으로 하강할 때, 제 1 인버터(111)의 출력 노드(B)의 전압은 접지 전압(VSS)으로부터 제 2 전압(V2)으로 충전된다.

[0055] 구체적으로, 제 1 PMOS 트랜지스터(P1)의 소스(S5)에 제 2 전압(V2)이 인가되고, 게이트(G6)에 접지 전압(VSS)이 인가되고, 그리고 드레인(D6)에 접지 전압(VSS)이 인가된 상태에서, 제 1 PMOS 트랜지스터(P1)의 채널을 통해 출력 노드(B)의 전압이 충전된다. 제 1 PMOS 트랜지스터(P1)의 바이어스 조건은 도 3을 참조하여 설명된 제 2 인버터(113)의 제 2 PMOS 트랜지스터(P2)의 바이어스 조건과 동일하다. 따라서, 제 1 인버터(111)의 출력 노드(B)의 전압이 제 2 전압(V2)으로 충전되는데 소요되는 시간은 제 2 시간(T2)일 수 있다. 제 2 시간(T2)은 제 1 인버터(111)의 출력 노드(B)의 전압이 제 1 클록(CLK1)의 하강 에지에 동기되어 상승할 때까지의 지연 시간일 수 있다.

[0056] 제 1 인버터(111)의 출력 전압이 제 2 전압(V2)일 때, 제 2 인버터(113)의 제 2 PMOS 트랜지스터(P2)는 턴 오프 되고, 제 2 NMOS 트랜지스터(N2)는 턴 온 된다. 즉, 제 2 인버터(113)의 출력 노드(C)에 접지 전압(VSS)이 공급된다.

[0057] 제 1 인버터(111)의 출력 전압이 접지 전압(VSS)일 때, 제 2 인버터(113)의 출력 노드(C)에 제 2 PMOS 트랜지스터(P2)를 통해 제 2 전압(V2)이 공급된다. 따라서, 제 1 인버터(111)의 출력 전압이 접지 전압(VSS)으로부터 제 2 전압(V2)으로 상승한 때에, 제 2 인버터(113)의 출력 노드(C)의 전압은 제 2 전압(V2)으로부터 접지

전압(VSS)으로 방전된다.

[0058] 구체적으로, 제 2 NMOS 트랜지스터(N2)의 드레인(D7)에 제 2 전압(V2)이 인가되고, 게이트(G7)에 제 2 전압(V2)이 인가되고, 그리고 소스(S7)에 접지 전압(VSS)이 인가된 상태에서, 제 2 NMOS 트랜지스터(N2)의 채널을 통해 출력 노드(C)의 전압이 방전된다.

[0059] 이때, 트랜지스터의 종류가 NMOS 트랜지스터인 것을 제외하면, 제 2 NMOS 트랜지스터(N2)의 바이어스 조건은 제 1 인버터(111)의 제 1 PMOS 트랜지스터(P1)의 바이어스 조건과 동일하다. 제 2 NMOS 트랜지스터(N2)의 게이트-소스 전압 차이는 제 2 전압(V2)이고, 제 1 PMOS 트랜지스터(P1)의 게이트-소스 전압 차이 또한 제 2 전압(V2)이다. 제 2 NMOS 트랜지스터(N2)의 드레인-소스 전압 차이는 제 2 전압(V2)이고, 제 1 PMOS 트랜지스터(P1)의 드레인-소스 전압 차이 또한 제 2 전압(V2)이다.

[0060] 제 1 내지 제 4 인버터들(111, 113, 121, 123) 각각은 하나의 PMOS 트랜지스터 및 하나의 NMOS 트랜지스터를 포함한다. 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 입력 전압들이 저레벨일 때, 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 출력 전압들은 PMOS 트랜지스터들(P1~P4)에 의해 생성된다. 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 입력 전압들이 고레벨일 때, 제 1 내지 제 4 인버터들(111, 113, 121, 123)의 출력 전압들은 NMOS 트랜지스터들(N1~N4)에 의해 생성된다.

[0061] 대칭적인 저레벨 출력 및 고레벨 출력을 갖도록, 제 1 내지 제 4 인버터들(111, 113, 121, 123)이 형성될 수 있다. 예를 들면, 고레벨을 출력할 때 충전하는 전류량과 저레벨을 출력할 때 방전하는 전류량이 평준화되도록, 제 1 내지 제 4 인버터들(111, 113, 121, 123)이 형성될 수 있다. 동일한 바이어스 조건에서, 제 1 내지 제 4 NMOS 트랜지스터들(N1~N4)은 제 1 내지 제 4 PMOS 트랜지스터들(P1~P4)과 동일하게 동작하도록 형성될 수 있다. 동일한 바이어스 조건에서, 제 2 NMOS 트랜지스터(N2)를 통해 흐르는 전류의 양은 제 1 PMOS 트랜지스터(P1)를 통해 흐르는 전류의 양과 같을 수 있다.

[0062] 제 2 NMOS 트랜지스터(N2)의 바이어스 조건이 제 1 PMOS 트랜지스터(P1)의 바이어스 조건과 동일하므로, 제 2 인버터(113)의 출력 노드(C)의 전압이 접지 전압(VSS)으로 방전되는데 소요되는 시간은 제 2 시간(T2)일 수 있다. 제 2 시간(T2)은 제 2 인버터(113)의 출력 노드(C)의 전압이 제 1 인버터(111)의 출력 전압의 상승 예지에 동기되어 하강할 때까지의 지연 시간일 수 있다.

[0063] 제 1 클록(CLK1)이 접지 전압(VSS)일 때, 제 3 인버터(121)의 제 3 NMOS 트랜지스터(N1)는 턴 오프 되고, 제 3 PMOS 트랜지스터(P3)는 턴 온 된다. 즉, 제 3 인버터(121)의 출력 노드(D)에 제 1 전압(V1)이 공급된다.

[0064] 제 1 클록(CLK1)이 제 1 전압(V1)일 때, 제 3 인버터(121)의 출력 노드(D)에 제 3 NMOS 트랜지스터(N3)를 통해 접지 전압(VSS)이 공급된다. 따라서, 제 1 클록(CLK1)이 제 1 전압(V1)으로부터 접지 전압(VSS)으로 하강할 때, 제 3 인버터(121)의 출력 노드(D)의 전압은 접지 전압(VSS)으로부터 제 1 전압(V1)으로 충전된다.

[0065] 구체적으로, 제 3 PMOS 트랜지스터(P3)의 소스(S7)에 제 1 전압(V1)이 인가되고, 게이트(G7)에 접지 전압(VSS)이 인가되고, 그리고 드레인(D7)에 접지 전압(VSS)이 인가된 상태에서, 제 3 PMOS 트랜지스터(P3)의 채널을 통해 출력 노드(D)의 전압이 충전된다.

[0066] 이때, 트랜지스터의 종류가 PMOS 트랜지스터인 것을 제외하면, 제 3 PMOS 트랜지스터(P2)의 바이어스 조건은 제 3 PMOS 트랜지스터(P3)의 바이어스 조건과 동일하다. 제 3 PMOS 트랜지스터(P3)의 게이트-소스 전압 차이는 제 1 전압(V1)이고, 제 3 NMOS 트랜지스터(N3)의 게이트-소스 전압 차이 또한 제 1 전압(V1)이다. 제 3 PMOS 트랜지스터(P3)의 드레인-소스 전압 차이는 제 1 전압(V1)이고, 제 3 NMOS 트랜지스터(N3)의 드레인-소스 전압 차이 또한 제 1 전압(V1)이다.

[0067] 따라서, 제 3 인버터(121)의 출력 노드(D)의 전압이 제 1 전압(V1)으로 충전되는데 소요되는 시간은 제 3 시간(T3)일 수 있다. 제 3 시간(T3)은 제 3 인버터(121)의 출력 노드(D)의 전압이 제 1 클록(CLK1)의 하강 예지에 동기되어 상승할 때까지의 지연 시간일 수 있다.

[0068] 제 3 인버터(121)의 출력 전압이 제 1 전압(V1)일 때, 제 4 인버터(123)의 제 4 PMOS 트랜지스터(P4)는 턴 오프 되고, 제 4 NMOS 트랜지스터(N4)는 턴 온 된다. 즉, 제 4 인버터(123)의 출력 노드(E)에 접지 전압(VSS)이 공급된다.

[0069] 제 3 인버터(121)의 출력 전압이 접지 전압(VSS)일 때, 제 4 인버터(123)의 출력 노드(E)에 제 4 PMOS 트랜지스터(P4)를 통해 제 2 전압(V2)이 공급된다. 따라서, 제 3 인버터(121)의 출력 전압이 접지 전압(VSS)으로부터 제 1 전압(V1)으로 상승할 때, 제 4 인버터(123)의 출력 노드(E)의 전압은 제 2 전압(V2)으로부터 접지 전

암(VSS)으로 방전된다.

[0070] 구체적으로, 제 4 NMOS 트랜지스터(N4)의 드레인(D8)에 제 2 전압(V2)이 인가되고, 게이트(G8)에 제 1 전압(V1)이 인가되고, 그리고 소스(S8)에 접지 전압(VSS)이 인가된 상태에서, 제 4 PMOS 트랜지스터(P4)의 채널을 통해 출력 노드(E)의 전압이 방전된다.

[0071] 이때, 제 4 인버터(123)의 제 4 NMOS 트랜지스터(N4)의 바이어스 조건은 도 3을 참조하여 설명된 제 1 NMOS 트랜지스터(N1)의 바이어스 조건과 동일하다. 따라서, 제 4 인버터(123)의 출력 노드(E)의 전압이 접지 전압(VSS)으로 방전되는데 소요되는 시간은 제 1 시간(T1)일 수 있다. 제 1 시간(T1)은 제 4 인버터(123)의 출력 노드(E)의 전압이 제 3 인버터(121)의 출력 전압의 상승 에지에 동기되어 하강할 때까지의 지연 시간일 수 있다.

[0072] 도 5는 도 1 내지 도 4를 참조하여 설명된 레벨 변환기(100)의 입력 클록(CLK1) 및 출력 클록(CLK2)을 보여주는 타이밍도이다. 도 1 내지 도 5를 참조하면, 제 1 클록(CLK1)이 레벨 변환기(100)에 입력된다. 제 1 클록(CLK1)은 제 1 전압(V1)의 스윙 폭을 갖는다. 제 1 클록(CLK1)은 주기적으로 반복되는 상승 에지 및 하강 에지를 갖는다.

[0073] 제 2 클록(CLK2)이 레벨 변환기(100)로부터 출력된다. 제 2 클록(CLK2)은 제 2 전압(V2)의 스윙 폭을 갖는다. 제 1 클록(CLK1)의 상승 에지에 동기되어, 제 2 클록(CLK2)이 상승한다. 제 2 클록(CLK2)은 제 1 전압 변환 회로(110)의 제 1 및 제 2 인버터들(111, 113)의 충전과 방전, 그리고 제 2 전압 변환 회로(120)의 제 3 및 제 4 인버터들(121, 123)의 충전과 방전에 의해 상승한다.

[0074] 도 3을 참조하여 설명된 바와 같이, 제 1 클록(CLK1)이 상승하고 제 1 시간(T1) 후에, 제 1 인버터(111)의 출력 전압이 감소하여 접지 전압(VSS)에 도달한다. 제 1 인버터(111)의 출력 전압이 하강하고 제 2 시간(T2) 후에, 제 2 인버터(113)의 출력 전압이 증가하여 제 2 전압(V2)에 도달한다. 제 1 클록(CLK1)이 상승하고 제 3 시간(T3) 후에, 제 3 인버터(121)의 출력 전압이 하강하여 접지 전압(VSS)에 도달한다. 제 3 인버터(121)의 출력 전압이 하강하고 제 2 시간(T2) 후에, 제 4 인버터(123)의 출력 전압이 상승하여 제 2 전압(V2)에 도달한다.

[0075] 제 2 및 제 4 인버터들(113, 123)의 출력 전압들이 혼합되어 제 2 클록(CLK2)이 형성된다. 즉, 제 1 클록(CLK1)의 상승 에지와 제 2 클록(CLK2)의 상승 에지 사이의 지연(D1)은 제 1 시간(T1), 제 2 시간(T2), 그리고 제 3 시간(T3)이 혼합되어 발생된다.

[0076] 도 4를 참조하여 설명된 바와 같이, 제 1 클록(CLK1)이 하강하고 제 2 시간(T2) 후에, 제 1 인버터(111)의 출력 전압이 상승하여 제 2 전압(V2)에 도달한다. 제 1 인버터(111)의 출력 전압이 상승하고 제 2 시간(T2) 후에, 제 2 인버터(113)의 출력 전압이 하강하여 접지 전압(VSS)에 도달한다. 제 1 클록(CLK1)이 하강하고 제 3 시간(T3) 후에, 제 3 인버터(121)의 출력 전압이 상승하여 제 1 전압(V1)에 도달한다. 제 3 인버터(121)의 출력 전압이 상승하고 제 1 시간(T1) 후에, 제 4 인버터(123)의 출력 전압이 하강하여 접지 전압(VSS)에 도달한다.

[0077] 제 2 및 제 4 인버터들(113, 123)의 출력 전압들이 혼합되어, 제 2 클록(CLK2)이 형성된다. 즉, 제 1 클록(CLK)의 하강 에지와 제 2 클록(CLK2)의 하강 에지 사이의 지연(D2)은 제 1 시간(T1), 제 2 시간(T2), 그리고 제 3 시간(T3)이 혼합되어 발생된다.

[0078] 상술된 바와 같이, 제 1 및 제 2 클록들(CLK1, CLK2)의 상승 에지를 사이의 지연(D1)을 유발하는 시간 요인들(T1, T2, T3)은 하강 에지를 사이의 지연(D2)을 유발하는 시간 요인들(T1, T2, T3)과 동일하다. 따라서, 제 1 및 제 2 클록들(CLK1, CLK2)의 상승 에지를 사이의 지연(D1)과 하강 에지를 사이의 지연(D2)은 동일할 수 있다.

[0079] 상승 에지를 사이의 지연(D1)과 하강 에지를 사이의 지연(D2)이 서로 다른 경우, 제 2 클록(CLK2)의 한 주기의 고레벨 구간과 저레벨 구간의 비율이 가변될 수 있다.

[0080] 예시적으로, 상승 에지를 사이의 지연(D1)이 하강 에지를 사이의 지연(D2)보다 큰 경우, 제 2 클록(CLK2)의 한 주기의 고레벨 구간의 비율은 제 1 클록(CLK1)의 한 주기의 고레벨 구간의 비율보다 감소한다. 반대로, 하강 에지를 사이의 지연(D2)이 상승 에지를 사이의 지연(D1)보다 큰 경우, 제 2 클록(CLK2)의 한 주기의 저레벨 구간의 비율은 제 1 클록(CLK1)의 한 주기의 저레벨 구간의 비율보다 감소한다. 본 발명의 실시 예들에 따르면, 레벨 변환기(100)는 고레벨 및 저레벨 구간들의 비율들(duty ratio)을 유지하며, 입력되는 제 1 클록(CLK1)과 다른 전압 도메인의 제 2 클록(CLK2)을 발생할 수 있다. 따라서, 레벨 변환기(100)의 출력 클록의

신뢰성이 향상될 수 있다.

[0081] 예시적으로, 제 2 전압(V2)은 제 1 전압(V1)보다 낮거나 높을 수 있다.

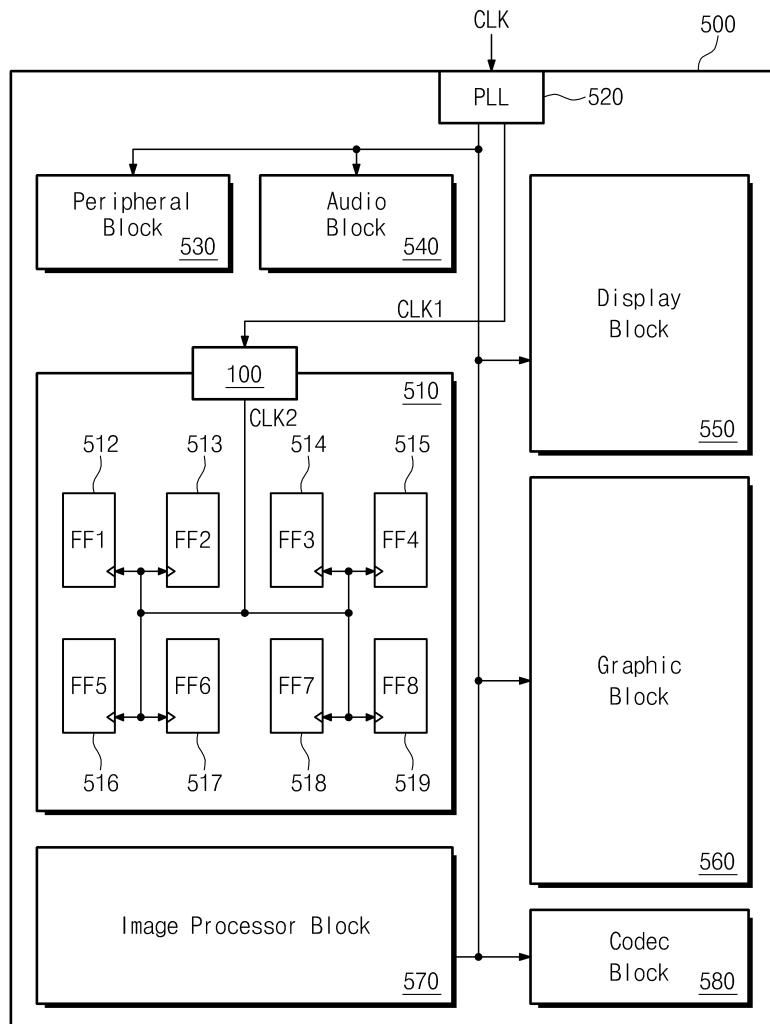

[0082] 도 6은 도 1 내지 도 5를 참조하여 설명된 레벨 변환기(100)를 포함하는 시스템-온-칩(500, SOC, System-On-Chip)을 보여주는 블록도이다. 도 6을 참조하면, 시스템-온-칩(500)은 프로세서(510), 위상 고정 루프(520), 주변 블록(530), 오디오 블록(540), 디스플레이 블록(550), 그래픽 블록(560), 이미지 프로세싱 블록(570), 그리고 코덱 블록(580)을 포함한다.

[0083] 프로세서(510)는 제 1 내지 제 8 플립플롭들(512~519)을 포함한다. 프로세서(510)는 레벨 변환기(100)를 더 포함하거나, 또는 레벨 변환기(100)에 연결될 수 있다. 레벨 변환기(100)는 위상 고정 루프(520)로부터 제 1 클록(CLK1)을 수신한다. 제 1 클록(CLK1)은 제 1 전압(V1)의 스윙폭을 가질 수 있다. 레벨 변환기(100)는 고레벨 및 저레벨 구간들의 비율들을 유지하며, 제 1 클록(CLK1)에 동기되는 제 2 클록(CLK2)을 발생한다. 제 2 클록(CLK2)은 제 2 전압(V1)의 스윙폭을 가질 수 있다. 제 2 전압(V2)은 제 1 전압(V1)보다 클 수 있다.

[0084] 레벨 변환기(100)에서 발생된 제 2 클록(CLK2)은 프로세서(510)의 플립플롭들(512~519)에 공급된다. 프로세서(510)의 플립플롭들(512~519)은 제 2 클록(CLK2)에 응답하여 동작한다.

[0085] 위상 고정 루프(520)는 외부로부터 클록(CLK)을 수신한다. 위상 고정 루프(520)는 수신된 클록(CLK)과 동기되는 제 1 클록(CLK1)을 발생한다. 제 1 클록(CLK1)은 프로세서(510)의 레벨 변환기(100), 주변 블록(530), 오디오 블록(540), 디스플레이 블록(550), 그래픽 블록(560), 이미지 프로세싱 블록(570), 그리고 코덱 블록(580)에 공급된다.

[0086] 주변 블록(530), 오디오 블록(540), 디스플레이 블록(550), 그래픽 블록(560), 이미지 프로세싱 블록(570), 그리고 코덱 블록(580)은 제 1 클록(CLK1)에 응답하여 동작한다. 주변 블록(530), 오디오 블록(540), 디스플레이 블록(550), 그래픽 블록(560), 이미지 프로세싱 블록(570), 그리고 코덱 블록(580)은 아이피들(IP, Intellectual Property)일 수 있다.

[0087] 오디오 블록(540)은 오디오 데이터를 처리할 수 있다. 디스플레이 블록(550)은 모니터(미도시)와 같은 디스플레이 장치를 제어하는 신호들을 발생할 수 있다. 그래픽 블록(560)은 모니터(미도시)와 같은 디스플레이 장치에 표시될 그래픽 데이터를 처리할 수 있다. 이미지 프로세싱 블록(570)은 카메라(미도시)와 같은 촬영 장치에 의해 촬영되는 이미지 데이터를 처리할 수 있다. 코덱(580)은 오디오 데이터의 인코딩 또는 디코딩을 수행할 수 있다. 코덱(580)은 그래픽 데이터의 인코딩 또는 디코딩을 수행할 수 있다.

[0088] 도 6에 도시된 바와 같이, 시스템-온-칩(500)의 주변 블록(530), 오디오 블록(540), 디스플레이 블록(550), 그래픽 블록(560), 이미지 프로세싱 블록(570), 그리고 코덱 블록(580)은 제 1 클록(CLK1)에 응답하여 동작한다. 프로세서(510)는 제 1 전압 도메인의 제 1 클록(CLK1)이 변환된 제 2 전압 도메인의 제 2 클록(CLK2)에 응답하여 동작할 수 있다. 제 2 전압(V2)은 제 1 전압(V1)보다 높을 수 있다.

[0089] 레벨 변환기(100)는 도 1 내지 도 5를 참조하여 설명된 레벨 변환기(100)일 수 있다. 예시적으로, 레벨 변환기(100)는 입력 노드(A)와 출력 노드(F) 사이에 병렬 연결되며, 동일한 구조를 갖는 제 1 및 제 2 전압 변환 회로들(110, 120)을 포함할 수 있다. 레벨 변환기(100)의 입력 클록(CLK1)과 출력 클록(CLK2)의 상승 에지들 사이의 지연(D1)과 하강 에지들 사이의 지연(D2)은 동일할 수 있다. 따라서, 제 2 클록(CLK2)에 응답하여 동작하는 프로세서(510)의 신뢰성, 그리고 프로세서(510)를 포함하는 시스템-온-칩(500)의 신뢰성이 향상된다.

[0090] 프로세서(510)가 고속으로 동작하도록 설계되는 경우, 프로세서(510)는 제 2 클록(CLK2)의 상승 에지와 하강 에지 모두에 동기되어 동작할 수 있다. 본 발명의 실시 예들에 따른 레벨 변환기(100)는 고레벨 구간 및 저레벨 구간의 비율을 유지하며, 제 1 전압 도메인의 제 1 클록(CLK1)을 제 2 전압 도메인의 제 2 클록(CLK2)으로 변환한다. 고레벨 구간 및 저레벨 구간의 비율이 유지되면, 제 2 클록(CLK2)의 상승 에지와 하강 에지의 마진(margin)이 최적화되어 유지될 수 있다. 따라서, 본 발명의 실시 예들에 따른 레벨 변환기(100)가 제공될 때, 제 2 클록(CLK2)의 상승 에지와 하강 에지 모두에 동기되어 동작하는 프로세서(510) 및 시스템-온-칩(500)의 신뢰성이 향상될 수 있다.

[0091] 도 7은 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(1000)의 제 1 예를 보여주는 블록도이다. 도 7을 참조하면, 멀티미디어 장치(1000)는 발진기(1010), 클록 발생부(1020), 위상 고정 루프(1030), 프로세서(1040), 메모리(1050), 디스플레이 제어부(1060), 디스플레이부(1070), 사운드 제어부(1080), 스피커(1090), 저장부(1100), 모뎀(1110), 이미지 프로세싱부(1120), 카메라(1130), 사용자 인터페이

스(1140), 그리고 코텍부(1150)를 포함한다.

[0092] 발진기(1010)는 특정 주파수에 따라 발진하는 발진 신호를 발생한다. 발진 신호는 클록 발생부(1020)에 공급된다.

[0093] 클록 발생부(1020)는 발진기(1010)로부터 공급되는 발진 신호에 응답하여 클록(1020)을 발생한다. 클록(CLK)은 위상 고정 루프(1030)에 공급될 수 있다.

[0094] 위상 고정 루프(1030)는 클록 발생부(1020)로부터 수신되는 클록(CLK)에 응답하여 제 1 클록(CLK1)을 발생하도록 구성된다. 제 1 클록(CLK1)은 수신된 클록(CLK)과 동기될 수 있다. 제 1 클록(CLK1)은 프로세서(1040)에 공급될 수 있다.

[0095] 프로세서(1040)는 멀티미디어 장치(1000)의 제반 동작을 제어하도록 구성된다. 프로세서(1040)는 멀티미디어 장치(1000)의 하드웨어 구성 요소들을 제어한다. 프로세서(1040)는 멀티미디어 장치(1000)의 소프트웨어 구성 요소들을 구동한다.

[0096] 프로세서(1040)는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하거나, 또는 레벨 변환기(100)에 연결될 수 있다. 레벨 변환기(100)는 위상 고정 루프(1030)로부터 공급되는 제 1 전압 도메인의 제 1 클록(CLK1)에 기반하여, 제 2 전압 도메인의 제 2 클록(CLK2)을 발생한다. 제 2 클록(CLK2)은 프로세서(1010)의 내부 클록으로 사용된다.

[0097] 메모리(1050)는 프로세서(1040)의 동작 메모리일 수 있다. 예시적으로, 메모리(1050)는 SRAM (Static RAM), DRAM (Dynamic RAM), SDRAM (Synchronous DRAM) 등과 같은 휘발성 메모리, 또는 플래시 메모리, PRAM (Phase-change RAM), MRAM (Magnetic RAM), RRAM (Resistive RAM), FRAM (Ferroelectric RAM) 등과 같은 불휘발성 메모리를 포함할 수 있다.

[0098] 디스플레이 제어부(1060)는 프로세서(1040)의 제어에 따라 동작한다. 디스플레이 제어부(1060)는 디스플레이부(1070)를 통해 표시되는 영상을 생성 및 제어하도록 구성된다. 디스플레이 제어부(1060)는 그래픽 처리 유닛(GPU, Graphic Processing Unit)을 포함할 수 있다.

[0099] 디스플레이부(1070)는 디스플레이 제어부(1060)에 의해 생성된 영상을 표시하도록 구성된다. 디스플레이부(1070)는 액정 디스플레이(LCD, Liquid Crystal Display), 유기 발광 다이오드(OLED, Organic Light Emitting Diode) 디스플레이, 액티브 매트릭스 유기 발광 다이오드(AMOLED, Active Matrix Organic Light Emitting Diode) 디스플레이, 전자 종이(electronic paper) 등을 포함할 수 있다.

[0100] 사운드 제어부(1080)는 프로세서(1040)의 제어에 따라 동작한다. 사운드 제어부(1080)는 스피커(1090)를 통해 출력되는 사운드를 생성 및 제어할 수 있다. 스피커(1090)는 사운드 제어부(1080)의 제어에 따라 사운드를 출력할 수 있다.

[0101] 저장부(1100)는 프로세서(1040)의 제어에 따라 데이터를 저장하도록 구성된다. 저장부(1100)는 플래시 메모리, PRAM (Phase-change RAM), MRAM (Magnetic RAM), RRAM (Resistive RAM), FRAM (Ferroelectric RAM) 등과 같은 불휘발성 메모리를 포함할 수 있다. 저장부(1100)는 하드 디스크 드라이브(HDD, Hard Disk Drive), 솔리드 스테이트 드라이브(SSD, Solid State Drive)를 포함할 수 있다.

[0102] 모뎀(1110)은 프로세서(1040)의 제어에 따라 외부와 통신할 수 있다. 예시적으로, 모뎀(1110)은 무선 채널 또는 유선 채널을 통해 외부와 통신할 수 있다. 모뎀(1110)은 CDMA (Code Division Multiple Access), GSM (Global System for Mobile communications), CDMA 2000, WCDMA (Wideband Code Division Multiple Access), LTE (Long Term Evolution), WiBro (Wireless Broadband Internet), Mobile WiMAX (World Interoperability), WiFi 등과 같은 무선 프로토콜에 따라 외부와 통신할 수 있다. 모뎀(1110)은 ADSL (Asymmetric Digital Subscriber Line), VDSL (Very high data rate Digital Subscriber Line), ISDN (Integrated Services Digital Network) 등과 같은 유선 프로토콜에 따라 외부와 통신할 수 있다.

[0103] 이미지 프로세싱부(1130)는 프로세서(1040)의 제어에 응답하여 동작한다. 이미지 프로세싱부(1130)는 카메라(1140)에 의해 포착 또는 녹화되는 이미지 데이터를 처리하도록 구성된다.

[0104] 사용자 인터페이스(1140)는 외부로부터 감지되는 신호를 프로세서(1140)에 전달하도록 구성된다. 예시적으로, 사용자 인터페이스(1120)는 마이크로폰(microphone), 터치패드(touch pad), 터치 스크린(touch screen), 버튼, 마우스, 키보드 등을 포함할 수 있다.

- [0105] 코덱부(1150)는 오디오 데이터를 인코딩 또는 디코딩할 수 있다. 코덱부(1150)는 비디오 데이터를 인코딩 또는 디코딩할 수 있다.

- [0106] 예시적으로, 위상 고정 루프(1030), 프로세서(1040), 메모리(1050), 디스플레이 제어부(1060), 사운드 제어부(1080), 이미지 프로세싱부(1120), 그리고 코덱부(1150)는 시스템-온-칩(1200)을 구성할 수 있다. 시스템-온-칩(1200)은 도 6을 참조하여 설명된 구조를 가질 수 있다. 프로세서(1040)는 도 6의 프로세서(510)에 대응할 수 있다. 메모리(1050)는 도 6의 주변 블록(530)에 대응할 수 있다. 디스플레이 제어부(1060)는 도 6의 디스플레이 블록(550) 및 그래픽 블록(560)에 대응할 수 있다. 사운드 제어부(1080)는 도 6의 오디오 블록(540)에 대응할 수 있다. 이미지 프로세싱부(1120)는 도 6의 이미지 프로세싱 블록(570)에 대응할 수 있다. 코덱부(1150)는 도 6의 코덱 블록(580)에 대응할 수 있다.

- [0107] 클록 발생부(1020)는 발생된 클록(CLK)을 시스템-온-칩(1200)에 공급하고, 그리고 멀티미디어 장치(1000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

- [0108] 시스템-온-칩(1200)의 위상 고정 루프(1030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(1040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(1200)의 다른 구성 요소들, 즉 메모리(1050), 디스플레이 제어부(1060), 사운드 제어부(1080), 이미지 프로세싱부(1120), 그리고 코덱부(1150)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

- [0109] 도 8은 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(2000)의 제 2 예를 보여주는 블록도이다. 도 8을 참조하면, 멀티미디어 장치(2000)는 발진기(2010), 클록 발생부(2020), 위상 고정 루프(2030), 프로세서(2040), 메모리(2050), 디스플레이 제어부(2060), 디스플레이부(2070), 사운드 제어부(2080), 스피커(2090), 저장부(2100), 모뎀(2110), 이미지 프로세싱부(2120), 카메라(2130), 사용자 인터페이스(2140), 그리고 코덱부(2150)를 포함한다.

- [0110] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(2000)에서 위상 고정 루프(2030), 프로세서(2040), 메모리(2050), 디스플레이 제어부(2060), 사운드 제어부(2080), 모뎀(2110), 이미지 프로세싱부(2120), 그리고 코덱부(2150)가 시스템-온-칩(2200)을 구성할 수 있다. 시스템-온-칩(2200)은 도 6을 참조하여 설명된 구조를 가질 수 있다. 프로세서(2040)는 도 6의 프로세서(510)에 대응할 수 있다. 메모리(2050) 및 모뎀(2110)은 도 6의 주변 블록(530)에 대응할 수 있다. 디스플레이 제어부(2060)는 도 6의 디스플레이 블록(550) 및 그래픽 블록(560)에 대응할 수 있다. 사운드 제어부(2080)는 도 6의 오디오 블록(540)에 대응할 수 있다. 이미지 프로세싱부(2120)는 도 6의 이미지 프로세싱 블록(570)에 대응할 수 있다. 코덱부(2150)는 도 6의 코덱 블록(580)에 대응할 수 있다.

- [0111] 클록 발생부(2020)는 발생된 클록(CLK)을 시스템-온-칩(2200)에 공급하고, 그리고 멀티미디어 장치(2000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

- [0112] 시스템-온-칩(2200)의 위상 고정 루프(2030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(2040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(2200)의 다른 구성 요소들, 즉 메모리(2050), 디스플레이 제어부(2060), 사운드 제어부(2080), 모뎀(2110), 이미지 프로세싱부(2120), 그리고 코덱부(2150)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

- [0113] 도 9는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(3000)의 제 3 예를 보여주는 블록도이다. 도 9를 참조하면, 멀티미디어 장치(3000)는 발진기(3010), 클록 발생부(3020), 위상 고정 루프(3030), 프로세서(3040), 메모리(3050), 디스플레이 제어부(3060), 디스플레이부(3070), 사운드 제어부(3080), 스피커(3090), 저장부(3100), 모뎀(3110), 이미지 프로세싱부(3120), 카메라(3130), 사용자 인터페이스(3140), 그리고 코덱부(3150)를 포함한다.

- [0114] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(3000)에서 위상 고정 루프(3030), 프로세서(3040), 메모리(3050), 디스플레이 제어부(3060), 사운드 제어부(3080), 그리고 코덱부(3150)가 시스템-온-칩(2200)을 구성할 수 있다.

- [0115] 클록 발생부(3020)는 발생된 클록(CLK)을 시스템-온-칩(3200)에 공급하고, 그리고 멀티미디어 장치(3000)의

구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

[0116] 시스템-온-칩(3200)의 위상 고정 루프(3030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(3040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(3200)의 다른 구성 요소, 즉 메모리(3050), 디스플레이 제어부(3060), 사운드 제어부(3080), 그리고 코덱부(3150)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

[0117] 도 10은 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(4000)의 제 4 예를 보여주는 블록도이다. 도 10을 참조하면, 멀티미디어 장치(4000)는 발진기(4010), 클록 발생부(4020), 위상 고정 루프(4030), 프로세서(4040), 메모리(4050), 디스플레이 제어부(4060), 디스플레이부(4070), 사운드 제어부(4080), 스피커(4090), 저장부(4100), 모뎀(4110), 이미지 프로세싱부(4120), 카메라(4130), 사용자 인터페이스(4140), 그리고 코덱부(4150)를 포함한다.

[0118] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(4000)에서 위상 고정 루프(4030), 프로세서(4040), 메모리(4050), 디스플레이 제어부(4060), 그리고 사운드 제어부(4080)가 시스템-온-칩(4200)을 구성할 수 있다.

[0119] 클록 발생부(4020)는 발생된 클록(CLK)을 시스템-온-칩(4200)에 공급하고, 그리고 멀티미디어 장치(4000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

[0120] 시스템-온-칩(4200)의 위상 고정 루프(4030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(4040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(4200)의 다른 구성 요소, 즉 메모리(4050), 디스플레이 제어부(4060), 그리고 사운드 제어부(4080)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

[0121] 도 11은 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(5000)의 제 5 예를 보여주는 블록도이다. 도 11을 참조하면, 멀티미디어 장치(5000)는 발진기(5010), 클록 발생부(5020), 위상 고정 루프(5030), 프로세서(5040), 메모리(5050), 디스플레이 제어부(5060), 디스플레이부(5070), 사운드 제어부(5080), 스피커(5090), 저장부(5100), 모뎀(5110), 이미지 프로세싱부(5120), 카메라(5130), 사용자 인터페이스(5140), 그리고 코덱부(5150)를 포함한다.

[0122] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(5000)에서 위상 고정 루프(5030), 프로세서(5040), 메모리(5050), 그리고 디스플레이 제어부(5060)가 시스템-온-칩(5200)을 구성할 수 있다.

[0123] 클록 발생부(5020)는 발생된 클록(CLK)을 시스템-온-칩(5200)에 공급하고, 그리고 멀티미디어 장치(5000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

[0124] 시스템-온-칩(5200)의 위상 고정 루프(5030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(5040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(5200)의 다른 구성 요소, 즉 메모리(5050) 및 디스플레이 제어부(5060)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

[0125] 도 12는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(6000)의 제 6 예를 보여주는 블록도이다. 도 12를 참조하면, 멀티미디어 장치(6000)는 발진기(6010), 클록 발생부(6020), 위상 고정 루프(6030), 프로세서(6040), 메모리(6050), 디스플레이 제어부(6060), 디스플레이부(6070), 사운드 제어부(6080), 스피커(6090), 저장부(6100), 모뎀(6110), 이미지 프로세싱부(6120), 카메라(6130), 사용자 인터페이스(6140), 그리고 코덱부(6150)를 포함한다.

[0126] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(6000)에서 위상 고정 루프(6030), 프로세서(6040), 그리고 메모리(6050)가 시스템-온-칩(6200)을 구성할 수 있다.

[0127] 클록 발생부(6020)는 발생된 클록(CLK)을 시스템-온-칩(6200)에 공급하고, 그리고 멀티미디어 장치(6000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

[0128] 시스템-온-칩(6200)의 위상 고정 루프(6030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레

밸 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(6040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(6200)의 다른 구성 요소, 즉 메모리(6050)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

[0129] 도 13은 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(7000)의 제 7 예를 보여주는 블록도이다. 도 13을 참조하면, 멀티미디어 장치(7000)는 발진기(7010), 클록 발생부(7020), 위상 고정 루프(7030), 프로세서(7040), 메모리(7050), 디스플레이 제어부(7060), 디스플레이부(7070), 사운드 제어부(7080), 스피커(7090), 저장부(7100), 모뎀(7110), 이미지 프로세싱부(7120), 카메라(7130), 사용자 인터페이스(7140), 그리고 코덱부(7150)를 포함한다.

[0130] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(7000)에서 위상 고정 루프(7030), 프로세서(7040), 메모리(7050), 그리고 사운드 제어부(7080)가 시스템-온-칩(7200)을 구성할 수 있다.

[0131] 클록 발생부(7020)는 발생된 클록(CLK)을 시스템-온-칩(7200)에 공급하고, 그리고 멀티미디어 장치(7000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

[0132] 시스템-온-칩(7200)의 위상 고정 루프(7030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(7040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(7200)의 다른 구성 요소, 즉 메모리(7050) 및 사운드 제어부(7080)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

[0133] 도 14는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하는 멀티미디어 장치(8000)의 제 8 예를 보여주는 블록도이다. 도 14를 참조하면, 멀티미디어 장치(8000)는 발진기(8010), 클록 발생부(8020), 위상 고정 루프(8030), 프로세서(8040), 메모리(8050), 디스플레이 제어부(8060), 디스플레이부(8070), 사운드 제어부(8080), 스피커(8090), 저장부(8100), 모뎀(8110), 사용자 인터페이스(8140), 그리고 코덱부(8150)를 포함한다.

[0134] 도 7을 참조하여 설명된 멀티미디어 장치(1000)와 비교하면, 멀티미디어 장치(8000)에서 이미지 프로세싱부(1120) 및 카메라(1130)가 제공되지 않을 수 있다. 그리고, 위상 고정 루프(8030), 프로세서(8040), 메모리(8050), 디스플레이 제어부(8060), 사운드 제어부(8080), 그리고 코덱부(8150)가 시스템-온-칩(7200)을 구성할 수 있다.

[0135] 클록 발생부(8020)는 발생된 클록(CLK)을 시스템-온-칩(8200)에 공급하고, 그리고 멀티미디어 장치(8000)의 구성 요소들 중 클록(CLK)을 필요로 하는 다른 구성 요소들에 공급할 수 있다.

[0136] 시스템-온-칩(8200)의 위상 고정 루프(8030)는 수신된 클록(CLK)에 동기하는 제 1 클록(CLK1)을 발생한다. 레벨 변환기(100)는, 도 1 내지 도 5를 참조하여 설명된 바와 같이, 고레벨 구간 및 저레벨 구간의 비율을 유지하며 제 1 클록(CLK1)에 기반하여 제 2 클록(CLK2)을 발생할 수 있다. 프로세서(8040)는 제 2 클록(CLK2)에 기반하여 동작할 수 있다. 시스템-온-칩(8200)의 다른 구성 요소, 즉 메모리(8050) 및 사운드 제어부(8080)는 제 1 클록(CLK1)에 응답하여 동작할 수 있다.

[0137] 이미지 프로세싱부(2120~7120) 및 카메라(2130~7130)가 제공되지 않는 것을 제외하면, 멀티미디어 장치(8000)의 구성 요소들 중 시스템-온-칩(8200)을 구성하는 구성 요소들은 도 8 내지 도 13을 참조하여 설명된 바와 같이 가변될 수 있다.

[0138] 도 7 내지 도 14를 참조하여, 본 발명의 실시 예들에 따른 멀티미디어 장치들이 설명되었다. 본 발명의 실시 예에 따른 멀티미디어 장치들은 다양한 제품으로 구현될 수 있다. 예시적으로, 본 발명의 실시 예들에 따른 멀티미디어 장치들은 컴퓨터, UMPC (Ultra Mobile PC), 워크스테이션, 넷북(net-book), PDA (Personal Digital Assistants), 포터블(portable) 컴퓨터, 태블릿 컴퓨터(tablet computer), 무선 전화기(wireless phone), 모바일 폰(mobile phone), 스마트폰(smart phone), e-북(e-book), PMP(portable multimedia player), 휴대용 게임기, 네비게이션(navigation) 장치, 블랙박스(black box), 디지털 카메라(digital camera), DMB (Digital Multimedia Broadcasting) 재생기, 3차원 텔레비전(3-dimensional television), 스마트 텔레비전(smart television), 디지털 음성 녹음기(digital audio recorder), 디지털 음성 재생기(digital audio player), 디지털 영상 녹화기(digital picture recorder), 디지털 영상 재생기(digital picture player), 디

지털 동영상 녹화기(digital video recorder), 디지털 동영상 재생기(digital video player), 정보를 무선 환경에서 송수신할 수 있는 장치, 흔 네트워크를 구성하는 다양한 전자 장치들 중 하나, 컴퓨터 네트워크를 구성하는 다양한 전자 장치들 중 하나, 텔레매틱스 네트워크를 구성하는 다양한 전자 장치들 중 하나, RFID 장치, 또는 컴퓨팅 시스템을 구성하는 다양한 구성 요소들 중 하나 등을 구성할 수 있다.

[0139] 도 15는 본 발명의 실시 예에 따른 스마트 폰(6100)을 보여주는 도면이다. 도 15를 참조하면, 스마트 폰(9100)은 외부 케이스(9110), 화면(9120), 카메라(9130), 스피커(9140), 그리고 조작 버튼(9150)을 포함한다.

[0140] 화면(9120)은 도 7 내지 도 14를 참조하여 설명된 디스플레이부(1070~8070)를 구성할 수 있다. 카메라(9130)는 도 7 내지 도 13을 참조하여 설명된 카메라(1130~7130)를 구성할 수 있다. 조작 버튼(9150)은 도 7 내지 도 14를 참조하여 설명된 사용자 인터페이스(1140~8140)를 구성할 수 있다. 화면(9120)이 터치 스크린으로 형성될 때, 화면(9120) 또한 사용자 인터페이스(1140~8140)를 구성할 수 있다. 스피커(9140)는 도 7 내지 도 14를 참조하여 설명된 스피커(1090~8090)에 대응할 수 있다.

[0141] 외부 케이스(9110)의 내부에, 발진기(1010~8010), 클록 발생부(1020~8020), 위상 고정 루프(1030~8030), 프로세서(1040~8040), 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 그리고 코덱부(1150~8150)가 제공될 수 있다. 외부 케이스(9110)의 내부에, 이미지 프로세싱부(1120~7120)가 더 제공될 수 있다. 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 이미지 프로세싱부(1120~7120), 그리고 코덱부(1150~7150) 중 적어도 하나는 위상 고정 루프(1030~8030) 및 프로세서(1040~8040)와 함께 시스템-온-칩(1200~8200)을 구성할 수 있다.

[0142] 클록 발생부(1020~8020)는 발진기(1010~8010)로부터 수신되는 발진 신호에 응답하여 클록(CLK)을 발생할 수 있다. 클록(CLK)은 시스템-온-칩(1200~8200)에 공급될 수 있다. 위상 고정 루프(1030~8030)는 클록(CLK)에 동기되는 제 1 클록(CLK1)을 발생할 수 있다. 제 1 클록(CLK1)은 시스템-온-칩(1200~8200)의 구성 요소들에 공급될 수 있다. 프로세서(1040~8040)는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하거나 레벨 변환기(100)와 연결될 수 있다. 레벨 변환기(100)는 고레벨 구간의 비율과 저레벨 구간의 비율을 유지하며, 제 1 전압 도메인의 제 1 클록(CLK1)을 제 2 전압 도메인의 제 2 클록(CLK2)으로 변환한다. 프로세서(1040~8040)는 제 2 클록(CLK2)에 응답하여 동작한다. 시스템-온-칩(1200~8200)의 다른 구성 요소들은 제 1 클록(CLK1)에 응답하여 동작한다.

[0143] 도 15에 도시되지 않았지만, 스마트 폰(6100)의 후면, 상면, 하면, 그리고 측면 중 적어도 하나에 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다. 또한, 스마트 폰(9100)에 연결되는 액세서리(accessory)로서, 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다.

[0144] 도 16은 본 발명의 실시 예에 따른 태블릿 컴퓨터(9200)를 보여주는 도면이다. 도 16을 참조하면, 태블릿 컴퓨터(9200)는 외부 케이스(9210), 화면(9220), 카메라(9230), 스피커(9240), 그리고 조작 버튼(9250)을 포함한다.

[0145] 화면(9220)은 도 7 내지 도 14를 참조하여 설명된 디스플레이부(1070~8070)를 구성할 수 있다. 카메라(9230)는 도 7 내지 도 13을 참조하여 설명된 카메라(1130~7130)를 구성할 수 있다. 조작 버튼(9250)은 도 7 내지 도 14를 참조하여 설명된 사용자 인터페이스(1140~8140)를 구성할 수 있다. 화면(9220)이 터치 스크린으로 형성될 때, 화면(9220) 또한 사용자 인터페이스(1140~8140)를 구성할 수 있다. 스피커(9240)는 도 7 내지 도 14를 참조하여 설명된 스피커(1090~8090)에 대응할 수 있다.

[0146] 외부 케이스(9210)의 내부에, 발진기(1010~8010), 클록 발생부(1020~8020), 위상 고정 루프(1030~8030), 프로세서(1040~8040), 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 그리고 코덱부(1150~8150)가 제공될 수 있다. 외부 케이스(9210)의 내부에, 이미지 프로세싱부(1120~7120)가 더 제공될 수 있다. 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 이미지 프로세싱부(1120~7120), 그리고 코덱부(1150~7150) 중 적어도 하나는 위상 고정 루프(1030~8030) 및 프로세서(1040~8040)와 함께 시스템-온-칩(1200~8200)을 구성할 수 있다.

[0147] 클록 발생부(1020~8020)는 발진기(1010~8010)로부터 수신되는 발진 신호에 응답하여 클록(CLK)을 발생할 수 있다. 클록(CLK)은 시스템-온-칩(1200~8200)에 공급될 수 있다. 위상 고정 루프(1030~8030)는 클록(CLK)에 동

기되는 제 1 클록(CLK1)을 발생할 수 있다. 제 1 클록(CLK1)은 시스템-온-칩(1200~8200)의 구성 요소들에 공급될 수 있다. 프로세서(1040~8040)는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하거나 레벨 변환기(100)와 연결될 수 있다. 레벨 변환기(100)는 고레벨 구간의 비율과 저레벨 구간의 비율을 유지하며, 제 1 전압 도메인의 제 1 클록(CLK1)을 제 2 전압 도메인의 제 2 클록(CLK2)으로 변환한다. 프로세서(1040~8040)는 제 2 클록(CLK2)에 응답하여 동작한다. 시스템-온-칩(1200~8200)의 다른 구성 요소들은 제 1 클록(CLK1)에 응답하여 동작한다.

[0148] 도 16에 도시되지 않았지만, 태블릿 컴퓨터(9200)의 후면, 상면, 하면, 그리고 측면 중 적어도 하나에 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다. 또한, 태블릿 컴퓨터(6200)에 연결되는 액세서리(accessory)로서, 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다.

[0149] 도 17은 본 발명의 실시 예에 따른 모바일 컴퓨터(9300)를 보여주는 도면이다. 도 17을 참조하면, 모바일 컴퓨터(9300)는 외부 케이스(9310), 화면(9320), 카메라(9330), 스피커(9340), 키보드(9350), 그리고 터치 패드(9360)를 포함한다.

[0150] 화면(9320)은 도 7 내지 도 14를 참조하여 설명된 디스플레이부(1070~8070)를 구성할 수 있다. 카메라(9330)는 도 7 내지 도 13을 참조하여 설명된 카메라(1130~7130)를 구성할 수 있다. 키보드(9350) 및 터치 패드(9360)는 도 7 내지 도 14를 참조하여 설명된 사용자 인터페이스(1140~8140)를 구성할 수 있다. 화면(9320)이 터치 스크린으로 형성될 때, 화면(9320) 또한 사용자 인터페이스(1140~8140)를 구성할 수 있다. 스피커(9340)는 도 7 내지 도 14를 참조하여 설명된 스피커(1090~8090)에 대응할 수 있다.

[0151] 외부 케이스(9310)의 내부에, 발진기(1010~8010), 클록 발생부(1020~8020), 위상 고정 루프(1030~8030), 프로세서(1040~8040), 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 그리고 코덱부(1150~8150)가 제공될 수 있다. 외부 케이스(9310)의 내부에, 이미지 프로세싱부(1120~7120)가 더 제공될 수 있다. 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 이미지 프로세싱부(1120~7120), 그리고 코덱부(1150~7150) 중 적어도 하나는 위상 고정 루프(1030~8030) 및 프로세서(1040~8040)와 함께 시스템-온-칩(1200~8200)을 구성할 수 있다.

[0152] 클록 발생부(1020~8020)는 발진기(1010~8010)로부터 수신되는 발진 신호에 응답하여 클록(CLK)을 발생할 수 있다. 클록(CLK)은 시스템-온-칩(1200~8200)에 공급될 수 있다. 위상 고정 루프(1030~8030)는 클록(CLK)에 동기되는 제 1 클록(CLK1)을 발생할 수 있다. 제 1 클록(CLK1)은 시스템-온-칩(1200~8200)의 구성 요소들에 공급될 수 있다. 프로세서(1040~8040)는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하거나 레벨 변환기(100)와 연결될 수 있다. 레벨 변환기(100)는 고레벨 구간의 비율과 저레벨 구간의 비율을 유지하며, 제 1 전압 도메인의 제 1 클록(CLK1)을 제 2 전압 도메인의 제 2 클록(CLK2)으로 변환한다. 프로세서(1040~8040)는 제 2 클록(CLK2)에 응답하여 동작한다. 시스템-온-칩(1200~8200)의 다른 구성 요소들은 제 1 클록(CLK1)에 응답하여 동작한다.

[0153] 모바일 컴퓨터(9300)는 노트북 컴퓨터 또는 넷북일 수 있다. 도 17에 도시되지 않았지만, 모바일 컴퓨터(9300)의 후면, 상면, 하면, 그리고 측면 중 적어도 하나에 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다. 또한, 모바일 컴퓨터(9300)에 연결되는 액세서리(accessory)로서, 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다.

[0154] 도 18은 본 발명의 실시 예에 따른 컴퓨터(9400)를 보여주는 도면이다. 도 18을 참조하면, 컴퓨터(9400)는 본체(9410), 모니터(9420), 그리고 키보드(9430)를 포함한다.

[0155] 모니터(9420)는 도 7 내지 도 14를 참조하여 설명된 디스플레이부(1070~8070)를 구성할 수 있다. 키보드(9430)는 도 7 내지 도 14를 참조하여 설명된 사용자 인터페이스(1140~8140)를 구성할 수 있다. 모니터(9420)가 터치 스크린으로 형성될 때, 모니터(9420) 또한 사용자 인터페이스(1140~8140)를 구성할 수 있다.

[0156] 본체(9410)의 내부에, 발진기(1010~8010), 클록 발생부(1020~8020), 위상 고정 루프(1030~8030), 프로세서(1040~8040), 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 그리고 코덱부(1150~8150)가 제공될 수 있다. 본체(9410)의 내부에, 이미지 프로세싱부(1120~7120)가 더 제공될 수 있다. 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 이미지 프로세싱부(1120~7120), 그리고 코덱부(1150~7150) 중 적어도 하나는 위상 고정 루프(1030~8030) 및 프로세서(1040~8040)와 함께 시스템-온-칩(1200~8200)을 구성할 수 있다.

어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 이미지 프로세싱부(1120~7120), 그리고 코덱부(1150~7150) 중 적어도 하나는 위상 고정 루프(1030~8030) 및 프로세서(1040~8040)와 함께 시스템-온-칩(1200~8200)을 구성할 수 있다.

[0157] 클록 발생부(1020~8020)는 발진기(1010~8010)로부터 수신되는 발진 신호에 응답하여 클록(CLK)을 발생할 수 있다. 클록(CLK)은 시스템-온-칩(1200~8200)에 공급될 수 있다. 위상 고정 루프(1030~8030)는 클록(CLK)에 동기되는 제 1 클록(CLK1)을 발생할 수 있다. 제 1 클록(CLK1)은 시스템-온-칩(1200~8200)의 구성 요소들에 공급될 수 있다. 프로세서(1040~8040)는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하거나 레벨 변환기(100)와 연결될 수 있다. 레벨 변환기(100)는 고레벨 구간의 비율과 저레벨 구간의 비율을 유지하며, 제 1 전압 도메인의 제 1 클록(CLK1)을 제 2 전압 도메인의 제 2 클록(CLK2)으로 변환한다. 프로세서(1040~8040)는 제 2 클록(CLK2)에 응답하여 동작한다. 시스템-온-칩(1200~8200)의 다른 구성 요소들은 제 1 클록(CLK1)에 응답하여 동작한다.

[0158] 도 18에 도시되지 않았지만, 컴퓨터(9400)의 후면, 상면, 하면, 그리고 측면 중 적어도 하나에 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다. 또한, 컴퓨터(6400)에 연결되는 액세서리(accessory)로서, 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다.

[0159] 도 19는 본 발명의 실시 예에 따른 텔레비전(9500)을 보여주는 도면이다. 도 19를 참조하면, 텔레비전(9500)은 외부 케이스(9510), 화면(9520), 그리고 조작 버튼(9530)을 포함한다.

[0160] 화면(9520)은 도 7 내지 도 14를 참조하여 설명된 디스플레이부(1070~8070)를 구성할 수 있다. 조작 버튼(9530)은 도 7 내지 도 14를 참조하여 설명된 사용자 인터페이스(1140~8140)를 구성할 수 있다. 화면(9520)이 터치 스크린으로 형성될 때, 화면(9520) 또한 사용자 인터페이스(1140~8140)를 구성할 수 있다.

[0161] 외부 케이스(9510)의 내부에, 발진기(1010~8010), 클록 발생부(1020~8020), 위상 고정 루프(1030~8030), 프로세서(1040~8040), 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 그리고 코덱부(1150~8150)가 제공될 수 있다. 외부 케이스(9510)의 내부에, 이미지 프로세싱부(1120~7120)가 더 제공될 수 있다. 메모리(1050~8050), 디스플레이 제어부(1060~8060), 사운드 제어부(1080~8080), 저장부(1100~8100), 모뎀(1110~8110), 이미지 프로세싱부(1120~7120), 그리고 코덱부(1150~7150) 중 적어도 하나는 위상 고정 루프(1030~8030) 및 프로세서(1040~8040)와 함께 시스템-온-칩(1200~8200)을 구성할 수 있다.

[0162] 클록 발생부(1020~8020)는 발진기(1010~8010)로부터 수신되는 발진 신호에 응답하여 클록(CLK)을 발생할 수 있다. 클록(CLK)은 시스템-온-칩(1200~8200)에 공급될 수 있다. 위상 고정 루프(1030~8030)는 클록(CLK)에 동기되는 제 1 클록(CLK1)을 발생할 수 있다. 제 1 클록(CLK1)은 시스템-온-칩(1200~8200)의 구성 요소들에 공급될 수 있다. 프로세서(1040~8040)는 본 발명의 실시 예에 따른 레벨 변환기(100)를 포함하거나 레벨 변환기(100)와 연결될 수 있다. 레벨 변환기(100)는 고레벨 구간의 비율과 저레벨 구간의 비율을 유지하며, 제 1 전압 도메인의 제 1 클록(CLK1)을 제 2 전압 도메인의 제 2 클록(CLK2)으로 변환한다. 프로세서(1040~8040)는 제 2 클록(CLK2)에 응답하여 동작한다. 시스템-온-칩(1200~8200)의 다른 구성 요소들은 제 1 클록(CLK1)에 응답하여 동작한다.

[0163] 텔레비전(9500)은 3차원 텔레비전 및 스마트 텔레비전일 수 있다. 도 19에 도시되지 않았지만, 텔레비전(9500)의 후면, 상면, 하면, 그리고 측면 중 적어도 하나에 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다. 또한, 텔레비전(6500)에 연결되는 액세서리(accessory)로서, 디스플레이부(1070~8070), 스피커(1090~8090), 그리고 사용자 인터페이스(1140~8140)가 추가적으로 제공될 수 있다. 예시적으로, 텔레비전(9500)과 통신하는 리모트 컨트롤러(remote controller)가 사용자 인터페이스(1140~8140)로 추가적으로 제공될 수 있다.

[0164] 본 발명의 상세한 설명에서는 구체적인 실시 예에 관하여 설명하였으나, 본 발명의 범위와 기술적 사상에서 벗어나지 않는 한도 내에서 여러 가지 변형이 가능하다. 그러므로 본 발명의 범위는 상술한 실시 예에 국한되어 정해져서는 안되며 후술하는 특허청구범위뿐만 아니라 이 발명의 특허청구범위와 균등한 것들에 의해 정해져야 한다.

## 부호의 설명

|        |                      |                     |

|--------|----------------------|---------------------|

| [0165] | 100; 레벨 변환기          | 110; 제 1 전압 변환 회로   |

|        | 111; 제 1 인버터         | 113; 제 2 인버터        |

|        | 120; 제 2 전압 변환 회로    | 121; 제 3 인버터        |

|        | 123; 제 4 인버터         | N1~N4; NMOS 트랜지스터들  |

|        | P1~P4; PMOS 트랜지스터들   | 500; 시스템-온-칩(SOC)   |

|        | 510; 프로세서            | 512~519; 플립플롭들      |

|        | 520; 위상 고정 루프        | 530; 주변 블록          |

|        | 540; 오디오 블록          | 550; 디스플레이 블록       |

|        | 560; 그래픽 블록          | 570; 이미지 프로세싱 블록    |

|        | 580; 코덱 블록           |                     |

|        | 1000~8000; 멀티미디어 장치  | 1010~8010; 발진기      |

|        | 1020~8020; 클록 발생부    | 1030~8030; 위상 고정 루프 |

|        | 1040~8040; 프로세서      | 1050~8050; 메모리      |

|        | 1060~8060; 디스플레이 제어부 | 1070~8070; 디스플레이부   |

|        | 1080~8080; 사운드 제어부   | 1090~8090; 스피커      |

|        | 1100~8100; 저장부       | 1110~8110; 모뎀       |

|        | 1120~71201 이미지 프로세싱부 | 1130~8130; 카메라      |

|        | 1140~8140; 사용자 인터페이스 | 1150~8150; 코덱부      |

|        | 9100; 스마트 폰          | 9200; 태블릿 컴퓨터       |

|        | 9300; 모바일 컴퓨터        | 9400; 컴퓨터           |

|        | 9500; 텔레비전           |                     |

도면

도면1

## 도면2

도면3

도면4

도면5

## 도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15