(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0016890

(43) 공개일자 2016년02월15일

- (51) 국제특허분류(Int. Cl.)

*G01R 31/3177* (2006.01) *G01R 31/3181*

(2006.01)

*G01R 31/3183* (2006.01) *G01R 31/3185*

(2006.01)

- (52) CPC특허분류(Coo. Cl.)

*G01R 31/3177* (2013.01)

*G01R 31/3181* (2013.01)

- (21) 출원번호 10-2015-7036440

- (22) 출원일자(국제) 2014년05월28일

심사청구일자 없음

- (85) 번역문제출일자 2015년12월23일

- (86) 국제출원번호 PCT/US2014/039856

- (87) 국제공개번호 WO 2014/193998

국제공개일자 2014년12월04일

- (30) 우선권주장

13/905,060 2013년05월29일 미국(US)

- (71) 출원인

퀄컴 인코포레이티드

미국 92121-1714 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

- (72) 발명자

샤, 제이 매드후카

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

스와미나탄, 체탄

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

다타, 아니메쉬

미국 92121 캘리포니아주 샌 디에고 모어하우스 드라이브 5775

- (74) 대리인

특허법인 남엔드남

전체 청구항 수 : 총 22 항

(54) 발명의 명칭 플롭 트레이 영역 및 전력 최적화를 위한 회로 및 레이아웃 기술들

### (57) 요 약

스캔 가능한 플롭 트레이에서 스캔 오버헤드를 감소시키기 위한 기술들이 본 명세서에 설명된다. 일 실시예에서, 플롭 트레이에 대한 스캔 회로는, 정상 모드에서, 입력 데이터 신호를 인버팅하여 인버팅된 데이터 신호를 플롭 트레이의 플립-플롭의 입력에 출력하고, 스캔 모드에서, 플립-플롭의 입력으로부터의 데이터 신호를 차단하도록 구성되는 3-상태 회로를 포함한다. 스캔 회로는 또한, 스캔 모드에서, 스캔 신호를 플립-플롭의 입력에 전달하고, 정상 모드에서, 플립-플롭의 입력으로부터의 스캔 신호를 차단하도록 구성되는 전달 게이트를 포함한다.

### 대 표 도 - 도3

(52) CPC특허분류(Coo. Cl.)

*G01R 31/3183* (2013.01)

*G01R 31/318541* (2013.01)

---

## 특허청구의 범위

### 청구항 1

플롭 트레이(flop tray)에 대한 스캔 회로로서,

정상 모드에서, 입력 데이터 신호를 인버팅(invert)하여 인버팅된 데이터 신호를 플립-플롭(flip-flop)의 입력에 출력하고, 스캔 모드에서, 상기 플롭 트레이의 상기 플립-플롭의 입력으로부터의 데이터 신호를 차단하도록 구성되는 3-상태(tri-state) 회로; 및

스캔 모드에서, 상기 플립-플롭의 입력에 스캔 신호를 전달하고, 정상 모드에서, 상기 플립-플롭의 입력으로부터의 스캔 신호를 차단하도록 구성되는 전달 게이트를 포함하는, 플롭 트레이에 대한 스캔 회로.

### 청구항 2

제 1 항에 있어서,

상기 전달 게이트는,

n-타입 트랜지스터; 및

상기 n-타입 트랜지스터와 병렬로 커플링되는 p-타입 트랜지스터를 포함하며,

상기 p-타입 트랜지스터 및 상기 n-타입 트랜지스터는 스캔 모드에서 턴 온(turn on)되고 정상 모드에서 턴 오프(turn off)되도록 구성되는, 플롭 트레이에 대한 스캔 회로.

### 청구항 3

제 1 항에 있어서,

상기 플롭 트레이의 스캔 입력과 상기 전달 게이트 사이에 커플링되는 인버터를 더 포함하는, 플롭 트레이에 대한 스캔 회로.

### 청구항 4

제 1 항에 있어서,

상기 전달 게이트는, 상기 플롭 트레이의 다른 플립-플롭의 출력과 상기 플립-플롭의 입력 사이에 커플링되는, 플롭 트레이에 대한 스캔 회로.

### 청구항 5

제 4 항에 있어서,

상기 다른 플립-플롭의 출력과 상기 전달 게이트 사이에 어떠한 인버터도 존재하지 않는, 플롭 트레이에 대한 스캔 회로.

### 청구항 6

플롭 트레이에 대한 스캔 회로로서,

정상 모드에서, 제 1 데이터 신호를 인버팅하여 인버팅된 제 1 데이터 신호를 상기 플롭 트레이의 제 1 플립-플롭의 입력에 출력하고, 스캔 모드에서, 상기 제 1 플립-플롭의 입력으로부터의 제 1 데이터 신호를 차단하도록 구성되는 제 1 3-상태 회로;

스캔 모드에서, 상기 제 1 플립-플롭의 입력에 스캔 신호를 전달하고, 정상 모드에서, 상기 제 1 플립-플롭의 입력으로부터의 스캔 신호를 차단하도록 구성되는 제 1 전달 게이트;

정상 모드에서, 제 2 데이터 신호를 인버팅하여 인버팅된 제 2 데이터 신호를 상기 플롭 트레이의 제 2 플립-플롭의 입력에 출력하고, 스캔 모드에서, 상기 제 2 플립-플롭의 입력으로부터의 제 2 데이터 신호를 차단하도록 구성되는 제 2 3-상태 회로; 및

스캔 모드에서, 상기 제 1 플립-플롭의 출력으로부터 상기 제 2 플립-플롭의 입력으로 상기 스캔 신호를 전달하고, 정상 모드에서, 상기 제 1 플립-플롭의 출력으로부터 상기 제 2 플립-플롭의 입력으로의 스캔 신호를 차단하도록 구성되는 제 2 전달 게이트를 포함하는, 플롭 트레이에 대한 스캔 회로.

#### 청구항 7

제 6 항에 있어서,

상기 제 1 플립-플롭의 출력과 상기 제 2 전달 게이트 사이에 어떠한 인버터도 존재하지 않는, 플롭 트레이에 대한 스캔 회로.

#### 청구항 8

제 6 항에 있어서,

상기 플롭 트레이의 스캔 입력과 상기 제 1 전달 게이트 사이에 커플링된 인버터를 더 포함하는, 플롭 트레이에 대한 스캔 회로

#### 청구항 9

제 8 항에 있어서,

상기 제 1 플립-플롭의 출력과 상기 제 2 전달 게이트 사이에 어떠한 인버터도 존재하지 않는, 플롭 트레이에 대한 스캔 회로

#### 청구항 10

제 9 항에 있어서,

상기 제 2 전달 게이트는,

n-타입 트랜지스터; 및

상기 n-타입 트랜지스터와 병렬로 커플링되는 p-타입 트랜지스터를 포함하며,

상기 p-타입 트랜지스터 및 상기 n-타입 트랜지스터는 스캔 모드에서 턴 온되고 정상 모드에서 턴 오프되도록 구성되는, 플롭 트레이에 대한 스캔 회로.

#### 청구항 11

플롭 트레이를 스캔하기 위한 방법으로서,

정상 모드에서, 3-상태 회로를 사용하여, 입력 데이터 신호를 인버팅하고 인버팅된 데이터 신호를 상기 플롭 트레이의 플립-플롭의 입력에 출력하는 단계;

스캔 모드에서, 상기 3-상태 회로를 사용하여, 상기 플립-플롭의 입력으로부터의 데이터 신호를 차단하는 단계;

스캔 모드에서, 전달 게이트를 사용하여, 스캔 신호를 상기 플립-플롭의 입력에 전달하는 단계; 및

정상 모드에서, 상기 전달 게이트를 사용하여, 상기 플립-플롭의 입력으로부터의 스캔 신호를 차단하는 단계를 포함하는, 플롭 트레이를 스캔하기 위한 방법.

#### 청구항 12

제 11 항에 있어서,

스캔 모드에서, 다른 전달 게이트를 사용하여, 상기 플립-플롭으로부터 출력된 스캔 신호를 상기 플롭 트레이의 다른 플립-플롭의 입력에 전달하는 단계를 더 포함하는, 플롭 트레이를 스캔하기 위한 방법.

#### 청구항 13

제 12 항에 있어서,

상기 플립-플롭으로부터 출력된 스캔 신호는, 상기 플립-플롭으로부터 출력된 스캔 신호를 인버팅함이 없이 상

기 다른 플립-플롭의 입력에 전달되는, 플롭 트레이를 스캔하기 위한 방법.

#### 청구항 14

제 11 항에 있어서,

상기 전달 게이트를 사용하여 상기 스캔 신호를 상기 플립-플롭의 입력에 전달하기에 앞서, 상기 스캔 신호를 인버팅하는 단계를 더 포함하는, 플롭 트레이를 스캔하기 위한 방법.

#### 청구항 15

제 14 항에 있어서,

스캔 모드에서, 다른 전달 게이트를 사용하여, 상기 플립-플롭으로부터 출력된 스캔 신호를 상기 플롭 트레이의 다른 플립-플롭의 입력에 전달하는 단계를 더 포함하는, 플롭 트레이를 스캔하기 위한 방법.

#### 청구항 16

제 15 항에 있어서,

상기 플립-플롭으로부터 출력된 스캔 신호는, 상기 플립-플롭으로부터 출력된 스캔 신호를 인버팅함이 없이 상기 다른 플립-플롭의 입력에 전달되는, 플롭 트레이를 스캔하기 위한 방법.

#### 청구항 17

플롭 트레이를 스캔하기 위한 장치로서,

정상 모드에서, 입력 데이터 신호를 인버팅하여 인버팅된 데이터 신호를 상기 플롭 트레이의 플립-플롭의 입력에 출력하기 위한 수단;

스캔 모드에서, 상기 플립-플롭의 입력으로부터의 데이터 신호를 차단하기 위한 수단;

스캔 모드에서, 스캔 신호를 상기 플립-플롭의 입력에 전달하기 위한 수단; 및

정상 모드에서, 상기 플립-플롭의 입력으로부터의 스캔 신호를 차단하기 위한 수단을 포함하는, 플롭 트레이를 스캔하기 위한 장치.

#### 청구항 18

제 17 항에 있어서,

스캔 모드에서, 상기 플립-플롭으로부터 출력된 스캔 신호를 상기 플롭 트레이의 다른 플립-플롭의 입력에 전달하기 위한 수단을 더 포함하는, 플롭 트레이를 스캔하기 위한 장치.

#### 청구항 19

제 18 항에 있어서,

상기 플립-플롭으로부터 출력된 스캔 신호는, 상기 플립-플롭으로부터 출력된 스캔 신호를 인버팅함이 없이 상기 다른 플립-플롭의 입력에 전달되는, 플롭 트레이를 스캔하기 위한 장치.

#### 청구항 20

제 17 항에 있어서,

상기 스캔 신호를 상기 플립-플롭의 입력에 전달하기 위한 수단 이전에, 상기 스캔 신호를 인버팅하기 위한 수단을 더 포함하는, 플롭 트레이를 스캔하기 위한 장치.

#### 청구항 21

제 20 항에 있어서,

스캔 모드에서, 상기 플립-플롭으로부터 출력된 스캔 신호를 상기 플롭 트레이의 다른 플립-플롭의 입력에 전달하기 위한 수단을 더 포함하는, 플롭 트레이를 스캔하기 위한 장치.

## 청구항 22

제 21 항에 있어서,

상기 플립-플롭으로부터 출력된 스캔 신호는, 상기 플립-플롭으로부터 출력된 스캔 신호를 인버팅함이 없이 상기 다른 플립-플롭의 입력에 전달되는, 플롭 트레이를 스캔하기 위한 장치.

## 명세서

### 기술 분야

[0001] 본 개시의 양상들은 일반적으로 스캔가능한 플롭 트레이(flop tray)들에 관한 것으로, 더 상세하게는, 스캔가능한 플롭 트레이의 스캔 오버헤드(overhead)를 감소시키는 것에 관한 것이다.

### 배경 기술

[0002] 플립-플롭(flip-flop)들은, 시스템의 다양한 컴포넌트들에 의한 프로세싱을 위한 하나 또는 그 초과의 데이터 신호들로부터 데이터 값들을 캡쳐(래칭(latch))하기 위해 시스템에서 사용될 수도 있다. 시스템은, 플립-플롭들이 테스팅 동안 정확하게 기능하고 있다는 것을 검증하기 위한 스캔 회로를 포함할 수도 있다. 이를 행하기 위해, 스캔 회로는, 알려진 테스트 패턴을 갖는 스캔 신호를 수신하고 플립-플롭들을 통해 스캔 신호를 스캔한다. 플립-플롭들을 통해 스캔 신호가 스캔된 후, 플립-플롭들이 정확하게 기능하고 있는지 여부를 결정하기 위해, 출력 스캔 신호는 기대되는 출력 스캔 신호와 비교된다. 기대되는 출력 스캔 신호는, 입력 스캔 신호의 알려진 테스트 패턴 및 플립-플롭들의 기대되는 기능에 기초할 수도 있다. 스캔 회로는, 스캔 회로에 의해 소모되는 전력 및 칩 영역으로 인해 시스템에 오버헤드를 부가한다.

### 발명의 내용

[0003] 다음은 하나 또는 그 초과의 실시예들의 기본적인 이해를 제공하기 위해 그러한 실시예들의 간략화된 개요를 제시한다. 이러한 개요는, 고려되는 모든 실시예들의 포괄적인 개관이 아니며, 모든 실시예들의 핵심 또는 중요 엘리먼트들을 식별하거나 임의의 실시예를 또는 모든 실시예들의 범위를 기술하도록 의도되지는 않는다. 그것의 유일한 목적은 이후에 제시되는 더 상세한 설명에 대한 서론으로서 간략화된 형태로 하나 또는 그 초과의 실시예들의 일부 개념들을 제시하는 것이다.

[0004] 일 양상에 따르면, 플롭 트레이에 대한 스캔 회로가 제공된다. 스캔 회로는, 정상 모드에서, 입력 데이터 신호를 인버팅(invert)하여 인버팅된 데이터 신호를 플롭 트레이의 플립-플롭의 입력에 출력하고, 스캔 모드에서, 플립-플롭의 입력으로부터의 데이터 신호를 차단(block)하도록 구성되는 3-상태(tri-state) 회로를 포함한다. 스캔 회로는 또한, 스캔 모드에서, 스캔 신호를 플립-플롭의 입력에 전달하고, 정상 모드에서, 플립-플롭의 입력으로부터의 스캔 신호를 차단하도록 구성되는 전달 게이트를 포함한다.

[0005] 제 2 양상은 플롭 트레이에 대한 스캔 회로에 관한 것이다. 스캔 회로는, 정상 모드에서 제 1 데이터 신호를 인버팅하여 인버팅된 제 1 데이터 신호를 플롭 트레이의 제 1 플립-플롭의 입력에 출력하고, 스캔 모드에서 제 1 플립-플롭의 입력으로부터의 제 1 데이터 신호를 차단하도록 구성되는 제 1 3-상태 회로를 포함한다. 스캔 회로는 또한, 스캔 모드에서, 스캔 신호를 제 1 플립-플롭의 입력에 전달하고, 정상 모드에서, 제 1 플립-플롭의 입력으로부터의 스캔 신호를 차단하도록 구성되는 제 1 전달 게이트를 포함한다. 스캔 회로는 또한, 정상 모드에서, 제 2 데이터 신호를 인버팅하여 인버팅된 제 2 데이터 신호를 플롭 트레이의 제 2 플립-플롭의 입력에 출력하고, 스캔 모드에서, 제 2 플립-플롭의 입력으로부터의 제 2 데이터 신호를 차단하도록 구성되는 제 2 3-상태 회로를 포함한다. 회로는 추가로, 스캔 모드에서 제 1 플립-플롭의 출력으로부터 제 2 플립-플롭의 입력으로 스캔 신호를 전달하고, 정상 모드에서 제 1 플립-플롭의 입력으로부터 제 2 플립-플롭의 출력으로의 스캔 신호를 차단하도록 구성되는 제 2 전달 게이트를 포함한다.

[0006] 제 3 양상은 플롭 트레이를 스캔하기 위한 방법에 관한 것이다. 방법은, 정상 모드에서, 3-상태 회로를 사용하여, 입력 데이터 신호를 인버팅하고 인버팅된 데이터 신호를 플롭 트레이의 플립-플롭의 입력에 출력하는 단계, 및 스캔 모드에서, 3-상태 회로를 사용하여, 플립-플롭의 입력으로부터의 데이터 신호를 차단하는 단계를 포함한다. 방법은 또한, 스캔 모드에서, 전달 게이트를 사용하여 스캔 신호를 플립-플롭의 입력에 전달하는 단계, 및 정상 모드에서, 전달 게이트를 사용하여 플립-플롭의 입력으로부터의 스캔 신호를 차단하는 단계를 포함한다.

[0007]

[0007] 제 4 양상은 플롭 트레이를 스캔하기 위한 장치에 관한 것이다. 장치는, 정상 모드에서, 입력 데이터 신호를 인버팅하고 인버팅된 데이터 신호를 플롭 트레이의 플립-플롭의 입력에 출력하기 위한 수단, 및 스캔 모드에서, 플립-플롭의 입력으로부터의 데이터 신호를 차단하기 위한 수단을 포함한다. 장치는 또한, 스캔 모드에서, 스캔 신호를 플립-플롭의 입력에 전달하기 위한 수단, 및 정상 모드에서, 플립-플롭의 입력으로부터의 스캔 신호를 차단하기 위한 수단을 포함한다.

[0008]

[0008] 상술한 목적 및 관련된 목적의 달성을 위해, 하나 또는 그 초과의 실시예들은 아래에서 완전히 설명되고 특히 청구항들에서 지적되는 특성들을 포함한다. 다음의 설명 및 첨부된 도면들은 하나 또는 그 초과의 실시예들의 특정한 예시적인 양상들을 상세하게 기재한다. 그러나, 이들 양상들은, 다양한 실시예들의 원리들이 이용될 수도 있는 다양한 방식들 중 단지 몇몇만을 표시하며, 설명된 실시예들은 모든 그러한 양상들 및 그들의 등가물들을 포함하도록 의도된다.

### 도면의 간단한 설명

[0009]

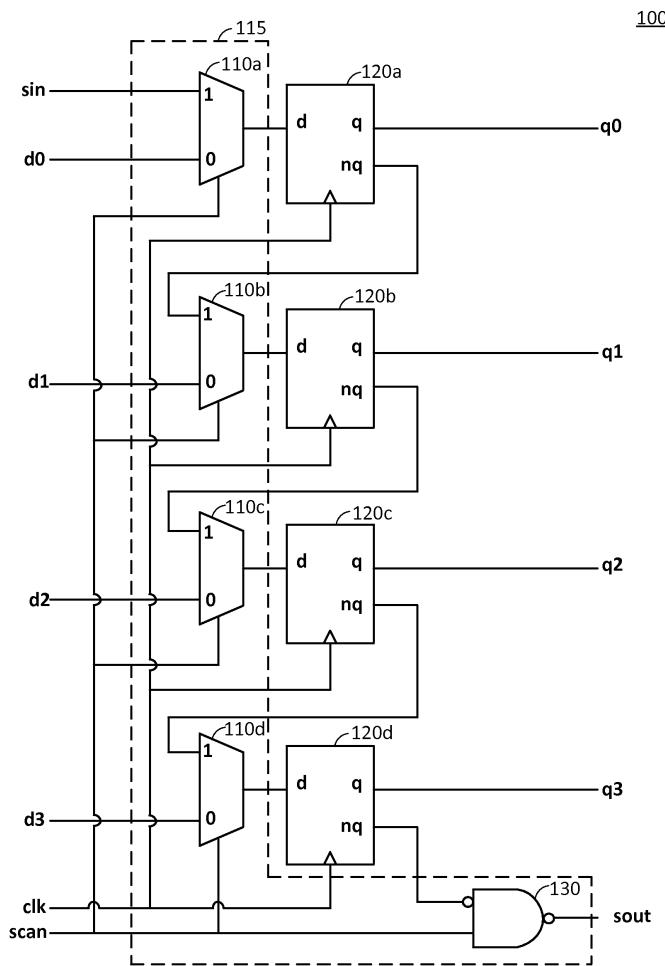

[0009] 도 1은 스캔가능한 플롭 트레이의 예를 도시한다.

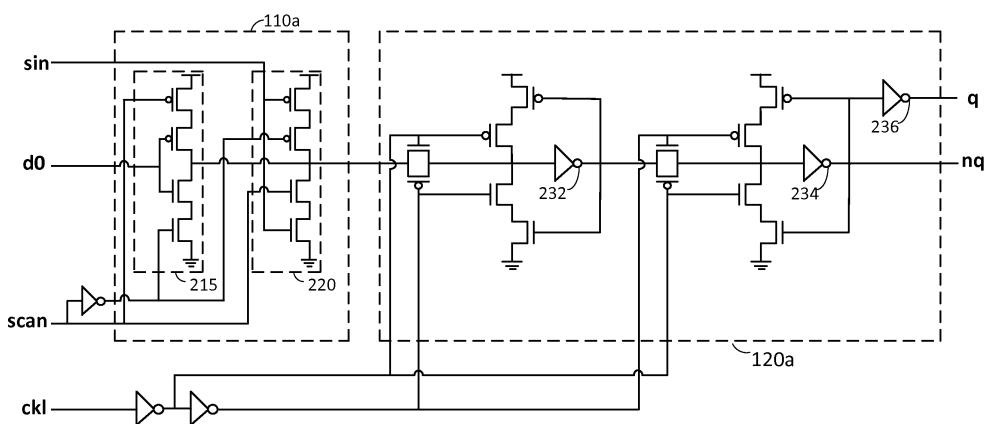

[0010] 도 2는 멀티플렉서의 예를 도시한다.

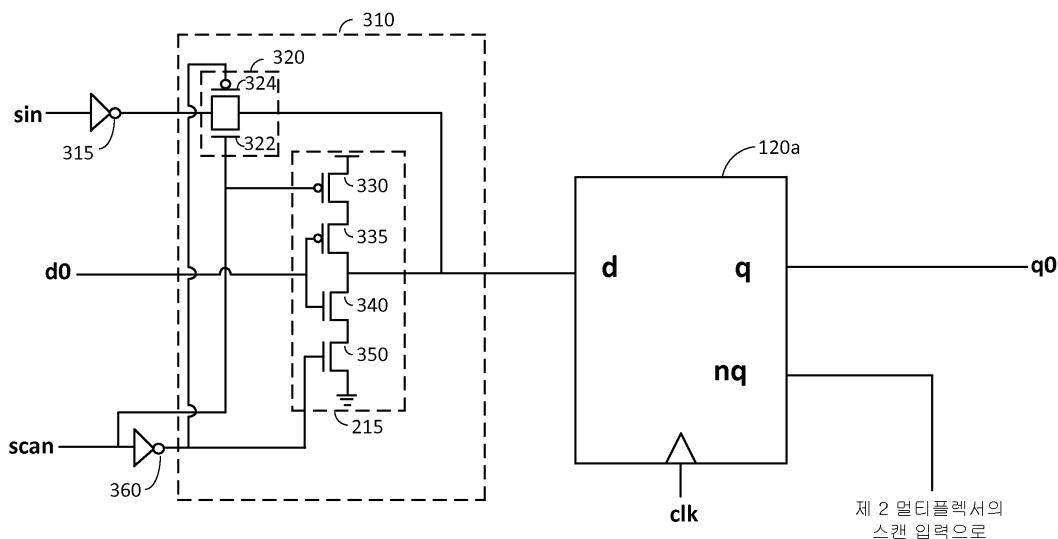

[0011] 도 3은 본 개시의 일 실시예에 따른, 감소된 오버헤드를 갖는 스캔 멀티플렉서를 도시한다.

[0012] 도 4는 본 개시의 일 실시예에 따른, 일 플립-플롭의 출력과 다른 플립-플롭의 입력 사이에 커플링된 스캔 멀티플렉서를 도시한다.

[0013] 도 5는 본 개시의 실시예에 따른 스캔가능한 플롭 트레이를 도시한다.

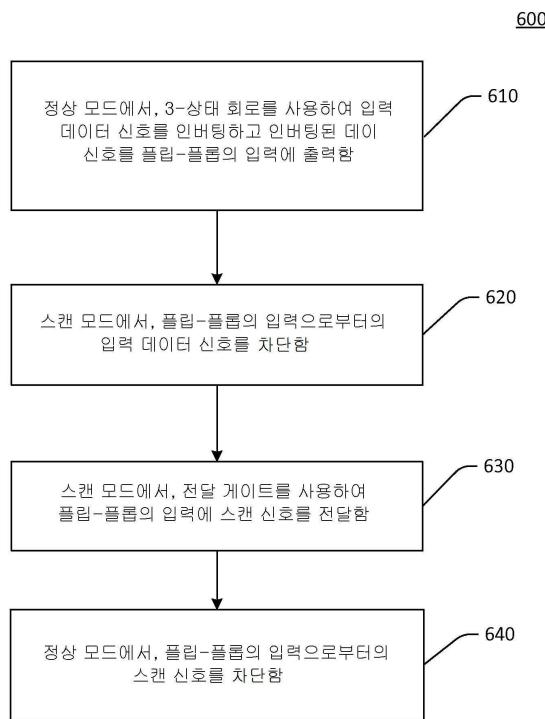

[0014] 도 6은 본 개시의 특정한 실시예들에 따른, 감소된 스캔 오버헤드로 플롭 트레이를 스캔하기 위한 방법을 예시하는 흐름도이다.

### 발명을 실시하기 위한 구체적인 내용

[0010]

[0015] 첨부된 도면들과 관련하여 아래에 기재되는 상세한 설명은, 다양한 구성들의 설명으로서 의도되며, 본 명세서에 설명된 개념들이 실시될 수 있는 유일한 구성들만을 표현하도록 의도되지 않는다. 상세한 설명은 다양한 개념들의 철저한 이해를 제공하려는 목적을 위해 특정한 세부사항들을 포함한다. 그러나, 이들 개념들이 이를 특정한 세부사항들 없이도 실시될 수도 있다는 것은 당업자들에게 명백할 것이다. 몇몇 예시들에서, 그러한 개념들을 불명료하게 하는 것을 회피하기 위해, 잘-알려진 구조들 및 컴포넌트들은 블록도 형태로 도시되어 있다.

[0011]

[0016] 도 1은 스캔가능한 플롭 트레이(100)의 예를 도시한다. 플롭 트레이(100)는 정상 모드 또는 스캔 모드에서 동작할 수 있다. 플롭 트레이(100)는, 플롭 트레이(100)의 정확한 기능을 테스트하기 위한 테스팅 동안 스캔 모드에서 동작된다.

[0012]

[0017] 플롭 트레이(100)는 제 1 D 플립-플롭(120a), 제 2 D 플립-플롭(120b), 제 3 D 플립-플롭(120c), 제 4 D 플립-플롭(120d), 및 스캔 회로(115)를 포함한다. 스캔 회로(115)는, 아래에서 추가로 설명되는 바와 같이, 테스팅 동안 플롭 트레이(100)를 스캔 모드에서 동작시키기 위해 사용된다. 스캔 회로(115)는 제 1 스캔 멀티플렉서(110a), 제 2 스캔 멀티플렉서(110b), 제 3 스캔 멀티플렉서(110c), 제 4 스캔 멀티플렉서(110d), 및 역-극성(inverted-polarity) NAND 게이트(130)를 포함한다. 각각의 스캔 멀티플렉서(110a-110d)는 D 플립-플롭들(120a-120d) 중 개별적인 하나에 커플링되며, 여기서, 제 1 스캔 멀티플렉서(110a)는 제 1 D 플립-플롭(120a)의 입력에 커플링되고, 제 2 스캔 멀티플렉서(110b)는 제 2 D 플립-플롭(120b)의 입력에 커플링되는 그러한 식이다. 스캔 회로(115)는 플롭 트레이(100)의 스캔 오버헤드를 구성한다.

[0013]

[0018] 정상 모드에서, 플롭 트레이(100)는 복수의 데이터 신호들 d0-d3을 병렬로 수신한다. 각각의 스캔 멀티플렉서(110a-110d)는 병렬 데이터 신호들 d0-d3 중 하나를 데이터 입력(도 1에서 "0"으로 라벨링됨)에서 수신하고, 개별적인 데이터 신호 d0-d3을 개별적인 D 플립-플롭(120a-120d)의 입력에 전달한다. 각각의 D 플립-플롭(120a-120d)은, 클록 신호 clk의 상승 또는 하강 엣지에서 개별적인 데이터 신호 d0-d3으로부터 데이터 값(예를 들어, 비트)을 캡쳐하고, 캡쳐된 데이터 값 q0-q3을 출력한다. 따라서, 각각의 클록 사이클 동안, 플롭 트레이(100)는, 클록 신호 clk의 상승 또는 하강 엣지에서 데이터 신호 d0-d3으로부터 병렬로 복수의 데이터 값들(예를 들어, 비트들)을 캡쳐하고, 캡쳐된 데이터 값들 q0-q3을 병렬로 출력한다. 도 1은 4개의 플립-플롭들을 포

함하는 4-비트 플롭 트레이의 예를 도시한다. 그러나, 본 개시는 이러한 예로 제한되지 않으며, 임의의 개수의 플립-플롭들을 포함하는 플롭 트레이에 적용될 수 있음이 인식될 것이다.

[0014] [0019] 스캔 모드에서, 제 1 스캔 멀티플렉서(110a)는 플롭 트레이(100)의 스캔 입력(도 1에서 "sin"으로 라벨링됨)을 제 1 플립-플롭(120a)의 입력에 커플링시킨다. 나머지 스캔 멀티플렉서들(110b-110d) 각각은 앞선 D 플립-플롭의 nq 출력을 개별적인 D 플립-플롭의 입력에 커플링시킨다. 예를 들면, 제 2 스캔 멀티플렉서(110b)는 제 1 D 플립-플롭(120a)의 nq 출력을 제 2 D 플립-플롭(120b)의 입력에 커플링시키고, 제 3 멀티플렉서(110c)는 제 2 D 플립-플롭(120b)의 nq 출력을 제 3 D 플립-플롭(120c)의 입력에 커플링시키는 그러한 식이다. 각각의 멀티플렉서의 스캔 입력은 도 1에서 "1"로 라벨링된다. 제 4 D 플립-플롭(120d)(마지막 플립-플롭)의 nq 출력은 NAND 게이트(130)의 인버팅 입력에 커플링된다. 결과적으로, 스캔 신호가 스캔 입력("sin")에서 플롭 트레이(100)에 입력되는 경우, 스캔 신호는 플롭 트레이(100)의 D 플립-플롭들(120a-120d)을 통해 순차적으로 전파된다. 스캔 신호는 최종적으로, NAND 게이트(130)의 출력("sout"으로 라벨링됨)에서 출력된다. 출력 스캔 신호는, 플롭 트레이(100)의 스캔 입력("sin")으로부터 스캔 출력("sout")까지의 스캔 경로 내의 인버전(inversion)들의 개수에 의존하여, 입력 스캔 신호에 대해 인버팅될 수도 있거나 또는 넌-인버팅(non-invert)될 수도 있다.

[0015] [0020] 따라서, 스캔 모드에서, 스캔 신호는 플롭 트레이(100)의 D 플립-플롭들(120a-120d)을 통해 스캔된다. 스캔 신호는 알려진 테스트 패턴을 포함할 수도 있고, 플롭 트레이(100)의 기능은, 알려진 테스트 패턴에 기초하여, 플롭 트레이(100)로부터의 출력 스캔 신호를 기대되는 출력 스캔 신호와 비교함으로써 평가될 수도 있다.

[0016] [0021] 도 1에 도시된 예에서, 플롭 트레이(100)의 동작 모드는 스캔 모드 입력(도 1에서 "scan"으로 라벨링됨)에서 수신되는 스캔 모드 신호에 의해 제어된다. 스캔 모드 신호는, 스캔 멀티플렉서가 개별적인 입력 데이터 신호 또는 스캔 신호를 개별적인 플립-플롭에 커플링시키는지 여부를 제어하기 위해 각각의 스캔 멀티플렉서(110a-110d)에 입력된다. 예를 들어, 스캔 모드 신호가 로직 0인 경우, 각각의 스캔 멀티플렉서(110a-110d)는 개별적인 입력 데이터 신호를 개별적인 플립-플롭에 커플링시킨다. 따라서, 스캔 모드 신호가 0인 경우 플롭 트레이는 정상 모드에서 동작한다. 스캔 모드 신호가 로직 1인 경우, 각각의 스캔 멀티플렉서(110a-110d)는 스캔 신호를 개별적인 플립-플롭에 커플링시킨다. 따라서, 스캔 모드 신호가 1인 경우 플롭 트레이는 스캔 모드에서 동작한다. 스캔 모드 신호는 또한, 도 1에 도시된 바와 같이, NAND 게이트(130)의 논-인버팅 입력에 커플링될 수도 있다. 스캔 모드 신호가 0(정상 모드)인 경우, NAND 게이트(130)의 출력은 1로 고정된다.

[0017] [0022] 도 2는 제 1 스캔 멀티플렉서(110a) 및 제 1 D 플립-플롭(120a)의 예시적인 구현을 도시한다. 제 1 스캔 멀티플렉서(110a)는 제 1 3-상태 회로(215) 및 제 2 3-상태 회로(220)를 포함하며, 여기서, 각각의 3-상태 회로는 4개의 트랜지스터들(예를 들어, MOS(metal-oxide-semiconductor) 트랜지스터들)을 포함한다. 제 1 및 제 2 3-상태 회로들(215 및 220)은, 스캔 모드 입력(도 2에서 "scan"으로 라벨링됨)에서 수신되는 스캔 모드 신호에 의해 제어된다. 3-상태 회로들(215 및 220)은, 스캔 모드 신호가 0인 경우 정상 모드에서 동작하고 스캔 모드 신호가 1인 경우 스캔 모드에서 동작한다.

[0018] [0023] 스캔 모드 신호가 0인 경우, 제 1 3-상태 회로(215)는 개별적인 입력 데이터 신호를 인버팅하고, 제 2 3-상태 회로(220)는 인버팅된 데이터 신호를 개별적인 D 플립-플롭(120a)의 입력에 전달한다. 도 2의 예에서, D 플립-플롭(120a)은 자신의 입력과 q 출력 사이에 홀수 개의 인버터들(즉, 인버터들(232, 234 및 236))을 갖는다. 홀수 개의 인버터들은 제 1 3-상태 회로(215)에 의한 로직 인버전을 원상태로 돌린다(undo). 결과적으로, 멀티플렉서(110a)의 데이터 입력으로부터 D 플립-플롭(120a)의 q 출력까지, 어떠한 로직 인버전도 존재하지 않는다.

[0019] [0024] 스캔 모드 신호가 1인 경우, 제 1 3-상태 회로(215)는 개별적인 데이터 입력을 차단한다. 제 2 3-상태 회로(220)는 개별적인 입력 스캔 신호를 인버팅하고, 인버팅된 스캔 신호를 개별적인 D 플립-플롭(120a)에 입력한다. 도 2의 예에서, D 플립-플롭(120a)은 자신의 입력과 nq 출력 사이에 짝수 개의 인버터들(즉, 인버터들(232 및 234))을 갖는다. 결과적으로, 멀티플렉서(110a)의 스캔 입력으로부터 D 플립-플롭(120a)의 nq 출력까지, 어떠한 로직 인버전도 존재하지 않는다.

[0020] [0025] 따라서, 정상 모드에서, 도 2의 스캔 멀티플렉서(110a)는 데이터 신호를 개별적인 플립-플롭(120a)에 출력하기 전에 입력 데이터 신호를 인버팅한다. 스캔 모드에서, 스캔 멀티플렉서(110a)는 스캔 신호를 개별적인 플립-플롭(120a)에 출력하기 전에 입력 스캔 신호를 인버팅한다. 따라서, 도 2의 스캔 멀티플렉서(110a)는 인버팅 멀티플렉서의 예이다.

- [0021] [0026] 플롭 트레이(100) 내의 나머지 스캔 멀티플렉서들(110b-110d) 각각은 또한, 도 2에 도시된 회로를 사용하여 구현될 수 있다. 나머지 스캔 멀티플렉서들(110b-110d) 각각에 대해, 멀티플렉서의 스캔 입력(도 1에서 "1"로 라벨링됨)은 앞선 D 플립-플롭(120a-120c)의 nq 출력에 커플링된다.

- [0022] [0027] 각각의 스캔 멀티플렉서(110a-110d)의 제 1 및 제 2 3-상태 회로들(215 및 220)을 구성하는 트랜ジ스터들은 칩 영역을 차지하고 전력을 소모한다. 따라서, 스캔 회로(115)의 영역 및/또는 전력 소모를 감소시키기 위해, 멀티플렉서들 내의 트랜ジ스터들의 개수를 감소시키는 것이 바람직하다.

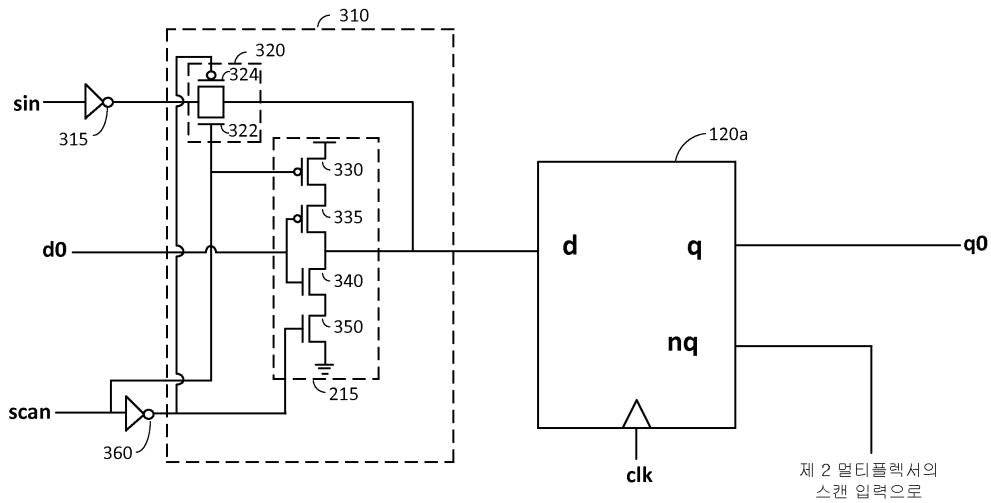

- [0023] [0028] 도 3은 본 개시의 일 실시예에 따른 스캔 멀티플렉서(310)를 도시한다. 도 3은, 플롭 트레이의 스캔 입력("sin")과 플롭 트레이의 제 1 플립-플롭(120a) 사이에 커플링되는 플롭 트레이의 제 1 스캔 멀티플렉서를 구현하는데 스캔 멀티플렉서(310)가 사용되는 예를 도시한다. 도 3에 도시된 스캔 멀티플렉서(310)를 사용하여 구현되는 스캔 멀티플렉서들을 포함하는 플롭 트레이의 예는 도 5를 참조하여 아래에서 설명된다.

- [0024] [0029] 스캔 멀티플렉서(310)에서, 도 2에 도시된 스캔 멀티플렉서(110a)의 제 2 3-상태 회로(220)는 전달 게이트(320)에 의해 대체된다. 전달 게이트(320)는, 제 2 3-상태 회로(220)에 대한 4개의 트랜ジ스터들과 비교되는 2개의 트랜ジ스터들을 포함하며, 이는 스캔 멀티플렉서(310) 내에서 2개의 트랜ジ스터들의 감소를 초래한다. 도 3에 도시된 예에서, 전달 게이트(320)는 별로 커플링된 n-타입 트랜ジ스터(322) 및 p-타입 트랜ジ스터(324)를 포함하며, 여기서, n-타입 트랜ジ스터(322)의 게이트는 스캔 모드 입력("scan")에 커플링되고, p-타입 트랜ジ스터(324)의 게이트는 스캔 모드 인버터(360)를 통해 스캔 모드 입력("scan")에 커플링된다. 따라서, n-타입 트랜ジ스터(322)의 게이트는 스캔 모드 신호에 의해 드라이빙(drive)되고, p-타입 트랜ジ스터(324)의 게이트는 스캔 모드 신호의 역에 의해 드라이빙된다. 트랜ジ스터들(322 및 324) 둘 모두는 스캔 모드에서 턴 온되고, 트랜ジ스터들(322 및 324) 둘 모두는 정상 모드에서 턴 오프된다.

- [0025] [0030] 스캔 모드 신호가 0(정상 모드)인 경우, 제 1 3-상태 회로(215)는 입력 데이터 신호를 인버팅하고, 인버팅된 데이터 신호를 플롭 트레이의 제 1 플립-플롭(120a)의 입력에 출력한다. 제 1 3-상태 회로(215)는 아래에서 더 상세히 설명된다. 전달 게이트(320)는 제 1 D 플립-플롭(120a)의 입력으로부터의 입력 스캔 신호를 차단한다. 따라서, 정상 모드에서, 스캔 멀티플렉서(310)는 도 2에 도시된 제 1 스캔 멀티플렉서(110a)와 기능적으로 동등하다.

- [0026] [0031] 스캔 모드 신호가 1(스캔 모드)인 경우, 제 1 3-상태 회로(215)는 제 1 D 플립-플롭(120a)의 입력으로부터의 입력 데이터 신호를 차단한다. 전달 게이트(320)는 입력 스캔 신호를 제 1 D 플립-플롭(120a)의 입력에 전달한다. 스캔 모드에서, 전달 게이트(320)는, 도 2에 도시된 제 1 멀티플렉서(110a)의 제 2 3-상태 회로(220)와 달리 입력 스캔 신호를 인버팅하지 않는다. 따라서, 스캔 모드에서, 스캔 멀티플렉서(310)는 인버전 없이 스캔 신호를 제 1 플립-플롭(120a)에 전달한다.

- [0027] [0032] 일 실시예에서, 인버터(315)는, 스캔 멀티플렉서(310)에 입력되기 전에 스캔 신호를 인버팅하기 위해, 플롭 트레이의 스캔 입력("sin")과 스캔 멀티플렉서(310) 사이에 커플링될 수도 있다. 따라서, 스캔 멀티플렉서(310) 내의 전달 게이트(320)와 인버터(315)의 결합은 도 2에 도시된 제 2 3-상태 회로(220)와 기능적으로 동등할 수도 있다.

- [0028] [0033] 플롭 트레이 내의 나머지 스캔 멀티플렉서들 각각은 또한 도 3에 도시된 멀티플렉서(310)를 사용하여 구현될 수 있다. 나머지 스캔 멀티플렉서들 각각에 대해, 전달 게이트(320)의 입력은 개재(intervening) 인버터 없이 앞선 D 플립-플롭의 nq 출력에 커플링될 수도 있다.

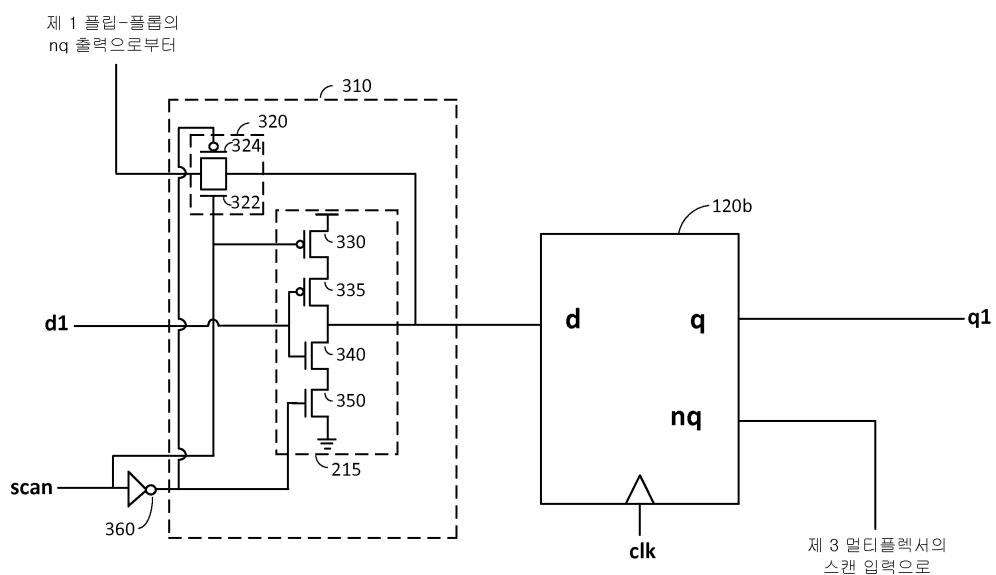

- [0029] [0034] 이와 관련하여, 도 4는, 스캔 멀티플렉서(310)가 플롭 트레이 내의 제 2 스캔 멀티플렉서를 구현하는데 사용되는 예를 도시한다. 이러한 예에서, 전달 게이트(320)는 개재 인버터 없이 (도 3에 도시된) 제 1 D 플립-플롭(120a)의 nq 출력에 커플링된다. 위에 설명된 바와 같이, 전달 게이트(320)는 도 2에 도시된 제 2 3-상태 회로(220)를 대체하며, 이는, 멀티플렉서(310) 내에서 2개의 트랜ジ스터들의 감소를 초래한다.

- [0030] [0035] 스캔 모드 신호가 0(정상 모드)인 경우, 제 1 3-상태 회로(215)는 입력 데이터 신호를 인버팅하고, 인버팅된 데이터 신호를 플롭 트레이의 제 2 D 플립-플롭(120b)의 입력에 출력한다. 전달 게이트(320)는 제 2 D 플립-플롭(120b)의 입력으로부터의 스캔 신호를 차단한다.

- [0031] [0036] 스캔 모드 신호가 1(스캔 모드)인 경우, 제 1 3-상태 회로(215)는 제 2 D 플립-플롭(120b)의 입력으로부터의 입력 데이터 신호를 차단한다. 전달 게이트(320)는 (도 3에 도시된) 제 1 D 플립-플롭(120a)의 nq 출력으로부터 제 2 D 플립-플롭(120b)의 입력으로 스캔 신호를 전달한다. 제 2 D 플립-플롭(120b)의 nq 출력으로부터

의 스캔 신호는 플롭 트레이 내의 제 3 스캔 멀티플렉서에 커플링된다.

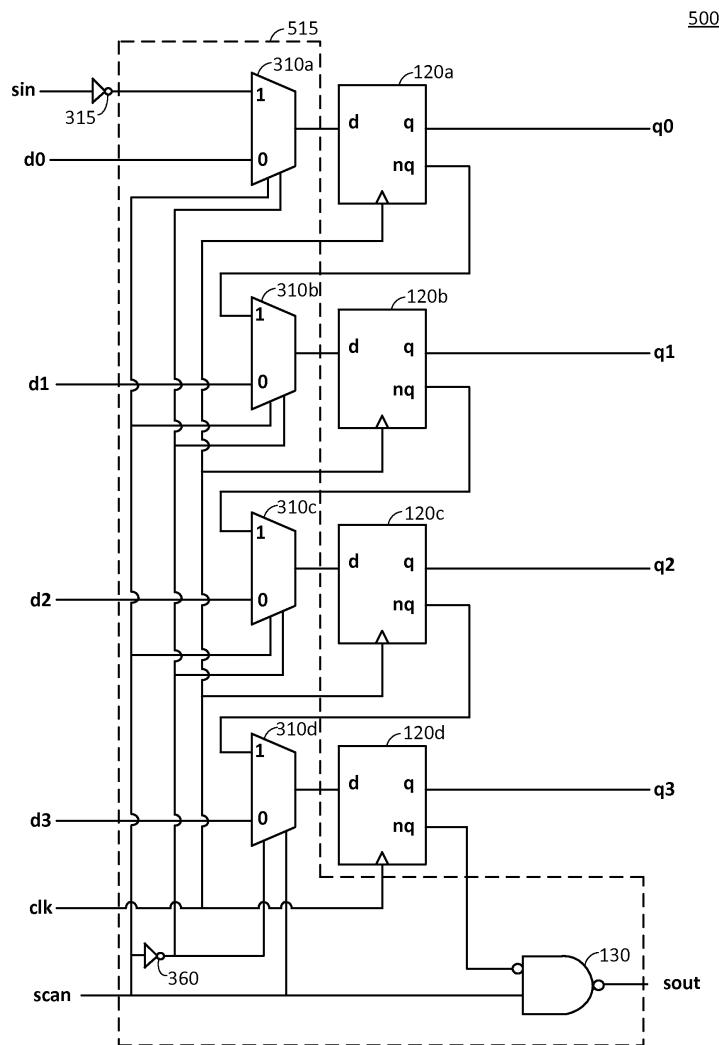

[0032] [0037] 도 5는, 도 1에서의 스캔 회로(115)가 본 개시의 일 실시예에 따른 스캔 회로(515)에 의해 대체되는 스캔 가능한 플롭 트레이(500)의 예를 도시한다. 스캔 회로(515)는 제 1 스캔 멀티플렉서(310a), 제 2 스캔 멀티플렉서(310b), 제 3 스캔 멀티플렉서(310c), 및 제 4 스캔 멀티플렉서(310d)를 포함하며, 여기서, 스캔 멀티플렉서들(310a-310d) 각각은 도 3에 도시된 스캔 멀티플렉서(310)를 사용하여 구현된다. 스캔 회로(515)는 또한, 스캔 멀티플렉서들(310a-310d)에 의해 공유되는 스캔 모드 인버터(360)를 포함한다. 스캔 모드 인버터(360)는, 스캔 모드 신호의 역을 각각의 스캔 멀티플렉서(310a-310d)에 제공한다. 플롭 트레이(500)는 또한, 플롭 트레이(500)의 스캔 입력("sin")과 제 1 스캔 멀티플렉서(310a)의 스캔 입력("1"로 라벨링됨) 사이에 커플링되는 인버터(315)를 포함한다.

[0033] [0038] 제 1 스캔 멀티플렉서(310)의 스캔 입력("1"로 라벨링됨)은 인버터(315)에 커플링된다. 나머지 스캔 멀티플렉서들(310b-310d) 각각의 스캔 입력("1"로 라벨링됨)은 개별 인버터 없이 앞선 D 플립-플롭(120a-120c)의 nq 출력에 커플링된다. 스캔 멀티플렉서들(310a-310d) 각각의 데이터 입력("0"으로 라벨링됨)은 개별적인 데이터 신호 d0-d3에 커플링되고, 스캔 멀티플렉서들(310a-310d) 각각의 출력은 개별적인 플립-플롭(120a-120d)의 입력에 커플링된다.

[0034] [0039] 정상 모드에서, 각각의 스캔 멀티플렉서(310a-310d)는 개별적인 3-상태 회로(215)를 사용하여 개별적인 데이터 신호 d0-d3을 인버팅하고, 인버팅된 데이터 신호를 개별적인 D 플립-플롭(120a-120d)의 입력에 출력한다. 각각의 D 플립-플롭(120a-120d)은 클록 신호 clk의 상승 또는 하강 엣지에서 개별적인 데이터 신호 d0-d3으로부터 데이터 값(예를 들어, 비트)을 캡처하고, 캡처된 데이터 값 q0-q3을 출력한다.

[0035] [0040] 스캔 모드에서, 인버터(315)는, 인버팅된 입력 스캔 신호를 생성하기 위해, 플롭 트레이(500)의 스캔 입력("sin")에서의 스캔 신호를 인버팅한다. 제 1 스캔 멀티플렉서(310a)는 인버팅된 입력 스캔 신호를 제 1 D 플립-플롭(120a)의 입력에 전달한다. 나머지 스캔 멀티플렉서들(310b-310c) 각각은, 앞선 플립-플롭(120a-120c)으로부터의 스캔 신호 출력을 인버전 없이 개별적인 플립-플롭(120b-120d)의 입력에 커플링시킨다. 스캔 신호는 최종적으로, NAND 게이트(130)의 출력("sout"으로 라벨링됨)에서 출력된다. 출력 스캔 신호는, 플롭 트레이(500)의 스캔 입력("sin")으로부터 스캔 출력("sout")까지의 스캔 경로 내의 인버전들의 개수에 의존하여, 입력 스캔 신호에 대해 인버팅될 수도 있거나 또는 논-인버팅될 수도 있다.

[0036] [0041] 따라서, 스캔 모드에서, 스캔 신호는 플롭 트레이(500)의 D 플립-플롭들(120a-120d)을 통해 스캔된다. 스캔 신호는 알려진 테스트 패턴을 포함할 수도 있고, 플롭 트레이(500)의 기능은, 알려진 테스트 패턴에 기초하여, 플롭 트레이(500)로부터의 출력 스캔 신호를 기대되는 출력 스캔 신호와 비교함으로써 평가될 수도 있다. 도 5에서의 플롭 트레이(500)에 대한 기대되는 출력 스캔 신호는, 주어진 테스트 패턴에 대해, 도 1에서의 플롭 트레이(100)에 대한 기대되는 출력 스캔 신호와 상이할 수도 있다. 이것은, 도 5에서의 플롭 트레이(500)가 스캔 경로에서 상이한 개수의 인버전들을 갖기 때문에, 스캔 멀티플렉서들(310a-310d)이 스캔 신호를 인버팅하지 않는다는 사실로 인해서이다.

[0037] [0042] 도 3에 도시된 멀티플렉서(310)를 사용하여 플롭 트레이(500)의 각각의 스캔 멀티플렉서(310a-310d)를 구현하는 것은, 플롭 트레이(500) 내의 트랜지스터들의 개수에서 상당한 감소를 유도할 수 있다. 플롭 트레이(500) 내의 제 1 스캔 멀티플렉서(310a)는, 플롭 트레이(500)의 스캔 입력("sin")과 제 1 스캔 멀티플렉서(310a) 사이에 커플링된 인버터(315) 때문에, 트랜지스터들의 개수에서의 감소에 기여하지 않을 수도 있다. 그러나, 플롭 트레이(500) 내의 나머지 스캔 멀티플렉서들(310b-310d)은 각각은 트랜지스터 수를 2개만큼 감소시킨다. 이것은, 나머지 스캔 멀티플렉서들(310b-310d) 각각에 대해, 개별적인 전달 게이트(320)가 도 2에 도시된 제 2 3-상태 회로(220)에 대한 4개의 트랜지스터들과 비교하여 2개의 트랜지스터들을 사용하기 때문이다. 예를 들어, 4-비트 플롭 트레이(도 5에 도시된 예)에 대해, 이것은 도 1에서의 플롭 트레이(100)와 비교하여 6개의 트랜지스터들의 감소(3개의 나머지 멀티플렉서들(310b-310d) 각각에 대해 2개의 트랜지스터의 감소)를 유도한다. 8개의 D 플립-플롭들을 포함하는 8-비트 플롭 트레이에 대해 이것은 14개의 트랜지스터들의 감소를 유도하며, 16개의 D 플립-플롭들을 포함하는 16-비트 플롭 트레이에 대해 이것은 30개의 트랜지스터들의 감소를 유도한다. 스캔 회로(515) 내의 트랜지스터들의 개수의 감소는 스캔 회로에 의해 차지되는 칩 영역을 감소시키고 전력 소모를 감소시킨다.

[0038] [0043] 각각의 D 플립-플롭(120a-120d)이 자신의 입력에서의 신호(예를 들어, 개별적인 데이터 신호 d0-d3 또는 스캔 신호)로부터 값을 적절히 캡처하기 위해, 값은 클록 clk의 상승 또는 하강 엣지 이후의 시간 기간에 대해 안정될 필요가 있다(유지 시간(hold time)으로 지정됨). 신호가 유지 시간 동안 값을 변경하는 경우, 유지 시

간 위반(violation)이 발생하고 플립-플롭은 준안정 상태로 진입할 수도 있다. 정상 모드에서 유지 시간 위반을 방지하기 위해, 플립-플롭의 입력에서 충분한 유지 시간 마진(margin)을 제공하도록 플립-플롭으로의 데이터 경로에서의 지연이 조절될 수도 있다. 유지 시간 마진은, 클록 clk의 상승 또는 하강 엣지 이후 신호에서의 변경에 대해 기대되는 시간과 유지 시간 사이의 차이일 수도 있다. 더 큰 유지 시간 마진은 프로세스 및 동작 변화들에 대해 더 큰 마진을 제공함으로써, 플립-플롭의 강건성(robustness)을 개선한다.

[0039] [0044] 스캔 모드에서, 도 5에서의 제 2, 제 3, 및 제 4 플립-플롭들(120b-120d) 각각에 대한 유지 시간 마진은, 도 1에서의 제 2, 제 3, 및 제 4 플립-플롭들(120b-120d)과 비교하여 대략적으로 하나의 인버터 지연 만큼 감소된다. 이것은, 도 5에서의 개별적인 멀티플렉서들(310b-310d) 각각이 도 1에서의 개별적인 멀티플렉서들(110b-110d)과 달리 스캔 신호를 인버팅하지 않기 때문이다. 그러나, 스캔 모드에서의 유지 시간 마진의 감소에도 불구하고, 유지 시간 마진은 테스팅 동안 유지 시간 위반들을 방지하기에 충분할 만큼 크게 유지될 수도 있다. 예를 들어, 플립-플롭들(120b-120d) 각각이 도 2에 도시된 플립-플롭을 사용하여 구현되는 경우, 스캔 모드에서의 유지 시간 마진이 유지 시간 위반들을 방지하기에 충분할 만큼 크게 유지된다는 것이 발견된다. 제 1 플립-플롭(120a)에 대한 유지 시간 마진은, 제 1 멀티플렉서(110a)에 커플링된 인버터(315)가 인버터 지연을 부가하기 때문에 대략적으로 동일할 수도 있다.

[0040] [0045] 도 3을 다시 참조하여 이제 제 1 3-상태 회로(215)가 더 상세히 설명될 것이다. 제 1 3-상태 회로(215)는 3-상태 인버터의 예이고, 제 1 p-타입 트랜지스터(330), 제 2 p-타입 트랜지스터(335), 제 1 n-타입 트랜지스터(350), 및 제 2 n-타입 트랜지스터(340)를 포함한다. 트랜지스터들(330, 335, 340, 및 350)은, 전력 공급부와 접지 사이에서 다른 트랜지스터의 상단 상에 적층(stack)된다. 더 구체적으로는, 제 1 p-타입 트랜지스터(330) 소스는 전력 공급부에 커플링되고, 제 2 p-타입 트랜지스터(335)의 소스는 제 1 p-타입 트랜지스터(330)의 드레인에 커플링되고, 제 2 n-타입 트랜지스터(340)의 드레인은 제 2 p-타입 트랜지스터(335)의 드레인에 커플링되고, 제 1 n-타입 트랜지스터(350)의 드레인은 제 2 n-타입 트랜지스터(340)의 소스에 커플링되고, 제 1 n-타입 트랜지스터(350)의 소스는 접지에 커플링된다.

[0041] [0046] 제 1 p-타입 트랜지스터(330)의 게이트는 스캔 모드 입력("scan")에 커플링되고, 제 1 n-타입 트랜지스터(350)의 게이트는, 도 5에 도시된 바와 같이, 스캔 멀티플렉서들(310a-310d)에 의해 공유될 수도 있는 스캔 모드 인버터(360)를 통해 스캔 모드 입력("scan")에 커플링된다. 따라서, 제 1 p-타입 트랜지스터(330)의 게이트는 스캔 모드 신호에 의해 드라이빙되고, 제 1 n-타입 트랜지스터(350)의 게이트는 스캔 모드 신호의 역에 의해 드라이빙된다. 제 2 p-타입 트랜지스터(335) 및 제 2 n-타입 트랜지스터(340)의 게이트들은 멀티플렉서(310)의 데이터 입력에 커플링된다.

[0042] [0047] 스캔 모드 신호가 0(정상 모드)인 경우, 제 1 p-타입 트랜지스터(330) 및 제 1 n-타입 트랜지스터(350) 둘 모두는 턴 온된다. 결과적으로, 제 1 p-타입 트랜지스터(330)는 제 2 p-타입 트랜지스터(335)의 소스를 전력 공급부에 커플링시키고, 제 1 n-타입(350)은 제 2 n-타입 트랜지스터(340)의 소스를 접지에 커플링시킨다. 이것은, 제 2 p-타입 트랜지스터(335)와 제 2 n-타입 트랜지스터(340)가 상보형 인버터로서 동작하는 것을 가능하게 하며, 여기서, 인버터의 입력은 제 2 p-타입 트랜지스터(335) 및 제 2 n-타입 트랜지스터(340)의 게이트들에 로케이팅(locate)되고, 인버터의 출력은 제 2 p-타입 트랜지스터(335) 및 제 2 n-타입 트랜지스터(340)의 드레인들에 로케이팅된다. 인버터는, 개별적인 데이터 신호를 인버팅하고, 인버팅된 데이터 신호를 개별적인 플립-플롭에 출력한다.

[0043] [0048] 스캔 모드 신호가 1(스캔 모드)인 경우, 제 1 p-타입 트랜지스터(330) 및 제 1 n-타입 트랜지스터(350) 둘 모두는 턴 오프된다. 이것은, 제 2 p-타입 트랜지스터(335)의 소스를 전력 공급부로부터 분리시키고, 제 2 n-타입 트랜지스터(340)의 소스를 접지로부터 분리시킨다. 결과적으로, 개별적인 플립-플롭의 입력으로부터의 개별적인 데이터 신호는 차단된다.

[0044] [0049] 도 6은 본 개시의 일 실시예에 따른, 감소된 스캔 오버헤드로 플롭 트레이를 스캔하기 위한 방법(600)의 흐름도이다.

[0045] [0050] 단계(610)에서, 정상 모드에서, 3-상태 회로를 사용하여 입력 데이터 신호가 인버팅되고 플립-플롭의 입력에 출력된다. 예를 들어, 단계(610)는 도 3에서의 3-상태 회로(215)를 사용하여 수행될 수도 있으며, 여기서, 3-상태 회로(215)는, 0의 스캔 모드 신호를 스캔 모드 입력("scan")에 입력함으로써 정상 모드에서 동작된다.

[0046] [0051] 단계(620)에서, 스캔 모드에서, 3-상태 회로를 사용하여 플립-플롭의 입력으로부터의 입력 데이터 신호

가 차단된다. 예를 들어, 단계(620)는 도 3에서의 3-상태 회로(215)를 사용하여 수행될 수도 있으며, 여기서, 3-상태 회로(215)는, 1의 스캔 모드 신호를 스캔 모드 입력("scan")에 입력함으로써 스캔 모드에서 동작된다.

[0047] 단계(630)에서, 스캔 모드에서, 전달 게이트를 사용하여 스캔 신호가 플립-플롭의 입력에 전달된다. 예를 들어, 단계(630)는 도 3에서의 전달 게이트(320)를 사용하여 수행될 수도 있으며, 여기서, 전달 게이트(320)는, 1의 스캔 모드 신호를 스캔 모드 입력("scan")에 입력함으로써 스캔 모드에서 동작된다. 전달 게이트(320)는 3-상태 회로보다 더 적은 트랜지스터들을 사용하여 구현될 수도 있으며, 그에 따라 스캔 오버헤드를 감소시킨다.

[0048] 단계(640)에서, 정상 모드에서, 전달 게이트를 사용하여 플립-플롭의 입력으로부터의 스캔 신호가 차단된다. 예를 들어, 단계(640)는 도 3에서의 전달 게이트(320)를 사용하여 수행될 수도 있으며, 여기서, 전달 게이트(320)는, 0의 스캔 모드 신호를 스캔 모드 입력("scan")에 입력함으로써 정상 모드에서 동작된다.

[0049] 당업자들은, 본 개시의 실시예들이 본 명세서에 설명된 예들로 제한되지 않는다는 것을 인식할 것이다. 예를 들어, 스캔 멀티플렉서의 스캔 입력은 nq 출력 대신 앞선 플립-플롭의 q 출력에 커플링될 수도 있다. 또한, 본 개시의 실시예들은, 다양한 타입들의 플립-플롭들을 포함하는 플롭 트레이들에서 사용될 수도 있으며, 따라서, 도 2에 도시된 예시적인 플립-플롭들로 제한되지 않는다. 추가로, 본 개시의 실시예들은, 예를 들어, 2개의 플립-플롭들, 4개의 플립-플롭들, 8개의 플립-플롭들, 16개의 플립-플롭들 등을 포함하는 임의의 개수의 플립-플롭들을 포함하는 플롭 트레이들에서 사용될 수도 있다.

[0050] 당업자들은, 본 명세서에 설명된 회로들이 다양한 트랜지스터 타입들을 사용하여 실현될 수도 있으며, 따라서 도면들에 도시된 특정한 트랜지스터 타입들로 제한되지 않는다는 것을 인식할 것이다. 예를 들어, 양극성 접합 트랜지스터(bipolar junction transistor)들, 접합형 전계 효과 트랜지스터(junction field effect transistor) 또는 임의의 다른 트랜지스터 타입과 같은 트랜지스터 타입들이 사용될 수도 있다. 당업자들은 또한, 본 명세서에 설명된 회로들이 COMS, BJT(bipolar junction transistor), BiCMOS(bipolar-CMOS), SiGe(silicon germanium), GaAs(gallium arsenide) 등과 같은 다양한 IC 프로세스 기술들로 제조될 수도 있다는 것을 인식할 것이다.

[0051] 본 개시의 이전 설명은 임의의 당업자가 본 개시를 사용 또는 실시할 수 있도록 제공된다. 본 개시에 대한 다양한 변형들은 당업자들에게 용이하게 명백할 것이며, 본 명세서에 정의된 일반적인 원리들은 본 개시의 사상 또는 범위로부터 벗어나지 않으면서 다른 변형들에 적용될 수도 있다. 따라서, 본 개시는 본 명세서에 설명된 예들로 제한되도록 의도되는 것이 아니라, 본 명세서에 기재된 원리들 및 신규한 특성들과 일치하는 가장 넓은 범위에 부합할 것이다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

**도면6**