(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2016년09월27일

(11) 등록번호 10-1660558

(24) 등록일자 2016년09월21일

- (51) 국제특허분류(Int. Cl.)

**H04N 7/24** (2011.01)

(21) 출원번호 10-2011-7020609

(22) 출원일자(국제) 2009년12월11일

심사청구일자 2014년12월11일

(85) 번역문제출일자 2011년09월02일

(65) 공개번호 10-2011-0116206

(43) 공개일자 2011년10월25일

(86) 국제출원번호 PCT/US2009/006528

(87) 국제공개번호 WO 2010/090630

국제공개일자 2010년08월12일

(30) 우선권주장

61/149,495 2009년02월03일 미국(US)

(56) 선행기술조사문헌

WO2009003499 A1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 29 항

심사관 : 박상철

(54) 발명의 명칭 **비트 깊이 스케일리밸리티에서 스무드 참조 프레임에 의한 모션 보상을 하는 방법들 및 장치**

**(57) 요 약**

비트 깊이 스케일리밸리티에서 스무드 레퍼런스 프레임으로의 모션 보상을 위한 방법들 및 장치들이 제공된다. 장치는 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행된 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인터-레이어 레지듀 예측을 생성함으로써 그 일부에 대한 픽쳐 데이터를 인코딩하기 위한 인코더(100)를 포함한다. 인버스 톤 매핑 동작은 레지듀 도메인에서 픽셀 도메인으로 시프트된다.

**대 표 도** - 도1

## 명세서

### 청구범위

#### 청구항 1

톤 매핑된 인핸스먼트 레이어 레퍼런스 픽처(tone mapped enhancement layer reference picture)를 베이스 레이어 레지듀(base layer residue)와 결합하여 스무드 베이스 레이어 레퍼런스 픽처(smooth base layer reference picture)를 형성하고, 그 다음에 비트 깊이 스케일리밸리티(bit depth scalability)에 대해 픽셀 도메인에서 수행되는 상기 스무드 베이스 레이어 레퍼런스 픽처 상에서의 인버스 톤 매핑 동작(inverse tone mapping operation)을 이용하여 픽처의 적어도 일부에 대한 인버스 톤 매핑된 인터-레이어 레지듀 예측(inverse tone mapped inter-layer residue prediction)을 생성함으로써 상기 픽처의 상기 적어도 일부에 대한 픽처 데이터를 인코딩하기 위한 인코더(100)

를 포함하고,

상기 인버스 톤 매핑 동작이 수행되는 도메인은 레지듀 도메인으로부터 상기 픽셀 도메인으로 시프트되는, 장치.

#### 청구항 2

제1항에 있어서, 상기 인코더는 인핸스먼트 레이어 레퍼런스(enhancement layer reference)를 이용하여 모션 보상을 수행함으로써 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 예측을 베이스 레이어 레퍼런스에 톤 매핑하여 톤 매핑된 예측을 생성하며, 상기 픽처의 적어도 일부에 대한 베이스 레이어 레지듀를 상기 톤 매핑된 예측과 조합하여 스무드 베이스 레이어 레퍼런스(smooth base layer reference)를 획득하고, 상기 스무드 베이스 레이어 레퍼런스를 인버스 톤 매핑하여 인버스 톤 매핑된 예측을 생성함으로써 상기 인터-레이어 레지듀 예측을 생성하며,

상기 인코더는 상기 인버스 톤 매핑된 예측을 이용하여 모션 추정 및 모션 보상을 수행함으로써 모션 벡터를 획득하고, 상기 모션 벡터, 및 상기 인버스 톤 매핑된 예측과 상기 픽처 사이의 에러를 인코딩하여 전송하는 장치.

#### 청구항 3

제2항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스와 동일한 비트 깊이를 가지고 있는 장치.

#### 청구항 4

제2항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스보다 큰 비트 깊이를 가지고 있는 장치.

#### 청구항 5

제2항에 있어서, 상기 베이스 레이어 레지듀는 공간적으로 업-샘플링되어 공간적으로 업-샘플링된 베이스 레이어 레지듀를 획득하고, 상기 공간적으로 업-샘플링된 베이스 레이어 레지듀는 상기 톤 매핑된 예측과 조합되어 상기 스무드 베이스 레이어 레퍼런스를 획득하는 장치.

#### 청구항 6

제2항에 있어서, 매크로블록 레벨 구문(macroblock level syntax)에서의 플래그는 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드의 이용을 시그널링하는데 이용되는 장치.

#### 청구항 7

제2항에 있어서, 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드는, 상기 스무드 베이스 레이어 레퍼런스에 포인팅하는 엔트리가 상기 인핸스먼트 레이어에 대한 기준의 레퍼런스 리스트에 부가되는 식으로, 기준의 인터 모드들에 내장되어 보내지는 장치.

#### 청구항 8

톤 매핑된 인핸스먼트 레이어 레퍼런스 픽처를 베이스 레이어 레지듀와 결합하여 스무드 베이스 레이어 레퍼런스 픽처를 형성하고, 그 다음에 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행되는 상기 스무드 베이스 레이어 레퍼런스 픽처 상에서의 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인버스 톤 매핑된 인터-레이어 레지듀 예측을 생성함으로써 상기 픽처의 상기 적어도 일부에 대한 픽처 데이터를 인코딩하는 단계

를 포함하고,

상기 인버스 톤 매핑 동작이 수행되는 도메인은 레지듀 도메인으로부터 상기 픽셀 도메인으로 시프트되는, 방법(400).

#### 청구항 9

제8항에 있어서, 상기 인터-레이어 레지듀 예측을 생성하는 것은,

인핸스먼트 레이어 레퍼런스를 이용하여 모션 보상을 수행함으로써 인핸스먼트 레이어 예측을 생성하는 것(425);

상기 인핸스먼트 레이어 예측을 베이스 레이어 레퍼런스에 톤 매핑하여 톤 매핑된 예측을 생성하는 것(430);

상기 픽처의 적어도 일부에 대한 베이스 레이어 레지듀를 상기 톤 매핑된 예측과 조합하여 스무드 베이스 레이어 레퍼런스를 획득하는 것(440); 및

상기 스무드 베이스 레이어 레퍼런스를 인버스 톤 매핑하여 인버스 톤 매핑된 예측을 생성하는 것(455)

을 포함하고,

상기 인코딩하는 단계는,

상기 인버스 톤 매핑된 예측을 이용하여 모션 추정 및 모션 보상을 수행함으로써 모션 벡터를 획득하는 단계, 및

상기 모션 벡터, 및 상기 인버스 톤 매핑된 예측과 상기 픽처 사이의 에러를 인코딩하여 전송하는 단계를 더 포함하는 방법.

#### 청구항 10

제9항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스와 동일한 비트 깊이를 가지고 있는 방법.

#### 청구항 11

제9항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스보다 큰 비트 깊이를 가지고 있는 방법.

#### 청구항 12

제9항에 있어서, 상기 베이스 레이어 레지듀는 공간적으로 업-샘플링되어 공간적으로 업-샘플링된 베이스 레이어 레지듀를 획득하고, 상기 공간적으로 업-샘플링된 베이스 레이어 레지듀는 상기 톤 매핑된 예측과 조합되어 상기 스무드 베이스 레이어 레퍼런스를 획득하는 방법.

#### 청구항 13

제9항에 있어서, 매크로블록 레벨 구문에서의 플래그는 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하

는 인터-레이어 레지듀 예측 모드의 이용을 시그널링하는데 이용되는 방법.

#### 청구항 14

제9항에 있어서, 상기 스무드 베이스 레이어 레퍼런스에 포인팅하는 엔트리가 상기 인핸스먼트 레이어에 대한 기준의 레퍼런스 리스트에 부가되는 식으로, 기준의 인터 모드들에 내장된 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드를 보내는 단계를 더 포함하는 방법.

#### 청구항 15

톤 매핑된 인핸스먼트 레이어 레퍼런스 픽처를 베이스 레이어 레지듀와 결합하여 스무드 베이스 레이어 레퍼런스 픽처를 형성하고, 그 다음에 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행되는 상기 스무드 베이스 레이어 레퍼런스 픽처 상에서의 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인버스 톤 매핑된 인터-레이어 레지듀 예측을 생성함으로써 상기 픽처의 상기 적어도 일부에 대한 픽처 데이터를 디코딩하기 위한 디코더(200)

를 포함하고,

상기 인버스 톤 매핑 동작이 수행되는 도메인은 레지듀 도메인으로부터 상기 픽셀 도메인으로 시프트되는, 장치.

#### 청구항 16

제15항에 있어서, 상기 디코더는 인핸스먼트 레이어 레퍼런스를 이용하여 모션 보상을 수행함으로써 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 예측을 베이스 레이어 레퍼런스에 톤 매핑하여 톤 매핑된 예측을 생성하며, 상기 픽처의 적어도 일부에 대한 베이스 레이어 레지듀를 상기 톤 매핑된 예측과 조합하여 스무드 베이스 레이어 레퍼런스를 획득하고, 상기 스무드 베이스 레이어 레퍼런스를 인버스 톤 매핑하여 인버스 톤 매핑된 예측을 생성함으로써 상기 인터-레이어 레지듀 예측을 생성하고,

상기 디코더는 상기 인버스 톤 매핑된 예측을 이용하여 모션 추정 및 모션 보상을 수행함으로써 모션 벡터를 획득하고, 상기 모션 벡터, 및 상기 인버스 톤 매핑된 예측과 상기 픽처 사이의 에러에 기초하여 상기 픽처의 적어도 일부의 재구성된 버전을 생성하는 장치.

#### 청구항 17

제16항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스와 동일한 비트 깊이를 가지고 있는 장치.

#### 청구항 18

제16항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스보다 큰 비트 깊이를 가지고 있는 장치.

#### 청구항 19

제16항에 있어서, 상기 베이스 레이어 레지듀는 공간적으로 업-샘플링되어 공간적으로 업-샘플링된 베이스 레이어 레지듀를 획득하고, 상기 공간적으로 업-샘플링된 베이스 레이어 레지듀는 상기 톤 매핑된 예측과 조합되어 상기 스무드 베이스 레이어 레퍼런스를 획득하는 장치.

#### 청구항 20

제16항에 있어서, 매크로블록 레벨 구문에서의 플래그는 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드의 이용을 시그널링하는데 이용되는 장치.

#### 청구항 21

제16항에 있어서, 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드는, 상기 스무드 베이스 레이어 레퍼런스에 포인팅하는 엔트리가 상기 인핸스먼트 레이어에 대한 기준의 레퍼런스

리스트에 부가되는 식으로, 기존의 인터 모드들에 내장되어 수신되는 장치.

### 청구항 22

톤 매핑된 인핸스먼트 레이어 레퍼런스 픽처를 베이스 레이어 레지듀와 결합하여 스무드 베이스 레이어 레퍼런스 픽처를 형성하고, 그 다음에 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행되는 상기 스무드 베이스 레이어 레퍼런스 픽처 상에서의 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인버스 톤 매핑된 인터-레이어 레지듀 예측을 생성함으로써 상기 픽처의 상기 적어도 일부에 대한 픽처 데이터를 디코딩하는 단계

를 포함하고,

상기 인버스 톤 매핑 동작이 수행되는 도메인은 레지듀 도메인으로부터 상기 픽셀 도메인으로 시프트되는(600), 방법.

### 청구항 23

제22항에 있어서, 상기 인터-레이어 레지듀 예측을 생성하는 것은,

인핸스먼트 레이어 레퍼런스를 이용하여 모션 보상을 수행함으로써 인핸스먼트 레이어 예측을 생성하는 것(625);

상기 인핸스먼트 레이어 예측을 베이스 레이어 레퍼런스에 톤 매핑하여 톤 매핑된 예측을 생성하는 것(630);

상기 픽처의 적어도 일부에 대한 베이스 레이어 레지듀를 상기 톤 매핑된 예측과 조합하여 스무드 베이스 레이어 레퍼런스를 획득하는 것(640); 및

상기 스무드 베이스 레이어 레퍼런스를 인버스 톤 매핑하여 인버스 톤 매핑된 예측을 생성하는 것(655)

을 포함하고,

상기 디코딩하는 단계는,

상기 인버스 톤 매핑된 예측을 이용하여 모션 추정 및 모션 보상을 수행함으로써 모션 벡터를 획득하는 단계, 및

상기 모션 벡터, 및 상기 인버스 톤 매핑된 예측과 상기 픽처 사이의 에러에 기초하여 상기 픽처의 적어도 일부의 재구성된 베판을 생성하는 단계(670)를 포함하는 방법.

### 청구항 24

제23항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스와 동일한 비트 깊이를 가지고 있는 방법.

### 청구항 25

제23항에 있어서, 상기 모션 보상은 상기 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 상기 인핸스먼트 레이어 예측을 생성하고, 상기 인핸스먼트 레이어 레퍼런스는 상기 베이스 레이어 레퍼런스보다 큰 비트 깊이를 가지고 있는 방법.

### 청구항 26

제23항에 있어서, 상기 베이스 레이어 레지듀는 공간적으로 업-샘플링되어 공간적으로 업-샘플링된 베이스 레이어 레지듀를 획득하고, 상기 공간적으로 업-샘플링된 베이스 레이어 레지듀는 상기 톤 매핑된 예측과 조합되어 상기 스무드 베이스 레이어 레퍼런스를 획득하는 방법.

### 청구항 27

제23항에 있어서, 매크로블록 레벨 구문에서의 플래그는 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드의 이용을 시그널링하는데 이용되는 방법.

## 청구항 28

제23항에 있어서, 상기 스무드 베이스 레이어 레퍼런스에 포인팅하는 엔트리가 상기 인핸스먼트 레이어에 대한 기존의 레퍼런스 리스트에 부가되는 식으로, 기존의 인터 모드들에 내장된 상기 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드를 수신하는 단계를 더 포함하는 방법.

## 청구항 29

비디오 신호 데이터가 인코딩된 컴퓨터-판독가능한 저장 매체로서,

톤 매핑된 인핸스먼트 레이어 레퍼런스 픽처를 베이스 레이어 레지듀와 결합하여 스무드 베이스 레이어 레퍼런스 픽처를 형성하고, 그 다음에 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행되는 상기 스무드 베이스 레이어 레퍼런스 픽처 상에서의 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인버스 톤 매핑된 인터-레이어 레지듀 예측을 생성함으로써 인코딩된 상기 픽처의 상기 적어도 일부에 대한 픽처 데이터를 포함하고,

상기 인버스 톤 매핑 동작이 수행되는 도메인은 레지듀 도메인으로부터 상기 픽셀 도메인으로 시프트되는, 컴퓨터-판독가능 저장 매체.

## 발명의 설명

### 기술 분야

#### [0001] 관련 출원서들에 대한 상호-참조들

본 출원서는 그 전체가 여기에 참고로 포함되어 있고 2009년 2월 3일에 출원된 미합중국 예비출원서 일련번호 61/149,495의 이점을 청구한다.

본 원리들은 일반적으로는 비디오 인코딩 및 디코딩에 관한 것으로, 특히 비트 깊이 스케일리밸리티(bit depth scalability)에서 스무딩된 레퍼런스 프레임(smoothed reference frame)에 의한 모션 보상을 하는 방법들 및 장치에 관한 것이다.

## 배경 기술

[0004] 최근에, 8보다 큰 비트 깊이를 가지는 디지털 이미지들/비디오들은 예를 들면 의료 이미지 처리, 프로덕션 및 포스트프로덕션에서의 디지털 시네마 워크플로우들, 홈시어터 관련 애플리케이션들, 등과 같은 다수의 애플리케이션 분야들에 더욱 바람직하게 되고 있다. 비트 깊이 스케일리밸리티는 미래에 언젠가는 종래의 8 비트 깊이 및 높은 비트 깊이 디지털 이미징 시스템이 동시에 존재하게 될 것이라는 사실을 고려할 때 잠재적으로 유용하다. 8-비트 비디오 및 10-비트 비디오의 공존을 취급하는 다수의 방식들이 있다. 제1 종래 해결책에서, 단지 10-비트 코딩된 비트-스트림만이 송신되고, 표준 8-비트 표시 디바이스들에 대한 8-비트 표현은 톤 매핑 방법들을 10-비트 프레젠테이션에 적용함으로써 얻어진다. 제2 종래 기술 해결책에서, 8-비트 코딩된 프레젠테이션 및 10-비트 코딩된 프레젠테이션을 포함하는 사이멀캐스트 비트-스트림(simulcast bit-stream)이 송신된다. 어느 비트 깊이를 디코딩할지를 선택하는 것은 디코더의 선호에 달렸다. 예를 들면, 10-비트 지원 디코더는 10-비트 비디오를 디코딩하여 출력할 수 있는데 대해, 단지 8-비트들만을 지원하는 보통의 디코더는 단지 8-비트 비디오만을 출력할 수 있다. 제1 종래기술 해결책은 ISO/IEC MPEG-4 part 10 AVC 표준/ITU-T H.264 제안(이하에서는, "MPEG-4 AVC 표준")의 8-비트 프로파일들과 본질적으로 호환할 수 없다. 제2 종래기술 해결책은 모든 현재의 표준들과 호환되지만 더 많은 오버헤드를 요구한다. 그러나, 비트 감소와 백워드 표준 스케일리밸리티 사이의 양호한 절충은 스케일링가능한 해결책일 수 있다. MPEG-4 AVC 표준의 스케일링가능한 확장으로도 알려져 있는 스케일링가능한 비디오 코딩(SVC)은 비트 깊이 스케일리밸리티의 지원을 고려하고 있다. 포스트-처리 또는 사이멀캐스트에 비교한 비트 깊이 스케일링가능한 코딩의 적어도 3개의 장점들이 있다. 하나의 장점은, 비트 깊이 스케일링가능한 코딩은 MPEG-4 AVC 표준의 하이 프로파일들과 하위 호환 방식으로 10-비트 비디오를 가능하게 한다는 점이다. 제2 장점은, 비트 깊이 스케일링가능한 코딩은 상이한 네트워크 대역폭들 또는 디바이스 성능들로의 적응을 가능하게 한다는 점이다. 제3 장점은, 비트 깊이 스케일링가능한 코딩은 낮은 복잡도, 높은 효율 및 높은 유연성을 제공한다는 점이다.

#### [0005] MPEG-4 AVC SVC 확장

- [0006] MPEG-4 AVC 표준의 SVC 확장의 현재 버전에서, 디코딩 복잡도를 감소시키기 위해 단일-루프 디코딩이 지원된다. 인터-코딩된 매크로블록들의, 모션-보상된 예측 및 디블록킹을 포함하는 완전한 디코딩은 현재의 공간 또는 거친-정밀도 스케일리밸리티(CGS) 레이어에 대해서만 요구된다. 이것은 인터-레이어 인트라 텍스처 예측을, 인트라 매크로블록들로 코딩되는 하부 레이어 퍽처의 그런 부분들로 제한시킴으로써 실현된다. 비트 깊이 스케일리밸리티에 대한 인터-레이어 인트라 텍스처 예측을 확장시키기 위해, 인버스 톤 매핑(inverse tone mapping)이 이용된다. SVC는 또한 인터-레이어 레지듀(residue) 예측을 지원한다. 톤 매핑은 통상적으로 퍽셀 도메인에서 이용되므로, 레지듀 도메인에서 대응하는 인버스 톤 매핑을 찾아내기가 매우 어렵다. 제3 및 제4 종래 기술 접근법들에서, 인터-레이어 레지듀 예측에 비트 시프트가 이용된다.

- [0007] 이하에서는 제3 종래기술 접근법으로도 지칭되는 MPEG-4 AVC 표준의 스케일링가능한 비디오 코딩(SVC) 확장의 조인트 드래프트 8(JD8)에서, 스무드 레퍼런스 예측(SRP:smooth reference prediction)으로 지칭되는 기술이 제안된다. 구문 요소들(syntax elements) residual\_prediction\_flag 및 base\_mode\_flag 양쪽이 설정되는 경우에, 1-비트 구문 요소 smoothed\_reference\_flag가 전송된다. smoothed\_reference\_flag=1인 경우, 디코더에서 이하의 단계들이 취해져서 재구성된 비디오 블록을 획득한다.

- [0008] 1. 예측 블록 P는 인핸스먼트 레이어 레퍼런스 프레임들 및 베이스 레이어로부터의 업-샘플링된 모션 벡터들을 이용하여 획득된다.

- [0009] 2. 대응하는 베이스 레이어 레지듀 블록  $r_b$ 가 업-샘플링되고  $U(r_b)$ 가 P에 가산되어  $P+U(r_b)$ 를 형성한다.

- [0010] 3. 텁[1,2,1]을 가지는 스무딩 필터가 처음에는 수평 방향으로, 그리고나서 수직 방향으로 적용되어,  $S(P+U(r_b))$ 를 획득한다.

- [0011] 4. 인핸스먼트 레이어 레지듀 블록은 바로 이전 단계 (3)의 결과에 가산되어 재구성 블록  $R=S(P+U(r_b))+r_e$ 를 획득한다.

- [0012] 또한, 제4 종래기술 접근법은 BDS(비트 깊이 스케일리밸리티)에 대해 인터-레이어 레지듀 예측을 위한 기술들을 제안한다. 제4 종래 기술 접근법은 인터-레이어 레지듀 예측에 대해 인버스 톤 매핑 문제를 레지듀 도메인으로부터 퍽셀 도메인으로 변환시킨다. 인터-레이어 레지듀 예측이 이용되는 경우에, 인버스 톤 매핑은 톤 매핑된 모션 보상된 예측 및 베이스 레이어로부터의 업-샘플링된 레지듀의 합에 적용된다. 인터-레이어 레지듀 예측이 이용되는 경우에, 이하의 단계들이 디코더에서 취해져 재구성된 비디오 블록을 획득한다.

- [0013] 1. 예측 블록 P는 인핸스먼트 레이어 레퍼런스 프레임들을 이용하여 획득되고, 그리고나서 P는 베이스 레이어 비트 깊이로 톤 매핑되어  $T(P)$ 를 획득한다.

- [0014] 2. 대응하는 베이스 레이어 레지듀 블록  $r_b$ 가 공간적으로 업-샘플링되고,  $U(r_b)$ 는 P에 가산되어  $T(P)+U(r_b)$ 를 형성한다.

- [0015] 3. 필터가 이용되어  $S(T(P)+U(r_b))$ 를 획득한다.

- [0016] 4. 그리고나서, 인버스 톤 매핑이 적용되어  $T^{-1}(S(T(P)+U(r_b)))$ 를 획득한다.

- [0017] 5. 인핸스먼트 레이어 레지듀 블록이 바로 이전 단계 (4)의 결과에 가산되어 재구성된 블록  $R=T^{-1}(S(T(P)+U(r_b)))+r_e$ 를 획득한다.

- [0018] 그러나, 이전 종래 기술 해결책들 모두는 불충분하다. 예를 들면, 제3 종래기술 접근법은 톤 매핑 및 인버스 톤 매핑 동작들의 결여로 인해, 인핸스먼트 및 베이스 레이어들에서 상이한 비트 깊이들을 다룰 수 없다. 더구나, 제4 종래 기술 접근법에 있어서, 인핸스먼트 레이어 예측의 정확성에서 개선의 여지가 있다.

## 발명의 내용

### 해결하려는 과제

- [0019] 종래 기술의 이들 및 다른 약점들 및 단점들은 비트 깊이 스케일리밸리티에서 스무딩된 레퍼런스 프레임에 의한 모션 보상을 하는 방법들 및 장치들에 관한 본 원리들에 의해 해결된다.

## 과제의 해결 수단

[0020]

본 원리들의 하나의 양태에 따르면, 하나의 장치가 제공된다. 장치는 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행된 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인터-레이어 레지듀 예측을 생성함으로써 그 일부에 대한 픽처 데이터를 인코딩하기 위한 인코더를 포함한다. 인버스 톤 매핑 동작은 레지듀 도메인으로부터 픽셀 도메인으로 시프트된다.

[0021]

본 원리들의 또 하나의 양태에 따르면, 하나의 방법이 제공된다. 방법은 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행된 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인터-레이어 레지듀 예측을 생성함으로써 그 일부에 대한 픽처 데이터를 인코딩하는 단계를 포함한다. 인버스 톤 매핑 동작은 레지듀 도메인으로부터 픽셀 도메인으로 시프트된다.

[0022]

본 원리들의 또 다른 하나의 양태에 따르면, 하나의 장치가 제공된다. 장치는 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행된 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인터-레이어 레지듀 예측을 생성함으로써 그 일부에 대한 픽처 데이터를 디코딩하기 위한 디코더를 포함한다. 인버스 톤 매핑 동작은 레지듀 도메인으로부터 픽셀 도메인으로 시프트된다.

[0023]

본 원리들의 또 다른 하나의 양태에 따르면, 하나의 방법이 제공된다. 방법은 비트 깊이 스케일리밸리티에 대해 픽셀 도메인에서 수행된 인버스 톤 매핑 동작을 이용하여 픽처의 적어도 일부에 대한 인터-레이어 레지듀 예측을 생성함으로써 그 일부에 대한 픽처 데이터를 디코딩하는 단계를 포함한다. 인버스 톤 매핑 동작은 레지듀 도메인으로부터 픽셀 도메인으로 시프트된다.

[0024]

본 원리들의 이들 및 다른 양태들, 특징들 및 장점들은 첨부된 도면들과 관련하여 읽어져야 될 예로 든 실시예들의 이하의 상세한 설명으로부터 명백하게 될 것이다.

## 도면의 간단한 설명

[0025]

본 원리들은 이하의 예로 든 도면들에 따라 더 잘 이해될 수 있다.

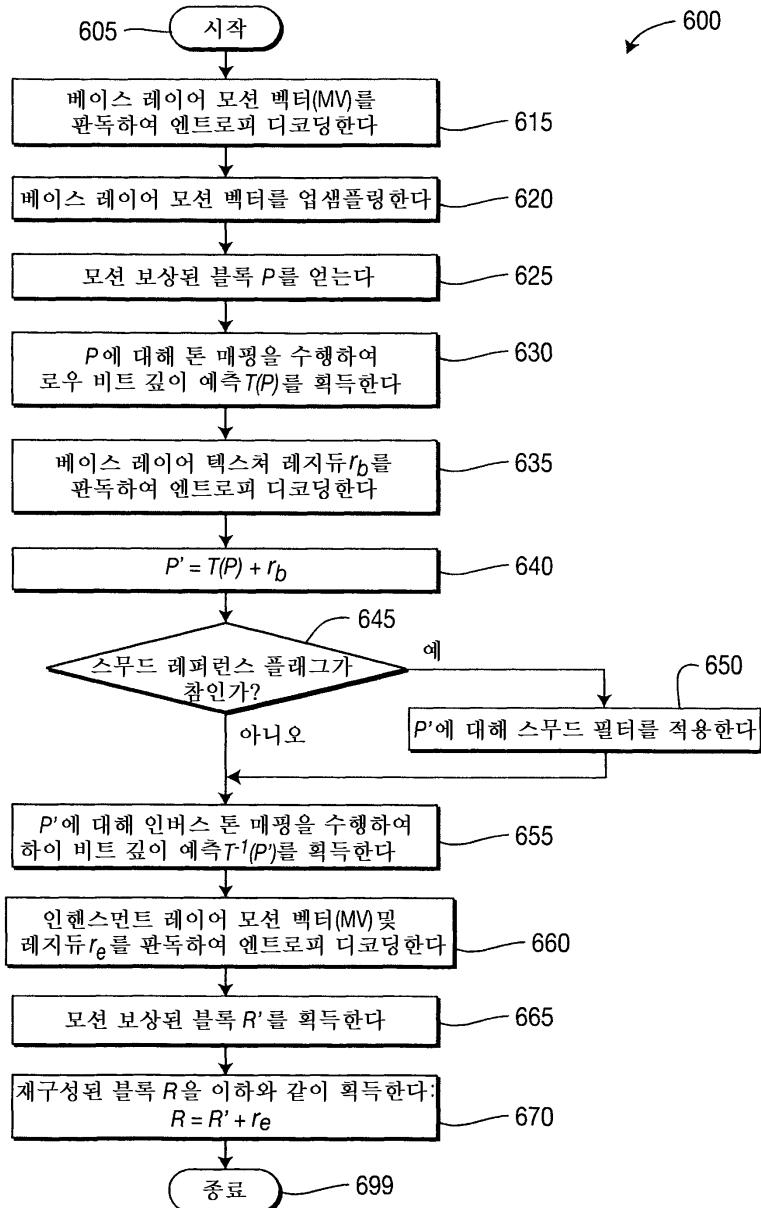

도 1은 본 원리들의 하나의 실시예에 따라, 비트 깊이 스케일리밸리티에 대해 인터-레이어 레지듀 예측을 이용하는 예로 든 비디오 인코더를 도시하는 블록도이다.

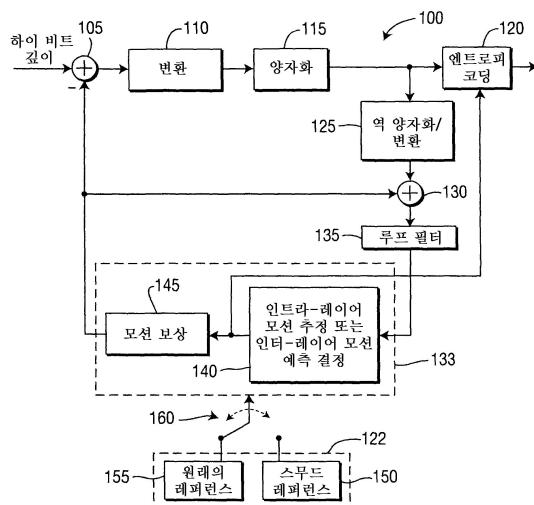

도 2는 본 원리들의 하나의 실시예에 따라, 비트 깊이 스케일리밸리티에 대해 인터-레이어 레지듀 예측을 이용하는 예로 든 비디오 디코더를 도시하는 블록도이다.

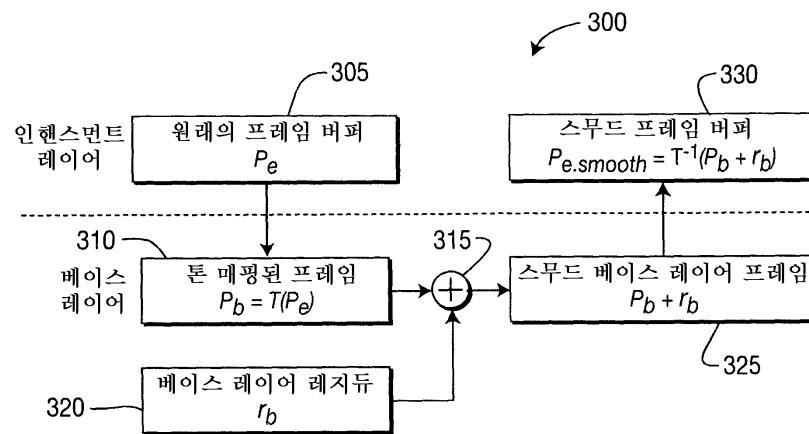

도 3은 본 원리들의 하나의 실시예에 따라, 원래의 레퍼런스 및 베이스 레이어 레지듀 정보를 이용하는 스무드 레퍼런스 생성의 예를 도시하는 하이 레벨 블록도이다.

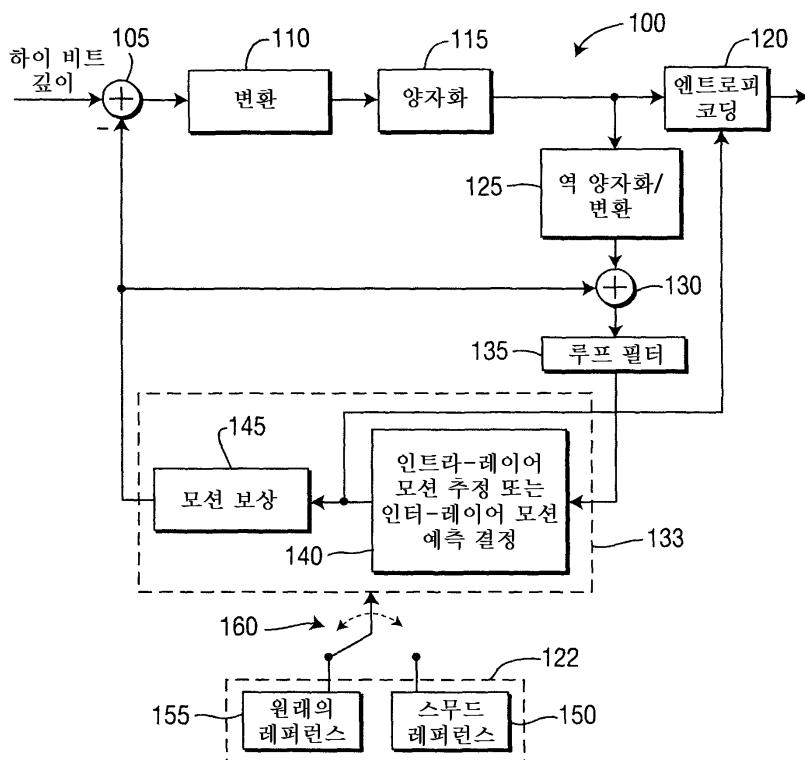

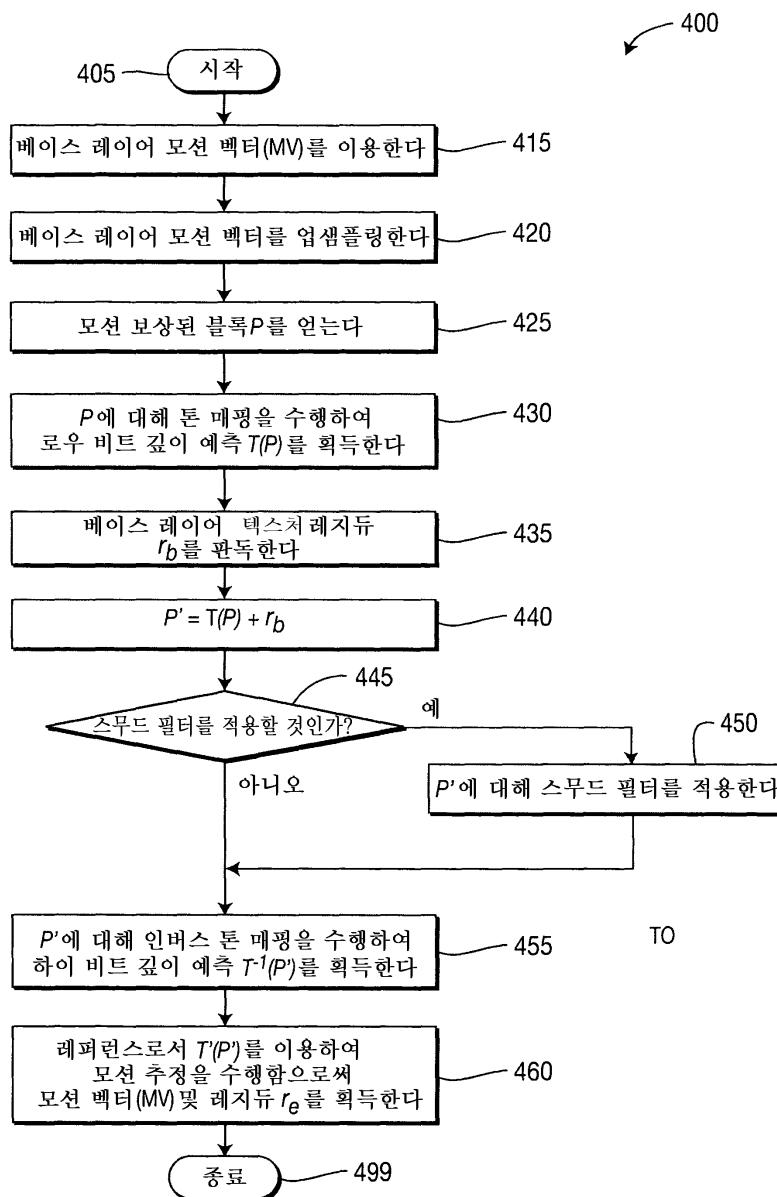

도 4는 본 원리들의 하나의 실시예에 따라, 비디오 인코더에서 비트 깊이 스케일리밸리티에 대한 인터-레이어 레지듀 예측을 위한 예로 든 방법을 도시하는 흐름도이다.

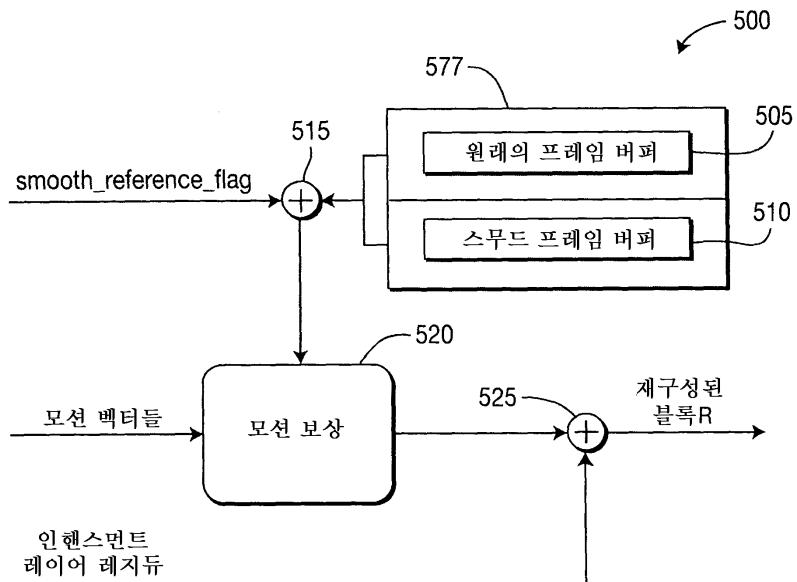

도 5는 본 원리들의 하나의 실시예에 따라, 스무드 레퍼런스 디코딩의 예를 도시하는 하이 레벨 블록도이다.

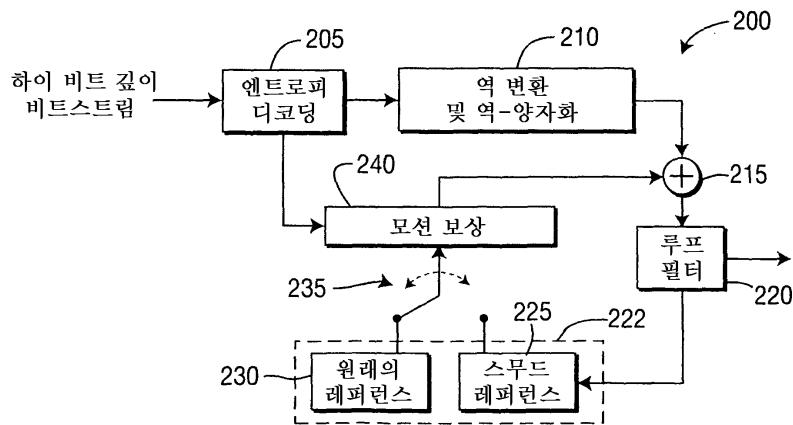

도 6은 본 원리들의 하나의 실시예에 따라, 비디오 디코더에서 비트 깊이 스케일리밸리티에 대한 인터-레이어 레지듀 예측을 위한 예로 든 방법을 도시하는 흐름도이다.

## 발명을 실시하기 위한 구체적인 내용

[0026]

본 원리들은 비트 깊이 스케일리밸리티에서 스무드 레퍼런스 프레임에 의한 모션 보상을 하는 방법들 및 장치들에 관한 것이다.

[0027]

본 설명은 본 원리들을 예시하고 있다. 그러므로, 본 기술분야의 숙련자들은, 여기에 명시적으로 기재되거나 도시되지 않더라도, 본 원리들을 실시하고 그 사상 및 범주 내에 포함되는 다양한 배열들을 고안할 수 있을 것이라는 것은 자명하다.

[0028]

여기에 인용된 모든 예들 및 조건들은 발명자(들)에 의해 본 기술분야를 심화시키는데 공헌된 본 원리들 및 개념들을 이해하는데 독자에게 도움을 주기 위해 교육적 목적으로 된 것이고, 그러한 구체적으로 인용된 예들 및 조건들에 대한 제한이 아닌 것으로 해석되어야 된다.

[0029]

더구나, 여기에서 본 원리들의 특정 예들뿐만 아니라, 이들의 원리들, 양태들 및 실시예들을 인용하는 모든 언

급들은 구조적 및 기능적 등가물들 양쪽 모두를 포함하려는 것이다. 추가적으로, 그러한 등가물들은 장래에 개발된 등가물들, 즉 구조에 관계없이 동일한 기능을 수행하는 개발된 임의의 구성요소들뿐만 아니라, 현재 주지된 등가물들 양쪽 모두를 포함하려는 것이다.

[0030] 그러므로, 예를 들면, 본 기술분야의 숙련자들이라면, 여기에 프리젠팅된 블록도들은 본 원리들을 실시하는 예시적 회로의 개념적 뷰들을 표현하고 있다는 것을 잘 알고 있을 것이다. 유사하게, 임의의 플로우차트들, 흐름도들, 상태 변이도들, 의사코드, 등은 컴퓨터 관통가능한 매체로 실질적으로 표현되고, 컴퓨터 또는 프로세서가 명시적으로 도시되어 있는지 여부에 관계없이, 그러한 컴퓨터 또는 프로세서에 의해 실행될 수 있는 다양한 프로세스들을 나타낸다는 것은 자명하다할 것이다.

[0031] 도면들에 도시된 다양한 구성요소들의 기능들은 적절한 소프트웨어와 연관된 소프트웨어를 실행할 수 있는 하드웨어뿐만 아니라 전용 하드웨어의 이용을 통해서도 제공될 수 있다. 프로세서에 의해 제공되는 경우에, 기능들은 단일 전용 프로세서에 의해, 단일 공유 프로세서에 의해, 또는 그 일부가 공유될 수 있는 복수의 개별적인 프로세서들에 의해 제공될 수 있다. 더구나, 용어 "프로세서" 또는 "컨트롤러"의 명시적 이용은 소프트웨어를 실행할 수 있는 하드웨어를 독점적으로 지칭하는 것으로 해석되어서는 안 되고, 내재적으로는, 제한없이, 디지털 신호 프로세서("DSP") 하드웨어, 소프트웨어를 저장하기 위한 판독 전용 메모리("ROM"), 랜덤 액세스 메모리("RAM"), 및 비휘발성 스토리지를 포함할 수 있다.

[0032] 종래 및/또는 관례적인 다른 하드웨어가 또한 포함될 수 있다. 유사하게, 도면들에 도시된 임의의 스위치들은 단지 개념적일 뿐이다. 그들의 기능은 프로그램 로직의 동작을 통해, 전용 로직을 통해, 프로그램 제어 및 전용 로직의 인터액션을 통해, 또는 심지어 수동으로 수행될 수 있고, 특정 기술은 컨텍스트로부터 더 구체적으로 이해되는 대로 구현자에 의해 선택가능하다.

[0033] 그 청구항들에서, 지정된 기능을 수행하기 위한 수단으로서 표현되는 임의의 구성요소는 예를 들면, a) 그 기능을 수행하는 회로 구성요소들의 조합, 또는 b) 기능을 수행하도록 소프트웨어를 실행하기 위한 적절한 회로와 조합된 펌웨어, 마이크로코드, 등을 포함하는 임의의 형태로 된 소프트웨어를 포함하여 그 기능을 수행하는 임의의 방식을 포함하려는 것이다. 그러한 청구항들에 의해 정의되는 본 원리들은, 다양한 인용된 수단들에 의해 제공된 기능들이 청구항들이 요구하는 방식으로 조합되고 합쳐진다는 사실에 있다. 그러므로, 이들 기능들을 제공할 수 있는 임의의 수단은 여기에 도시된 것들과 동가인 것으로 간주된다.

[0034] 명세서에서 본 원리들의 "하나의 실시예" 또는 "실시예"뿐만 아니라 다른 변동들에 대한 참조는, 그 실시예와 관련하여 기재된 특정 특징, 구조, 특성 등이 본 원리들의 적어도 하나의 실시예에 포함된다는 것을 의미한다. 그러므로, 명세서 전체에 걸쳐 다양한 장소들에서 나타나는, 구문 "하나의 실시예에서" 또는 "실시예에서"뿐만 아니라 임의의 다른 변동들의 출현은 반드시 동일한 실시예를 지칭하는 것은 아니다.

[0035] 이하 "/", "및/또는", 및 "적어도 하나"의 임의의 하나의 이용은, 예를 들면 "A/B", "A 및/또는 B", 및 "A 및 B 중 적어도 하나"의 경우에, 제1 리스트된 옵션 (A)만의 선택, 또는 제2 리스트된 옵션 (B)만의 선택, 또는 양쪽 옵션들 (A 및 B)의 선택을 포함하려 한다는 것은 자명하다. 하나의 추가 예로서, "A, B 및/또는 C" 및 "A, B 및 C의 적어도 하나"의 경우들에서, 그러한 구문들은 제1 리스트된 옵션 (A)만의 선택, 또는 제2 리스트된 옵션 (B)만의 선택, 또는 제3 리스트된 옵션 (C)만의 선택, 또는 제1 및 제2 리스트된 옵션들 (A 및 B)만의 선택, 또는 제1 및 제3 리스트된 옵션들 (A 및 C)만의 선택, 또는 제2 및 제3 리스트된 옵션들 (B 및 C)만의 선택, 또는 모두 3가지 옵션들 (A 및 B 및 C)의 선택을 포함하려는 것이다. 이것은 본 기술분야 및 관련 기술분야들의 통상의 기술자들에게 자명한 바와 같이, 다수의 아이템들이 리스트되는 대로 확장될 수 있다.

[0036] 종래기술뿐만 아니라 본 원리들을 설명할 목적으로, 용어들인 로우 비트 깊이 및 하이 비트 깊이가 여기에 이용된다. 이를 용어들은 비트 깊이 정의의 2개의 상이한 레벨을 정의하는데 이용된다. 하이 비트 깊이는 로우 비트 깊이보다 더 높은 비트 깊이에 있다는 것을 특징으로 하고, 따라서 상대적 용어이다. 설명 및 예시의 목적상, 로우 비트 깊이는 8비트인 것으로 추정되는데 대해, 하이 비트 깊이는 10비트인 것으로 추정된다. 이를 용어들인 로우 비트 깊이 및 하이 비트 깊이의 상대성으로 인해, 용어들이 임의적이더라도, 여기에서의 요구조건은 로우 비트 깊이가 하이 깊이보다 작다는 점이라는 것을 용이하게 알 수 있다. 그러므로, 유일한 요구조건은 계획된 하이 비트 깊이가 로우 비트 깊이보다 더 크다는 것이므로, 예를 들면, 로우 비트 깊이는 4비트, 6비트, 또는 그에 대해서는 12비트일 수 있다. 그러므로, 12비트들의 비트 깊이가 로우 비트 깊이로 정의된다고 가정하면, 하이 비트 깊이는 14비트, 16비트 또는 12보다 큰 임의의 다른 비트 깊이가 고려될 수 있다. 여기에서, 본 원리들의 설명 및 예시는 로우 비트 깊이가 8비트와 동일한 것으로 가정하고 있는 경우에, 하이 비트 깊이에 대한 요구조건은 8비트보다 큰 임의의 하나일 것이다(여기에서 설명을 위해 10비트가 가정되지만, 용이하게 12

비트, 14비트의 비트 깊이 또는 8보다 큰 임의의 다른 비트 깊이를 포함할 수 있다). 로우 및 하이 비트 깊이의 비교를 기술하는 또 하나의 방식은 베이스 레이어 비트 깊이 및 인핸스먼트 레이어 비트 깊이이고, 인핸스된 레이어 비트 깊이는 베이스 레이어 비트 깊이보다 더 크다. 그러므로, 본 원리들의 하나 이상의 실시예들은 하이 비트 깊이에 대한 하나의 예로서 10-비트 픽처의 이용과 관련되지만, 본 원리들은 이것으로 제한되지 않고, 따라서 하이 비트 깊이와 관련된 본 원리들의 이용은 12비트, 14 비트 등을 포함하고 이들로 제한되지 않는 8보다 큰 다른 값들(10 초과)을 취할 수 있다는 것은 자명하다.

[0037] 더구나, 여기에 이용된 바와 같이, 단어들 "픽처" 및 "이미지"는 상호교환가능하게 이용되고, 정지 이미지 또는 비디오 시퀀스로부터의 하나의 픽처를 지칭한다. 주지된 바와 같이, 하나의 픽처는 하나의 프레임 또는 하나의 필드이다.

[0038] 또한, 본 원리들의 하나의 이상의 실시예들은 MPEG-4 AVC 표준의 스케일링가능한 비디오 코딩(SVC) 확장에 관해 여기에 설명되어 있지만, 본 원리들은 이러한 확장 및/또는 이러한 표준으로만 제한되지 않고, 따라서 본 원리들의 사상을 유지하면서도 다른 비디오 코딩 표준들, 추천들, 및 그 확장들과 관련하여 활용될 수도 있다는 것은 자명하다.

[0039] 도 1을 참조하면, 비트 깊이 스케일리밸리티에 대해 인터-레이어 레지듀 예측을 이용하는 예로 든 비디오 인코더는 참조번호 100으로 일반적으로 표시된다. 비디오 인코더(100)는 변환기(110)의 입력과 신호 통신 상태에 있는 출력을 가지는 조합기(105)를 포함한다. 변환기(110)의 출력은 양자화기(115)의 입력과 신호 통신 상태로 접속된다. 양자화기(115)의 출력은 엔트로피 코더(120)의 제1 입력 및 역 양자화기/역 변환기(125)의 입력과 신호 통신 상태로 접속된다. 역 양자화기/역 변환기(125)의 출력은 조합기(130)의 제1 비-반전 입력과 신호 통신 상태로 접속된다. 조합기(130)의 출력은 루프 필터(135)의 입력과 신호 통신 상태로 접속된다. 루프 필터(135)의 출력은 인트라-레이어 모션 추정 또는 인터-레이어 모션 예측 결정을 위한 디바이스(140)의 입력과 신호 통신 상태로 접속된다. 디바이스(140)의 출력은 엔트로피 인코더(120)의 제2 입력 및 모션 보상기(145)의 입력과 신호 통신 상태로 접속된다. 모션 보상기(145)의 출력은 조합기(130)의 제2 비-반전 입력 및 조합기(105)의 반전 유닛과 신호 통신 상태로 접속된다. 디바이스(140) 및 모션 보상기(145)는 디바이스(133)에 포함된다. 레퍼런스 제공자(222)는 스무드 레퍼런스 제공자(150) 및 원래 레퍼런스 제공자(155)를 포함한다. 원래 레퍼런스 제공자(155)의 출력은 스위치(160)의 제1 입력과 신호 통신 상태로 접속된다. 스무드 레퍼런스 제공자(150)의 출력은 스위치(160)의 제2 입력과 신호 통신 상태로 접속된다. 스위치(160)의 출력은 디바이스(133)와 신호 통신 상태로 접속되고, 디바이스(140) 및/또는 모션 보상기(145)에 제공될 수 있다. 조합기(105)의 비-반전 입력은 하이 비트 깊이 신호를 수신하기 위한, 비디오 인코더(100)의 입력으로서 가용하다. 엔트로피 코더(120)의 출력은 하이 비트 깊이 비트스트림을 출력하기 위한, 비디오 인코더(100)의 출력으로서 가용하다.

[0040] 도 2를 참조하면, 비트 깊이 스케일리밸리티에 대해 인터-레이어 레지듀 예측을 이용하는 예로 든 비디오 디코더는 참조번호 200에 의해 일반적으로 표시된다. 비디오 디코더(200)는 역 변환기 및 역-양자화기(210)의 입력과 신호 통신 상태인 제1 출력을 가지는 엔트로피 디코더(205)를 포함한다. 역 변환기 및 역-양자화기(210)의 출력은 조합기(215)의 제1 비-반전 입력과 신호 통신 상태로 접속된다. 조합기(215)의 출력은 루프 필터(220)의 입력과 신호 통신 상태로 접속된다. 루프 필터(220)의 제1 출력은 레퍼런스 제공자(222)의 입력과 신호 통신 상태로 접속된다. 레퍼런스 제공자(222)는 원래 레퍼런스 제공자(230) 및 스무드 레퍼런스 제공자(225)를 포함한다. 원래 레퍼런스 제공자(230)의 출력은 스위치(235)의 제1 입력과 신호 통신 상태로 접속된다. 스무드 레퍼런스 제공자(240)의 출력은 스위치(235)의 제2 입력과 신호 통신 상태로 접속된다. 스위치의 출력은 모션 보상기(240)의 제1 입력에 접속된다. 모션 보상기(240)의 출력은 조합기(215)의 제2 비-반전 입력과 신호 통신 상태로 접속된다. 엔트로피 디코더(205)의 제2 출력은 모션 보상기(240)의 제2 입력과 신호 통신 상태로 접속된다. 엔트로피 디코더(205)의 입력은 하이 비트 깊이 비트스트림을 수신하기 위한, 비디오 디코더(200)의 입력으로서 가용하다. 루프 필터(220)의 제2 출력은 하이 비트 깊이 픽처들을 출력하기 위한, 비디오 디코더(200)의 출력으로서 가용하다.

[0041] 본 원리들에 따르면, 모션 보상을 위한 레퍼런스 프레임으로서 인버스 톤 매핑된 스무드 레퍼런스의 이용을 제안한다. 하나의 실시예에서, 인터-레이어 레지듀 예측에 대해 인버스 톤 매핑 문제를 레지듀 도메인에서 픽셀 도메인으로 변환한다. 예시를 위해, 단지 비트 깊이 스케일리밸리티만이 관련되며 하나의 단일 루프 디코딩 아키텍처가 이용되는 하나 이상의 실시예들이 여기에 기재된다. 그러나, 본 원리들은 이전 것으로 제한되지 않고, 여기에 제공된 본 원리들의 사상들이 주어진다면, 본 및 관련 기술분야들의 통상의 기술자에 의해 본 원리들의 사상을 유지하면서도, 본 원리는 복수-루프 디코딩 아키텍처뿐만 아니라 비트 깊이 및 공간 스케일리밸

리티 등과 같은 조합된 스케일리빌리티와 관련되도록 용이하게 확장될 수 있다는 것은 자명하다 할 것이다.

[0042] 모션 보상을 위해 대안 스무드 레퍼런스를 이용하는 코딩 모드를 추가하는 것을 제안한다. 대안 스무드 레퍼런스는 인핸스먼트 레이어의 레퍼런스 프레임, 및 베이스 레이어로부터의 모션 및 레지듀 데이터를 이용하여 구축된다.

[0043] 도 3을 참조하면, 원래의 레퍼런스 및 베이스 레이어 레지듀 정보를 이용하는 스무드 레퍼런스 생성의 예는 참조번호 300에 의해 일반적으로 표시되어 있다. 원래의 프레임 버퍼로부터의 인핸스먼트 레이어 예측  $p_e(305)$ 가 톤 매핑되어  $p_b=T(p_e)(310)$ 를 획득한다. 톤 매핑된 프레임  $p_b(310)$ 은 조합기(315)의 제1 비-반전 입력에 입력된다. 베이스 레이어 레지듀  $r_b(320)$ 은 조합기(315)의 제2 비-반전 입력에 입력된다. 조합기(315)의 출력은 스무드 베이스 레이어 프레임  $p_b+r_b(325)$ 를 포함한다. 스무드 베이스 레이어 프레임  $p_b+r_b(325)$ 는 인버스 톤 매핑되어  $p_{e,smooth}=T^{-1}(p_b+r_b)(330)$ 를 획득한다.

[0044] 본 원리들의 실시예에 따른 비디오 인코딩 절차는 이하와 같다.

[0045] 1. 이하의 서브-단계들을 이용하여 각 블록에 대한 대안 레퍼런스 프레임  $REF_{alt}$ 를 생성한다.

[0046] a. 배열된 베이스 레이어 블록이 인트라 코딩되면, 인버스 톤 매핑된 디코딩된 블록을 복사하라. 그렇지 않으면, 이하의 b 또는 c의 서브-단계들 중 하나를 수행하라.

[0047] b. 하나의 실시예에서, 모션 보상은 10-비트 인핸스먼트 레이어 레퍼런스 픽처들 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 예측 블록 P를 형성한다. 그리고나서, P는 8-비트 버전 이미지  $T(P)$ 로 톤 매핑된다.

[0048] c. 또 하나의 실시예에서, 모션 보상은 인핸스먼트 레이어로부터의 8-비트 톤 매핑된 레퍼런스 픽처 및 베이스 레이어로부터의 업-샘플링된 모션 데이터를 이용하여 수행되어, 예측 블록  $T(P)$ 를 형성한다.

[0049] d. 대응하는 베이스 레이어 레지듀 프레임  $r_b$ 가  $U(r_b)$ 로 공간적으로 업-샘플링된다. 그리고나서,  $U(r_b)$ 를  $T(P)$ 에 가산하여  $T(P) + U(r_b)$ 를 형성한다.

[0050] e. 필터가 이용되어  $S(T(P)+U(r_b))$ 를 획득한다.

[0051] f. 그리고나서, 인버스 톤 매핑이 적용되어  $T^{-1}(S(T(P)+U(r_b)))$ 를 획득한다.

[0052] 2. 그리고나서, 모션 추정은 레퍼런스 프레임으로서  $REF_{alt}$ 를 이용하여 적용된다. 모션 벡터  $mv$  및 레지듀  $r_e$ 가 인코딩되어 송신된다.

[0053] 매크로블록(MB) 레벨 구문에서 플래그 `smooth_ref_flag`는 이러한 코딩 모드의 이용을 시그널링하는데 이용된다.

[0054] 또 하나의 실시예에서, 이러한 코딩 모드는, 대안 레퍼런스로 포인팅하는 하나 이상의 엔트리가 인핸스먼트 레이어에 대한 레퍼런스 리스트에 추가되도록, INTER 코딩 프로세스에 내장될 수 있다. 이러한 실시예에 있어서, 이러한 코딩 모드의 이용을 시그널링하는데 어떠한 플래그도 필요하지 않다.

[0055] 도 4를 참조하면, 비디오 인코더에서 비트 깊이 스케일리빌리티에 대한 인터-레이어 레지듀 예측을 위한 예로든 방법이 참조번호 400으로 일반적으로 표시된다. 방법(400)은 제어를 기능 블록(415)에 패싱하는 시작 블록(405)을 포함한다. 기능 블록(415)은 베이스 레이어 모션 벡터( $mv$ )를 이용하고, 제어를 기능 블록(420)에 패싱한다. 기능 블록(420)은 베이스 레이어 모션 벡터를 업-샘플링하고 제어를 기능 블록(425)에 패싱한다. 기능 블록(425)은 현재 블록에 대응하는 모션 보상된 블록 P를 얻고 제어를 기능 블록(430)에 패싱한다. 기능 블록(430)은 모션 보상된 블록에 대해 톤 매핑을 수행하여 로우 비트 깊이 예측  $T(P)$ 를 획득하고 제어를 기능 블록(435)에 패싱한다. 기능 블록(435)은 베이스 레이어 텍스처 레지듀  $r_b$ 를 판독하고, 제어를 기능 블록(440)에 패싱한다. 기능 블록(440)은 베이스 레이어 텍스처 레지듀  $r_b$ 를 로우 비트 깊이 예측  $T(P)$ 와 조합하여 스무드 레퍼런스 픽처, 즉  $P'=T(P)+r_b$ 를 획득하고, 제어를 결정 블록(445)에 패싱한다. 결정 블록(445)은 스무드 레퍼런스를 적용할 지 여부를 결정한다. 그렇다면, 제어는 기능 블록(450)으로 패싱된다. 그렇지 않으면, 제어는 기능 블록(455)로 패싱된다.

[0056] 기능 블록(450)은 스무드 레퍼런스 핵처 P'에 대해 스무드 필터를 적용하고, 제어를 기능 블록(455)에 패싱한다.

[0057] 기능 블록(455)은 P'에 대해 인버스 톤 매핑을 수행하여 하이 비트 깊이 예측  $T^{-1}(P')$ 를 획득하고 제어를 기능 블록(460)에 패싱한다. 기능 블록(460)은 레퍼런스로서  $T'(P')$ 를 이용하여 모션 추정을 수행함으로써 모션 벡터(mv) 및 인핸스먼트 레지듀  $r_e$ 를 획득하고, 제어를 종료 블록(499)에 패싱한다.

[0058] 도 5를 참조하면, 스무드 레퍼런스 디코딩의 예는 참조번호 500으로 일반적으로 표시되어 있다. 원래의 프레임 버퍼(505)의 출력 및 스무드 프레임 버퍼(510)의 출력은 조합기(515)의 제1 비-반전 입력과 신호 통신 상태로 접속된다. 조합기(515)의 출력은 모션 보상기(520)의 제1 입력과 신호 통신 상태로 접속된다. 모션 보상기(520)의 출력은 조합기(525)의 제1 비-반전 입력과 신호 통신 상태로 접속된다. 조합기(515)의 제2 비-반전 입력은 smooth\_reference\_flag를 수신하기 위한, 스무드 레퍼런스 디코딩(500)에 대한 입력으로서 가용하다. 모션 보상기(520)의 제2 입력은 모션 벡터들을 수신하기 위한, 스무드 레퍼런스 디코딩(500)의 입력으로서 가용하다. 조합기(525)의 제2 비-반전 입력은 인핸스먼트 레이어 레지듀를 수신하기 위한, 스무드 레퍼런스 디코딩(500)의 입력으로 가용하다. 조합기(525)의 출력은 재구성된 블록 R을 출력하기 위한, 스무드 레퍼런스 디코딩(500)의 출력으로서 가용하다. 원래의 프레임 버퍼(505) 및 스무드 프레임 버퍼(510)는 메모리(577)에 포함된다. 양쪽 원래의 프레임 버퍼(505) 및 스무드 프레임 버퍼(510)는 단일 메모리(577)와 관련하여 도시되어 있지만, 그러한 버퍼들(505 및 510)은 상이한 메모리들에 저장될 수 있다. 이들 및 다른 변동들은 본 원리들의 사상 내에 있다.

[0059] 본 원리들의 실시예에 따른 비디오 디코딩 절차는 이하와 같다.

[0060] 1. 이하의 서브-단계들을 이용하여 각 블록에 대한 대안 레퍼런스 프레임  $REF_{alt}$ 를 생성한다.

[0061] a. 배열된 베이스 레이어 블록이 인트라 코딩되면, 인버스 톤 매핑된 디코딩된 블록을 복사하라. 그렇지 않으면, 이하의 b 또는 c의 서브-단계를 중 하나를 수행하라.

[0062] b. 하나의 실시예에서, 모션 보상은 10-비트 인핸스먼트 레이어 레퍼런스 핵처들 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 예측 블록 P를 형성한다. 그리고나서, P는 8-비트 버전 이미지  $T(P)$ 로 톤 매핑된다.

[0063] c. 또 하나의 실시예에서, 모션 보상은 인핸스먼트 레이어로부터의 8-비트 톤 매핑된 레퍼런스 핵처 및 베이스 레이어로부터의 업-샘플링된 모션 데이터를 이용하여 수행되어, 예측 블록  $T(P)$ 를 형성한다.

[0064] d. 대응하는 베이스 레이어 레지듀 프레임  $r_b$ 가  $U(r_b)$ 로 공간적으로 업-샘플링된다. 그리고나서,  $U(r_b)$ 를  $T(P)$ 에 가산하여  $T(P) + U(r_b)$ 를 형성한다.

[0065] e. 필터가 이용되어  $S(T(P)+U(r_b))$ 를 획득한다.

[0066] f. 그리고나서, 인버스 톤 매핑이 적용되어  $T^{-1}(S(T(P)+U(r_b)))$ 를 획득한다.

[0067] 2. 그리고나서, 모션 추정이 적용되어  $MC(REF_{alt}, mv)$ 를 획득하고, 여기에서 mv는 모션 벡터이다.

[0068] 3. 인핸스먼트 레이어 레지듀 블록은 바로 이전 단계(2)의 결과에 가산되어, 재구성된 블록  $R=MC(REF_{alt}, mv)+r_e$ 를 획득한다.

[0069] 도 6을 참조하면, 비디오 디코더에서 비트 깊이 스케일리밸리티에 대한 인터-레이어 레지듀 예측을 위한 예로든 방법은 참조번호 600에 의해 일반적으로 표시된다. 방법(600)은 제어를 기능 블록(615)에 패싱하는 시작 블록(605)을 포함한다. 기능 블록(615)은 베이스 레이어 모션 벡터(mv)를 판독하여 엔트로피 디코딩하고, 제어를 기능 블록(620)에 패싱한다. 기능 블록(620)은 베이스 레이어 모션 벡터(mv)를 업-샘플링하고, 제어를 기능 블록(625)에 패싱한다. 기능 블록(625)은 모션 보상된 블록 P를 얻고, 제어를 기능 블록(630)에 패싱한다. 기능 블록(630)은 P에 대해 톤 매핑을 수행하여 로우 비트 깊이 예측  $T(P)$ 를 획득하고 제어를 기능 블록(635)에 패싱한다. 기능 블록(635)은 베이스 레이어 텍스처 레지듀  $r_b$ 를 판독하여 엔트로피 디코딩하고 제어를 기능 블록(640)에 패싱한다. 기능 블록(640)은 베이스 레이어 텍스처 레지듀  $r_b$ 를 로우 비트 깊이 예측  $T(P)$ 와 조합하여

스무드 레퍼런스 핵처, 즉  $P' = T(P) + r_b$ 를 획득하고, 제어를 결정 블록(645)에 패싱한다. 결정 블록(645)은 스무드 레퍼런스 플래그가 참과 동일한지 여부를 결정한다. 그렇다면, 제어는 기능 블록(650)에 패싱된다. 그렇지 않다면, 제어는 기능 블록(655)에 패싱된다.

[0070] 기능 블록(650)은 스무드 레퍼런스 핵처  $P'$ 에 대해 스무드 필터를 적용하고, 제어를 기능 블록(655)에 패싱한다.

[0071] 기능 블록(655)은  $P'$ 에 대해 인버스 톤 매핑을 수행하여 하이 비트 깊이 예측  $T^{-1}(P')$ 를 획득하고, 제어를 기능 블록(660)에게 패싱한다. 기능 블록(660)은 모션 벡터(mv) 및 인핸스먼트 레이어 레지듀  $r_e$ 를 판독하여 엔트로피 디코딩하고 기능 블록(665)에 패싱한다. 기능 블록(665)은 모션 보상을 수행하여 블록  $R'$ 를 획득하고 기능 블록(670)에 패싱한다. 기능 블록(670)은 하이 비트 깊이 예측  $T^{-1}(P')$ 를 인핸스먼트 레이어 레지듀  $r_e$ 와 조합함으로써 얻어진 현재 블록에 대한 재구성 블록  $R$ , 즉  $R = T^{-1}(P') + r_e$ 를 생성하고, 제어를 종료 블록(699)에 패싱한다.

[0072] 이제, 그 일부가 상기 언급된 본 발명의 다수의 부수적인 여러 장점들/특징들에 대한 설명이 제공될 것이다. 예를 들면, 하나의 장점/특징은 비트 깊이 스케일리밸리티에 대해 핵셀 도메인에서 수행된 인버스 톤 매핑 동작을 이용하여 핵처의 적어도 일부에 대한 인터-레이어 레지듀 예측을 생성함으로써 그 일부에 대한 핵처 데이터를 인코딩하기 위한 인코더를 구비하는 장치이다. 인버스 톤 매핑 동작은 레지듀 도메인에서 핵셀 도메인으로 시프트된다.

[0073] 또 하나의 장점/특징은 상기 설명된 바와 같은 인코더를 구비하는 장치이고, 여기에서, 인코더는 인핸스먼트 레이어 레퍼런스를 이용하여 모션 보상을 수행함으로써 인핸스먼트 레이어 예측을 생성하고, 인핸스먼트 레이어 예측을 베이스 레이어 레퍼런스에 톤 매핑하여 톤 매핑된 예측을 생성하며, 그 일부에 대한 베이스 레이어 레지듀를 톤 매핑된 예측과 조합하여 스무드 베이스 레이어 레퍼런스를 획득하고, 스무드 베이스 레이어 레퍼런스를 인버스 톤 매핑하여 인버스 톤 매핑된 예측을 생성함으로써, 인터-레이어 레지듀 예측을 생성한다. 인코더는 인버스 톤 매핑된 예측을 이용하여 모션 추정 및 모션 보상을 수행하여, 모션 벡터를 획득하고, 모션 벡터, 및 인버스 톤 매핑된 예측과 입력 핵처 사이의 어려를 인코딩하여 송신한다.

[0074] 또 다른 하나의 장점/특징은 상기 설명된 바와 같이 모션 보상을 적어도 수행하는 인코더를 구비하는 장치이고, 여기에서 모션 보상은 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 인핸스먼트 레이어 예측을 생성한다. 인핸스먼트 레이어 레퍼런스는 베이스 레이어 레퍼런스와 동일한 비트 깊이를 가지고 있다.

[0075] 또 다른 하나의 장점/특징은 상기 설명된 바와 같이 모션 보상을 적어도 수행하는 인코더를 구비하는 장치이고, 여기에서 모션 보상은 인핸스먼트 레이어 레퍼런스 및 베이스 레이어 업-샘플링된 모션 데이터를 이용하여 수행되어 인핸스먼트 레이어 예측을 생성한다. 인핸스먼트 레이어 레퍼런스는 베이스 레이어 레퍼런스보다 큰 비트 깊이를 가지고 있다.

[0076] 더구나, 또 하나의 장점/특징은 상기 설명된 바와 같이 모션 보상을 적어도 수행하는 인코더를 구비하는 장치이고, 여기에서 베이스 레이어 레지듀는 공간적으로 업-샘플링되어 공간적으로 업-샘플링된 베이스 레이어 레지듀를 획득하고, 공간적으로 업-샘플링된 베이스 레이어 레지듀는 톤 매핑된 예측과 조합되어 스무드 베이스 레이어 레퍼런스를 획득한다.

[0077] 또한, 또 하나의 장점/특징은 상기 설명된 바와 같이 모션 보상을 적어도 수행하는 인코더를 구비하는 장치이고, 여기에서 매크로블록 레벨 구문에서의 플래그는 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드의 이용을 시그널링하는데 이용된다.

[0078] 또한, 또 하나의 장점/특징은 상기 설명된 바와 같이 모션 보상을 적어도 수행하는 인코더를 구비하는 장치이고, 여기에서 인터-레이어 레지듀 예측을 생성하는 것에 대응하는 인터-레이어 레지듀 예측 모드는, 스무드 베이스 레이어 레퍼런스에 포인팅하는 엔트리가 인핸스먼트 레이어에 대한 현재의 레퍼런스 리스트에 부가되도록, 현재의 인터 모드들에 내장되어 전송된다.

[0079] 본 원리들의 이들 및 다른 특징들 및 장점들은 본 사상들에 기초하여 관련 기술분야의 통상의 기술자에 의해 용이하게 확인될 수 있다. 본 원리들의 사상들은 하드웨어, 소프트웨어, 펌웨어, 특별 목적 프로세서들, 또는 그

조합들의 다양한 형태들로 구현될 수 있다는 것은 자명하다.

[0080] 가장 바람직하게는, 본 원리들은 하드웨어 및 소프트웨어의 조합으로 구현된다. 더구나, 소프트웨어는 프로그램 저장 유닛 상에 실체적으로 실시되는 애플리케이션 프로그램으로 구현될 수 있다. 애플리케이션 프로그램은 임의의 적합한 아키텍처를 포함하는 머신에 로딩되어 실행될 수 있다. 양호하게는, 머신은 하나 이상의 중앙 처리 유닛들("CPU"), 랜덤 액세스 메모리("RAM"), 및 입/출력("I/O") 인터페이스들과 같은 하드웨어를 구비하는 컴퓨터 플랫폼 상에 구현된다. 컴퓨터 플랫폼은 오퍼레이팅 시스템 및 마이크로명령 코드를 또한 포함할 수 있다. 여기에 기재된 다양한 프로세스들 및 기능들은 CPU에 의해 실행될 수 있는, 마이크로명령 코드의 일부, 또는 애플리케이션 프로그램의 일부, 또는 임의의 그 조합일 수 있다. 뿐만 아니라, 추가적인 데이터 저장 유닛 및 프린팅 유닛과 같은 다양한 다른 주변장치 유닛들이 컴퓨터 플랫폼에 접속될 수 있다.

[0081] 첨부된 도면들에 도시된 구성하는 시스템 컴포넌트들 및 방법들의 일부는 양호하게는 소프트웨어로 구현되기 때문에, 시스템 컴포넌트들 또는 프로세스 기능 블록들 사이의 실제 접속은 본 원리들이 프로그래밍되는 방식에 따라 상이할 수 있다는 것도 추가적으로 자명하다. 본 사상들이 주어지는 경우, 본 관련 기술분야의 통상의 기술자라면 본 원리들의 이들 및 유사한 구현들 또는 구성들을 고안할 수 있을 것이다.

[0082] 예시적 실시예들이 첨부된 도면들을 참조하여 여기에 기재되었지만, 본 원리들은 이를 정확한 실시예들로 제한되지 않고 본 기술분야의 통상의 기술자에 의해 본 원리들의 범주 및 사상에서 벗어나지 않고서도 다양한 변경들 및 변형들이 달성될 수 있다는 것은 자명하다. 모든 그러한 변경들 및 변형들은 첨부된 청구항들에 제시된 본 원리들의 범주 내에 포함된다고 할 것이다.

## 도면

### 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6