(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3907705号

(P3907705)

(45) 発行日 平成19年4月18日(2007.4.18)

(24) 登録日 平成19年1月26日(2007.1.26)

(51) Int.C1.

F 1

|            |           |            |

|------------|-----------|------------|

| HO4N 5/46  | (2006.01) | HO4N 5/46  |

| HO4N 7/26  | (2006.01) | HO4N 7/13  |

| HO4N 11/04 | (2006.01) | HO4N 11/04 |

Z

Z

請求項の数 6 (全 13 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願平10-527671                  |

| (86) (22) 出願日 | 平成9年9月30日(1997.9.30)          |

| (65) 公表番号     | 特表2001-526848 (P2001-526848A) |

| (43) 公表日      | 平成13年12月18日(2001.12.18)       |

| (86) 國際出願番号   | PCT/US1997/017512             |

| (87) 國際公開番号   | W01998/027720                 |

| (87) 國際公開日    | 平成10年6月25日(1998.6.25)         |

| 審査請求日         | 平成16年9月29日(2004.9.29)         |

| (31) 優先権主張番号  | 96402785.8                    |

| (32) 優先日      | 平成8年12月18日(1996.12.18)        |

| (33) 優先権主張国   | 欧州特許庁(EP)                     |

|           |                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | トムソン コンシューマ エレクトロニクス インコーポレイテッド<br>アメリカ合衆国 46290-1024<br>インディアナ州 インディアナポリス ノース・メリディアン・ストリート 103<br>30 |

| (74) 代理人  | 弁理士 谷 義一                                                                                              |

| (74) 代理人  | 弁理士 阿部 和夫                                                                                             |

| (72) 発明者  | シェルツ, マーク, アラン.<br>アメリカ合衆国 46033 インディアナ州 カーメル サマーセット ウェイ<br>サウス 4437                                  |

最終頁に続く

(54) 【発明の名称】多重フォーマットビデオ信号処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

デジタルビデオ信号処理システムであって、

MPEG HDフォーマットデータを受信するための入力と、

非MPEG SDフォーマットデータを受信するための入力と、

ロックフォーマットのMPEGデータと、ライン/ロック変換を行った非MPEGフォーマットデータとを処理するロック/ライン変換器と、SD信号をHD信号に再フォーマットし、前記HDフォーマットデータを圧縮解除する手段とを含む表示処理装置と、

前記表示処理装置から表示装置へデータを搬送するための出力とを備えるシステム。

## 【請求項 2】

前記ロック/ライン変換器は、ルミナンスロック/ライン変換器であり、前記表示処理装置は、クロミナンスロック/ライン変換器を含む請求項1に記載のシステム。

## 【請求項 3】

多重フォーマットのビデオ信号を処理する方法であって、

処理すべきデータを含む信号を受信するステップと、

前記受信信号を、MPEG HDフォーマット信号および非MPEG SDフォーマット信号の1つとして識別するステップと、

受信時に入力MPEG HDフォーマット信号を復号化してロックフォーマットのデータを生成するステップと、

受信時に入力非MPEG SDフォーマット信号を事前処理してロックフォーマットの

10

20

データを生成するステップと、

前記ロックフォーマットのデータを表示装置であって前記H D フォーマットデータを圧縮解除し前記非M P E G フォーマット信号をH D 信号に再フォーマットする表示装置に搬送するステップとを含む方法。

【請求項4】

前記事前処理ステップは、ラインフォーマットデータをロックフォーマットデータに変換する請求項3に記載の方法。

【請求項5】

前記搬送ステップは、ロックフォーマットデータをラインフォーマットデータに変換する請求項3に記載の方法。

10

【請求項6】

ロックフォーマットデータをメモリに書き込むステップと、ロックフォーマットデータを前記搬送ステップの前に前記メモリから読み取るステップとをさらに含む請求項3に記載の方法。

【発明の詳細な説明】

技術分野

本発明は、ビデオ信号を表示するための処理に関する。

背景情報

圧縮ビデオ信号伝送システム、たとえばM P E G - 2 ( M o t i o n P i c t u r e E x p e r t s G r o u p ) 圧縮フォーマット ( 「 C o d i n g o f M o v i n g P i c t u r e s a n d A s s o c i a t e d A u d i o 」 I S O / I E C J T C 1 / S C 2 9 / W G 1 1 N 0 7 0 2 ( 改訂 ) 1 9 9 4 年 5 月 1 0 日 ) を使用したシステムでは、現在数カ所の試験場からH D T V ( 高精細度テレビジョン ) のデジタル信号を放送している。最初のH D T V 受像機が市場に登場するのに合わせて商用プログラム放送が開始される計画である。H D T V 信号と現在のテレビジョン受像機との間には、米国のN T S C 標準信号処理におけるような互換性がない。したがって、S D 受像機がすぐにも使いものにならなくなることのないように移行期間が設けられ、その間はN T S C またはP A L テレビジョン標準方式に準拠するS D ( 標準精細度 ) テレビジョン信号の放送が継続される。さらに、放送局が移行準備によって、一部のプログラムが一定期間M P E G フォーマットでは利用できなくなる。

20

ビデオデータは、様々なフォーマット ( たとえば、画像表示縦横比 4 : 3 および 1 6 : 9 、データサンプルフォーマット 4 : 4 : 4 、 4 : 2 : 2 、および 4 : 2 : 0 、飛び越し / 非飛び越し走査など ) ならびに様々な空間解像度 ( たとえば、ライン当たり画素数 3 5 2 、 4 8 0 、 5 4 4 、 6 4 0 、 7 2 0 ... 1 9 2 0 およびフレーム当たりアクティブライン 2 4 0 、 4 8 0 、 7 2 0 、 1 0 8 0 など ) で伝送される。通常、ビデオ信号受信機に伝送前のフォーマットで圧縮解除信号を表示できる機能を備えるのは、美的感覚および経費の両面から見て非実用的である。むしろ、圧縮解除後処理回路を組み込んで、様々なフォーマットの圧縮解除ビデオ信号を希望の表示フォーマットにトランスコードする方が好ましい。

30

ビデオ信号処理分野の当業者に知られている数多くのトランスコーディングまたは時空変換システムがある。一般に、それぞれが飛び越しから非飛び越しへの変換、あるいはサンプル、ライン、またはフィールドレートの倍加など、特定タイプの変換を対象としている。

40

ビデオ圧縮解除システムには相当量の回路が組み込まれているが、非圧縮または標準精細度のビデオ信号を処理する追加回路を採用することが望ましい。受信機に含まれる後処理回路は、トランスコーディング回路の量を著しく増加させずにS D ビデオ信号をトランスコードするものでなければならない。デジタルのM P E G フォーマットテレビジョン信号は、復号された画素ロックフォーマットでM P E G 互換表示処理装置に到来するので、これは困難である。S D テレビジョン信号は、通常N T S C またはP A L いずれかのフォーマットで、多重化アナログY C R C B 表示対応画素ライン ( ラスタ走査 ) として 4 : 2 :

50

2の割合で表示処理装置に到来する。

#### 発明の概要

本発明によれば、MPEGフォーマットテレビジョン信号を受理しこれを画素ブロックフォーマットに復号する。このシステムはまた、SDテレビジョン信号をNTSC、PAL、またはSECAMのいずれかのフォーマットで受理し、受理した信号は表示処理装置が受理可能な画素ブロックに再配列される。表示処理装置は、画素ブロックフォーマットのビデオデータを受理し、表示ドライブ信号を生成する。

#### 【図面の簡単な説明】

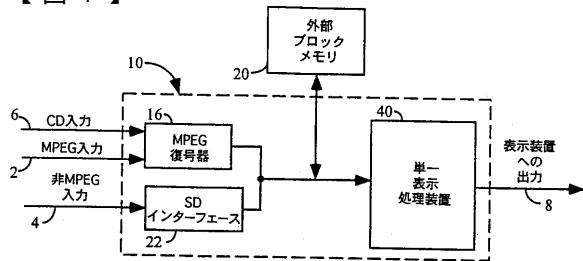

図1は、本発明の一実施例を示す構成図である。

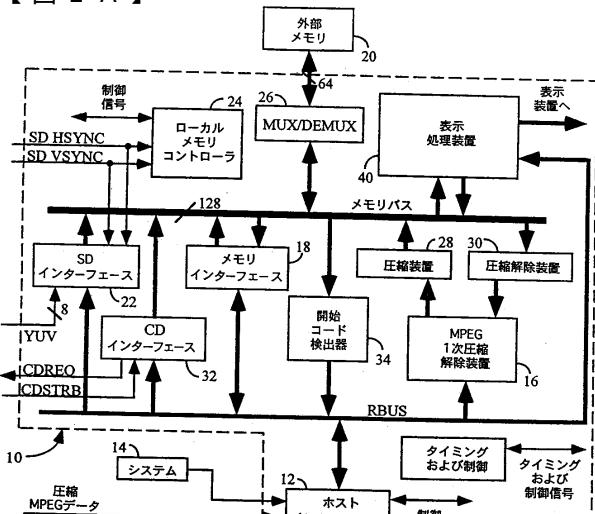

図2Aは、本発明を採用したSD/HDTV MPEG復号器および表示処理回路の構成図である。 10

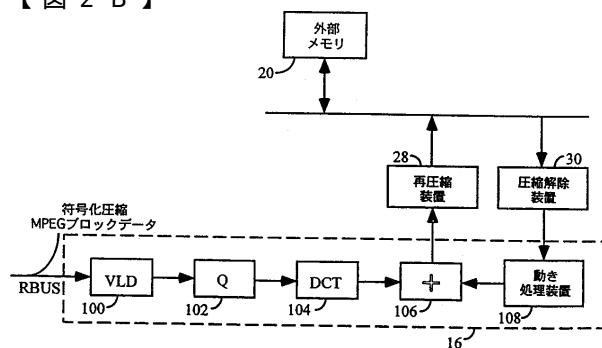

図2Bは、図2Aで使用されたMPEG圧縮解除装置の一実施例を示す構成図である。

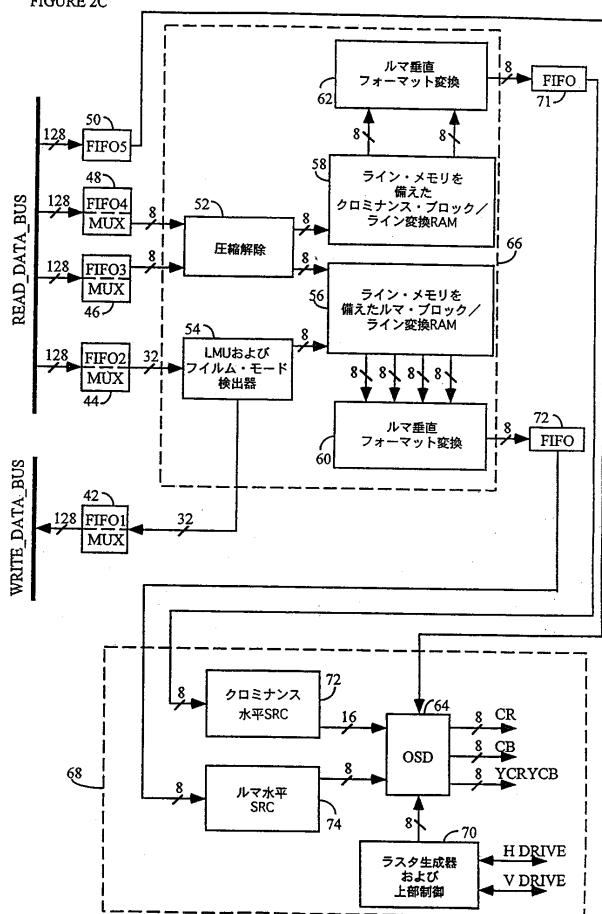

図2Cは、図2Aの表示処理装置の構成図である。

図3は、ラインからブロックへの変換例を示す図である。

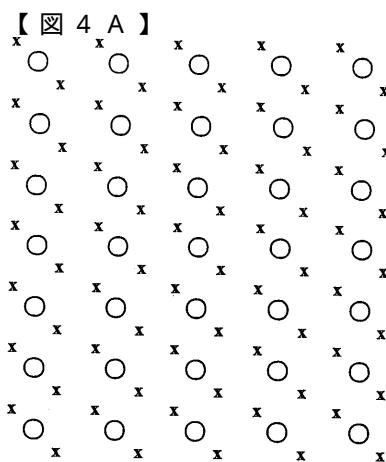

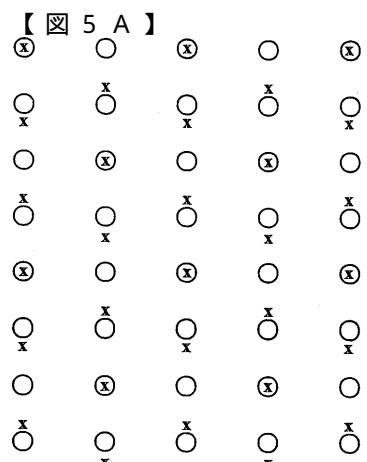

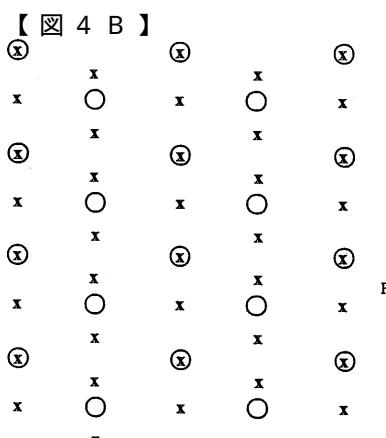

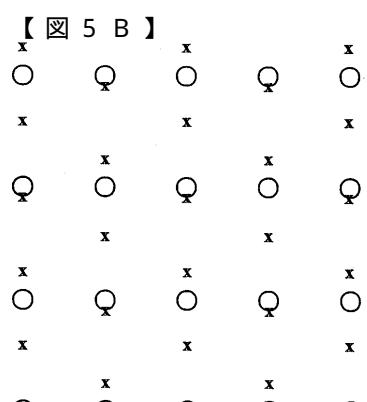

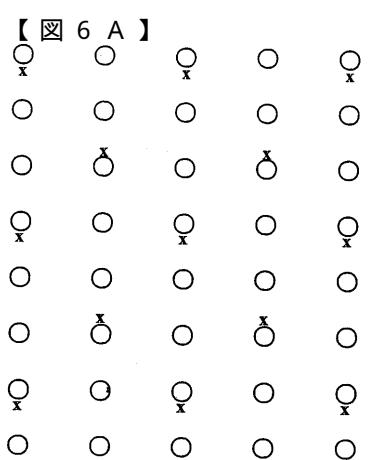

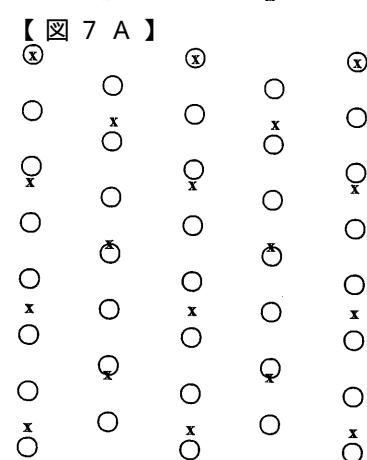

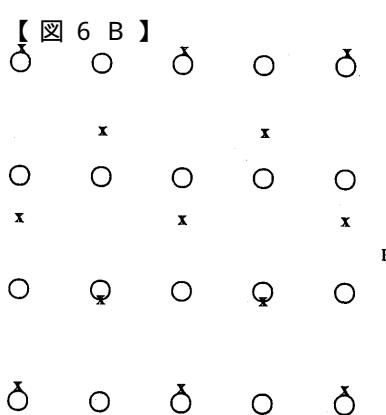

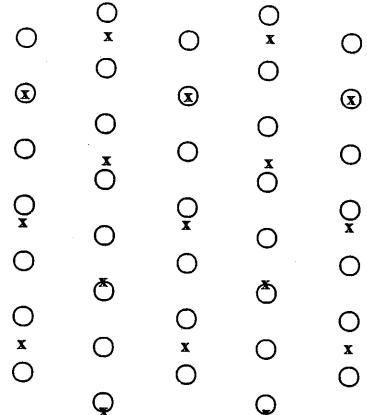

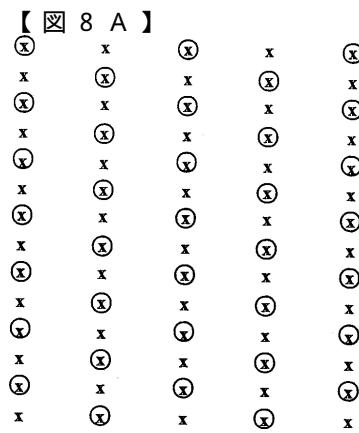

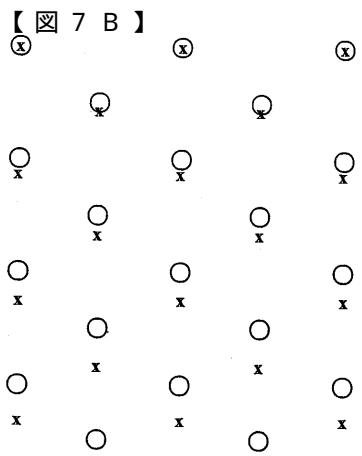

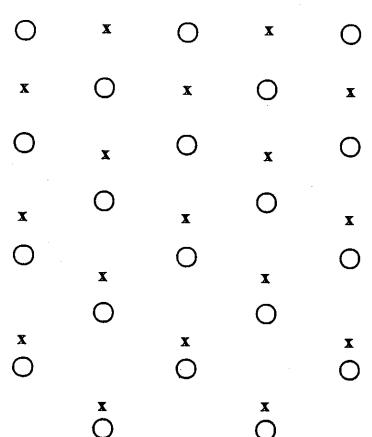

図4Aおよび図4Bから図8Aおよび図8Bは、復号器回路が実施する様々な信号フォーマット変換を示す図である。

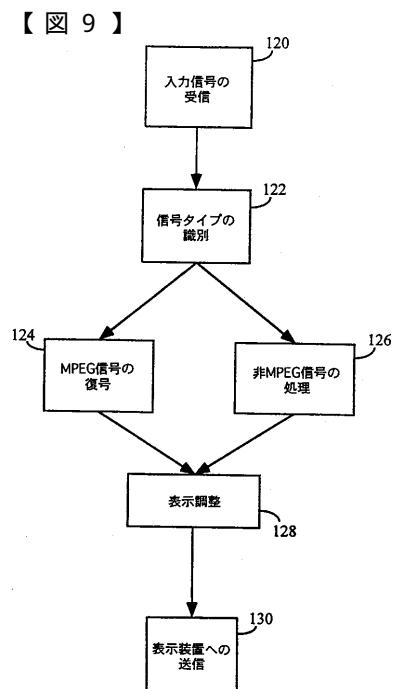

図9は、本発明に基づく、復号器を含む受信機を通る信号経路の流れ図である。

#### 好ましい実施例の説明

図1に、本発明の好ましい実施例の基本要素を示す。CD入力からおよびMPEG入力からの圧縮されたMPEGデータは、圧縮されたMPEGデータをMPEG復号器16に提供する。復号されたMPEGデータは、ブロックメモリ20および表示処理装置40に提供される。標準精細度データ、たとえばNTSCフォーマットの放送データは、SDインターフェース22によって受信され、これがラインデータを受理しブロックデータに変換する。ブロックメモリ20および同一の表示処理装置40は、標準精細度データをSDインターフェース22からブロックフォーマットで受信する。表示処理装置40は、両方のソースからブロックデータを受信し、所望の表示装置に合わせたフォーマットのブロック/ライン変換ならびに縦横比変換を行う。各要素16、20、22、および40の間のバス構造は、図のような共通バスでもよいが、要素16および22のそれぞれを要素20および40の両方に接続する別々のバスでもよい。 20

図2Aは、異なるフォーマットで発生する信号を1つまたは複数の好ましいフォーマットに変換するための表示処理回路を含む、圧縮ビデオ信号復号器の一部分を示す構成図である。図示されたすべての回路は、外部メモリおよびシステム制御を除き、単一の集積回路に組み込むことができるが、本発明を実施するにはそれは必ずしも必要ではない。たとえば図2Aの装置は、MPEG圧縮デジタルビデオ信号などを供給する、チューナ/中間周波回路、インターリーブ解除回路、エラー修正回路、および逆移送(transport)回路などを含んだ、高性能テレビジョン受像機(ATV)に組み込むことができる。図2Aの装置は、テレビジョン受信機が、たとえばコンポーネントNTSC、PAL、またはSECAM信号(すべてSDと呼ばれる)をCCIR601などのデジタルフォーマットで供給することを想定している。さらに図2Aの装置は、連続的にまたはバーストで一定速度および可変速度で伝送される、他のソースからの圧縮ビデオ信号を受信して復号する。受理可能なフォーマットで信号を供給する変換器を追加することで、復号器10に他のデータフォーマットを入力することもできる。そのようなデータフォーマットは、コンピュータ業界でたとえばRGB、VGA、SVGAなどとして知られているものである。復号器10は、SDビデオデータ以外の外部圧縮ビデオデータを復号器に結合する、入力インターフェース12を含んでいる。たとえば入力インターフェース12は、全システムコントローラ14、MPEG1次圧縮解除装置16、およびメモリインターフェース18に結合される。圧縮ビデオデータとは、たとえばHD-MPEGフォーマットデータなどである。入力インターフェース12は、この例では21ビット幅であるRBUSを介して、外部データおよび制御信号を復号器10の様々な部分と結合する。圧縮ビデオデータはMPEGフォーマットのパケットから取り出され、圧縮解除の前に外部メモリ20のバッ 30

40

50

ファへ格納される。

標準精細度デジタルビデオは、外部ソースから S D D A T A B U S と呼ばれる 8 ビットバスを介して S D インターフェース 2 2 へ直接加えられる。S D データは、デジタルラスタラインフォーマットで、すなわちラインごとに受信される。S D インターフェース 2 2 は、L M C 2 4 (ローカルメモリコントローラ) の制御下で動作し、S D データを表示処理装置 4 0 の入力要件に適合する画素ブロックデータとして外部メモリ 2 0 へ渡す。S D データはラインフォーマットの画素表示であるため、画素データは離散コサイン変換などを使用して他の表示に変換するのではなく、単に位置によって画素ブロックに再編成されるだけである。L M C 2 4 は、画素のラインを M P E G 互換表示処理装置 4 0 に適合する画素ブロックに再配列する高速コントローラである。L M C 2 4 は主としてハードウェアコントローラであり、ソフトウェアによるデータの部分的再編成を含んでいる。S D データを画素ブロックに変換すると、S D データおよび圧縮解除した M P E G データの両方が同一の表示処理装置によって処理できるので有利である。

S D インターフェース 2 2 は、表示処理装置 4 0 をバイパスしたり第 2 の互換表示処理装置を提供したりするよりも、簡単かつ低価格である。画素ブロックデータはラスタラインデータのように処理されないため、バイパスを行うには、S D データの受信時に表示処理装置 4 0 内にある多数の要素の再プログラミングおよび再構成を処理する必要がある。S D インターフェース 2 2 は、他の方法でならシステムコントローラ 1 4 が処理するはずのある種のタスクを処理する単純な要素である。これらのタスクには、1 ライン当たりの画素数を受信およびカウントすること、常に正しい量または情報が外部メモリ 2 0 に出力されるようにすること、およびブランкиング期間中はデータが出力されないようにすることが含まれる。さらに L M C 2 4 は、S D インターフェース 2 2 が受信したデータの再編成を指示する単純なアルゴリズムのみを必要とする。

図 3 には、ラインフォーマットからブロックフォーマットへデータを再編成する例を示す。一般に、S D インターフェース 2 2 が受信するデータはデジタルフォーマットである。ただし、S D インターフェース 2 2 の入力時または入力前に変換器(表示せず)を簡単に追加して、必要に応じてデータをデジタルフォーマットに変換することができる。A から L までの行は、4 : 2 : 2 の縦横比およびラスタラインフォーマットを有する画素データを示す。データ行は受信したデータフォーマットに基づいて継続する。S D インターフェース 2 2 は、ルミナンス(ルマ)と U および V クロミナンス値とを分離することによってデータを再編成する。ルミナンスデータは 8 × 8 ブロックのグループに分けられ、U および V クロミナンスデータは 4 × 4 ブロックのグループに分けられる。クロミナンスデータブロックには、U ブロックの奇数データ位置と V ブロックの偶数位置とが含まれる。また、再編成時に縦横比が 4 : 2 : 2 から 4 : 2 : 0 に変換されているが、縦横比変換は表示装置の入力データ要件によって異なる。再編成されたデータは、ブロックとして外部メモリ 2 0 に格納される。

1 回だけ表示される、可変速度で受信される、またはバーストで受信される圧縮データは、優先 C D (圧縮データ) インターフェース 3 2 の復号器 1 0 で受信される。データが C D インターフェース 3 2 上にあると、復号器 1 0 は正しい受信を行うためにそのインターフェースの動作を最優先にする。C D インターフェース 3 2 は、圧縮ビデオデータを M P E G 互換フォーマットで受け取る。C D インターフェース 3 2 は 8 ビット入力および 1 2 8 ビット出力を有するバッファを含み、このバッファがデータを変換し、圧縮解除の前に外部メモリ 2 0 に送信する。

外部メモリ 2 0 はさらに復号器 1 0 に外部接続されており、高精細度テレビジョン信号用に 9 6 M ビットの大きさまで可能である。接続は、マルチプレクサ / ディマルチプレクサ 2 6 を介して結合された 6 4 ビットバスである。ユニット 2 6 は、データを 1 2 8 ビット内部メモリデータバス (M E M B U S) から 6 4 ビットメモリバスに変換する。L M C 2 4 は、様々なインターフェースおよび様々な処理回路の要求に応じて、外部メモリ 2 0 への読み取り / 書き込みを制御する。L M C 2 4 は、ビデオデータをブロックフォーマットでメモリ 2 0 に格納するようにプログラムされ、この場合 1 ブロックは 8 × 8 画素データ

タのMPEG構造化ブロックと一致する。

復号器10は、その記憶域容量上の理由から、外部フレームメモリ20を圧縮ビデオデータ用の受信およびタイミングバッファとして使用する。受信データを圧縮解除する前にバッファに入れるには、大容量の記憶域が必要である。このバッファを集積回路に含めると、物理領域をかなり占有するので不利である。また、バッファリングはフレームを再構築するための画素ブロックの構成を容易にする。開始コード検出器34がオーバーヘッド情報を取り去り、圧縮解除に必要な情報を取得する。

圧縮された入力ビデオデータが初回圧縮解除のために外部メモリ20から取り出され、MEM BUSを介してMPEG圧縮解除装置16に加えられる。本発明の趣旨を変えることなく、他の圧縮解除フォーマットを利用することもできる。予測フレームのMPEG圧縮解除を行うには、予め圧縮解除した「アンカ(anchor)」フレームをメモリに格納し、圧縮解除してイメージを再構築する必要が生じたときに取り出す必要がある。図2Aの装置は、全フレームをメモリ20に格納する前に、圧縮解除したMPEGビデオデータの2次圧縮を組み込むので、受信機が必要とする外部メモリの量が著しく減少する。以下では、2次圧縮を再圧縮と呼ぶ。

初回圧縮およびそれ以降に行う圧縮解除は、移送(transport)ストリームにおける放送用MPEGフォーマットでのデータのフォーマット化である。図2Bは、MPEG圧縮解除装置の例である。図2Aの圧縮解除装置16は、MPEG圧縮解除装置に必要な一般要素を示した拡大図である。符号化および圧縮されたMPEGデータは、VLD(可変長復号器)100によってRBUS上で受信される。VLD100は復号されたデータを逆量子化器102に渡し、これが未量子化データを逆離散変形処理装置104に渡し、これがMPEG圧縮解除ブロックベースデータを作成する。このデータは結合器106にある動作処理装置108からのデータと結合され、再圧縮装置28に渡される。

再圧縮装置28はMPEG符号器内のMPEG圧縮とは異なり、数多くのフォーマットで実施される。たとえば再圧縮は、ブロックベースの差分パルス符号変調と、それに続く固定長、可変長、またはランレンジス符号化を含むことがある。あるいは、ブロックベースのハフマン符号化を組み込んでいることもある。圧縮による損失は、ない場合とある場合がある。

再圧縮は、図2AのMPEG圧縮解除装置16とMEM BUSとの間を結合する圧縮装置28で実行される。したがって、MPEGの復号および圧縮解除ビデオデータは、圧縮装置28に加えられてデータ再圧縮された後、外部メモリ20に格納される。再圧縮されたビデオデータが動作処理ネットワークにおけるMPEG予測フレームの再構築のために取り出されると、まず圧縮解除装置30に加えられ、この装置が圧縮装置28とは逆の処理を行う。圧縮解除装置30を通過した後に取り出されたデータは、MPEG復号器10が一連の動作補正処理で予測フレームを再構築するために使用する状態になっている。

HD再圧縮ビデオフレームとSDビデオフレームは、どちらも外部メモリ20から取り出され、表示または格納の前にコンポーネント信号として希望の縦横比および表示解像度で処理するために、MEM BUSを介して表示処理装置40に加えられる。外部メモリ20から取り出されたデータは、2つの機能を実行するFIFOの42、44、46、48、50を通じて表示処理装置40に加えられる。その1つはデータのタイムバッファリング機能である。もう1つは、MEM BUSからの16バイト幅データ(128ビット)を、1バイト幅データ(圧縮解除装置52へのMPEGデータ)または4バイト幅データ( LMU54へのSDデータ)に変換する機能である。ここで指定したバイト幅は例示的なものである。

表示処理装置40は図2Cに示してある。表示処理装置40では、再圧縮されたMPEGビデオデータが最初に圧縮解除装置52に加えられる。この装置は圧縮解除装置30と同じである。圧縮解除装置52は、圧縮解除したビデオルミナンス(Y)およびクロミナンス(C)ビデオコンポーネント信号をブロックごとに提供する。圧縮解除装置52からの圧縮解除されたMPEGコンポーネント信号は、それぞれ、ルミナンスおよびクロミナンスのブロック/ライン変換器56および58に加えられる。ブロック/ライン変換器は、

10

20

20

30

40

40

50

YおよびCコンポーネント信号をそれぞれルミナンスサンプルレート変換器（LUMA SRC60）とクロミナンスサンプルレート変換器（CHROMA SRC62）へラインごとに加える。ルミナンスおよびクロミナンスレート変換器60と62のどちらにも、垂直フォーマット変換用および水平サンプルレート変換用の回路が含まれる。垂直および水平変換器は、変換器間のタイミング移行を処理するように FIFOによって分割される。

サンプルレート変換器は特定システムのパラメータに応じてプログラム可能であり、画像当たりのライン数を増減したり、ライン当たりの画素数を増減したりすることができる。サンプルレート変換器からのルミナンスおよびクロミナンスコンポーネントデータは、コンポーネントビデオ信号上のオーバーレイテキストおよび／またはグラフィックスが認識するように選択的に調整された画面上表示（OSD64）に結合される。システムコントローラ14または入力データストリームのいずれかが外部メモリ20に格納されているOSDデータを提供するが、ブロックごとではない。

復号器10は、SD画像フォーマットの飛び越し解除、ならびにアップサンプリングした合計1125本のライン（アクティブラインは1080本）飛び越し走査出力または480本（アクティブ）のライン順次走査出力の生成のための回路を含んでいるので有利である。この回路はLMU54に配置されている。SD画像フォーマットには480本のアクティブ飛び越しラインが含まれる。より高い垂直解像度表示を高解像度モニタ画面に提供するために、出力のアクティブ順次ラインは最低480本にまで増やされる（960本のアクティブ飛び越しラインも可能か）。残りのアクティブライン（1080から960を引いた数）は黒になる。

LMU54（直線動き対応アップコンバータ）は、出力イメージ表示装置が必要とするライン変換を実行する。SD信号は外部メモリ20に格納され、その後、LMU54がイメージ動作を算出するために隣接フレームからのSD信号を同時に必要とするので外部メモリ20から取り出される。これは、MPEGフォーマットで知られる動き補正ではない。各フィールドでは、関連付けられたラインがLMU54を通過し、イメージの動き量に基づいてフィールドラインの隙間にあるラインを推定する。イメージの動きは、前のフィールドとフレームとの対応する画素値の差から推定する。動き値が通常ゼロの場合、前のフィールドからの飛び越しラインが推定ラインとして使用される。大きな動きが隙間ラインの近傍にある場合、その隙間ラインは現在のフィールドの隙間ラインより上および下にあるラインの平均から推定される。小さな動きしかない場合、その隙間ラインは、前のフィールドにあるラインと現在のフィールドから平均したラインとの組み合わせから推定される。動きが多いほど、前のフィールドからの飛び越しラインに関連して使用される現在のフィールドからの現在のラインより上および下にあるラインの平均も多くなる。ラインの平均値算出のためにメモリ20に隣接ラインを強制的に提供させるのではなく、ルミナンスのブロック／ライン変換器60の内部にあるメモリを使用して、隣接ラインからLMU54へビデオ信号を同時に提供するので有利である。さらに、LMU54は、フィルタと、ラインまたはフィールドあるいはその両方の遅延を使用し、フレーム内で発生した動作を基準にしてフレームを明瞭にする。

処理要素内部のFIFOメモリ（図を簡略するため図示せず）を介してMEMBUSからおよびMEMBUSへデータを加えることができる。図2Aの要素には入力FIFOまたは出力FIFOあるいはその両方があり、復号器10はこれを使用して途切れなく機能することができる。各要素は、データのセグメントをバッファ／FIFOにロードして、システムコントローラ14から独立して常駐データを処理することができるので、システムコントローラ14は他のタスクに専念できる。

表示処理装置には、異なるセクションを制御する2つの異なるクロックがある。

1つは圧縮解除クロックドメイン66で、もう1つは表示クロックドメイン68である。圧縮解除クロックドメイン66には、ブロック／ライン変換RAM56、58と同期的にインターフェースする必要があり、希望の帯域幅を達成するために40MHzから81MHzのクロック速度で動作する必要のある、すべての機能が含まれている。表示クロック

10

20

30

40

50

ドメイン 6 8 には、27MHz から 81MHz のクロック速度で最終出力と同期的に動作する必要のある機能が含まれている。この 2 つのクロックは、アプリケーションによって同じ速度で動作する場合と異なる速度で動作する場合がある。2 つのクロックドメイン間で受け渡されるビデオデータは、水平サンプルレート変換器コントローラから入力される FIFO の読み取り要求によって、FIFO 71、73（ルミナンスおよびクロミナンスにそれぞれ 1 つ）を介して渡される。

それぞれの FIFO には、表示処理装置 40 と LMC 24 からの読み取りおよび書き込みアクノリッジおよび要求信号に応答する制御論理が含まれる。制御論理には、それぞれの FIFO にあるデータ量を追跡するという目的と、データバスと同じクロックを使用する FIFO の「バス」エンドと表示クロックを使用する FIFO の「表示」エンドとの間で非同期インターフェースを制御するという目的もある。表示セクションには、実際には「バス」クロックなしで動作している回路の量をできる限り少なくする制御論理が含まれる。

10

表示データは必ずしも連続していたり均一である必要がないので、垂直フォーマット変換処理は、LMC 24 にいくつかの制約を与えていた。この実施例では、それぞれのビデオデータ経路（FIFO 3 ~ FIFO 5）について、メモリポインタ、アクティブラインレジスタ、上部フィールド開始レジスタ、および下部フィールド開始レジスタがある。上部および下部のフィールド開始レジスタは、ホストバスによって、最初に読み取られるフレームラインのアドレスに設定される。ここで、ライン 0 はフレームの最初のアクティブラインに対応している。上部または下部それぞれのフィールドが開始すると、対応するフィールド開始レジスタからのデータが、アクティブラインレジスタに転送される。

20

LMC 24 は各表示ラインの開始位置で、アクティブラインレジスタの内容を使用して（フィールドが別々に格納されている場合は、最初の有効ビットを使用して適切なフィールドを選択して）物理メモリアドレスを算出する。算出結果はメモリポインタにロードされ、FIFO はリセットされて指定した表示ラインに対応するデータが入力される。ラインインターバルでは、必要に応じてメモリポインタを修正し、追加データがフェッチ（fetch）される。同じラインインターバルで、アクティブラインレジスタは必ずしも増分する。ただし n は、0 から 7 までである。垂直フォーマット変換器は、各 FIFO の各ラインに対して新しい値 n を提供する。

フォーマット変換を実行する場合、FIFO 2~4 を使用して LMU 54 の制御ワードにアクセスする。それぞれの制御ワードは、外部メモリ 20 の 128 ビットワードに含まれている。この機能には、別々の上部および下部フィールド開始レジスタが必要であるが、各表示ラインには 1 つの 128 ビットワードだけが使用される。LMU 54 からの信号は、次の連続するメモリ位置から、またはフィールド開始レジスタが指定した位置から、次のラインの制御ワードを取得するように LMC 24 に指示する。

30

1 次または MPEG 圧縮解除データ（ただし 2 次的に再圧縮されたデータ）には、プロックベースで外部メモリ 20 からアクセスする。このデータは FIFO 3~4 および FIFO 4~8 を介してルミナンスおよびクロミナンス 2 次圧縮解除装置に加えられ、この装置が、圧縮解除したルミナンスおよびクロミナンス画素プロック値を与える。圧縮解除したルミナンスおよびクロミナンス画素値のプロックは、ローカル RAM メモリを備えるプロック / ライン変換器 56 と 58 とにそれぞれ加えられる。8 × 8 ブロック（ルミナンス）または 4 × 4 ブロック（クロミナンス）の全行が、それぞれのローカルメモリに書き込まれる。このメモリは、メモリ出力メモリに接続された変換器回路の即時機能に応じて、ラインごとまたは平行な複数ラインごとに読み出される。データが読み出されると新しいデータがその位置に書き込まれて、必要なローカルメモリ量を最小限にする。プロック / ライン変換器 56 と 58 のローカルメモリの例示サイズは、幅 8 バイト深さ 120 バイトと幅 8 バイト深さ 240 バイトである。ローカルメモリには入力マルチプレクサと出力マルチプレクサが含まれてあり、入力データをローカルメモリ内の記憶域用に 8 バイト幅データに配列し、メモリから読み取った 8 バイト幅データをそれぞれの垂直サンプルレート変換器で使用するように適切に配列する。

40

50

圧縮解除されたMPEGビデオを高精細度の16:9画面上に表示するための処理を行う水平および垂直のサンプルレート変換器は、それぞれ表Iおよび表IIに記載したライン変換を実行する。水平変換器は、81MHzまでの最大画素出力レートが可能であるものとする。

表I：水平変換

| 入力フォーマット                            | 出力フォーマット |

|-------------------------------------|----------|

| 352, 480, 544, 640, 720, 1280, 1920 | 1920     |

| 352, 480, 544, 640, 720, 960        | 960      |

| 352, 480, 544, 640, 720,            | 720      |

10

表II：垂直変換

| 入力フォーマット | 出力フォーマット                 |

|----------|--------------------------|

| 720順次    | 480飛び越し, 480順次, 1080飛び越し |

| 1080飛び越し | 480飛び越し, 480順次           |

| 240CIF   | 480飛び越し, 480順次, 1080飛び越し |

表Iおよび表IIは、ルミナンス信号変換について記載したものである。クロミナンス信号でも同様の変換が実行される。クロミナンスについて言えば、圧縮された信号は4:2:0フォーマットであり、前述のクロミナンス変換には4:2:0から4:2:2への追加変換が含まれる。通常このクロミナンス処理は、他の何らかの必要な垂直処理に含まれる。クロミナンス変換の場合、通常、結合再サンプリングおよび4:2:0/4:2:2変換用に2タップ多相フィルタが採用される。

図4から図8では、XおよびOが位置合わせされていないかまたは不正にオーバーラップしている場合がある。これらの図は配置を近似したものであるが、XとOの全体的位置関係は正確である。見かけの位置合わせ不良やオーバーラップは正常で、変換の非整数比によって生じるものである。

図4Aおよび図4Bは、4:2:0/4:2:2変換のみが必要な場合（すなわち、480順次を受け取り480飛び越しを表示するか、1080順次を受け取り1080飛び越しを表示する）に、入力クロミナンスラインと出力クロミナンスラインとの垂直/時間関係を図示したものである。図4Aおよび図4Bは、フィールドのライン部分を示したものである。円は4:2:0フォーマットの元の画素を示している。Xは4:2:2信号に変換された画素を示している。各フィールドの補間ラインは、それぞれのフィールドのラインから算出される。

図4Aはフレームベースの表示を示したもので、すべてのクロミナンスラインを使用して第1すなわち上のフィールドを生成した後、第2すなわち下のフィールドをもう一度生成する。図4Bはフィールドベースの表示を示したものである。この場合、偶数のクロミナンスライン（ライン0から始まる）を使用して第1すなわち上のフィールドを生成し、奇数のクロミナンスラインを使用して第2すなわち下のフィールドを生成する。

図5Aおよび図6Aは、図2Aに関して説明したのと同じフォーマットのルミナンス変換オプションを示したものである。図5Aは、720順次フォーマットを1080飛び越しフォーマットに変換する場合の、入力ルミナンスラインと出力ルミナンスラインの垂直/時間関係を示したものである。図6Aは、720順次フォーマットを480飛び越しフォーマットに変換する場合の、入力ルミナンスラインと出力起動ラインの垂直/時間関係を示したものである。

図5Bおよび図6Bは、前述のルミナンス変換に関連した対応するクロミナンス変換オプションを示したものである。図5Bは、720順次フォーマットを1080飛び越しフォーマットに変換する場合の、入力クロミナンスラインと出力クロミナンスラインとの垂直

20

30

40

50

/ 時間関係を示したものである。図 6 B は、720 順次フォーマットを 480 飛び越しフォーマットに変換する場合の、入力クロミナンスラインと出力クロミナンスラインとの垂直 / 時間関係を示したものである。

これら例示的変換に、時間処理は含まれていない。ルミナンスおよびクロミナンス処理は、垂直方向の場合にのみ生じる。さらに、入力クロミナンス情報はフレームベースであるため、フレームベースの 4 : 2 : 0 / 4 : 2 : 2 変換についてのみ考察すればよい。

図 7 A と図 7 B とは異なるものである。図 7 A は、1080 飛び越しフォーマットを 480 飛び越しフォーマットに変換する場合の、入力ルミナンスラインと出力ルミナンスラインとの垂直 / 時間関係を示したものである。図 7 B は、1080 飛び越しフォーマットを 480 飛び越しフォーマットに変換する場合の、入力クロミナンスラインと出力クロミナンスラインとの垂直 / 時間関係を示したものである。

10

図 8 A および図 8 B は、それぞれ、LMU54 が実行する SD ビデオ信号のルミナンス垂直変換とクロミナンス垂直変換とを図示したものである。垂直および時間処理は、垂直のみの処理ではなくこれらの変換に含まれるということを想起されたい。通常、飛び越し解除アルゴリズムの演算は、 $720 \times 480$  飛び越し（すなわち CCI-R601 解像度）サイズまでのイメージにのみ必要である。これらのイメージは、MPEG 復号プロセスから、または SD 入力ポートからの入力として発生させることができる。

図 9 は、本発明の原理に従った復号器を含む受信機を通る信号経路の流れ図である。受信機はこの入力信号を受信する（120）。前述のように、この入力信号は MPEG または非 MPEG の互換信号としてフォーマット化される。信号フォーマットは識別され（122）、適切な処理経路に送られる。信号フォーマットが MPEG 互換の場合、信号は前述のように復号化され（124）、表示処理装置と互換性のあるブロックデータが生成される。信号が MPEG 互換でない場合、信号は前述のように処理され（126）、表示処理装置と互換性のあるブロックデータが生成される。表示処理装置互換ブロックデータは表示処理装置に渡され、フォーマット化され特定の表示装置あるいは別の記憶装置との互換性を持たせたデータを生成する（128）。最終的に表示互換データは、表示装置または記憶媒体に送信される（130）。

20

【図1】

【 図 2 B 】

**FIGURE 2B**

【図2A】

FIGURE 2A

【 2 C 】

FIGURE 2C

【図3】

|     |    |    |    |    |    |    |    |    |    |    |    |    |     |      |      |      |      |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|-----|------|------|------|------|

| 行 A | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 B | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 C | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 D | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 E | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 F | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 G | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 H | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 I | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 J | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 K | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

| 行 L | Y1 | U1 | Y2 | V2 | Y3 | U3 | Y4 | V4 | Y5 | U5 | Y6 | V6 | ... | Y719 | U719 | Y720 | V720 |

FIGURE 3

|     |    |    |    |    |    |    |    |    |

|-----|----|----|----|----|----|----|----|----|

| 行 A | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 B | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 C | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 D | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 E | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 F | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 G | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

| 行 H | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 | Y8 |

|     |    |    |    |    |

|-----|----|----|----|----|

| 行 A | U1 | U3 | U5 | U7 |

| 行 C | U1 | U3 | U5 | U7 |

| 行 E | U1 | U3 | U5 | U7 |

| 行 G | U1 | U3 | U5 | U7 |

| 行 A | V2 | V4 | V6 | V8 |

| 行 C | V2 | V4 | V6 | V8 |

| 行 E | V2 | V4 | V6 | V8 |

| 行 G | V2 | V4 | V6 | V8 |

|     |    |     |     |     |     |     |     |     |

|-----|----|-----|-----|-----|-----|-----|-----|-----|

| 行 A | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 B | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 C | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 D | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 E | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 F | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 G | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

| 行 H | Y9 | Y10 | Y11 | Y12 | Y13 | Y14 | Y15 | Y16 |

|     |     |     |     |     |

|-----|-----|-----|-----|-----|

| 行 A | U9  | U11 | U13 | U15 |

| 行 C | U9  | U11 | U13 | U15 |

| 行 E | U9  | U11 | U13 | U15 |

| 行 G | U9  | U11 | U13 | U15 |

| 行 A | V10 | V12 | V14 | V16 |

| 行 C | V10 | V12 | V14 | V16 |

| 行 E | V10 | V12 | V14 | V16 |

| 行 G | V10 | V12 | V14 | V16 |

FIGURE 4A

FIGURE 5A

FIGURE 4B

FIGURE 5B

FIGURE 6A

FIGURE 7A

FIGURE 6B

FIGURE 8A

FIGURE 8B

FIGURE 9

---

フロントページの続き

(72)発明者 クラナウェター, グレッグ, アラン .

アメリカ合衆国 92692 カリフォルニア州 ミッション ヴィエジョ マルグリータ パー

クウェイ 21622 アパートメント 597

審査官 菅原 道晴

(56)参考文献 特開平08-098105 (JP, A)

D.Gilles, J.Doty, A.Rothermel, R.Schweer, "Combined TV Format Control and Sampling Rate Conversion IC", IEEE Transactions on Consumer Electronics, 米国, IEEE, 1994年

8月, Vol.40, No.3, p.711-p.717

(58)調査した分野(Int.Cl., DB名)

H04N 5/38 - 5/46

H04N 7/26 - 7/68

H04N 7/00 - 7/01