등록특허 10-2271643

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년07월05일

(11) 등록번호 10-2271643

(24) 등록일자 2021년06월25일

- (51) 국제특허분류(Int. Cl.)

*G06F 13/16* (2006.01)

- (52) CPC특허분류

*G06F 13/1673* (2013.01)

- (21) 출원번호 10-2019-7016088

- (22) 출원일자(국제) 2017년08월28일

심사청구일자 2019년06월04일

- (85) 번역문제출일자 2019년06월04일

- (65) 공개번호 10-2019-0067938

- (43) 공개일자 2019년06월17일

- (86) 국제출원번호 PCT/US2017/048849

- (87) 국제공개번호 WO 2018/089085

국제공개일자 2018년05월17일

- (30) 우선권주장

15/345,919 2016년11월08일 미국(US)

- (56) 선행기술조사문현

US20020056025 A1\*

US20090049234 A1\*

US20130111160 A1\*

US20150106582 A1\*

- \*는 심사관에 의하여 인용된 문헌

(73) 특허권자

마이크론 테크놀로지, 인크.

미국, 아이다호, 보이세, 사우스 페더럴 웨이

8000

(72) 발명자

콘팔로니에리, 에마누엘

이탈리아 레스모 20855 비아 씨. 엔에이 바라기아

1

달라보라, 마르코

이탈리아 멜레그나노 20077 비아 에프. 코리도니

10

(뒷면에 계속)

(74) 대리인

양영준, 백만기

전체 청구항 수 : 총 16 항

심사관 : 김세영

## (54) 발명의 명칭 하이브리드 메모리의 데이터 재배치

**(57) 요약**

본 개시는 하이브리드 메모리에서의 데이터 재배치를 위한 장치, 방법 및 시스템을 포함한다. 다수의 실시 예들은 메모리로서, 제1 유형의 메모리 및 제2 유형의 메모리를 포함하는, 메모리 및 제1 유형의 메모리에 저장된 데이터의 서브셋트에 대응하는 어드레스가 메모리 상에서 수행되는 프로그램 동작 중에 액세스되는 빈도에 적어도 부분적으로 기초하여 제1 유형의 메모리에 저장된 데이터의 서브셋트를 식별하여 제2 유형의 메모리로 재배치시키도록 구성된 제어기를 포함한다.

**대 표 도 - 도3**

(72) 발명자

아마토, 파울로

이탈리아 트래비글리오 24047 비아 이. 비그나미니

2/디

카라치오, 다닐로

이탈리아 밀라노 20133 비아 레나토 푸치니 3

발루치, 다니엘

이탈리아 세르누스코 술 나비글리오 20063 비아 고

리치아 14비]

## 명세서

### 청구범위

#### 청구항 1

장치에 있어서,

메모리로서, 제1 유형의 메모리 및 제2 유형의 메모리를 포함하는, 상기 메모리; 및

제어기로서,

상기 메모리 상에서 수행되는 프로그램 동작 동안 상기 제1 유형의 메모리에 저장된 데이터의 서브세트(subset)에 대응되는 어드레스(address)가 최소 빈도로 액세스(access)되었음을 결정할 때 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별하고;

상기 제2 유형의 메모리에 저장된 데이터를 상기 제1 유형의 메모리에 재배치할지 여부를 결정하기 위한 데이터의 임계량을 설정하고;

상기 제2 유형의 메모리에 저장된 데이터의 서브세트에 대해 수행되는 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족하지 않음을 결정할 때 상기 제1 유형의 메모리에 재배치하기 위해 상기 제2 유형의 메모리에 저장된 데이터의 서브세트를 식별하고; 그리고

상기 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족하지 않음을 결정할 때 상기 제2 유형의 메모리에 저장된 상기 식별된 데이터의 서브세트를 상기 제2 유형의 메모리로부터 상기 제1 유형의 메모리에 재배치하는 것을 개시하도록 구성된, 상기 제어기를 포함하는, 장치.

#### 청구항 2

제1항에 있어서, 상기 메모리 상에서 수행되는 프로그램 동작 동안 상기 제1 유형의 메모리에 저장된 데이터의 서브세트에 대응되는 어드레스가 액세스된 빈도를 나타내는 데이터는 상기 제1 유형의 메모리에 저장되는, 장치.

#### 청구항 3

제1항 및 제2항 중 어느 한 항에 있어서, 상기 제어기는 상기 제1 유형의 메모리의 FIFO(first in, first out) 버퍼의 상기 데이터의 서브세트의 위치에 적어도 부분적으로 기초하여 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별하도록 구성된, 장치.

#### 청구항 4

장치에 있어서,

메모리로서, 제1 유형의 메모리 및 제2 유형의 메모리를 포함하는, 상기 메모리; 및

제어기로서,

상기 제1 유형의 메모리에 저장된 데이터를 상기 제2 유형의 메모리에 재배치할지 여부를 결정하기 위한 데이터의 임계량을 결정하고;

상기 제1 유형의 메모리에 저장된 데이터의 서브세트에 대해 수행되는 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족하지 않음을 결정할 때 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별하고;

상기 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족하지 않음을 결정할 때 상기 제1 유형의 메모리에 저장된 상기 식별된 데이터의 서브세트를 상기 제1 유형의 메모리로부터 상기 제2 유형의 메모리에 재배치하는 것을 개시하고; 그리고

상기 메모리 상에서 수행되는 프로그램 동작 동안 상기 제2 유형의 메모리에 저장된 데이터의 서브세트에 대응되는 어드레스가 최소 빈도로 액세스되었음을 결정할 때 상기 제1 유형의 메모리에 재배치하기 위해 상

기 제2 유형의 메모리에 저장된 데이터의 서브세트를 식별하도록 구성된, 상기 제어기를 포함하는, 장치.

#### 청구항 5

제4항에 있어서, 상기 제어기는 상기 제1 유형의 메모리에 저장된 데이터의 서브세트에 대해 상기 감지 동작이 수행될 때 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별하도록 구성된, 장치.

#### 청구항 6

메모리를 동작시키는 방법에 있어서,

상기 메모리 상에서 수행되는 프로그램 동작 동안 데이터의 제1 서브세트가 최소 빈도로 액세스되었음을 결정할 때 제2 유형의 메모리에 재배치하기 위해 제1 유형의 메모리에 저장된 다수의 데이터의 서브세트들 중 데이터의 제1 서브세트를 식별하는 단계;

상기 제2 유형의 메모리에 저장된 데이터를 상기 제1 유형의 메모리에 재배치할지 여부를 결정하기 위한 데이터의 임계량을 설정하는 단계;

상기 제2 유형의 메모리에 저장된 데이터의 제2 서브세트에 대해 수행되는 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하지 않음을 결정할 때 상기 제1 유형의 메모리에 재배치하기 위해 상기 제2 유형의 메모리에 저장된 다수의 데이터의 서브세트들 중 데이터의 제2 서브세트를 식별하는 단계;

상기 식별된 데이터의 제1 서브세트를 상기 제1 유형의 메모리로부터 상기 제2 유형의 메모리에 재배치하는 단계; 및

상기 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하지 않음을 결정할 때 상기 식별된 데이터의 제2 서브세트를 상기 제2 유형의 메모리로부터 상기 제1 유형의 메모리에 재배치하는 단계를 포함하는, 방법.

#### 청구항 7

제6항에 있어서, 상기 메모리 상에서 수행되는 프로그램 동작 동안 최소 빈도로 액세스된 데이터의 서브세트는 상기 제1 유형의 메모리의 FIFO 버퍼의 가장 오래된 데이터의 서브세트인, 방법.

#### 청구항 8

제6항 및 제7항 중 어느 한 항에 있어서, 상기 메모리 상에서 수행되는 프로그램 동작 동안 최소 빈도로 액세스된 데이터의 서브세트는 상기 제1 유형의 메모리의 FIFO 버퍼로부터 제거된 데이터의 서브세트인, 방법.

#### 청구항 9

제6항 및 제7항 중 어느 한 항에 있어서,

상기 제1 유형의 메모리는 다수의 FIFO 버퍼들을 포함하고,

상기 다수의 FIFO 버퍼들 중 제1 버퍼는 상기 제2 유형의 메모리로부터 상기 제1 유형의 메모리에 재배치되고 재배치된 후 상기 메모리 상에서 수행되는 프로그램 동작 중에 액세스되지 않은 데이터의 서브세트를 포함하고;

상기 다수의 FIFO 버퍼들 중 제2 버퍼는 상기 메모리 상에서 수행되는 프로그램 동작 중에 한번 액세스된 데이터의 서브세트를 포함하고;

상기 다수의 FIFO 버퍼들 중 제3 버퍼는 상기 메모리 상에서 수행되는 프로그램 동작 중에 두 번 액세스된 데이터의 서브세트를 포함하고;

상기 다수의 FIFO 버퍼들 중 제4 버퍼는 상기 메모리 상에서 수행되는 프로그램 동작 중에 세 번 이상 액세스된 데이터의 서브세트를 포함하고; 그리고

상기 메모리 상에서 수행되는 프로그램 동작 중에 최소 빈도로 액세스된 데이터의 서브세트는 상기 다수의 FIFO 버퍼들 중 제1 버퍼 또는 상기 다수의 FIFO 버퍼들 중 제2 버퍼 중 하나로부터 제거된 데이터의 서브세트인, 방

법.

## 청구항 10

메모리를 동작시키는 방법에 있어서,

제1 유형의 메모리에 저장된 데이터를 제2 유형의 메모리에 재배치할지 여부를 결정하기 위한 데이터의 임계량을 설정하는 단계;

상기 제1 유형의 메모리에 저장된 데이터의 제1 서브세트에 대해 수행되는 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하는지 여부를 결정하는 단계;

상기 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하지 않음을 결정할 때 상기 데이터의 제1 서브세트를 상기 제1 유형의 메모리로부터 상기 제2 유형의 메모리에 재배치하는 단계;

상기 메모리 상에서 수행되는 프로그램 동작 동안 데이터의 제2 서브세트가 최소 빈도로 액세스되었음을 결정할 때 상기 제1 유형의 메모리에 재배치하기 위해 상기 제2 유형의 메모리에 저장된 데이터의 제2 서브세트를 식별하는 단계; 및

상기 데이터의 제2 서브세트를 상기 제2 유형의 메모리로부터 상기 제1 유형의 메모리에 재배치하는 단계를 포함하는, 방법.

## 청구항 11

제10항에 있어서,

상기 데이터의 서브세트는 상기 제1 유형의 메모리에 저장된 데이터의 서브세트들의 그룹 내의 하나의 데이터의 서브세트이고; 그리고

상기 방법은 상기 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하지 않음을 결정할 때 상기 제1 유형의 메모리로부터 상기 제2 유형의 메모리에 상기 데이터의 서브세트들의 그룹을 재배치하는 단계를 포함하는, 방법.

## 청구항 12

제10항에 있어서, 상기 제1 유형의 메모리로부터 상기 제2 유형의 메모리에 상기 데이터의 서브세트들의 그룹을 재배치하는 단계는,

상기 감지 동작 동안 감지되는 데이터를 상기 제2 유형의 메모리에 프로그래밍 하기 위해 프로그램 동작을 수행하는 단계; 및

상기 데이터의 서브세트에 대한 위치 데이터를 상기 감지되는 데이터가 프로그래밍되는 상기 제2 유형의 메모리의 위치로 업데이트하는 단계를 포함하는, 방법.

## 청구항 13

제12항에 있어서, 상기 제1 유형의 메모리로부터 상기 제2 유형의 메모리에 상기 데이터의 서브세트들의 그룹을 재배치하는 단계는 상기 제1 유형의 메모리의 상기 데이터의 서브세트에 저장된 상기 데이터를 무효화시키는 단계를 포함하는, 방법.

## 청구항 14

장치에 있어서,

메모리로서, 제1 유형의 메모리 및 제2 유형의 메모리를 포함하는, 상기 메모리; 및

제어기로서,

상기 메모리 상에서 수행되는 프로그램 동작 동안 상기 제1 유형의 메모리에 저장된 데이터의 서브세트에 대응되는 어드레스가 최소 빈도로 액세스되었음을 결정할 때 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별하고;

상기 제2 유형의 메모리에 저장된 데이터를 상기 제1 유형의 메모리에 재배치할지 여부를 결정하기 위

한 데이터의 임계량을 설정하고;

상기 제2 유형의 메모리에 저장된 데이터의 서브세트에 대해 수행되는 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하지 않음을 결정할 때 상기 제1 유형의 메모리에 재배치하기 위해 상기 제2 유형의 메모리에 저장된 데이터의 서브세트를 식별하고; 그리고

상기 감지 동작 동안 감지되는 데이터의 양이 상기 데이터의 임계량을 만족 또는 초과하지 않음을 결정할 때 상기 제2 유형의 메모리에 저장된 상기 식별된 데이터의 서브세트를 상기 제2 유형의 메모리로부터 상기 제1 유형의 메모리에 재배치하는 것을 개시하도록 구성된, 상기 제어기를 포함하는, 장치.

### 청구항 15

제14항에 있어서, 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별할 때, 상기 제어기는,

상기 제1 유형의 메모리의 상기 식별된 데이터의 서브세트에 저장된 상기 데이터를 감지하기 위한 감지 동작을 수행하고;

상기 감지되는 데이터를 상기 제2 유형의 메모리에 프로그래밍하기 위한 프로그램 동작을 수행하고;

상기 식별된 데이터의 서브세트에 대한 위치 데이터를 상기 감지되는 데이터가 프로그래밍되는 상기 제2 유형의 메모리의 위치로 업데이트하고; 그리고

상기 제1 유형의 메모리의 상기 식별된 데이터의 서브세트에 저장된 상기 데이터를 무효화시키도록 구성된, 장치.

### 청구항 16

제14항에 있어서, 상기 제2 유형의 메모리에 재배치하기 위해 상기 제1 유형의 메모리에 저장된 상기 데이터의 서브세트를 식별할 때, 상기 제어기는,

상기 식별된 데이터의 서브세트에 저장된 상기 데이터의 백업 사본이 저장되는 상기 제2 유형의 메모리의 위치를 검색하고;

상기 식별된 데이터의 서브세트에 대한 위치 데이터를 상기 검색된 위치로 업데이트하고; 그리고

상기 제1 유형의 메모리의 상기 식별된 데이터 서브세트에 저장된 상기 데이터를 무효화시키도록 구성된, 장치.

### 청구항 17

삭제

### 청구항 18

삭제

### 청구항 19

삭제

### 청구항 20

삭제

## 발명의 설명

### 기술 분야

[0001] 본 개시는 일반적으로 반도체 메모리 및 방법에 관한 것으로, 보다 상세하게는 하이브리드 메모리의 데이터 재배치(data relocation)에 관한 것이다.

### 배경 기술

- [0002] 메모리 디바이스는 일반적으로 컴퓨터 또는 기타 전자 디바이스의 내부, 반도체, 집적 회로 및/또는 외부 제거 가능한 디바이스로 제공된다. 휘발성 메모리와 비-휘발성 메모리를 포함하여 다양한 유형의 메모리가 있다. 휘발성 메모리는 데이터를 유지하기 위해 전력이 필요할 수 있으며, 랜덤 액세스 메모리(RAM), 동적 랜덤 액세스 메모리(DRAM), 및 동기식 동적 랜덤 액세스 메모리(SDRAM)를 포함할 수 있다. 비-휘발성 메모리는 전원이 공급되지 않을 때 저장된 데이터를 유지함으로써 영구 데이터를 제공할 수 있고, NAND 플래시 메모리, NOR 플래시 메모리, 판독 전용 메모리(ROM) 및 위상 변화 랜덤 액세스 메모리(PCRAM), 저항성 랜덤 액세스 메모리(RRAM), 및 자기 랜덤 액세스 메모리(MRAM)와 같은 저항 가변 메모리를 포함할 수 있다.

- [0003] 메모리 디바이스들은 고체 상태 드라이브 SSD, 내장된 멀티미디어 카드(e.MMC) 및/또는 범용 플래시 저장소(UFS) 디바이스를 구성하기 위해 함께 결합될 수 있다. SSD, e.MMC 및/또는 UFS 디바이스는 다양한 다른 유형의 비-휘발성 및 휘발성 메모리 중 비-휘발성 메모리(예를 들어, NAND 플래시 메모리 및/또는 NOR 플래시 메모리)를 포함할 수 있고 및/또는 휘발성 메모리(예를 들어, DRAM 및/또는 SDRAM)를 포함할 수 있다. 비-휘발성 메모리는 개인용 컴퓨터, 휴대용 메모리 스틱, 디지털 카메라, 셀룰러 전화, MP3 플레이어와 같은 휴대용 뮤직 플레이어, 영화 플레이어 등과 같은 다양한 전자 어플리케이션들에서 사용될 수 있다.

- [0004] 플래시 메모리 디바이스들은 예를 들어 플로팅 게이트와 같은 전하 저장 구조에 데이터를 저장하는 메모리 셀들을 포함할 수 있다. 플래시 메모리 디바이스들은 일반적으로 높은 메모리 밀도, 높은 신뢰성 및 낮은 전력 소모를 가능하게 하는 1-트랜지스터 메모리 셀을 사용한다. 저항 가변 메모리 디바이스들은 저장 요소(예를 들어, 가변 저항을 갖는 저항성 메모리 요소)의 저항 상태에 기초하여 데이터를 저장할 수 있는 저항성 메모리 셀들을 포함할 수 있다.

- [0005] 메모리 셀들은 어레이로 배열될 수 있고, 어레이 아키텍처의 메모리 셀들은 타겟(예를 들어, 원하는) 상태로 프로그래밍 될 수 있다. 예를 들어, 전하를 플래시 메모리 셀의 전하 저장 구조(예를 들어, 플로팅 게이트) 상에 배치하거나 이로부터 제거하여 특정 데이터 상태로 프로그래밍 할 수 있다. 셀의 전하 저장 구조 상의 저장된 전하는 셀의 임계 전압(Vt)을 나타낼 수 있다. 플래시 메모리 셀의 상태는 셀의 전하 저장 구조 상의 저장된 전하(예를 들어, Vt)를 감지함으로써 결정될 수 있다.

- [0006] 추가적인 예로서, 저항성 메모리 소자는 저항성 메모리 소자의 저항 레벨을 변화시킴으로써 타겟 데이터 상태에 대응하는 데이터를 저장하도록 프로그래밍 될 수 있다. 저항성 메모리 셀들은 특정 기간 동안 양 또는 음의 전기적 펄스(예를 들어, 양 또는 음 전압 또는 전류 펄스)와 같은 전기장 또는 에너지 원을 셀들(예를 들어, 셀의 저항성 메모리 요소에)에 인가함으로써 타겟 데이터 상태(예를 들어, 특정 저항 상태에 대응)로 프로그래밍 될 수 있다. 저항성 메모리 셀의 상태는 인가된 질의 전압(interrogation voltage)에 응답하여 셀을 통하는 전류를 감지함으로써 결정될 수 있다. 감지된 전류는 셀의 저항 레벨에 따라 달라지며 셀의 상태를 나타낼 수 있다.

- [0007] 단일 레벨 메모리 셀(single level memory cell, SLC)은, 이진 단위 1 또는 0으로 표현될 수 있는, 두 개의 다른 데이터 상태들 중 타겟팅된 하나로 프로그래밍 될 수 있다. 일부 플래시 및 저항성 메모리 셀들은 2 개 이상의 데이터 상태들(예를 들어, 1111, 0111, 0011, 1011, 1001, 0001, 0101, 1101, 1100, 0100, 0000, 1000, 1010, 0010, 0110 및 1110) 중 타겟팅된 하나로 프로그래밍 될 수 있다. 그러한 셀들은 다중 상태 메모리 셀들, 다중유닛 셀들 또는 다중레벨 셀들(MLCs)로 지칭될 수 있다. MLC들은 각각의 셀이 하나의 디지트 이상(예를 들어, 1 비트 이상)을 나타낼 수 있기 때문에 메모리 셀들의 수를 증가시키지 않고 고밀도 메모리를 제공 할 수 있다.

## 발명의 내용

### 도면의 간단한 설명

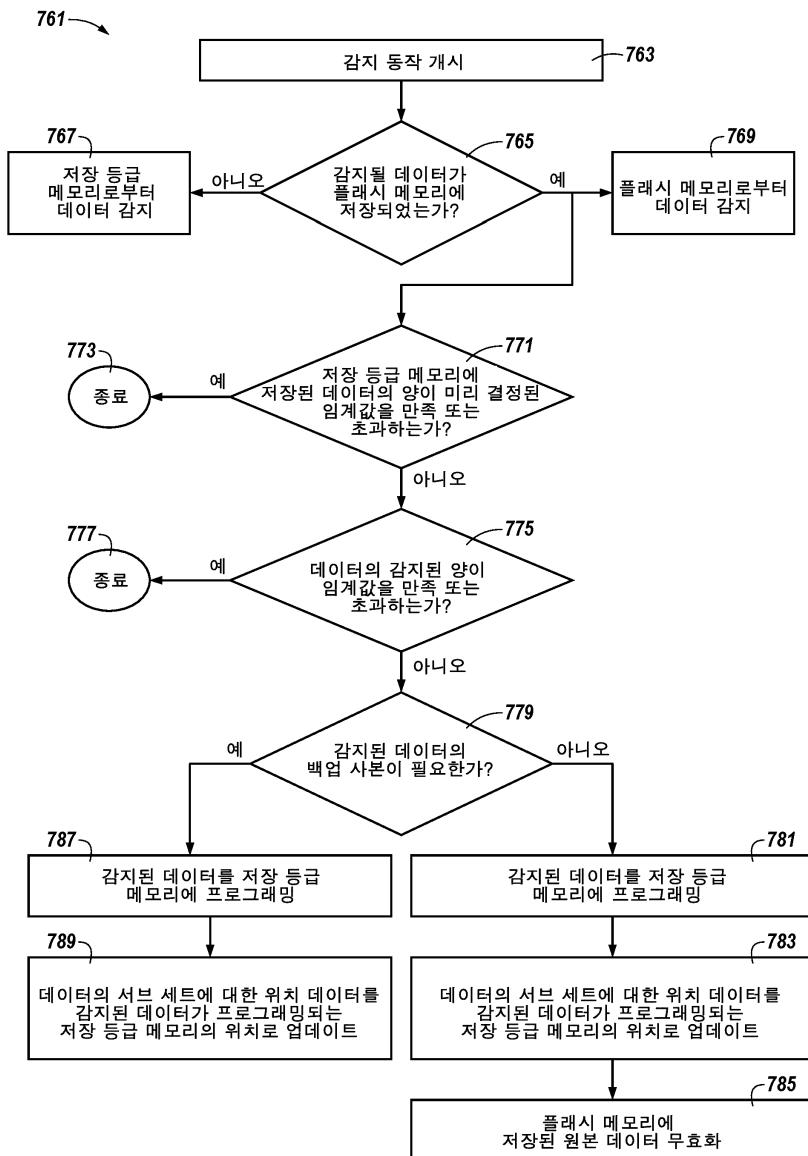

- [0008] 도 1은 본 개시의 다수의 실시 예들에 따른 다수의 물리적 블록들을 갖는 메모리 어레이의 일부의 다이어그램이다.

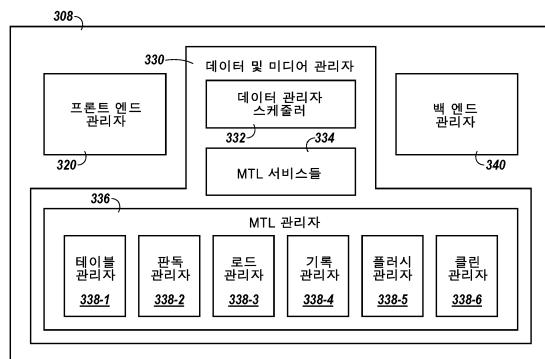

- 도 2는 본 개시의 다수의 실시 예들에 따른 메모리 디바이스의 형태로 호스트 및 장치를 포함하는 컴퓨팅 시스템의 블록 다이어그램이다.

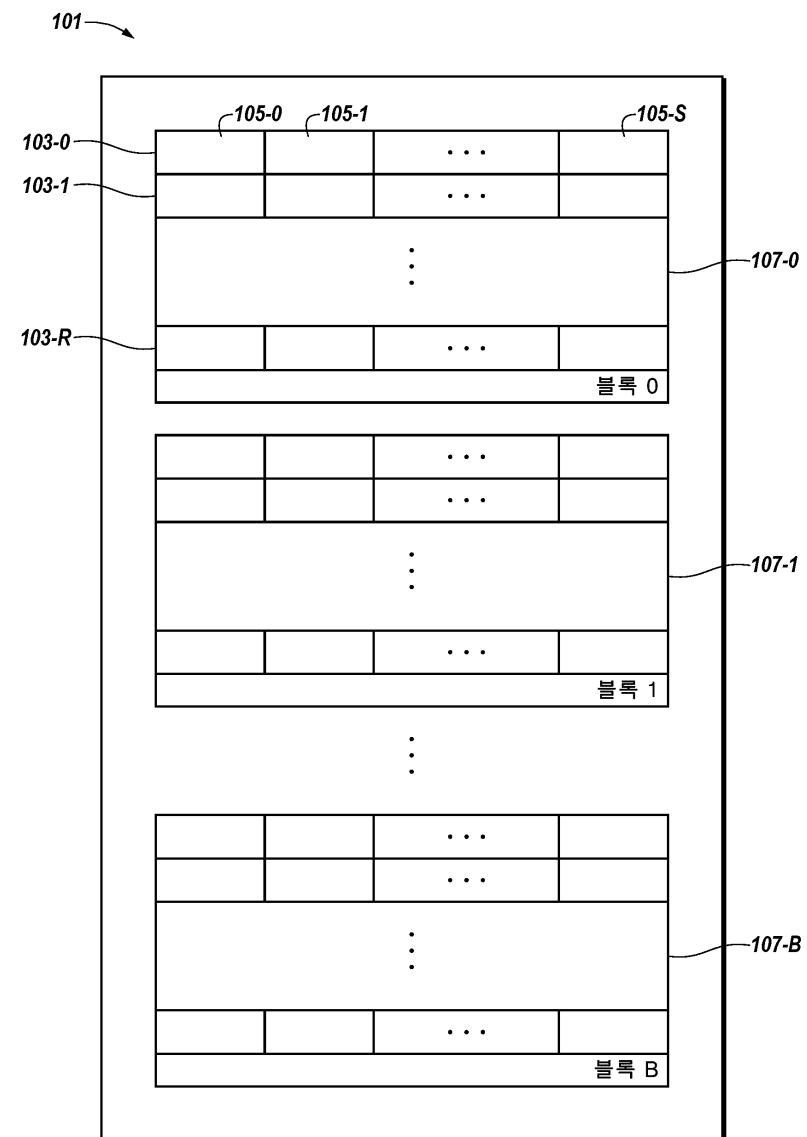

- 도 3은 본 개시의 다수의 실시 예들에 따른 메모리 디바이스 상의 제어기를 도시한다.

- 도 4는 본 개시의 다수의 실시 예들에 따른 메모리에 저장되고 테이블 매니저에 의해 관리되는 테이블의 엔트리 예시를 도시한다.

도 5는 본 개시의 다수의 실시 예들에 따른 메모리에서 재배치시키기 위한 데이터를 식별하는 프로세스의 개념적인 예시를 도시한다.

도 6a 및 도 6b는 본 개시의 다수의 실시 예에 따른 메모리를 동작시키는 방법을 도시한다.

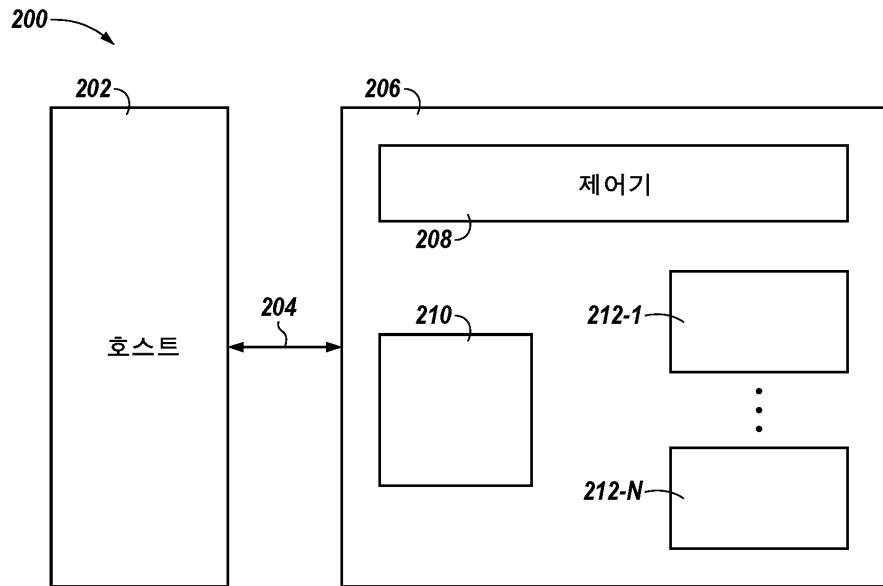

도 7은 본 개시의 다수의 실시 예들에 따른 메모리를 동작시키는 방법을 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0009]

본 발명은 하이브리드 메모리에서의 데이터 재배치를 위한 장치, 방법 및 시스템을 포함한다. 다수의 실시 예들은 메모리로서, 제1 유형의 메모리 및 제2 유형의 메모리를 포함하는, 상기 메모리 및 상기 제1 유형의 메모리에 저장된 상기 데이터의 서브세트에 대응하는 어드레스가 상기 메모리상에서 수행되는 프로그램 동작 중에 액세스되는 빈도에 적어도 부분적으로 기초하여 상기 제2 유형의 메모리로 재배치하기 위해 상기 제1 유형의 메모리에 저장된 데이터의 서브세트를 식별하도록 구성된 제어기를 포함한다.

[0010]

본원에 기술된 메모리와 같은, 2차 저장소로 사용하기 위해 2 가지 다른 유형의 메모리를 포함하는 메모리(예를 들어, DRAM 또는 SDRAM과 같은 메인 메모리에 추가로 및/또는 이와 분리하여)는 하이브리드 메모리로 지칭될 수 있다. 두 가지 유형의 메모리 중 하나는 다른 유형보다 빠른 액세스 시간을 가질 수 있으며 더 빠른 액세스 시간으로 소량의 데이터 프로그래밍을 메모리로 리디렉션하면 하이브리드 메모리의 성능이 향상될 수 있다(예를 들어, 속도를 증가시키고, 신뢰성을 증가 시키며 및/또는 전력 소비를 감소시키는). 또한 적은 양의 데이터 및/또는 빈번하게 감지되는 데이터를 더 느린 액세스 시간을 갖는 메모리에서 더 빠른 액세스 시간을 갖는 메모리로 재배치하면 하이브리드 메모리의 성능이 향상될 수 있다.

[0011]

그러나, 이러한 방식으로 하이브리드 메모리의 성능을 효과적으로 증가시키기 위해, 데이터가 프로그래밍 및/또는 재배치될 수 있는 보다 빠른 액세스 시간을 갖는 메모리에 이용 가능한 여유 공간이 있는 것이 유리할 수 있다(예를 들어, 보다 빠른 액세스 시간을 갖는 메모리가 가득 찬 경우, 추가 데이터는 거기에 프로그래밍 및/또는 재배치될 수 없다). 본 개시의 실시 예는 더 느린 액세스 시간을 갖는 메모리에 재배치될 수 있는 더 빠른 액세스 시간을 갖는 메모리에 저장된 데이터를 식별하고, 식별된 데이터를 더 느린 액세스 시간을 갖는 메모리로 재배치하고, 고속 메모리 액세스가 가능하고 하이브리드 메모리의 높은 성능을 유지할 수 있도록 여유 공간이 메모리에 계속 남아 있도록 보장한다. 또한, 본 개시의 실시 예는 더 빠른 액세스 시간을 갖는 메모리로 재배치될 수 있는 더 느린 액세스 시간을 갖는 메모리에 저장된 데이터를 효과적으로 식별할 수 있고, 하이브리드 메모리의 성능을 증가시키기 위해 식별된 데이터를 더 빠른 액세스 시간을 갖는 메모리에 재배치한다. 본 개시의 실시 예들은 전력 소비를 증가시키고 하이브리드 메모리의 성능을 감소시킬 수 있는 데이터 루프를 사용하지 않고 시너지(synergy)에서 이들 유형의 데이터 모두의 식별 및 재배치를 실행할 수 있다.

[0012]

본 명세서에서 사용되는 "다수의(a number of)" 무언가는 하나 이상의 그러한 것들을 지칭할 수 있다. 예를 들어, 다수의 메모리 셀들은 하나 이상의 메모리 셀들을 지칭할 수 있다. 또한, 특히 도면의 참조 번호에 대해 본 명세서에 사용된 지정자 "R", "B", "S" 및 "N"은 그렇게 지정된 특정 특징의 수가 본 개시의 다수의 실시 예에 포함될 수 있음을 나타낸다.

[0013]

본 명세서의 도면은 첫 번째 자리 또는 숫자가 도면 번호에 대응하고 나머지 숫자가 도면에서 요소 또는 구성 요소를 식별하는 번호 부여 규칙을 따른다. 서로 다른 숫자 사이의 유사한 요소 또는 구성 요소는 유사한 숫자를 사용하여 식별 할 수 있다. 예를 들어, 206은 도 2에서 요소 "06"을 참조할 수 있고, 유사한 요소는 도 3에서 306으로 참조될 수 있다.

[0014]

도 1은 본 개시의 다수의 실시 예들에 따른 다수의 물리적 블록들을 갖는 메모리 어레이(101)의 일부의 다이어그램을 도시한다. 메모리 어레이(101)는 예를 들어 NAND 플래시 메모리 어레이일 수 있다. 추가적인 예로서, 메모리 어레이(101)는 예를 들어 3D XPoint 메모리 어레이와 같은 저장 등급 메모리(storage class memory, SCM) 어레이, 강유전성 RAM(FRAM) 어레이 또는 PCRAM, RRAM와 같은 저항 가변 메모리 어레이 또는 스핀 토크 전달(spin torque transfer, STT) 어레이 등일 수 있다. 메모리 어레이(101)는 본원에서 더 설명되는 바와 같이(예를 들어, 도 2와 관련하여), 하이브리드 메모리의 일부일 수 있다. 또한, 도 1에는 도시되지 않았지만, 메모리 어레이(101)는 그 동작과 관련된 다양한 주변 회로와 함께 특정 반도체 다이 상에 위치될 수 있다.

[0015]

도 1에 도시된 바와 같이, 메모리 어레이(101)는 메모리 셀들의 다수의 물리적 블록들(107-0(BLOCK 0), 107-1(BLOCK 1), ..., 107-B(BLOCK B))을 포함한다. 메모리 셀들은 단일 레벨 셀들 및/또는 예를 들어 2 레벨 셀들, 3 레벨 셀들(TLCs) 또는 4 레벨 셀들(QLCs)과 같은 다중레벨 셀들일 수 있다. 예시로서, 메모리 어레이

(101) 내의 물리적 블록들의 수는 128 블록들, 512 블록들 또는 1024 블록들일 수 있으나, 실시 예들은 메모리 어레이(101) 내의 2의 특정 제곱 또는 임의의 특정 수의 물리적 블록들에 제한되지 않는다.

[0016] 메모리 셀들의 다수의 물리적 블록들(예를 들어, 블록들(107-0, 107-1, ..., 107-B))이 메모리 셀들의 평면에 포함될 수 있고, 다수의 메모리 셀들의 평면들이 다이에 포함될 수 있다. 예를 들어, 도 1에 도시된 예시에서, 각각의 물리적 블록(107-0, 107-1, ..., 107-B)은 단일 다이의 일부일 수 있다. 즉, 도 1에 도시된 메모리 어레이(101)의 부분은 메모리 셀들의 다이일 수 있다.

[0017] 도 1에 도시된 바와 같이, 각각의 물리적 블록(107-0, 107-1, ..., 107-B)은 액세스 라인들(예를 들어, 워드 라인들)에 결합된 메모리 셀들의 다수의 물리적 로우(row)들(예를 들어, 103-0, 103-1, ..., 103-R)를 포함한다. 각 물리적 블록의 로우들의 수(예를 들어, 워드 라인들)는 32일 수 있으나, 실시 예들은 물리적 블록당 로우들(103-0, 103-1, ..., 103-R)의 특정 수로 제한되지 않는다. 또한, 도 1에는 도시되지 않았지만, 메모리 셀들은 감지 라인들(예를 들어, 데이터 라인들 및/또는 디지트 라인들)에 결합될 수 있다.

[0018] 당업자가 알 수 있는 바와 같이, 각 로우(103-0, 103-1, ..., 103-R)는 다수의 메모리 셀들의 페이지들을 포함할 수 있다(예를 들어, 물리적 페이지들). 물리적 페이지는 프로그래밍 및/또는 감지 유닛을 나타낸다(예를 들어, 기능 그룹으로서 함께 프로그래밍 및/또는 감지되는 다수의 메모리 셀들). 도 1에 도시된 실시 예에서, 각각의 로우(103-0, 103-1, ..., 103-R)은 메모리 셀들의 하나의 물리적 페이지를 포함한다. 그러나, 본 개시의 실시 예들은 이에 제한되지 않는다. 예를 들어, 다수의 실시 예들에서, 각각의 로우는 메모리 셀들의 다수의 물리적 페이지들을 포함할 수 있다(예를 들어, 짹수의 비트 라인들에 결합된 메모리 셀들의 하나 이상의 짹수 페이지들 및 홀수의 비트 라인에 결합된 메모리 셀들의 하나 이상의 홀수 페이지들). 또한, 다중레벨 셀들을 포함하는 실시 예들에 있어서, 메모리 셀들의 물리적 페이지는 데이터의 다중 페이지들(예를 들어, 논리 페이지들)을 저장할 수 있다(예를 들어, 데이터의 상위 페이지 및 데이터의 하위 페이지로, 물리 페이지의 각 셀은 데이터의 상위 페이지를 향한 하나 이상의 비트 및 데이터의 하위 페이지를 향한 하나 이상의 비트를 저장함).

[0019] 본 개시의 다수의 실시 예들에서, 도 1에 도시된 바와 같이, 메모리 셀들의 페이지는 다수의 물리적 섹터들(105-0, 105-1, ..., 105-S)을 포함할 수 있다(예를 들어, 메모리 셀들의 서브세트들). 셀들의 각 물리적 섹터(105-0, 105-1, ..., 105-S)는 다수의 데이터(예를 들어, 데이터 워드들)의 논리 섹터들을 저장할 수 있다. 또한, 데이터의 각 논리 섹터는 특정 데이터 페이지의 일부분에 대응할 수 있다. 예로서, 특정 물리적 섹터에 저장된 데이터의 제1 논리 섹터는 데이터의 제1 페이지에 대응되는 논리 섹터에 대응될 수 있고, 특정 물리적 섹터에 저장된 데이터의 제2 논리 섹터는 데이터의 제2 페이지에 대응될 수 있다. 각 물리 섹터(105-0, 105-1, ..., 105-S)는 시스템 및/또는 사용자 데이터를 저장할 수 있고 및/또는 에러 정정 코드(error correction code, ECC) 데이터, 논리 블록 어드레스(logical block address, LBA) 데이터 및 반복 에러 데이터와 같은 오버헤드 데이터(overhead data)를 포함할 수 있다.

[0020] 논리 블록 어드레싱은 호스트가 데이터의 논리 섹터를 식별하는 데 사용할 수 있는 체계다. 예를 들어, 각각의 논리 섹터는 고유한 논리 블록 어드레스(LBA)에 대응될 수 있다. 또한, LBA는 또한 물리적 어드레스에 대응(예컨대, 동적으로 매핑)될 수도 있다. 데이터의 논리 섹터는 데이터의 다수의 바이트 수(예를 들어, 256 바이트, 512 바이트, 1,024 바이트 또는 4,096 바이트)일 수 있다. 그러나, 실시 예는 이를 예시들에 제한되지 않는다.

[0021] 물리적 블록들(107-0, 107-1, ..., 107-B), 로우들(103-0, 103-1, ..., 103-R), 섹터들(105-0, 105-1, ..., 105-S) 및 페이지들의 다른 구성이 가능할 수 있다는 것을 주목해야 한다. 예를 들어, 물리적 블록들(107-0, 107-1, ..., 107-B)의 로우들(103-0, 103-1, ..., 103-R)은 각각 512 바이트보다 많거나 적은 데이터를 포함할 수 있는 단일 논리 섹터에 대응하는 데이터를 저장할 수 있다.

[0022] 도 2는 본 개시의 다수의 실시 예에 따른 메모리 디바이스(206) 형태의 호스트(202) 및 장치를 포함하는 컴퓨팅 시스템(200)의 블록 다이어그램이다. 본원에서 사용된 바와 같이, "장치(apparatus)"는, 이에 제한되는 것은 아니지만, 예를 들어, 회로 또는 회로 소자, 다이 또는 다이들, 모듈 또는 모듈들, 디바이스 또는 디바이스들, 또는 시스템 또는 시스템들과 다양한 구조 또는 구조의 조합 중 임의의 것을 지칭할 수 있다. 또한, 다수의 실시 예들에서, 컴퓨팅 시스템(200)은 메모리 디바이스(206)와 유사한 다수의 메모리 디바이스들을 포함할 수 있다.

[0023] 도 2에 도시된 실시 예에서, 메모리 디바이스(206)는 제1 유형의 메모리(예를 들어, 제1 메모리 어레이(210)) 및 제2 유형의 메모리(예를 들어, 다수의 제2 메모리 어레이들(212-1, ..., 212-N))를 포함할 수 있다. 메모리 디바이스(206)는 하이브리드 메모리 디바이스일 수 있으며, 여기서 메모리 디바이스(206)는 다수의 제2 메모리 어레이들(212-1, ..., 212-N)과 다른 유형의 메모리인 제1 메모리 어레이(210)를 포함한다. 제1 메모리 어레이

(210)는 저장 등급 메모리(storage class memory, SCM)일 수 있으며, 이는 메모리 디바이스(206)를 위한 메모리로서 작용하는 비-휘발성 메모리일 수 있고, 이는 다수의 제2 메모리 어레이들(212-1, ..., 212-N)보다 빠른 액세스 시간을 가지기 때문이다. 예를 들어, 제1 메모리 어레이(210)는 3D XPoint 메모리, FRAM, 또는 PCRAM, RRAM 또는 STT 등과 같은 저항 가변 메모리일 수 있다. 다수의 제2 메모리 어레이들(212-1, ..., 212-N)은 다른 유형의 메모리 중에서 NAND 플래시 메모리일 수 있다.

[0024] 메모리 어레이(210) 및 메모리 어레이들(212-1, ..., 212-N)은 각각 도 1과 관련하여 이전에 설명된 메모리 어레이(101)와 유사한 방식으로 다수의 메모리 셀들의 물리적 블록들을 가질 수 있다. 또한, 메모리 어레이(210) 및 메모리 어레이들(212-1, ..., 212-N)은 다수의 데이터 서브세트들을 포함(예를 들어, 저장)할 수 있다. 각각의 데이터 서브세트는 시스템 및/또는 사용자(예를 들어, 호스트) 데이터, 메타 데이터 및 ECC 데이터(예를 들어, 패리티 비트)를 포함할 수 있다(예를 들어, 이들로 구성될 수 있다). 이러한 데이터의 서브세트들은 본 명세서에서 대형 관리 유닛들(large managed units, LMUs)로 지칭될 수 있으며, 예를 들어, 4 kB의 호스트 데이터를 포함할 수 있다.

[0025] 또한, 메모리 어레이(210) 및/또는 메모리 어레이들(212-1, ..., 212-N)은 다수의 엔트리들을 포함하는 데이터 테이블을 포함(예를 들어, 저장)할 수 있다. 테이블의 각각의 엔트리는 다수의 데이터 서브세트들 중 다른 하나에 대응될 수 있다. 예를 들어, 테이블의 각각의 엔트리는, 본원에서 더 설명되는 바와 같이(예를 들어, 도 4와 관련하여), 그의 데이터 서브세트 각각이 메모리 어레이(210) 및/또는 메모리 어레이들(212-1, ..., 212-N)에 저장되어 있는지를 나타내는 데이터와 그 어레이(들)의 그의 데이터 서브세트 각각의 위치를 나타내는 데이터를 포함할 수 있다. 각각의 테이블 엔트리는 또한, 본원에서 더 설명되는 바와 같이(예를 들어, 도 4와 관련하여), 메모리 어레이들(210 및 212-1, ..., 212-N) 상에서 수행된 프로그램 동작 중에 그의 각각의 데이터 서브세트에 대응하는 어드레스가 액세스된 빈도를 나타내는 데이터를 포함할 수 있다. 이러한 엔트리들은 본 명세서에서 작은 관리 유닛들(small managed units, SMUs)로 지칭될 수 있으며, 예를 들어 64B의 데이터를 포함할 수 있다. 다수의 실시 예들에서, 테이블 엔트리들의 크기는 SMU들의 크기보다 작을 수 있다. 이러한 실시 예들에서, 각각의 개별 SMU는 다수의 테이블 엔트리들을 포함할 수 있다.

[0026] 비록 도 2에 도시된 실시 예가 제1 유형의 메모리의 하나의 메모리 어레이를 포함하지만, 본 개시의 실시 예들은 이에 제한되지 않는다. 예를 들어, 다수의 실시 예들에서, 메모리 디바이스(206)는 다수의 SCM 어레이들을 포함할 수 있다. 그러나, 메모리 디바이스(206)는 제2 유형의 메모리보다 적은 제1 유형의 메모리를 포함할 수 있다. 예를 들어, 메모리 어레이(210)는 메모리 어레이들(212-1, ..., 212-N)에 저장된 것보다 적은 데이터를 저장할 수 있다.

[0027] 도 2에 도시된 바와 같이, 호스트(202)는 인터페이스(204)를 통해 메모리 디바이스(206)에 결합될 수 있다. 호스트(202) 및 메모리 디바이스(206)는 인터페이스(204) 상에서 통신(예를 들어, 커맨드 및/또는 데이터를 송신)할 수 있다. 호스트(202)는 랩탑 컴퓨터, 퍼스널 컴퓨터, 디지털 카메라, 디지털 기록 및 재생 디바이스, 이동 전화, PDA, 메모리 카드 판독기, 다른 호스트 시스템들 사이의 인터페이스 허브일 수 있고, 메모리 액세스 디바이스(예를 들어, 프로세서)를 포함할 수 있다. 당업자는 "프로세서(a processor)"가 병렬 처리 시스템, 다수의 코프로세서들 등과 같은 하나 이상의 프로세서들을 의도할 수 있다는 것을 이해할 것이다.

[0028] 인터페이스(204)는 표준화된 물리적 인터페이스의 형태일 수 있다. 예를 들어, 메모리 디바이스(206)가 컴퓨팅 시스템(200)의 정보 저장을 위해 사용될 때, 인터페이스(204)는, 다른 물리적 커넥터들 및/또는 인터페이스들 중에서, SATA (Serial Advanced Technology Attachment) 물리적 인터페이스, PCIe(peripheral component interconnect express) 물리적 인터페이스, USB(universal serial bus) 물리적 인터페이스 또는 SCSI(small computer system interface)일 수 있다. 그러나 일반적으로, 인터페이스(204)는 메모리 디바이스(206)와 인터페이스(204)를 위한 호환 가능한 수신기를 갖는 호스트(예를 들어, 호스트(202)) 사이에서 제어, 어드레스, 정보(예를 들어, 데이터) 및 다른 신호를 전달하기 위한 인터페이스를 제공할 수 있다.

[0029] 메모리 디바이스(206)는 호스트(202) 및 제1 메모리 어레이(210) 및 다수의 제2 메모리 어레이들(212-1, ..., 212-N)과 통신하기 위한 제어기(208)를 포함한다. 제어기(208)는 제1 메모리 어레이(210) 및 다수의 제2 메모리 어레이들(212-1, ..., 212-N)에 대한 동작을 수행하기 위한 명령을 전송할 수 있다. 제어기(208)는 제1 메모리 어레이(210) 및 다수의 제2 메모리 어레이들(212-1, ..., 212-N)과 통신하여, 다른 동작들 중에서, 데이터를 감지(예를 들어, 판독), 프로그래밍(예를 들어, 기록), 이동 및/또는 소거할 수 있다.

[0030] 제어기(208)는 메모리들(210 및 212-1, ..., 212-N)로서 동일한 물리적 디바이스(예를 들어, 동일한 다이) 상에 포함될 수 있다. 대안적으로, 제어기(208)는 메모리들(210 및 212-1, ..., 212-N)을 포함하는 물리적 디바이스

에 통신 가능하게 결합된 별도의 물리적 장치 상에 포함될 수 있다. 다수의 실시 예들에서, 제어기(208)의 구성 요소들은 분산된 제어기로서 다수의 물리적 디바이스들에 걸쳐 분산될 수 있다(예를 들어, 메모리와 동일한 다이 상의 일부 구성 요소들 및 다른 다이, 모듈 또는 보드 상의 일부 구성 요소들).

[0031] 호스트(202)는 메모리 디바이스(206)와 통신하기 위한 호스트 제어기를 포함할 수 있다. 호스트 제어기는 인터페이스(204)를 통해 메모리 디바이스(206)에 커맨드를 전송할 수 있다. 호스트 제어기는, 다른 동작들 중에서, 데이터를 판독, 기록 및/또는 소거하기 위해 메모리 디바이스(206) 및/또는 메모리 디바이스(206) 상의 제어기(208)와 통신할 수 있다.

[0032] 메모리 디바이스(206) 상의 제어기(208) 및/또는 호스트(202) 상의 호스트 제어기는 제어 회로 및/또는 로직(예를 들어, 하드웨어 및 펌웨어)을 포함할 수 있다. 다수의 실시 예들에서, 메모리 디바이스(206) 상의 제어기(208) 및/또는 호스트(202) 상의 호스트 제어기는 물리적 인터페이스를 포함하는 인쇄 회로 기판에 결합된 주문형 집적 회로(application specific integrated circuit, ASIC)일 수 있다. 또한, 메모리 디바이스(206) 및/또는 호스트(202)는 레지스터 및 휘발성 및/또는 비-휘발성 메모리의 버퍼를 포함할 수 있다.

[0033] 다수의 실시 예들에서, 제어기(208)는 메모리 어레이들(210 및 212-1, ..., 212-N) 상에서 수행된(예를 들어, 호스트 기록 커맨드의 결과로서 실행되는) 프로그램 동작 동안 제1 유형의 메모리에 저장된 데이터의 서브세트들에 대응하는 어드레스들이 액세스되는 빙도(예를 들어, LBA들이 데이터의 서브세트들을 식별하는 빙도)에 적어도 부분적으로 기초하여 제2 유형의 메모리(예를 들어, 메모리 어레이들(212-1, ..., 212-N)로 재배치(예를 들어, 이주)시키기 위해 제1 유형의 메모리(예를 들어, 메모리 어레이(210)의)에 저장된 데이터 서브세트들(예를 들어, LMU들)을 식별할 수 있고, 제1 유형의 메모리로부터 식별된 서브세트들을 제2 유형의 메모리로 재배치(relocate)할 수 있다. 예를 들어, 제어기(208)는 메모리 어레이들(210 및 212-1, ..., 212-N) 상에서 수행되는 프로그램 동작들 동안 제1 유형의 메모리에 저장된 다수의 데이터의 서브세트들 중에서 최소 빙도로 액세스된 데이터의 서브세트를 식별할 수 있고, 상기 데이터의 서브세트를 제2 유형의 메모리로 재배치할 수 있다. 식별 및 재배치는 메모리 어레이(210)에 저장된 테이블의 데이터를 사용하여 수행될 수 있으며, 본원에서 더 설명될 것이다.

[0034] 더욱이, 다수의 실시 예들에서, 제2 유형의 메모리에 저장된 데이터의 서브세트들에 대해 수행된 감지 동작들 동안 감지된 데이터의 양(예를 들어, 호스트 판독 커맨드들에 의해 요청된 데이터의 양) 및/또는 제2 유형의 메모리에 저장된 데이터의 서브세트들에 대응되는 어드레스들이 메모리 어레이들(210 및 212-1, ..., 212-N) 상에서 수행되는 감지 동작 동안 액세스된 빙도에 적어도 부분적으로 기초하여 제어기(208)는 제2 유형의 메모리에 저장된 데이터의 서브세트를 식별하여 제1 유형의 메모리로 재배치할 수 있고, 상기 제2 유형의 메모리로부터 상기 식별된 서브세트들을 상기 제1 유형의 메모리로 재배치할 수 있다. 예를 들어, 제어기(208)는 제2 유형의 메모리에 저장된 데이터의 서브세트에 대해 수행된 감지 동작 동안 감지된 데이터의 양이 특정 임계 값을 만족 또는 초과하는지를 결정할 수 있고, 상기 데이터의 양이 상기 특정 임계 값을 만족 또는 초과하지 않는 것(예를 들어, 보다 작다)을 결정할 때 상기 데이터의 서브세트를 상기 제1 유형의 메모리로 재배치한다. 식별 및 재배치는 본원에서 추가로 설명될 것이다.

[0035] 도 2에 도시된 실시 예는 본 개시의 실시 예들을 모호하게 하지 않기 위해 도시되지 않은 부가적인 회로, 로직 및/또는 구성 요소들을 포함할 수 있다. 예를 들어, 메모리 디바이스(206)는 I/O 회로를 통해 I/O 커넥터 상으로 제공된 어드레스 신호를 래칭(latching)하기 위한 어드레스 회로를 포함할 수 있다. 어드레스 신호는 로우 디코더 및 컬럼 디코더에 의해 수신되고 디코딩되어, 메모리 어레이(210 및 212-1, ..., 212-N)에 액세스 할 수 있다. 또한, 메모리 장치(206)는 예를 들어 DRAM 또는 SDRAM과 같은 주 메모리를 포함할 수 있으며, 이는 메모리 어레이들(210-1 및 212-1, ..., 212-N)과는 별도 것 및/또는 이에 추가 것일 수 있다.

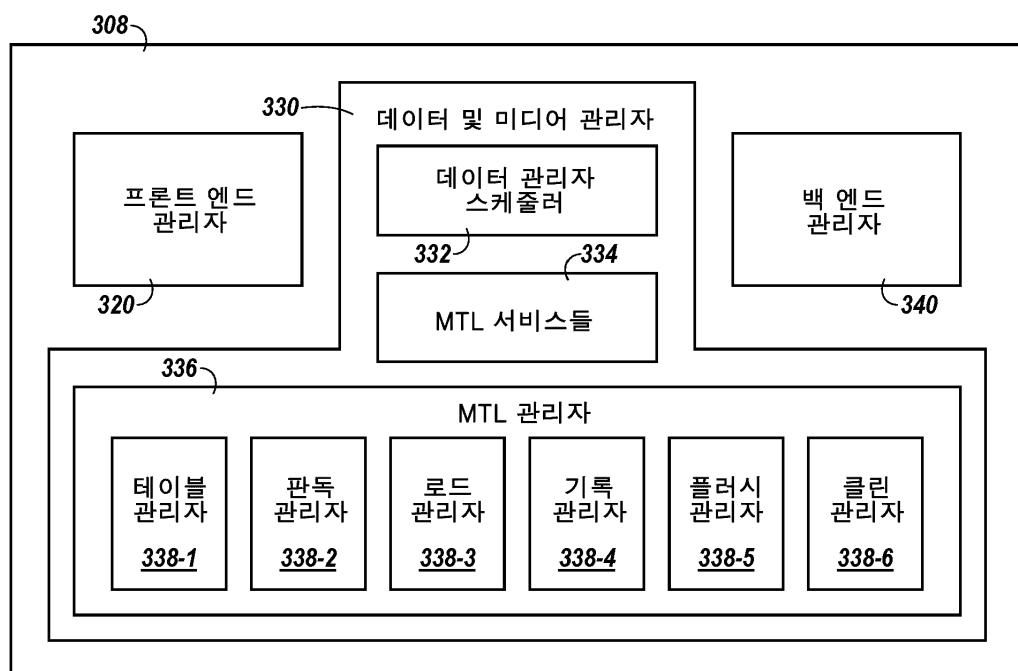

[0036] 도 3은 본 개시의 다수의 실시 예들에 따른 메모리 디바이스 상의 제어기(308)를 도시한다. 제어기(308)는 예를 들어 도 2와 관련하여 이전에 설명된 메모리 디바이스(206) 상의 제어기(208)일 수 있다. 예를 들어, 제어기(308)는 호스트(예를 들어, 도 2의 호스트(202)) 및/또는 메모리 어레이들(예를 들어, 도 2의 제1 메모리 어레이(210) 및/또는 다수의 제2 메모리 어레이들(212-1, ..., 212-N))과 통신하여 호스트 및/또는 메모리 어레이들로부터 및/또는 이들로 데이터를 판독, 기록, 이동 및/또는 소거할 수 있다.

[0037] 도 3에 도시된 바와 같이, 제어기(308)는 프론트 엔드 관리자 모듈(front end manager module)(320), 데이터 및 미디어 관리자 모듈(330) 및 백 엔드(back end) 관리자 모듈(340)을 포함할 수 있다. 프론트 엔드 관리자(320)는 호스트로부터 커맨드들을 수신하고 이를 커맨드들을 해석할 수 있다. 프론트 엔드 관리자(320)는 커맨드들과 관련된 데이터의 논리 어드레스들의 변환을 수행할 수 있다. 본원에서 사용된 바와 같이, "모듈

(module)"은 특정 기능을 수행하는데 사용될 수 있는 하드웨어, 펌웨어, 소프트웨어 및/또는 로직을 포함할 수 있다.

[0038] 데이터 및 미디어 관리자(330)는 호스트로부터 수신된 커맨드들을 더 처리할 수 있다. 데이터 및 미디어 관리자(330)는 데이터 관리자 스케줄러 모듈(332), 미디어 변환 계층(MTL) 서비스 모듈(334) 및 MTL 관리자 모듈(336)을 포함할 수 있다. 데이터 관리자 스케줄러(332)는 호스트로부터 수신된 각각의 커맨드가 언제 수행될지를 결정할 수 있다. MTL 서비스(334)는 기능을 MTL 관리자(336)에 제공하기 위한 다수의 API(application programming interface) 명령들의 세트들을 포함할 수 있다. 예를 들어, MTL 서비스(334)는, 다른 서비스들 중에서, 논리 어드레스-물리적 어드레스 변환을 수행하고, 메모리 어레이들로부터 데이터를 판독하고 및/또는 메모리 어레이에 데이터를 기록하는 API 명령을 포함할 수 있다.

[0039] 도 3에 도시된 바와 같이, MTL 관리자(336)는 테이블 관리자 모듈(338-1), 판독 관리자 모듈(338-2), 로드 관리자 모듈(338-3), 기록 관리자 모듈(338-4), 플러시(flush) 관리자 모듈(338-5) 및 클린(clean) 관리자 모듈(338-6)을 포함하여 메모리 어레이들에 대한 동작들을 수행할 수 있다. 테이블 관리자(338-1)는 메모리 어레이들에 저장된 데이터(예를 들어, 데이터의 서브세트들)를 위치 시키는데 사용될 수 있는 정보(예를 들어, 데이터)를 제공하고 관리하며, 프로그램 동작 동안 메모리 어레이들에 저장된 데이터(예를 들어, 데이터의 서브세트들)에 대응하는 어드레스들(예를 들어, LBA들)가 액세스되는 빈도를 식별한다. 이 정보는 메모리 어레이들 유형들 중 하나(예를 들어, 어레이(210))의 테이블에 저장될 수 있다. 예를 들어, 테이블은 다수의 엔트리들을 포함할 수 있으며, 각각의 상이한 엔트리는 메모리 어레이들의 데이터의 각각의 서브세트의 위치를 나타내는 데이터 및 프로그램 동작들 동안 그 각각의 서브세트에 대응하는 어드레스가 액세스된 빈도를 나타내는 데이터를 포함한다.

[0040] 예를 들어, 테이블 관리자(338-1)는 제1 유형의 메모리(예를 들어, 어레이(210))에 데이터에 대한 논리-물리 테이블을 생성 및 저장함으로써 메모리 디바이스(206)의 물리적 메모리 어레이들에 저장된 논리 블록들에 대한 논리 어드레스-물리적 어드레스 매핑을 제공할 수 있다. 논리-물리 테이블은 데이터가 제1 유형의 메모리(예를 들어, 어레이(210)) 및/또는 제2 유형의 메모리(예를 들어, 어레이(212-1, ..., 212-N))에 저장되는지 여부를 나타내는 논리 어드레스-물리적 어드레스 매핑의 비트 또는 비트들을 포함할 수 있다. 이러한 비트들은 본원에서 레지던시(residency) 데이터 또는 레지던시 비트들이라고 지칭될 수 있으며, 본 명세서에서 더 설명될 것이다(예를 들어, 도 4와 관련하여). 테이블 관리자(338-1)는 또한 메모리 어레이에 데이터를 배치하기 위해 논리-물리적 포인터들(pointers)을 생성 및 저장할 수 있다.

[0041] 또한, 테이블 관리자(338-1)는 카운터를 사용하여 메모리 어레이들에 저장된 데이터에 대한 주파수 정보를 제공하여 메모리 어레이들 상에서 수행되는 프로그램 동작 동안 데이터가 액세스되었는지의 여부 및/또는 얼마나 자주 그려하였는지 여부를 나타내는 테이블에 비트 또는 비트들을 생성 및 저장할 수 있다. 이러한 비트들은 본원에서 핫니스(hotness) 데이터 또는 핫니스 비트라고 지칭될 수 있으며, 본원에서 더 설명될 것이다(예를 들어, 도 4와 관련하여). 이러한 핫니스 비트들은 메모리 동작 중에도 업데이트될 수 있다. 예를 들어, 데이터의 서브세트에 대한 핫니스 비트는 메모리의 동작 중에 주기적으로 감소될 수 있고 및/또는 본 명세서에서 추가로 설명되는 바와 같이(예를 들어, 도 5와 관련하여), 프로그램 동작 중에 액세스되는 서브세트에 따라 증가될 수 있다.

[0042] 또한, 테이블 관리자(338-1)는 제1 유형의 메모리 내의 다수의 제1 입출력(FIFO) 버퍼에서 데이터의 서브세트(예를 들어, 각각의 서브세트에 대한 테이블 엔트리들)를 구성할 수 있으며, 각각의 버퍼는 다른 핫니스 데이터에 대응한다. 버퍼(들)은 예를 들어 순환 버퍼(들)일 수 있다. 특정 버퍼 내의 데이터 서브세트의 위치 및/또는 데이터의 서브세트가 버퍼 내에 있는지 여부는 프로그램 동작 동안 데이터 서브세트에 대응하는 어드레스가 액세스되는 빈도에 대응할 수 있고, 이 어드레스는 해당 어드레스에 연결된 데이터의 수명과 일치할 수 있다. 예를 들어, 특정 버퍼 내의 데이터의 가장 오래된 서브세트 및/또는 그 버퍼(예를 들어, 버퍼에서 다른 서브세트(들)로 대체 됨)로부터 제거된 데이터의 서브세트는, 그 버퍼에 대응하는 핫니스 데이터에 대해 최소 빈도로 액세스된 데이터의 서브세트(들)일 수 있다. 이러한 버퍼는 본 명세서에서 추가로 설명될 것이다(예를 들어, 도 5와 관련하여).

[0043] 판독 관리자(338-2)는 데이터를 메모리 어레이에 위치시키고 감지 커맨드들과 관련된 데이터를 호스트로 전송함으로써 감지(예를 들어, 판독) 커맨드들을 실행할 수 있다. 예를 들어, 호스트로부터 감지(예를 들어, 판독) 커맨드를 수신한 것에 응답하여, 판독 관리자(338-2)는 커맨드와 연관된 데이터를 감지하기 위한 감지 동작을 개시할 수 있다. 판독 매니저 (338-2)는, 테이블 매니저(338-1)에 의해 관리되는 테이블에 저장된 레지던시 데이터

터를 사용하여, 감지 동작 동안 감지될 데이터가 제1 유형의 메모리(예를 들어, 어레이(210)) 또는 제2 유형의 메모리(예를 들어, 어레이(212-1, ..., 212-N))에 저장되는지의 여부를 결정할 수 있고, 적절한 위치에서 데이터를 감지하고 감지된 데이터를 호스트로 전송할 수 있다. 감지된 데이터는 메모리 어레이에 저장된 다수의 데이터의 서브세트들 중 하나 이상의 일부 또는 전부를 포함할 수 있다.

[0044] 로드 관리자(338-3)는, 제2 유형의 메모리 상의 관독 관리자(338-2)에 의해 감지 동작이 수행되면(예를 들어, 감지된 데이터가 어레이(212-1, ..., 212-N)에 저장되는 경우), 감지 동작 동안 감지된 데이터의 양 및/또는 관독 관리자(338-2)에 의해 수행되는 감지 동작 중에 제2 유형의 메모리에 저장된 데이터의 서브세트(들)에 대응하는 어드레스(들)가 액세스된 빈도에 적어도 부분적으로 기초하여 제1 유형의 메모리(예를 들어, 어레이(210))로 재배치하기 위해 제2 유형의 메모리에 저장된 데이터의 서브세트 또는 서브세트들(예를 들어, LMU(들))을 식별할 수 있다. 예를 들어, 관독 관리자(338-2)에 의해 수행된 감지 동작 동안 감지된 데이터가 제2 유형의 메모리에 저장되는 경우, 그리고 제1 유형의 메모리에 저장된 데이터의 양이 사전 정의된 임계 값을 만족 또는 초과하지 않는 경우, 로드 관리자(338-2)는 감지 동작 동안 감지된 데이터의 양이 특정 임계 값을 만족 또는 초과하는지 및/또는 데이터가 감지된 빈도가 특정 임계 값을 만족 또는 초과하는지를 결정할 수 있다. 감지된 데이터의 양이 특정 임계 값을 만족 또는 초과하지 않는 경우 및/또는 데이터가 감지된 빈도가 특정 임계 값을 만족 또는 초과하는 경우, 로드 관리자(338-2)는 감지된 데이터를 포함하는 데이터의 서브세트(들)을 제1 유형의 메모리로 재배치하는 서브세트(들)로서 식별할 수 있다.

[0045] 제1 유형의 메모리로 재배치하기 위한 데이터의 서브세트(들)를 식별하면, 로드 관리자(338-3)는 재배치(예를 들어, 이송)를 진행할 수 있다. 예를 들어, 로드 관리자(338-3)는 관독 관리자(338-2)에 의해 수행된 감지 동작 동안 감지된 데이터를 제1 유형의 메모리에 프로그래밍하는 프로그램 동작을 수행하도록 기록 관리자(338-4)에 지시할 수 있고, 감지된 데이터가 프로그래밍되는 제1 유형의 메모리 내의 위치로 테이블 내의 식별된 서브세트(들)에 대한 위치(예를 들어, 레지던트) 데이터를 업데이트하도록 테이블 관리자(338-1)에 지시할 수 있다. 더욱이, 제2 유형의 메모리에 저장된 감지된 데이터의 백업 사본이 없다면, 로드 관리자(338-3)는 제2 유형의 메모리에 저장된 데이터의 원래 버전을 무효화할 수 있다. 그러나 백업 복사본이 있는 경우 이러한 무효화가 발생할 수 없다.

[0046] 다수의 실시 예들에서, 식별된 서브세트(들)은 제1 유형의 메모리에 저장된 데이터의 서브세트들의 순차 그룹(예를 들어, 클러스터)의 일부일 수 있다. 이러한 실시 예들에서, 서브세트들의 전체 그룹(예를 들어, 식별된 서브세트(들)뿐만 아니라 그룹 내의 데이터의 모든 서브세트들)은 제2 유형의 메모리로 재배치될 수 있다. 서브세트들의 그룹의 크기는, 예를 들어, 제1 유형의 메모리에 저장된 데이터 페이지의 크기와 동일할 수 있다.

[0047] 기록 관리자(338-4)는 프로그램 커맨드와 관련된 데이터를 제1 유형의 메모리(예를 들어, 어레이(210)) 및/또는 제2 유형의 메모리(예를 들어, 어레이(212-1, ..., 212-N))로 라우팅함으로써 프로그램(예를 들어, 기록) 커맨드를 실행할 수 있다. 예를 들어, 호스트로부터 프로그램 명령을 수신하는 것에 응답하여, 기록 관리자(338-4)는 프로그램 동작을 개시하여 그 커맨드와 관련된 데이터를 프로그래밍 할 수 있다.

[0048] 기록 관리자(338-4)는 다수의 기준들에 기초하여 제1 유형의 메모리, 제2 유형의 메모리, 또는 둘 모두에 데이터를 프로그래밍 할지 여부를 결정할 수 있다. 다수의 기준들은 다른 기준 중에서 프로그래밍되는 데이터의 크기, 메모리 어레이에서 사용 가능한 공간의 양 및/또는 데이터가 메모리 어레이에 기록되는 빈도를 포함할 수 있다. 예를 들어, 제1 유형의 메모리에 저장된 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하는 경우, 기록 관리자(338-4)는 데이터를 제2 유형의 메모리에 프로그래밍 할 수 있다. 더욱이, 제1 유형의 메모리에 저장된 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하지 않지만 프로그래밍 될 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하는 경우, 기록 관리자(338-4)는 또한 데이터를 제2 유형의 메모리에 프로그래밍 할 수 있다. 그러나, 제1 유형의 메모리에 저장된 데이터의 양이 그 미리 정의된 임계 값을 만족 또는 초과하지 않는 경우, 그리고 프로그래밍 될 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하지 않는 경우, 기록 관리자(338-4)는 데이터를 제1 유형의 메모리에 프로그래밍 할 수 있다.

[0049] 플러시 관리자(338-5)는, 미리 정의된 임계 값을 만족 또는 초과하는 제1 유형의 메모리(예를 들어, 어레이(210))에 저장된 데이터의 양에 따라, 제1 유형의 메모리에 저장된 데이터의 서브세트(들)에 대응하는 어드레스(들)가 기록 관리자(338-4)에 의해 수행되는 프로그램 동작 중에 액세스 된 빈도에 적어도 부분적으로 기초하여 제2 유형의 메모리(예를 들어, 어레이들(212-1, ..., 212-N))로 재배치하기 위해 제1 유형의 메모리에 저장된 데이터의 서브세트 또는 서브세트들(예를 들어, LMU(들))을 식별할 수 있다. 예를 들어, 플러시 관리자(338-5)는 미리 정의된 임계 값이 만족될 때 또는 미리 정의된 임계 값이 만족된 후에 다음 전원 사이클이 발생할 때

즉시 이 식별을 수행할 수 있다.

[0050] 예로서, 플러시 관리자(338-5)는 기록 관리자(338-4)에 의해 수행되는 프로그램 동작 동안, 메모리에 저장된 다수의 데이터의 서브세트들 중에서 최소 빈도로 액세스된 제1 유형의 데이터의 서브세트(들)을 식별하여, 서브세트(들)로서 제2 유형의 메모리로 재배치할 수 있다. 플러시 관리자(338-5)는 테이블 관리자(338-1)에 의해 관리되는 테이블에 저장된 주파수(예를 들어, 핫니스) 데이터를 사용하여 최소 빈도로 액세스되는 서브세트(들)를 식별할 수 있다. 또한, 플러시 관리자(338-5)는 서브세트가 테이블 관리자(338-1)에 의해 관리되는 베퍼에 있고, 및/또는 베퍼 내의 서브세트의 위치에 기초하여 최소 빈도로 액세스되는 서브세트(들)를 식별할 수 있다. 예를 들어, 플러시 관리자(338-5)는 최소 빈도로 액세스되는 서브세트로서 베퍼로부터 제거된 서브세트(들)를 식별할 수 있다. 추가적인 예로서, 플러시 관리자(338-5)는 베퍼 내의 각 서브세트에 대한 테이블 엔트리의 위치에 기초하여 최소 빈도로 액세스되는 서브세트(들)를 식별할 수 있다. 최소 빈도로 액세스되는 서브세트(들)의 식별은 본 명세서에서 더 설명될 것이다(예를 들어, 도 5와 관련하여).

[0051] 제2 유형의 메모리로 재배치하기 위한 데이터의 서브세트(들)를 식별하면, 플러시 매니저(338-5)는 재배치(예를 들어, 이송)를 진행할 수 있다. 예를 들어, 식별된 서브세트(들)에 대한 주파수 데이터가 그 서브세트(들)에 대응하는 어드레스(들)가 (예를 들어, 하나의) 프로그램 동작 동안 액세스되었음을 나타내는 경우, 플러시 매니저(338-5)는 식별된 서브세트(들)에 저장된 데이터를 감지하기 위해 판독 동작을 수행하도록 판독 관리자(338-2)에 명령하고, 기록 관리자(338-4)가 이 감지된 데이터를 제2 유형의 메모리에 프로그래밍 하기 위한 프로그램 동작을 수행하도록 명령하고, 테이블 관리자(338-1)에게, 감지된 데이터가 프로그래밍된 제2 유형의 메모리 내의 위치로 테이블 내의 식별된 서브세트에 대한 위치(예를 들어, 레지던시) 데이터를 업데이트하도록 명령하고, 그리고 식별된 서브세트(들)에 저장된 데이터를 제1 유형의 메모리에서 무효화할 수 있다. 식별된 서브세트(들)에 대한 주파수 데이터가 임의의 프로그램 동작 동안 그 서브세트(들)에 대응하는 어드레스가 액세스되지 않았음을 나타내는 경우, 그리고 식별된 서브세트(들)에 저장된 데이터의 백업 사본이 존재하면, 플러시 매니저(338-5)는 데이터의 백업 사본이 저장된 제2 유형의 메모리 내의 위치를 검색하고, 테이블 관리자(338-1)에게 이 검색된 위치를 갖는 테이블 내의 식별된 서브세트들에 대한 위치(예를 들어, 레지던시) 데이터를 갱신하도록 명령하고, 식별된 서브세트(들)에 저장된 데이터를 제1 유형의 메모리에서 무효화할 수 있다. 식별된 서브세트에 저장된 데이터의 백업 사본이 존재하지 않는 경우, 플러시 매니저(338-5)는 그 서브세트(들)에 대응하는 어드레스(들)가 프로그램 동작 중에 액세스되었음을 나타내는 식별된 서브세트(들)에 대한 주파수 데이터와 관련하여 기술된 것과 유사한 방식으로 식별된 서브세트(들)를 재배치할 수 있다.

[0052] 클린 매니저(338-6)는 데이터의 무효화된 서브세트(예를 들어, 무효화된 LMU들)를 소정의 값으로 리셋하고 그에 따라 리셋된 LMU의 상태를 업데이트 할 수 있다(예를 들어, 상태를 무효에서 프리(free)로 변경). 예를 들어, 제1 유형의 메모리에 이전에 기록된 데이터가 호스트에 의해 업데이트되고 테이블 관리자(338-1)가 아웃-오브-플레이스(out-of-place) 업데이트 전략을 구현하면, 업데이트된 데이터는 제1 유형의 메모리 내의 새로운 물리적 위치에 기록될 수 있고, 이전의 데이터는 무효화될 수 있다. 무효화 된 데이터는 이후 클린 관리자(338-6)에 의해 클리닝 될 수 있다.

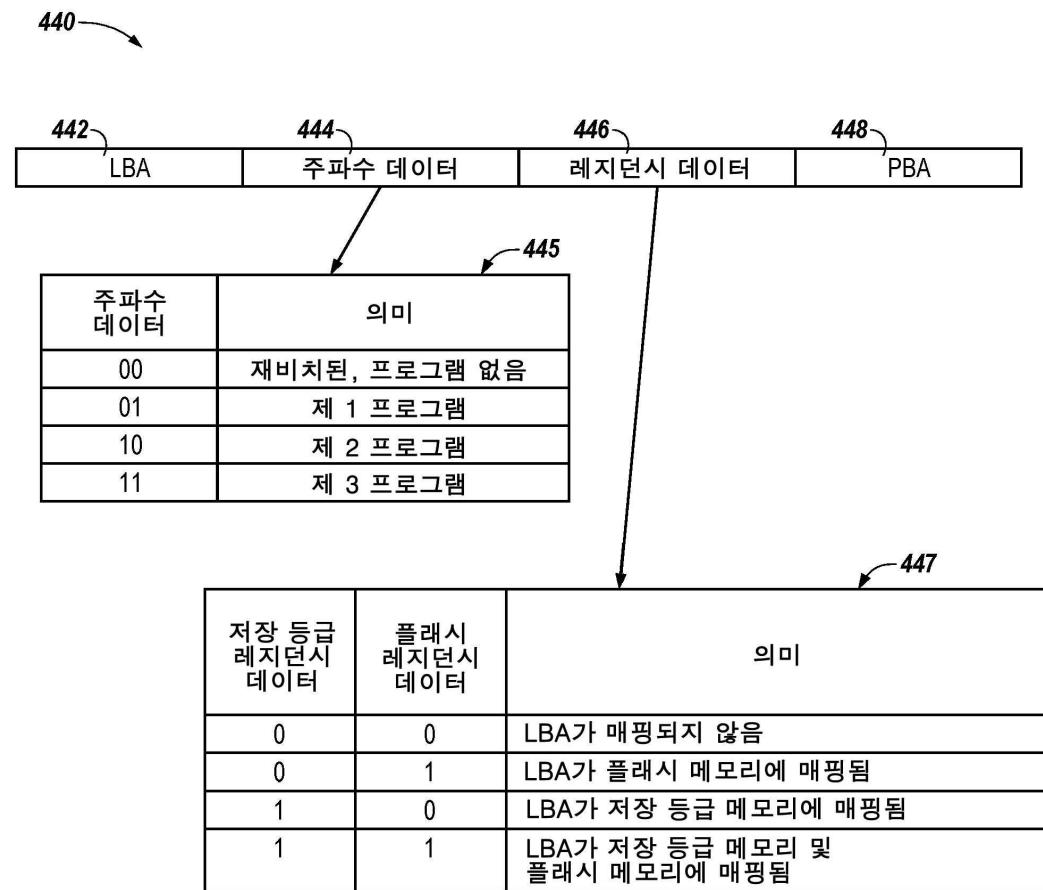

[0053] 도 4는 본 개시의 다수의 실시 예에 따른 메모리에 저장되고 테이블 관리자에 의해 관리되는 테이블 내의 엔트리(440)의 예를 도시한다. 예를 들어, 엔트리(440)는 제1 유형의 메모리(예를 들어, 도 2와 관련하여 이전에 기술된 어레이(210), 이는 예를 들어, SCM일 수 있음)에 저장된 테이블 내의 엔트리(예를 들어, SMU)일 수 있고 도 3과 관련하여 이전에 설명된 테이블 관리자 모듈(338-1)에 의해 관리될 수 있다. 또한, 엔트리(440)는 제1 유형의 메모리 및/또는 제2 유형의 메모리(예를 들어, NAND 플래시 메모리일 수 있는 도 2와 관련하여 앞서 설명된 어레이(212-1, ..., 212-N))에 저장된 데이터(예를 들어, LMU)의 서브세트에 대응할 수 있다.

[0054] 도 4에 도시된 바와 같이, 엔트리(440)는 논리 블록 어드레스(LBA)(442), 빈도(예를 들어, 핫니스) 데이터(444), 레지던시 데이터(446) 및 물리 블록 어드레스(PBA)(448)를 포함할 수 있다. 레지던시 데이터(446)는 데이터의 서브세트가 제1 유형의 메모리(예컨대, SCM), 제2 유형의 메모리(예를 들어, 플래시 메모리), 또는 둘 다에 저장되는지 여부를 나타낼 수 있으며, LBA(442) 및 PBA(448)는 그것이 저장되어있는 어레이(들)에서 데이터의 서브세트를 위치 시키는데 사용될 수 있다.

[0055] 도 4에 도시된 테이블(447)은 엔트리(440)에 포함될 수 있는 상이한 가능한 레지던시 데이터(예를 들어, 비트)의 예를 도시한다. 테이블(447)에 도시된 예에서, 레지던시 데이터(446)는 데이터 서브세트가 SCM에 저장되는지 여부를 나타낼 수 있는 제1 비트(예를 들어, 저장 등급 레지던시 비트) 및 데이터 서브세트가 플래시 메모리에 저장되는지 여부를 나타낼 수 있는 제2 비트(예를 들어, 플래시 레지던시 비트)를 포함할 수 있다. 예를 들어,

테이블(447)에 설명된 것처럼, 저장 등급 레지던시 비트 0 및 플래시 레지던시 비트 1은 플래시 메모리에 데이터의 서브세트가 저장되었음을 나타내며(예를 들어, LBA(442)는 PBA(448)에 매핑되어 데이터를 위치 시킴), 저장 등급 레지던시 비트 1 및 플래시 레지던시 비트 0은 데이터의 서브세트가 SCM에 저장되었음을 나타내고(예를 들어, LBA(442)는 PBA(448)에 매핑되어 데이터를 위치 시킴), 저장 등급 레지던시 비트 1 및 플래시 레지던시 비트 1은 SCM 및 플래시 메모리 모두에 데이터의 서브세트가 저장됨을 나타낸다(예를 들어, LBA(442)는 PBA(448)에 매핑되어 데이터를 위치 시킴). 저장 등급 레지던시 비트 및 플래시 레지던시 비트는 매핑되지 않은 LBA의 경우 모두 디폴트가 0이다.

[0056] 주파수(예컨대, 핫니스) 데이터(444)는 프로그램 동작 중에 데이터 서브세트에 액세스됨(예를 들어, LBA 식별) 어드레스에 주파수가 표시될 수 있다. 도 4에 도시된 테이블(445)은 엔트리(440)에 포함될 수 있는 상이한 가능한 주파수 데이터(예를 들어, 비트)의 예를 도시한다. 테이블(445)에 설명된 예시에서, 주파수 데이터(444)는 데이터 서브세트에 대응하는 어드레스가 액세스될 수 있는 4 개의 가능한 주파수를 나타내기 위해 사용될 수 있는 2 비트를 포함할 수 있다. 예를 들어, 테이블(445)에 예시된 바와 같이, 주파수 비트 00은 데이터 서브세트가 플래시 메모리에서 SCM으로 재배치되었지만 재배치된 후 임의의 프로그램 동작(들) 동안 아직 액세스되지 않았음을 나타낸다. 주파수 비트 01은 프로그램 동작 중 데이터 서브세트가 한 번 액세스되었음을 나타내며, 이는 SCM에 데이터를 직접 기록하는 동안 또는 플래시 메모리에서 재배치된 후 서브세트에서 수행된 첫 번째 기록 중에 발생할 수 있다. 주파수 비트 10은 프로그램 동작 중에 데이터의 서브세트가 두 번 액세스되었음을 나타내고, 주파수 비트 11은 프로그램 동작 중 데이터 서브세트가 세 번 이상 액세스되었음을 나타낸다.

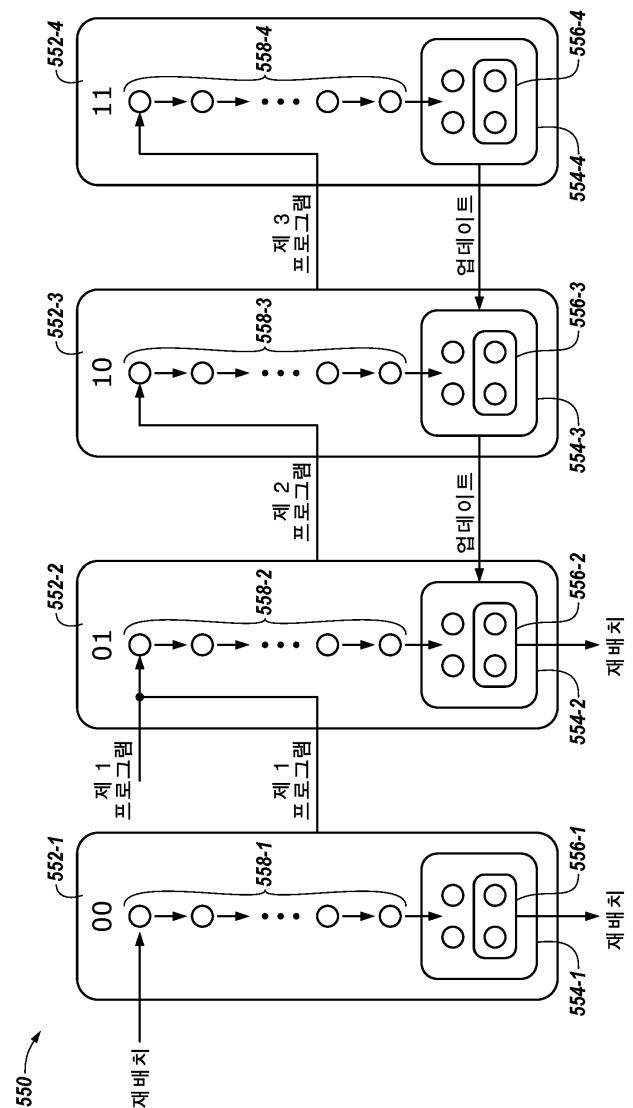

[0057] 도 5는 본 개시의 다수의 실시 예들에 따른 메모리에서 재배치하기 위한 데이터를 식별하는 프로세스의 개념적 예시(550)를 도시한다. 예를 들어, 도 5는 제1 유형의 메모리에 저장된 데이터 서브세트(예를 들어, LMU)를 식별하여 제2 유형의 메모리로 재배치하기 위한 예시적인 프로세스를 도시한다. 제1 유형의 메모리는, 예를 들어, 도 2와 관련(예를 들어, SCM)하여 이전에 설명된 어레이(210)일 수 있고, 제2 유형의 메모리는 예를 들어 도 2와 관련(예컨대, NAND 플래시 메모리)하여 설명된 어레이(212-1, ..., 212-N)일 수고, 프로세스는 예를 들어 각각 도 2 및 도 3과 관련하여 이전에 기술된 제어기들(208 및 / 또는 308)에 의해 수행될 수 있다. 데이터의 서브세트는 도 5에 표시된 원으로 표시된다. 예를 들어, 도 5에 도시된 각각의 원은 제1 유형의 메모리에 저장된 데이터의 상이한 서브세트들을 나타낸다.

[0058] 본 명세서에서 이전에 설명된 바와 같이, 데이터의 서브세트들 각각은 데이터의 서브세트 각각의 대응하는 어드레스가 메모리 상에서 수행되는 프로그램 동작 중에 액세스된 빈도를 지시하는 제1 유형의 메모리 내의 테이블에 저장된 주파수 데이터와 관련된 주파수(예를 들어, 고온) 데이터를 가질 수 있다. 도 5에 도시된 예에서, 데이터의 서브세트들 각각은 4 개의 가능한 주파수 값들(예를 들어, 00, 01, 10 또는 11) 중 하나와 연관되고, 이는 도 4와 관련하여 이전에 설명된 주파수 데이터(예를 들어, 비트)와 유사하다(예를 들어, 비트 00과 관련된 데이터의 서브세트가 플래시 메모리로부터 SCM으로 재배치되며, 재배치된 후에 어떤 프로그램 동작(들) 동안에도 아직 액세스되지 않고, 비트 01과 관련된 데이터의 서브세트는 프로그램 동작 중에 한번 액세스되었고, 비트 10과 관련된 데이터의 서브세트는 프로그램 동작 중에 두 번 액세스되었고, 비트 11과 관련된 데이터의 서브세트는 프로그램 동작 중에 3 번 이상 액세스되었다). 세트(552-1)는 비트 00과 관련된 데이터의 서브세트를 포함하고, 세트(552-2)는 비트들 01과 관련된 데이터의 서브세트를 포함하고, 세트(552-3)은 비트 10과 관련된 데이터의 서브세트를 포함하며, 세트(552-4)는 비트 11과 관련된 데이터의 서브세트를 포함한다.

[0059] 본 명세서에서 이전에 설명된 바와 같이, 데이터 서브세트(552)는 제1 유형의 메모리의 FIFO 버퍼(558)에서 적어도 부분적으로(예를 들어, 도 3과 관련하여 전술한 테이블 관리자(338-1)에 의해) 구성될 수 있다. 도 5에 도시된 예에서, 제1 유형의 메모리는 4 개의 FIFO 버퍼들(예를 들어, 558-1, 558-2, 558-3 및 558-4)을 포함하며, 버퍼(558-1)에서 조직화된 주파수 비트 00(예를 들어, 세트(552-1)의 데이터의 서브세트)과 연관된 데이터의 서브세트, 버퍼(558-2)에서 조직화된 주파수 비트 01(예를 들어, 세트(552-2)의 데이터의 서브세트)과 연관된 데이터의 서브세트, 버퍼(558-3)에서 조직화된 주파수 비트 10(예를 들어, 세트(552-3)의 데이터의 서브세트)과 연관된 데이터의 서브세트, 및 버퍼(558-4)에 조직된 주파수 비트 11(예를 들어, 세트(552-4)의 데이터의 서브세트)과 연관된 데이터의 서브세트를 갖는다.

[0060] 데이터 서브세트들은 프로그램 동작 동안 얼마나 최근에 액세스되었는지에 따라 각각의 개별 버퍼(558-1, 558-2, 558-3, 및 558-4)에서 조직화될 수 있다. 이와 같이, 각각의 버퍼(558-1, 558-2, 558-3, 및 558-4)의 서브세트의 위치는 프로그램 동작 동안 그 서브세트에 대응하는 어드레스가 액세스된 주파수의 추가 표시를 제공할 수 있다. 또한, 각 개별 버퍼(558)는 데이터(552)의 각각의 서브세트보다 작을 수 있어, 최근에 액세스한 데이터

터만 최근에 액세스한 방법에 따라 구성된다.

[0061] 예를 들어, 데이터의 서브세트가 플래시 메모리로부터 SCM으로 재배치될 때, 도 5에 도시된 바와 같이, 서브세트는 베피(558-1)의 제1(예를 들어, 가장 새로운) 위치에 배치될 수 있다. 다른 데이터 서브세트가 플래시 메모리로부터 SCM으로 재배치될 때, 그 서브세트는 베피(558-1)의 제1 위치에 배치될 수 있고, 도 5에 도시된 바와 같이, 제1 서브세트는 베피(558-1) 내의 다음 위치로 이동될 수 있다. 베피(558-1)가 가득 찰 때까지 데이터의 추가 서브세트가 플래시 메모리로부터 SCM으로 재배치됨에 따라 이 프로세스가 계속될 수 있다(예를 들어, 데이터의 서브세트가 베피(558-1)의 마지막 위치로 이동될 때까지). 이와 같이, 베피(558-1) 내의 서브세트의 위치가 오래될수록 그 서브세트가 액세스되는 빈도가 적어진다. 예를 들어, 베피(558-1) 내의 마지막(예를 들어, 가장 오래된) 위치에 있는 데이터의 서브세트는 베피(558-1)의 데이터 서브세트들 중에서 최소 빈도로 액세스된다.

[0062] 베피(558-1)가 가득 차있는 동안 데이터의 서브세트가 플래시 메모리로부터 SCM으로 재배치될 때, 베피(558-1)로부터 최종 위치에 있는 데이터의 서브세트(예를 들어, 데이터의 가장 오래된 서브세트)를 제거함으로써 그 데이터의 서브세트에 대해 베피(558-1)에서 공간을 만들 수 있고, 도 5에 도시된 바와 같이, 베피(558-1) 내의 각각의 서브세트를 각각 베피(558-1)의 다음 위치로 이동시킨다. 그 다음, 새롭게 재배치된 데이터의 서브세트는 베피(558-1)의 제1(예를 들어, 최신) 위치에 배치될 수 있다. 이 프로세스는, 예를 들어 순환 베피(예를 들어, 베피(558-1)는 순환 베피일 수 있음)를 사용하여 구현될 수 있다. 도 5에 도시된 바와 같이, 세트(552-1)의 서브세트(554-1)는 세트(552-1)에서 베피(558-1)로부터 제거된 데이터의 서브세트를 포함한다.

[0063] 이와 같이, 데이터의 서브세트가 베피(558-1)로부터 제거되었는지 여부는 프로그램 동작 동안 그 서브세트에 대응하는 어드레스가 액세스된 빈도의 추가 표시를 제공할 수 있다. 예를 들어, 데이터의 서브세트가 베피(558-1)로부터 제거되었는지 여부는 데이터의 에이지(age)의 표시를 제공할 수 있어서, 최근에 기록된 데이터와 구형 데이터를 구별할 수 있다. 예를 들어, 베피(558-1)로부터 제거된 데이터의 서브세트(예를 들어, 서브세트(554-1)의 데이터의 서브세트)는 주파수 비트 00과 연관된 데이터의 서브세트 중에서 최소 빈도로 액세스된 데이터의 서브세트다(예를 들어, 세트(552-1)의 데이터의 서브세트). 이와 같이, 베피(558-1)로부터 제거된 하나 이상의 서브세트는 제1 유형의 메모리(예를 들어, SCM)로부터 제2 유형의 메모리(예를 들어, 플래시 메모리)로 재배치하기 위한 데이터의 서브세트(들)로서 식별될 수 있다.

[0064] 예를 들어, 베피(558-1)로부터 제거된 서브세트들의 그룹(예를 들어, 클러스터)은 SCM으로부터 플래시 메모리로 재배치하기 위한 데이터의 서브세트로서 식별될 수 있다. 예를 들어, 도 5에 도시된 예에서, 서브세트(554-1)의 데이터의 서브세트들 중 그룹(556-1)은 재배치될 서브세트로서 식별되었다. 이러한 그룹은 그 크기가 플래시 메모리에 저장된 데이터 페이지의 크기와 동일한 베피(558-1)로부터의 서브세트들의 순차 그룹일 수 있다.

[0065] 도 5에 도시된 바와 같이, 세트(552-1)에서 데이터의 서브세트에 대해 발생하는 제1 프로그램 동작 액세스 시, 데이터 서브세트에 대한 주파수 비트는 00에서 01로 업데이트(예를 들어, 증가)될 수 있고, 데이터의 서브세트는 세트(552-1)에서 세트(552-2)로 이동될 수 있다. 예를 들어, 도 5에 도시된 바와 같이, 데이터의 서브세트는 세트(552-2)의 베피(558-2)의 제1(예를 들어, 가장 새로운) 위치에 배치될 수 있다. 또한, SCM으로의 직접 기록의 일부로서 제1 프로그램 동작 액세스가 발생하는 데이터의 서브세트는 도 5에 도시된 바와 같이, 세트(552-2)의 베피(558-2)의 제1 위치에 배치될 수 있다.

[0066] 다른 데이터 서브세트가 그 제1 프로그램 동작을 겪을 때, 그 서브세트는 베피(558-2)의 제1 위치에 배치될 수 있고, 도 5에 도시된 바와 같이, 제1 서브세트는 베피(558-2)의 다음 위치로 이동될 수 있다. 이 프로세스는 베피(558-2)가 가득 찰 때까지 추가의 데이터 서브세트가 각각의 제1 프로그램 동작을 거치면서 계속될 수 있다. 이와 같이, 베피(558-1)에 대해 설명된 것과 유사한 방식으로, 베피(558-2)의 서브세트의 위치가 나이가 적을수록, 서브세트가 액세스되는 빈도가 적다.

[0067] 베피(558-2)가 가득 차있는 동안 데이터의 서브세트가 그 제1 프로그램 동작을 겪을 때, 베피(558-2)로부터 최종 위치(예를 들어, 데이터의 가장 오래된 서브세트)에있는 데이터의 서브세트를 제거함으로써 그 서브세트에 대한 베피(558-2)에서 공간을 생성할 수 있고, 도 5에 도시된 바와 같이, 베피(558-2) 내의 각각의 서브세트를 베피(558-2)의 각각의 다음 위치로 이동시킨다. 새롭게 프로그래밍된 데이터 서브세트는 베피(558-2)의 제1 위치에 배치될 수 있다. 세트(552-2)의 서브세트(554-2)는 도 5에 도시된 바와 같이 세트(552-2)에서 베피(558-2)로부터 제거된 데이터의 서브세트를 포함한다.

[0068] 이와 같이, 데이터의 서브세트가 베피(558-2)로부터 제거되었는지 여부는 프로그램 동작 동안 그 서브세트에 대

응하는 어드레스가 액세스된 빈도의 추가 표시를 제공할 수 있다. 예를 들어, 베퍼(558-2)로부터 제거된 데이터의 서브세트(예를 들어, 서브세트(554-2)의 데이터의 서브세트)는 주파수 비트 01과 연관된 데이터의 서브세트 중에서 최소 빈도로 액세스된 데이터의 서브세트다(예를 들어, 세트(552-2)의 데이터의 서브세트). 이와 같이, 베퍼(558-2)로부터 제거된 하나 이상의 서브세트는 제1 유형의 메모리(예컨대, SCM)로부터 제2 유형의 메모리(예를 들어, 플래시 메모리)로 재배치하기 위해 데이터의 서브세트(들)로서 식별될 수 있다.

[0069] 예를 들어, 베퍼(558-2)로부터 제거된 서브세트들의 그룹(예를 들어, 클러스터)은 SCM으로부터 플래시 메모리로 재배치하기 위한 데이터의 서브세트로서 식별될 수 있다. 예를 들어, 도 5에 도시된 예에서, 서브세트(554-2)의 데이터의 서브세트들 중 그룹(556-2)은(예를 들어, 서브세트(554-1)의 데이터의 서브세트와 함께) 재배치될 서브세트로서 식별되었다. 그러한 그룹은 그 크기가 플래시 메모리에 저장된 데이터 페이지의 크기와 동일한 베퍼(558-2)로부터의 서브세트들의 순차 그룹일 수 있다.

[0070] 도 5에 도시된 바와 같이, 세트(552-2)에서 데이터의 서브세트에 대해 발생하는 제2 프로그램 동작 액세스 시, 데이터 서브세트에 대한 주파수 비트는 01에서 10으로 업데이트(예를 들어, 증가)될 수 있고, 데이터의 서브세트는 세트(552-2)에서 세트(552-3)로 이동될 수 있다. 예를 들어, 도 5에 도시된 바와 같이, 데이터의 서브세트는 세트(552-3)에서 베퍼(558-3)의 제1 위치에 배치될 수 있다. 다른 데이터 서브세트가 제2 프로그램 동작을 겪을 때, 그 서브세트는 베퍼(558-3)의 제1 위치에 배치될 수 있고, 제1 서브세트는 베퍼(558-3)의 다음 위치로 이동될 수 있고, 이 프로세스는 베퍼(558-1 및 558-2)에 대해 기술된 것과 유사한 방식으로, 베퍼(558-3)가 가득 찰 때까지 추가의 데이터 서브세트가 각각의 제2 프로그램 동작을 거치는 동안 계속될 수 있다.

[0071] 베퍼(558-3)가 가득 차있는 동안 데이터의 서브세트가 제2 프로그램 동작을 겪을 때, 베퍼(558-3)로부터 최종 위치에 있는 데이터의 서브세트를 제거함으로써 그 서브세트에 대한 베퍼(558-3)에서 공간을 만들 수 있고, 도 5에 도시된 바와 같이, 베퍼(558-3) 내의 각각의 서브세트를 각각 베퍼(558-3)의 다음 위치로 이동시킨다. 새롭게 프로그래밍된 데이터 서브세트는 베퍼(558-3)의 제1 위치에 배치될 수 있다. 세트(552-3)의 서브세트(554-3)는 세트(552-3)의 베퍼(558-3)으로부터 제거된 데이터의 서브세트를 포함하고, 도 5에 도시된 바와 같이 서브세트(556-3)의 그룹(예를 들어, 클러스터)을 포함할 수 있다.

[0072] 도 5에 도시된 바와 같이, 베퍼(558-3)로부터 제거된 데이터의 서브세트(예를 들어, 서브세트(554-3)의 데이터의 서브세트)에 대한 주파수 비트는 10에서 01로 주기적으로 업데이트(예를 들어, 감소)될 수 있고, 이러한 데이터 서브세트는 세트(552-3)에서 세트(552-2)로 이동할 수 있다. 예를 들어, 도 5에 도시된 바와 같이, 이들 데이터 서브세트는 세트(552-2)의 서브세트(554-2)에 배치될 수 있다. 주기적인 업데이트는, 예를 들어 메모리상에서 수행되는 미리 정의된 수의 프로그램 연산들에서 발생할 수 있고 및/또는 데이터 서브세트들에 대한 라운드 로빈 스케줄링(round-robin scheduling) 순서로 발생할 수 있다.

[0073] 도 5에 도시된 바와 같이, 세트(552-3)에서 데이터의 서브세트에 대해 발생하는 제3 프로그램 동작 액세스 시, 데이터 서브세트에 대한 주파수 비트는 10에서 11로 업데이트(예를 들어, 증가)될 수 있고, 데이터 서브세트는 세트(552-3)에서 세트(552-4)로 이동될 수 있다. 예를 들어, 도 5에 도시된 바와 같이, 데이터의 서브세트는 세트(552-4)에서 베퍼(558-4)의 제1 위치에 배치될 수 있다. 다른 데이터 서브세트가 제3 프로그램 동작을 겪을 때, 그 서브세트는 베퍼(558-4)의 제1 위치에 배치될 수 있고, 제1 서브세트는 베퍼(558-4) 내의 다음 위치로 이동될 수 있고, 이 프로세스는 베퍼(558-1 및 558-2 및 558-3)에 대해 기술된 것과 유사한 방식으로 베퍼(558-4)가 가득 찰 때까지 추가의 데이터 서브세트가 각각의 제3 프로그램 동작을 거치는 동안 계속될 수 있다.

[0074] 베퍼(558-4)가 가득 찬 동안 데이터의 서브세트가 그의 제3 프로그램 동작을 겪을 때, 베퍼(558-4)로부터 최종 위치에 있는 데이터의 서브세트를 제거함으로써 그 서브세트에 대한 베퍼(558-4)에서 공간을 만들 수 있고, 도 5에 도시된 바와 같이, 베퍼(558-4)의 각각의 서브세트를 각각 베퍼(558-4)의 다음 위치로 이동시킨다. 새롭게 프로그래밍된 데이터 서브세트는 베퍼(558-4)의 제1 위치에 배치될 수 있다. 세트(552-4)의 서브세트(554-4)는 세트(552-4)의 베퍼(558-4)로부터 제거된 데이터의 서브세트를 포함하고, 도 5에 도시된 바와 같이, 서브세트들(556-4)의 그룹(예를 들어, 클러스터)을 포함할 수 있다.

[0075] 도 5에 도시된 바와 같이, 베퍼(558-4)로부터 제거된 데이터의 서브세트(예를 들어, 서브세트(554-4)의 데이터의 서브세트)에 대한 주파수 비트는 11에서 10으로 주기적으로 업데이트(예를 들어, 감소)될 수 있고, 이러한 데이터 서브세트는 세트(552-4)에서 세트(552-3)으로 이동할 수 있다. 예를 들어, 도 5에 도시된 바와 같이, 이들 데이터 서브세트는 세트(552-3)의 서브세트(554-3)에 위치할 수 있다. 주기적 업데이트는 예를 들어 세트(552-3)와 관련하여 설명된 주기적인 업데이트와 동시에 발생할 수 있다(예를 들어, 둘 모두 동일한 주기적인 업데이트의 일부로서 발생할 수 있음). 그러나, 도 5에 도시된 예에서, 이 주기적인 업데이트는 베퍼(558-2 및

는 558-1)로부터 제거된 데이터의 서브세트에 대한 주파수 비트를 업데이트하는 것을 포함하지 않는다(예를 들어, 서브세트들(554-2 또는 554-1)의 데이터의 서브세트들). 즉, 버퍼(558-2 및 558-1)로부터 제거된 데이터의 서브세트에 대한 주파수 비트는 주기적인 업데이트의 일부로서 감소되지 않는다.

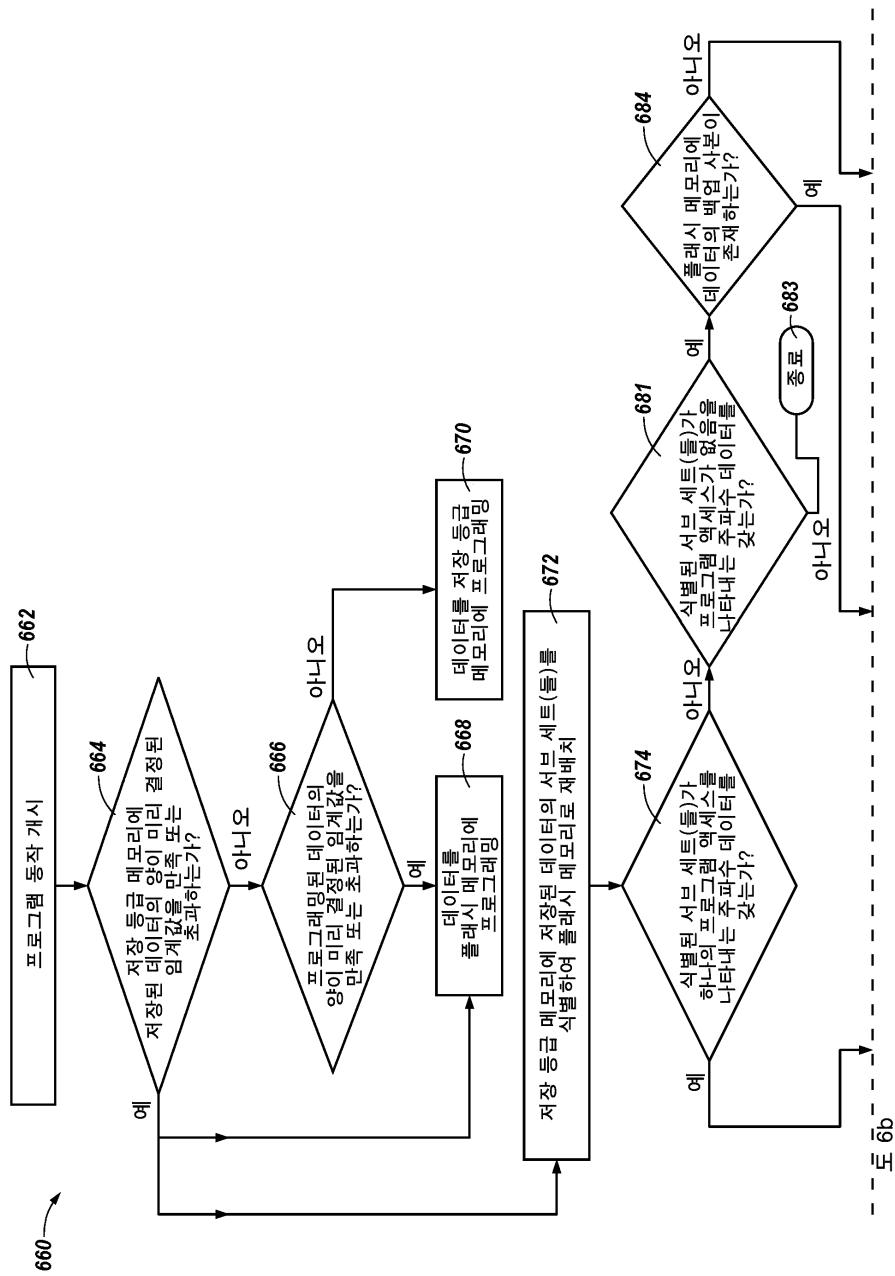

[0076] 도 6a 및 도 6b는 본 개시의 다수의 실시 예들에 따른 예를 들어, 도 2와 관련하여 이전에 기술된 바와 같은 메모리들(210(예를 들어, SCM) 및 212-1, ..., 212-N(예를 들어, 플래시 메모리))과 같은 메모리를 동작시키는 방법(660)을 도시한다. 방법(660)은 예를 들어 각각 도 2 및 도 3과 관련하여 이전에 기술된 제어기(206 및/또는 306)에 의해 수행될 수 있다.

[0077] 블록(662)에서, 방법(660)은 데이터를 메모리에 프로그래밍하는 프로그램 동작을 개시하는 단계를 포함하고, 블록(664)에서, 방법(660)은, 예를 들어 SCM이 가득 찼는지 아니면 거의 가득 찼는지 여부와 같은, SCM에 저장된 데이터의 양이 미리 정의된 임계 값(예를 들어, 메모리의 동작 동안 빈번하게 만족 또는 초과하지 않는 임계 값)을 만족 또는 초과하는지 여부를 결정하는 것을 포함한다.

[0078] SCM에 저장된 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하지 않는 것으로 결정되면, 블록(666)에서, 프로그램 동작 동안 프로그래밍될 데이터의 양이, 예를 들어 4KB, 128KB 또는 512KB와 같은, 미리 결정된 임계 값을 만족 또는 초과하는지 여부가 결정된다. 프로그래밍될 데이터의 양이 이 미리 결정된 임계 값을 만족 또는 초과하는 것으로 결정되면, 블록(668)에서 데이터는 플래시 메모리에 프로그래밍 될 수 있다. 그러나, 프로그래밍될 데이터의 양이 이 미리 정의된 임계 값을 만족 또는 초과하지 않는다고 결정되면, 블록(670)에서 데이터는 SCM에 프로그래밍될 수 있다. 미리 정의된 4KB의 임계 값을 사용하면 SCM에 프로그래밍할 데이터의 양을 최소화 할 수 있으며, 128KB의 미리 정의된 임계 값을 SCM에 프로그래밍된 임의 기록 액세스와 관련된 데이터를 보장할 수 있으며 512KB의 미리 정의된 임계 값을 통해 모든 데이터가 SCM에 프로그래밍되도록 할 수 있다.

[0079] 블록(664)에서, SCM에 저장된 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하는 것으로 결정되면, 프로그램 동작 동안 프로그래밍될 데이터는 블록(668)에서 플래시 메모리에 프로그래밍되고, 방법(660)은 블록(672)으로 진행한다. 블록(672)에서, 방법(660)은 SCM에 저장된 데이터(예를 들어, LMU(들))의 서브세트 또는 서브세트들을 식별하여 플래시 메모리로 재배치(예를 들어, 이동)한다. 서브세트(들)는 이전에 설명된 바와 같이 SCM에 저장된 데이터의 서브세트(들)에 대응하는 어드레스(들)(예를 들어, LBA(들))가 메모리 상에서 수행된 이전 프로그램 동작들 동안 액세스된 빈도에 적어도 부분적으로 기초하여 식별될 수 있다. 예를 들어, 식별된 서브세트(들)는 전술한 바와 같이 액세스되지 않았거나 및/또는 한번 액세스된 서브세트를 포함 할 수 있다.

[0080] 블록(674)에서, 방법(660)은 식별된 서브세트(들)가 그와 연관된(예를 들어, 도 4 및 도 5와 관련하여 이전에 기술된 주파수 데이터 01), 식별된 서브세트(들)가 이전 프로그램 동작들 동안 한번 액세스되었음을 지시하는, 주파수 데이터를 갖는지 여부를 결정하는 단계를 포함한다. 식별된 서브세트(들)가 이전의 프로그램 동작 중에 한번 액세스되었음을 나타내는 그것과 관련된 주파수 데이터를 갖는 것으로 결정되면, 식별된 서브세트(들)에 저장된 데이터는 블록(676)에서 감지될 수 있고, 이 감지된 데이터는 블록(678)에서 플래시 메모리에 프로그래밍될 수 있고, SCM의 테이블에 저장된 식별된 서브세트(들)에 대한 위치(예를 들어, 레지던시) 데이터는(전술한 바와 같이) 블록(680)에서 감지된 데이터가 프로그래밍되는 플래시 메모리 내의 위치로 업데이트될 수 있고, 블록(682)에서 SCM 내의 식별된 서브세트(들)에 저장된 데이터는 무효화될 수 있다. 식별된 서브세트(들)가 그와 연관된 식별된 서브세트(들)가 이전 프로그램 동작 동안 한번 액세스되었음을 나타내는 주파수 데이터를 가지지 않는다고 결정되면, 방법(660)은 블록(681)으로 진행한다.

[0081] 블록(681)에서, 방법(660)은 식별된 서브세트(들)가 이전 프로그램 동작들 동안 액세스되지 않았음을 나타내는 식별된 서브세트(들)가 주파수 데이터(예를 들어, 도 4 및 도 5와 관련하여 앞서 설명된 주파수 데이터 00)와 연관된 주파수 데이터를 갖는지 여부를 결정하는 단계를 포함한다. 식별된 서브세트(들)가 이전의 프로그램 동작들 동안 액세스되지 않았음을 나타내는 주파수 데이터와 연관된 주파수 데이터를 가지지 않는다고 결정되면, 방법(660)은 블록(683)에서 종료한다. 식별된 서브세트(들)가 이전의 프로그램 동작 중에 액세스되지 않았음을 나타내는 주파수 데이터와 관련된 주파수 데이터를 갖는 것으로 결정되면, 방법(660)은 블록(684)으로 진행한다.

[0082] 블록(684)에서, 방법(660)은 플래시 메모리에 저장된 식별된 서브세트(들)에 데이터의 백업 사본이 존재 하는지를 결정하는 단계를 포함한다. 플래시 메모리에 저장된 데이터의 백업 사본이 있는 경우, 블록(686)에서 데이터의 백업 사본이 플래시 메모리에 저장되는 위치가 검색될 수 있고, 식별된 서브세트(들)에 대한 위치 데이터는 블록(688)에서 검색된 위치로 업데이트될 수 있고, SCM에서 식별된 서브세트(들)에 저장된 데이터는 블록(690)에서 무효화될 수 있다. 플래시 메모리에 저장된 데이터의 백업 사본이 없는 경우, 식별된 서브세트(들)에 저장

된 데이터는 블록(692)에서 감지될 수 있고, 이 감지된 데이터는 블록(694)에서 플래시 메모리에 프로그래밍될 수 있고, SCM에서 테이블에 저장된 식별된 서브세트(들)에 대한 위치 데이터(예를 들어, 레지던시)는 블록(696)에서 감지된 데이터가 프로그래밍되는 플래시 메모리 내의 위치로 업데이트될 수 있고(전술한 바와 같이), SCM에서 식별된 서브세트(들)에 저장된 데이터는 블록(698)에서 무효화될 수 있다.

[0083] 도 7은 본 개시의 다수의 실시 예들에 따른 예를 들어, 도 2와 관련하여 이전에 기술된 메모리(210(예컨대, SCM) 및 212-1, ..., 212-N(예를 들어, 플래시 메모리))와 같은 메모리를 동작시키는 방법(761)을 예시한다. 방법(761)은 예를 들어 도 2 및 도 3과 관련하여 이전에 기술된 제어기(206 및 / 또는 306)에 의해 각각 수행될 수 있다.

[0084] 블록(763)에서, 방법(761)은 메모리에 저장된 데이터를 감지하기 위한 감지 동작을 개시하는 단계를 포함하고, 블록(765)에서, 방법(761)은 감지 동작 동안 감지될 데이터가 플래시 메모리에 저장되는지 여부를 결정하는 단계를 포함한다. 이 결정은 예를 들어, 전술한 바와 같이, SCM의 테이블에 저장된 위치(예를 들면, 레지던시) 데이터를 사용하여 행해질 수 있다. 감지될 데이터가 플래시 메모리에 저장되어 있지 않다고 결정되면, 데이터는 블록(767)에서 SCM으로부터 감지될 수 있다. 감지될 데이터가 플래시 메모리에 저장되어 있다고 결정되면, 블록(769)에서 플래시 메모리로부터 데이터가 감지될 수 있고, 방법(761)은 블록(771)으로 진행한다.

[0085] 블록(771)에서, 방법(761)은 SCM에 저장된 데이터의 양이 미리 정의된 임계 값을 만족 또는 초과하는지 여부를 결정하는 것을 포함한다. 이 임계 값은, 예를 들어 도 6a의 블록(664)에서 사용된 것과 동일한 임계 값일 수 있다. SCM에 저장된 데이터의 양이 소정의 임계 값을 만족 또는 초과하는 것으로 결정되면, 방법(761)은 블록(773)에서 종료한다. SCM에 저장된 데이터의 양이 소정의 임계 값을 만족 또는 초과하지 않는다고 결정되면, 방법(761)은 블록(775)으로 진행한다.

[0086] 블록(775)에서, 방법(761)은 감지 동작 동안 플래시 메모리로부터 감지된 데이터의 양이 예를 들어, 4 KB 또는 512 KB와 같은 특정 임계 값을 만족 또는 초과하는지를 결정하는 단계를 포함한다. 임계 값이 4KB이면 감지된 데이터의 양이 SCM으로 재배치되는 것을 보장할 수 있으며 임계 값이 512KB이면 모든 감지된 데이터가 SCM으로 재배치될 수 있다. 감지 동작 동안 감지된 데이터의 양이 특정 임계 값을 만족 또는 초과하는 것으로 결정되면, 방법(761)은 블록(777)에서 종료한다. 감지 동작 동안 감지된 데이터의 양이 특정 임계 값을 만족 또는 초과하지 않는 것으로 결정되면, 방법(761)은 블록(779)으로 진행한다.

[0087] 블록(779)에서, 방법(761)은 감지 동작 동안 감지된 데이터의 백업 사본이 필요한지를 결정하는 단계를 포함한다. 이 결정은 예를 들어 구성 비트 검사일 수 있다. 감지된 데이터의 백업 사본이 필요하지 않은 것으로 결정되면, 감지된 데이터는 블록(781)에서 SCM에 프로그래밍되고, 데이터 서브세트에 대한 위치 데이터는 블록(783)에서 감지된 데이터가 프로그래밍되는 SCM 내의 위치로 업데이트될 수 있고, 플래시 메모리에 저장된 원래의 데이터는 블록(785)에서 무효화될 수 있다. 감지된 데이터의 백업 사본이 필요하다고 결정되면, 감지된 데이터는 블록(787)에서 SCM에 프로그래밍되고, 데이터 서브세트에 대한 위치 데이터는 블록(789)에서 감지된 데이터가 프로그래밍되는 SCM 내의 위치로 업데이트될 수 있다.

[0088] 특정 실시 예들이 본 명세서에 도시되고 설명되었지만, 당업자라면 동일한 결과를 얻기 위해 계산된 배열이 도시된 특정 실시 예를 대체할 수 있다는 것을 이해할 것이다. 이 개시는 본 개시의 다수의 실시 예들의 적용 또는 변형을 포함하도록 의도된다. 상기 설명은 예시적인 방식으로 이루어졌으며 제한적인 것이 아님을 이해해야 한다. 상기 실시 예들 및 여기에 구체적으로 기술되지 않은 다른 실시 예들의 조합은 상기 설명을 검토할 때 당업자에게 명백할 것이다. 본 개시의 다수의 실시 예들의 범위는 상기 구조 및 방법이 사용되는 다른 어플리케이션을 포함한다. 따라서, 본 개시의 다수의 실시 예들의 범위는 첨부된 청구 범위를 참조하여, 그러한 청구 범위가 부여되는 균등률의 전체 범위와 함께 결정되어야 한다.

[0089] 전술한 상세한 설명에서, 일부 특징들은 본 발명을 능률화할 목적으로 단일 실시 예에서 함께 그룹화된다. 본 개시의 방법은 본 개시의 실시 예가 각 청구항에 명시적으로 언급된 것보다 많은 특징을 이용해야 한다는 의도를 반영하는 것으로 해석되어서는 안 된다. 오히려, 이하의 청구 범위가 반영하는 바와 같이, 발명의 주제는 단일 개시된 실시 예의 모든 특징보다 적다. 따라서, 이하의 청구 범위는 발명의 상세한 설명에 포함되며, 각 청구항은 별개의 실시 예로서 독자적으로 기재된다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6a

### 도면6b

## 도면7