(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-212509

(P2009-212509A)

(43) 公開日 平成21年9月17日(2009.9.17)

| (51) Int.Cl.          | F 1                   | テーマコード (参考) |

|-----------------------|-----------------------|-------------|

| HO1L 21/316 (2006.01) | HO1L 21/316 X 5F058   |             |

| HO1L 21/336 (2006.01) | HO1L 29/78 617V 5F110 |             |

| HO1L 29/786 (2006.01) | HO1L 29/78 617T       |             |

| HO1L 21/02 (2006.01)  | HO1L 27/12 B          |             |

| HO1L 27/12 (2006.01)  | HO1L 21/316 P         |             |

審査請求 未請求 請求項の数 10 O L (全 36 頁)

|              |                            |          |                                 |

|--------------|----------------------------|----------|---------------------------------|

| (21) 出願番号    | 特願2009-26277 (P2009-26277) | (71) 出願人 | 000153878                       |

| (22) 出願日     | 平成21年2月6日 (2009.2.6)       |          | 株式会社半導体エネルギー研究所                 |

| (31) 優先権主張番号 | 特願2008-29086 (P2008-29086) |          | 神奈川県厚木市長谷398番地                  |

| (32) 優先日     | 平成20年2月8日 (2008.2.8)       | (72) 発明者 | 一條 充弘                           |

| (33) 優先権主張国  | 日本国 (JP)                   |          | 神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内 |

|              |                            | (72) 発明者 | 岡崎 健一                           |

|              |                            |          | 栃木県下都賀郡都賀町大字升塚161-2             |

|              |                            |          | アドバンスト フィルム ディバイス               |

|              |                            |          | インク株式会社内                        |

|              |                            | (72) 発明者 | 田中 哲弘                           |

|              |                            |          | 栃木県下都賀郡都賀町大字升塚161-2             |

|              |                            |          | アドバンスト フィルム ディバイス               |

|              |                            |          | インク株式会社内                        |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【要約】

【課題】半導体集積回路に用いる絶縁膜として、膜厚が薄くとも信頼性を確保することができる絶縁膜の作製方法を提供することを課題とする。特に、ガラス等の大面積化が可能な絶縁表面を有する基板上に低い基板温度で高品質の絶縁膜を提供することを課題とする。

【解決手段】チャンバーにモノシランガス (SiH<sub>4</sub>) と亜酸化窒素 (N<sub>2</sub>O) と希ガスを導入し、10Pa～30Paの圧力下で高密度プラズマを発生させてガラス等の絶縁表面を有する基板上に絶縁膜を形成する。その後、モノシランガスの供給を停止し、大気に曝すことなく亜酸化窒素 (N<sub>2</sub>O) と希ガスとを導入して絶縁膜表面にプラズマ処理を行う。

【選択図】図 1

**【特許請求の範囲】****【請求項 1】**

絶縁表面を有する基板上に、モノシランガス及び亜酸化窒素を材料ガスとして絶縁膜を形成し、該絶縁膜に亜酸化窒素のプラズマ処理を行う半導体装置の作製方法。

**【請求項 2】**

絶縁表面を有する基板上に、半導体層を形成し、

モノシランガス及び亜酸化窒素を材料ガスとして前記半導体層を覆う絶縁膜を形成し、該絶縁膜に亜酸化窒素のプラズマ処理を行い、

前記絶縁膜を介して前記半導体層に一導電型を付与する不純物元素を添加し、

前記絶縁膜上に金属電極を形成し、

前記一導電型を付与する不純物元素が添加された半導体層及び金属電極を一対の電極とし、

前記絶縁膜を誘電体とする容量素子を有する半導体装置の作製方法。

10

**【請求項 3】**

請求項 2 において、前記半導体層の形成は、前記絶縁表面を有する基板上に成膜された非晶質半導体膜に対してレーザ光を照射する半導体装置の作製方法。

**【請求項 4】**

請求項 2 において、前記半導体層の形成は、半導体基板から分離させた半導体層を前記絶縁表面を有する基板上に固定した後、選択的にエッチングして前記半導体層を形成する半導体装置の作製方法。

20

**【請求項 5】**

請求項 2 乃至 4 のいずれか一において、前記一導電型を付与する不純物元素はボロンである半導体装置の作製方法。

**【請求項 6】**

請求項 2 乃至 4 のいずれか一において、前記一導電型を付与する不純物元素はリンである半導体装置の作製方法。

**【請求項 7】**

絶縁表面を有する基板上に、第 1 の半導体層及び第 2 の半導体層を形成し、

モノシランガス及び亜酸化窒素を材料ガスとして前記第 1 の半導体層及び前記第 2 の半導体層を覆う絶縁膜を形成し、該絶縁膜に亜酸化窒素のプラズマ処理を行い、

前記絶縁膜を介して前記第 1 の半導体層に一導電型を付与する不純物元素を添加し、

前記第 1 の半導体層と重なる絶縁膜上に金属電極と、前記第 2 の半導体層と重なる絶縁膜上にゲート電極とを形成し、

前記金属電極およびゲート電極を覆う層間絶縁膜を形成し、

前記層間絶縁膜上に前記第 2 の半導体層と電気的に接続するソース電極及びドレイン電極を形成する半導体装置の作製方法。

30

**【請求項 8】**

請求項 7 において、前記第 1 の半導体層及び前記第 2 の半導体層の形成は、前記絶縁表面を有する基板上に成膜された非晶質半導体膜に対してレーザ光を照射する半導体装置の作製方法。

**【請求項 9】**

請求項 7 において、前記第 1 の半導体層及び前記第 2 の半導体層の形成は、半導体基板から分離させた半導体層を前記絶縁表面を有する基板上に固定した後、選択的にエッチングして前記第 1 の半導体層及び前記第 2 の半導体層を形成する半導体装置の作製方法。

40

**【請求項 10】**

請求項 7 乃至 9 のいずれか一において、前記第 1 の半導体層と、前記絶縁膜と、前記金属電極は、少なくとも一部が重なっており、重なっている部分は容量素子を形成する半導体装置の作製方法。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

50

薄膜トランジスタ（以下、TFTという）で構成された回路を有する半導体装置およびその作製方法に関する。例えば、液晶表示パネルに代表される電気光学装置や、有機発光素子を有する発光表示装置や、アンテナを搭載する無線チップや、受光素子などを部品として搭載した電子機器に関する。

#### 【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

#### 【背景技術】

#### 【0003】

近年、絶縁表面を有する基板上に形成された半導体薄膜（厚さ数～数百nm程度）を用いて薄膜トランジスタ（TFT）を構成する技術が注目されている。今後、薄膜トランジスタはICや電気光学装置のような電子デバイスに広く応用されることが予想され、半導体装置の小型化または高性能化の要求に伴い、より微細な構造を有する薄膜トランジスタの開発が求められている。10

#### 【0004】

微細な構造を有する薄膜トランジスタを作製するためには、ゲート電極やソース配線またはドレイン配線等の導電膜だけでなく、ゲート絶縁膜で代表される絶縁膜の薄膜化が望まれる。

#### 【0005】

薄膜トランジスタを組み込んだ集積回路を電子機器に搭載する場合、例えば液晶パネルの画素部においては液晶のモードにもよるが5V～10Vの駆動電圧が用いられるため、画素部に配置される薄膜トランジスタには5V～10Vの駆動電圧で動作するに適した構造とすることが望ましいとされている。20

#### 【0006】

さらに、液晶表示装置の低電力化を図る一つの方法として、駆動電圧を小さくすることが挙げられる。低電圧動作でも薄膜トランジスタの駆動能力が低下しないように薄膜トランジスタのゲート絶縁膜を薄くすることが挙げられる。

#### 【0007】

膜厚の薄いゲート絶縁膜の作製方法として、熱酸化法による酸化膜形成方法を挙げることができると、熱酸化は高温の加熱処理であるため、基板としてガラス基板を用いる場合には、熱酸化の際の加熱温度は、ガラス基板の融点を超えててしまう。また、熱酸化は、半導体層の一部を酸化させるため、半導体層の薄膜化に繋がってしまい、半導体層が非常に薄い場合には、半導体層が消失する恐れがある。30

#### 【0008】

薄膜トランジスタのゲート絶縁膜を薄くすると、スイッチングに必要な電圧を小さくすることができる一方、薄膜トランジスタの耐圧が低下する恐れがあった。

#### 【0009】

従って、薄膜トランジスタの信頼性を確保するためには、ゲート絶縁膜の厚さをある程度大きく確保することが必要であった。従来の集積回路を搭載する電気機器は、信頼性が最優先されるため、ある程度厚いゲート絶縁膜を用いている。40

#### 【0010】

液晶表示装置に限らず、有機発光素子を有する発光表示装置や、アンテナを搭載する無線チップや、受光素子においても信頼性を確保するためにゲート絶縁膜等の絶縁膜の厚さをある程度大きく確保することが必要であるという同様の問題があった。

#### 【0011】

ガラス等の絶縁表面を有する基板上に形成された半導体膜または絶縁膜に対して高周波を用いたプラズマ処理を行うことによって緻密な絶縁膜を形成する方法が特許文献1に開示されている。

#### 【0012】

また、アクティブマトリクス表示装置において、回路の集積度を高めるため、絶縁膜を誘

電体として半導体薄膜と容量線とで構成し、キャパシタの半導体薄膜が、画素電極に接続されている薄膜トランジスタのチャネル形成領域と同じ半導体薄膜であるキャパシタが特許文献2に開示されている。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2006-332634

【特許文献2】特開平11-121763

【発明の概要】

【発明が解決しようとする課題】

10

【0014】

トランジスタやキャパシタなどの半導体素子に用いる絶縁膜に対する高耐圧化の要求は高まるばかりで、さらなる膜特性の向上が求められている。例えば、トランジスタのゲート絶縁膜を薄くすると、耐圧が低下し、ゲート絶縁膜の絶縁破壊をまねく恐れがある。

【0015】

また、キャパシタにおいても、誘電体となる絶縁膜を薄くすると狭い電極面積で高い容量値を確保できる一方、電圧を印加することによってリーク電流が大きく流れ、キャパシタそのものが破壊されて機能しなくなる恐れがある。

【0016】

このように、トランジスタやキャパシタなどの半導体素子に用いられている絶縁膜は薄膜化し、且つ、高い信頼性を実現することが望まれている。

20

【0017】

従来の平行平板型のプラズマ処理装置やスパッタ装置を用いて薄い膜厚で形成した絶縁膜は、膜の内部に欠陥を有し、膜質が十分でないため、リーク電流の増大や、短絡等の恐れがある。

【0018】

半導体集積回路に用いる絶縁膜として、膜厚が薄くとも信頼性を確保することができる絶縁膜の作製方法を提供することを課題の一とする。特に、ガラス等の大面積化が可能な絶縁表面を有する基板上に低い基板温度で高品質の絶縁膜を提供することを課題の一とする。

30

【0019】

また、誘電体となる絶縁膜が薄いキャパシタと薄膜トランジスタとを同一ガラス基板上有する半導体装置を提供する。

【課題を解決するための手段】

【0020】

チャンバーに材料ガスとしてモノシリコンガス( $\text{SiH}_4$ )と亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスを導入し、10Pa～30Paの圧力下で高密度プラズマを発生させてガラス等の絶縁表面を有する基板上に絶縁膜を形成する。その後、モノシリコンガスの供給を停止し、大気に曝すことなく亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスとを導入して絶縁膜表面にプラズマ処理を行う。少なくとも亜酸化窒素( $\text{N}_2\text{O}$ )と希ガスとを導入して絶縁膜表面に行われるプラズマ処理は、絶縁膜の成膜より後に行う。上記プロセス順序を経た絶縁膜は、膜厚が薄く、例えば100nm未満であっても信頼性を確保することができる絶縁膜である。

40

【0021】

絶縁膜の形成は、高密度プラズマ装置により行う。ここでは、高密度プラズマ装置は、 $1 \times 10^{11} / \text{cm}^3$ 以上のプラズマ密度を達成できる装置を指している。例えば、3kW～6kWのマイクロ波電力を印加してプラズマを発生させて、絶縁膜の成膜を行う。

【0022】

絶縁膜の形成の際、チャンバーに導入するモノシリコンガス( $\text{SiH}_4$ )と亜酸化窒素( $\text{N}_2\text{O}$ )との流量比は、1:10から1:200の範囲とする。また、チャンバーに導入する希ガスとしては、ヘリウム、アルゴン、クリプトン、キセノンなどを用いることができる。

50

るが、中でも安価であるアルゴンを用いることが好ましい。

【0023】

また、高密度プラズマ装置により得られた絶縁膜は、一定した厚さの膜形成ができるため段差被覆性に優れている。また、高密度プラズマ装置により得られる絶縁膜は、薄い膜の厚みを精密に制御することができる。

【0024】

上記プロセス順序を経た絶縁膜は、従来の平行平板型のプラズマCVD装置で得られる絶縁膜とは大きく異なっており、同じエッチャントを用いてエッチング速度を比較した場合において、従来の平行平板型のプラズマCVD装置で得られる絶縁膜の10%以上または20%以上遅く、上記作製方法で得られる絶縁膜は緻密な膜と言える。

10

【0025】

また、ガラス等の絶縁表面を有する基板上に半導体膜を形成し、該半導体膜上に高密度プラズマ装置により絶縁膜を形成した後、大気に曝すことなく亜酸化窒素(N<sub>2</sub>O)と希ガスとを導入して絶縁膜表面にプラズマ処理を行う。その後、絶縁膜を介して半導体膜に一導電型を付与する不純物元素を添加する。その後、絶縁膜上に金属電極を形成して容量素子を形成する。

【0026】

一導電型を付与する不純物元素はp型の不純物元素であるボロンを用いる。ボロンは、原子半径が小さいため、絶縁膜にほとんどダメージを与えることなく絶縁膜を通過させて半導体膜に添加させることができる。従って、得られる容量素子は、絶縁膜が薄い膜厚であっても高い耐圧を実現することができる。

20

【0027】

また、上記方法によって得られる半導体装置も特徴を有しており、その構成は、同一基板上に薄膜トランジスタと容量とを有し、容量は、絶縁膜を誘電体とし、金属電極と、半導体に一導電型を付与する不純物元素を含む半導体層とを一対の電極として有し、容量の絶縁膜は、薄膜トランジスタのゲート絶縁膜とほぼ同じ膜厚であることを特徴とする半導体装置である。

【0028】

例えば、得られた絶縁膜を液晶表示装置のスイッチング素子である薄膜トランジスタのゲート絶縁膜として用いることによって、ゲート絶縁膜の膜厚が30nmであっても、信頼性を確保することができる。さらに得られた絶縁膜を誘電体とし、一対の電極の一方を導電型が付与された半導体膜とし、液晶表示装置の保持容量として用いた場合であっても、信頼性を確保することができる。液晶表示装置の1画素あたりの保持容量は、例えば、約2pF～約5pFであり、ゲート絶縁膜の膜厚を薄く、且つ品質を向上させることで、容量値を増大することができるために保持容量が占める電極面積を縮小することができ、開口率の向上を図ることができる。発光表示装置においても、1画素あたりの保持容量が必要であり、例えば、約0.2pF～約0.5pFであるが、同様にゲート絶縁膜の膜厚を薄く、且つ品質を向上させることで、容量値を増大するするために保持容量が占める電極面積を縮小することができ、開口率の向上を図ることができる。

30

【0029】

また、フォトダイオードを有するフォトICの增幅回路に用いられる薄膜トランジスタのゲート絶縁膜として用いることによって、ゲート絶縁膜の膜厚が20nmであっても、信頼性を確保することができる。ゲート絶縁膜の膜厚を薄くすることで薄膜トランジスタのしきい値のバラツキが抑えられ、フォトICの消費電力の低減に寄与することができる。

40

【0030】

また、得られた絶縁膜を誘電体とし、一対の電極の一方を導電型が付与された半導体層とし、薄膜トランジスタを有する無線チップの保持容量部として用いることによって、絶縁膜の膜厚が10nmであっても、信頼性を確保することができる。薄膜トランジスタを有する無線チップは、主に、電源回路、制御回路、記憶回路、共振容量部とを有している。電源回路は、アンテナが受信した交流信号を整流後に平滑化を行い直流電圧を発生させる

50

。また、電源回路は、交流信号を整流後に平滑化を行い電荷を保持するための保持容量部と呼ばれる容量素子を有している。この容量素子は、一対の電極で挟まれた絶縁膜を誘電体としている。また、無線チップには共振容量部等にも別の容量素子が設けられる。これらの容量素子の静電容量が十分でない場合、通信距離の低下や無線チップの非動作を招く恐れがある。容量素子の面積を大きくすれば、十分な静電容量を得ることができるが、無線チップにおいては、結果として集積回路の占める面積サイズが大きくなってしまい、サイズの拡大により消費電力の増大を招く恐れもある。アンテナから得られる電力は限られているため、無線チップにとって消費電力の増大は、通信距離の短縮に繋がる恐れがあるため、大きな問題となる。また、静電容量は、面積だけでなく、絶縁膜の誘電率や膜厚が影響する。従って、絶縁膜の膜厚を 10 nm として静電容量の増大を図ることができる。例えば、UHF 帯の無線信号を送受信する場合、交流信号を整流後に平滑化を行い電荷を保持するための保持容量部と呼ばれる容量素子の合計容量値は、1 nF (1000 pF) を超える。

10

#### 【0031】

さらに無線チップに搭載する薄膜トランジスタのゲート絶縁膜の膜厚を薄くすることで薄膜トランジスタのしきい値のバラツキが抑えられ、無線チップの動作電圧及び消費電力の低減を図ることができ、その結果、無線チップの通信距離の延長を実現することができる。

20

#### 【0032】

大量生産をする上で大面積ガラス基板等の絶縁表面を有する基板上に無線チップを作製することは製造コスト上、有利である。一方、薄膜トランジスタを有する無線チップは、送受信するための回路をガラス等の絶縁表面を有する基板上に形成する場合、薄膜トランジスタなどを用いて回路を構成すると、デザインルールが微細で 3 次元に回路を積層できる単結晶シリコンチップに比べ、回路の占める面積が大きくなる短所がある。従って、絶縁膜の膜厚を薄くすることで集積回路の占める面積サイズを縮小でき、且つ、消費電力の低減を図ることができるため、薄膜トランジスタを有する無線チップにおいて特に有効である。

20

#### 【0033】

上述したこれらの手段は単なる設計事項ではなく、高密度プラズマ装置を用いて絶縁膜を形成し、その絶縁膜を用いた薄膜トランジスタやキャパシタを含む半導体装置を作製し、その半導体装置の信頼性試験を繰り返し行い、発明者らの深い検討の後、発明された事項である。

30

#### 【0034】

本明細書において、上、下、側、水平、垂直等の方向を表す文言は、基板表面の上にデバイスを配置した場合の基板面を基準とする方向を指す。

30

#### 【0035】

また、本明細書において使用した程度を表す用語、例えば「ほぼ」、「約」などは、最終結果が顕著には変化しないように幾分変更された用語の合理的な逸脱の程度を意味する。これらの用語は、幾分変更された用語の少なくとも  $\pm 5\%$  の逸脱を含むものとして解釈されるべきであるが、この逸脱が幾分変更される用語の意味を否定しないことを条件とする。

40

#### 【発明の効果】

#### 【0036】

高密度プラズマ装置を用いてガラス等の絶縁表面を有する基板上に低い基板温度で得られる絶縁膜は、窒素を含む酸化珪素膜であり、平行平板型のプラズマ CVD 装置で得られる膜よりも緻密な薄膜が得られる。また、ガラス等の絶縁表面を有する同一基板上に低い基板温度で得られる高品質の絶縁膜を誘電体とするキャパシタと、高品質の絶縁膜をゲート絶縁膜とする薄膜トランジスタとを有する半導体装置を実現できる。

#### 【図面の簡単な説明】

#### 【0037】

50

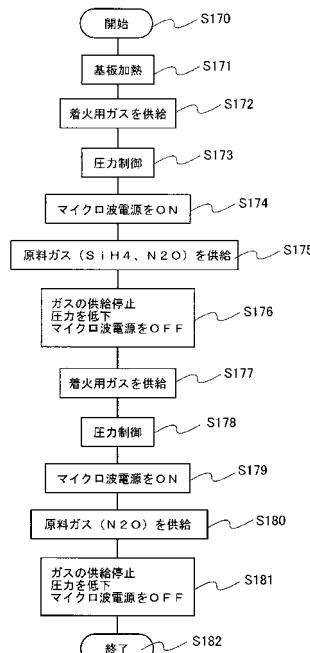

- 【図1】作製フローを示す図。

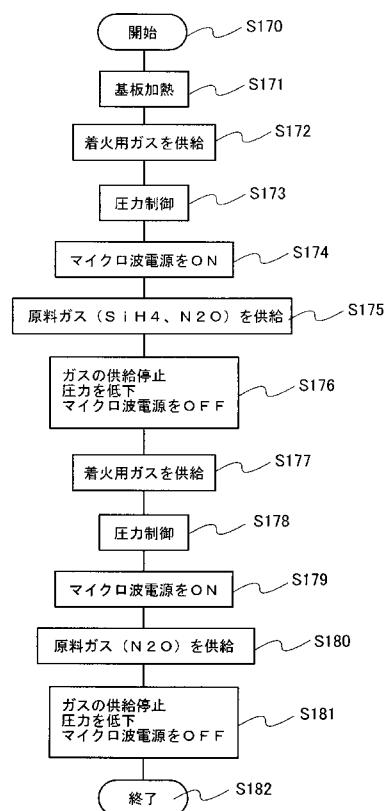

- 【図2】高密度プラズマ装置の上面図を示す図。

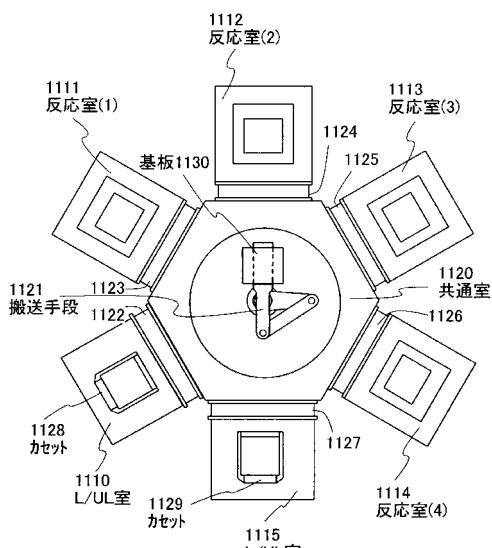

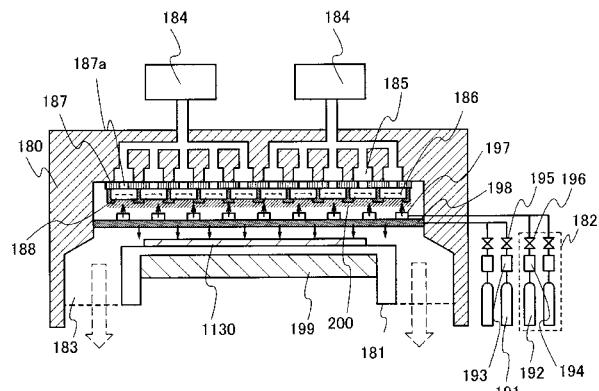

- 【図3】高密度プラズマ装置の断面図を示す図。

- 【図4】信頼性試験の結果を示すグラフ。

- 【図5】I-V特性を示すグラフ。

- 【図6】圧力依存性を示すグラフ。

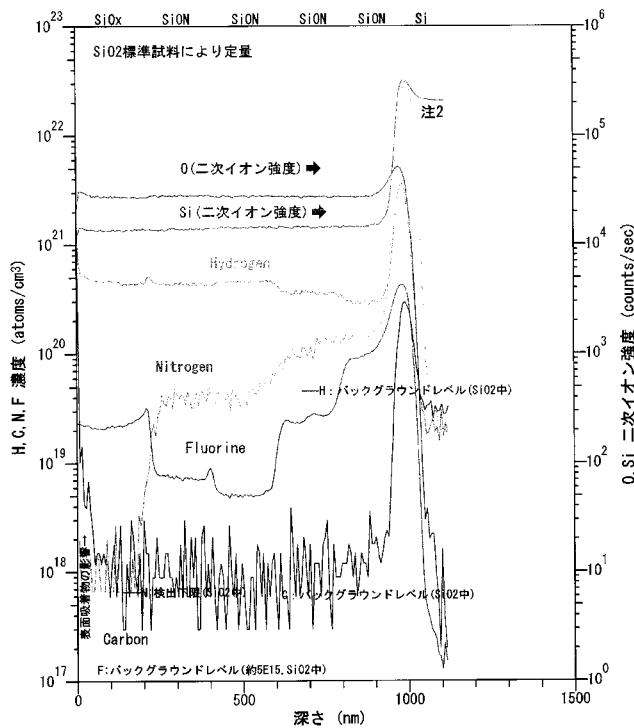

- 【図7】SIMS分析結果を示す図。

- 【図8】無線チップの作製工程図。

- 【図9】無線チップの作製工程図。

- 【図10】無線チップの作製工程図。

- 【図11】液晶表示装置の上面図及び断面図。

- 【図12】発光表示装置の作製工程図。

- 【図13】発光表示装置の作製工程図。

- 【図14】光電変換装置の断面図。

- 【図15】無線チップの作製工程図。

- 【図16】電子機器の一例を示す図。

- 【発明を実施するための形態】

- 【0038】

- 実施の形態について、以下に説明する。

- 【0039】

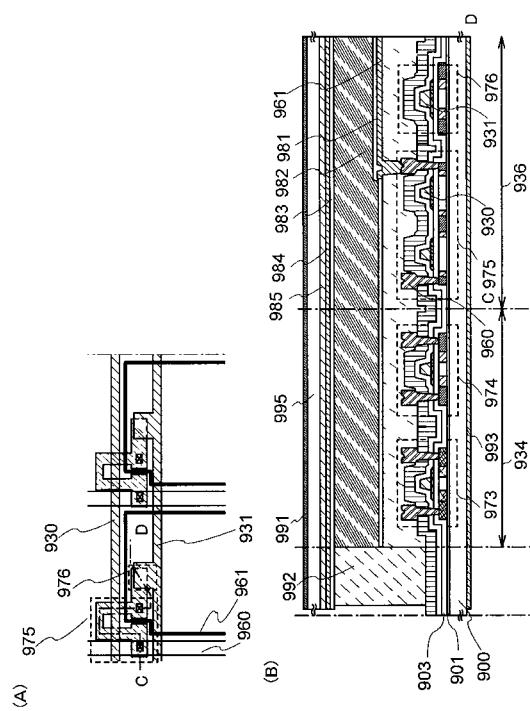

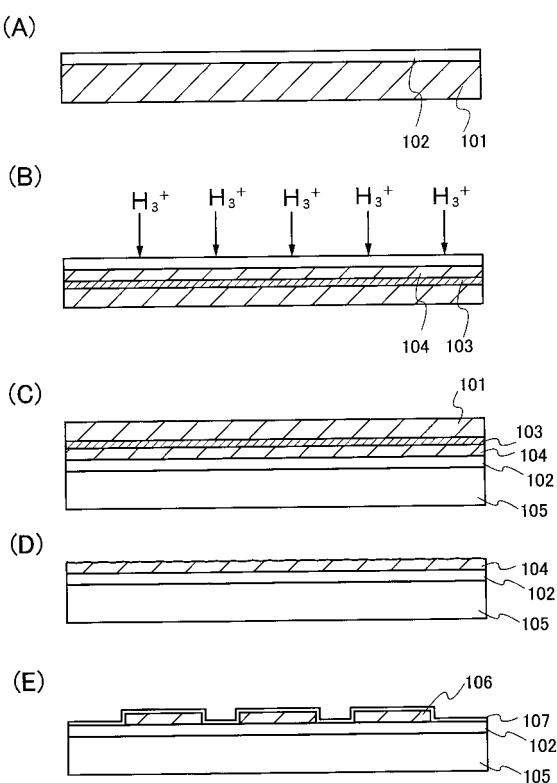

- ガラス等の絶縁表面を有する基板上に半導体層を覆う薄い絶縁膜を形成する作製手順フローを図1に示す。

- 【0040】

- 半導体層が設けられたガラス基板を高密度プラズマ装置（周波数が1GHz以上、ここでは2.45GHzのマイクロ波プラズマCVD装置）の処理容器内に搬送する。

- 【0041】

- ここで、高密度プラズマ装置の一例の上面図を図2に示す。共通室1120は、ロード・アンロード（L/UL）室1110、1115、及び反応室（1）～反応室（4）1111～1114とゲート弁1122～1127を介して連結されている。基板1130は、ロード・アンロード（L/UL）室1110、1115のカセット1128、1129に装填され、共通室1120の搬送手段1121により各反応室に搬送される。

- 【0042】

- なお、図2に示す高密度プラズマCVD装置には、ロード・アンロード（L/UL）室が複数設けられているが、一つでもよい。また、高密度プラズマCVD装置に予備室を設けてもよい。予備室で基板を予備加熱することで、各反応室において成膜までの加熱時間を短縮することができるため、スループットを向上させることができる。

- 【0043】

- 図3は、このような高密度プラズマCVD装置の一つの反応室の構成の一例を詳細に説明するものである。図3は断面図であり、一つの反応室には、処理容器180、処理容器180内に設けられ基板1130を配置するための支持台181、処理容器180内にガスを導入するためのガス供給部182、処理容器180内のガスを排気するために真空ポンプに接続する排気口183、プラズマ発生用のマイクロ波を供給するマイクロ波発生装置184、マイクロ波供給部からマイクロ波を処理容器180に導入する導波管185、導波管185に接し且つ開口部187aを有する天板187、取り付け具188で天板187に設けられた複数の誘電体板186が設けられる。

- 【0044】

- また、基板1130及び誘電体板186の間に着火用ガスを流すガス管197、及び原料ガスを流すガス管198が設けられる。ガス管197、198は、ガス供給部182と接続される。具体的には、着火用ガスを流すガス管197は、バルブ196及び質量流量コントローラ194を介して着火用ガス供給源192に接続される。また、原料ガスを流す

10

20

30

40

50

ガス管 198 は、バルブ 195 及び質量流量コントローラ 193 を介して原料ガス供給源 191 に接続される。また、支持台 181 に温度制御部 199 を設けることによって、基板 1130 の温度を制御することも可能である。また、支持台 181 に高周波電源を接続し、高周波電源から出力された交流の電力により、支持台 181 に所定のバイアス電圧を印加する構成としてもよい。なお、ガス供給部 182 及びマイクロ波発生装置 184 は処理容器の外に設けられる。

【0045】

マイクロ波発生装置 184 は、周波数が 1 GHz 以上、好ましくは 2.45 GHz または 8.3 GHz のマイクロ波を供給する。なお、マイクロ波発生装置 184 を複数有することで、安定な大面積のプラズマを生成することが可能である。このため、一辺が 600 mm を超える基板、特に一辺が 1000 mm を超える大面積基板においても、均一性の高い膜を成膜する事が可能であり、且つ成膜速度を高めることができる。

10

【0046】

誘電体板 186 は、天板 187 の開口部に密着するように設けられる。マイクロ波発生装置 184 で発生したマイクロ波が導波管 185 及び天板 187 の開口部を経て、誘電体板 186 に伝播し、誘電体板 186 を透過して処理容器内に放出される。処理容器内に放出されたマイクロ波の電界エネルギーにより、着火用ガスがプラズマ化する。当該プラズマ 200 は、誘電体板 186 表面でより密度が高いため、基板 1130 へのダメージを低減することができる。また、誘電体板 186 を複数設けることで、均一な大面積のプラズマの発生及び維持が可能である。なお、誘電体板 186 は、プラズマ 200 発生側に窪みが形成されてもよい。当該窪みにより、安定したプラズマを生成することができる。

20

【0047】

ガス管 197、198 は、着火用ガスを流すガス管 197 と原料ガスを流すガス管 198 が交差して設けられており、着火用ガスを流すガス管 197 の吹出し口が誘電体板 186 側に設けられ、原料ガスを流すガス管 198 の吹出し口が基板 1130 側に設けられる。着火用ガスが誘電体板 186 側に噴出されることにより、誘電体板 186 表面での成膜を回避しつつプラズマ 200 を発生させることができる。また、基板 1130 により近い位置で原料ガスを噴出しが可能であり、成膜速度を高めることができる。ガス管 197、198 は、アルミナ、窒化アルミニウム等のセラミックスで形成される。セラミックスはマイクロ波の透過率が高いため、ガス管 197、198 をセラミックスで形成することで、誘電体板 186 の直下にガス管を設けても、電界の乱れが生じずプラズマの分布を均一にすることができる。

30

【0048】

図 2 及び図 3 に示す高密度プラズマ装置を用いた成膜処理の手順を以下に示す。まず、図 1 のステップ S170 から成膜処理を開始し、ステップ S171 にて、基板を加熱する。基板は室温、若しくは温度制御部により 100 ~ 550 に加熱する。

【0049】

ステップ S172 にて処理容器内を真空にし、プラズマ着火用ガスとして、ヘリウム、アルゴン、キセノン、クリプトン等の希ガスのいずれか一種以上及び酸素ガスを導入する。2.45 GHz の周波数を用いる場合、希ガスと共に、酸素ガスを処理容器内に導入することで、プラズマの着火を容易とすることができます。なお、周波数などのプラズマ発生条件を適宜設定することで、酸素ガスを用いることなく、希ガスと亜酸化窒素を処理容器内に導入することでプラズマの着火を行うこともできる。この場合、使用するガス種を削減することができる。

40

【0050】

次に、ステップ S173 にて、処理容器内の圧力を所定の圧力にする。処理容器内の圧力は 1 ~ 200 Pa、好ましくは 10 ~ 20 Pa とする。次に、ステップ S174 にて、マイクロ波発生装置の電源をオンにし、マイクロ波発生装置から導波管にマイクロ波を供給し、処理容器内でプラズマを生成する。マイクロ波発生装置の出力は 500 ~ 6000 W、好ましくは 4000 ~ 6000 W とする。マイクロ波の導入によりプラズマの励起を行

50

うと、低電子温度（0.7 eV 以上 3 eV 以下、好ましくは 0.7 eV 以上 1.5 eV 以下）で高電子密度（ $1 \times 10^{11} \sim 1 \times 10^{13} \text{ cm}^{-3}$  以上）のプラズマを生成することができる。

【0051】

次に、ステップ S175 にて、ガス管から原料ガスを処理容器内に導入する。具体的には、酸素ガスの供給を停止し、原料ガスとして、亜酸化窒素、及び希ガスを導入した後、亜酸化窒素、希ガス、及び珪素化合物ガスを導入することで、基板上に半導体層を覆う酸化珪素膜を形成することができる。具体的には、原料ガスは、シランに対する亜酸化窒素の流量比を 10 倍以上 300 倍以下、好ましくは 50 倍とする。

【0052】

次に、ステップ S176 にて、原料ガスの供給を停止し、処理容器内の圧力を低下し、マイクロ波発生装置の電源をオフにする。

【0053】

次に、ステップ S177 にて、プラズマ着火用ガスとして、ヘリウム、アルゴン、キセノン、クリプトン等の希ガスのいずれか一種以上及び酸素ガスを導入する。

【0054】

次に、ステップ S178 にて、処理容器内の圧力を所定の圧力にする。

【0055】

次に、ステップ S179 にて、マイクロ波発生装置の電源をオンにし、マイクロ波発生装置から導波管にマイクロ波を供給し、処理容器内でプラズマを生成する。

【0056】

次に、ステップ S180 にて、ガス管から原料ガスを処理容器 180 内に導入する。具体的には、酸素ガスの供給を停止し、原料ガスとして、亜酸化窒素及び希ガスを導入することで、酸化珪素膜の表面に対してプラズマ処理を行う。

【0057】

次に、ステップ S181 にて、原料ガスの供給を停止し、処理容器内の圧力を低下し、マイクロ波発生装置の電源をオフにして、ステップ S182 で成膜プロセスを終了する。そして、基板を処理容器外に搬送する。

【0058】

こうして得られる窒素を含む酸化珪素膜を薄膜トランジスタのゲート絶縁膜やキャパシタの誘電体などに用いた場合、半導体素子の耐圧を高めることができる。

【0059】

得られた絶縁膜の耐圧を測定するため、以下に示す実験を行った。

【0060】

サンプルの作製手順を示す。まず、ガラス基板上に平行平板型のプラズマ CVD 装置を用いてアモルファスシリコン膜を成膜し、波長が 532 nm のレーザ光（500 μm の長軸ビーム幅）を走査（スキャン速度 350 mm/s）し、結晶化させポリシリコン膜を形成する。なお、レーザ照射前には酸化膜をフッ酸を含むエッチャントを用いてウエットエッティングで除去する。

【0061】

次いで、ポリシリコン膜を選択的にエッティングして島状半導体層を形成した後、島状半導体層を覆うように、高密度プラズマ装置を用いて絶縁膜を形成する。

【0062】

なお、絶縁膜の形成前に高密度プラズマ装置を用いてプラズマ処理を行う。4 台のマイクロ波発生装置（4.5 kW）を有する高密度プラズマ装置を用いる。プラズマ処理は、圧力 20 Pa、基板温度 325、ギャップ間隔（誘電体 - 基板間隔）160 mm、亜酸化窒素の流量 1000 sccm、アルゴン流量 2500 sccm として 5 分間行った。次いで、圧力 20 Pa、基板温度 325、ギャップ間隔（誘電体 - 基板間隔）160 mm、モノシランの流量 30 sccm、亜酸化窒素の流量 1500 sccm、アルゴンの流量 2500 sccm として膜厚 10 nm の絶縁膜を成膜した。成膜後、再度、成膜前に行つた

10

20

30

40

50

プラズマ処理と同じ条件のプラズマ処理を行った。

【0063】

次いで、絶縁膜を通過させて絶縁膜と重なる半導体層にボロンをドーピングする。加速電圧は20kVとし、 $1 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{20} / \text{cm}^3$ 未満の濃度となるドーピング処理を行う。

【0064】

次いで、半導体層と重なる絶縁膜上に電極を形成し、電極をマスクとしてボロンを半導体層に添加する。なお、添加されるボロンは、 $1 \times 10^{20} / \text{cm}^3$ 以上 $1 \times 10^{22} / \text{cm}^3$ 未満の濃度となるドーピング処理を行う。

【0065】

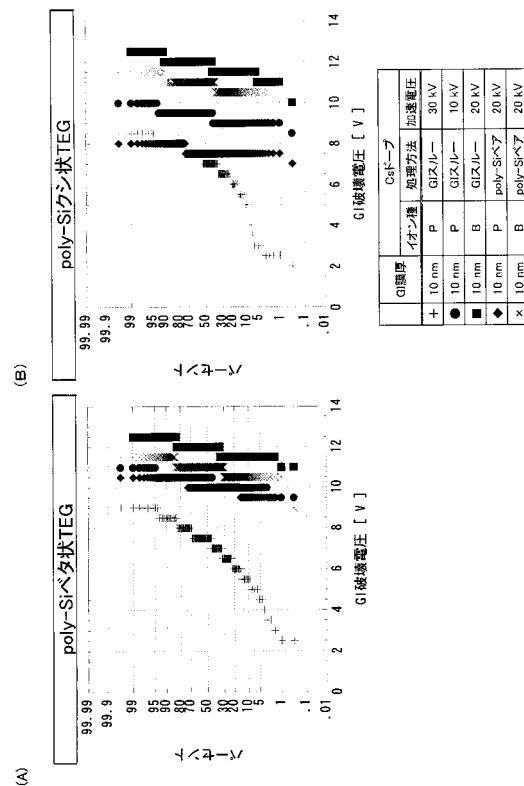

また、絶縁膜を通過させて半導体層にボロンを添加した上記サンプルとは異なる工程順序、具体的には絶縁膜を形成する前にドーピングを行ったサンプルを作製し、絶縁破壊が生じるまで電圧を与える、その分布を示すグラフを図4(A)に示す。

10

【0066】

また、図4(A)は、ドーピングの加速電圧の条件も振った結果も含んでいる。また、ボロンに代えてリンをドーピングしたサンプルの結果も含んでいる。図4(A)の結果から、絶縁膜の形成前にドーピングを行うサンプルよりも絶縁膜を通過させて半導体層にドーピングするサンプルのほうが、破壊される電圧値が高く、高い耐圧を有している傾向が読み取れる。また、ドーピング処理の加速電圧が低いほうが、破壊される電圧値が高く、高い耐圧を有している傾向が読み取れる。

20

【0067】

また、図4(A)からは、電極と重なる半導体層にリンをドーピングしたサンプルよりも電極と重なる半導体層にボロンをドーピングしたサンプルのほうが、破壊される電圧値が高い傾向が読み取れる。このことは、イオン種がリンの場合では絶縁膜にドーピングによるダメージが入ってしまうが、ボロンでは原子サイズがリンより小さいためダメージを低減できていることに起因している。

【0068】

また、図4(A)とは異なる半導体層の上面形状、具体的には電極と重なる半導体層を短冊状に形成したサンプルの結果を図4(B)に示す。図4(B)で特筆すべきは、絶縁膜を介してボロンをドーピングしたサンプルに関しては、図4(A)とほぼ同じ結果を示していることである。このことは、半導体層が短冊状であれば、その上に形成される絶縁膜にも凹凸が形成されることになるが、本実施の形態に示す作製方法により、膜厚10nmと薄い絶縁膜であっても均一な膜厚が短冊状の半導体層上に被覆性良く形成されていると言える。

30

【0069】

なお、図4(A)、図4(B)では、絶縁膜の成膜の前後にプラズマ処理を行った例を示しているが特に限定されず、例えば、さらなる高信頼性を得るために、絶縁膜の成膜後のみにプラズマ処理を行うことが好ましい。

【0070】

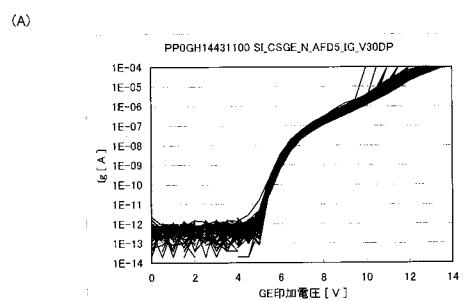

また、ドーピング処理の加速電圧が低いほうが、I-V特性のバラツキも低減する。図5にI-V特性を示すグラフを示す。図5(A)は、電極と重なる短冊状の半導体層にリンを10kVでドーピングしたサンプルのI-V特性のバラツキを示す実験結果であり、図5(B)は、電極と重なる短冊状の半導体層にリンを20kVでドーピングしたサンプルのI-V特性のバラツキを示す実験結果である。

40

【0071】

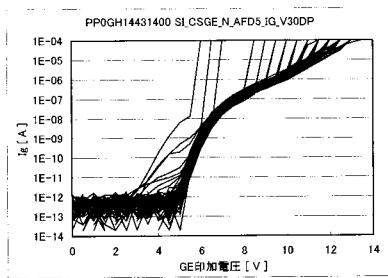

また、絶縁膜の成膜後のパーティクル数の圧力依存性を測定した結果を図6に示す。成膜条件は、成膜温度325、ギャップ間隔160mm、シラン30sccm、亜酸化窒素の流量3000sccm、アルゴンの流量2500sccmとして膜厚10nmの絶縁膜を成膜した。成膜圧力を20Paと30Paとでパーティクル数の比較を行っている。図6に示すように30Paよりも20Paのほうがパーティクル数が少なく、好ましい圧力

50

条件であることが分かる。図6の成膜条件においてシランに対する亜酸化窒素の流量比は、100倍であり、50倍に比べてパーティクル数が多く発生する条件である。パーティクルが多く発生すると、絶縁膜表面に微小な凸部が形成される恐れがあり、膜厚均一性が低下する。

【0072】

ここでは、膜厚10nmの絶縁膜を用いて比較した例を説明したが、特にこの膜厚に限定されず、100nm未満の薄い膜厚であれば同様の効果が得られる。勿論、膜厚が薄ければ薄いほど成膜に要する時間を短縮することができる。また、高密度プラズマ装置を用いた絶縁膜を誘電体とする容量を形成する場合、絶縁膜の膜厚が薄ければ薄いほど大きな容量を形成することができる。

10

【0073】

また、高密度プラズマ装置を用いて、シリコンウエハ上に第1の絶縁膜、第2の絶縁膜、第3の絶縁膜、第4の絶縁膜、第5の絶縁膜をそれぞれ200nmの膜厚で積層し、SIMS(二次イオン質量分析計)を用いた分析により、膜中の水素、炭素、窒素、及びフッ素の濃度を測定した結果を図7に示す。第1の絶縁膜の成膜条件は、圧力を20Paとし、シラン流量を30sccmとし、亜酸化窒素の流量を1500sccmとしてシランに対する亜酸化窒素の流量比を50倍とした。また、第2の絶縁膜の成膜条件は、圧力を20Paとし、シラン流量を60sccmとし、亜酸化窒素の流量を3000sccmとしてシランに対する亜酸化窒素の流量比を50倍とした。また、第3の絶縁膜の成膜条件は、圧力を30Paとし、シラン流量を100sccm、亜酸化窒素を流量3000sccmとしてシランに対する亜酸化窒素の流量比を30倍とした。また、第4の絶縁膜の成膜条件は、圧力を30Paとし、シラン流量を250sccm、亜酸化窒素の流量を2500sccmとしてシランに対する亜酸化窒素の流量比を10倍としている。なお、第1、第2、第3、第4の絶縁膜は、流量2500sccmのアルゴンガスを誘電体板側に噴出させ、原料ガス(シラン及び亜酸化窒素)を基板側に噴出させた。また、第5の絶縁膜は酸化珪素膜のリファレンスである。第5の絶縁膜の成膜条件は、圧力を15Paとし、シラン流量を250sccm、酸素の流量を1500sccm、アルゴンガスの流量を3500sccmとして全てのガスを基板側に噴出させた。また、第1、第2、第3、第4、第5の絶縁膜は、基板温度を325とし、ギャップ間隔を160mmとした。図7からは、シランと、亜酸化窒素とを成膜ガスとし、高密度プラズマ装置を用いて得られる絶縁膜の窒素濃度が、 $1 \times 10^{19} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 未満であることが読み取れる。本実施の形態では、上述した第1、第2、第3、第4のいずれか一の絶縁膜に対して成膜室と同じチャンバーで大気に曝すことなく連続的に、亜酸化窒素を用いたプラズマ処理を行うことで、さらなる絶縁膜の表面改質を行っている。また、本明細書における濃度は、SIMSを用いた分析による濃度のピーク値を指している。SIMSは濃度の低い側から高い側に向かって深さ方向に分析された値である。

20

30

【0074】

以上の構成でなる実施の形態について、以下に示す実施例でもってさらに詳細な説明を行うこととする。

40

【実施例1】

【0075】

本実施例では、アンテナ回路を含む半導体装置を基板上に設ける構成について説明する。

【0076】

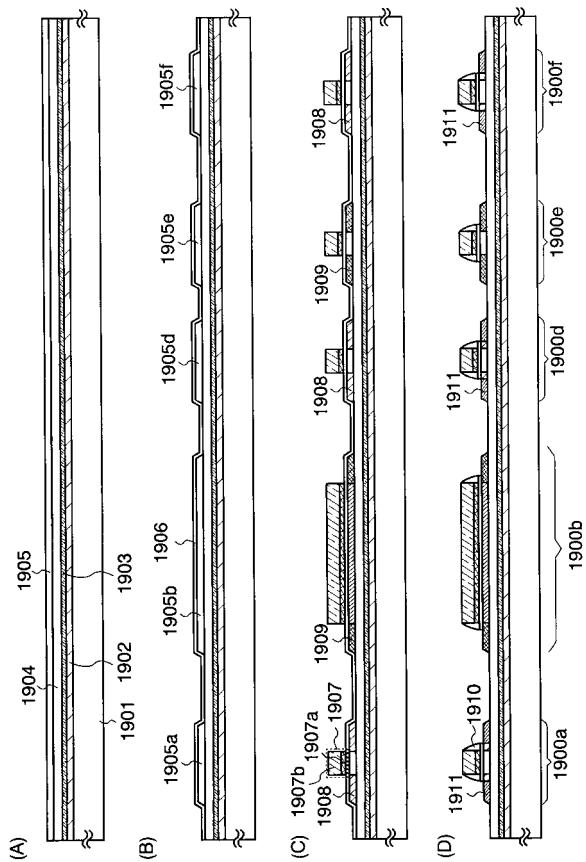

まず、図8(A)に示すように、基板1901の一表面に絶縁膜1902を介して剥離層1903を形成し、続けて下地膜として機能する絶縁膜1904と半導体膜1905(例えば、非晶質珪素を含む膜)を積層して形成する。なお、絶縁膜1902、剥離層1903、絶縁膜1904および半導体膜1905は、連続して形成することができる。

【0077】

なお、基板1901は、ガラス基板、石英基板、金属基板(例えばステンレス基板など)、セラミック基板から選択されるものである。なお、本工程では、剥離層1903は、

50

絶縁膜 1902 を介して基板 1901 の全面に設けているが、必要に応じて、基板 1901 の全面に剥離層を設けた後に、フォトリソグラフィ法により選択的に設けてもよい。

【0078】

また、絶縁膜 1902、絶縁膜 1904 は、プラズマ CVD 法やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン ( $\text{SiO}_x\text{N}_y$ ) ( $x > y > 0$ )、窒化酸化シリコン ( $\text{SiN}_x\text{O}_y$ ) ( $x > y > 0$ ) 等の材料を用いて形成する。例えば、絶縁膜 1902、1904 を 2 層構造とする場合、第 1 層目の絶縁膜として窒化酸化シリコン膜を形成し、第 2 層目の絶縁膜として酸化窒化シリコン膜を形成するとよい。また、第 1 層目の絶縁膜として窒化シリコン膜を形成し、第 2 層目の絶縁膜として酸化シリコン膜を形成してもよい。絶縁膜 1902 は、基板 1901 から剥離層 1903 またはその上に形成される素子に不純物元素が混入するのを防ぐブロッキング層として機能し、絶縁膜 1904 は基板 1901、剥離層 1903 からその上に形成される素子に不純物元素が混入するのを防ぐブロッキング層として機能する。このように、ブロッキング層として機能する絶縁膜 1902、1904 を形成することによって、基板 1901 から Na などのアルカリ金属やアルカリ土類金属が、剥離層 1903 から剥離層に含まれる不純物元素がこの上に形成する素子に悪影響を与えることを防ぐことができる。なお、基板 1901 として石英を用いるような場合には絶縁膜 1902、1904 を省略してもよい。

10

【0079】

また、剥離層 1903 は、金属膜や金属膜と金属酸化膜の積層構造等を用いることができる。金属膜としては、タンゲステン (W)、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、ニオブ (Nb)、ニッケル (Ni)、コバルト (Co)、ジルコニウム (Zr)、亜鉛 (Zn)、ルテニウム (Ru)、ロジウム (Rh)、パラジウム (Pd)、オスミウム (Os)、イリジウム (Ir) から選択された元素または当該元素を主成分とする合金材料若しくは化合物材料からなる膜を単層または積層して形成する。また、これらの材料は、スパッタ法やプラズマ CVD 法等を用いて形成することができる。金属膜と金属酸化膜の積層構造としては、上述した金属膜を形成した後に、酸素雰囲気下または酸化窒素雰囲気下におけるプラズマ処理、酸素雰囲気下または酸化窒素雰囲気下における加熱処理を行うことによって、金属膜表面に当該金属膜の酸化物または酸化窒化物を設けることができる。例えば、金属膜としてスパッタ法や CVD 法等によりタンゲステン膜を設けた場合、タンゲステン膜にプラズマ処理を行うことによって、タンゲステン膜表面にタンゲステン酸化物からなる金属酸化膜を形成することができる。他にも、例えば、金属膜 (例えば、タンゲステン) を形成した後に、当該金属膜上にスパッタ法で酸化珪素等の絶縁膜を設けると共に、金属膜上に金属酸化物 (例えば、タンゲステン上にタンゲステン酸化物) を形成してもよい。また、プラズマ処理として、例えば高密度プラズマ装置を用いた高密度プラズマ処理を行ってもよい。また、金属酸化膜の他にも、金属窒化物や金属酸化窒化物を用いてもよい。この場合、金属膜に窒素雰囲気下または窒素と酸素雰囲気下でプラズマ処理や加熱処理を行えばよい。

20

30

【0080】

また、半導体膜 1905 は、スパッタリング法、LPCVD 法、プラズマ CVD 法等により、25 nm 以上 200 nm 以下 (好ましくは 30 nm 以上 150 nm 以下) の厚さで形成する。

40

【0081】

次に、図 8 (B) に示すように、半導体膜 1905 にレーザビームを照射して結晶化を行う。なお、レーザビームの照射と、RTA またはファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により半導体膜 1905 の結晶化を行ってもよい。

【0082】

結晶化工程の一例を以下に簡単に説明すると、まず、平行平板型のプラズマ CVD 装置を用いて非晶質半導体膜を成膜し、膜厚 66 nm とする。その後、メガヘルツレーザビームを照射し、結晶質半導体膜 1905 を形成する。なお、本明細書においてメガヘルツレー

50

ザビームとは、周波数 10 MHz 以上、パルス幅 100 fs 以上 1 ns 以下の極短パルスを有するレーザビームを言う。周波数を 10 MHz 以上とすることで、連続的に半導体膜に熱を与えることができるため、連続的な結晶成長が可能となる。本実施例では、メガヘルツレーザビーム照射前に酸化膜除去を行った後、周波数 80 MHz、パルス幅 15 ps の YVO<sub>4</sub> レーザを用いて、波長 532 nm、照射パワー 8 ~ 9 W、長軸ビーム幅 500 μm、スキャン速度 350 mm/s とする。照射後の半導体膜の膜厚は 60 nm となる。

【0083】

半導体膜 1905 の結晶化の後、フォトリソグラフィ法を用いることによって得られた結晶質半導体膜を所望の形状にエッチングして、結晶質半導体膜 1905a、1905b、1905d、1905e、1905f を形成し、当該半導体膜を覆うようにゲート絶縁膜 1906 を形成する。

10

【0084】

ゲート絶縁膜 1906 は、高密度プラズマ装置を用いて形成する。例えば、圧力 20 Pa、基板温度 325 °C、ギャップ間隔（誘電体 - 基板間隔）160 mm、モノシランの流量 30 sccm、亜酸化窒素の流量 1500 sccm、アルゴンの流量 2500 sccm として膜厚 10 nm の絶縁膜を成膜する。

20

【0085】

次いで、高密度プラズマ装置を用いてプラズマ処理を行う。プラズマ処理は、圧力 20 Pa、基板温度 325 °C、ギャップ間隔（誘電体 - 基板間隔）160 mm、亜酸化窒素の流量 1000 sccm、アルゴン流量 2500 sccm とする。このような高密度プラズマを用いた処理により、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜が形成され、その結果、高耐圧である 10 nm のゲート絶縁膜 1906 を得ることができる。

20

【0086】

本実施例では、ゲート絶縁膜 1906 の膜厚を 10 nm とする例を説明したが、特にこの膜厚に限定されず、10 nm よりも厚く 100 nm 未満の膜厚であっても、均一性が良く、界面準位密度が低い絶縁膜が得られる。

30

【0087】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、イオンドープ法またはイオン注入法により、保持容量部 1900b となる半導体膜 1905b にゲート絶縁膜 1906 を介して p 型を付与する不純物元素を添加する。p 型を示す不純物元素としては、ボロン (B) やアルミニウム (Al) やガリウム (Ga) 等を用いることができる。ここでは、p 型を付与する不純物元素としてボロン (B) を用い、 $1 \times 10^{19} / \text{cm}^3$  以上  $1 \times 10^{20} / \text{cm}^3$  以下の濃度で含まれるように選択的に添加する。添加した後は、レジストからなるマスクを除去する。

30

【0088】

次に、ゲート絶縁膜 1906 上に、第 1 の導電膜と第 2 の導電膜とを積層して形成する。ここでは、第 1 の導電膜は、CVD 法やスパッタリング法等により、20 nm 以上 100 nm 以下の厚さで形成する。第 2 の導電膜は、100 nm 以上 400 nm 以下の厚さで形成する。第 1 の導電膜と第 2 の導電膜は、タンタル (Ta)、タンゲステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、銅 (Cu)、クロム (Cr)、ニオブ (Nb) 等から選択された元素、またはこれらの元素を主成分とする合金材料若しくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第 1 の導電膜と第 2 の導電膜の組み合わせの例を挙げると、窒化タンタル膜とタンゲステン膜、窒化タンゲステン膜とタンゲステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、第 1 の導電膜と第 2 の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2 層構造ではなく、3 層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。

40

【0089】

50

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、半導体膜 1905a、1905b、1905d、1905e、1905fの上方にゲート電極 1907を形成する。ここでは、ゲート電極 1907として、第1の導電膜 1907aと第2の導電膜 1907bの積層構造で設けた例を示している。

【0090】

次に、図8(C)に示すように、ゲート電極 1907をマスクとして半導体膜 1905a、1905b、1905d、1905e、1905fに、イオンドープ法またはイオン注入法により、n型を付与する不純物元素を低濃度に添加し、その後、フォトリソグラフィ法によりレジストからなるマスクを選択的に形成して、p型を付与する不純物元素を高濃度に半導体膜 1905b、1905eに添加する。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。ここでは、n型を付与する不純物元素としてリン(P)を用い、 $1 \times 10^{18} / \text{cm}^3$ 以上 $1 \times 10^{19} / \text{cm}^3$ 以下の濃度で含まれるように半導体膜 1905a、1905b、1905d、1905e、1905fに導入し、n型を示す不純物領域 1908を形成する。また、p型を付与する不純物元素としてボロン(B)を用い、 $1 \times 10^{18} / \text{cm}^3$ 以上 $1 \times 10^{19} / \text{cm}^3$ 以下の濃度で含まれるように選択的に半導体膜 1905b、1905eに導入し、p型を示す不純物領域 1909を形成する。

10

【0091】

続いて、ゲート絶縁膜 1906とゲート電極 1907を覆うように、絶縁膜を形成する。絶縁膜は、プラズマCVD法やスパッタリング法等により、珪素、珪素の酸化物または珪素の窒化物の無機材料を含む膜、及び有機樹脂などの有機材料を含む膜の一種または複数種を、単層または積層して形成する。次に、絶縁膜を垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極 1907の側面に接する絶縁膜 1910(サイドウォールともよばれる)を形成する。絶縁膜 1910は、LDD(Lightley Doped drain)領域を形成する際のドーピング用のマスクとして用いる。

20

【0092】

続いて、フォトリソグラフィ法により形成したレジストからなるマスクと、ゲート電極 1907および絶縁膜 1910をマスクとして用いて、半導体膜 1905a、半導体膜 1905d、半導体膜 1905fにn型を付与する不純物元素を高濃度に添加して、n型を示す高濃度不純物領域 1911を形成する。ここでは、n型を付与する不純物元素としてリン(P)を用い、 $1 \times 10^{20} / \text{cm}^3$ 以上 $1 \times 10^{21} / \text{cm}^3$ 以下の濃度で含まれるように半導体膜 1905a、半導体膜 1905d、半導体膜 1905fに選択的に導入し、不純物領域 1908より高濃度のn型を示す高濃度不純物領域 1911を形成する。

30

【0093】

以上の工程により、図8(D)に示すように、nチャネル型である薄膜トランジスタ 1900a、1900d、及び 1900fと、pチャネル型である薄膜トランジスタ 1900eと、保持容量部 1900bが形成される。

40

【0094】

なお、薄膜トランジスタ 1900aは、ゲート電極 1907と重なる半導体膜 1905aの領域にチャネル形成領域が形成され、ゲート電極 1907及び絶縁膜 1910と重ならない領域にソース領域またはドレイン領域を形成する高濃度不純物領域 1911が形成され、絶縁膜 1910と重なる領域であってチャネル形成領域と高濃度不純物領域 1911の間に低濃度不純物領域(LDD領域)が形成されている。また、薄膜トランジスタ 1900d、薄膜トランジスタ 1900fも同様にチャネル形成領域、低濃度不純物領域及び高濃度不純物領域 1911が形成されている。

【0095】

また、薄膜トランジスタ 1900eは、ゲート電極 1907と重なる半導体膜 1905eの領域にチャネル形成領域が形成され、ゲート電極 1907と重ならない領域に高濃度

50

不純物領域 1909 が形成されている。なお、ここでは、薄膜トランジスタ 1900e には、LDD 領域を設けていないが、LDD 領域を設けてもよいし、薄膜トランジスタ 1900a に LDD 領域を設けない構成としてもよい。

【0096】

また、保持容量部 1900b は、ゲート電極 1907 と同じ工程で形成された電極と、半導体膜 1905b とを一対の電極とし、膜厚 10 nm の絶縁膜を誘電体としている。UHF 帯の無線信号を送受信する場合、交流信号を整流後に平滑化を行い電荷を保持するための保持容量部の合計容量値は、1 nF (1000 pF) を超える。ここでは、合計容量値が約 30 nF とする。

【0097】

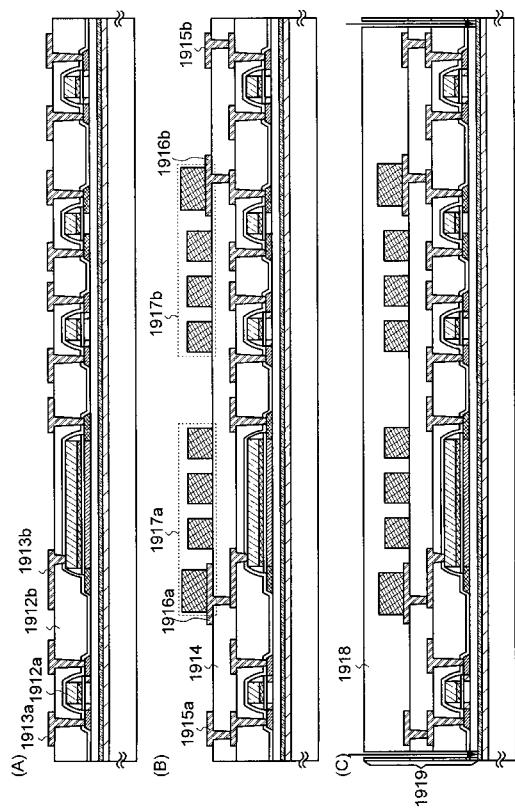

次に、図 9 (A) に示すように、半導体膜 1905a、1905b、1905d、1905e、1905f、ゲート電極 1907 等を覆うように、絶縁膜を単層または積層を形成し、当該絶縁膜上に高濃度不純物領域 1909、1911 と電気的に接続する導電膜 1913a と、保持容量部と電気的に接続する導電膜 1913b を形成する。絶縁膜は、CVD 法、スパッタリング法、SOG 法、液滴吐出法、スクリーン印刷法等により、珪素の酸化物及び珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、及びエポキシ等の有機材料、シロキサン材料のいずれか一種または複数種を単層または積層で形成する。ここでは、当該絶縁膜を 2 層で設け、1 層目の絶縁膜 1912a として窒化酸化珪素膜で形成し、2 層目の絶縁膜 1912b として酸化窒化珪素膜で形成する。また、導電膜 1913a は、半導体膜 1905a、1905d、1905e、1905f と電気的に接続するソース電極またはドレイン電極を形成する。

10

20

【0098】

なお、絶縁膜 1912a、1912b を形成する前、または絶縁膜 1912a、1912b のうちの 1 つまたは複数の薄膜を形成した後に、半導体膜の結晶性の回復や半導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザニール法または RTA 法などを適用するとよい。

【0099】

また、導電膜 1913a、1913b は、CVD 法やスパッタリング法等により、アルミニウム、タンクステン、チタン、タンタル、モリブデン、ニッケル、白金、銅、金、銀、マンガン、ネオジム、炭素、及びシリコンから選択された元素、またはこれらの元素を主成分とする合金材料または化合物材料で、単層または積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分とし、ニッケルを含む材料、またはアルミニウムを主成分とし、ニッケルと、炭素と珪素の一方または両方とを含む合金材料などを用いることができる。導電膜 1913a、1913b は、例えば、バリア膜とアルミニウムシリコン (Al-Si) 膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン (Al-Si) 膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、またはモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜 1913a、1913b を形成する材料として最適である。

30

【0100】

40

次に、導電膜 1913a、1913b を覆うように、層間絶縁膜 1914 を形成する。

【0101】

なお、層間絶縁膜 1914 は、CVD 法やスパッタ法等により、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等の酸素または窒素を有する絶縁膜や DLC (ダイヤモンドライクカーボン) 等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si 結合を含む材料に相当する。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、有機基 (例えばアルキル基、芳香族炭化水素基) やフルオロ基を用いてもよい。有機基は、フルオロ基を有してもよい。

50

## 【0102】

次に、層間絶縁膜1914上に、薄膜トランジスタ1900a、1900fのソース電極またはドレイン電極を形成する導電膜1913aとそれぞれ電気的に接続する導電膜1915a、1915bを形成する。また、保持容量部1900bの電極と電気的に接続する導電膜1916aを形成する。薄膜トランジスタ1900eのソース電極またはドレイン電極を形成する導電膜1913aと電気的に接続する導電膜1916bを形成する。なお、導電膜1915a、1915bと導電膜1916a、1916bは同一の材料で同時に形成してもよい。導電膜1915a、1915bと導電膜1916a、1916bは、上述した導電膜1913a、1913bに用いることのできる材料のいずれかを用いて形成することができる。

10

## 【0103】

続いて、図9(B)に示すように、導電膜1916a、1916b上にアンテナとして機能する導電膜1917a、1917bが電気的に接続されるように形成する。

## 【0104】

また、導電膜1917a、1917bは、CVD法、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム、チタン、銀、銅、金、白金、ニッケル、パラジウム、タンタル、モリブデンから選択された元素、またはこれらの元素を主成分とする合金材料若しくは化合物材料で、単層構造または積層構造で形成する。

20

## 【0105】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電膜1917a、1917bを形成する場合には、粒径が数nmから数十μmの導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀、金、銅、ニッケル、白金、パラジウム、タンタル、モリブデンおよびチタン等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコーン樹脂等の有機樹脂が挙げられる。また、導電膜1917a、1917bの形成にあたり、導電性のペーストを押し出した後に焼成することが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子(例えば粒径1nm以上100nm以下)を用いる場合、150以上300以下の温度範囲で焼成することにより硬化させて導電膜を得ることができる。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径20μm以下の微粒子を用いることが好ましい。はんだや鉛フリーはんだは、低コストであるといった利点を有している。

30

## 【0106】

次に、図9(C)に示すように、導電膜1917a、1917bを覆うように絶縁膜1918を形成した後、薄膜トランジスタ1900a、1900d、1900e、1900f、保持容量部1900b、導電膜1917a、1917b等を含む層(以下、素子形成層1919と記す)を基板1901から剥離する。ここでは、レーザビーム(例えばUV光)を照射することによって、薄膜トランジスタ1900a、1900d、1900e、1900f、及び保持容量部1900bを避けた領域に開口部を形成後、物理的な力を用いて基板1901から素子形成層1919を剥離することができる。

40

## 【0107】

絶縁膜1918は、CVD法やスパッタ法等により、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライカーボン)等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。

## 【0108】

50

本実施例では、図10(A)に示すように、レーザビームの照射により素子形成層1919に開口部を形成した後に、当該素子形成層1919の一方の面(絶縁膜1918の露出した面)に第1のシート材1920を貼り合わせた後、基板1901から素子形成層1919を剥離する。

【0109】

次に、図10(B)に示すように、素子形成層1919の他方の面(剥離により露出した面)に、加熱処理と加圧処理の一方または両方を行って第2のシート材1921を貼り合わせる。好ましくは、素子形成層1919の周囲全体を第2のシート材1921で覆う。第1のシート材1920、第2のシート材1921として、ホットマルトフィルム等を用いることができる。

10

【0110】

また、第2のシート材1921として、繊維体を含む樹脂を用いてもよい。繊維体は、有機化合物または無機化合物の高強度繊維を用いた織布または不織布であり、その高強度繊維の代表例としては、ポリビニルアルコール系繊維、ポリエステル系繊維、ポリアミド系繊維、ポリエチレン系繊維、アラミド系繊維、ポリパラフェニレンベンゾビスオキサゾール繊維、ガラス繊維、または炭素繊維である。ガラス繊維としては、Eガラス、Sガラス、Dガラス、Qガラス等を用いたガラス繊維を用いることができる。なお、繊維体は、一種類の上記高強度繊維で形成されてもよい。また、複数の上記高強度繊維で形成されてもよい。繊維体を含む樹脂を用いることで高温高湿の環境に対して信頼性を向上させることができる。

20

【0111】

また、第2のシート材1921として、紙を用いることができる。また、1枚の紙に素子形成層1919を抄き込むこともできる。素子形成層1919を紙に抄き込む方法は、多層に抄紙する方法が好適である。

【0112】

また、第1のシート材1920、第2のシート材1921として、静電気等を防止する帯電防止対策を施したフィルム(以下、帯電防止フィルムと記す)を用いることもできる。帯電防止フィルムとしては、帯電防止可能な材料を樹脂中に分散させたフィルム、及び帯電防止可能な材料が貼り付けられたフィルム等が挙げられる。帯電防止可能な材料が設けられたフィルムは、片面に帯電防止可能な材料を設けたフィルムであってもよいし、両面に帯電防止可能な材料を設けたフィルムであってもよい。さらに、片面に帯電防止可能な材料が設けられたフィルムは、帯電防止可能な材料が設けられた面をフィルムの内側になるように素子形成層1919に貼り付けてもよいし、フィルムの外側になるように貼り付けてもよい。なお、帯電防止可能な材料はフィルムの全面、あるいは一部に設けてあればよい。ここでの帯電防止可能な材料としては、金属、インジウムと錫の酸化物(ITO)、両性界面活性剤や陽イオン性界面活性剤や非イオン性界面活性剤等の界面活性剤を用いることができる。また、他にも帯電防止材料として、側鎖にカルボキシル基および4級アンモニウム塩基をもつ架橋性共重合体高分子を含む樹脂材料等を用いることができる。これらの材料をフィルムに貼り付けたり、練り込んだり、塗布することによって帯電防止フィルムとすることができる。帯電防止フィルムで封止を行うことによって、商品として取り扱う際に、外部からの静電気等によって半導体素子に悪影響が及ぶことを抑制することができる。

30

【0113】

次いで、必要であれば分断を行い、個々の半導体装置に切り分ける。

【0114】

また本実施例では素子形成層1919を基板1901から剥離して利用する例を示しているが、剥離層1903を設けずに、基板1901上に上述の素子形成層1919を作製し、半導体装置として利用しても良い。なお基板1901として、SOI(Silicon on Insulator)基板を用いる場合は、半導体膜として単結晶半導体膜を用いればよく、半導体膜の結晶化の工程の分の短縮を図ることが出来る。

40

50

## 【0115】

以上のように、本実施例の作製方法を用いることにより、小型で、物理的形状に対する柔軟性を有し、且つ、より信頼性の高い半導体装置を提供できる。

## 【0116】

特に高密度プラズマ装置を用いて、絶縁膜の膜厚を均一に 10 nm とすることができるため、比較的狭い平面積で容量を確保することができ、保持容量部の合計容量値のバラツキも低減することができる。また、回路に用いられる薄膜トランジスタのゲート絶縁膜の膜厚を均一に 10 nm とすることができるため、I-V 特性カーブの立ち上がり部分における傾きが急峻となり、薄膜トランジスタのしきい値を低減することができる。薄膜トランジスタのしきい値を低減することは、低電圧での動作が可能な回路を実現でき、または高速動作させることができる。無線チップにおいては、低電圧での動作が可能な回路として、通信距離の延長を図ることができる。本実施例の無線チップにおいて無線信号から定電圧回路に出力される電圧は 2 V 未満である。

10

## 【実施例 2】

## 【0117】

本実施例では、液晶素子を用いた半導体装置の例を図 11 (A)、図 11 (B) を用いて説明する。

## 【0118】

透光性を有する基板 900 上に画素部 936 と駆動回路 934 にそれぞれ薄膜トランジスタを形成する。また、画素部 936 には、保持容量 976 を形成する。

20

## 【0119】

画素部 936においては 5 V ~ 10 V の駆動電圧が用いられるため、画素部 936 に配置される薄膜トランジスタ 975 には 5 V ~ 10 V の駆動電圧で動作するに適した構造とすることが望ましい。画素部 936 に用いる薄膜トランジスタ 975 は、少なくとも実施例 1 の無線チップに搭載する薄膜トランジスタよりもゲート絶縁膜を厚くする。また、液晶素子には焼き付き防止のため、画素電極には負の電圧と正の電圧とが交互に印加される。また、1 画素あたりの保持容量 976 は、約 0.2 pF ~ 数 pF とする。

## 【0120】

透光性を有する基板 900 上にバリア膜となる下地絶縁膜 901 を形成した後、非晶質半導体膜を形成し、公知の結晶化技術により結晶質半導体膜を形成する。次いで、結晶質半導体膜を選択的にエッティングして島状の半導体層を複数形成し、その上に絶縁膜 903 を形成する。本実施例では、高密度プラズマ装置を用いて、絶縁膜 903 の膜厚を均一に 30 nm とすることができる。絶縁膜 903 を 30 nm と薄いものとしても 5 V ~ 10 V の駆動電圧で動作するのに適した構造とすることができます。また、長期信頼性も高い薄膜トランジスタを提供することができる。また、絶縁膜 903 の膜厚を薄くすることによって、1 画素あたりの保持容量を少ない電極面積で確保することができるため、画素部の開口率の向上に寄与することができる。

30

## 【0121】

本実施例では、絶縁膜 903 の膜厚を 30 nm とする例を説明したが、特にこの膜厚に限られず、30 nm よりも厚く 100 nm 未満の膜厚であっても、長期信頼性も高い薄膜トランジスタを提供することができる。

40

## 【0122】

そして、導電膜を形成した後、選択的にエッティングしてゲート電極 930、及び容量配線 931 を形成する。次いで、島状半導体層に n 型または p 型を付与する不純物元素を適宜添加して不純物領域を形成する。本実施例では、2 層の導電膜を選択的にエッティングした後、リンを添加して低濃度不純物領域を形成し、さらに導電膜の一部をエッティングして図 11 (B) に示す電極形状を得た後、画素部の薄膜トランジスタ 975 の一部と、薄膜トランジスタ 973 を覆うレジストマスクをマスクとしてリンを添加して高濃度不純物領域を形成する。そして、薄膜トランジスタ 974、975 及び保持容量 976 が形成される領域を覆うレジストマスクを形成し、ボロンを添加して、p チャネル型の薄膜トランジス

50

タ 9 7 3 のソース領域またはドレイン領域を形成する。本実施例では、保持容量 9 7 6 は、絶縁膜 9 0 3 を誘電体とし、リンが添加された高濃度不純物領域を有する島状半導体層と、容量配線 9 3 1 を一対の電極とする容量である。

【 0 1 2 3 】

次いで、ゲート電極 9 3 0 、及び容量配線 9 3 1 を層間絶縁膜で覆う。次いで、島状半導体層に達するコンタクトホールを形成した後、島状半導体層と電気的に接続するソース配線 9 6 0 や電極などを層間絶縁膜上に形成する。

【 0 1 2 4 】

次いで、層間絶縁膜上に平坦化膜を形成し、薄膜トランジスタ 9 7 5 のソース電極またはドレイン電極に達するコンタクトホールを形成し、薄膜トランジスタ 9 7 5 のソース電極またはドレイン電極と電気的に接続する画素電極 9 6 1 を形成する。

10

【 0 1 2 5 】

次いで、スクリーン印刷法やインクジェット法により画素部に画素電極 9 6 1 を覆う配向膜 9 8 1 を形成する。

【 0 1 2 6 】

以上の工程で、画素部に薄膜トランジスタを有する基板を作製する。次いで、対向電極 9 8 4 を有する対向基板 9 9 5 と基板 9 0 0 とをシール材 9 9 2 を用いて貼り合わせる。なお、貼り合わせる前に、対向基板 9 9 5 にもカラーフィルタ 9 8 5 及び対向電極 9 8 4 を覆う配向膜 9 8 3 を形成する。液晶滴下法を用いる場合には、閉ループのシール材 9 9 2 に囲まれた領域に液晶を滴下し、減圧下で一対の基板の貼り合わせを行う。こうして一対の基板とシール材で囲まれた領域に液晶層 9 8 2 を充填する。

20

【 0 1 2 7 】

次いで、基板 9 0 0 に偏光板 9 9 3 などの光学フィルムを設け、対向基板 9 9 5 にも偏光板 9 9 1 などの光学フィルムを設ける。

【 0 1 2 8 】

以上の工程により、液晶パネルを作製する。

【 実施例 3 】

【 0 1 2 9 】

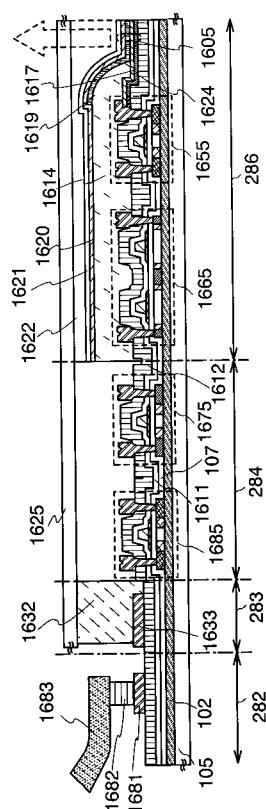

本実施例では、有機発光素子を用いた半導体装置の作製例を図 1 2 及び図 1 3 を用いて説明する。

30

【 0 1 3 0 】

ここではガラス基板を用いた SOI 基板を作製し、有機発光素子を形成する。まず、半導体ウエハ 1 0 1 上にバッファ層 1 0 2 を形成する。本実施例では半導体ウエハ 1 0 1 として、結晶方位が (1 0 0) である 12 インチの単結晶シリコンウエハ（直径約 300 mm）を例に用いる。

【 0 1 3 1 】

円形状の単結晶半導体ウエハには、シリコンやゲルマニウムなどの半導体ウエハ、ガリウムヒ素やインジウムリンなどの化合物半導体ウエハなどがある。もちろん、単結晶半導体基板は、円形のウエハに限定されるものではなく、様々な形状の単結晶半導体基板を用いることができる。例えば、長方形、五角形、六角形などの多角形の基板を用いることができる。

40

【 0 1 3 2 】

また、長方形の単結晶半導体基板は、市販の円形状の単結晶半導体ウエハを切断することで形成することができる。基板の切断には、ダイサー或いはワイヤソー等の切断装置、レーザ切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いることができる。また、基板として薄片化する前の半導体基板製造用のインゴットを、その断面が長方形になるように直方体状に加工し、この直方体状のインゴットを薄片化することでも、長方形形状の単結晶半導体基板を製造することができる。また、単結晶半導体基板の厚さは特に限定されないが、単結晶半導体基板を再利用することを考慮すれば、厚い方が 1 枚の原料ウエハからより多くの単結晶半導体層を形成することができるため、好ましい。市場に流

50

通している単結晶シリコンウエハの厚さとそのサイズは SEMI 規格に準じており、例えば直径 6 インチのウエハは膜厚 625  $\mu\text{m}$ 、直径 8 インチのウエハは膜厚 725  $\mu\text{m}$ 、直径 12 インチのウエハは膜厚 775  $\mu\text{m}$  とされている。なお、SEMI 規格のウエハの厚さは公差  $\pm 25 \mu\text{m}$  を含んでいる。もちろん、原料となる単結晶半導体基板の厚さは SEMI 規格に限定されず、インゴットをスライスするときに、その厚さを適宜調節することができる。もちろん、再利用された単結晶半導体基板を用いるときには、その厚さは、SEMI 規格よりも薄くなる。

#### 【 0133 】

バッファ層 102 は、1 層または 2 層以上の膜で形成することができる。バッファ層 102 としては、十分な平坦性が得られるのであれば、PECVD 法またはスパッタ法により得られる酸化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、窒化珪素膜、酸化ゲルマニウム膜、窒化ゲルマニウム膜、酸化窒化ゲルマニウム膜、窒化酸化ゲルマニウム膜などのシリコンまたはゲルマニウムを組成に含む絶縁膜を用いることができる。また、バッファ層 102 としてプロセスガスに有機シランガスと酸素を用いて、PECVD 法で形成される酸化珪素膜を用いてもよい。また、熱酸化により得られる熱酸化膜を用いることもできる。ただし、熱酸化により得られる熱酸化膜はウエハの表面及び裏面および端面を含む表面に形成される。

10

#### 【 0134 】

また、バッファ層 102 として酸化アルミニウム、酸化タンタル、酸化ハフニウムなどの金属の酸化物でなる絶縁膜、窒化アルミニウムなどの金属の窒化物でなる絶縁膜、酸化窒化アルミニウム膜などの金属の酸化窒化物でなる絶縁膜、窒化酸化アルミニウム膜などの金属の窒化酸化物でなる絶縁膜を用いることもできる。

20

#### 【 0135 】

なお、本明細書において、酸化窒化物とは、その組成として、窒素原子よりも酸素原子の数が多い物質とし、また、窒化酸化物とは、その組成として、酸素原子よりも窒素原子の数が多い物質とする。なお、酸化窒化シリコン膜とは、その組成として、窒素よりも酸素の含有量が多いものであって、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、Si が 2.5 ~ 3.5 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれるものという。また、窒化酸化シリコン膜とは、その組成として、酸素よりも窒素の含有量が多いものであって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 2.0 ~ 5.5 原子%、Si が 2.5 ~ 3.5 原子%、水素が 1.0 ~ 3.0 原子% の範囲で含まれるものという。但し、酸化窒化シリコンまたは窒化酸化シリコンを構成する原子の合計を 100 原子% としたとき、窒素、酸素、Si 及び水素の含有比率が上記の範囲内に含まれるものとする。

30

#### 【 0136 】

本実施例では、バッファ層 102 として PECVD 法により得られる酸化珪素膜 (膜厚 100 nm) と、その上に窒化珪素膜 (膜厚 50 nm) を積層した 2 層構造を用いる。なお、半導体ウエハ 101 上に接して窒化珪素膜を形成することは、後に形成されるトランジスタの特性上望ましくないため、間に酸化珪素膜を設ける。また、窒化珪素膜に代えて窒化酸化珪素膜を用いてもよい。

40

#### 【 0137 】

また、バッファ層 102 の少なくとも 1 層として窒化珪素膜、窒化酸化珪素膜などの窒化酸化物を用いる場合、バッファ層 102 の膜応力により生ずる Si の格子歪を利用してバッファ層 102 上に高い電子移動度を有するトランジスタを作製することができる。

#### 【 0138 】

ここまで段階を示す工程断面図が図 12 (A) に相当する。

#### 【 0139 】

50

次いで、イオンドーピング装置を用いてバッファ層 102 を介して半導体ウエハ 101 中に  $H_3^+$  イオンの照射を行う。このドーピングの条件は、電源出力 100W、加速電圧 35 kV、ドーズ量は  $2.2 \times 10^{16}$  ions /  $cm^2$  とする。イオンドーピング装置は、イオンの添加分布を均一化するために半導体ウエハ 101 を回転させている。この  $H_3^+$  イオンの照射により水素を多く含む分離層 103 が形成される。また、分離層 103 とバッファ層 102 との間には、単結晶半導体層 104 が形成される。ここまで段階を示す工程断面図が図 12 (B) に相当する。この単結晶半導体層 104 の膜厚は、分離層 103 の深さ方向の位置により決定される。従って、単結晶半導体層 104 の膜厚は、 $H_3^+$  イオンのドーピング条件 ( 加速電圧など ) に依存する。照射される水素イオン種の全体における  $H_3^+$  イオンの割合を高めておくと効率を高めることができ、照射時間を短縮することができる。

10

## 【0140】

次いで、バッファ層 102 が形成された半導体ウエハ 101 を純水中で超音波洗浄する。

## 【0141】

次いで、バッファ層 102 の表面を清浄化した後、ガラス基板 105 の一方の面とバッファ層 102 の表面とを密接させ、少なくとも一箇所を外部から軽く押しつけると、局所的に接合面同士の距離が縮まる事によって、ファン・デル・ワールス力が強まり、さらに水素結合も寄与し、お互いに引きつけ合い、半導体ウエハ 101 とガラス基板 105 とが接着する。更に、隣接した領域でも対向する基板間の距離が縮まるので、ファン・デル・ワールス力が強く作用する領域や水素結合が関与する領域が広がる事によって、ボンディングが進行し接合面全域に接合が広がる。なお、接合を形成するガラス基板 105 の一方の面は、十分に清浄化しておく。

20

## 【0142】

また、半導体ウエハ 101 のバッファ層が形成されている面とガラス基板 105 の一方の面とを密接させる前にオゾンを含む純水で洗浄してもよい。

## 【0143】

また、半導体ウエハ 101 のバッファ層が形成されている面とガラス基板 105 の一方の面とを密接させる前に半導体ウエハ 101 上にバッファ層の一層となる絶縁膜をさらに形成してもよい。また、半導体ウエハ 101 のバッファ層が形成されている面とガラス基板 105 の一方の面とを密接させる前にガラス基板 105 上にバッファ層の一層となる絶縁膜をさらに形成してもよい。

30

## 【0144】

半導体ウエハ 101 とガラス基板 105 とをバッファ層 102 を介して貼り合わせた後は、加熱処理又は加圧処理を行うことが好ましい。加熱処理又は加圧処理を行うことで接合強度を向上させることができるとなる。ここで加熱温度は、分離層 103 に添加した元素または分子が析出しない温度とし、その加熱温度は 350 以下が好ましい。言い換えると、この加熱温度は分離層 103 からガスが抜けない温度である。加圧処理を行う場合は、接合面に垂直な方向に圧力が加わるように行い、半導体ウエハ 101 及びガラス基板 105 の耐圧性を考慮して行う。

40

## 【0145】

ここまで段階を示す工程断面図が図 12 (C) に相当する。

## 【0146】

次いで、400 乃至 600 の加熱処理を行うことにより、分離層 103 に形成された微小な空洞の体積変化が起こり、分離層 103 に沿って劈開する。ここで加熱処理には、RTA ( Rapid Thermal Anneal ) 装置、抵抗加熱炉、マイクロ波加熱装置を用いることができる。RTA 装置には、GRTA ( Gas Rapid Thermal Anneal ) 装置、LRTA ( Lamp Rapid Thermal Anneal ) 装置を用いることができる。この加熱処理で、単結晶半導体層 104 が貼り付けられたガラス基板 105 の温度を 550 以上 650 以下の範囲に上昇させることができると好ましい。

50

## 【0147】

本実施例では、抵抗加熱を有する縦型炉を用いた加熱処理を行う。半導体ウエハ101が貼り付けられたガラス基板105を縦型炉のポートに載置する。ポートを縦型炉のチャンバーに搬入する。半導体ウエハ101の酸化を抑制するため、まずチャンバー内を排気して真空状態とする。真空度は、 $5 \times 10^{-3}$  Pa程度とする。真空状態にした後、窒素をチャンバー内に供給して、チャンバー内を大気圧の窒素雰囲気にする。この間、温度を200に上昇させる。

## 【0148】

チャンバー内を大気圧の窒素雰囲気にした後、温度200で2時間加熱する。その後、1時間かけて400に温度上昇させる。加熱温度400の状態が安定したら、1時間かけて600に温度上昇させる。加熱温度600の状態が安定したら、600で2時間加熱処理する。その後、1時間かけて、加熱温度400まで下げ、10分～30分間後に、チャンバー内からポートを搬出する。大気雰囲気下で、ポート上の半導体ウエハ101、および半導体ウエハ101が貼り付けられたガラス基板105を冷却する。

10

## 【0149】

上記の抵抗加熱炉を用いた加熱処理は、半導体ウエハ101とガラス基板105との結合力を強化するための加熱処理と、分離層103の層内または界面に分離を生じさせる加熱処理が連続して行われる。この2つの加熱処理を異なる装置で行う場合は、例えば、抵抗加熱炉において、処理温度200、処理時間2時間の加熱処理を行った後、貼り合わされたガラス基板105と半導体ウエハ101を炉から搬出する。次いで、RTA装置で、処理温度600以上ガラス基板105の歪み点以下、処理時間1分以上30分以下の加熱処理を行い、半導体ウエハ101を分離層103で分離させる。

20

## 【0150】

700以下の低温処理で、半導体ウエハ101とガラス基板105を強固に接合させた場合には、バッファ層102の表面、およびガラス基板105の表面にOH基、水分子(H<sub>2</sub>O)が存在することが好ましい。これは、バッファ層102とガラス基板105との接合が、OH基や水分子が共有結合(酸素分子と水素分子の共有結合)や水素結合を形成することで開始するからである。

30

## 【0151】

以上の工程を経ることによって、図12(D)に示すSOI基板を得ることができる。図12(D)に示すSOI基板は、ガラス基板105上にバッファ層102を有し、そのバッファ層102上に単結晶半導体層104を有する構造である。単結晶半導体層104は、厚さを100nmまたはそれ以下とするとできる。単結晶半導体層104の厚さを100nmまたはそれ以下とすると、トランジスタのチャネル形成領域の空乏層の最大深さより薄くなり、顕著なトランジスタの電気特性をもたらす。トランジスタの十分な空乏層化によりほとんど理想的なS値、しきい値電圧などを得ることができる。さらに、CMOS構造を作製した場合、速いスイッチング速度を得ることができる。

30

## 【0152】

次いで、単結晶半導体層104の平坦性を向上させる処理または結晶性を回復させる処理を行う。平坦性を向上させる処理として、化学機械研磨(Chemical Mechanical Polishing、略称: CMP)またはレーザ光の照射を行う。なお、レーザビームを照射する場合には、照射前にエッチング処理を単結晶半導体層104の表面に行なうことが好ましい。

40

## 【0153】

次いで、単結晶半導体層104を選択的にエッチングして島状の半導体層106を形成し、島状の半導体層106を覆うゲート絶縁膜107を形成する。ここまで断面図を図12(E)に示す。ゲート絶縁膜は、実施例1または実施例2と同様に高密度プラズマ装置を用いて形成する。高密度プラズマ装置を用いて膜厚10nmの絶縁膜を成膜した後、高密度プラズマ装置を用いてプラズマ処理を行う。高密度プラズマを用いた処理により、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶

50

縁膜が形成される。

【0154】

本実施例では、ゲート絶縁膜107の膜厚を10nmとする例を説明したが、特にこの膜厚に限定されず、10nmよりも厚く100nm未満の膜厚であっても、均一性が良く、界面準位密度が低い絶縁膜が得られる。

【0155】

次いで、ゲート絶縁膜107上に島状の半導体層106と重なるゲート電極を形成する。そしてこのゲート電極を用いる薄膜トランジスタを形成する。次いで薄膜トランジスタと電気的に接続する発光素子1605を形成し、封止を行うことで、図13に示す発光表示装置が作製できる。

10

【0156】

図13の発光表示装置は、図13中に示す矢印の方向に発光を上面射出する構造である。図13に示す発光表示装置は、ガラス基板105、バッファ層102、薄膜トランジスタ1655、薄膜トランジスタ1665、薄膜トランジスタ1675、薄膜トランジスタ1685、配線層1624、第1の電極層1617、発光層1619、第2の電極層1620、透明導電膜1621、充填材1622、シール材1632、ゲート絶縁膜107、絶縁膜1611、絶縁膜1612、絶縁層1614、封止基板1625、配線層1633、端子電極層1681、異方性導電層1682、FPC1683によって構成されている。

【0157】

図13において半導体装置は、外部端子接続領域282、封止領域283、駆動回路領域284、画素領域286を有している。第1の電極層1617の下に、反射性を有する金属層である配線層1624を形成する。配線層1624の上に透明導電膜である第1の電極層1617を形成する。配線層1624としては、反射性を有すればよいので、チタン、タンゲステン、ニッケル、金、白金、銀、銅、タンタル、モリブデン、アルミニウム、マグネシウム、カルシウム、リチウム、およびそれらの合金からなる導電膜などを用いればよい。好ましくは、可視光の領域で反射性が高い物質を用いることがよい。また、第1の電極層1617にも導電膜を用いてもよく、その場合、反射性を有する配線層1624は設けなくてもよい。

20

【0158】

第1の電極層1617及び第2の電極層1620に、具体的には透光性を有する導電性材料からなる透明導電膜を用いればよく、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いることができる。

30

【0159】

また、透光性を有さない金属膜のような材料であっても膜厚を薄く(好ましくは、5nm～30nm程度の厚さ)して光を透過可能な状態としておくことで、第1の電極層1617、第2の電極層1620から光を放射することが可能となる。また、第1の電極層1617、第2の電極層1620に用いることのできる金属薄膜としては、チタン、タンゲステン、ニッケル、金、白金、銀、アルミニウム、マグネシウム、カルシウム、リチウム、およびそれらの合金からなる導電膜などを用いることができる。

40

【0160】

封止基板にカラーフィルタ(着色層)を形成してもよい。カラーフィルタ(着色層)は、蒸着法や液滴吐出法によって形成することができ、カラーフィルタ(着色層)を用いると、高精細な表示を行うこともできる。カラーフィルタ(着色層)により、各RGBの発光スペクトルにおいてブロードなピークが鋭いピークになるように補正できるからである。

【0161】

単色の発光を示す材料を形成し、カラーフィルタや色変換層を組み合わせることによりフルカラー表示を行うことができる。カラーフィルタ(着色層)や色変換層は、例えば封止

50

基板に形成し、ガラス基板 105 へ貼り合わせればよい。

【0162】

もちろん単色発光の表示を行ってもよい。例えば、単色発光を用いてエリアカラータイプの半導体装置を形成してもよい。エリアカラータイプは、パッシブマトリクス型の表示部が適しており、主に文字や記号を表示することができる。

【0163】

単結晶半導体層を用いることにより、画素領域と駆動回路領域を同一基板上に一体形成することができる。その場合、画素領域のトランジスタと、駆動回路領域のトランジスタとは同時に形成される。

【0164】

また、高密度プラズマ装置を用いたゲート絶縁膜を用いることで、ゲート絶縁膜の薄膜化を実現でき、且つ、薄膜トランジスタに単結晶半導体層を用いるため、低消費電力での駆動が可能である発光表示装置を提供することができる。

10

【0165】

本実施例は、実施の形態、実施例 1、実施例 2 と自由に組み合わせることができる。

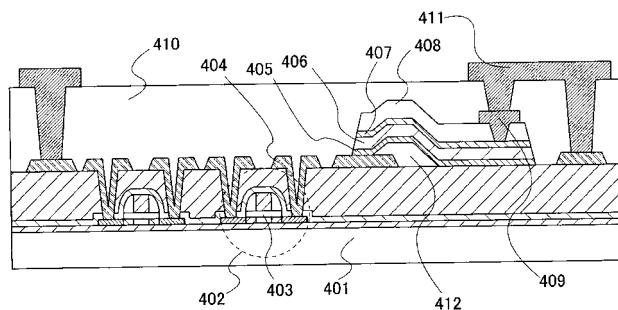

【実施例 4】

【0166】

本実施例では、薄膜トランジスタとフォトダイオードを用いた光電変換装置の例を図 14 を用いて説明する。

20

【0167】

本実施例で示す光電変換装置は、薄膜トランジスタで構成される増幅回路とフォトダイオードを同一基板上に一体形成している。

【0168】

ガラス基板 401 上に薄膜トランジスタ 402 を形成する。なお、薄膜トランジスタのゲート絶縁膜 403 は、実施例 1 または実施例 2 と同様に高密度プラズマ装置を用いて形成する。高密度プラズマ装置を用いて膜厚 20 nm の絶縁膜を成膜した後、高密度プラズマ装置を用いてプラズマ処理を行う。高密度プラズマを用いた処理により、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低いゲート絶縁膜 403 が形成される。

30

【0169】

本実施例では、ゲート絶縁膜 403 の膜厚を 20 nm とする例を説明したが、特にこの膜厚に限定されず、20 nm よりも厚く 100 nm 未満の膜厚であっても、均一性が良く、界面準位密度が低いゲート絶縁膜 403 が形成される。

40

【0170】

次いで、薄膜トランジスタ 402 に接続する電極を形成する。電極は導電性材料であればよいが、後に形成する光電変換層（代表的にはアモルファスシリコン）と反応して合金になりにくい導電性の金属膜を用いることが望ましい。次に、電極の端部がテーパー形状になるようにエッチングして、電極 404 を形成する。このとき、テーパー角は 80 度以下、望ましくは 45 度以下になるように形成する。これにより、後に形成する光電変換層のカバレッジがよくなり、信頼性向上ができる。また、電極 404 の端部と重なる絶縁物 412 を形成する。

【0171】

次に、p 型半導体膜を形成する。本実施例では p 型半導体膜として、例えば p 型アモルファス半導体膜を形成する。p 型アモルファス半導体膜として、周期表第 13 族の不純物元素、例えばボロン (B) を含んだアモルファスシリコン膜をプラズマ CVD 法にて成膜する。

【0172】

p 型半導体膜を形成したら、さらに導電型を付与する不純物を含まない半導体膜である i 型半導体膜（真性半導体膜ともいう。）及び n 型半導体膜を順に形成する。本実施例では、p 型半導体膜を 10 ~ 50 nm、i 型半導体膜を 200 ~ 1000 nm、n 型半導体

50

膜を 20 ~ 200 nm の膜厚で形成する。

【 0173 】

i 型半導体膜としては、例えばプラズマ CVD 法でアモルファスシリコン膜を形成すればよい。また n 型半導体膜としては、15 属の不純物元素、例えばリン (P) を含むアモルファスシリコン膜を形成してもよいし、アモルファスシリコン膜を形成後、15 属の不純物元素を導入してもよい。

【 0174 】

なお p 型半導体膜、i 型半導体膜及び n 型半導体膜は、逆の順番で積層されていてもよく、すなわち n 型半導体膜、i 型半導体膜及び p 型半導体膜の順で積層してもよい。

【 0175 】

次に、絶縁膜 408、電極 409 をスクリーン印刷法で形成する。もしくは、インクジェット法で形成してもよいし、全面に形成し、フォトリソグラフィーにて、所望の形状を作製しても良い。本実施例では、絶縁膜 408 はエポキシ樹脂、電極 409 はニッケル (Ni) を用いる。なお、ニッケル (Ni) をスクリーン印刷法で形成するときには、それを含む導電ペーストを用いる。

【 0176 】

次に、絶縁膜 408 と電極 409 をマスクとして、p 型半導体膜、i 型半導体膜及び n 型半導体膜をエッティングし、p 型半導体層 405、i 型半導体層 406 及び n 型半導体層 407 を形成する。このエッティングのときのオーバーエッティングにより、電極 404 の膜もエッティングされる場合があり、導電性の低下などの問題がおきるため、電極 404 と、p 型半導体膜と i 型半導体膜及び n 型半導体膜とのエッティング選択比は大きくしておくことが望ましい。

【 0177 】

次に、絶縁膜 410、電極 411 をスクリーン印刷法で形成する。本実施例では、絶縁膜 410 はエポキシ樹脂を用い、電極 411 は半田とのぬれ性向上と実装時の強度向上のため、ニッケル (Ni) と銅 (Cu) の積層構造とする。

【 0178 】

光がガラス基板 401 側から入射する場合、薄膜トランジスタ 402 を構成する複数の屈折率の異なる絶縁膜の膜厚を調整することで、光を干渉させて、光電変換層へ入射する光の波長分布を制御することができる。人間の視感度へできるだけ近づけるように調整すると、精度の良い可視光センサとして用いることができる。

【 0179 】

この光電変換装置は、フォトダイオードの出力を増幅する増幅回路を備えている。増幅回路としてはさまざまな回路構成を適用することができるが、本実施例では複数の薄膜トランジスタでカレントミラー回路を構成している。フォトダイオードは、p-n 接合、p-i-n 接合若しくはそれと同等な機能を備えたものであれば良い。フォトダイオードの陽極 (p 層側) は薄膜トランジスタのドレイン端子と接続し、陰極 (n 層側) は出力端子と接続している。

【 0180 】

フォトダイオードに光が照射されると、陰極 (n 層側) から陽極 (p 層側) に光電流が流れる。これによって、増幅回路の薄膜トランジスタに電流が流れ、その電流を流すのに必要な電圧がゲートに発生する。

【 0181 】

また、高密度プラズマ装置を用いたゲート絶縁膜を用いることで、ゲート絶縁膜の薄膜化を実現できる。

【 0182 】

本実施例は、実施の形態、実施例 1、実施例 2 と自由に組み合わせることができる。

【 実施例 5 】

【 0183 】

本実施例では、容量素子及びトランジスタに加え、メモリ素子を同一基板上に形成し、ア

10

20

30

40

50

ンテナ回路を含む半導体装置を作製する例を図15を用いて説明する。

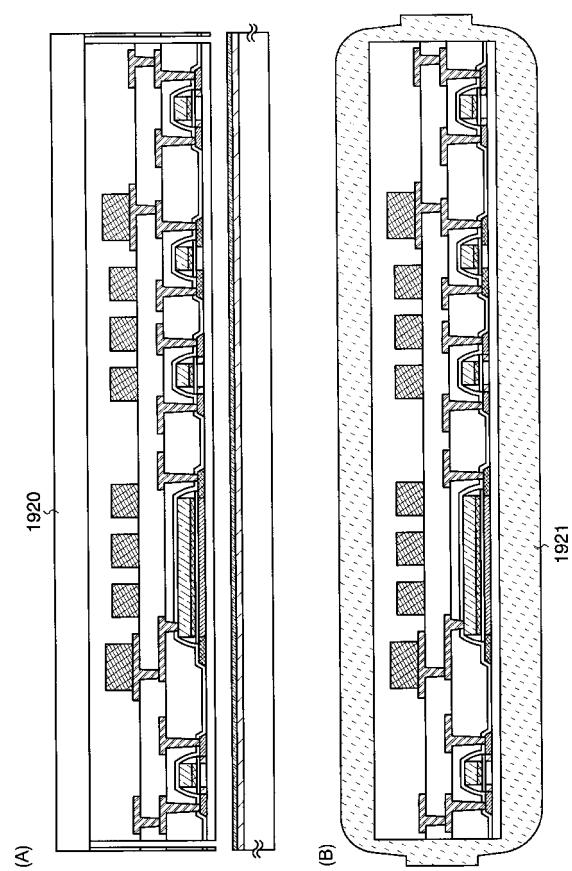

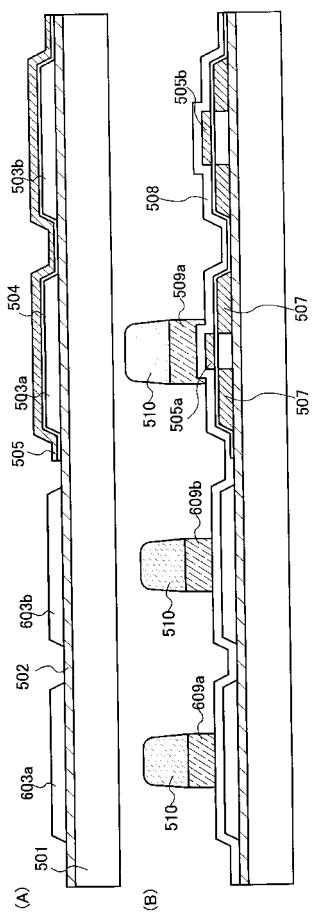

【0184】

まず、基板501の一表面に絶縁膜502を介して、島状の半導体膜503a、503b、603a、603bを形成する。なお、半導体膜503aは後に形成されるメモリ素子を構成し、半導体膜503bは後に形成される容量素子を構成し、半導体膜603a、603bは後に形成される薄膜トランジスタを構成する。

【0185】

次に、半導体膜503a、503b、603a、603bを覆うように絶縁膜504を形成する。絶縁膜504は、高密度プラズマ装置を用いて膜厚10nmの絶縁膜を成膜した後、高密度プラズマ装置を用いてプラズマ処理を行う。その後、当該絶縁膜504を覆うように導電膜を形成する。

10

【0186】

なお、半導体膜503a、603a、603bにしきい値等を制御するため、あらかじめ低濃度の不純物元素を導入しておいてもよい。この場合は、半導体膜503a、603a、603bにおいて、後にチャネル形成領域となる領域にも不純物元素が導入されることとなる。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いることができる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、不純物元素として、ボロン(B)を $5 \times 10^{15} \sim 5 \times 10^{17} / \text{cm}^3$ の濃度で含まれるように半導体膜503a、603a、603bの全面にあらかじめ導入する。

20

【0187】

次に、半導体膜603a、603bの上方に設けられた導電膜を選択的に除去した後、露呈した絶縁膜も選択的に除去する(図15(A)参照)。なお、半導体膜503a、503bの上方には導電膜505及び絶縁膜504を残存させる。

30

【0188】

次に、残存した導電膜505上に選択的にレジストを形成し、半導体膜603a、603bを覆うようにレジストを形成した後、当該レジストをマスクとして残存した導電膜505をさらに選択的にエッチングして、半導体膜503a上に導電膜505a、半導体膜503b上に導電膜505bを残存させる。続いて、当該レジストをマスクとして、半導体膜503a、503bに不純物元素を導入し、半導体膜503a、503bに不純物領域507を形成する。

【0189】

導入する不純物元素は、n型の不純物元素又はp型の不純物元素を用いる。n型の不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型の不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、半導体膜503a、503bにリン(P)を導入し、不純物領域507としてn型の不純物領域を形成する場合について示す。

【0190】

次に、レジストを除去した後、半導体膜603a、603b、導電膜505a、505bを覆うように絶縁膜508を形成する。絶縁膜508は、高密度プラズマ装置を用いて膜厚40nmの絶縁膜を成膜した後、高密度プラズマ装置を用いてプラズマ処理を行う。その後、当該絶縁膜508上に導電膜を形成する。

40

【0191】

次に、導電膜上に選択的にレジスト510を形成し、当該レジスト510をマスクとして導電膜を選択的にエッチングして、半導体膜503a、603a、603b上にそれぞれ導電膜509a、609a、609bを残存させる。半導体膜503b上に形成された導電膜は除去する(図15(B)参照)。

【0192】

次に、レジスト510を除去した後、半導体膜503a、603bを覆うようにレジスト

50

を形成し、当該レジスト、導電膜 609a をマスクとして、半導体膜 603a、503b に不純物元素を導入する。半導体膜 603a には、導電膜 609a と重ならない領域に不純物元素が導入され、不純物領域 611 が形成される。半導体膜 503b には、導電膜 505b を突き抜けて全面に不純物元素が導入され、不純物領域 512b と、導電膜 505b と重なる不純物領域 512a とが形成される。

【0193】

なお、導入する不純物元素は、n 型の不純物元素又は p 型の不純物元素を用いる。ここでは、半導体膜 603a、503b に高濃度の p 型不純物元素のボロン (B) 等の元素 (質量の軽い元素) を導入し、p 型の不純物元素が添加されている不純物領域 611、512a、512b を形成する場合について示している。絶縁膜 508、導電膜 505、絶縁膜 504 を介して半導体膜 503b に不純物元素の導入を行う場合、ボロン (B) 等の元素 (質量の軽い元素) を用いることにより絶縁膜 504 に加わるダメージを低減することができる。

10

【0194】

次に、レジストを除去した後、半導体膜 503b、603a を覆うようにレジストを形成し、当該レジスト、導電膜 509a、609b をマスクとして、半導体膜 503a、603b に不純物元素を導入する。半導体膜 503a には、導電膜 509a と重ならない領域に不純物元素が導入され、不純物領域 511 が形成される。半導体膜 603b には、導電膜 609b と重ならない領域に不純物元素が導入され、不純物領域 612 が形成される。

20

【0195】

導入する不純物元素は、n 型の不純物元素又は p 型の不純物元素を用いる。ここでは、半導体膜 503a、603b に高濃度のリン (P) を導入し、n 型の不純物領域 511、612 を形成する場合について示す。

【0196】

次に、導電膜 509a、609a、609b、絶縁膜 508 を覆うように絶縁膜 513 を形成した後、半導体膜 503a の不純物領域 511、半導体膜 503b の不純物領域 512b、半導体膜 603a の不純物領域 611、半導体膜 603b の不純物領域 612 に電気的に接続された導電膜 514 をそれぞれ形成する。

【0197】

以上の工程により、メモリ素子 520、容量素子 521、薄膜トランジスタ 620、621 を有する半導体装置を得ることができる。

30

【0198】

次いで、絶縁膜 513、導電膜 514 を覆うように絶縁膜 702 を形成し、当該絶縁膜 702 上にアンテナとして機能する導電膜 703 を形成する (図 15 (C) 参照)。

【0199】

絶縁膜 702 は、スパッタ法、CVD 法、SOG 法、液滴吐出法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ、シロキサン等の有機材料等で形成する。

【0200】

導電膜 703 は、CVD 法、スパッタ法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム (Al)、チタン (Ti)、銀 (Ag)、銅 (Cu)、金 (Au)、白金 (Pt)、ニッケル (Ni)、パラジウム (Pd)、タンタル (Ta)、モリブデン (Mo) から選択された元素、又はこれらの元素を主成分とする合金材料若しくは化合物材料で、単層構造又は積層構造で形成する。

40

【0201】

以上に示す工程で無線チップを作製することができる。

【0202】

また、高密度プラズマ装置を用いた絶縁膜 504 を用いることで、容量素子 521 の容量の増大を図ることができ、メモリ素子 520 へのデータ書き込み、またはデータ消去を低

50

電力で行うことができる。また、高密度プラズマ装置を用いた絶縁膜 508 を用いることで、薄膜トランジスタ 620、621 を有する駆動回路の高速駆動を可能とすることができる。

【0203】

本実施例では、絶縁膜 504 の膜厚を 10 nm とし、絶縁膜 508 の膜厚を 40 nm とする例を説明したが、特にこれらの膜厚に限定されず、10 nm よりも厚く 100 nm 未満の膜厚であればよい。

【0204】

本実施例は、実施の形態と自由に組み合わせることができる。

10

【実施例 6】

【0205】

実施の形態により集積回路を有するチップ（以下、プロセッサチップ、無線チップ、無線プロセッサ、無線メモリ、無線タグともよぶ）として機能する半導体装置を形成することができる。実施の形態の作製方法で得られる半導体装置の用途は広範にわたるが、例えば、紙幣、硬貨、有価証券類、証書類、無記名債券類、包装用容器類、書籍類、記録媒体、身の回り品、乗物類、食品類、衣類、保健用品類、生活用品類、薬品類及び電子機器等に設けて使用することができる。

【0206】

例えば、実施例 1 や実施例 5 に従って TFT を有する集積回路を形成し、無線チップを作製することができる。

20

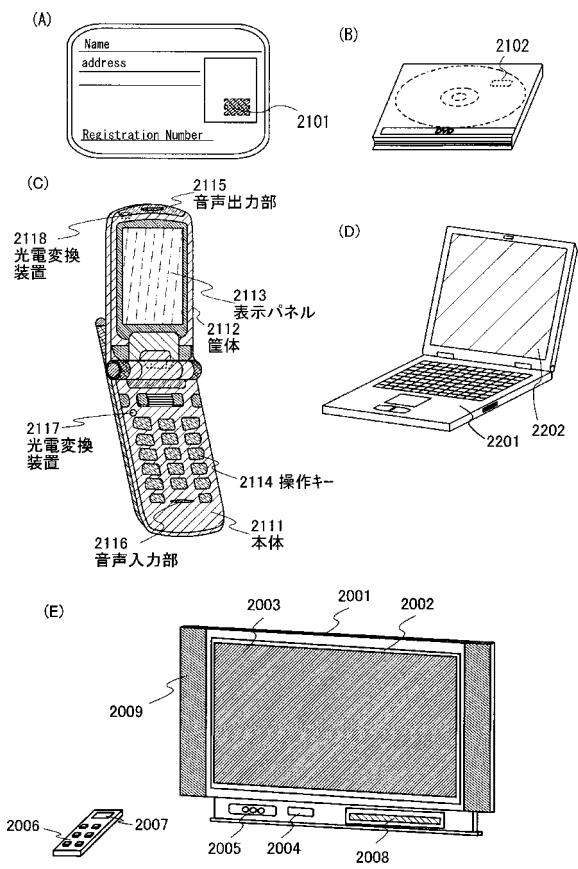

【0207】

紙幣、硬貨とは、市場に流通する金銭であり、特定の地域で貨幣と同じように通用するもの（金券）、記念コイン等を含む。有価証券類とは、小切手、証券、約束手形等を指し、無線チップを設けることができる。証書類とは、運転免許証、住民票等を指し、無線チップ 2101 を設けることができる（図 16（A）参照）。

【0208】

身の回り品とは、鞄、眼鏡等を指し、無線チップを設けることができる。無記名債券類とは、切手、おこめ券、各種ギフト券等を指す。包装用容器類とは、お弁当等の包装紙、ペットボトル等を指し、無線チップを設けることができる。書籍類とは、書物、本等を指し、無線チップを設けることができる。記録媒体とは、DVD ソフト、ビデオテープ等を指し、無線チップ 2102 を設けることができる（図 16（B）参照）。

30

【0209】

食品類とは、食料品、飲料等を指す。衣類とは、衣服、履物等を指す。保健用品類とは、医療器具、健康器具等を指す。生活用品類とは、家具、照明器具等を指す。薬品類とは、医薬品、農薬等を指す。電子機器とは、液晶表示装置、EL 表示装置、テレビジョン装置（テレビ受像機、薄型テレビ受像機）、携帯電話等を指す。

【0210】

実施の形態の作製方法により得られる半導体装置は、プリント基板に実装する、表面に貼る、または埋め込む等により、物品に固定される。例えば、本の場合には紙に半導体装置を埋め込む、または有機樹脂からなるパッケージの場合には当該有機樹脂に半導体装置を埋め込むなどして、各物品に固定される。実施の形態の作製方法により得られる半導体装置は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に実施の形態の作製方法により得られる半導体装置を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。

40

【0211】

また、実施の形態の作製方法により得られる半導体装置を携帯電話機に用いる例を図 16（C）に示す。図 16（C）において、本体 2111 は、筐体 2112、表示パネル 2113、操作キー 2114、音声出力部 2115、音声入力部 2116、光電変換装置 2117、2118 を含んでいる。例えば、光電変換装置 2117、2118 は、実施例 4 に

50

従って得ることができる。

【0212】

図16(C)に示す携帯電話では、本体2111に設けられた光電変換装置2117により外部の光を検知することにより表示パネル2113及び操作キー2114の輝度を制御することができる。また、本体2111の内部に光電変換装置2118を設けている。光電変換装置2118により、表示パネル2113に設けられているバックライトの輝度を検出することも可能となる。光電流を增幅して電圧出力として取り出す回路を備えた光電変換装置が携帯電話機に用いられているので、回路基板に実装する部品点数を削減することができ、携帯電話機本体の小型化を図ることができる。また、回路と光電変換装置を同一基板上に形成できるため、ノイズを低減することができる。

10

【0213】

また、表示パネル2113として、例えば液晶パネルを用いた場合、実施例2に従って得ることもできる。

【0214】

また、表示パネル2113として、例えば発光表示パネルを用いた場合、実施例3に従って得ることもできる。

【0215】

また、図16(D)に示す携帯型のコンピュータは、本体2201、表示部2202等を含んでいる。表示部2202に、実施例2または実施例3に示す表示装置を適用することにより、消費電力の低減を図ることができる。

20

【0216】

また、図16(E)はテレビジョン装置である。実施例2または実施例3に示す表示装置を、図16(E)に示すように、筐体に組みこんで、テレビジョン装置を完成させることができる。FPCまで取り付けられた表示パネルのことを表示モジュールとも呼ぶ。表示モジュールにより主画面2003が形成され、その他付属設備としてスピーカー部2009、操作スイッチなどが備えられている。このように、テレビジョン装置を完成させることができる。

【0217】

図16(E)に示すように、筐体2001に表示素子を利用した表示用パネル2002が組み込まれ、受信機2005により一般的なテレビ放送の受信をはじめ、モデム2004を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者から受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることもできる。テレビジョン装置の操作は、筐体に組み込まれたスイッチ又は別体のリモコン操作機2006により行うことが可能であり、このリモコン装置にも出力する情報を表示する表示部2007が設けられていても良い。

30

【0218】

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構成において、主画面2003を実施例2に示す液晶表示パネルで形成し、サブ画面2008を実施例3に示した低消費電力で表示可能な発光表示パネルで形成しても良い。また、低消費電力化を優先させるためには、主画面2003を発光表示パネルで形成し、サブ画2008面を発光表示パネルで形成し、サブ画面2008は点滅可能とする構成としても良い。

40

【0219】

勿論、実施の形態の作製方法により得られる半導体装置はテレビジョン装置に限定されず、パーソナルコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積の表示媒体としても様々な用途に適用することができる。

【産業上の利用可能性】

【0220】

50

大面積基板であるガラス基板上に膜厚が均一な絶縁膜を作製することができ、半導体装置1つ当たりの製造コストを削減することができる。

## 【符号の説明】

## 【0 2 2 1】

|                 |            |    |

|-----------------|------------|----|

| 1 0 1           | 半導体ウエハ     | 10 |

| 1 0 2           | バッファ層      |    |

| 1 0 3           | 分離層        |    |

| 1 0 4           | 単結晶半導体層    |    |

| 1 0 5           | ガラス基板      |    |

| 1 0 6           | 島状の半導体層    |    |

| 1 0 7           | ゲート絶縁膜     |    |

| 1 8 0           | 処理容器       |    |

| 1 8 1           | 支持台        |    |

| 1 8 2           | ガス供給部      |    |

| 1 8 3           | 排気口        |    |

| 1 8 4           | マイクロ波発生装置  |    |

| 1 8 5           | 導波管        |    |

| 1 8 6           | 誘電体板       |    |

| 1 8 7           | 天板         |    |

| 1 8 8           | 取り付け具      | 20 |

| 1 9 1           | 原料ガス供給源    |    |

| 1 9 2           | 着火用ガス供給源   |    |

| 1 9 3           | 質量流量コントローラ |    |

| 1 9 4           | 質量流量コントローラ |    |

| 1 9 5           | バルブ        |    |

| 1 9 6           | バルブ        |    |

| 1 9 7           | ガス管        |    |

| 1 9 8           | ガス管        |    |

| 1 9 9           | 温度制御部      |    |

| 2 0 0           | プラズマ       | 30 |

| 2 8 2           | 外部端子接続領域   |    |

| 2 8 3           | 封止領域       |    |

| 2 8 4           | 駆動回路領域     |    |

| 2 8 6           | 画素領域       |    |

| 4 0 1           | ガラス基板      |    |

| 4 0 2           | 薄膜トランジスタ   |    |

| 4 0 3           | ゲート絶縁膜     |    |

| 4 0 4           | 電極         |    |

| 4 0 7           | n型半導体層     |    |

| 4 0 8           | 絶縁膜        | 40 |

| 4 0 9           | 電極         |    |

| 4 1 0           | 絶縁膜        |    |

| 4 1 1           | 電極         |    |

| 4 1 2           | 絶縁物        |    |

| 5 0 1           | 基板         |    |

| 5 0 2           | 絶縁膜        |    |

| 5 0 3 a、5 0 3 b | 島状の半導体膜    |    |

| 5 0 4           | 絶縁膜        |    |

| 5 0 5 a、5 0 5 b | 導電膜        |    |

| 5 0 7           | 不純物領域      | 50 |

5 0 8 : 絶縁膜

5 0 9 a : 導電膜

5 1 0 : レジスト

5 1 1 : n 型の不純物領域

5 1 2 a : 不純物領域

5 1 2 b : 不純物領域

5 1 4 : 導電膜

5 2 0 : メモリ素子

5 2 1 : 容量素子

6 0 3 a 、 6 0 3 b : 島状の半導体膜

10

6 0 9 a 、 6 0 9 b : 導電膜

6 1 1 : 不純物領域

6 1 2 : n 型の不純物領域

6 2 0 、 6 2 1 : 薄膜トランジスタ

7 0 2 : 絶縁膜

7 0 3 : 導電膜

1 1 1 0 ロード・アンロード (L / UL) 室

1 1 2 0 共通室

1 1 2 1 搬送手段

1 1 2 2 ゲート弁

1 1 2 8 カセット

1 1 3 0 基板

20

【図1】

【図2】

【図3】

【図4】

【図5】

(B)

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 15】

【図 16】

---

フロントページの続き

(72)発明者 大槻 高志

神奈川県厚木市長谷3 9 8 番地 株式会社半導体エネルギー研究所内

(72)発明者 保本 清治

栃木県下都賀郡都賀町大字升塚1 6 1 - 2 アドバンスト フィルム ディバイス インク株会

社内

(72)発明者 山崎 舜平

神奈川県厚木市長谷3 9 8 番地 株式会社半導体エネルギー研究所内

F ターム(参考) 5F058 BA01 BA06 BA11 BC02 BC04 BD04 BD06 BF08 BF23 BF29

BH02 BH03 BH16 BJ04

5F110 AA30 BB01 BB04 CC07 DD01 DD02 DD03 DD13 DD14 DD15

DD17 EE01 EE02 EE03 EE04 EE09 EE14 EE15 EE32 EE44

EE45 FF04 FF26 FF30 GG02 GG13 GG24 GG25 GG32 GG34

GG45 GG51 GG52 HJ01 HJ04 HJ12 HJ13 HJ23 HL01 HL02

HL03 HL04 HL05 HL11 HL12 HL23 HL24 HM15 NN03 NN22

NN23 NN24 NN27 NN34 NN35 NN73 PP02 PP04 PP34 QQ16

QQ21