(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5702381号

(P5702381)

(45) 発行日 平成27年4月15日(2015.4.15)

(24) 登録日 平成27年2月27日(2015.2.27)

|                         |                    |

|-------------------------|--------------------|

| (51) Int.Cl.            | F 1                |

| HO 1 L 29/47 (2006.01)  | HO 1 L 29/48 F     |

| HO 1 L 29/872 (2006.01) | HO 1 L 27/10 4 4 8 |

| HO 1 L 27/105 (2006.01) | HO 1 L 27/10 4 4 9 |

| HO 1 L 27/28 (2006.01)  | HO 1 L 45/00 Z     |

| HO 1 L 51/05 (2006.01)  | HO 1 L 49/00 Z     |

請求項の数 13 (全 20 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2012-520683 (P2012-520683)  |

| (86) (22) 出願日 | 平成22年7月9日(2010.7.9)           |

| (65) 公表番号     | 特表2012-533192 (P2012-533192A) |

| (43) 公表日      | 平成24年12月20日(2012.12.20)       |

| (86) 國際出願番号   | PCT/US2010/041539             |

| (87) 國際公開番号   | W02011/008650                 |

| (87) 國際公開日    | 平成23年1月20日(2011.1.20)         |

| 審査請求日         | 平成25年4月16日(2013.4.16)         |

| (31) 優先権主張番号  | 12/502,221                    |

| (32) 優先日      | 平成21年7月13日(2009.7.13)         |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                         |

|-----------|-----------------------------------------------------------------------------------------|

| (73) 特許権者 | 500373758<br>シーゲイト テクノロジー エルエルシー<br>アメリカ合衆国、95014 カリフォルニア州、クパチーノ、サウス・ディ・アンザ・ブルバード、10200 |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                                                              |

| (72) 発明者  | キム、ヨン・ビル<br>アメリカ合衆国、55347 ミネソタ州、エデン・プレリー、ビクトリア・ドライブ、9151                                |

| (72) 発明者  | アミン、ヌルル<br>アメリカ合衆国、55125 ミネソタ州、ウッドベリー、レーニア・ドライブ、8797                                    |

最終頁に続く

(54) 【発明の名称】ショットキーダイオードスイッチおよびそれを含むメモリユニット

## (57) 【特許請求の範囲】

## 【請求項 1】

スイッチング素子であって、

第1の部分と第2の部分とを有する第1の半導体層と、

第1の部分と第2の部分とを有する第2の半導体層と、

前記第1の半導体層と前記第2の半導体層との間に配置される絶縁層と、

前記第1の半導体層の前記第1の部分と接触して第1の接合部を形成するとともに、前記第2の半導体層の前記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、

前記第1の半導体層の前記第2の部分と接触して第3の接合部を形成するとともに、前記第2の半導体層の前記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、

前記第1の接合部と前記第4の接合部とはショットキー接觸部であり、前記第2の接合部と前記第3の接合部とはオーミック接觸部である、スイッチング素子。

## 【請求項 2】

前記第1の半導体層と前記第2の半導体層とは、シリコン、シリコン含有化合物、ゲルマニウム、ゲルマニウム含有化合物、アルミニウム含有化合物、ホウ素含有化合物、ガリウム含有化合物、インジウム含有化合物、カドミウム含有化合物、亜鉛含有化合物、鉛含有化合物、および錫含有化合物から独立して選択される、請求項1に記載のスイッチング素子。

**【請求項 3】**

前記第1の半導体層は結晶シリコンであり、前記第2の部分はリン( P )、ホウ素( B )、または砒素( As )でドーピングされる、請求項1または2に記載のスイッチング素子。

**【請求項 4】**

前記第2の半導体層は結晶シリコンであり、前記第1の部分はリン( P )、ホウ素( B )、または砒素( As )でドーピングされる、請求項1～3のいずれか1項に記載のスイッチング素子。

**【請求項 5】**

前記第1の半導体層の前記第2の部分と前記第2の半導体層の前記第1の部分とは、リン( P )、ホウ素( B )、または砒素( As )で高濃度にドーピングされる、請求項13、4のいずれか1項に記載のスイッチング素子。 10

**【請求項 6】**

前記第1の半導体層の前記第1の部分と前記第2の半導体層の前記第2の部分とは高濃度にドーピングされない、請求項5に記載のスイッチング素子。

**【請求項 7】**

第2の絶縁層と基板層とをさらに含み、前記第2の絶縁層は前記基板層と前記第1の半導体層との間に配置され、前記第2の絶縁層は前記第1および第2の金属コントタクトと接触する、請求項1～6のいずれか1項に記載のスイッチング素子。 20

**【請求項 8】**

不揮発性メモリ素子であって、

スイッチング装置と、

不揮発性メモリセルとを含み、

前記スイッチング装置は、

第1の部分と第2の部分とを有する第1の半導体層と、

第1の部分と第2の部分とを有する第2の半導体層と、

前記第1の半導体層と前記第2の半導体層との間に配置される絶縁層と、

前記第1の半導体層の前記第1の部分と接触して第1の接合部を形成するとともに、前記第2の半導体層の前記第1の部分と接触して第2の接合部を形成する第1の金属コントタクトと、

前記第1の半導体層の前記第2の部分と接触して第3の接合部を形成するとともに、前記第2の半導体層の前記第2の部分と接触して第4の接合部を形成する第2の金属コントタクトとを含み、

前記第2の接合部と前記第3の接合部とはオーム接触部であり、

前記スイッチング装置は前記不揮発性メモリセルと直列に電気的に接続される、不揮発性メモリ素子。 30

**【請求項 9】**

前記第1の接合部と前記第4の接合部とはショットキー接合部である、請求項8に記載の不揮発性メモリ素子。

**【請求項 10】**

前記第1の半導体層の前記第2の部分と前記第2の半導体層の前記第1の部分とは、リン( P )、ホウ素( B )、または砒素( As )でドーピングされる、請求項8または9に記載の不揮発性メモリ素子。 40

**【請求項 11】**

前記第1の半導体層の前記第1の部分と前記第2の半導体層の前記第2の部分とはドーピングされない、請求項8～10のいずれか1項に記載の不揮発性メモリ素子。

**【請求項 12】**

前記第1および第2の半導体層は同じ厚さを有する、請求項8～11のいずれか1項に記載の不揮発性メモリ素子。

**【請求項 13】**

前記不揮発性メモリセルはスピントルクトランスマルチアクセスマモリ(STRAM)スレーブである、請求項8～12のいずれか1項に記載の不揮発性メモリ素子。

【発明の詳細な説明】

【背景技術】

【0001】

背景

新しいタイプのメモリは、一般に利用されているタイプのメモリと競合する可能性が大きい。たとえば、不揮発性のスピントランスマルチアクセスマモリ(spin-transfer torque random access memory(本願明細書において「STRAM」と称する))および抵抗性ランダムアクセスメモリ(resistive random access memory(本願明細書において「RRAM(登録商標)」と称する))はともに、次世代のメモリの有力な候補であると考えられる。FLASHメモリ(NANDまたはNOR)のような既成のメモリタイプに対してより有効に競合するSTRAMおよびRRAM(登録商標)の能力は、メモリユニット(メモリセルおよびその関連する駆動装置)がチップ上に形成され得る密度を増加させることによって最大化され得る。10

【発明の概要】

【課題を解決するための手段】

【0002】

概要

本願明細書においてスイッチング素子が開示される。このスイッチング素子は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接觸部であり、上記第2の接合部と上記第3の接合部とはオーム接觸部である。20

【0003】

さらに本願明細書において不揮発性メモリ素子が開示される。この不揮発性メモリ素子は、スイッチング装置と、不揮発性メモリセルとを含み、上記スイッチング装置は、第1の部分と第2の部分とを有する第1の半導体層と、第1の部分と第2の部分とを有する第2の半導体層と、上記第1の半導体層と上記第2の半導体層との間に配置される絶縁層と、上記第1の半導体層の上記第1の部分と接触して第1の接合部を形成するとともに、上記第2の半導体層の上記第1の部分と接触して第2の接合部を形成する第1の金属コンタクトと、上記第1の半導体層の上記第2の部分と接触して第3の接合部を形成するとともに、上記第2の半導体層の上記第2の部分と接触して第4の接合部を形成する第2の金属コンタクトとを含み、上記第1の接合部と上記第4の接合部とはショットキー接觸部であり、上記第2の接合部と上記第3の接合部とはオーム接觸部であり、上記スイッチング装置は上記不揮発性メモリセルと直列に電気的に接続される。30

【0004】

さらに本願明細書において、スイッチング素子を形成する方法が開示される。この方法は、第1の半導体層と、絶縁層と、第2の半導体層とを含む積層物を設けるステップと、上記積層物の第1の部分のみを保護する第1のマスク領域を形成するステップと、上記第2の半導体層の第1の部分のみを第1のエネルギー準位を用いてドーピングするステップと、上記積層物の第2の部分のみを保護する第2のマスク領域を形成するステップとを含み、上記積層物の上記第1の部分および上記第2の部分は部分的にのみ重なり、上記方法はさらに、上記第1の半導体層の第2の部分のみを第2のエネルギー準位を用いてドーピングするステップを含み、上記第1のエネルギー準位と上記第2のエネルギー準位とは異なり、これによりドーピングされた積層物を形成し、上記方法はさらに、上記ドーピングされた積4050

層物の部分の上のみにコンタクトマスクを形成するステップと、少なくとも上記第2の半導体層、上記絶縁層、および上記第1の半導体層の部分をエッティングするステップと、上記第2の半導体層、上記絶縁層、および上記第1の半導体層のエッティングされた領域に第1および第2の金属コンタクトを形成するステップとを含む。

**【0005】**

これらおよびさまざまな他の特徴および利点は、以下の詳細な説明を読めば、明確になるであろう。

**【0006】**

この開示は、添付の図面に関連して、この開示のさまざまな実施例の以下の詳細な説明を考慮するとより完全に理解され得る。

10

**【図面の簡単な説明】**

**【0007】**

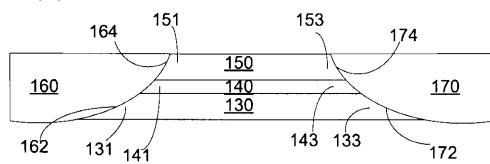

【図1A】本願明細書において開示されるスイッチング素子の実施例の概略図である。

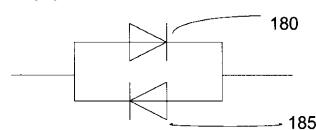

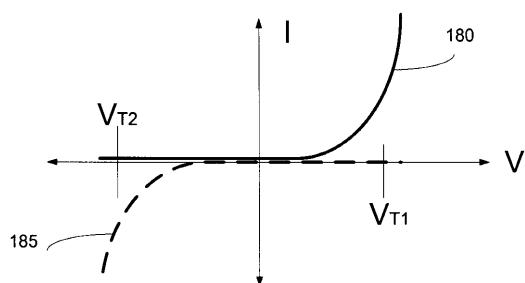

【図1B】本願明細書において開示されるスイッチング素子の機能を示す回路図である。

【図1C】本願明細書において開示される仮想のスイッチング素子の電流 - 電圧(1 - V)曲線の図である。

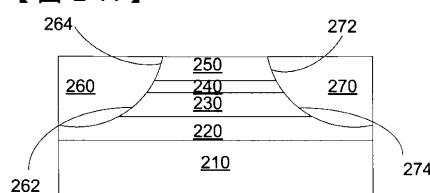

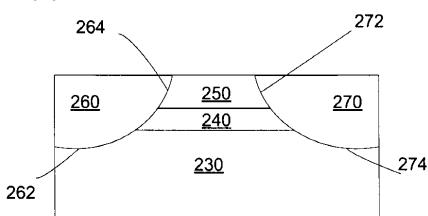

【図2A】本願明細書において開示されるスイッチング素子の概略図である。

【図2B】本願明細書において開示されるスイッチング素子の概略図である。

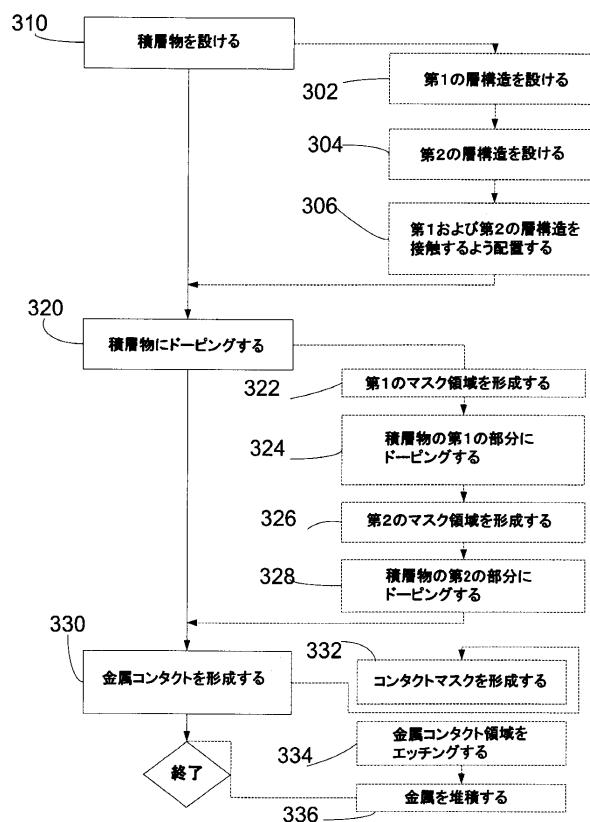

【図3】スイッチング素子を形成する例示的な方法を示すフローチャートの図である。

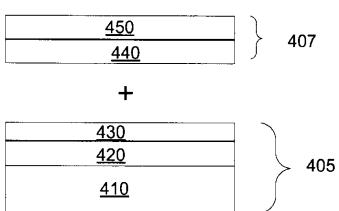

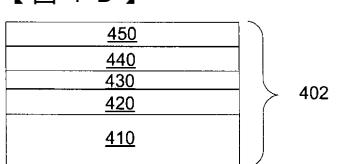

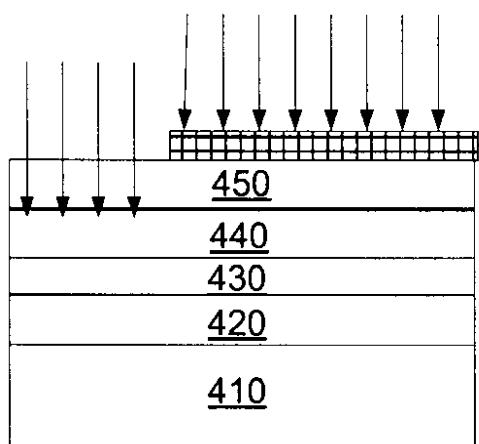

【図4A】作製のある段階でのスイッチング素子を示す図である。

20

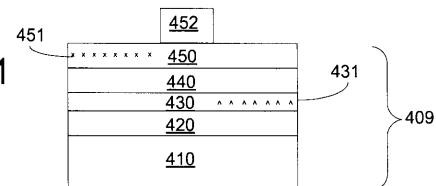

【図4B】作製のある段階でのスイッチング素子を示す図である。

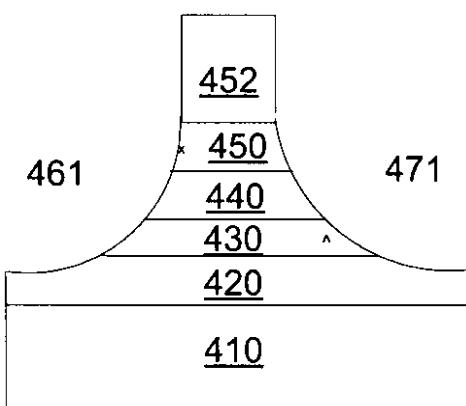

【図4C】作製のある段階でのスイッチング素子を示す図である。

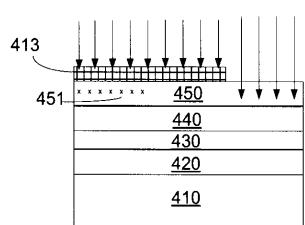

【図4D】作製のある段階でのスイッチング素子を示す図である。

【図4E】作製のある段階でのスイッチング素子を示す図である。

【図4F】作製のある段階でのスイッチング素子を示す図である。

【図4G】作製のある段階でのスイッチング素子を示す図である。

【図5A】本願明細書において開示される不揮発性メモリ素子において利用され得るさまざまなタイプの抵抗性感知メモリ(RSM)セルの概略図であり、STRAMを示す図である。

【図5B】本願明細書において開示される不揮発性メモリ素子において利用され得るさまざまなタイプの抵抗性感知メモリ(RSM)セルの概略図であり、STRAMを示す図である。

30

【図5C】本願明細書において開示される不揮発性メモリ素子において利用され得るさまざまなタイプの抵抗性感知メモリ(RSM)セルの概略図であり、RRAM(登録商標)を示す図である。

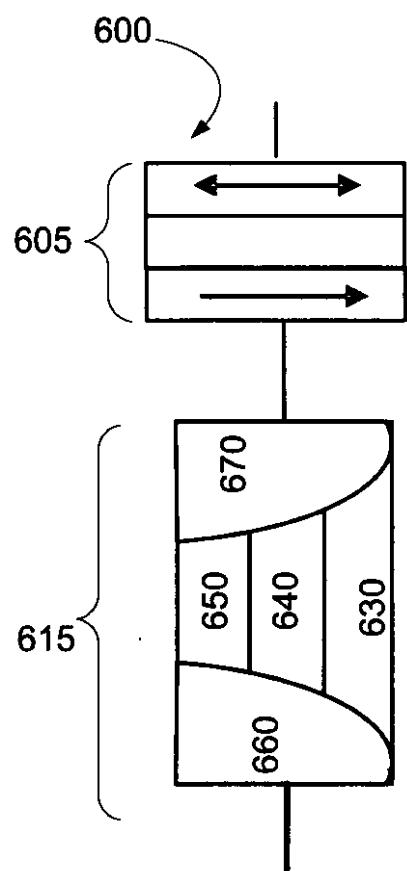

【図6A】本願明細書において開示される不揮発性メモリ素子の概略図である。

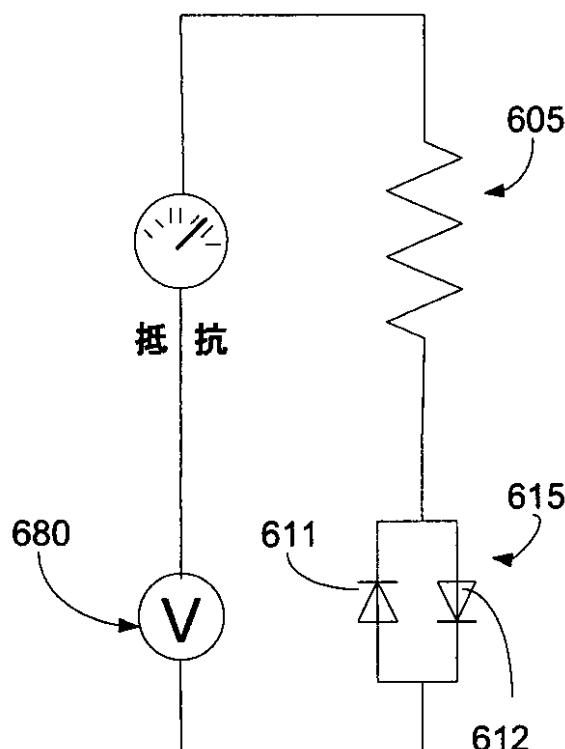

【図6B】本願明細書において開示される不揮発性メモリ素子の回路図である。

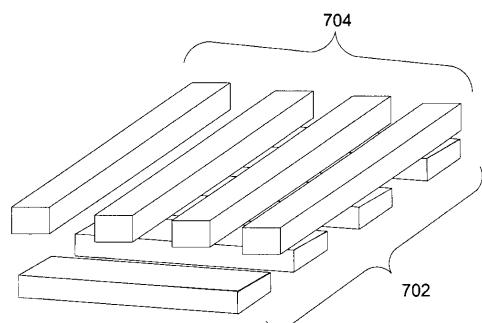

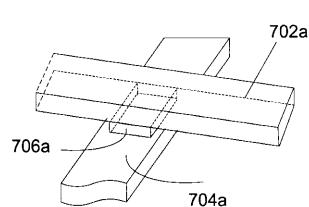

【図7A】本願明細書において開示される不揮発性メモリユニットを組み得るクロスバーメモリアレイの部分の斜視図である。

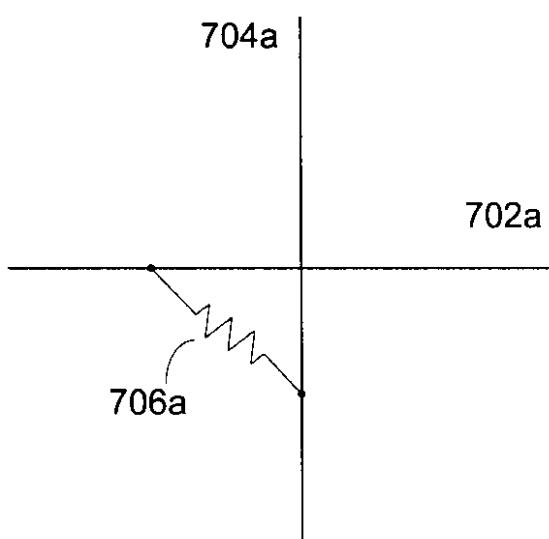

【図7B】本願明細書において開示される不揮発性メモリユニットを組み得るクロスバーメモリアレイの部分の斜視図である。

40

【図7C】本願明細書において開示される不揮発性メモリユニットを組み得るクロスバーメモリアレイの部分の線図である。

**【発明を実施するための形態】**

**【0008】**

図面は必ずしも正確な縮尺ではない。図において用いられる同様の番号は同様の構成要素を指す。しかしながら、所与の図面におけるある構成要素を指す番号の使用は、同じ番号を付された、他の図での構成要素を限定することを意図していないということが理解されるであろう。

**【0009】**

50

### 詳細な説明

以下の説明では、本願明細書の一部を形成し、いくつかの特定の実施例を例示目的で示す添付の図面の集合を参照する。本開示の範囲または精神から逸脱することができなければ、他の実施例も考慮および作製されてもよいということが理解されるべきである。したがって、以下の詳細な説明は、限定的な意味に解釈されるべきではない。

#### 【0010】

当該明細書および特許請求の範囲において用いられる形状、量、および物性を示すすべての数は、他の態様で示されなければならない、すべての場合において、「約」という用語によって修飾されると理解されるべきである。したがって、上記の明細書および添付の特許請求の範囲に記載される数値パラメータは、逆の態様で示されなければならない、当業者が本願明細書において開示される教示を利用することによって得ることを求める所望の特性に依存して変動し得る近似値である。10

#### 【0011】

端点による数値範囲の記載は、その範囲内に含まれるすべての数（たとえば1～5は、1、1.5、2、2.75、3、3.80、4、および5を含む）およびその範囲内の任意の範囲を含む。

#### 【0012】

当該明細書および添付の特許請求の範囲において用いられるように、「ある(a, an)」および「その(the)」といった単数形は、明確にその内容がそうでない態様を示していないければ、複数の対象物を有する実施例を包含する。当該明細書および添付の特許請求の範囲において用いられるように、「または」という用語は、明確にその内容がそうでない態様を示していないければ、一般的に「および／または」を含む意味で用いられる。20

#### 【0013】

「下側」、「上側」、「真下」、「下」、「上」および、「上部」を含むがこれらに限定されない空間に関連する用語は、本願明細書において用いられた場合、要素同士の空間的な関係を記載する際の説明を容易にするよう用いられる。このような空間に関連する用語は、図面および本願明細書に示される特定の方位に加えて、使用時または動作時の装置の異なる方位も包含する。たとえば、図に示されるセルを反転させる、すなわちひっくり返すと、以前は他の要素の下または真下に位置するよう記載された部分が、当該他の要素の上になる。30

#### 【0014】

本願明細書において用いられるように、たとえばある要素、構成要素、または層が別の要素、構成要素、または層の「上に存在」、別の要素、構成要素、もしくは層に「接続される」、「結合される」、もしくは「接触される」と記載される場合はたとえば、直接的にその上に存在し、直接的に接続され、直接的に結合され、直接的に接触し得るか、または間に介在する要素、構成要素または層が特定の要素、構成要素、または層の上に存在、接続、結合、もしくは接触してもよい。たとえば、ある要素、構成要素、または層が、他の要素と「直接的に上に存在」、「直接的に接続」、「直接的に結合」、または「直接的に接触」する場合は、間に介在する要素、構成要素、または層が存在しない。

#### 【0015】

本願明細書においては、スイッチとして利用され得る電子装置が開示される。この開示される電子装置は、スイッチング装置またはスイッチング素子とも称され得る。一般的にスイッチは、電気回路を切断、電流を遮断、またはある導体から別の導体へ電流を分岐させ得る電気的な構成要素である。本願明細書において開示されるスイッチは双方向スイッチとも称され得る。双方向スイッチは、電気回路を切断することができ、当該スイッチを通る電流をいずれの方向にも方向付けすることもできる。スイッチング装置は、以前はダイオードを利用していた用途、またはダイオードを利用したであろう用途、および他の用途に利用することができる。本願明細書において開示されるスイッチング装置は高い駆動電流にも耐え得る。40

#### 【0016】

50

本願明細書において開示されるスイッチング装置の実施例が図1Aに示され得る。この例示的なスイッチング装置は、第1の半導体層130と、絶縁層140と、第2の半導体層150と、第1の金属コンタクト160と、第2の金属コンタクト170とを含む。図1Aに示されるように、(ある実施例においては第1の絶縁層140とも称され得る)絶縁層140は、第1の半導体層130と第2の半導体層150との間に配置され得る。ある実施例では、絶縁層140は、第1の半導体層130と第2の半導体層150との間に直接的に配置され得るとともに、第1の半導体層130および第2の半導体層150の両方に接触する。

#### 【0017】

ある実施例では、第1の金属コンタクト160は第1の半導体層130、絶縁層140、および第2の半導体層150に隣接している。ある実施例では、第1の金属コンタクト160は第1の半導体層130、絶縁層140、および第2の半導体層150のそれぞれの第1の部分131、141、および151に隣接している。ある実施例では、第1の金属コンタクト160は、第1の半導体層130、絶縁層140、および第2の半導体層150の第1の部分131、141、および151に接触している。ある実施例では、第1の金属コンタクト160は、第1の半導体層130、絶縁層140、および第2の半導体層150の第1の部分131、141、および151に直接的に接触している。

#### 【0018】

ある実施例では、第2の金属コンタクト170は第1の半導体層130、絶縁層140、および第2の半導体層150に隣接している。ある実施例では、第2の金属コンタクト170は、第1の半導体層130、絶縁層140、および第2の半導体層150のそれぞれの第2の部分133、143、および153に隣接している。ある実施例では、第2の金属コンタクト170は、第1の半導体層130、絶縁層140、および第2の半導体層150の第2の部分133、143、および153に接触している。ある実施例では、第2の金属コンタクト170は、第1の半導体層130、絶縁層140、および第2の半導体層150の第2の部分133、143、および153に直接的に接触している。

#### 【0019】

第1の半導体層130の第1の部分131は第1の接合部162にて第1の金属コンタクト160と接触している。第2の半導体層150の第1の部分151は、第2の接合部164にて第1の金属コンタクト160と接触している。第1の半導体層130の第2の部分133は、第3の接合部172にて第2の金属コンタクト170と接触している。第2の半導体層150の第2の部分153は、第4の接合部174にて第2の金属コンタクト170と接触している。第1、第2、第3、および第4の接合部162、164、172、および174は、オーミック接合部またはショットキー接合部のいずれかである。

#### 【0020】

金属と半導体とが密接に接触すると、ポテンシャル障壁が当該2つの材料の間に存在することになる。ポテンシャル障壁は、ほとんどの電荷キャリア(電子または正孔)が一方の材料から他方の材料に通過するのを防止する。この障壁を乗り越えて他方の材料へと横断するのに十分なエネルギーを有しているのは、ほんのわずかな数のキャリアだけである。バイアスがその接合部に適用されると、バイアスをかけることは、半導体側よりも低く障壁を現し得る効果と、半導体側よりも高く障壁を現し得る効果との2つの効果のうちの1つの効果を有し得る。上記バイアスは、金属側からは障壁の高さを変更しない。この結果、接合部が1つのバイアス極性については伝導するが他方のバイアス極性については伝導しない、ショットキー接合部とも称され得るショットキー障壁または整流性接觸部が存在することになる。他方、オーミック接觸部は両方の極性について同じように伝導する。オーミック接觸部またはオーミック接合部は、線形かつ対称的な電流-電圧(I-V)曲線を有する。ショットキー接觸部またはショットキー接合部は、非線形かつ非対称的な電流-電圧(I-V)曲線を有する。

#### 【0021】

特定の金属-半導体接合部がオーミック接合部またはショットキー接合部になるかどうか

10

20

30

40

50

かは、当該金属の仕事関数と、当該半導体のバンドギャップと、半導体におけるドーパントのタイプおよび濃度と、他の要因とに少なくとも部分的に依存し得る。一般的に、高濃度にドーピングされた半導体と金属との接合部は、より薄いエネルギー障壁を形成する（ドーパントのレベルが高くなればなるほど、障壁が薄くなる）。逆バイアス条件では、電荷は量子力学的トンネルによりこの障壁を通って流れる。ある実施例では、高濃度にドーピングされた半導体材料と金属との接合部が、オーミック接合部を形成し（電流はいずれかの方向に流れる。すなわち、一方向における順方向にバイアスされた電流および他の（逆）方向におけるトネリング）、ドーピングされていないかまたは低濃度にドーピングされた半導体材料と金属との接合部がショットキー接合部を形成することとなる。

## 【0022】

10

本願明細書において開示されるスイッチング素子の実施例では、第1の半導体層130は1つのオーミック接触部と1つのショットキー接触部とを有し、第2の半導体層150は1つのオーミック接触部と1つのショットキー接触部とを有することとなる。第1の半導体層130内のショットキー接触部およびオーミック接触部の方位は、第2の半導体層150内のショットキー接触部およびオーミック接触部の方位と略反対となる。ある実施例では、第1の接合部162がショットキー接合部であり得、第2の接合部164がオーミック接合部であり得、第3の接合部172がオーミック接合部であり得、第4の接合部174がショットキー接合部であり得る。ある実施例では、第1の接合部162がオーミック接合部であり得、第2の接合部164がショットキー接合部であり得、第3の接合部172がショットキー接合部であり得、第4の接合部174がオーミック接合部であり得る。

## 【0023】

20

第1の半導体層130および第2の半導体層150内のショットキー接触部およびオーミック接触部の方位が反対であることにより、スイッチング素子はこのような双方向スイッチの構成を有する。双方向スイッチは、第1の極性を有する電流が適用されると、電流を第1の方向に流し、（第1の極性とは反対の）第2の極性を有する電流が適用されると、（第1の方向とは反対の）第2の方向に電流を流す。図1Bは、本願明細書において開示されるスイッチング素子の双方向性を説明する回線図を示す。図1Bの回線図に示されるように、第1の半導体層および第2の半導体層はそれぞれ、並列である第1のダイオード180および第2のダイオード185の機能を提供する。第1のダイオード180は電流を、第2のダイオード185が流すのとは反対方向に流す。図1Cは開示される仮想のスイッチング素子についての電流-電圧（I-V）曲線を示す。図1Cに示されるように、第1のダイオード180は、実質的な電流が第1の方向に流れ始めるしきい値電圧 $V_{T_1}$ を有する。第2のダイオード185は、実質的な電流が第2の方向に流れ始めるしきい値電圧 $V_{T_2}$ を有する。図1Cに示されるように、2つの電圧にてスイッチング素子から流れる電流と同様に、 $V_{T_1}$ および $V_{T_2}$ の極性は反対である。これにより、電圧 $V_{T_1}$ と電圧 $V_{T_2}$ との間では電流を本質的にブロックし、 $V_{T_2}$ を下回る電圧では、第1の極性を有する電流を流すとともに、 $V_{T_1}$ を上回る電圧では第2の極性の電流を流すスイッチング素子が提供される。

## 【0024】

30

これは、スイッチとして動作する際に、 $V_{T_2}$ 未満の電圧がスイッチング素子に適用されると、電流は第1の方向に流れ、 $V_{T_1}$ より大きい電圧がスイッチング素子に適用されると、電流が第2の方向に流れることを意味する。したがって、スイッチング素子は、電流がたとえば不揮発性メモリセルのような電気的に接続される構成要素を通って流れる方向を制御するのに用いられ得る。

## 【0025】

40

本願明細書において開示されるようなスイッチング素子には、双方向のスイッチングと高い駆動電流に耐える能力との組合せを提供し得るという利点がある。本願明細書において開示されるスイッチング素子は、開示されるスイッチング素子の電流経路の断面が（従来のMOSトランジスタと比較して）相対的に大きいことにより相対的に大きな量の電流

50

を流すことができるので、高い駆動電流が必要な場合に用いられ得る。高い駆動電流を扱う能力は、高い駆動電流が必要であるかまたは高い駆動電流が望まれる構成要素とともにスイッチが用いられ得るようになるので、有利であり得る。当該構成要素の例としては、スピントルクトランスマゼンダムアクセスメモリ(STRAM)がある。

#### 【0026】

図2Aは本願明細書において開示されるスイッチング素子の別の実施例を示す。図2Aにおけるスイッチング素子は、上で論じた構成要素を含み、かつ他の構成要素も含む。たとえば、第1の半導体層230に隣接して別の絶縁層220が存在し得る。この別の絶縁層220は、第2の絶縁層220とも称され得る。ある実施例では、第2の絶縁層220は第1の半導体層230に直接的に隣接して存在し得る。第2の絶縁層220は第1の半導体層230を基板210から電気的に絶縁するよう機能し得る。当該基板は、導電性または半導電性の材料であり得る。基板210は、スイッチング素子の構造的な安定性を与えるよう機能し得るとともに、スイッチング素子の形成プロセスを補助し得る。

#### 【0027】

図1Cに示される仮想のI-V曲線は対称的である。一般的に、開示されるスイッチング素子のI-V曲線が対称的になるように、第1の半導体層および第2の半導体層に亘る経路の長さは少なくとも実質的に同じである必要があり、金属/半導体接合部(たとえば、162、164、172、および174)の表面領域は少なくとも実質的に同じである必要がある。スイッチング素子が対称的な第1および第2の半導体層ならびに/または実質的に同じ表面領域を有さない場合は、あまり非対称的にならぬように修正され得る。これは、たとえば、ドーパント(性質(identity)または量のいずれか)を変更するか、金属コンタクトの一方または両方を変更するか、本願明細書において論じられていない他の要因を変更するか、またはこれらの要因の組合せを変更することによって、スイッチング素子を構成する構成要素を修正することで達成される。対称的なI-V曲線を有するスイッチング素子はいくつかの用途において有利であり得る。たとえば、メモリ素子と組み合わせて用いられることになるスイッチング素子が対称的なI-V曲線を有することは有利であり得る。

#### 【0028】

図2Aに示される例示的なスイッチング素子は、一般的に第1および第2の半導体層の厚さを実質的に同じにすることは相対的に単純なことであるので、対称的なI-V曲線を有するよう比較的容易に製造され得る。ある実施例では、実質的に同じ厚さを有する第1の半導体層および第2の半導体層を有するスイッチング素子は大抵、対称的なI-V曲線を有することになる。

#### 【0029】

図2Bに示される例示的なスイッチング素子は大抵、対称的なI-V曲線を有することはない。図2Bに示されるように、例示されるスイッチング素子の第1の半導体層230は、第2の半導体層250よりも著しく分厚い。さらに、第1の半導体層230の接合部である第1の接合部262および第3の接合部274は、第2の半導体層250の接合部(すなわち、第1の金属コンタクト260および第2の金属コンタクト270との第2の接合部264および第4の接合部272)よりも著しく大きな表面領域を有する。これにより、第1の半導体層230が第2の半導体層250よりも高いしきい値電圧を有する可能性がもっとも高くなる。したがって、このようなスイッチング素子は大抵、非対称のI-V曲線を有することになる。

#### 【0030】

第1の半導体層および第2の半導体層は任意の半導体材料を含み得る。第1の半導体層および第2の半導体層は同じ材料であり得るが、同じ材料である必要はない。第1の半導体層、第2の半導体層、またはその両方のために用いられ得る例示的な半導体は、シリコン、シリコン含有化合物、ゲルマニウム、ゲルマニウム含有化合物、アルミニウム含有化合物、ホウ素含有化合物、ガリウム含有化合物、インジウム含有化合物、カドミウム含有化合物、亜鉛含有化合物、鉛含有化合物、錫含有化合物を含むがこれらに限定されない。

10

20

30

40

50

例示的な元素半導体および化合物半導体は、シリコン、たとえば結晶シリコン、ゲルマニウム、炭化珪素（SiC）、シリコンゲルマニウム（SiGe）、アンチモン化アルミニウム（AlSb）、砒化アルミニウム（AlAs）、窒化アルミニウム（AlN）、リン化アルミニウム（AlP）、窒化ホウ素（BN）、リン化ホウ素（BP）、砒化ホウ素（BAs）、アンチモン化ガリウム（GaSb）、砒化ガリウム（GaAs）、窒化ガリウム（GaN）、リン化ガリウム（GaP）、アンチモン化インジウム（InSb）、砒化インジウム（InAs）、窒化インジウム（InN）、リン化インジウム（InP）、砒化アルミニウムガリウム（AlGaAs、Al<sub>x</sub>Ga<sub>1-x</sub>As）、砒化インジウムガリウム（InGaP）、砒化アルミニウムインジウム（AlInAs）、アンチモン化アルミニウムインジウム（AUnSb）、砒化窒化ガリウム（GaAsN）、砒化リン化ガリウム（InGaAsN）、窒化アルミニウムガリウム（AlGaN）、リン化アルミニウムガリウム（AlGaP）、窒化インジウムガリウム（InGaN）、砒化アンチモン化インジウム（InAsSb）、アンチモン化インジウムガリウム（InGaInP、InAlGaP、InGaAlP、AlInGaP）、砒化リン化アルミニウムガリウム（AlGaAsP）、砒化リン化インジウムガリウム（InGaAsP）、砒化リン化アルミニウムインジウム（AlInAsP）、砒化窒化アルミニウムガリウム（InAlAsN）、砒化窒化インジウムガリウム（InAlAsN）、砒化窒化アンチモン化ガリウム（GaAsSbN）、窒化砒化アンチモン化インジウムガリウム（GaInNAsSb）、砒化アンチモン化リン化インジウムガリウム（GaInAsSbP）、セレン化カドミウム（CdSe）、硫化カドミウム（CdS）、テルル化カドミウム（CdTe）、酸化亜鉛（ZnO）、セレン化亜鉛（ZnSe）、硫化亜鉛（ZnS）、テルル化亜鉛（ZnTe）、テルル化亜鉛カドミウム（CdZnTe、CZT）、テルル化カドミウム水銀（HgCdTe）、テルル化水銀亜鉛（HgZnTe）、セレン化水銀亜鉛（HgZnSe）、塩化第一銅（CuCl）、セレン化鉛（PbSe）、硫化鉛（PbS）、テルル化鉛（PbTe）、硫化錫（SnS）、テルル化錫（SnTe）、鉛テルル化錫（PbSnTe）、タリウムテルル化錫（Tl<sub>2</sub>SnTe<sub>5</sub>）、タリウムテルル化ゲルマニウム（Tl<sub>2</sub>GeTe<sub>5</sub>）、テルル化蒼鉛（Bi<sub>2</sub>Te<sub>3</sub>）、リン化カドミウム（Cd<sub>3</sub>P<sub>2</sub>）、砒化カドミウム（Cd<sub>3</sub>As<sub>2</sub>）、アンチモン化カドミウム（Cd<sub>3</sub>Sb<sub>2</sub>）、リン化亜鉛（Zn<sub>3</sub>P<sub>2</sub>）、砒化亜鉛（Zn<sub>3</sub>As<sub>2</sub>）、およびアンチモン化亜鉛（Zn<sub>3</sub>Sb<sub>2</sub>）を含むがこれらに限定されない。

10

20

30

### 【0031】

第1の半導体層および第2の半導体層の両方の一部はドーピングされる。ドーピングとは、不純物を半導体の中に意図的に導入してその電気的特性を変更するプロセスである。選択される特定のドーパントは最終のスイッチング素子において望まれる特定の特性、ドーピングされる半導体材料の性質（identity）、本願明細書において論じられていない他の要因、またはこれらの組合せに少なくとも部分的に依存し得る。例示的なドーパントはIII族元素およびV族元素を含み得るが、これらに限定されない。半導体材料がIV族材料（たとえば、シリコン、ゲルマニウム、および炭化珪素）である実施例では、IIII族元素またはV族元素がドーパントとして用いられ得る。特定の例示的なドーパントは、ホウ素（B）、砒素（As）、リン（P）、およびガリウム（Ga）を含み得るが、これらに限定されない。

40

### 【0032】

第1の絶縁層および随意である第2の絶縁層は、電気的に絶縁性の任意の材料から形成され得る。第1の絶縁層および随意である第2の絶縁層は同じ材料であってもよいが、同じ材料である必要はない。例示的な絶縁材料は、たとえばアルミナ（Al<sub>2</sub>O<sub>3</sub>）、酸化シリコン（SiO<sub>2</sub>）、および酸化マグネシウム（MgO）といった酸化物を含むがこれらに限定されない。

### 【0033】

金属コンタクトは、導電性の任意の金属材料からなり得る。第1の金属コンタクトおよび第2の金属コンタクトは同じ材料であり得るが、同じ材料である必要はない。例示的な導電性の金属材料は、タンゲステン(W)や、金(Au)、プラチナ(Pt)、パラジウム(Pd)、ロジウム(Rh)、銅(Cu)、ニッケル(Ni)、銀(Ag)、コバルト(Co)、鉄(Fe)、といった貴金属や、またはそのシリサイドを含むがこれらに限定されない。

#### 【0034】

ある実施例では、第1および第2の半導体の両方は結晶シリコンから形成される。ある実施例では、第1および第2の半導体層はホウ素、リン、または砒素でドーピングされる。ある実施例では、第1の絶縁層と、存在する場合は第2の絶縁層とは酸化シリコン(SiO<sub>2</sub>)から形成される。ある実施例では、金属コンタクトはタンゲステン(W)、ニッケルシリサイド、またはコバルトシリサイドである。

10

#### 【0035】

図2Aに示されるようなスイッチング素子の例示的な作製方法が図3において与えられ、図4Aから図4Gにおいてステップ順に示される。一般的に、このような作製スキームは、フォトリソグラフィ技術、およびエッティングのような他の除去技術、ならびに化学機械平坦化(chemical mechanical planarization(CMP))を含む半導体作製方法を含み得る。当該例示的な方法においてさまざまな層を堆積させるのに、プラズマ堆積(plasma vapor deposition(PVD))、イオン化プラズマベースのスパッタリング(iонized plasma based sputtering)、遠距離スパッタリング(long throw sputtering)、化学気相堆積(chemical vapor deposition(CVD))、原子層堆積(atomic layer deposition(ALD))、および金属有機物化学気相堆積(metal organic chemical vapor deposition(MOCVD))を含む堆積方法を利用できるが、これらに限定されない。図3におけるステップおよび図4A～図4Gにおけるその記載は、本願明細書において開示されるスイッチング素子が作製され得る方法を限定するものでは決してない。なお、図4A～図4Gは必ずしも正確な縮尺ではなく、すべての準備の状態での積層物を必ずしも示しているわけではない。すなわち当該積層物のいくつかの中間段階が図のシーケンスに説明されない場合もある。さらに、図4A～図4Gについて論じる材料およびプロセスは、本願明細書において用いられ得る材料またはプロセスを限定するものではない。

20

#### 【0036】

30

図3および図4A～図4Gに示される例示的な方法では、基板の使用が示される。この明細書を読んだ当業者であれば、基板の使用は必須ではなく、本願明細書において開示されるスイッチング素子は基板を使用することなく作製され得るか、スイッチング素子は作製の後で支持部上に配置され得るか、基板が利用されるがスイッチング素子の作製の間またはその後のいずれかに取り除かれるか、または基板がまったく利用される必要がないということを理解するであろう。基板が利用される場合、当該基板はシリコン、シリコンおよびゲルマニウムの混合物、または他の同様の材料といった材料を含み得る。

#### 【0037】

40

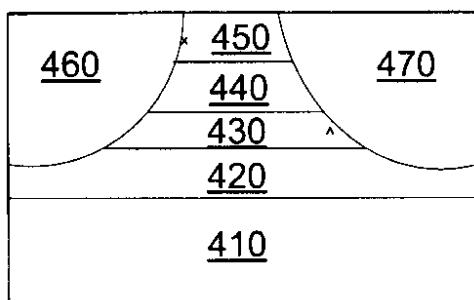

本願明細書において開示されるスイッチング素子を作製する例示的な方法を示すフローチャートを図3に示す。この例示的な方法における第1のステップは、積層物を設けるステップ310である。この積層物は少なくとも第1の半導体層と、(第1の絶縁層とも称され得る)絶縁層と、第2の半導体層とを含み、上記絶縁層は第1の半導体層と第2の半導体層との間に配置される。図4Bに例示的な積層物402が示され得る。この積層物402は、基板410と、第2の絶縁層420と、第1の半導体層430と、第1の絶縁層440と、第2の半導体層450とを含む。この明細書を読めば、積層物は図4Bに示されるよりも多いまたは少ない層を有し得るということが理解されるはずである。積層物は、たとえば市販の源により作製または取得され得る。

#### 【0038】

積層物を作製するのに利用され得る例示的な随意のステップがステップ302、304、および306に示される。ステップ302は第1の層構造を設けることを含む。第1の

50

層構造は少なくとも第1の基板と、第2の絶縁層と、第1の半導体層とを含み得る。第2の絶縁層は第1の基板と第1の半導体層との間に配置される。第1の層構造の例は、絶縁層が上に配置されるとともに当該絶縁層の上に第1の半導体層が配置された基板（たとえばシリコンウェハ）を含み得る。第1の層構造の絶縁層（第2の絶縁層）は、絶縁材料を堆積するか、または基板の一部を酸化して当該基板の一部を絶縁材料にする（たとえばSiO<sub>2</sub>）ことにより形成され得る。例示的な第1の層構造405を図4Aに示す。第1の層構造405は基板410と、第2の絶縁層420と、第1の半導体層430とを含む。

#### 【0039】

ステップ304は第2の層構造を設けることを含む。第2の層構造は少なくとも（第1の絶縁層とも称され得る）絶縁層と、第2の半導体層とを含み得る。当該絶縁層は第2の半導体層上に配置される（その逆も成立する）。第2の層構造の例は酸化基板（たとえばシリコンウェハ）を含み得る。この酸化基板では、酸化された部分は絶縁層となり、酸化されない部分は第2の半導体層となる。代替的には、（シリコンウェハのような）半導体材料は、半導体材料の上に配置された絶縁材料を有し得、これにより絶縁層を第2の半導体層に形成する。シリコンウェハのような基板が第2の層構造を形成するのに利用される実施例では、シリコンウェハの部分は第2の半導体層の厚さを調節するよう取り除かれ得る。これは、たとえば化学機械平坦化（CMP）といった技術により達成される。例示的な第2の層構造407を図4Aに示す。第2の層構造407は絶縁層440と第2の半導体層450とを含む。

#### 【0040】

ステップ306は、第1の層構造を第2の層構造に接触するよう（その逆も成立する）配置することを含む。第1および第2の層構造は、第2の層構造の絶縁層が第1の層構造の第1の半導体層に隣接して上記積層物を形成するように構成される。ある実施例では、第1の層構造の第1の半導体層は、第2の層構造の絶縁層と直接的に隣接または直接的に接触する。次いで、第1および第2の層構造はウェハボンディング技術を用いて一緒になるよう接合され得る。このステップの完了により、図4Bに示される積層物402が形成される。

#### 【0041】

積層物がどのように（ステップ302、304、および306または他の態様によって）設けられても、スイッチング素子の形成方法における次のステップは積層物にドーピングするステップ320である。積層物にドーピングするステップは、第1の半導体層の一部および第2の半導体層の一部をドーピングするよう機能する。より具体的には、積層物にドーピングするステップは、第2の半導体層の第1の部分と第1の半導体層の第2の部分とをドーピングするよう機能する（その逆も成立する）。積層物にドーピングをするよう行われ得る例示的な随意のステップが、ステップ322、324、326、および328において示される。

#### 【0042】

ステップ322は第1のマスク領域を形成することを含む。（以下で論じる第1のマスク領域および第2のマスク領域の両方の）マスク領域は、当該マスク領域の下に位置する材料の中へのドーパントの注入を防止する材料から形成される（この文脈においては、「上」および「下」は、積層物の層およびマスク領域のすべての上に位置するドーパント源の位置により定義される）。マスク領域として利用され得る例示的な材料は、酸化物材料、窒化珪素、またはフォトレジストを含むが、これらに限定されない。第1のマスク領域は、積層物の一部のみを注入から保護する。図4Cに示される積層物は第1のマスク領域411を含む。

#### 【0043】

次のステップであるステップ324は、積層物の一部にドーピングすることを含む。（ステップ322において形成された）第1のマスク領域により、積層物の一部、たとえば第1の部分のみに対してドーピングがなされる。図4Cに示されるように、第1のマスク領域の下では、（矢印で示される）注入が防止されるとともに、第1のマスク領域が積層

10

20

30

40

50

物を覆っていないところでは注入がなされる。積層物の第1の部分へのドーピングは、第1のエネルギー準位を用いて達成される。ある実施例では、第1の部分へのドーピングにより、第2の半導体層450が高濃度にドーピングされるとともに、第1の半導体層430がほんの少しドーピングされるかまたは実質的にまったくドーピングされないことになる。異なるドーピングレベル（すなわちドーピング有および実質的にドーピング無）は、異なるエネルギー準位を用いることにより達成され得る。

#### 【0044】

本願明細書において示されるステップ324では、（この実施例において示されるように積層物の上部層である）第2の半導体層450への優先的なドーピングが達成される。層構造の上部層のみへの優先的なドーピングは、低い注入エネルギーを用いてドーピングすることにより達成され得る。低いエネルギーを用いるドーピングでも、ある深さにまで入り込むのに十分なだけのエネルギーをドーパントに与えることができる。図4Dは、ステップ324の完了後に第2の半導体層450に存在するドーパント451を示す。

10

#### 【0045】

ステップ326は、第2のマスク領域を形成することを含む。第2のマスク領域は、注入から積層物の一部のみを保護する。図4Dに示される積層物は第2のマスク領域413を含む。第1のマスク領域411および第2のマスク領域413の位置は少なくとも部分的に重なり得る。ある実施例では、第1のマスク領域411および第2のマスク領域413は完全には重ならず部分的にのみ重なる。第2のマスク領域413は一般的に少なくとも、第2の半導体層450においてステップ324にてドーピングされなかった部分を保護する。ある実施例では、第2のマスク領域413は一般的に、第2の半導体層450においてステップ324にてドーピングされた部分と、第2の半導体層450においてステップ324にてドーピングされなかった部分とを保護する。

20

#### 【0046】

次のステップであるステップ328は、積層物の一部にドーピングすることを含む。（ステップ326において形成された）第2のマスク領域により、積層物の一部のみ、たとえば第2の部分のドーピングがなされる。図4Dに示されるように、第2のマスク領域の下においては、（矢印で示される）注入が防止されるとともに、第2のマスク領域が積層物を覆っていないところでは注入がなされる。積層物の第2の部分へのドーピングは、第2のエネルギー準位を用いて達成される。第2のエネルギー準位は（第1の部分にドーピングするために用いられる）第1のエネルギー準位とは異なる。ある実施例では、第2の部分へのドーピングにより、第1の半導体層430が高濃度にドーピングされるとともに、第2の半導体層450がほんの少しドーピングされるかまたは実質的にまったくドーピングされないことになる。より高いエネルギーを用いるドーピングにより、ドーパントは積層物の中のより深くへと注入される。より高いエネルギー準位のドーピングはさらに、一般的にドーパントまたは少なくとも実質的な量のドーパントを積層物の上部層に堆積させない。図4Eは、ステップ328の完了後に第1の半導体層430に存在するドーパント431を示す。

30

#### 【0047】

ステップ320または付加的なステップ322、324、326、および328の効果は、第2の半導体層450の第1の部分のみをドーピングまたは高濃度にドーピングし、かつ第1の半導体層430の第2の部分のみをドーピングまたは高濃度にドーピングすることである。第1の半導体層430および第2の半導体層450におけるドーピングまたは高濃度にドーピングした領域同士が反対にある構成により、（金属コンタクトの形成後に）反対に整列したオーミックおよびショットキー接合部が第1および第2の半導体層430および450に形成される。ステップ320の効果は、本願明細書において図4に示され、409として指定されるドーピングされた積層物と称されるものを形成することである。

40

#### 【0048】

図3に示される方法における次のステップは金属コンタクトの形成を行うステップ33

50

0である。一般的に、金属コンタクトの形成はエッチングおよび堆積技術を用いて達成され得る。金属コンタクトを形成するよう行われ得る例示的な特定の随意のステップがステップ332、334、および336において示される。金属コンタクトを形成するこの随意の方法における第1のステップは、コンタクトマスクを形成するステップ332である。コンタクトマスク452は、図4Fに示され、一般的に、ドーピングされた積層物の一部のみを覆う。ある実施例では、コンタクトマスク452は、ドーピングされた積層物において、第1の半導体層450または第2の半導体層430のいずれかでのドーピングされない領域を覆う。コンタクトマスク452は少なくとも、ドーピングされた積層物において、第1のマスク領域411および第2のマスク領域413がドーピングからの保護を与えた部分を覆うとも言うことができる。一般的に、コンタクトマスクはドーピングされた積層物の中央に位置する。ある実施例では、コンタクトマスク452は、ドーピングされた積層物がエッチングされても、ドーピングされた第1の半導体層およびドーピングされた第2の半導体層の少なくとも一部が残るように配置される。

#### 【0049】

次のステップであるステップ334はドーピングされた積層物をコンタクトマスク452を用いてエッチングすることを含む。このステップはドーピングされた積層物の一部を取り除くよう機能する。コンタクトマスク452によって保護されていない部分が、ドーピングされた積層物から取り除かれる。エッチングにより、第1および第2の金属コンタクト領域461および471を形成するとも言うことができる。第1および第2の金属コンタクト領域461および471は、金属コンタクトを形成するよう最終的に金属で充填されることになる。エッチングは公知のエッチング技術および方法を用いて行われ得る。

#### 【0050】

次のステップであるステップ336は、第1の金属コンタクト領域461および第2の金属コンタクト領域471に金属を堆積することを含む。ある実施例では、金属はただ単に第1の金属コンタクト領域461および第2の金属コンタクト領域471に堆積されるわけではない。ある実施例では、ドーピングされた積層物の全体に、第1および第2の金属コンタクト領域461および471を満たす深さまで金属が堆積されるとともに、コンタクトマスク452が覆っていた領域の上に当該金属により層が設けられる。次いで、第1および第2の金属コンタクト領域461および471にのみ金属を残して第1および第2の金属コンタクト460および470を形成するように余分な金属がたとえばCMPにより除去され得る。図4Gは、第1および第2の金属コンタクト460および470の形成の後の、スイッチング素子を構成する積層物を示す。

#### 【0051】

さらに本願明細書において示されないまたは論じられない他の随意の作製ステップが、本願明細書において論じられるとともに例示されるステップの前、後、最中、または組み合わせて行われ得る。さらにこの方法は、一度に1つより多いスイッチング素子が作製されるように行われ得る。

#### 【0052】

本願明細書において開示されるスイッチング素子は不揮発性メモリセルのための選択的な素子として不揮発性メモリセルとともに利用され得る。メモリ装置において利用される不揮発性メモリセルは、本願明細書において記載されるように、多くの異なるタイプのメモリを含み得る。本願明細書において開示される電子装置において利用され得る不揮発性メモリセルの例示的なタイプには、抵抗性感知メモリ(RSM)セルが含まれるがこれに限定されない。RSMセルの例は、強誘電性メモリ(FeRAMまたはFRAM(登録商標))と、磁気抵抗性RAM(MRAM)と、抵抗性RAM(RRAM(登録商標))と、PRAM、PCRAMおよびC-RAMとも称される相変化メモリ(PCM)と、導電性ブリッジRAMまたはCBRAMとも称されるプログラマブルメタライゼーションセル(PMC)と、SRAMとも称されるスピントルクトランスマモリAMとを含むが、これらに限定されない。

#### 【0053】

10

20

30

40

50

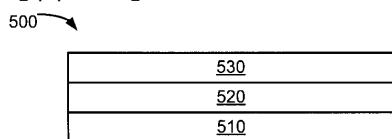

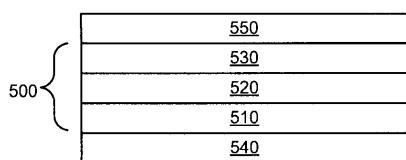

実施例では、RSMセルはSRAMセルであり得る。SRAMメモリセルは、MTJ（磁気トンネル接合部（magnetic tunnel junction））を含む。MTJは一般的に、トンネル障壁としても既知である薄い絶縁層によって分離される2つの磁気電極層を含む。MTJのある実施例を図5Aに示す。図5AにおけるMTJ500は、絶縁層520によって分離される第1の磁気層510と第2の磁気層530とを含む。第1の磁気層510および第2の磁気層530はともに独立して多層構造であってもよい。図5Bは、第1の電極層540および第2の電極層550と接触するMTJ500を示す。第1の電極層540および第2の電極層550は、第1の磁気層510および第2の磁気層530をそれぞれ制御回路（図示せず）に電気的に接続して、磁気層を通る読み込み電流および書き込み電流を提供する。第1の磁気層510および第2の磁気層530の磁化ベクトルの相対的な方位は、MTJ500の両端の抵抗によって決定され得、MTJ500の両端の抵抗は、第1の磁気層510および第2の磁気層530の磁化ベクトルの相対的な方位によって決定され得る。

10

#### 【0054】

第1の磁気層510および第2の磁気層530は一般的に鉄（Fe）、コバルト（Co）、およびニッケル（Ni）合金といった強磁性合金から形成される。ある実施例では、第1の磁気層510および第2の磁気層530はFeMn、NiO、IrMn、PtPdMn、NiMnおよびTbCoといった合金から形成され得る。絶縁層520は一般的に酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）または酸化マグネシウム（MgO）といった絶縁材料から形成される。

20

#### 【0055】

たとえば第1の磁気層510のような、磁気層のうちの1つの磁気層の磁化は一般的にある所定の方向に固定される一方、たとえば第2の磁気層530のような他方の磁気層の磁化方向はスピントルクの影響下で自由に回転する。第1の磁気層510を固定することは、たとえば、PtMnおよびIrMnなどといった反強磁性秩序材料との交換バイアスの使用により達成されてもよい。

#### 【0056】

特定のMTJ500では、メモリセルを通じて第2の磁気層530（自由層）から第1の磁気層510（固定層）への方向に第1の電流を流すことにより読み込みが行われる。MTJ500の抵抗は、自由層が上記固定層と一致して整列するかまたは反対に整列するかどうかに依存して変化し得る。この抵抗に依存する電圧が次いで検知され、基準電圧と比較され、MTJが一致または反対に整列しているかどうか、すなわち「1」または「0」を含んでいるかどうかを判定する。特定のMTJ500では、第2の電流（第2の電流は第1の電流よりも大きい）がMTJを通過するようにすることにより書き込みが行われ得る。電流を一方向に通過させることにより「1」を書き込み、電流を他方向に通過させることにより「0」を書き込む。本願明細書において開示されるスイッチング素子の双方向性により、MTJ500を通じて電流を両方向に駆動する能力が与えられ得る。

30

#### 【0057】

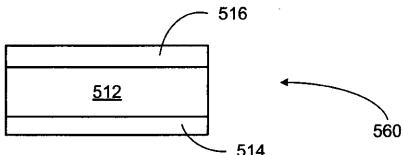

ある実施例では、RSMセルはRRAM（登録商標）セルであり得る。図5Cは、例示的な抵抗性ランダムアクセスメモリ（RRAM（登録商標））セル560の概略図である。RRAM（登録商標）セル560は、媒体層512の電気抵抗を変更することにより電流または電圧パルスに応答する媒体層512を含む。この現象は、電気パルス誘起抵抗変化効果とも称され得る。この効果はたとえば、メモリの抵抗（すなわちデータ状態）を1つ以上の高抵抗状態から低抵抗状態に変化させる。媒体層512は第1の電極514と第2の電極516との間に介在し、RRAM（登録商標）セルのデータ格納材料層として作用する。第1の電極514および第2の電極516は電圧源（図示せず）に電気的に接続される。第1の電極514および第2の電極516は、たとえば金属のような任意の有用な導電材料から形成され得る。

40

#### 【0058】

媒体層512を形成する材料は任意の公知のRRAM（登録商標）材料であり得る。あ

50

る実施例では、媒体層 512 を形成する材料は、金属酸化物のような酸化物材料を含み得る。いくつかの実施例では、金属酸化物は二元酸化物材料または複合金属酸化物材料である。他の実施例では、媒体層 512 を形成する材料はカルコゲニド固体電解質材料または有機 / ポリマー材料を含み得る。

#### 【0059】

二元金属酸化材料は、 $M_xO_y$  という化学式で示され得る。この式において、文字「M」、「O」、「x」、および「y」は、金属、酸素、金属組成比、および酸素組成比をそれぞれ指す。金属「M」は遷移金属および / またはアルミニウム (Al) であってもよい。この場合、遷移金属はニッケル (Ni)、ニオブ (Nb)、チタン (Ti)、ジルコニア (Zr)、ハフニウム (Hf)、コバルト (Co)、鉄 (Fe)、銅 (Cu) および / またはクロム (Cr) であってもよい。媒体層 512 として用いられ得る二元金属酸化物の特定の例には、 $CuO$ 、 $NiO$ 、 $CoO$ 、 $ZnO$ 、 $CrO_2$ 、 $TiO_2$ 、 $HfO_2$ 、 $ZrO_2$ 、 $Fe_2O_3$ 、および  $Nb_2O_5$  が含まれる。

#### 【0060】

ある実施例では、金属酸化物はたとえば、 $Pr_{0.7}Ca_{0.3}MnO_3$ 、 $SrTiO_3$ 、もしくは  $SiZrO_3$  といった化学式の複合酸化物材料、または Cr または Nb でドーピングされたこれらの酸化物といった任意の有用な複合金属酸化物であり得る。複合材料はさらに  $LaCuO_4$ 、または  $Bi_2Sr_2CaCu_2O_8$  を含み得る。固体カルコゲニド材料の一例としては、銀 (Ag) 成分を含むセレン化ゲルマニウム ( $Ge_xSe_{10-x}$ ) がある。有機材料の一例としては、ポリ (3,4-エチレンジオキシチオフェン) (すなわち PEDOT) がある。

#### 【0061】

RSMセルはさらに、(「PZT」とも称する)ジルコン酸チタン酸鉛または(「SBT」とも称する) $SrBi_2Ta_2O_9$  といった材料を用いる、図 5C に類似した構造を有する強誘電体キャパシタをさらに含み得る。このようなメモリセルでは、電流は分極方向を切り替えるよう用いられ得、読込電流は当該分極が上または下であるかどうかを検知し得る。このような実施例では、読込動作はセルが格納するデータを失うことになる破壊的処理であり、当該セルにデータを書き戻すようリフレッシュが必要である。

#### 【0062】

開示されるメモリ素子は、上で開示されたようなスイッチング素子と、不揮発性メモリセルとを含む。本願明細書において開示されるメモリ素子 600 の例示的な実施例を図 6A に示す。メモリ素子 600 は、上で記載および例示したように第 1 の半導体層 650 と、絶縁層 640 と、第 2 の半導体層 630 と、第 1 の金属コンタクト 660 と、第 2 の金属コンタクト 670 とを含むスイッチング素子 615 を含む。メモリセル 605 に対する空間方位はこの記載によって限定されることを意味しない。この方位は一般的に、不揮発性メモリセル 605 が金属コンタクトの 1 つに直列に電気的に接続されることを示すよう意図されるのみである(図 6A は第 2 の金属コンタクト 670 に電気的に接続される不揮発性メモリセル 605 を示すが、もちろん第 1 の金属コンタクト 660 であり得る)。

#### 【0063】

図 6B は、不揮発性メモリ素子の構成要素の機能を示す回路図である。図 6B に示されるように、スイッチング素子 615 は、並列の 2 つの個々のダイオード 611 および 612 として機能する。次いで、スイッチング素子 615 は抵抗器として機能する不揮発性メモリセル 605 に直列に接続される。源 680 が与えた電圧により、 $V_{T1}$  (図 1C 参照) より大きな電圧が与えられ、これにより電流が回路を通って 1 方向に流れる。あるいは、 $V_{T2}$  (図 1C 参照) より小さい電圧が与えられ、これにより電流が回路を通って他の方向に流れる。これら 2 つの経路によって、不揮発性メモリセル 605 上においてさまざまな動作が行われることが可能になる。当該動作には、不揮発性メモリセル 605 の抵抗状態を決定することが含まれる。

#### 【0064】

本願明細書において開示されるメモリ素子はメモリアレイにおいて用いられ得る。ある

10

20

30

40

50

実施例では、本願明細書において開示されるメモリ素子は、クロスバー・メモリアレイにおいて用いられ得る。クロスバー・メモリアレイの例示を図7Aに示す。例示的なクロスバー・メモリアレイは、ほぼ並列の導体の第2の層704が重なる（下にある）ほぼ並列の導体の第1の層702を含む。ある実施例では、導体の第2の層704は、導体の第1の層702に対して方位が実質的に垂直であり得る。ある実施例では、層同士の間の方位の角度は垂直以外であってもよい。これら導体の2つの層は、格子またはクロスバーを形成する。当該格子またはクロスバーでは、第2の層704の各導体が第1の層702の導体のすべてに重なり、導体交差部にて第1の層702の各導体と密接する。導体交差部は、2つの導体同士の間のもっとも密接した接触部を示す。図7Aにおける個々の導体は長方形断面にて示されるが、導体は正方形断面、円形断面、橢円断面、または任意の他の規則的または不規則な断面も有し得る。当該導体はさらに多くの異なる幅または直径および縦横比または偏心を有してもよい。

#### 【0065】

上で開示したメモリ素子は、クロスバー・メモリアレイの導体交差部の少なくともいくつかに配置され得る。ある実施例では、開示されるメモリ素子は、導体交差部の実質的にすべてに配置され得る。開示されるメモリ素子によって接続される導体交差部は、「クロスバー接合部」とも称され得る。図7Bおよび図7Cは、クロスバー・メモリアレイ内の2つの隣接している層の導体702aおよび704aを相互接続するクロスバー接合部の2つの異なる図を提供する。クロスバー接合部は、2つの導体702aおよび704aとの間に物理的接触を伴ってもよく、伴わなくてもよい。図7Bに示されるように、2つの導体がそれらの重畠点にて物理的接触しないが、当該2つの導体の間ににおいてそれらのもっとも近い重畠点に存在するメモリ素子706aが導体702aおよび704aの間のギャップにまたがって存在している。図7Cは、メモリ素子706aと、図7Bに示される重なっている導体702aおよび704aの概略図を示す。

#### 【0066】

開示されるメモリ素子はクロスバー・メモリアレイにおいて有利に利用され得る。なぜならば、メモリ素子に含まれるスイッチング装置は、読込動作、書き動作、および消去動作中における意図しないセルに対する漏洩電流による障害を回避または最小化し得る統合された選択素子として機能し得るからである。本願明細書において開示されるスイッチング装置は、S T R A Mと組み合わせると特に有利である。なぜならば、S T R A Mは反対の極性を用いて書きおよび消去動作を行うことを必要とするからである。

#### 【0067】

ショットキーダイオードスイッチおよびショットキーダイオードスイッチを含むメモリユニットの実施例を開示した。上記の実現例および他の実現例は添付の特許請求の範囲内である。当業者ならば、本開示は開示されたものとは別の実施例で実施され得るということを理解するであろう。開示される実施例は限定目的ではなく、例示目的で示される。本開示は添付の特許請求の範囲によってのみ限定される。

【図1A】

【図1B】

【図1C】

【図2A】

【図2B】

【図3】

【図4A】

【図4B】

【図4C】

【図4E】

【図4F】

【図4D】

【図4G】

【図5C】

【図5A】

【図5B】

【図 6 A】

【図 6 B】

【図 7 A】

【図 7 C】

【図 7 B】

---

フロントページの続き

|                |           |              |         |

|----------------|-----------|--------------|---------|

| (51)Int.Cl.    | F I       |              |         |

| H 01 L 45/00   | (2006.01) | H 01 L 27/10 | 4 4 4 Z |

| H 01 L 49/00   | (2006.01) | H 01 L 27/10 | 4 4 7   |

| H 01 L 21/8246 | (2006.01) | H 01 L 29/82 | Z       |

| H 01 L 29/82   | (2006.01) | H 01 L 43/08 | Z       |

| H 01 L 43/08   | (2006.01) | H 01 L 49/02 |         |

| H 01 L 49/02   | (2006.01) |              |         |

(72)発明者 セティアディ，ダディ

アメリカ合衆国、55436 ミネソタ州、エディナ、ジェフ・プレイス、5841

(72)発明者 バイスヤナタン，ベヌゴーパラン

アメリカ合衆国、55437 ミネソタ州、ブルーミントン、ハリソン・ロード、9851、アパートメント・308

(72)発明者 ティエン，ウェイ

アメリカ合衆国、55437 ミネソタ州、ブルーミントン、ウェスト・ナインティエイトス・ストリート、4101、ナンバー・202

(72)発明者 ジン，インシク

アメリカ合衆国、55122 ミネソタ州、イーガン、ジョニー・ケイク・アルコープ、1569

審査官 河合 俊英

(56)参考文献 特開平06-196683(JP,A)

特開平11-186568(JP,A)

特開2007-188603(JP,A)

特開2007-311014(JP,A)

特開2007-311772(JP,A)

特開2007-158325(JP,A)

特開2009-117485(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |               |

|--------|---------------|

| H 01 L | 2 9 / 4 7     |

| H 01 L | 2 1 / 8 2 4 6 |

| H 01 L | 2 7 / 1 0 5   |

| H 01 L | 2 7 / 2 8     |

| H 01 L | 2 9 / 8 2     |

| H 01 L | 2 9 / 8 7 2   |

| H 01 L | 4 3 / 0 8     |

| H 01 L | 4 5 / 0 0     |

| H 01 L | 4 9 / 0 0     |

| H 01 L | 4 9 / 0 2     |

| H 01 L | 5 1 / 0 5     |