## (19) World Intellectual Property **Organization**

International Bureau

(43) International Publication Date 1 April 2004 (01.04.2004)

PCT

## (10) International Publication Number WO 2004/027821 A2

(51) International Patent Classification<sup>7</sup>:

H01L

(21) International Application Number:

PCT/US2003/024385

(22) International Filing Date: 4 August 2003 (04.08.2003)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/246,975 19 September 2002 (19.09.2002) US 10/305,205 26 November 2002 (26.11.2002)

(71) Applicant: COVA TECHNOLOGIES, INC. [US/US]; Suite 105, 5061 North 30th Street, Colorado Springs, CO 80919 (US).

(72) Inventors: GNADINGER, Alfred, P.; 19 Learning Road, Colorado Springs, CO 80906 (US). DIMMLER, Klaus; 495 Vanderbilt Ct., Colorado Springs, CO 80906 (US).

(74) Agent: BURTON, Carol, W. à; Hogan & Hartson LLP, Suite 1500, 1200 Seventeenth Street, Denver, CO 80202 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, YU, ZA, ZM, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: FERROELECTRIC TRANSISTOR FOR STORING TWO DATA BITS

(57) Abstract: A method of storing and accessing two data bits in a single ferroelectric FET includes selectively polarizing two distinct ferroelectric regions in the same gate dielectric layer separated by a non-ferroelectric dielectric region. A first ferroelectric region is sandwiched between the substrate and the gate terminal in the region of the source and is polarized in one of two states to form a first data bit within the FET. A second ferroelectric region is sandwiched between the substrate and the gate terminal in the region of the drain and is polarized in one of two states to form a second data bit within the FET. Detection of the first data bit is accomplished by selectively applying a read bias to the FET terminals, a first current resulting when a first state is stored and a second current resulting when a second state is stored. The polarization of the second data bit is accomplished by reversing the source and drain voltages.

#### FERROELECTRIC TRANSISTOR FOR STORING TWO DATA BITS

#### FIELD OF THE INVENTION

The invention disclosed relates generally to memory cells, and more particularly to ferroelectric nonvolatile memory cells.

# 5 BACKGROUND OF THE INVENTION

10

15

20

25

30

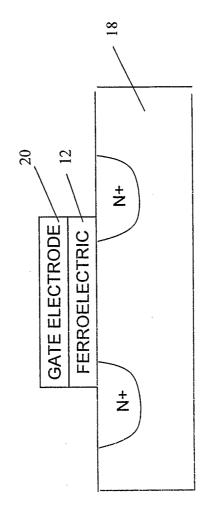

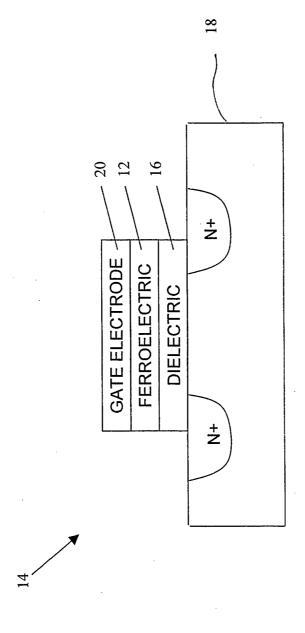

Ferroelectric transistors are structurally identical to metal-oxide-silicon field effect transistor (MOSFET) devices with the gate oxide layer replaced by a ferroelectric material layer 12, as shown in FIG. 1. The polarization state of the ferroelectric material layer 12 gives rise to an electric field, which shifts the turn-on threshold voltage of the device 10. Transistors known in the prior art often include a non-ferroelectric dielectric layer 16 between the ferroelectric material and the silicon substrate 18, as shown in the device 14 of FIG. 2. This dielectric layer 16 generally has several purposes at the silicon/ferroelectric interface including avoidance of uncontrolled growth of silicon dioxide, avoidance of high electric fields at the interface, separating the ferroelectric materials from the silicon, avoidance of crystal lattice structure mismatch between the silicon and the ferroelectric materials, and keeping hydrogen away from the ferroelectric materials. Such a dielectric layer 16 is sometimes also placed between the top electrode layer 20 and the ferroelectric layer 12 for the same reasons. These devices, such as devices 10 and 14 and variants thereof, are utilized in arrays of rows and columns to form one-transistor ("1T") non-volatile ferroelectric memories.

When a voltage greater than a coercive voltage is applied across the ferroelectric material, the ferroelectric material polarizes in the direction aligning with the electric field. When the applied voltage is removed, the polarization state is preserved. When a voltage greater than the coercive voltage is applied to the ferroelectric material in the opposite direction, the polarization in the ferroelectric material reverses. When that electric field is removed, the reversed polarization state remains in the material. The electric field generated by the polarization offsets the natural turn-on threshold of the transistors, effectively shifting the turn-on thresholds of the transistors. By

5

10

15

20

25

30

applying known voltages less than the coercive voltage on the terminals of the transistor, the state of the polarization within the ferroelectric material can be detected without altering the stored polarization states, a method known in the prior art as non-destructive read-out.

These devices are generally electrically connected in an array of rows and columns with common row signals and column signals to form a memory array. A common figure of merit to establish manufacturing costs of these memory arrays is the area utilized per data bit. When utilized in an array of this type, many prior art configurations require additional transistors to provide for the selection of a single device within the array.

What is desired, therefore, is a minimum area ferroelectric non-volatile memory cell structure and a method of biasing such that a single one-transistor memory cell capable of storing two data bits can be written to and accessed without disturbing other cells within an array.

# **SUMMARY OF THE INVENTION**

According to principles of the present invention, a novel apparatus and method of storing and accessing two bits in a single ferroelectric FET (field effect transistor) exhibiting hysteresis, each FET having gate, source, and drain. terminals and a substrate is disclosed. Ferroelectric material sandwiched between the substrate and the gate terminal in the region of the source is polarized in one of two states to form a first data bit within the FET. Ferroelectric material sandwiched between the substrate and the gate terminal in the region of the drain is polarized in one of two states to form a second data bit within the FET. Non-ferroelectric dielectric is sandwiched between the substrate and the gate terminals in regions between the ferroelectric material in the source region and the ferroelectric material in the drain region. The polarization of the ferroelectric material in the source region changes the threshold voltage of the FET regardless of the polarization state in the drain region. Accordingly, the detection of the first data bit, determined by the polarization state of the material in the source region, is accomplished by applying a read bias to the FET terminals, a first current resulting when a first state is stored and a second current resulting when a second state is stored. The polarization of the

second data bit is accomplished by reversing the source and drain voltages. The FETs are electrically connected in an array of rows and columns, the gates of the FETs in a common row connected by a common word line, the sources of the FETs in a common column sharing a common bit line, the drains of the FETs in a common column sharing a common bit line, and the substrate of all FETs sharing a common substrate. Appropriate write voltage biasing of the word lines, bit lines, and substrate provides means for polarizing a single ferroelectric region of a single FET within the array, while leaving the polarization of all other ferroelectric regions unchanged.

5

15

30

Appropriate read voltage biasing of the word lines, bit lines, and substrate provides means for detection of the polarization state of a single ferroelectric region of a single FET within the array, a first bit line current determining a first state and a second bit line current determining a second state.

The foregoing and other objects, features and advantages of the invention will become more readily apparent from the following detailed description of a preferred embodiment of the invention, which proceeds with reference to the accompanying drawings.

#### **DESCRIPTION OF THE DRAWINGS**

Figure 1 is a cross section of a ferroelectric transistor as known in the 20 prior art.

Figure 2 is a cross section of a ferroelectric transistor with a bottom buffer layer as is known in the prior art.

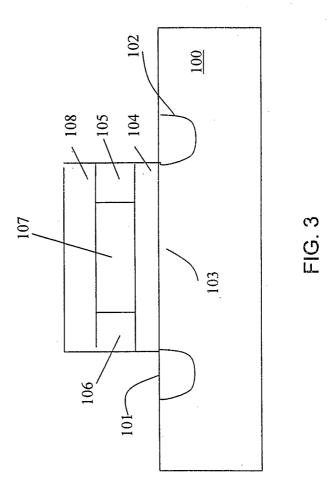

Figure 3 is a cross sectional view illustrating the structure of a ferroelectric FET according to one embodiment of the present invention.

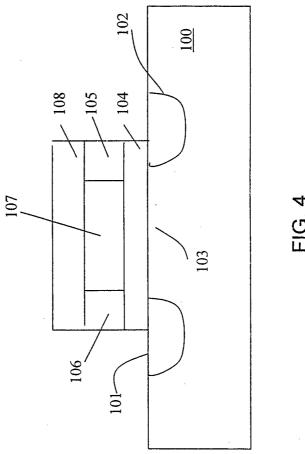

Figure 4 illustrates the structure of a ferroelectric FET according to a second embodiment of the present invention wherein the n-type source and drain regions partially or fully overlap the ferroelectric regions.

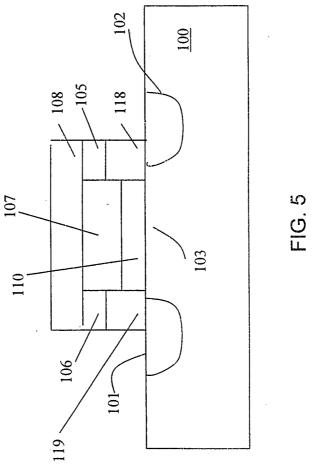

Figure 5 illustrates a third embodiment wherein the buffer layers below the ferroelectric regions are made of different materials and have a different thickness than the dielectric between the ferroelectric regions.

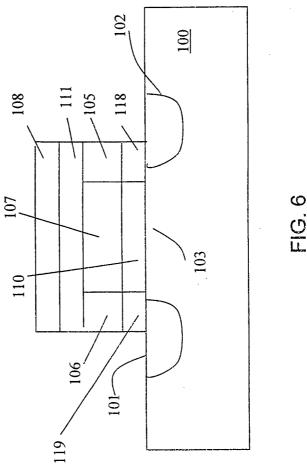

Figure 6 illustrates a fourth embodiment wherein the top buffer layer is formed between the gate electrode and the top dielectric layer.

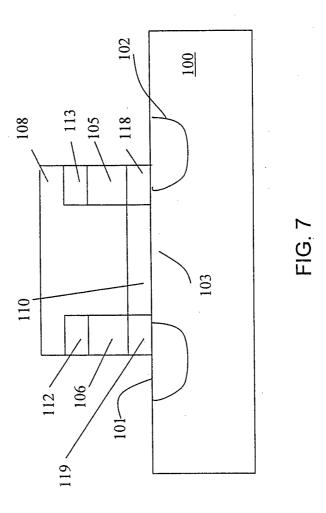

Figure 7 illustrates a fifth embodiment wherein the top buffer layers are formed over the ferroelectric regions.

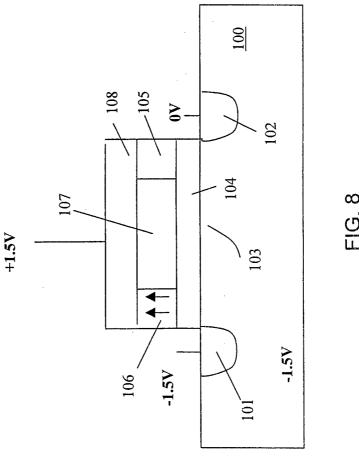

Figure 8 illustrates an example of the applied voltages to the ferroelectric transistor structure in order to polarize a left ferroelectric region to one state.

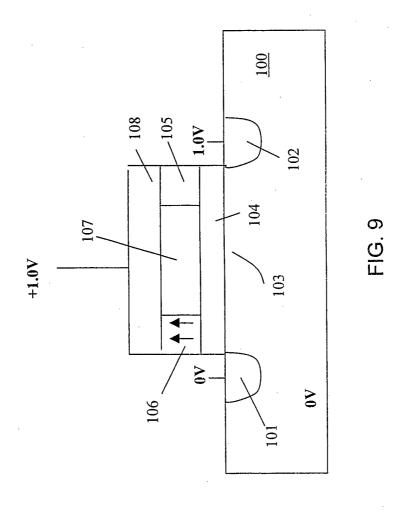

Figure 9 illustrates an example of a read bias of the ferroelectric FET wherein one n-type region acts as a source.

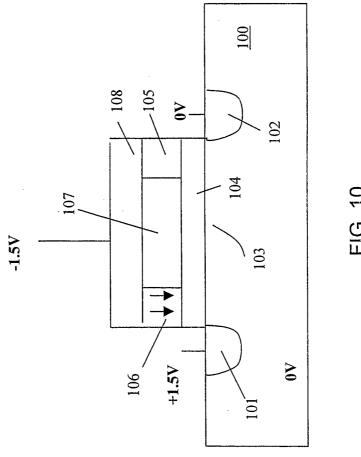

Figure 10 illustrates an example of a bias that polarizes the ferroelectric material in a left region to a "high state".

5

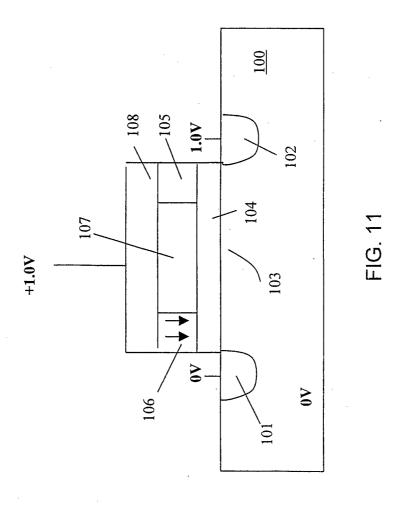

Figure 11 illustrates an example of a read bias of the ferroelectric FET wherein an n-type region acts as a source when the ferroelectric material of region is polarized in the high state.

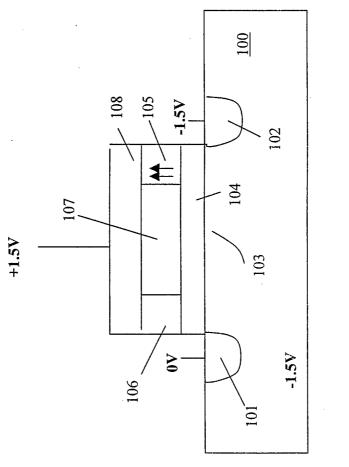

Figure 12 illustrates an example of the applied voltages to the ferroelectric transistor structure in order to polarize right ferroelectric region to a "low state".

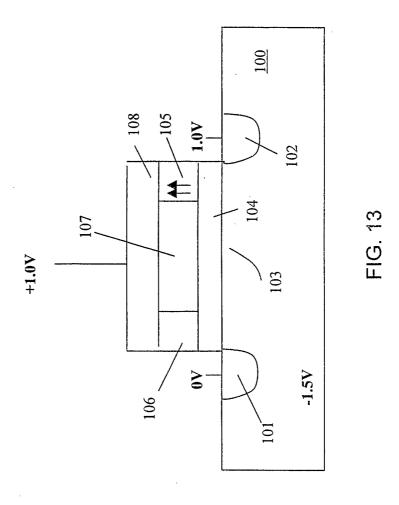

Figure 13 illustrates an example of a read bias of the ferroelectric FET wherein an n-type region acts as a source.

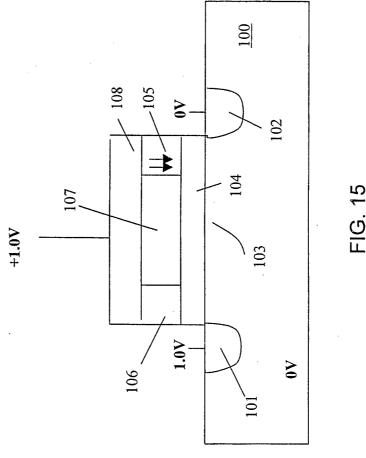

Figure 14 illustrates an example of a bias that polarizes the ferroelectric material in a right region to a "high state".

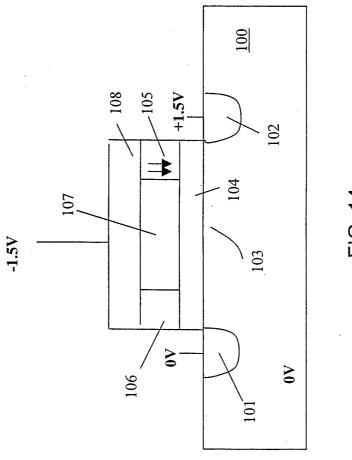

Figure 15 illustrates an example of a read bias of the ferroelectric FET wherein an n-type region acts as a source.

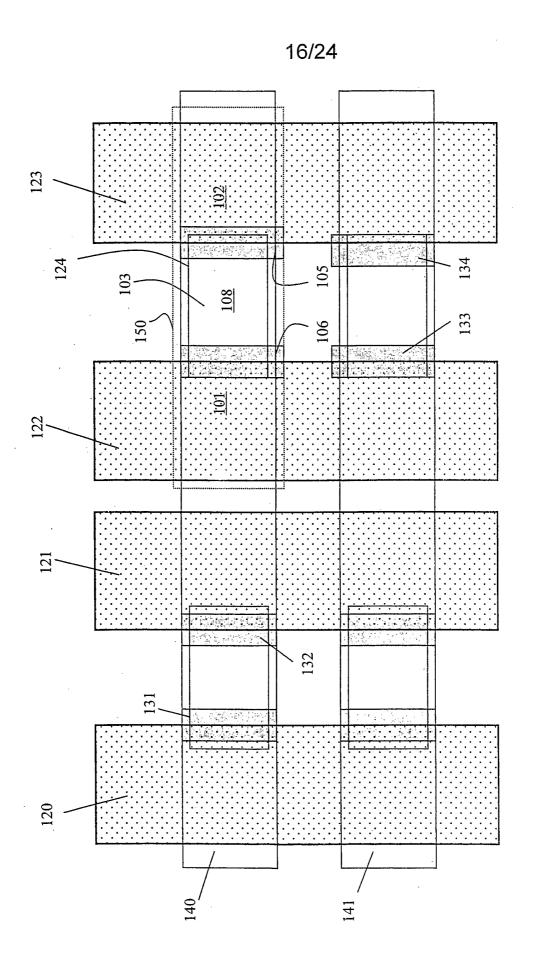

Figure 16 is a plan view diagram illustrating the ferroelectric FET structures placed and electrically connected in rows and columns to form a memory array.

Figure 17 illustrates another embodiment wherein the ferroelectric material is removed between the word lines.

Figure 18 is a schematic diagram illustrating the connection of ferroelectric FETs connected in rows and columns to form a memory array.

Figure 19 is a schematic diagram indicating a bias on the columns and rows to polarize the left ferroelectric region of an FET to a low state according to the present invention.

5

20

25

30

Figure 20 is a schematic diagram indicating a bias on the columns and rows to polarize the left ferroelectric region of an FET to a high state according to the present invention.

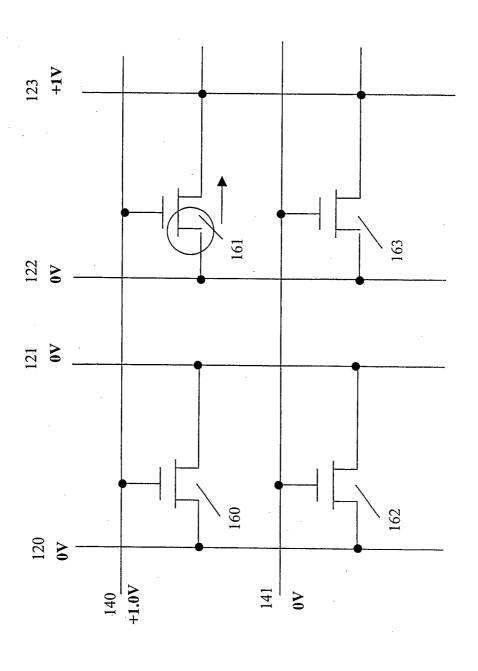

Figure 21 is a schematic diagram indicating a bias on the columns and rows to read the polarized state of the left ferroelectric region of an FET according to the present invention.

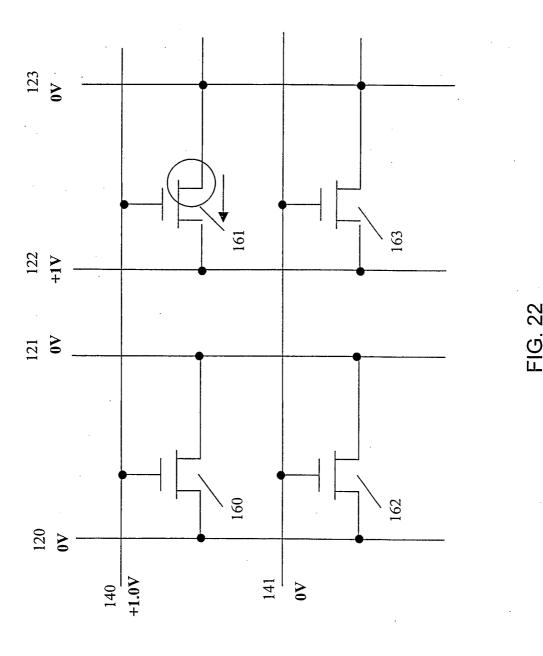

Figure 22 is a schematic diagram that illustrates the biasing in order to read the polarization of the right ferroelectric region of an FET according to the present invention.

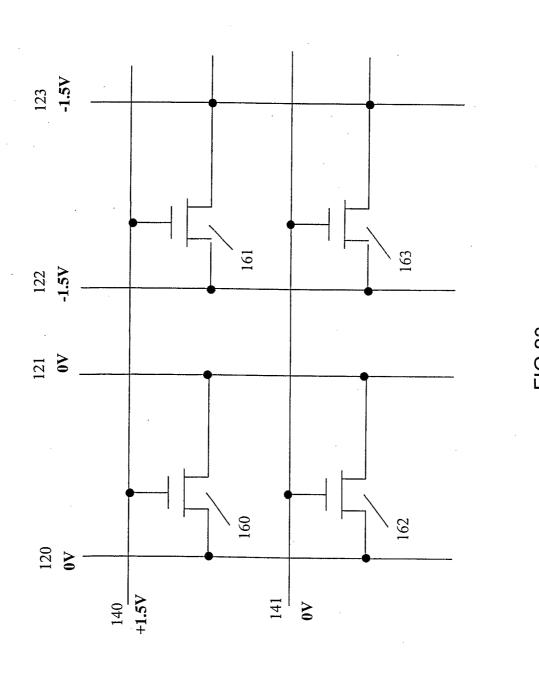

Figure 23 is a schematic diagram that illustrates the biasing of an initial stage of a multiple stage write sequence according to the present invention.

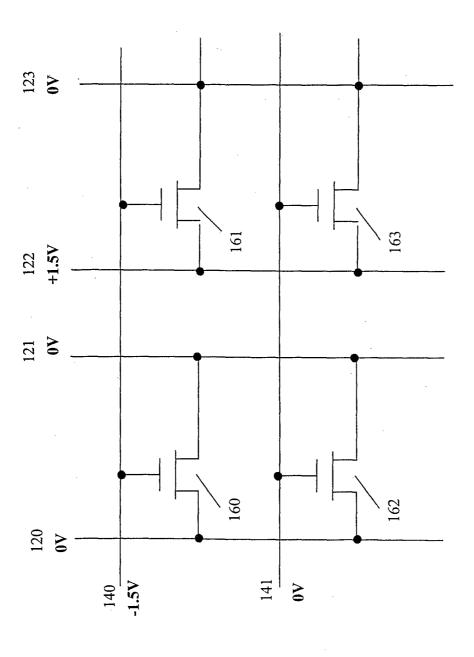

Figure 24 is a schematic diagram that illustrates the biasing of another stage of a multiple stage write sequence according to the present invention.

## **DETAILED DESCRIPTION OF THE INVENTION**

The present invention discloses a ferroelectric transistor structure exhibiting hysteresis wherein two storage bits are stored in a single device. Figure 3 is a cross sectional view illustrating the structure of a ferroelectric FET according to one embodiment of the present invention. In a first embodiment, n-type silicon regions 101 and 102 are formed within p-type silicon substrate 100, the region between them disposing the channel region 103. A dielectric buffer layer 104 is formed on the channel region 103. Ferroelectric regions 105 and 106 are formed on dielectric buffer layer 104 in the vicinity of source 101 and drain 102, and a non-ferroelectric gate oxide layer 107 is formed between these ferroelectric regions 105 and 106. A gate electrode layer 108 is formed on top of dielectric layer 107 and ferroelectric

5

10

15

20

25

30

regions 105 and 106. In operation, ferroelectric region 105 stores one bit and ferroelectric region 106 stores another bit.

Ferroelectric regions 105 and 106 can be formed using a sidewall processing technique. The non-ferroelectric gate dielectric 107 is deposited on the buffer layer 104 and patterned, followed by a deposition of a ferroelectric layer. The ferroelectric layer is then planarized using techniques such as chemical mechanical polishing (CMP), thereby removing the ferroelectric material from the top of non-ferroelectric dielectric gate oxide layer 107 but leaving the ferroelectric material on the sides of dielectric gate oxide 107 layer, forming ferroelectric regions 105 and 106 on the sides of dielectric gate oxide layer 107. The ferroelectric material utilized can be any material exhibiting hysteresis, including ferroelectrics with low dielectric constants and materials having the general formula A<sub>x</sub>Mn<sub>y</sub>O<sub>z</sub>, where x, y, z vary from 0.1 to 10 and A is a rare earth selected from a group consisting of Ce, Pr, Nd, Pm, Sm, Eu, GD, Tb, Dy, Ho, Er, Tm, Yb, Lu, Y or Sc. Ferroelectric materials with low dielectric constants increase the component of voltage across the ferroelectric layer when a voltage is applied across a structure consisting of buffer dielectric layers and ferroelectric layers. Such materials can be produced by any of a variety of methods including sputtering. spin-on gels, and MOCVD (metal-oxide-chemical-vapor-deposition).

Materials used as the dielectric layer include silicon nitride, silicon dioxide, thermally grown silicon dioxide, and dielectric materials with high dielectric constants. Buffer dielectric materials with high dielectric constants increase the component of voltage across the ferroelectric layer when a voltage is applied across a structure consisting of buffer dielectric layers and ferroelectric layers. More than one material can be layered to form the dielectric layer such as a silicon nitride layer overlying a silicon dioxide layer. Such materials can be formed by any of a variety of methods including ALD (atomic layer deposition), sputtering, and MOCVD.

Materials used as the electrode layer include metals, doped polysilicon, and metal silicides.

Figure 4 illustrates a second embodiment wherein the n-type region of source 101 and 102 partially or fully overlaps ferroelectric regions 106 and 105, respectively.

The substrate is a CMOS compatible silicon substrate or a silicon-on-insulator substrate or the like.

5

10

15

20

25

30

Figure 5 illustrates a third embodiment wherein buffer layer 118 and 119 under ferroelectric regions 105 and 106, respectively, are formed with a different material and a different thickness from buffer layer 110 under non-ferroelectric gate oxide 107.

Figure 6 illustrates a fourth embodiment wherein top buffer layer 111 is formed between the gate electrode 108 and the layer consisting of ferroelectric region 105, gate oxide layer 107, and ferroelectric region 106. In this embodiment, this top buffer layer serves to reduce high electric fields at the gate electrode/ferroelectric interface, to contain the ferroelectric materials within an encapsulated region, to reduce leakage currents, and to keep hydrogen away from the ferroelectric materials.

Figure 7 illustrates a fifth embodiment wherein top buffer layers 113 and 112 are formed over ferroelectric regions 105 and 106, respectively. In this embodiment, no buffer layer is formed between gate electrode layer 108 and the bottom oxide layer 110.

Figure 8 illustrates an example of the voltages applied to the ferroelectric transistor structure in order to polarize left ferroelectric region 106 to one state, herein referred to as the "low state". A voltage of +1.5V is applied to the gate electrode,

-1.5V is applied to n-type region 101, 0V is applied to n-type region 102, and -1.5V is applied to substrate 100, thereby avoiding a forward bias condition between n-type region 101 and substrate 100. The applied voltage between n-type region 101 and electrode 108 determines the electric field strength on ferroelectric region 106, while the applied voltage between n-type region 102 and electrode 108 determines the field strength on ferroelectric region 105. For the purposes of illustration, the coercive voltage is assumed

to be 2V. Accordingly, the polarization of ferroelectric region 105 remains unchanged since the applied voltage between n-type region 102 and electrode 108 is 1.5V, less than the coercive voltage. The voltage between n-type region 101 and electrode 108 is 3V, greater than the coercive voltage. It is assumed for the purposes of illustration that voltage drops across bottom buffer layer 104 and the top buffer layer, if there is one, are sufficiently small due to appropriate dielectric constants and thicknesses in order to produce at least a coercive voltage across ferroelectric region 106. Accordingly, ferroelectric region 106 polarizes to a low state.

5

10

15

20

25

30

When the applied voltages are removed, the ferroelectric polarization remains. Since ferroelectric region 106 is in the vicinity of n-type region 101, the electric field affects the turn-on threshold voltage when n-type region 101 is operated as the source of the transistor. The direction of the electric field produced when ferroelectric region 106 is polarized to the "low state" causes the turn-on threshold to be lower than if that same region were not polarized. For the purposes of illustration, the threshold voltage corresponding to the low state is 0.5V.

Figure 9 illustrates an example of a read bias of the ferroelectric FET wherein n-type region 101 acts as a source. A voltage of 1.0V is applied to gate electrode 108, 0V to n-type region 101 thereby acting as the source, 1.0V to n-type region 102 thereby acting as a drain, and 0V to substrate 100. Assuming that ferroelectric region 106 is polarized to the low state, the turn-on threshold of the FET is 0.5V. The polarization of the ferroelectric material in region 105 does not affect the threshold voltage since the channel is pinched off in this region, and carriers are injected from the point of pinch-off to the depletion region around the drain. Therefore a current flows from source 101 to drain 102 in this device.

Figure 10 illustrates an example of a bias that polarizes the ferroelectric material in region 106 to a "high state". A voltage of -1.5V is applied to the gate electrode, +1.5V is applied to n-type region 101, 0V is applied to n-type region 102, and 0V is applied to substrate 100. The applied voltage between n-type region 101 and electrode 108 is higher than the

coercive voltage, and the electric field is in the direction to polarize the ferroelectric material to a "high state". For purposes of illustration, the threshold voltage corresponding to the high state is 1.5V.

5

10

15

20

25

30

Figure 11 illustrates an example of a read bias of the ferroelectric FET wherein n-type region 101 acts as a source when the ferroelectric material of region 106 is polarized in the high state. A voltage of 1.0V is applied to gate electrode 108, 0V to n-type region 101 thereby acting as the source, 1.0V to n-type region 102 thereby acting as a drain, and 0V to substrate 100. For the sake of illustration, it is assumed that when the ferroelectric region 106 is polarized to the high state, the turn-on threshold of the FET is 1.5V. The polarization of the ferroelectric material in region 105 does not affect the threshold voltage since the channel in this region is depleted. Since the turn-on threshold voltage is higher than the gate-to-source voltage, no current flows through this device.

Figure 12 illustrates an example of the voltages applied to the ferroelectric transistor structure in order to polarize right ferroelectric region 105 to the "low state". A voltage of +1.5V is applied to the gate electrode, 0V is applied to n-type region 101, -1.5V is applied to n-type region 102, and -1.5V is applied to substrate 100, thereby avoiding a forward bias condition between n-type region 102 and substrate 100. The applied voltage between n-type region 102 and electrode 108 is greater than the coercive voltage. while the voltage between n-type region 101 and gate electrode 108 is less than the coercive voltage. Accordingly, the polarization of ferroelectric region 106 remains unchanged since the applied voltage between n-type region 101 and electrode 108 is 1.5V, less than the coercive voltage. The voltage between n-type region 102 and electrode 108 is 3V, greater than the coercive voltage. It is assumed for the purposes of illustration that voltage drops across bottom buffer layer 104 and the top buffer layer 108, if there is one, are sufficiently small to allow at least a coercive voltage across ferroelectric region 105. Accordingly, ferroelectric region 105 is polarized to the low state.

Figure 13 illustrates an example of a read bias of the ferroelectric FET wherein n-type region 102 acts as a source. A voltage of 1.0V is applied to

gate electrode 108, 0V to n-type region 102 thereby acting as the source, 1.0V to n-type region 101 thereby acting as a drain, and 0V to substrate 100. Assuming that ferroelectric region 105 is polarized to the low state, the turn-on threshold of the FET is 0.5V. The polarization of the ferroelectric material in region 106 does not affect the threshold voltage since the channel in this region is depleted. Therefore a current flows from source 102 to drain 101 in this device.

5

10

15

20

25

30

Figure 14 illustrates an example of a bias that polarizes the ferroelectric material in region 105 to a high state. A voltage of -1.5V is applied to the gate electrode, 0V is applied to n-type region 101, +1.5V is applied to n-type region 102, and 0V is applied to substrate 100. The applied voltage between n-type region 102 and electrode 108 is higher than the coercive voltage; the electric field is the direction to polarize the ferroelectric material to a high state, corresponding to a turn-on threshold of 1.5V.

Figure 15 illustrates an example of a read bias of the ferroelectric FET wherein n-type region 102 acts as a source and the ferroelectric region 105 is polarized to the high state. A voltage of 1.0V is applied to gate electrode 108, 0V to n-type region 102 thereby acting as the source, 1.0V to n-type region 101 thereby acting as a drain, and 0V to substrate 100. Assuming that ferroelectric region 105 is polarized to the high state, the turn-on threshold of the FET is 1.5V. The polarization of the ferroelectric material in region 106 does not affect the threshold voltage since the channel in this region is depleted. Therefore, no current flows between source 102 to drain 101 in this device.

Optionally, the voltages used to polarize the ferroelectric regions 105 and 106 can be made significantly larger in magnitude than the voltages used to read the data state. For example, the voltages used to polarize the ferroelectric material might be 5V, while the peak read voltages used are 1V. Successive voltages applied to the device during the read, though less than the coercive voltage, nevertheless may alter the polarization of some ferroelectric materials. By using voltages for read that are low relative to the

polarization voltage, potential disturbs to the polarization state that might result are minimized.

5

10

15

20

25

30

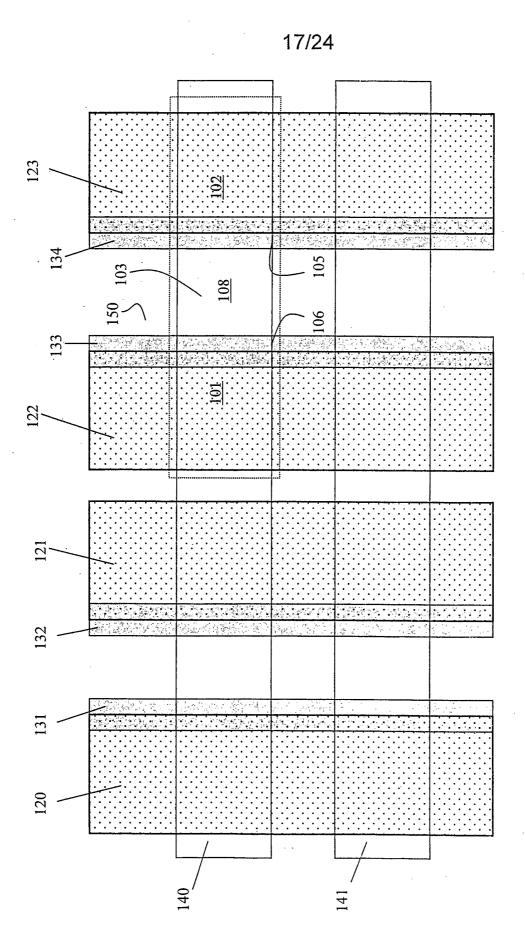

Figure 16 is a plan view diagram illustrating the ferroelectric FET structures placed and electrically connected in rows and columns to form a memory array. Gate electrodes of FETs in any given row of the array are connected with a word line. In one embodiment, the word line consists of a strip of conductive thin film 140 or 141 across the array, consisting of any conductive material including platinum, aluminum, polysilicon, and silicides. The source and drains of FETs in any given column of the array are electrically connected. In one embodiment, sources of FETs in a given column are connected with strips of n-type material formed in a p-type substrate, such as buried bit line 122 of FIG. 16. Drains are similarly connected with buried bit line 123. Active area 124 span the area under the word between bit line 122 and 123, defining an area of thin silicon dioxide to make up the channel region. Regions outside the active area are covered with a thick layer of silicon dioxide to make up the field region between the transistors. The ferroelectric material is formed on the inside edges of the buried bit line where the bit line intersects the word line. For example, ferroelectric material 133 and 134 are formed along the inside edge of bit line 122 and 123, respectively. This ferroelectric material may overlap, partially overlap, or underlap the buried bit line.

The region 150 of FIG. 16 is a single cell within the memory array, each terminal marked with the same numbers as used in the cross sectional diagram of Figure 15. Bit line 122 and bit line 123 under word line 140 form n-type region source/drain 101 and source/drain 102, respectively. The region between source/drain 101 and 102 disposes the channel region 103. Above channel 103 is the gate electrode 108. Ferroelectric regions 105 and 106 in the memory cell are formed where bit line 122 and 123 intersect word line 140, respectively.

Figure 17 illustrates another embodiment wherein the ferroelectric material is not removed between the word lines. The ferroelectric material

without an overlying word line is electrically inactive since the ferroelectric material in those areas has no top electrode.

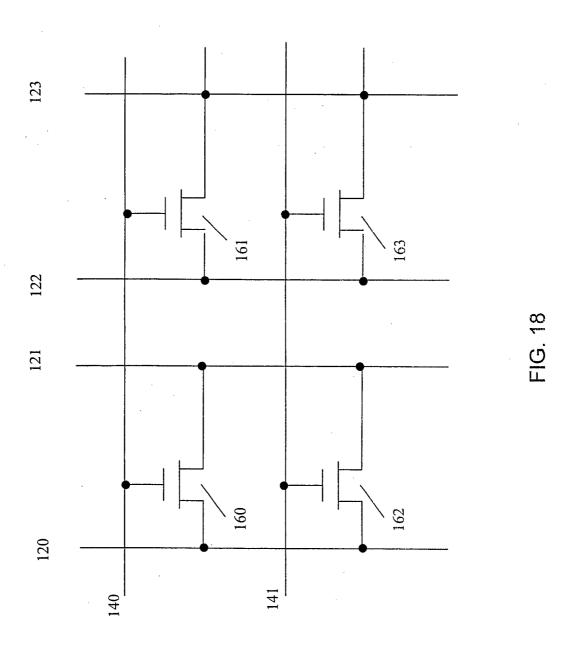

Figure 18 is a schematic diagram illustrating the connection of ferroelectric FETs connected in rows and columns to form a memory array. The diagram shows word line 140 connecting the gates of FETs 160 and 161, and word line 141 connecting the gates of FETs 162 and 163. Columns 120 and 121 connects the sources and drains of FETs 160 and 162. Columns 122 and 123 connect the sources and drains of FETs 161 and 163.

5

10

15

20

25

30

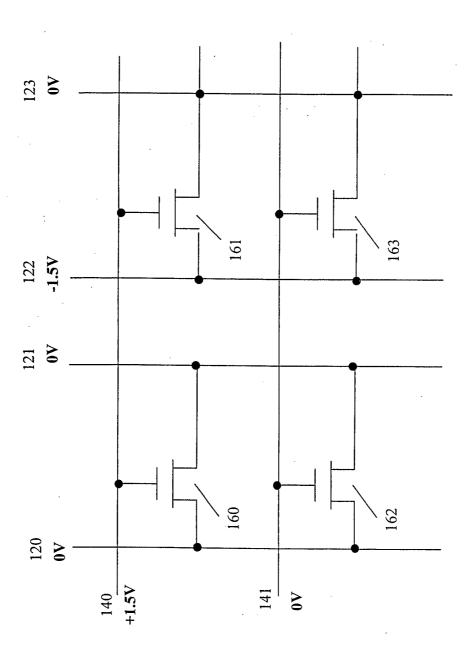

Figure 19 is a schematic diagram indicating a bias on the columns and rows to polarize the left ferroelectric region of FET 161 to a low state. A voltage of -1.5V is applied to the selected bit line 122, and +1.5V on selected word line 140. A voltage of -1.5V is applied to the substrate to avoid the n-type regions forward biasing to the substrate. More than a coercive voltage is thereby applied across left ferroelectric region of FET 161, polarizing it to a low state. OV is applied to unselected word lines and bit lines, thereby applying less than a coercive voltage to right ferroelectric region of FET 161, and so this polarization stays unchanged. This same bias is applied to the left and right ferroelectric regions of FETs along the selected word line on deselected bit lines, for example FET 160 of FIG. 19. FET 163 illustrates that less than a coercive voltage is also applied to an FET on a deselected word line but selected bit line. FET 162 is an example of an FET bias on a deselected word line and deselected bit lines. In this case, no electric field is applied across the ferroelectric regions of the device, thereby leaving the polarization unchanged.

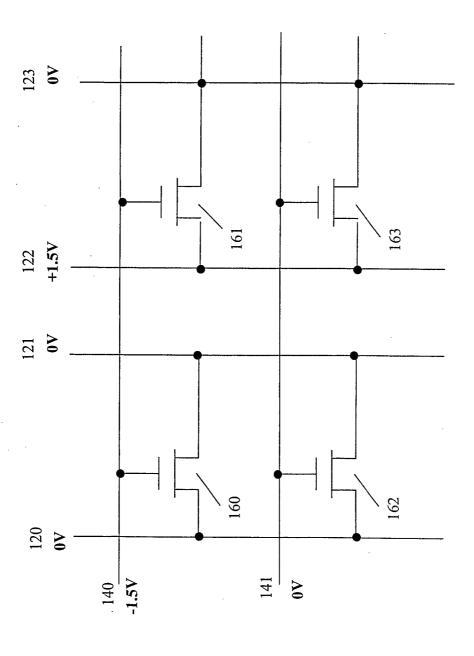

Figure 20 is a schematic diagram indicating a bias on the columns and rows to polarize the left ferroelectric region of FET 161 to a high state. A voltage of +1.5V is applied to the selected bit line 122, and -1.5V on selected word line 140. The substrate is biased to 0V. More than a coercive voltage is thereby applied across left ferroelectric region of FET 161, polarizing it to a high state. 0V is applied to unselected word lines and bit lines, thereby applying less than a coercive voltage to right ferroelectric region of FET 161, and so this polarization stays unchanged. This same bias is applied to the left

and right ferroelectric regions of FETs along the selected word line on deselected bit lines, for example FET 160 of FIG. 20. FET 163 illustrates that less than a coercive voltage is also applied to an FET on a deselected word line but selected bit line. FET 162 is an example of an FET bias on a deselected word line and deselected bit lines. In this case, no electric field is applied across the ferroelectric regions of the device, thereby leaving the polarization unchanged.

5

10

15

20

25

30

Figure 21 is a schematic diagram indicating a bias on the columns and rows to read the polarized state of left ferroelectric region of FET 161. A voltage of +1.0V is applied to selected word line 140. 0V is applied to the bit line connected to the left n-type region of FET 161, that n-type region thereby acting as the source. The gate-to-source voltage is therefore 1.0V. 1.0V is applied to the other n-type region of FET 161, thereby acting as the drain. If the high state is stored on the left ferroelectric, FET 161 remains off since the turn-on threshold of FET 161 would then be 1.5V, higher than the applied gate-to-source voltage. If a low state is stored in the left ferroelectric, FET 161 turns on since the turn-on threshold of the FET is 0.5V, less than the gate-to-source voltage.

No current flows through any other device in the array. The FETs along the selected word line, such as FET 160, have 0V on both the source and drain. The FETs along the unselected word line, such as FETs 162 and 163, have 0V on the gate.

Figure 22 illustrates the biasing in order to read the polarization of the right ferroelectric region of FET 161. Biasing is identical to FIG. 21, except that the voltages on bit line 122 and 123 are reversed. Now the right n-type region acts as source of FET 161. Measuring the resulting current determines the polarization state, high current corresponding to a low state and low current corresponding to a high state.

It should be noted that the method of array biasing described above results in current flow through the selected device during programming. Referring to Figure 19, the biasing results in a current flow through the selected FET 161 between bit line 122 and bit line 123. In some circuit

5

10

15

20

25

30

methods, the –1.5V on bit line 122 is created by capacitive pumping of positive voltages, a method that cannot tolerate large current drains from the negative power supply. In another embodiment of this invention, utilizing a multiple stage write method eliminates this current.

Figure 23 illustrates the first stage of this write sequence, wherein bit lines 122 and 123 are biased to –1.5V. Since the source and drain of FET 161 are now at the same electrical potential, no current flows through the device. This bias causes both the left and the right ferroelectric gate regions of FET 161 to be polarized to the low state.

Figure 24 illustrates a second stage of this write sequence, wherein word line 140 is based to –1.5V, bit line 122 is biased to +1.5V and bit line 123 is biased to 0V. In this bias condition, FET 161 is in an off state and therefore does not conduct current. The electric field across the left ferroelectric gate region is higher than the coercive voltage, and so the left ferroelectric gate region now polarizes to the high state. The bias across the right ferroelectric region is less than the coercive voltage, and so the right ferroelectric region remains unchanged from the low state to which it was polarized in the previous stage of the write cycle. The right ferroelectric gate region could be programmed to a high state by bringing bit line 123 to +1.5V, in which case the electric field across the right ferroelectric region would have been greater than the coercive voltage. Similarly, the polarization of the left ferroelectric would remain unchanged if bit line 122 had been brought to 0V, in which case the left ferroelectric region would be polarized in a low state to which it was programmed in the previous cycle.

This multiple stage write cycle programs two bits within the array at one time, namely the left and the right ferroelectric regions of FET 161. By reading the polarization of the left and right ferroelectric regions and storing the data in a latch on the perimeter of the array before applying the write cycle, a data bit to which no polarization change is desired could be written back. This process enables this array configuration to be used in situation where it is desired to change the polarization of only one bit in the array during a single write cycle sequence.

5

10

The foregoing description is only illustrative of the invention. Various alternatives and modifications can be devised by those skilled in the art without departing from the invention. In particular, though reference to a ferroelectric FET formed on a P-type silicon substrate and N-type source and drain regions has been made, the ferroelectric FET can also be formed on N-type substrate with P-type source and drain regions. Though mention is made of a single dielectric buffer layer, this layer could be composed of multiple layers without departing from the invention. Though specific bias voltages are described in the foregoing description, other voltage values can be utilized without departing from the present invention. Accordingly, the present invention embraces all such alternatives, modifications, and variances that fall within the scope of the appended claims.

#### **CLAIMS**

What is claimed is:

5

10

30

1. A ferroelectric field effect transistor (FET) exhibiting hysteresis, comprising:

a semiconductor substrate of a first conductivity type;

a source, said source comprising a region of said semiconductor substrate doped to have a conductivity opposite that of said semiconductor substrate;

a drain, spaced from said source, said drain comprising a portion of said semiconductor substrate doped to have a conductivity opposite of said substrate;

a channel being formed in the space between said source and said drain:

a gate dielectric layer comprising a first ferroelectric region overlaying

the channel in the vicinity of the source, a second ferroelectric region

overlaying the channel in the vicinity of the drain, and a non-ferroelectric

dielectric overlaying the channel between the first and second ferroelectric

region; and

a conductive electrode layer overlaying said gate dielectric layer.

- 20 2. The FET of claim 1 wherein first and second ferroelectric regions are formed utilizing sidewall deposition processing techniques.

- 3. The FET of claim 1 further comprising a dielectric layer formed between said gate dielectric layer and conductive electrode layer.

- 4. The FET of claim 1 further comprising a dielectric layer formed between said channel and said gate dielectric layer.

- 5. The FET of claim 1 further comprising a dielectric layer formed between the channel and the ferroelectric regions of said gate dielectric layer.

- 6. The FET of claim 1 further comprising a dielectric layer formed between said conductive layer and the ferroelectric regions of said gate dielectric layer.

7. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer comprises silicon nitride.

- 8. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer comprises silicon dioxide.

- 5 9. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer comprises thermally grown silicon dioxide.

- 10. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer comprises two or more dielectric sub-layers.

- 11. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer10 comprises a silicon nitride layer overlying a silicon dioxide layer.

15

- 12. The FET of claim 1 wherein the conductive electrode layer comprises a polysilicon-containing material.

- 13. The FET of claim 1 wherein the ferroelectric layer comprises a material having the general formula  $A_xMn_yO_z$  where x, y, z vary from 0.1 to 10 and A is a rare earth selected from a group consisting of Ce, Pr, Nd, Pm, Sm, Eu, GD, Tb, Dy, Ho, Er, Tm, Yb, Lu, Y or Sc.

- 14. The FET of claim 1 wherein the ferroelectric layer comprises a low-dielectric ferroelectric material.

- 15. The FET of claim 1 wherein the ferroelectric layer is formed utilizing MOCVD.

- 16. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer is formed utilizing MOCVD.

- 17. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer is formed utilizing ALD.

- 25 18. The FET of claim 3, 4, 5 or 6 wherein the dielectric layer comprises a material with a dielectric constant of 10 and greater.

19. The FET of claim 1 wherein the silicon substrate comprises a CMOS compatible substrate.

- 20. The FET of claim 1 wherein the silicon substrate comprises a silicon-on-insulator substrate.

- 21. A method for the non-volatile storage of two data bits in a single FET transistor comprising:

5

10

15

20

25

30

providing a field effect transistor (FET) having gate, drain, source, and substrate terminals, and having a first ferroelectric region between the gate and the source and a second ferroelectric region between the gate and the drain;

applying a positive voltage greater than the coercive voltage between the gate and the source to polarize said first ferroelectric region to a first state;

applying a negative voltage greater than the coercive voltage between the gate and source to polarize said first ferroelectric region to a second state;

applying a positive voltage greater than the coercive voltage between the gate and the drain to polarize said second ferroelectric region to the first state;

applying a negative voltage greater than the coercive voltage between the gate and the drain to polarize said second ferroelectric region to the second state;

applying a positive voltage less than the coercive voltage on the gate, ground potential on the source, and a positive voltage no greater than the gate voltage on the drain to detect the polarization state of said first ferroelectric region, a high current between source and drain indicating the first state and a low current between source and drain indicating the second state; and

applying a positive voltage less than the coercive voltage on the gate, ground potential on the drain, and a positive voltage no greater than the gate voltage on the source to detect the polarization state of said second ferroelectric region, a high current between source and drain indicating the first state and a low current between source and drain indicating the second state.

22. A non-volatile memory storage method comprising: providing an array of field effect transistors (FETs), wherein each FET in the array has a gate, drain, source, and substrate terminals, a first ferroelectric region between the gate and the source, and a second ferroelectric region between the gate and the drain, wherein the array is arranged in rows and columns, the gates of the FETs in a same row being coupled to a word line, the sources of FETs in a same column being coupled to a source bit line, and the drains of FETs in a same column being coupled to a drain bit line:

5

10

15

20

25

30

applying a positive voltage to a selected word line, a negative voltage on a selected source bit line, ground potential on unselected word lines, unselected source lines and all drain bit lines such that a voltage greater that the coercive voltage is applied between the selected word line and selected source line, but a voltage less than the coercive voltage is applied between unselected word lines and selected source bit lines, between unselected word lines and unselected source bit lines, between unselected word lines and drain bit lines, selected word lines and drain bit lines, selected word lines and unselected source bit lines to polarize said first ferroelectric region of a selected FET to a first state while leaving the polarization of all other ferroelectric materials in the array unchanged;

applying a negative voltage to the selected word line, a positive voltage on the selected source bit line, ground potential on unselected word lines, unselected source lines and all drain bit lines such that a voltage greater that the coercive voltage is applied between the selected word line and selected source line, but a voltage less than the coercive voltage is applied between unselected word lines and selected source bit lines, between unselected word lines and unselected source bit lines, between unselected word lines and drain bit lines, selected word lines and drain bit lines, and selected word lines and unselected source bit lines to polarize said first ferroelectric region of the selected FET to a second state while leaving the polarization of all other ferroelectric materials in the array unchanged;

applying a positive voltage to the selected word line, a negative voltage on the selected drain bit line, ground potential on unselected word lines,

unselected drain lines and all source bit lines such that a voltage greater that the coercive voltage is applied between the selected word line and selected drain line, but a voltage less than the coercive voltage is applied between unselected word lines and selected drain bit lines, between unselected word lines and unselected drain bit lines, between unselected word lines and source bit lines, selected word lines and source bit lines, and selected word lines and unselected drain bit lines to polarize said second ferroelectric material of the selected FET to the first state while leaving the polarization of all other ferroelectric materials in the array unchanged;

5

10

15

20

25

30

applying a negative voltage to the selected word line, a positive voltage on the selected drain bit line, ground potential on unselected word lines, unselected drain lines and all source bit lines such that a voltage greater that the coercive voltage is applied between the selected word line and selected drain line, but a voltage less than the coercive voltage is applied between unselected word lines and selected drain bit lines, between unselected word lines and unselected drain bit lines, between unselected word lines and source bit lines, selected word lines and source bit lines, and selected word lines and unselected drain bit lines to polarize said second ferroelectric material of the selected FET to second state while leaving the polarization of all other ferroelectric materials in the array unchanged;

applying a positive voltage less the coercive voltage on the selected word line, ground potential on the selected source bit line, a positive voltage no greater than the word line voltage on the selected drain bit line, and ground potential on unselected word lines, unselected source bit lines, and unselected drain bit lines to detect the polarization state of said first ferroelectric region, a high current between the selected source bit line and the selected drain bit line indicating first state and a low current between selected source bit line and selected drain bit line indicating the second state; and

applying a positive voltage less the coercive voltage on the selected word line, ground potential on the selected drain bit line, a positive voltage no greater than the word line voltage on the selected source bit line, and ground potential on unselected word lines, unselected source bit lines, and

unselected drain bit lines to detect the polarization state of said second ferroelectric region, a high current between selected drain bit line and selected source bit line indicating first state and a low current between selected drain bit line and selected source bit line indicating second state.

5 23. A ferroelectric field effect transistor comprising: a source, a gate, a drain, and a channel;

10

20

25

30

a gate dielectric layer including a first ferroelectric region overlaying the channel in the vicinity of the source, a second ferroelectric region overlaying the channel in the vicinity of the drain, and a non-ferroelectric dielectric overlaying the channel between the first and second ferroelectric region; and a conductive electrode layer overlaying said gate layer.

- 24. A ferroelectric field effect transistor comprising a source, a gate, a drain, and a gate dielectric layer including distinct first and second ferroelectric regions that are separately polarized representing two data bits.

- 15 25. A method for the non-volatile storage of two data bits in a single FET transistor comprising:

providing a field effect transistor (FET) having a gate, drain, source, and substrate, and having a first ferroelectric region between the gate and the source and a second ferroelectric region between the gate and the drain;

selectively applying a voltage greater than a coercive voltage across the gate and the source to polarize said first ferroelectric region;

selectively applying a voltage greater than the coercive voltage across the gate and the drain to polarize said second ferroelectric region;

applying a positive voltage less than the coercive voltage on the gate, ground potential on the source, and a positive voltage no greater than the gate voltage on the drain to detect the polarization state of said first ferroelectric region; and

applying a positive voltage less than the coercive voltage on the gate, ground potential on the drain, and a positive voltage no greater than the gate voltage on the source to detect the polarization state of said second ferroelectric region.

26. A non-volatile memory storage method comprising:

providing an array of field effect transistors (FETs), wherein each FET

in the array has a gate, drain, source, and substrate terminals, a first

ferroelectric region between the gate and the source, and a second

ferroelectric region between the gate and the drain, wherein the array is

arranged in rows and columns, the gates of the FETs in a same row being

coupled to a word line, the sources of FETs in a same column being coupled

5

10

15

20

25

30

a drain bit line;

applying a voltage greater that the coercive voltage across a selected word line and a selected source line to polarize said first ferroelectric region of a selected FET while leaving the polarization of all other ferroelectric materials in the array unchanged;

to a source bit line, and the drains of FETs in a same column being coupled to

applying a voltage greater that the coercive voltage across the selected word line and a selected drain line to polarize said second ferroelectric region of the selected FET while leaving the polarization of all other ferroelectric materials in the array unchanged;

applying a positive voltage less the coercive voltage on the selected word line, ground potential on the selected source bit line, a positive voltage no greater than the word line voltage on the selected drain bit line to detect the polarization state of said first ferroelectric region; and

applying a positive voltage less the coercive voltage on the selected word line, ground potential on the selected drain bit line, a positive voltage no greater than the word line voltage on the selected source bit line to detect the polarization state of said second ferroelectric region.

27. A non-volatile memory storage method comprising: providing an array of field effect transistors (FETs), wherein each FET in the array has a gate, drain, source, and substrate terminals, a first ferroelectric region between the gate and the source, and a second ferroelectric region between the gate and the drain, wherein the array is arranged in rows and columns, the gates of the FETs in a same row being coupled to a word line, the sources of FETs in a same column being coupled

to a source bit line, and the drains of FETs in a same column being coupled to a drain bit line:

applying a voltage greater than the coercive voltage across a selected word line and a source bit line and the selected word line and the drain bit line of the same FET to polarize first and second ferroelectric regions associated with that FET to a first state while leaving the polarization of all other ferroelectric materials in the array unchanged;

5

10

15

20

25

30

applying a voltage greater that the coercive voltage across the selected word line and the source bit line in the opposite direction to polarize said first ferroelectric region of the selected FET to a second state while leaving the polarization of all other ferroelectric materials in the array unchanged;

applying a voltage less that the coercive voltage across the selected word line and the source bit line in the opposite direction to not polarize said first ferroelectric region of the selected FET while leaving the polarization of all other ferroelectric materials in the array unchanged;

applying a voltage greater that the coercive voltage across the selected word line and the drain bit line in the opposite direction to polarize said first ferroelectric region of the selected FET to a second state while leaving the polarization of all other ferroelectric materials in the array unchanged; and

applying a voltage less that the coercive voltage across the selected word line and the drain bit line in the opposite direction to not polarize said first ferroelectric region of the selected FET while leaving the polarization of all other ferroelectric materials in the array unchanged.

# 28. A non-volatile memory storage method comprising:

providing an array of field effect transistors (FETs), wherein each FET in the array has a gate, drain, source, and substrate terminals, a first ferroelectric gate region, and a second ferroelectric gate region, wherein the array is arranged in rows and columns, the gates of the FETs in a same row being coupled to a word line, the sources of FETs in a same column being coupled to a source bit line, and the drains of FETs in a same column being coupled to a drain bit line;

applying a predetermined voltage greater than the coercive voltage across a selected word line and a source bit line of the FET; and

applying the same predetermined voltage across the selected word line and a drain bit line of the FET to polarize first and second ferroelectric gate regions associated with the FET to a first state while leaving the polarization of all other ferroelectric materials in the array unchanged and without drawing current between the source bit line and the drain bit line.

5

10

15

- 29. The storage method of claim 28 further comprising the step of polarizing the first or second ferroelectric gate region to a second state.

- 30. A non-volatile memory storage method comprising: providing a field effect transistor having a gate, drain, source, a first ferroelectric gate region, and a second ferroelectric gate region;

applying a predetermined voltage greater than the coercive voltage across the gate and source of the FET; and

applying the same predetermined voltage across the gate and drain of the FET to polarize the first and second ferroelectric gate regions to a first state without drawing current between the source and the drain.

- 31. The storage method of claim 30 further comprising the step of polarizing the first or second ferroelectric gate region to a second state.

- 32. A non-volatile memory comprising a field effect transistor having a gate, drain, source, a first ferroelectric gate region, and a second ferroelectric gate region wherein the first and second ferroelectric gate regions are selectively polarized to first and second states without drawing a current between the source and the drain.

- 25 33. The memory of claim 32 further comprising at least one buffer dielectric layer between the ferroelectric gate regions and a channel and/or between the ferroelectric gate regions and the gate.

34. The memory of claim 33 wherein the buffer dielectric layer comprises a material selected from the group consisting of silicon nitride, silicon dioxide, and thermally grown silicon dioxide.

- 35. The memory of claim 33 wherein the buffer dielectric layer comprises two or more dielectric sub-layers.

- 36. The memory of claim 33 wherein the buffer dielectric layer is formed utilizing MOCVD or ALD.

- 37. The memory of claim 33 wherein the buffer dielectric layer comprises a material having a dielectric constant of 10 and greater.

- 10 38. The memory of claim 32 wherein the gate comprises a conductive electrode layer.

- 39. The memory of claim 38 wherein the conductive electrode layer comprises a polysilicon-containing material.

- 40. The memory of claim 32 wherein the ferroelectric gate regions comprise a material having the general formula A<sub>x</sub>Mn<sub>y</sub>O<sub>z</sub> where x, y, and z is from 0.1 to 10 and A is a rare earth material selected from the group consisting of Ce, Pr, Nd, Pm, Sm, Eu, GD, Tb, Dy, Ho, Er, Tm, Yb, Lu, Y and Sc.

- 41. The memory of claim 32 wherein the ferroelectric gate regions comprise a low-dielectric ferroelectric material.

- 42. The memory of claim 32 wherein the ferroelectric gate regions are formed using MOCVD.

- 43. The memory of claim 32 wherein the ferroelectric gate regions are formed using ALD.

- 25 44. The memory of claim 32 further comprising a silicon transistor substrate.

45. The memory of claim 32 further comprising a CMOS compatible transistor substrate.

46. The memory of claim 32 further comprising a silicon-on-insulator transistor substrate.

5

FIG. 1 (PRIOR ART)

FIG. 2 (PRIOR ART)

FIG. 12

14/24

FIG. 14

FIG. 16

FIG. 17

18/24

FIG. 19

FIG. 20

FIG. 21

FIG.24