등록특허 10-2152272

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2020년09월04일

(11) 등록번호 10-2152272

(24) 등록일자 2020년08월31일

- (51) 국제특허분류(Int. Cl.)

*H01L 27/115* (2017.01)

- (21) 출원번호 10-2013-0147585

(22) 출원일자 2013년11월29일

심사청구일자 2018년11월15일

- (65) 공개번호 10-2015-0062680

(43) 공개일자 2015년06월08일

- (56) 선행기술조사문현

KR100922557 B1\*

(뒷면에 계속)

전체 청구항 수 : 총 4 항

(54) 발명의 명칭 **비휘발성 메모리 장치 및 그 제조방법****(57) 요 약**

본 기술은 집적도 및 동작 특성을 향상시킬 수 있는 비휘발성 메모리 장치 및 그 제조방법을 제공하기 위한 것으로, 기판에 형성된 제1도전형의 제1웨л; 상기 기판에 형성되어 상기 제1웨л과 접하는 제2도전형의 제2웨л; 상기 제1웨л과 상기 제2웨л이 접하는 경계지역의 기판에 형성된 트렌치; 및 상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡핑하는 게이트전극을 포함한 메모리게이트를 포함하는 비휘발성 메모리 장치를 제공한다.

**대 표 도** - 도1a

(56) 선행기술조사문현

US20030209767 A1\*

KR1020090023233 A

JP2538857 B2

US20020160581 A1

KR1020120120682 A

KR1020110064963 A

\*는 심사관에 의하여 인용된 문현

---

## 명세서

### 청구범위

#### 청구항 1

기판에 형성된 제1도전형의 제1웰;

상기 기판에 형성되어 상기 제1웰과 접하는 제2도전형의 제2웰;

상기 제1웰과 상기 제2웰이 접하는 경계지역의 기판에 형성된 트렌치; 및

상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡필하는 게이트전극을 포함한

메모리게이트

를 포함하되,

상기 메모리게이트, 상기 제1웰 및 상기 제2웰 모두 동일한 방향인 제1 방향을 따라 제2 방향보다 더 길게 연장

되며, 상기 제2 방향은 상기 제1 방향과 교차되는 비휘발성 메모리 장치.

#### 청구항 2

◆청구항 2은(는) 설정등록료 납부시 포기되었습니다.◆

제1항에 있어서,

상기 제1웰에 형성된 제1도전형의 제1접합영역 및 상기 제2웰에 형성된 제1도전형의 제2접합영역을 더 포함하는

비휘발성 메모리 장치.

#### 청구항 3

◆청구항 3은(는) 설정등록료 납부시 포기되었습니다.◆

제1항에 있어서,

상기 제1웰과 상기 제2웰이 접하는 경계면이 상기 트렌치의 저면에 위치하는 비휘발성 메모리 장치.

#### 청구항 4

◆청구항 4은(는) 설정등록료 납부시 포기되었습니다.◆

제1항에 있어서,

상기 메모리막은 소자분리구조물의 라이너막을 포함하는 비휘발성 메모리 장치.

#### 청구항 5

◆청구항 5은(는) 설정등록료 납부시 포기되었습니다.◆

제2항에 있어서,

상기 제1도전형은 P형을 포함하고, 상기 제2도전형은 N형을 포함하는 비휘발성 메모리 장치.

#### 청구항 6

기판에 형성된 복수의 제1도전형을 갖는 제1웰;

상기 제1웰 사이의 기판에 형성되어 제1웰과 접하는 제2도전형의 제2웰;

상기 제2웰 양측의 상기 제1웰과 상기 제2웰이 접하는 경계지역 기판에 형성된 복수의 트렌치; 및

상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡핑하는 게이트전극을 포함한 복수의 메모리게이트를 포함하고,

상기 제2웰 양측에 위치하는 복수의 상기 메모리게이트는 상기 제2웰을 공유하도록 동작간 동일한 바이어스를 인가받되,

상기 메모리게이트, 상기 제1웰 및 상기 제2웰 모두 동일한 방향인 제1 방향을 따라 제2 방향 보다 더 길게 연장되며, 상기 제2 방향은 상기 제1 방향과 교차되는 비휘발성 메모리 장치.

## 청구항 7

◆청구항 7은(는) 설정등록료 납부시 포기되었습니다.◆

제6항에 있어서,

각각의 상기 제1웰에 형성된 제1도전형의 제1접합영역 및 상기 제2웰에 형성된 제1도전형의 제2접합영역을 더 포함하는 비휘발성 메모리 장치.

## 청구항 8

◆청구항 8은(는) 설정등록료 납부시 포기되었습니다.◆

제7항에 있어서,

각각의 상기 제1접합영역은 동작간 동일한 바이어스를 인가받는 비휘발성 메모리 장치.

## 청구항 9

◆청구항 9은(는) 설정등록료 납부시 포기되었습니다.◆

제6항에 있어서,

상기 제1웰과 상기 제2웰이 접하는 경계면이 상기 트렌치의 저면에 위치하는 비휘발성 메모리 장치.

## 청구항 10

◆청구항 10은(는) 설정등록료 납부시 포기되었습니다.◆

제6항에 있어서,

상기 메모리막은 소자분리구조물의 라이너막을 포함하는 비휘발성 메모리 장치.

## 청구항 11

◆청구항 11은(는) 설정등록료 납부시 포기되었습니다.◆

제7항에 있어서,

상기 제1도전형은 P형을 포함하고, 상기 제2도전형은 N형을 포함하는 비휘발성 메모리 장치.

## 청구항 12

기판에 형성되어 제1방향으로 연장되고 상기 제1방향과 교차하는 제2방향으로 이격된 복수의 제1도전형을 갖는 제1웰;

상기 기판에 형성된 상기 제1방향으로 연장되고 상기 제2방향으로 이격되어 상기 제1웰과 접하는 복수의 제2도전형을 갖는 제2웰;

상기 제1웰과 제2웰이 접하는 경계지역의 기판에 형성된 복수의 트렌치;

상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡필하는 케이트전극을 포함한 복수의 메모리케이트;

상기 메모리케이트 사이의 제1웰에 형성되고 상기 제1방향으로 이격된 복수의 제1도전형을 갖는 제1접합영역; 및

상기 메모리케이트 사이의 제2웰에 형성되고 상기 제1방향으로 이격된 복수의 제1도전형을 갖는 제2접합영역을 포함하되,

상기 메모리케이트, 상기 제1웰 및 상기 제2웰 모두 동일한 방향인 제1 방향을 따라 제2 방향보다 더 길게 연장되며, 상기 제2 방향은 상기 제1 방향과 교차되는 비휘발성 메모리 장치.

## 청구항 13

◆청구항 13은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

상기 제1웰에 형성된 제1도전형의 제1불순물영역을 포함한 제1핀업영역; 및

상기 제2웰에 형성된 제2도전형의 제2불순물영역을 포함한 제2핀업영역

을 더 포함하는 비휘발성 메모리 장치.

## 청구항 14

◆청구항 14은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

상기 복수의 제2웰 중에서 어느 하나의 제2웰을 기준으로 상기 어느 하나의 제2웰에 접하는 두 개의 메모리케이트는 상기 어느 하나의 제2웰을 공유하도록 동작간 동일한 바이어스를 인가받는 비휘발성 메모리 장치.

## 청구항 15

◆청구항 15은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

상기 제2방향으로 상기 제1웰과 상기 제2웰은 교번 배치되는 비휘발성 메모리 장치.

## 청구항 16

◆청구항 16은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

복수의 상기 트렌치는 상기 제1방향으로 연장되고 상기 제2방향으로 이격되어 배치된 비휘발성 메모리 장치.

### 청구항 17

◆청구항 17은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

상기 제1웰과 상기 제2웰이 접하는 경계면이 상기 트렌치의 저면에 위치하는 비휘발성 메모리 장치.

### 청구항 18

◆청구항 18은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

상기 메모리게이트를 기준으로 상기 제1접합영역 및 상기 제2접합영역은 상기 제2방향으로 대칭되도록 배치된 비휘발성 메모리 장치.

### 청구항 19

◆청구항 19은(는) 설정등록료 납부시 포기되었습니다.◆

제12항에 있어서,

상기 메모리막은 소자분리구조물의 라이너막을 포함하는 비휘발성 메모리 장치.

### 청구항 20

◆청구항 20은(는) 설정등록료 납부시 포기되었습니다.◆

제13항에 있어서,

상기 제1도전형은 P형을 포함하고, 상기 제2도전형은 N형을 포함하는 비휘발성 메모리 장치.

### 청구항 21

로직영역과 메모리영역을 갖는 기판을 준비하는 단계;

상기 메모리영역의 기판에 서로 다른 도전형을 갖는 제1웰 및 제2웰을 형성하는 단계;

상기 로직영역의 기판에 소자분리 트렌치를 형성함과 동시에 상기 메모리영역에서 상기 제1웰과 상기 제2웰이 접하는 경계지역의 기판에 메모리 트렌치를 형성하는 단계;

상기 소자분리 트렌치 표면에 라이너막을 형성함과 동시에 상기 메모리 트렌치 표면에 메모리막을 형성하는 단계; 및

상기 소자분리 트렌치에 절연막을 캡필하고, 상기 메모리 트렌치에 도전막을 캡필하는 단계

를 포함하되,

상기 제1웰 및 상기 제2웰은 모두 동일한 방향인 제1 방향을 따라 제2 방향보다 더 길게 연장되며, 상기 제1 방향은 상기 제2 방향과 교차되는 비휘발성 메모리 장치 제조방법.

### 발명의 설명

## 기술 분야

[0001] 본 발명은 반도체 장치 제조 기술에 관한 것으로, 보다 구체적으로는 비휘발성 메모리 장치에 관한 것이다.

## 배경 기술

[0002] 최근 등장하고 있는 디지털 미디어 기기들로 인해 언제, 어디서든 원하는 정보를 간편하게 이용할 수 있는 생활 환경으로 변해가고 있다. 아날로그에서 디지털로 전환되면서 급속하게 확산되고 있는 디지털 방식의 각종 기기들은 촬영한 영상, 녹음한 음악, 그리고 각종 데이터를 간편하게 보관할 수 있는 저장매체를 필요로 하게 되었다. 이에 발맞추어 비메모리 반도체에도 고집적화 경향에 따라 시스템 온 칩(System on Chip, SoC) 분야에 관심을 쏟고 있으며, 세계 반도체 업계가 시스템 온 칩 기반 기술 강화를 위해 투자 경쟁을 벌이고 있다. 시스템 온 칩은 하나의 반도체에 모든 시스템 기술을 집적하는 것으로, 시스템 설계 기술을 확보하지 못하면 이제 비메모리 반도체 개발은 어려워지게 될 것이다. 이처럼 복잡한 기술이 집약되어 있는 시스템 온 칩 분야에서 디지털회로(digital circuit)와 아날로그회로(analog circuit)가 혼재된 복합기능을 갖는 칩이 최근 주류로 떠오르고 있다. 이에 따라, 아날로그장치(analog device)를 트리밍(trimming)하거나, 내부 연산 알고리즘(algorithm)을 저장할 임베디드 메모리(embedded memory)에 대한 필요성이 점점 증가하고 있다.

[0003] 그러나, 임베디드 메모리는 로직회로(logic circuit)를 형성하기 위한 CMOS공정(CMOS process) 또는 로직공정(logic process)을 기반으로 제작되기 때문에 집적도 및 동작 특성을 향상시키기 어렵다.

## 발명의 내용

### 해결하려는 과제

[0004] 본 발명의 실시예들은 집적도 및 동작 특성을 향상시킬 수 있는 비휘발성 메모리 장치 및 그 제조방법을 제공한다.

### 과제의 해결 수단

[0005] 본 발명의 실시예에 따른 비휘발성 메모리 장치는 기판에 형성된 제1도전형의 제1웰; 상기 기판에 형성되어 상기 제1웰과 접하는 제2도전형의 제2웰; 상기 제1웰과 상기 제2웰이 접하는 경계지역의 기판에 형성된 트렌치; 및 상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡필하는 게이트전극을 포함한 메모리게이트를 포함할 수 있다. 또한, 상기 제1웰에 형성된 제1도전형의 제1접합영역 및 상기 제2웰에 형성된 제1도전형의 제2접합영역을 더 포함할 수 있다.

[0006] 또한, 본 발명의 실시예에 따른 비휘발성 메모리 장치는 기판에 형성된 복수의 제1도전형을 갖는 제1웰; 상기 제1웰 사이의 기판에 형성되어 제1웰과 접하는 제2도전형의 제2웰; 상기 제2웰 양측의 상기 제1웰과 상기 제2웰이 접하는 경계지역 기판에 형성된 복수의 트렌치; 및 상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡필하는 게이트전극을 포함한 복수의 메모리게이트를 포함하고, 상기 제2웰 양측에 위치하는 복수의 상기 메모리게이트는 상기 제2웰을 공유하도록 동작간 동일한 바이어스를 인가받을 수 있다. 또한, 각각의 상기 제1웰에 형성된 제1도전형의 제1접합영역 및 상기 제2웰에 형성된 제1도전형의 제2접합영역을 더 포함할 수 있다.

[0007] 또한, 본 발명의 실시예에 따른 비휘발성 메모리 장치는 기판에 형성되어 제1방향으로 연장되고 상기 제1방향과 교차하는 제2방향으로 이격된 복수의 제1도전형을 갖는 제1웰; 상기 기판에 형성된 상기 제1방향으로 연장되고 상기 제2방향으로 이격되어 상기 제1웰과 접하는 복수의 제2도전형을 갖는 제2웰; 상기 제1웰과 제2웰이 접하는 경계지역의 기판에 형성된 복수의 트렌치; 상기 트렌치 표면상에 형성된 메모리막과 상기 메모리막 상에서 상기 트렌치를 캡필하는 게이트전극을 포함한 복수의 메모리게이트; 상기 메모리게이트 사이의 제1웰에 형성되고 상

기 제1방향으로 이격된 복수의 제1도전형을 갖는 제1접합영역; 및 상기 메모리게이트 사이의 제2웰에 형성되고 상기 제1방향으로 이격된 복수의 제1도전형을 갖는 제2접합영역을 포함할 수 있다. 또한, 상기 제1웰에 형성된 제1도전형의 제1불순물영역을 포함한 제1핀업영역; 및 상기 제2웰에 형성된 제2도전형의 제2불순물영역을 포함한 제2핀업영역을 더 포함할 수 있다.

[0008] 본 발명의 실시예에 따른 비휘발성 메모리 장치의 제조방법은 로직영역과 메모리영역을 갖는 기판을 준비하는 단계; 상기 메모리영역의 기판에 서로 다른 도전형을 갖는 제1웰 및 제2웰을 형성하는 단계; 상기 로직영역의 기판에 소자분리 트렌치를 형성함과 동시에 상기 메모리영역에서 상기 제1웰과 상기 제2웰이 접하는 경계지역의 기판에 메모리 트렌치를 형성하는 단계; 상기 소자분리 트렌치 표면에 라이너막을 형성함과 동시에 상기 메모리 트렌치 표면에 메모리막을 형성하는 단계; 및 상기 소자분리 트렌치에 절연막을 캡필하고, 상기 메모리 트렌치에 도전막을 캡필하는 단계를 포함할 수 있다.

### 발명의 효과

[0009] 상술한 과제의 해결 수단을 바탕으로 하는 본 기술은 서로 다른 도전형을 갖는 제1웰과 제2웰이 접하는 경계지역에 메모리게이트가 위치함에 따라 셀 구조가 단순하여 비휘발성 메모리 장치의 집적도를 효과적으로 향상시킬 수 있다. 아울러, P 채널타입으로 적용이 용이하여 사이클링 횟수가 증가함에 따른 전류 열화 현상을 방지할 수 있다. 따라서, 비휘발성 메모리 장치의 유지 특성을 개선할 수 있다.

[0010] 또한, 메모리게이트가 기판에 매립된 형태를 갖기 때문에 유효채널길이를 손쉽게 증가시킬 수 있으며, 이를 통해 동작 특성을 향상시킬 수 있다.

[0011] 또한, 별도의 추가 공정없이 예정된 로직공정을 통해 형성된 소자분리구조물의 라이너막을 메모리막으로 이용함에 따라 메모리막 형성공정에 기인한 특성 열화를 방지함과 동시에 로직 호환성을 향상시킬 수 있다.

[0012] 또한, 두 개의 메모리게이트가 하나의 제2웰을 공유함에 따라 단위셀이 두 개의 채널을 갖기 때문에 동작 특성 및 수율을 향상시킬 수 있다.

### 도면의 간단한 설명

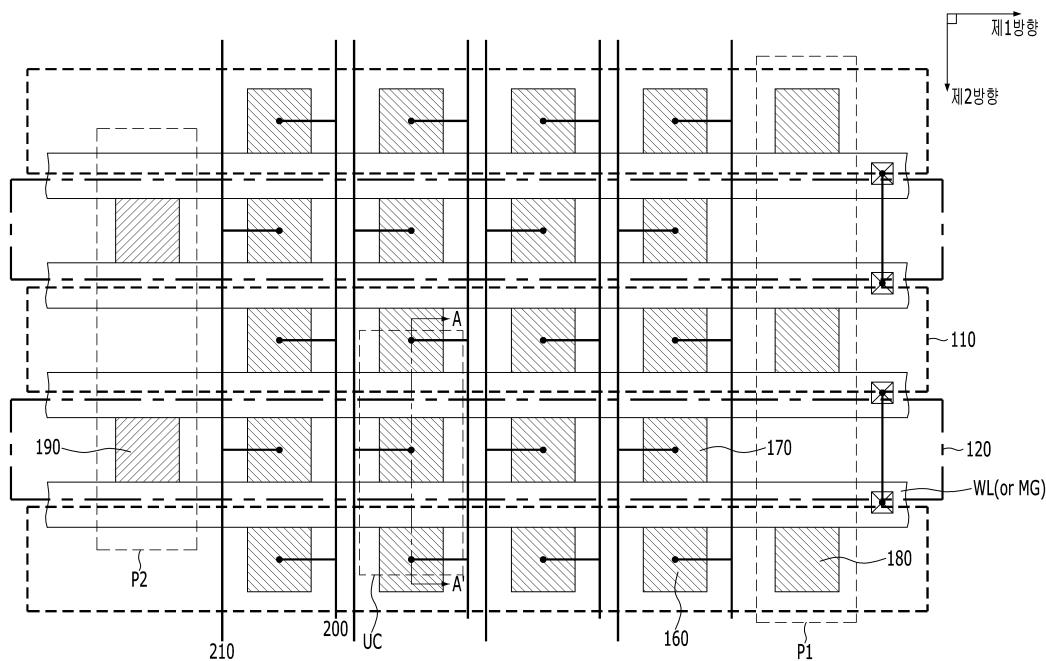

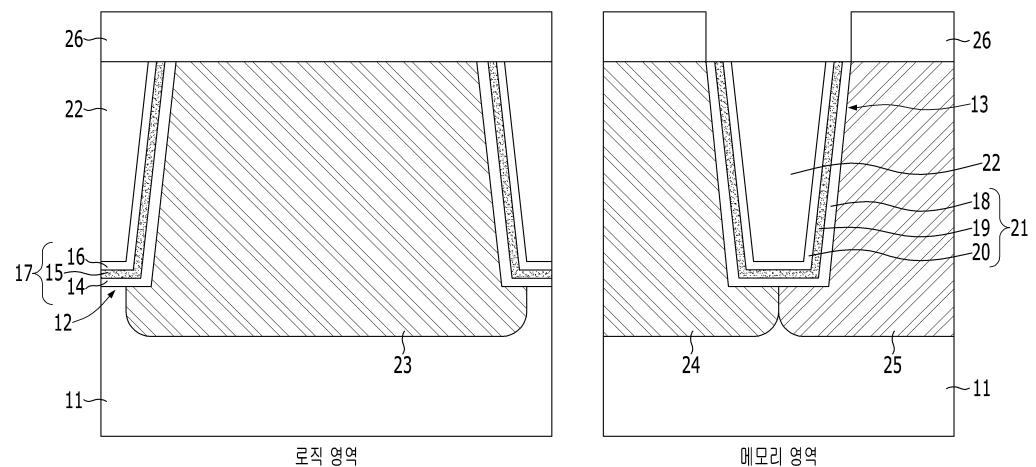

[0013] 도 1a 및 도 1b는 제1실시예에 따른 비휘발성 메모리 장치를 도시한 도면.

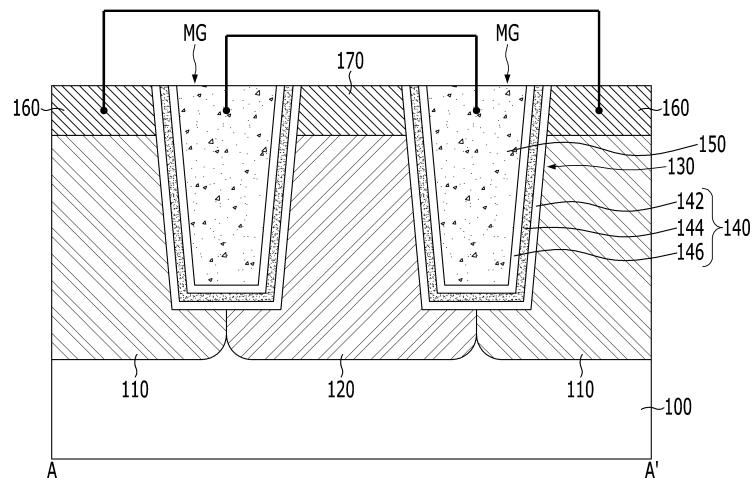

도 2a 및 도 2b는 제2실시예에 따른 비휘발성 메모리 장치를 도시한 도면.

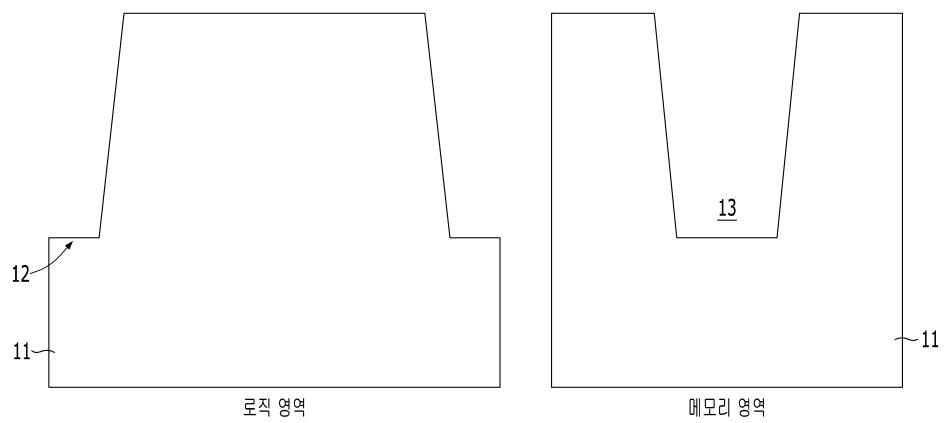

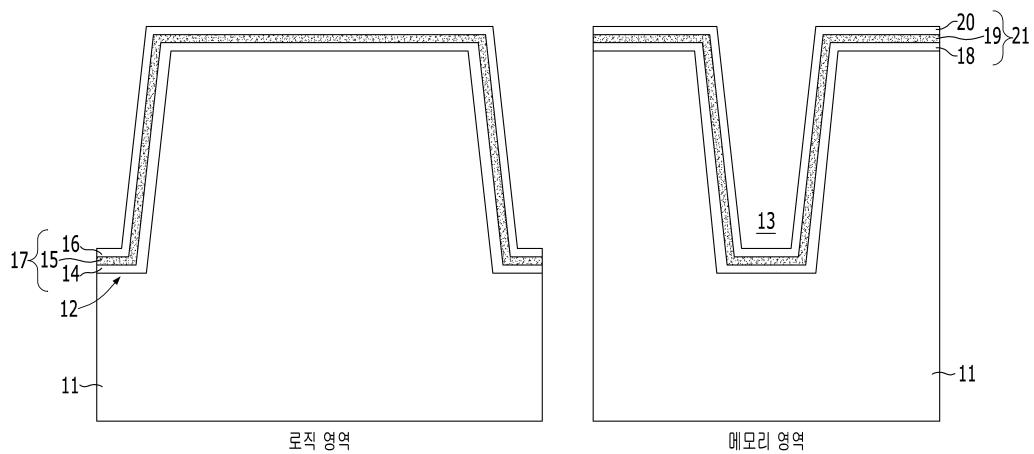

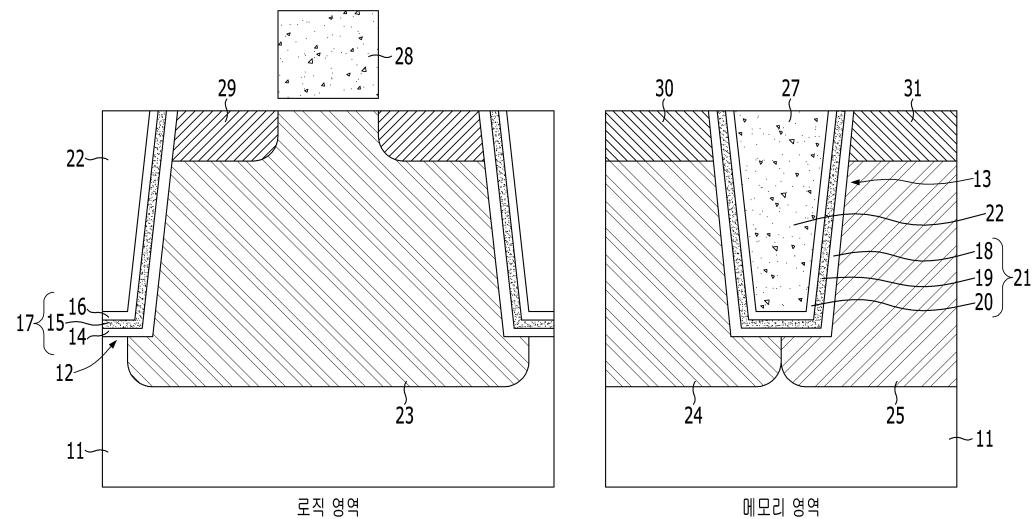

도 3a 내지 도 3e는 실시예에 따른 비휘발성 메모리 장치 제조방법을 도시한 공정단면도.

도 4는 실시예에 따른 전자장치의 구성도.

### 발명을 실시하기 위한 구체적인 내용

[0014] 이하 본 발명이 속하는 기술분야에서 통상의 지식을 가진자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 가장 바람직한 실시예를 도면을 참조하여 설명하기로 한다. 도면은 반드시 일정한 비율로 도시된 것이라 할 수 없으며, 몇몇 예시들에서, 실시예들의 특징을 명확히 보여주기 위하여 도면에 도시된 구조물 중 적어도 일부의 비례는 과장될 수도 있다. 도면 또는 상세한 설명에 둘 이상의 층을 갖는 다층 구조물이 개시된 경우, 도시된 것과 같은 층들의 상대적인 위치 관계나 배열 순서는 특정 실시예를 반영할 뿐이어서 본 발명이 이에 한정되는 것은 아니며, 층들의 상대적인 위치 관계나 배열 순서는 달라질 수도 있다. 또한, 다층 구조물의 도면 또는 상세한 설명은 특정 다층 구조물에 존재하는 모든 층들을 반영하지 않을 수도 있다(예를 들어, 도시된 두 개의 층 사이에 하나 이상의 추가 층이 존재할 수도 있다). 예컨대, 도면 또는 상세한 설명의 다층 구조물에서 제1 층이 제2 층 상에 있거나 또는 기판상에 있는 경우, 제1 층이 제2 층 상에 직접 형성되거나 또는 기판상에 직접 형성될 수 있음을 나타낼 뿐만 아니라, 하나 이상의 다른 층이 제1 층과 제2 층 사이 또는 제1 층과 기판 사이에 존재하는 경우도 나타낼 수 있다.

- [0015] 후술할 실시예들은 복잡한 기술이 집약되어 있는 시스템 온 칩(System on Chip, SoC) 분야에서 각광받고 있는 임베디드 메모리(embedded memory)에 적용이 용이하고, 집적도 및 동작 특성을 향상시킬 수 있는 비휘발성 메모리 장치 및 그 제조방법을 제공하기 위한 것이다. 이를 위해, 실시예들은 임베디드 메모리에 적용이 용이하여 각광받고 있는 플래시 메모리(Flash Memory)를 예시하여 설명하기로 한다. 플래시 메모리는 플로팅게이트 타입(Floating Gate type)과 SONOS 타입(Silicon - Oxide - Nitride - Oxide - Silicon type)으로 구분할 수 있다. 최근에는 집적도 및 동작특성을 보다 용이하게 향상시킬 수 있는 SONOS 타입에 대한 연구가 활발하게 진행되고 있다. 참고로, SONOS 타입의 플래시 메모리는 물질막(예컨대, 질화막)의 트랩사이트(Trap site)에 전하를 트랩핑(trapping) 또는 디트랩핑(de-trapping)시키는 매커니즘(mechanism)을 이용하는 비휘발성 메모리 장치이다.

- [0016] 기존의 SONOS 타입 플래시 메모리는 터널절연막, 전하트랩막 및 전하차단막이 순차적으로 적층된 메모리막과 메모리막 상에 메모리게이트(또는 게이트전극)가 적층된 적층구조물의 양측 기판에 소스영역 및 드레인영역이 배치된 형태를 가진다. 여기서, 임베디드 메모리는 로직공정(logic process)을 기반으로 제작되는 바, 공정 변수에 기인한 특성 열화를 방지하기 위해 예정된 로직공정 이외의 다른 공정이 최대한 추가되지 않도록 설계하는 것이 바람직하다.

- [0017] 그러나, 기존의 SONOS 타입의 플래시 메모리는 로직공정 이외에 메모리막을 형성하기 위한 추가 공정이 반드시 필요하다는 단점이 있다. 특히, 메모리막은 데이터를 저장하는 스토리지(storage)로 작용하여 양질의 막질이 요구되기 때문에 메모리막 형성공정시 기형성된 구조물에 가해지는 공정 부담 예컨대, 열적 부담이 매우 크다는 문제점이 있다. 결과적으로, 기존의 SONOS 타입의 플래시 메모리는 로직공정 이외의 추가 공정을 통해 메모리막을 형성함에 따라 로직 호환성(logic compatibility)이 저하됨과 동시에 장치의 특성이 열화되는 바, 이를 임베디드 메모리에 적용하는데 한계가 있다.

- [0018] 상술한 문제점을 해결하기 위해 후술하는 실시예들은 임베디드 메모리에 적용이 용이하고, 로직 호환성이 우수하며, 집적도 및 동작특성을 향상시킬 수 있는 비휘발성 메모리 장치 및 그 제조방법을 제공하고자 한다. 보다 구체적으로, 후술하는 실시예들은 로직 호환성이 우수한 SONOS 타입의 비휘발성 메모리 장치 및 그 제조방법을 제공한다. 이를 위해, 예정된 로직공정 이외의 별도 공정을 통해 메모리막을 형성하지 않고, 트렌치형 소자분리 구조물 제조공정시 형성되는 라이너막(Liner layer)을 메모리막으로 사용할 수 있는 비휘발성 메모리 장치 및 그 제조방법을 제공한다. 참고로, 라이너막은 소자분리를 위한 트렌치 표면상에 형성되는 측벽산화막(Wall Oxide), 라이너질화막(Liner Nitride) 및 라이너산화막(Liner Oxide)이 순차적으로 적층된 적층막일 수 있다.

- [0019] 한편, 이하의 설명에서 제1도전형과 제2도전형은 서로 상보적인(또는 서로 다른) 도전형을 의미한다. 즉, 제1도전형이 P형인 경우에 제2도전형은 N형이고, 제1도전형이 N형인 경우에 제2도전형은 P형이다. 설명의 편의를 위하여 이하에서 제1도전형은 P형으로, 제2도전형은 N형으로 한다. 즉, P 채널타입의 비휘발성 메모리 장치를 예시하여 설명하기로 한다.

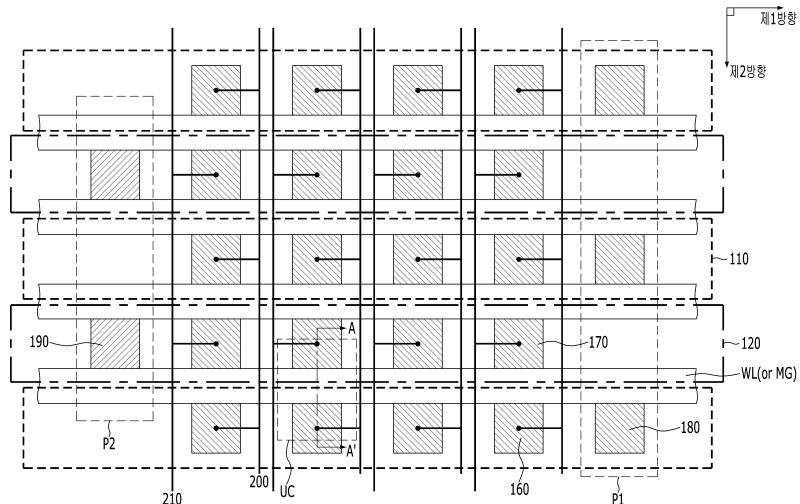

- [0020] 도 1a 및 도 1b는 제1실시예에 따른 비휘발성 메모리 장치를 도시한 도면이다. 구체적으로, 도 1a는 단위셀(Unit Cell, UC)을 포함한 셀 어레이의 일부를 도시한 평면도이고, 도 1b는 도 1a에 도시된 A-A' 절취선을 따라 도시한 단면도이다.

- [0021] 도 1a 및 도 1b에 도시된 바와 같이, 제1실시예에 따른 비휘발성 메모리 장치는 기판(100)에 형성된 제1도전형의 제1웰(110), 기판(100)에 형성된 제2도전형의 제2웰(120), 제1웰(110)과 제2웰(120)이 접하는 경계지역의 기판(100)에 형성된 메모리게이트(Memory Gate, MG) 및 메모리게이트(MG) 양측 제1웰(110) 및 제2웰(120)에 각각 형성된 제1도전형의 제1접합영역(160) 및 제2도전형의 제2접합영역(170)을 포함할 수 있다.

- [0022] 또한, 제1실시예에 따른 비휘발성 메모리 장치는 제1웰(110)에 대한 핵업으로 작용하는 제1도전형의 제1불순물영역(180)을 포함한 제1핀업영역(P1), 제2웰(120)에 대한 핵업으로 작용하는 제2도전형의 제2불순물영역(190)을 포함한 제2핀업영역(P2) 및 제1접합영역(160)과 제2접합영역(170)에 각각 연결된 제1도전라인(200) 및 제2도전라인(210)을 더 포함할 수 있다.

- [0023] 이하, 제1실시예에 따른 비휘발성 메모리 장치의 각 구성요소에 대하여 자세히 설명하기로 한다.

- [0024] 제1실시예에 따른 비휘발성 메모리 장치는 기판(100)에 형성된 제1도전형의 제1웰(110) 및 제2도전형과 상보적인(또는 다른) 제2도전형을 갖는 제2웰(120)을 포함할 수 있다.

- [0025] 제2웰(120)은 각각의 단위셀(UC)에서 채널을 제공하는 활성웰(Active well)로 작용할 수 있으며, 제1웰(110)은

인접한 제2웰(120) 사이를 전기적으로 분리시키는 분리웰(Isolated well)로 작용할 수 있다. 아울러, 제1웰(110)은 제1접합영역(160)의 확장영역으로도 작용할 수 있다. 즉, 제1웰(110)이 제1접합영역(160)으로 작용할 수 있다. 제1웰(110) 및 제2웰(120)은 기판(100)에 불순물을 이온주입하여 형성된 것일 수 있다. 제1웰(110) 및 제2웰(120)은 제1방향으로 연장된 바타입(Bar type) 또는 라인타입(Line type)일 수 있다. 제1웰(110) 및 제2웰(120)은 제2방향으로 서로 접하여 복수개가 교번 배치될 수 있다.

[0026] 기판(100)은 반도체 기판일 수 있다. 반도체 기판은 단결정 상태(Single crystal state)일 수 있으며, 실리콘 함유 재료를 포함할 수 있다. 즉, 반도체 기판은 단결정의 실리콘 함유 재료를 포함할 수 있다. 일례로, 기판(100)은 별크 실리콘기판이거나, 또는 지지기판, 매몰절연층 및 단결정 실리콘층이 순차적으로 적층된 SOI(Silicon On Insulator) 기판일 수 있다.

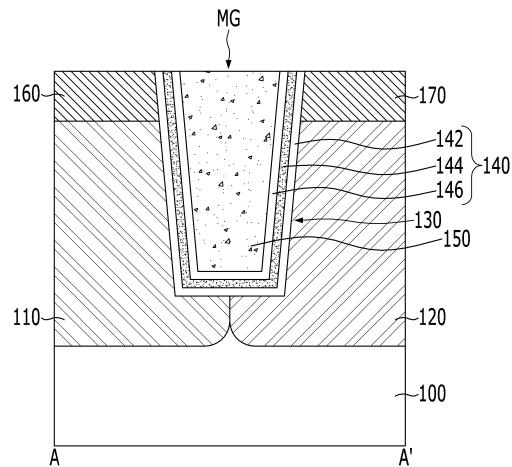

[0027] 제1실시예에 따른 비휘발성 메모리 장치에서 메모리게이트(MG)는 제1웰(110)과 제2웰(120)이 접하는 경계지역의 기판(100)에 형성된 트렌치(130), 트렌치(130) 표면에 형성된 메모리막(140), 메모리막(140) 상에서 트렌치(130)를 캡필하는 게이트전극(150)을 포함할 수 있다. 메모리게이트(MG)는 워드라인(WL)으로 작용할 수 있다.

[0028] 트렌치(130)는 제2방향으로 소정 간격 이격되어 복수개가 배치될 수 있으며, 제1웰(110)과 제2웰(120)이 접하는 경계면을 따라 제1방향으로 연장된 라인타입일 수 있다. 이때, 제1웰(110)과 제2웰(120)이 접하는 경계면은 트렌치(130)의 저면에 접할 수 있으며, 트렌치(130)의 일측 및 타측 측벽은 각각 제1웰(110) 및 제2웰(120)이 접할 수 있다. 균일한 동작 특성을 확보하기 위해 제1웰(110)과 트렌치(130)가 접하는 면적은 제2웰(120)과 트렌치(130)가 접하는 면적과 동일할 수 있다. 트렌치(130)는 트렌치(130)형 소자분리구조물(미도시) 형성공정시 형성된 것일 수 있다.

[0029] 메모리막(140)은 터널절연막(142), 전하트랩막(144) 및 전하차단막(146)이 순차적으로 적층된 적층막일 수 있다. 메모리막(140)은 트렌치(130)의 표면 즉, 저면 및 측면을 따라 일정한 두께를 갖도록 형성된 것일 수 있다. 메모리막(140)은 절연막일 수 있다. 즉, 터널절연막(142), 전하트랩막(144) 및 전하차단막(146) 각각은 산화막, 질화막 및 산화질화막으로 이루어진 그룹으로부터 선택된 어느 하나의 단일막 또는 둘 이상의 적층막을 포함할 수 있다. 구체적으로, 터널절연막(142)은 산화막을 포함할 수 있으며, 소자분리구조물(미도시)의 측벽산화막(Wall Oxide)일 수 있다. 전하트랩막(144)은 질화막을 포함할 수 있으며, 소자분리구조물(미도시)의 라이너질화막(Liner Nitride)일 수 있다. 그리고, 전하차단막(146)은 산화막을 포함할 수 있으며, 소자분리구조물(미도시)의 라이너산화막(Liner Oxide)일 수 있다. 이처럼, 메모리막(140)은 측벽산화막, 라이너질화막 및 라이너산화막이 순차적으로 적층된 소자분리구조물(미도시)의 라이너막을 포함할 수 있다. 이는 후술하는 도 3a 내지 도 3e를 통해 보다 구체적으로 확인할 수 있다.

[0030] 제1실시예에 따른 비휘발성 메모리 장치는 메모리게이트(MG) 양측 제1웰(110) 및 제2웰(120)에 각각 형성된 제1도전형의 제1접합영역(160) 및 제1도전형의 제2접합영역(170), 복수의 제1접합영역(160)과 연결된 제1도전라인(200) 및 복수의 제2접합영역(170)과 연결된 제2도전라인(210)을 포함할 수 있다.

[0031] 제1접합영역(160) 및 제2접합영역(170)은 소스영역 및 드레인영역으로 작용하며, 제1웰(110) 및 제2웰(120)보다 큰 불순물 도핑농도를 가질 수 있다. 제1방향으로 제1접합영역(160) 및 제2접합영역(170)은 소정 간격 이격되어 복수개가 배치될 수 있다. 제2방향으로는 메모리게이트(MG)를 기준으로 제1접합영역(160)과 제2접합영역(170)이 서로 대칭되도록 배치될 수 있다. 제1도전라인(200) 및 제2도전라인(210)은 소스라인(Source Line) 및 비트라인(Bit Line)으로 작용할 수 있다. 제1도전라인(200) 및 제2도전라인(210)은 제2방향으로 연장된 라인타입일 수 있으며, 각각 제2방향으로 배치된 복수의 제1접합영역(160) 및 제2접합영역(170)과 연결될 수 있다. 제1도전라인(200) 및 제2도전라인(210)은 제1방향으로 소정 간격 이격되어 복수개가 배치될 수 있다.

[0032] 상술한 구조를 갖는 제1실시예에 따른 비휘발성 메모리 장치는 서로 다른 도전형을 갖는 제1웰(110)과 제2웰(120)이 접하는 경계지역에 메모리게이트(MG)가 위치함에 따라 셀 구조가 단순하여 비휘발성 메모리 장치의 접적도를 효과적으로 향상시킬 수 있다. 아울러, P 채널타입으로 적용이 용이하여 N 채널타입 대비 사이클링(Cycling) 횟수가 증가함에 따른 전류 열화 현상을 방지할 수 있다. 따라서, 비휘발성 메모리 장치의 유지(endurance) 특성을 개선할 수 있다.

[0033] 또한, 메모리게이트(MG)가 기판(100)에 매립된 형태를 갖기 때문에 유효채널길이(effective channel length)를 손쉽게 증가시킬 수 있으며, 이를 통해 동작 특성을 향상시킬 수 있다.

[0034] 또한, 별도의 추가 공정없이 예정된 로직공정을 통해 형성된 소자분리구조물의 라이너막을 메모리막(140)으로 이용함에 따라 메모리막(140) 형성공정에 기인한 특성 열화를 방지함과 동시에 로직 호환성을 향상시킬 수

있다.

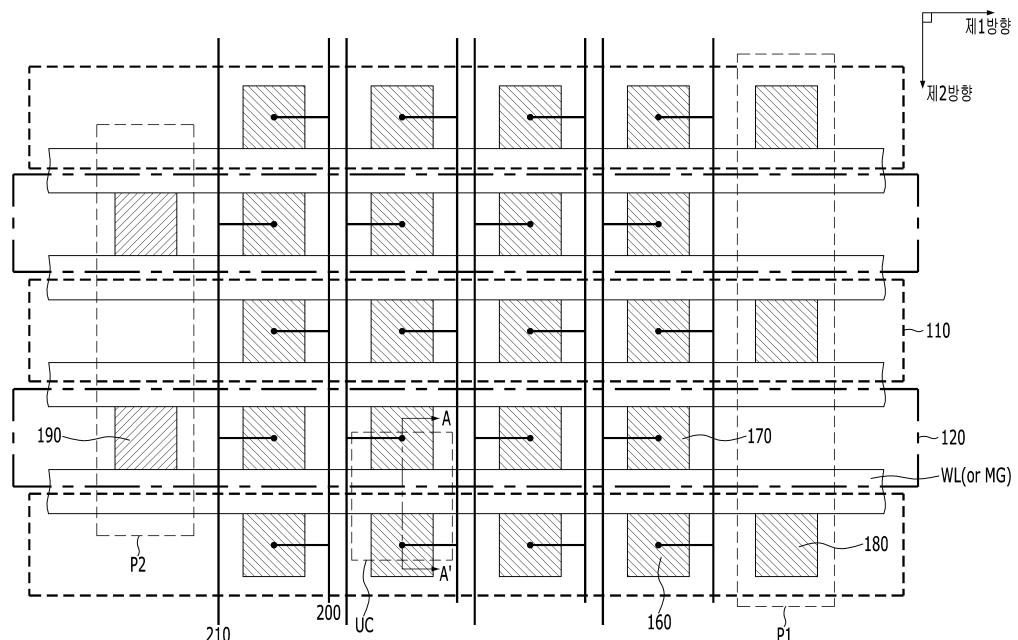

[0035] 이하에서는, 상술한 제1실시예에 따른 비휘발성 메모리 장치 대비 동작 특성 및 수율을 향상시킬 수 있는 제2실시예에 따른 비휘발성 메모리 장치를 도 2a 및 도 2b를 참조하여 설명하기로 한다. 설명의 편의를 위해 동일한 구성요소에 대하여 동일한 도면부호를 사용하고, 자세한 설명은 생략하기로 한다.

[0036] 도 2a 및 도 2b는 제2실시예에 따른 비휘발성 메모리 장치를 도시한 도면이다. 구체적으로, 도 2a는 단위셀(UC)을 포함한 셀 어레이의 일부를 도시한 평면도이고, 도 2b는 도 2a에 도시된 A-A' 절취선을 따라 도시한 단면이다.

[0037] 도 2a 및 도 2b에 도시된 바와 같이, 제2실시예에 따른 비휘발성 메모리 장치는 기판(100)에 형성된 제1도전형의 제1웰(110), 기판(100)에 형성된 제2도전형의 제2웰(120), 제1웰(110)과 제2웰(120)이 접하는 경계지역의 기판(100)에 형성된 메모리게이트(MG) 및 메모리게이트(MG) 양측 제1웰(110) 및 제2웰(120)에 각각 형성된 제1도전형의 제1접합영역(160) 및 제1도전형의 제2접합영역(170)을 포함할 수 있다. 또한, 제2실시예에 따른 비휘발성 메모리 장치는 제1웰(110)에 대한 꾹업으로 작용하는 제1도전형의 제1불순물영역(180)을 포함한 제1꺾업영역(P1), 제2웰(120)에 대한 꾹업으로 작용하는 제2도전형의 제2불순물영역(190)을 포함한 제2꺾업영역(P2) 및 제1접합영역(160)과 제2접합영역(170)에 각각 연결된 제1도전라인(200) 및 제2도전라인(210)을 더 포함할 수 있다.

[0038] 제2실시예에 따른 비휘발성 메모리 장치는 어느 하나의 제2웰(120)을 기준으로 제2웰(120)에 접하는 두 개의 메모리게이트(MG, 또는 워드라인)가 전기적으로 병합된(merge) 형태를 가질 수 있다. 즉, 두 개의 메모리게이트(MG)가 하나의 제2웰(120)을 공유하는 형태를 가질 수 있으며, 제2웰(120)을 공유하는 두 개의 메모리게이트(MG)는 동작간 동일한 바이어스를 인가받을 수 있다. 제2웰(120)을 공유하는 두 개의 메모리게이트(MG)가 전기적으로 병합된 형태를 갖기 위해 일측 또는 타측 끝단의 메모리게이트(MG)가 연결되거나, 또는 메모리게이트(MG)를 연결되는 배선구조물을 구비할 수 있다.

[0039] 두 개의 메모리게이트(MG)가 하나의 제2웰(120)을 공유함에 따라 단위셀(UC)은 두 개의 제1접합영역(160)과 하나의 제2접합영역(170)을 포함할 수 있으며, 두 개의 제1접합영역(160)은 동작간 동일한 바이어스를 인가받을 수 있다. 즉, 단위셀 측면에서 두 개의 제1접합영역(160)도 전기적으로 병합된 형태를 가질 수 있다.

[0040] 상술한 제2실시예에 따른 비휘발성 메모리 장치는 두 개의 메모리게이트(MG)가 하나의 제2웰(120)을 공유함에 따라 단위셀(UC)이 하나의 채널을 갖는 제1실시예 대비 단위셀(UC)이 두 개의 채널을 갖기 때문에 동작 특성 및 수율(yield)을 향상시킬 수 있다. 구체적으로, 채널 수가 증가함에 따라 전하를 저장할 수 있는 공간도 증가하고, 공정마진 부족으로 어느 일측의 채널이 손상되더라도 타측 채널에 의해 수율 손실을 방지할 수 있다.

[0041] 또한, 제1웰(110)과 제2웰(120)이 접하는 경계지역에 메모리게이트(MG)가 위치함에 따라 셀 구조가 단순하여 비휘발성 메모리 장치의 접적도를 효과적으로 향상시킬 수 있다. 아울러, P 채널타입으로 적용이 용이하여 N 채널타입 대비 사이클링(Cycling) 횟수가 증가함에 따른 전류 열화 현상을 방지할 수 있다. 따라서, 비휘발성 메모리 장치의 유지(endurance) 특성을 개선할 수 있다.

[0042] 또한, 메모리게이트(MG)가 기판(100)에 매립된 형태를 갖기 때문에 유효채널길이(effective channel length)를 손쉽게 증가시킬 수 있으며, 이를 통해 동작 특성을 향상시킬 수 있다.

[0043] 또한, 별도의 추가 공정없이 예정된 로직공정을 통해 형성된 소자분리구조물(미도시)의 라이너막을 메모리막(140)으로 이용함에 따라 메모리막(140) 형성공정에 기인한 특성 열화를 방지함과 동시에 로직 호환성을 향상시킬 수 있다.

[0044] 이하에서는, 제1 및 제2실시예에 따른 비휘발성 메모리 장치 단위셀의 동작에 대하여 표 1을 참조하여 설명하기로 한다. 아래 표 1은 제1 및 제2실시예에 따른 비휘발성 메모리 장치 단위셀의 동작 조건에 대한 일례를 나타낸 것이다. 참고로, 제1실시예 및 제2실시예는 단위셀의 형태가 상이하나, 아래 예시된 동작방법을 동일하게 적용할 수 있다.

## 표 1

| 동작       | 프로그램  | 소거    | 리드      |

|----------|-------|-------|---------|

| 방식       | HCI   | BTBT  | Reverse |

| 메모리게이트   | VDD   | -VPP1 | VDD     |

| 제1접합영역   | GND   | GND   | GND     |

| 제2접합영역   | -VPP1 | GND   | -VPP2   |

| 제2웰(활성웰) | GND   | VDD   | GND     |

[0045]

먼저, 프로그램동작은 HCI(Hot Carrier Injection) 방식을 이용할 수 있다. 제1웰(110) 및 제2웰(120)에 각각 접지전압(GND)을 인가하고, 메모리게이트(MG) 및 제2접합영역(170)에 각각 전원전압(VDD) 및 네거티브 제1펌핑전압(-VPP1)을 인가하는 방법으로 프로그램동작을 수행할 수 있다. 제1웰(110)은 제1접합영역(160) 또는 제1펌핑영역(P1)을 통해 바이어스를 인가할 수 있으며, 제2웰(120)은 제2펌핑영역(P2)을 통해 바이어스를 인가할 수 있다. 제1펌핑전압(VPP1)은 그 절대값이 전원전압(VDD)보다 큰 전압일 수 있다.

[0047]

다음으로, 소거동작은 BTBT(Band To Band Tuneling) 방식을 이용할 수 있다. 제1접합영역(160) 및 제2접합영역(170)에 접지전압(GND)을 인가한 상태에서 메모리게이트(MG) 및 제2웰(120)에 각각 네거티브 제1펌핑전압(-VPP1) 및 전원전압(VDD)을 인가하는 방법으로 소거동작을 수행할 수 있다.

[0048]

다음으로, 리드동작은 리버스리드(Reverse read) 방식을 이용할 수 있다. 리버스리드는 프로그램동작시 전하의 이동방향과 반대방향으로의 전하이동을 통해 리드동작이 이루어지는 것을 의미하며, 리드 디스터번스(read disturbance)에 대한 내성이 크다는 장점이 있다. 리드동작은 제1웰(110) 및 제2웰(120)이 접지전압(GND)을 인가하고, 메모리게이트(MG) 및 제2접합영역(170)에 각각 전원전압(VDD) 및 네거티브 제2펌핑전압(-VPP2)을 인가하는 방법으로 리드동작을 수행할 수 있다. 제2펌핑전압(VPP2)은 그 절대값이 전원전압(VDD)보다 크고, 제1펌핑전압(VPP1)보다 작을 수 있다. 리드동작과 프로그램동작 사이의 전류 차이를 통해 전하 트랩 여부를 센싱할 수 있다.

[0049]

이하에서는, 제1 및 제2실시예에 따른 비휘발성 메모리 장치가 예정된 로직공정을 통해 형성되는 소자분리구조물의 라이너막을 이용하여 메모리막을 구현할 수 있음에 대하여 자세히 설명하기로 한다. 설명의 편의를 위해 제1실시예에 따른 비휘발성 메모리 장치의 제조방법에 대한 일례를 예시하여 설명하기로 한다.

[0050]

도 3a 내지 도 3e는 실시예에 따른 비휘발성 메모리 장치 제조방법을 도시한 공정단면도이다.

[0051]

도 3a에 도시된 바와 같이, 로직영역(Logic region) 및 메모리영역(Memory region)을 포함하는 기판(11)을 준비한다. 로직영역은 파워소자영역(Power device region), COMS영역(COMS region) 등을 포함할 수 있다. 실시예에서는 로직영역이 NMOS영역인 경우를 예시하여 도시하기로 한다. 그리고, 메모리영역은 상술한 실시예들에 따른 비휘발성 메모리 장치를 포함할 수 있다. 기판(11)은 반도체 기판을 사용할 수 있다. 반도체 기판은 단결정상태(Single crystal state)일 수 있으며, 실리콘함유 재료를 포함할 수 있다. 즉, 반도체 기판은 단결정의 실리콘 함유 재료를 포함할 수 있다. 예컨대, 기판(11)으로는 벌크 실리콘기판 또는 SOI(Silicon On Insulator) 기판을 사용할 수 있다.

[0052]

다음으로, 기판(11)상에 소자분리를 위한 마스크패턴(미도시)을 형성하고, 마스크패턴(26)을 식각장벽(etch barrier)으로 기판(11)을 식각하여 로직영역에 소자분리 트렌치(12)를 형성함과 동시에 메모리영역에 메모리 트렌치(13)를 형성한다. 소자분리 트렌치(12) 및 메모리 트렌치(13)를 형성하기 위한 식각공정은 건식식각법을 사용하여 진행할 수 있다. 소자분리 트렌치(12) 및 메모리 트렌치(13)의 측벽은 경사질 수 있으며, 소자분리 트렌치(12) 및 메모리 트렌치(13)는 서로 동일한 종횡비를 갖거나, 또는 서로 상이한 종횡비를 가질 수 있다.

[0053]

도 3b에 도시된 바와 같이, 소자분리 트렌치(12) 및 메모리 트렌치(13)를 포함한 기판(11) 표면을 따라 제1라이너막(14, 18)을 형성한다. 제1라이너막(14, 18)은 산화막으로 형성할 수 있으며, 산화막은 열산화법을 사용하여 형성할 수 있다. 제1라이너막(14, 18)은 소자분리 트렌치(12) 및 메모리 트렌치(13) 형성공정시 이들 표면에 형

성된 결합 또는 손상을 치유하는 역할을 수행한다. 아울러, 로직영역에서 제1라이너막(14, 18)은 측벽산화막(14)으로 작용할 수 있고, 메모리영역에서 제1라이너막(14, 18)은 터널절연막(18)으로 작용할 수 있다.

[0054] 다음으로, 제1라이너막(14, 18)을 포함한 구조물 표면을 따라 제2라이너막(15, 19)을 형성한다. 제2라이너막(15, 19)은 질화막으로 형성할 수 있으며, 소자분리 트렌치(12) 및 메모리 트렌치(13)를 포함한 구조물 표면을 따라 균일한 두께를 갖도록 형성할 수 있다. 제2라이너막(15, 19)은 불순물의 침투 또는 확산을 방지하는 역할을 수행한다. 아울러, 로직영역에서 제2라이너막(15, 19)은 라이너질화막(15)으로 작용할 수 있고, 메모리영역에서 제2라이너막(15, 19)은 전하트랩막(19)으로 작용할 수 있다.

[0055] 다음으로, 제2라이너막(15, 19)을 포함한 구조물 표면을 따라 제3라이너막(16, 20)을 형성한다. 제3라이너막(16, 20)은 산화막으로 형성할 수 있다. 제3라이너막(16, 20)은 제2라이너막(15, 19)의 계면특성을 개선하는 역할을 수행한다. 아울러, 로직영역에서 제3라이너막(16, 20)은 라이너산화막(16)으로 작용할 수 있고, 메모리영역에서 제3라이너막(16, 20)은 전하차단막(20)으로 작용할 수 있다.

[0056] 상술한 공정을 통해 로직영역의 소자분리 트렌치(12)를 포함한 기판(11) 표면을 따라 측벽산화막(14), 라이너질화막(15) 및 라이너산화막(16)이 순차적으로 적층된 라이너막(17)을 형성함과 동시에 메모리영역의 메모리 트렌치(13)를 포함한 기판(11) 표면을 따라 터널절연막(18), 전하트랩막(19) 및 전하차단막(20)이 순차적으로 적층된 메모리막(21)을 형성할 수 있다.

[0057] 한편, 경우에 따라서 제2라이너막(15, 19)을 형성한 이후에 연속해서 제3라이너막(16, 20)을 형성하지 않고, 후속 공정을 통해 제3라이너막(16, 20) 특히, 전하차단막(20)을 형성할 수도 있다.

[0058] 도 3b에 도시된 바와 같이, 소자분리 트렌치(12) 및 메모리 트렌치(13)를 캡필함과 동시에 기판(11) 전면을 덮는 캡필절연막(22)을 형성한다. 캡필절연막(22)은 산화막 예컨대, 고밀도플라즈마산화막(High Density Plasma oxide, HDP oxide)으로 형성할 수 있다.

[0059] 다음으로, 기판(11) 표면이 노출될때까지 캡필절연막(22), 라이너막(17) 및 메모리막(21)에 대한 평탄화공정을 진행한다. 평탄화공정은 화학적기계적연마법(CMP)을 사용할 수 있다.

[0060] 이로써, 로직영역에 소자분리 트렌치(12), 측벽산화막(14), 라이너질화막(15) 및 라이너산화막(16)이 적층된 라이너막(17) 및 캡필절연막(22)을 포함하는 소자분리구조물을 형성할 수 있다.

[0061] 다음으로, 로직영역의 기판(11)에 불순물을 이온주입하여 로직웰(23)을 형성하고, 메모리영역의 기판(11)에 제1도전형의 제1웰(24) 및 제2도전형의 제2웰(25)을 형성한다. 여기서, 서로 동일한 도전형을 갖는 로직웰(23)과 제1웰(24)은 동시에 형성할 수도 있다.

[0062] 도 3d에 도시된 바와 같이, 기판(11)상에 로직영역을 덮고, 적어도 메모리영역의 캡필절연막(22)을 오픈하는 마스크패턴(26)을 형성한다. 마스크패턴(26)에 의해 메모리막(21) 및 메모리 트렌치(13) 인접 기판(11)도 노출될 수 있다.

[0063] 다음으로, 마스크패턴(26)을 식각장벽으로 메모리 트렌치(13) 내부의 캡필절연막(22)을 제거한다. 캡필절연막(22)을 제거하기 위한 식각공정은 기형성된 구조물의 손상을 최소화시키기 위해 습식식각으로 진행할 수 있다.

[0064] 한편, 도면에 도시하지는 않았지만, 캡필절연막(22)을 제거하는 과정에서 메모리막(21)의 전하차단막(20)도 함께 제거될 수 있다. 따라서, 캡필절연막(22) 및 마스크패턴(26)을 제거한 이후에 전하차단막(20) 형성공정을 추가 진행할 수도 있다. 여기서, 메모리영역에 전하차단막(20)을 형성함과 동시에 로직영역에 게이트절연막을 형성할 수 있다.

[0065] 도 3e에 도시된 바와 같이, 메모리 트렌치(13)를 캡필하고 기판(11) 전면을 덮도록 게이트도전막을 형성한 이후에 게이트도전막을 선택적으로 식각하여 로직영역에 로직게이트(28)를 형성함과 동시에 메모리영역에 메모리 트렌치(13)에 캡필된 게이트전극(27)을 형성한다. 게이트도전막으로는 폴리실리콘막을 사용할 수 있다.

[0066] 이로써, 메모리영역에 메모리 트렌치(13), 메모리막(21) 및 게이트전극(27)을 포함한 메모리게이트를 형성할 수 있다.

[0067] 다음으로, 로직게이트(28) 양측 기판(11)의 소스영역/드레인영역(29), 메모리영역의 메모리게이트 양측에 위치하도록 제1웰(24) 및 제2웰(25)에 각각 제1도전형의 제1접합영역(30) 및 제1도전형의 제2접합영역(31)을 형성한다.

- [0068] 이후, 도면에 도시하지는 않았지만 공지된 반도체 장치 제조기술을 이용하여 장치를 완성할 수 있다.

- [0069] 상술한 바와 같이, 소자분리구조물의 라이너막(17)을 SONOS 타입의 비휘발성 메모리 장치의 메모리막(21)으로 사용함에 따라 메모리막(21) 형성공정에 기인한 특성 열화를 방지함과 동시에 로직 호환성을 향상시킬 수 있다.

- [0070] 이하에서는, 본 발명의 실시예들에 따른 비휘발성 메모리 장치의 활용분야에 대한 일례를 도 4를 참조하여 간략히 설명하기로 한다.

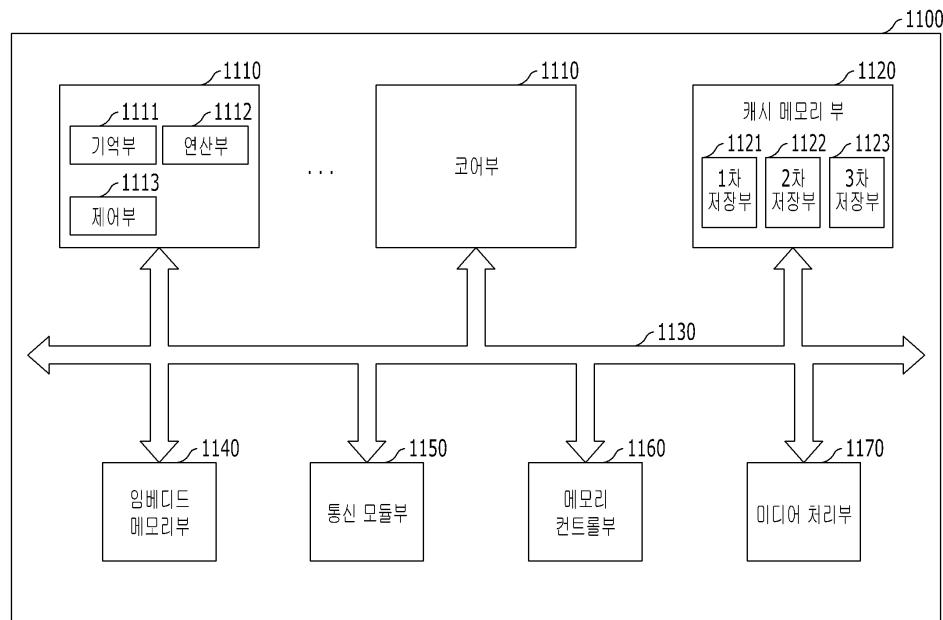

- [0071] 도 4는 실시예에 따른 전자장치의 구성도이다.

- [0072] 도 4에 도시된 바와 같이, 전자장치(1100)는 다양한 외부 장치로부터 데이터를 받아서 처리한 후 그 결과를 외부 장치로 보내는 일련의 과정을 제어하고 조정하는 일을 수행하는 프로세서 이외의 다양한 기능을 포함하여 성능 향상 및 다기능을 구현할 수 있으며 코어부(1110), 캐시 메모리부(1120) 및 버스 인터페이스(1130)를 포함할 수 있다. 실시예의 코어부(1110)는 외부 장치로부터 입력된 데이터를 산술 논리 연산하는 부분으로 기억부(1111), 연산부(1112), 제어부(1113)를 포함할 수 있다. 전자장치(1100)는 멀티 코어 프로세서(Multi Core Processor), 그래픽 처리 장치(Graphic Processing Unit, GPU), 어플리케이션 프로세서(Application Processor, AP) 등 각종 시스템 온 칩(System on Chip, SoC)일 수 있다.

- [0073] 기억부(1111)는 프로세서 레지스터(Processor register) 또는 레지스터(Register)로 전자장치(1100) 내에서 데이터를 저장하는 부분으로 데이터 레지스터, 주소 레지스터 및 부동 소수점 레지스터를 포함할 수 있으며 이외에 다양한 레지스터를 포함할 수 있다. 기억부(1111)는 연산부(1112)에서 연산을 수행하는 데이터나 수행결과 데이터, 수행을 위한 데이터가 저장되어 있는 주소를 일시적으로 저장하는 역할을 수행할 수 있다. 연산부(1112)는 전자장치(1100)의 내부에서 연산을 수행하는 부분으로 제어부(1113)가 명령을 해독한 결과에 따라서 여러 가지 사칙 연산 또는 논리 연산을 수행한다. 연산부(1112)는 하나 이상의 산술 놀리 연산 장치(Arithmetic and Logic Unit, ALU)를 포함할 수 있다. 제어부(1113)는 기억부(1111)나 연산부(1112) 및 전자장치(1100) 외부 장치로부터의 신호를 수신 받아 명령의 추출이나 해독, 입력이나 출력의 제어 등을 하고, 프로그램으로 나타내어진 처리를 실행한다.

- [0074] 캐시 메모리부(1120)는 고속으로 동작하는 코어부(1110)와는 달리 저속의 외부 장치의 데이터 처리 속도 차이를 보완하기 위해 임시로 데이터를 저장하는 부분으로 1차 저장부(1121), 2차 저장부(1122) 및 3차 저장부(1123)를 포함할 수 있다. 일반적으로 캐시 메모리부(1120)는 1차, 2차 저장부(1121, 1122)를 포함하며 고용량이 필요할 경우 3차 저장부(1123)를 포함할 수 있으며, 필요시 더 많은 저장부를 포함할 수 있다. 즉 캐시 메모리부(1120)가 포함하는 저장부의 개수는 설계에 따라 달라질 수 있다. 여기서, 1차, 2차, 3차 저장부(1121, 1122, 1123)의 데이터 저장 및 판별하는 처리 속도는 같을 수도 있고 다를 수도 있다. 각 저장부의 처리 속도가 다른 경우, 1차 저장부의 속도가 제일 빠를 수 있다. 도 8에는 1차, 2차, 3차 저장부(1121, 1122, 1123)가 모두 캐시 메모리부(1120)의 내부에 구성된 경우를 도시하였으나 캐시 메모리부(1120)의 1차, 2차, 3차 저장부(1121, 1122, 1123)는 모두 코어부(1110)의 외부에 구성될 수 있으며, 코어부(1110)와 외부 장치간의 처리 속도 차이를 보완할 수 있다. 또한, 캐시 메모리부(1120)의 1차 저장부(1121)는 코어부(1110)의 내부에 위치할 수 있으며 2차 저장부(1122) 및 3차 저장부(1123)는 코어부(1110)의 외부에 구성하여 처리 속도 보완을 위한 기능을 좀 더 강화시킬 수 있다.

- [0075] 버스 인터페이스(1130)는 코어부(1110)와 캐시 메모리부(1120)를 연결하여 데이터를 효율적으로 전송할 수 있게 해주는 부분이다.

- [0076] 실시예에 따른 전자장치(1100)는 다수의 코어부(1110)를 포함할 수 있으며 다수의 코어부(1110)가 캐시 메모리부(1120)를 공유할 수 있다. 다수의 코어부(1110)와 캐시 메모리부(1120)는 버스 인터페이스(1130)를 통해 연결될 수 있다. 다수의 코어부(1110)는 모두 상술한 코어부의 구성과 동일하게 구성될 수 있다. 다수의 코어부(1110)를 포함할 경우, 캐시 메모리부(1120)의 1차 저장부(1121)는 다수의 코어부(1110)의 개수에 대응하여 각각의 코어부(1110) 내에 구성되고 2차 저장부(1122)와 3차 저장부(1123)는 하나로 다수의 코어부(1110)의 외부에 버스 인터페이스(1130)를 통해 공유되도록 구성될 수 있다. 여기서, 1차 저장부(1121)의 처리 속도가 2차, 3차 저장부(1122, 1123)의 처리 속도보다 빠를 수 있다.

- [0077] 실시예에 따른 전자장치(1100)는 데이터를 저장하는 임베디드(Embedded) 메모리부(1140), 외부 장치와 유선 또

는 무선으로 데이터를 송수신 할 수 있는 통신모듈부(1150), 외부 기억 장치를 구동하는 메모리 컨트롤부(1160), 외부 인터페이스 장치에 전자장치(1100)에서 처리된 데이터나 외부 입력장치에서 입력된 데이터를 가공하고 출력하는 미디어처리부(1170)를 추가로 포함할 수 있으며, 이 이외에도 다수의 모듈을 포함할 수 있다. 이 경우 추가된 다수의 모듈들은 버스 인터페이스(1130)를 통해 코어부(1110), 캐시 메모리부(1120) 및 상호간 데이터를 주고 받을 수 있다.

[0078] 여기서 임베디드 메모리부(1140)는 휘발성 메모리뿐만 아니라 비휘발성 메모리를 포함할 수 있다. 휘발성 메모리는 DRAM(Dynamic Random Access Memory), Mobile DRAM, SRAM(Static Random Access Memory) 등을 포함할 수 있으며, 비휘발성 메모리는 ROM(Read Only Memory), NOR Flash Memory, NAND Flash Memory, 상변환 메모리(Phase Change Random Access Memory, PRAM), 저항 메모리(Resistive Random Access Memory, RRAM), 스핀 주입 메모리(Spin Transfer Torque Random Access Memory, STTRAM), 자기메모리(Magnetic Random Access Memory, MRAM) 등을 포함할 수 있다. 특히, 비휘발성 메모리로서 상술한 실시예들에 따른 비휘발성 메모리 장치를 포함할 수 있다. 상술한 실시예에 따른 반도체 장치를 포함한 임베디드 메모리부(1140)는 기판에 형성된 제1도전형의 제1웰, 기판에 형성되어 제1웰과 접하고 제1도전형과 상보적인 제2도전형의 제2웰, 제1웰과 제2웰이 접하는 경계지역의 기판에 형성된 트렌치 및 트렌치 표면상에 형성된 메모리막과 메모리막 상에서 트렌치를 갭필하는 게이트전극을 포함한 메모리게이트, 제1웰에 형성된 제1도전형의 제1접합영역 및 제2웰에 형성된 제1도전형의 제2접합영역을 더 포함할 수 있다. 상술한 임베디드 메모리부(1140)는 셀 구조가 단순하고, 사이클링 횟수가 증가함에 따른 전류 열화 현상을 방지하여 유지 특성을 향상시킬 수 있으며, 별도의 추가 공정없이 예정된 로직공정을 통해 형성된 라이너막을 메모리막으로 이용함에 따라 메모리막 형성공정에 기인한 특성 열화를 방지함과 동시에 로직 호환성을 향상시킬 수 있다. 따라서, 임베디드 메모리부(1140) 및 임베디드 메모리부(1140)를 포함한 전자장치(1100)의 소형화, 고성능화가 가능하다.

[0079] 통신모듈부(1150)는 유선 네트워크와 연결할 수 있는 모듈과 무선 네트워크와 연결할 수 있는 모듈을 모두 포함할 수 있다. 유선 네트워크 모듈은 유선랜(Local Area Network, LAN), 유에스비(Universal Serial Bus, USB), 이더넷(Ethernet), 전력선통신(Power Line Communication, PLC) 등을 포함할 수 있으며, 무선 네트워크 모듈은 적외선 통신(Infrared Data Association, IrDA), 코드 분할 다중 접속(Code Division Multiple Access, CDMA), 시분할 다중 접속(Time Division Multiple Access, TDMA), 주파수 분할 다중 접속(Frequency Division Multiple Access, FDMA), 무선랜(Wireless LAN), 지그비(Zigbee), 유비쿼터스 센서 네트워크(Ubiquitous Sensor Network, USN), 블루투스(Bluetooth), RFID(Radio Frequency IDentification), 롱텀에볼루션(Long Term Evolution, LTE), 근거리 무선통신(Near Field Communication, NFC), 광대역 무선 인터넷(Wireless Broadband Internet, Wibro), 고속 하향 패킷 접속(High Speed Downlink Packet Access, HSDPA), 광대역 코드 분할 다중 접속(Wideband CDMA, WCDMA), 초광대역 통신(Ultra WideBand, UWB) 등을 포함할 수 있다.

[0080] 메모리 컨트롤부(1160)는 전자장치(1100)와 서로 다른 통신 규격에 따라 동작하는 외부 저장 장치 사이에 전송되는 데이터를 관리하기 위한 것으로 각종 메모리 컨트롤러, IDE(Integrated Device Electronics), SATA(Serial Advanced Technology Attachment), SCSI(Small Computer System Interface), RAID(Redundant Array of Independent Disks), SSD(Solid State Disk), eSATA(External SATA), PCMCIA(Personal Computer Memory Card International Association), USB(Universal Serial Bus), 씨큐어 디지털 카드(Secure Digital, SD), 미니 씨큐어 디지털 카드(mini Secure Digital card, mSD), 마이크로 씨큐어 디지털 카드(micro SD), 고용량 씨큐어 디지털 카드(Secure Digital High Capacity, SDHC), 메모리 스틱 카드(Memory Stick Card), 스마트 미디어 카드(Smart Media Card, SM), 멀티 미디어 카드(Multi Media Card, MMC), 내장 멀티 미디어 카드(Embedded MMC, eMMC), 컴팩트 플래시 카드(Compact Flash, CF) 등을 제어하는 컨트롤러를 포함 할 수 있다.

[0081] 미디어처리부(1170)는 전자장치(1100)에서 처리된 데이터나 외부 입력장치에서 입력된 데이터를 가공하여 영상, 음성 및 기타 형태로 전달되도록 외부 인터페이스 장치로 출력하는 그래픽 처리 장치(Graphics Processing Unit, GPU), 디지털 신호 처리 장치(Digital Signal Processor, DSP), 고선명 오디오(High Definition Audio, HD Audio), 고선명 멀티미디어 인터페이스(High Definition Multimedia Interface, HDMI) 컨트롤러 등을 포함할 수 있다.

[0082] 본 발명의 기술 사상은 상기 바람직한 실시예에 따라 구체적으로 기술되었으나, 상기 실시예는 그 설명을 위한 것이며, 그 제한을 위한 것이 아님을 주의하여야 한다. 또한, 본 발명의 기술분야의 통상의 전문가라면 본 발명의 기술사상의 범위내의 다양한 실시예가 가능함을 이해할 수 있을 것이다.

### 부호의 설명

|        |               |               |

|--------|---------------|---------------|

| [0083] | 100 : 기판      | 110 : 제1웰     |

|        | 120 : 제2웰     | 130 : 트렌치     |

|        | 140 : 메모리막    | 142 : 터널절연막   |

|        | 144 : 전하트랩막   | 146 : 전하차단막   |

|        | 150 : 게이트전극   | 160 : 제1접합영역  |

|        | 170 : 제2접합영역  | 180 : 제1불순물영역 |

|        | 190 : 제2불순물영역 | 200 : 제1도전라인  |

|        | 210 : 제2도전라인  | MG : 메모리게이트   |

### 도면

#### 도면 1a

도면1b

도면2a

## 도면2b

## 도면3a

## 도면3b

## 도면3c

## 도면3d

## 도면3e

## 도면4