(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5019689号

(P5019689)

(45) 発行日 平成24年9月5日(2012.9.5)

(24) 登録日 平成24年6月22日(2012.6.22)

(51) Int.Cl.

F 1

|        |         |           |

|--------|---------|-----------|

| HO 1 L | 27/06   | (2006.01) |

| HO 1 L | 27/088  | (2006.01) |

| HO 1 L | 21/8234 | (2006.01) |

| HO 1 L | 27/04   | (2006.01) |

| HO 1 L | 21/822  | (2006.01) |

|        |       |         |

|--------|-------|---------|

| HO 1 L | 27/06 | 3 1 1 A |

| HO 1 L | 27/08 | 1 0 2 F |

| HO 1 L | 27/04 | H       |

請求項の数 10 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2001-550813 (P2001-550813)  |

| (86) (22) 出願日 | 平成13年1月4日 (2001.1.4)          |

| (65) 公表番号     | 特表2003-519926 (P2003-519926A) |

| (43) 公表日      | 平成15年6月24日 (2003.6.24)        |

| (86) 國際出願番号   | PCT/US2001/000182             |

| (87) 國際公開番号   | W02001/050533                 |

| (87) 國際公開日    | 平成13年7月12日 (2001.7.12)        |

| 審査請求日         | 平成19年12月14日 (2007.12.14)      |

| (31) 優先権主張番号  | 60/174,326                    |

| (32) 優先日      | 平成12年1月4日 (2000.1.4)          |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 09/583,141                    |

| (32) 優先日      | 平成12年5月30日 (2000.5.30)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                         |

|-----------|-------------------------------------------------------------------------|

| (73) 特許権者 | 509302434<br>ソフィックス ビーヴィービーエー<br>ベルギー, ベー-8470 ギステル,<br>ブルーゼ バーン 188ア-  |

| (74) 代理人  | 100094318<br>弁理士 山田 行一                                                  |

| (74) 代理人  | 100123995<br>弁理士 野田 雅一                                                  |

| (74) 代理人  | 100107456<br>弁理士 池田 成人                                                  |

| (72) 発明者  | ラス, ク里斯チャン, コーネリアス<br>アメリカ合衆国, ニュージャージー州<br>, プリンストン, キャッスルトン<br>ロード 73 |

最終頁に続く

(54) 【発明の名称】電流バラスティングE S D高感度装置のための装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第一の領域及び第二の領域を有している静電放電高感度(E S D)装置の電流を安定させ、該E S D装置のオン時に、基準電位のソースに接続されているターミナルへの前記第一の領域及び前記第二の領域を通る伝導パスを提供することによって過電圧状態から電子回路のノードを保護する装置であって、前記装置は、

前記E S D高感度装置の前記第一の領域に設けられた複数の離隔配置された接続ターミナルであって、前記第一の領域にそれぞれの電気コンタクトを提供し、前記第一の領域及び前記離隔配置された接続ターミナルは、前記第一の領域内の離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すように構成されており、前記横方向抵抗は、前記E S D装置がオン時の前記伝導パスの抵抗より大きい、複数の離隔配置された接続ターミナルと、

複数の絶縁した非交差伝導性のストリップであって、各々が第一の端及び第二の端を有し、前記絶縁した非交差伝導性のストリップの各々の前記第一の端部が電気的に前記ノードに接続しており、前記絶縁した非交差伝導性のストリップの各々の前記第二の端部が前記複数の離隔配置された接続ターミナルのそれぞれ異なる一つに接続している、複数の絶縁した非交差伝導性のストリップと、

を備える装置。

## 【請求項 2】

前記E S D高感度装置の前記第二の領域に設けられた複数の更なる離隔配置された接続

10

20

ターミナルであって、前記第二の領域にそれぞれの電気コンタクトを提供し、前記第二の領域及び前記離隔配置された接続ターミナルは、前記更なる離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すために構成されている、複数の更なる離隔配置された接続ターミナルと、

複数の更なる非交差伝導性のストリップであって、各々が第一の端部及び第二の端部を有し、前記更なる非交差伝導性のストリップの各々の前記第一の端部が、前記更なる離隔配置された接続ターミナルのそれぞれ異なる一つに電気的に接続されており、前記更なる非交差伝導性のストリップの各々の前記第二の端部が、基準電位の前記ソースに接続された前記ターミナルに接続されている、複数の更なる非交差伝導性のストリップと、

を更に備える請求項1に記載の装置。

10

### 【請求項3】

第一の領域及び第二の領域を有している静電放電高感度(ESD)装置の電流を安定させ、過電圧状態から電子回路のノードを保護するための装置であって、前記装置は、

前記ESD高感度装置の前記第一の領域に設けられた複数の離隔配置された接続ターミナルであって、前記第一の領域にそれぞれの電気コンタクトを提供し、前記第一の領域及び前記離隔配置された接続ターミナルは、前記離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すように構成されている、複数の離隔配置された接続ターミナルと、

複数の絶縁した非交差伝導性のストリップであって、各々が第一の端及び第二の端を有し、前記絶縁した非交差伝導性のストリップの各々の前記第一の端部が電気的に前記ノードに接続しており、前記絶縁した非交差伝導性のストリップの各々の前記第二の端部が前記複数の離隔配置された接続ターミナルのそれぞれ異なる一つに接続している、複数の絶縁した非交差伝導性のストリップと、

20

前記ESD高感度装置の前記第二の領域に設けられた複数の更なる離隔配置された接続ターミナルであって、前記第二の領域にそれぞれの電気コンタクトを提供し、前記第二の領域及び前記離隔配置された接続ターミナルは、前記更なる離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すために構成されている、複数の更なる離隔配置された接続ターミナルと、

複数の更なる非交差伝導性のストリップであって、各々が第一の端部及び第二の端部を有し、前記更なる非交差伝導性のストリップの各々の前記第一の端部が、前記更なる離隔配置された接続ターミナルのそれぞれ異なる一つに電気的に接続されており、前記更なる非交差伝導性のストリップの各々の前記第二の端部が、基準電位のソースに接続されている、複数の更なる非交差伝導性のストリップと、

を備えており、

30

前記ESD高感度装置が寄生的バイポーラトランジスタを形成するNMOS-ESD装置を備え、前記第一の領域がドレイン領域であり、前記第二の領域がソース領域であり、第三の領域がゲート領域であり、前記装置が複数の伝導性の素子を含み、各々の伝導性の素子が、前記ESD装置の前記第三領域に電気的に接続しており、前記複数の離隔配置された接続ターミナルの隣接のしたものそれぞれの対の間の前記第一の領域に延び、前記さらなる離隔配置した接続ターミナルの複数の隣接のもののそれぞれの対の間の前記ESD装置の前記第2領域に延びた、装置。

40

### 【請求項4】

前記絶縁した非交差伝導性のストリップの各々は、抵抗を示し、前記第一の領域及び前記複数の離隔配置された接続ターミナルは、前記ESD装置の前記第一の領域内の離隔配置された接続ターミナルの連続したものの間の前記横方向抵抗が、少なくとも一つの前記非交差伝導性のストリップによって示される抵抗と比べ比較的大きいように構成される請求項3に記載の装置。

### 【請求項5】

メインゲート及び二次ゲートを有する分割ゲートと、

複数の伝導性の素子と、

50

を更に備え、

前記二次ゲートは前記前記 E S D 装置の前記第一の領域の完全に上方にあり、各々の伝導性の素子が第一の端部及び第二の端部を有し、前記伝導性の素子の前記第一の端部は前記 E S D 装置の前記第一の領域の上の前記二次ゲートに電気的に接続され、前記第二の端部は、前記離隔配置された接続ターミナルのそれぞれの対の間で、前記 E S D 装置の前記第一の領域を横切って延びた、請求項1に記載の装置。

**【請求項 6】**

静電破壊（E S D）保護装置であって、該 E S D 装置のオン時に、基準電位のソースに接続されているターミナルへの該 E S D 装置を通る伝導パスを提供することによって過電圧状態から電子回路のノードを保護するものであり、当該 E S D 装置は、

10

第一の半導体型のドレイン領域であって、前記ドレイン領域は、該ドレイン領域にそれぞれの電気コンタクトを提供する複数の離隔配置された接続ターミナルを備え、前記ドレイン領域及び前記離隔配置された接続ターミナルが、前記離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すために構成され、前記横方向抵抗は、前記 E S D 装置がオン時の当該 E S D 装置を通る前記伝導パスの抵抗より大きい、ドレイン領域と、

第二の半導体型のチャネル領域であって、所定の長さ及び幅を有し、該チャネル領域の前記幅に沿って、前記ドレイン領域と物理的に接触する、チャネル領域と、

第一の半導体型のソース領域であって、前記チャネル領域の前記幅に沿って前記チャネル領域と物理的に接触し、前記チャネル領域の前記長さによって前記ドレイン領域から分離されており、基準電位のソースに接続されている前記ターミナルに接続されている、ソース領域と、

20

前記チャネル領域から絶縁され、その上に配置されるゲート電極と、

複数の絶縁した非交差伝導性のストリップであって、各々が第一の端部及び第二の端部を有し、前記絶縁された非交差伝導性のストリップの各々の前記第一の端部は、前記第一の領域の上方の前記ノードに接続しており、前記非交差伝導性のストリップの各々の前記第二の端部は、前記複数の離隔配置された接続ターミナルのそれぞれ異なる一つに接続している、複数の絶縁した非交差伝導性のストリップと、

を備える装置。

**【請求項 7】**

前記 E S D 保護装置の前記ソース領域に設けられた複数の更なる離隔配置された接続ターミナルであって、前記ソース領域にそれぞれの電気コンタクトを提供し、前記ソース領域及び前記離隔配置された接続ターミナルが、前記更なる離隔配置された接続ターミナルの連続したものの間での横方向抵抗を示すために構成されている、複数の更なる離隔配置された接続ターミナルと、

30

複数の更なる非交差伝導性のストリップであって、各々が第一の端部及び第二の端部を有し、前記更なる非交差伝導性のストリップの各々の前記第一の端部は、前記更なる離隔配置された接続ターミナルのそれ異なる一つに電気的に接続しており、前記更なる非交差伝導性のストリップの各々の前記第二の端部は基準電位のソースに接続している、複数の更なる非交差伝導性のストリップと、

を更に備える請求項 6 に記載の E S D 装置。

40

**【請求項 8】**

静電破壊（E S D）保護装置であって、

第一の半導体型のドレイン領域であって、前記ドレイン領域は、該ドレイン領域にそれぞれの電気コンタクトを提供する複数の離隔配置された接続ターミナルを備え、前記ドレイン領域及び前記離隔配置された接続ターミナルが、前記離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すために構成される、ドレイン領域と、

第二の半導体型のチャネル領域であって、所定の長さ及び幅を有し、該チャネル領域の幅に沿って前記ドレイン領域と物理的に接触する、チャネル領域と、

第一の半導体型のソース領域であって、前記チャネル領域の幅に沿って前記チャネル領域と物理的に接触し、前記チャネル領域の長さによって前記ドレイン領域から分離されて

50

いる、ソース領域と、

前記チャネル領域から絶縁され、その上に配置されるゲート電極と、

複数の絶縁した非交差伝導性のストリップであって、各々が第一の端部及び第二の端部を有し、前記絶縁された非交差伝導性のストリップの各々の前記第一の端部は、前記第一の領域の上方の前記ノードに接続しており、前記非交差伝導性のストリップの各々の前記第二の端部は、前記複数の離隔配置された接続ターミナルのそれぞれ異なる一つに接続している、複数の絶縁した非交差伝導性のストリップと、

を備えており、

前記ドレイン領域は、複数のドレイン領域にセグメント化され、各々のセグメント化されたドレイン領域は、前記離隔配置された接続ターミナルのそれぞれ異なる一つを備え、前記セグメント化されたドレイン領域は、前記第二の型の半導体のそれぞれのチャネルによって分離されており、

10

前記ソース領域は複数のソース領域にセグメント化され、各々のセグメント化されたソース領域は、前記更なる離隔配置された接続ターミナルのそれぞれ異なる一つを備え、前記セグメント化されたソース領域は、前記第二の型の半導体のそれぞれのチャネルによって分離されている、E S D 装置。

#### 【請求項 9】

複数の伝導性の素子であって、前記離隔配置された接続ターミナルの隣接するものの間に20

ある前記ドレイン領域のそれぞれの領域から絶縁され、その上に配置されている、複数の伝導性の素子と、

前記複数の伝導性の素子を相互接続させる接続素子であって、前記ゲート電極に隣接しているが前記ゲート電極から分離した前記ドレイン領域のエリア内の前記ドレイン領域より上に位置し、そこから絶縁された接続素子と、

を含む請求項 6 に記載の E S D 装置。

#### 【請求項 10】

マルチプルコンポーネント静電破壊 ( E S D ) 保護装置であって、該マルチプルコンポーネント E S D 装置のオン時に、基準電位のソースに接続されている端子への該マルチプルコンポーネント E S D 装置を通る伝導バスを提供することによって過電圧状態から電子回路のノードを保護するものであり、当該マルチプルコンポーネント E S D 装置は、

複数のコンポーネント E S D 装置であって、

30

各々のコンポーネント E S D 装置は、

第一の半導体型のドレイン領域であって、前記ドレイン領域は、該ドレイン領域にそれぞれの電気コンタクトを提供する複数の離隔配置された接続ターミナルを含み、前記ドレインの領域及び前記離隔配置された接続ターミナルが、前記離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すために構成されており、前記横方向抵抗は、当該マルチプルコンポーネント E S D 装置がオン時の前記伝導バスによって示される抵抗より大きい、ドレイン領域と、

第二の半導体型のチャネル領域であって、所定の長さ及び幅を有し、該チャネル領域の前記幅に沿って、前記ドレイン領域と物理的に接触する、チャネル領域と、第一の半導体型のソース領域であって、前記チャネル領域の前記幅に沿って前記チャネル領域と物理的に接触し、前記チャネル領域の長さによって前記ドレイン領域から分離されており、前記ソース領域は、前記ソース領域にそれぞれの電気コンタクトを提供する複数の更なる離隔配置された接続ターミナルを含み、前記ソース領域及び前記更なる離隔配置された接続ターミナルが、前記更なる離隔配置された接続ターミナルの連続したものの間の横方向抵抗を示すために構成されているソース領域と、

40

前記チャネル領域から絶縁され、その上に配置されるゲート電極と、

第一の電気的に伝導性のターミナル及び第二の電気的に伝導性のターミナルと、

複数の第一の非交差伝導性のストリップであって、各々、第一の端部及び第二の端部を有し、前記第一の非交差伝導性のストリップの各々の前記第一の端部が、電気的に前記第一の電気的に伝導性のターミナルに接続し、前記第一の非交差伝導性のストリップの各

50

々の第二の端部が、前記ドレイン領域との電気コンタクトを作るために、前記複数の離隔配置された接続ターミナルのそれぞれ異なる一つに接続されている、複数の第一の非交差伝導性のストリップと、

複数の第二の非交差伝導性のストリップであって、各々、第一の端部及び第二の端部を有し、前記第二の非交差伝導性のストリップの各々の前記第一の端部が、電気的に前記第二の電気的に伝導性のターミナルに接続し、前記第二の非交差伝導性のストリップの各々の前記第二の端部は、前記ソース領域とのコンタクトに領域を作るために前記複数の異なる離隔配置された接続ターミナルのそれぞれ異なる一つに接続されている、複数の第二の非交差伝導性のストリップと、

を備える複数のコンポーネント ESD 装置と、

10

前記コンポーネント ESD 装置の全ての前記第一の電気的に伝導性のターミナルを接続している第一の導体と、

前記コンポーネント ESD 装置の全ての前記第二の電気的に伝導性のターミナルを接続している第二の導体と、

を備える装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

この特許出願は、2000年1月4日に出願したアメリカ仮出願第 60/174,326 号の利益を主張する。なお、その内容は当該明細書に援用されている。

20

##### 【0002】

##### 【発明の分野】

この発明は、一般に電子デバイスの電流保護に関連があり、特に完全にシリサイド化された静電気放電高感度装置での電流バラスティングに関する。

##### 【0003】

##### 【発明の背景】

金属酸化物半導体 (MOS) ドラッグ・アンド・ドロップ回路は、電圧の形で入力信号及び移送出力信号を受ける。これらの装置は、非常に少ない装置面積で一般的に作られ、回路の合計を最大にするために、集積回路の上で実行されることができ、回路が高周波数であるが最小の電源デマンドで動くことができるようになっている。しかし、これらの装置の問題は、集積回路の内部回路ノード、出力端子、又は入力端子に印加される電気過負荷からの損傷に対する感度である。これらの装置のためのゲート酸化膜は一般的に非常に薄く、印加電圧が比較的低いレベルを超えたときでさえ壊れる可能性がある。このような破壊は、トランジスタ又は他の装置の即時又は促進された破壊を引き起こすであろう。過剰電圧は、静電破壊 (ESD) の形でしばしば応力に起因する。広く知られるように、ESD 現象は、簡潔に述べるが、アンペアのオーダーの比較的大きい電流を示すことができる。ESD 現象と関連した闘争問題のために、MOS 装置の製造業者は、速くノードを放電することのできるパスを提供する保護装置を設計する。保護装置は、装置の入力バッファ又は出力バッファー・パッドと、基準電位 (例えば接地) のソースとの間に配置され、害される可能性のある装置から ESD 電圧を速く伝導するようになっている。なお、ESD 装置、ESD 保護装置、及び ESD 高感度装置の用語は、この文書中で取り換えられて使われることに注意してほしい。

30

##### 【0004】

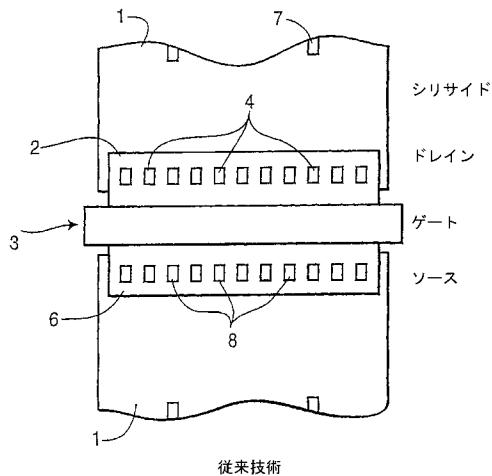

図 1 は、そのような ESD 保護装置の平面図である。例示的な装置は、ソース及びドレイン領域、ソース及びドレイン領域を分離するチャネル領域の上のゲート電極を有する N チャネル MOS ドラッグ・アンド・ドロップ回路として実行される。装置は MOS ドラッグ・アンド・ドロップ回路として実行されるが、それは、ドレイン領域に対応するコレクタ領域、ソース領域に対応したエミッタ領域、及びチャネル領域に対応したベース領域を有する寄生バイポーラトランジスタとして ESD 保護方式で動く。代表的な構成で、ゲート電極は、直接接続によって抵抗する接続を通して基準電位 (例えば接地) のソースに結ばれる。広く知られたように、バイポ

40

50

ーラトランジスタのコレクタとエミッタ (V<sub>c e</sub>)との間の電位が予め定められた電圧より大きくなるとき、スナップバック・トリガー電圧として知られているように、電圧V<sub>c e</sub>は、低い値へ急に戻る。装置は、スナップバックホールディング電圧として既知のようにこの低い値で電圧を固定し、この伝導方式で、トランジスタは、非常に低いインピーダンスを提示し、従ってどんな電流でも接地へ導く。

#### 【0005】

図1で示すE S D保護装置は、装置に対する電流ストレス及び電圧を低減するために、比較的高いE S D電流が伝えられることができる多重チャネルを含む。各々のチャネルは、トランジスタ3のドレイン領域2内の金属接続ターミナル4、及び対応する、トランジスタのソース領域6の金属接続ターミナル8によって画成される。接続ターミナル4は、固体の金属接続1に接続される。金属開口又はスロット7は、時々種々のプロセス理由のために必要である。理想的には、E S D状態の間、実質的に等しい「電流パス」は、E S D電流を放電するために複合の非交差及び非識別パスを作る接続ターミナルの各々の対の間に確立される。10

#### 【0006】

半導体処理におけるもう一つの傾向は、それらの性能を改良するためにシリサイドをM O Sトランジスタのソース及びドレイン領域に印加することである。シリサイド化された領域は、一般的にソース及びドレイン領域を形成するドープされたシリコンより低い表面抵抗を示す。20

#### 【0007】

しかし、E S D保護装置のゲート及びソース領域へのシリサイドを適用するのは、装置の性能に影響を及ぼすことができる。シリサイドがゲートの次に比較的あらいエッジを有することができるので、これは、高い局部的な電場、及び高電流密度（及び温度での対応する増加）によるエッジの劣化につながる。シリサイドが比較的低いシート抵抗を有するので、全体の装置電流は一つの少ない装置領域に流れることができ、即時の損傷を引き起こすことができる。20

#### 【0008】

E S D保護装置でのゲート - ツー - コンタクトスペーシングを増加させる試みがなされ、シリサイド故障の可能性を最小にする試みで熱 - 発生コレクタ - ベース接合領域から遠く離れてシリサイドを置く。そのような装置は以下に示すように図2で示される。しかし、これらの方法は、シリサイドを選択的に装置のソース及びドレイン電極の部分に加えることを防止するために、E S D保護装置のための特殊加工ステップを要求し、装置の幾何学形状を増加させる。30

#### 【0009】

分散平行放電パスを有するM O Sトランジスタ配列構造を実行することによって、E S D保護を提供するための試みもなされた。それは、アメリカ特許番号5,763,919において説明されている。これらの分散平行放電パスは、n - w e l l 領域で及び構造体のN + ドレイン領域で形成される。分散N + ドレイン領域は、局所酸化又は浅いトレンチアイソレーション（S T I）によって画成される。局部的な酸化又はS T I界面の近くの基板接合へのN + の部分は、機械的ストレス発生を示し、他のものの中で、電界焦点、電流リーケ及びブレークダウンへの弱さを起こす。この構造体も、N - w e l l による非線形放電パス抵抗を有し、構造体の性能は、拡散 / ウェル抵抗に依存している。この構造体のもう一つの特徴は、分散平行放電パスが基板から絶縁されないということであり、従って、基板に電位破壊を引き起こし（分散N + ドレイン領域）、望ましくない追加の寄生容量（分散N + 領域及びN - w e l l 領域）を加える。40

#### 【0010】

##### 【発明の概要】

本発明は、E S D保護装置の電流をバラスティングするための装置で具体化される。バラスティング抵抗は、一般の導体パッドと、E S D保護装置の離隔配置された複数の接続ターミナルのそれぞれとの間で非相交わっている伝導性ストリップを連結することによっ50

て達成される。接続ストリップは、E S D 装置の接続ターミナルと、コンタクトパッドとの間のそれぞれのバラスティング抵抗器を形成する。

**【 0 0 1 1 】**

本発明の一つの見地によれば、伝導性のストリップは、金属から形成される。

**【 0 0 1 2 】**

本発明の別の見地から述べると、伝導性のストリップは、ポリシリコンから形成される。

**【 0 0 1 3 】**

本発明のまだもう一つの見地に従うと、伝導性のストリップは、バイア及び接続している層の垂直に曲折接続から形成される。

10

**【 0 0 1 4 】**

本発明のまだもう一つの見地に従うと、接続ターミナルの間の横方向抵抗は、ターミナルの各々の対の間で局所的に E S D 装置のドレイン領域をセグメント化することによって高められる。

**【 0 0 1 5 】**

本発明の別の見地から述べると、接続ターミナルの間の横方向抵抗は、E S D 装置のゲート電極に平行な部分及び伝導性のストリップの間で伸びた更なる部分を有する、更なるゲート電極を画成することによって高められる。

**【 0 0 1 6 】**

本発明の別の見地から述べると、マルチプルコンポーネント並列接続 E S D 装置として E S D 装置は実行され、各々のコンポーネント E S D 装置はドレイン領域、ゲート領域及びソース領域を有し、個々の複数のバラスティング抵抗器を形成する複数の非交差伝導性のストリップを、一般的の電気的に伝導性のターミナルと各 E S D 装置の個々のドレイン領域での離隔配置された複数の接続ターミナルの各々との間で含む。

20

**【 0 0 1 7 】**

上述のもの概要及び後述の詳細な説明は本発明の例示であって、限定的でないことを理解されたい。

**【 0 0 1 8 】**

**【本発明の詳細な説明】**

添付の図面と関連して読んだ場合、本発明は以下の詳細な説明から最もよく理解される。通常の習慣に従うと、図面の種々の特徴は、一定の尺度を持っていないことを強調する。これに対して、種々の特徴の寸法は、明確にするために任意に拡大又は縮小されている。

30

**【 0 0 1 9 】**

本発明は、寄生N P Nトランジスタとして機能するN M O S E S D保護装置に関して説明されるが、本発明が、寄生P N Pトランジスタ、ダイオード（例えばツェナーダイオード、アバランシダイオード）及びシリコン制御整流器として機能するP M O S保護装置等の他のE S D装置（例えばM O S又はバイポーラ）のために使われることができることは、熟考される。これらの代替実施形態で、一つのE S D保護装置は、マルチプル並列接続を有する。

40

**【 0 0 2 0 】**

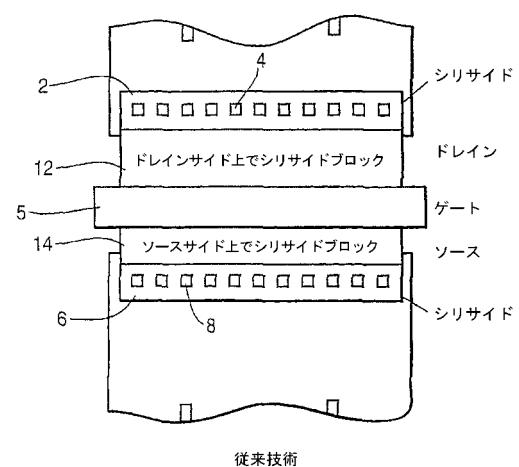

上で述べるように、装置でローカライズされた電流の大きさを縮小する一つの方法は、バラスティング抵抗器を加えることである。図2（先行技術）はシリサイド化したN M O S装置の平面図である。そして、それは電流バラスティングを導入するためにシリサイドの局所プロッキングを使う。図2で示されるE S D保護装置は、離散的接続ターミナル4及び8を含み、接点領域2及び6だけに、シリサイドが加えられている。ドレイン領域12の残余及びソース領域14は、シリサイド化していない。電流バラスティングは、シリサイドが加えられない領域の長さに対する構造体の幅のアスペクト比のために発生する（例えば領域12及び14）。図2で表される形状の一つの不利は、シリサイドが選択されたM O S装置のドレイン及び/又はソース電極の一部だけに適用された装置を形成するた

50

めに要求される追加の処理ステップが高価であり、場合によっては、集積回路操作の歩留まり及び／又は性能を縮小すると知られている。

#### 【0021】

本発明は、E S D 装置のコンタクト電極と外部コンタクトとの間の別個の電気的に絶縁したバラスト電流バス、あるいは、保護されている電流伝達装置を作ることによって先行技術の不足を克服する。これらの絶縁したバラスト電流バスは、先行技術装置より均一に電流を分散するか、電流の集中を低減し、次に、E S D 装置の局所加熱を低減する。本発明の例示的な実施形態は、主にE S D 電流をチャネルの間で横方向抵抗を示す非交差抵抗チャネルに閉じ込める。チャネル間横方向抵抗及び抵抗チャネルの組合わせは電流フローがチャネルの中で均一に広げられることを確実にし、そして、E S D 電流フローを閉じ込めて電流集中を大きく低減する。

#### 【0022】

電流発明のバラスト電流バスが電気的に半導体基板から分離されるので、いくつかの利点が先行技術に提供される。これらの利点は、拡散／ウェル抵抗から独立した保護性能と、局部的な酸化及びシリコンの間の材料界面に起因する付加された機械的ストレスのないことを含む。付加された機械的ストレスの不利は、(1)電界の局所化、(2)リーク電流及び(3)ブレーカダウンの増加する見込みを含む。また、本発明の絶縁バラスト電流バスは、先行技術に対して、バラスト抵抗線形性、バラスト抵抗のより低い値、接合容量の付加のこと、よりコンパクトなレイアウト及び余分のプロセスステップ(シリサイド-ブロック化デバイスが有するような)のない、他の利点を提供する。

#### 【0023】

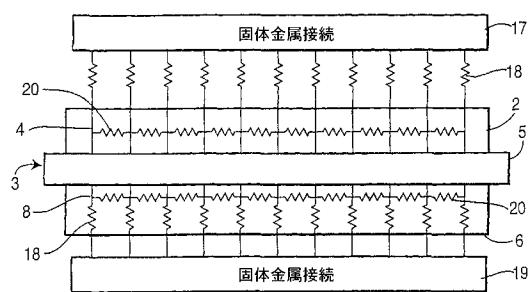

図3は、横方向抵抗及びバラスティング抵抗を説明した本発明の例示的な実施形態の平面図の部分的な回路図である。本実施形態で、例えば、集積回路の外部コンタクトを示す金属コンタクト17は、複数の非交差抵抗素子18を通して、E S D 保護装置3のドレイン領域2に接続される。下記のように、素子18の各々は、それぞれのバラスティング抵抗を提供する。E S D 装置3のドレイン領域2の上の抵抗素子18の間に複数の抵抗素子20がある。これらの素子の各々は、抵抗素子18のバラスティング作用を高める横方向抵抗を提供する。横方向抵抗器は、E S D 装置3のドレイン2の形状のプロダクトであり、電気絶縁が中で提供されている。ドレイン領域が比較的狭いので、かなりの抵抗が、隣接の接続ターミナルの間に存在する。この抵抗は、装置に沿った追加であって、右端のコンタクト電極と左端の接点との間の抵抗が、介在抵抗の合計であるこのようになっている。E S D 装置3のソース領域6も、バラスティング抵抗器18及び横方向抵抗器20を含む。

#### 【0024】

本発明の例示的な実施形態では外部コネクタ17にE S D 装置を連結するが、E S D 装置が過電圧状態から回路の他のノードを保護するために連結されることは、企図される。例えば、E S D 装置は、回路の正と負の操作可能電力接続の間で連結することができる。図3は、E S D 装置の両方のソース及びドレイン領域に連結されているバラスティング抵抗器を示すが、それらがソース領域だけ又はドレイン領域だけのどちらにも接続されることができるることは、企図される。

#### 【0025】

非交差抵抗チャネルの中の電流の均一な分配が発生する。それは、一つのチャネルが他のチャネルより多くの電流を引き出すならば、抵抗チャネル18を横切る電圧降下は、外部コンタクト17でのより高い電圧という結果を増加させるからである。このより高い電圧は、次に、他の非交差チャネルを通してより大きな電流フローを誘導し、高い電流が他のチャネルの中で再分配されるべき高い電圧を一つのチャネルに引き起こすことになる。この分析は、チャネルが装置を通して異なったままであると仮定する。横方向抵抗20は、電流フローがE S D 保護装置の上で接続ターミナルの間で低減されることを確実とする。E S D 現象の間、E S D 保護装置を通した伝導バスは、一つの接続ターミナルから次の伝導バスより低い抵抗を有する。理想的には、横方向抵抗20の値は、できるだけ大き

10

20

30

40

50

くなければならない。横方向抵抗の値は、コンタクト4の各々及びコンタクト8の各々の間隔を増加させることによって増加することができる、しかし実現すると、間隔が若干の値より増加するとき、装置の幅効率は減少する。発明者は、E S D保護装置の「オン」抵抗よりも大体大きな抵抗のどのような値が許容できるか決定した。従って、バラスティング抵抗器18及び横方向抵抗器20の組合せは、E S D装置3を通して複合の非交差バスの中でE S D電流を均一に分散するために作動する。

#### 【0026】

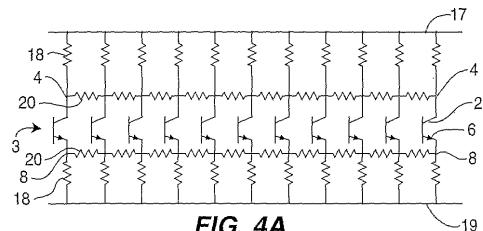

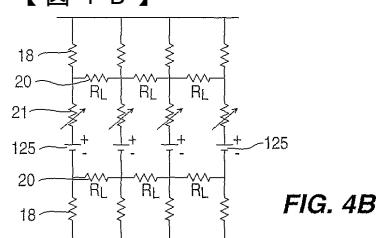

図4Aは、寄生的なバイポーラトランジスタを図で示している発明の例示的な実施形態の回路図であり、E S D装置のドレイン及びソース上の接続ターミナル4及び8のそれぞれの対の間で流れている「電流バス」によって形成される。図4Aで示すように、例示的なE S D装置の構造体は、E S D装置のドレイン接続ターミナル4に接続されるコレクタ電極を有している複数のオープンベースN P Nトランジスタを形成し、エミッタ電極は、E S D装置のソース接続ターミナル8に接続した。トランジスタを横切る電圧がスナップバック閾値電位を超える時、複数の寄生的なN P Nトランジスタの各々は、E S D電流及び電圧状態の上に他から生じている電流を伝えるためにスナップバックモードに入る。オープンベース装置として、寄生的なN P Nトランジスタが示されるが、ベース電極が半導体基板で実行されるので、装置が必ずしもオープンベースであるというわけではない。しかしベース電極に印加される基板電位は、比較的小さく、寄生的なN P NトランジスタのE S D保護装置としての性能に実質的に影響を及ぼさない。

#### 【0027】

図4Bは、N P Nトランジスタによって示される可変抵抗を図示した図4Aで示される本発明の実施形態の等価回路図である。図4Bで、図4Aで示されるN P Nトランジスタは各々がスナップバック保持電圧によって決定されたオフセット電圧ソース125を有する可変抵抗21としてモデル化される。各々の可変抵抗21のための抵抗の値は、それぞれの導電バス中を流れるE S D電流の関数である。理想的には、前に述べたように、横方向抵抗20は伝導バスの中でE S D電流の均一な分配を確実にするようにできるだけ大きくなければならない。この状態は、横方向抵抗20及びバラスト抵抗18を可変抵抗21と比較して大きくすることによって満足される。

#### 【0028】

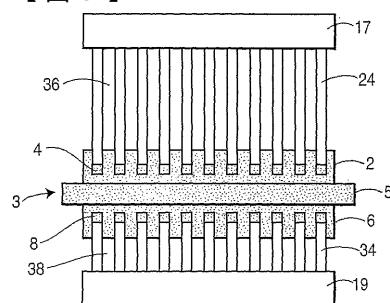

図5は、本発明の第一の例示的な実施形態の平面図であり、バラスト抵抗器を形成するために金属非交差ストリップ24及び34を使用する。図5で、装置のドレイン側の金属ストリップ24は、E S D装置3のシリサイド化したドレイン領域2内の、共通端子17及び離散的な接続ターミナル4の間で連結される。装置のソース側の金属ストリップ34は、シリサイド化したソース領域6内のそれらの離散的な接続ターミナル8に連結されてソース領域6を共通端子19に接続し、それは、例えば、基準電位（例えば接地）のソースに接続されることができる。金属ストリップ24は、非交差であるために構成されて及び間隔36で分離される。金属ストリップ34は、また、非交差であるために構成されて及び間隔38によって分離される。金属の各々のストリップは、E S D電流フローのためのパスを提供して及びバラスティング抵抗を提供する。横方向抵抗は、離散的な接続点に各々の金属ストリップを連結することによって隣接の金属ストリップの間で示される。本発明の例示的な実施形態で、各々の金属細長片、ストリップの間の間隔及びドレイン領域2の高さの長さ及び幅は、バラスティング抵抗の所望の量を提供するように選ばれる。発明のもう一つの実施形態で、電流バラスティングは、装置の一方（すなわち、ドレイン側かソース側）だけで、提供される。酸化物コーティングは金属ストリップ24及び34及び半導体基板の間で絶縁を提供することを支援する。ストリップ24及び34の形成は、標準的な金属溶射手続の部分として少しの特殊加工ステップも必要としない。

#### 【0029】

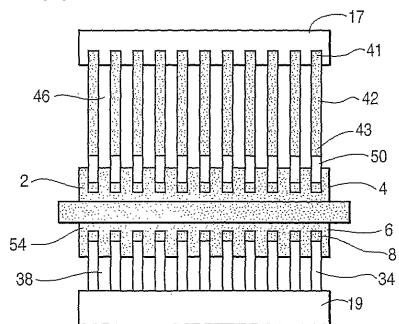

図6は、バラスティング抵抗器を形成するためにポリシリコンの非交差ストリップの使用を図で示す本発明の第二の例示的な実施形態の平面図である。本実施形態において、ポリシリコン・ストリップ42は、コネクタ41によって共通端子17に接続されて及びコ

10

20

30

40

50

ネクタ43によって短い金属ストリップ50に接続される。順番に、短い金属ストリップ50は、接続ターミナル4によってESD装置3のドレイン領域2に接続される。発明の例示的な実施形態で、金属領域50が、ESD装置にポリシリコン・ストリップを接続するために使われる。それは、今の現状技術処理ルールがシリサイド化拡散2に直接にポリシリコンを接続しないからである。ストリップ42は、非交差であるように構成され、間隔46によって分離される。発明のこの例示的な実施形態で、ESD装置3のソース側で、金属ストリップ34は離散的な接続ターミナル8で、シリサイド化したソース領域6に連結される。例示的な実施形態で、これらのストリップは、共通端子19によって接地にソース領域6を接続する。

## 【0030】

10

図5で示される実施形態のように、ストリップ34は、非交差であるように構成され、間隔38によって分離される。金属ストリップ24の上にポリシリコン・ストリップ42を使う利点は、図5で示される、ポリシリコン・ストリップのシート抵抗がほぼ金属のシート抵抗より大きな桁であることである。このより高い抵抗のため、シリサイド化したポリシリコン・ストリップの使用は、金属ストリップが使われる時よりもコンパクトな構造体ができるようにする。図6で示される構造体は、どんな追加のプロセスステップなしでも形成されることができる。他のポリシリコン層が処理されるとき、ポリシリコン・ストリップ42は置かれることができ、従って、下にある酸化物層は、ストリップ34及び42の間で絶縁を提供する。金属ストリップ50及び34は、標準的なメタライゼーションプロセス及びコネクタ41、43の部分であることができ、例えば、接続ターミナル4及び8は、また、標準的な半導体プロセスの部分であるタングステン・バイアであることができる。

20

## 【0031】

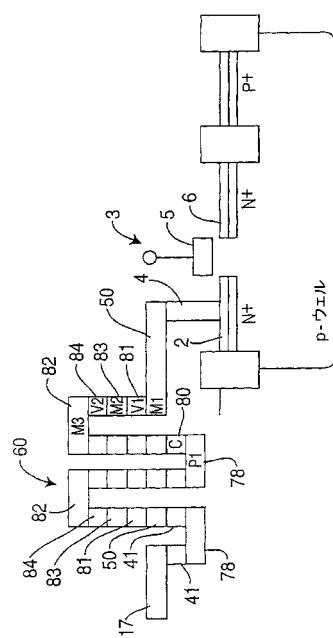

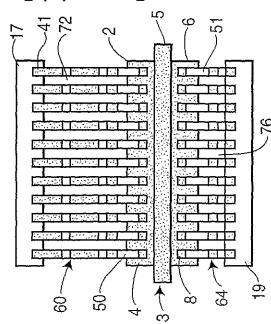

図7Aは、垂直曲折非交差ストリップを図で示した本発明の第三例示的な実施形態の平面図である。本実施形態において、各々のストリップ60及び64は、例えば、接合することによって形成される。そして、また、プロセスの部分であるコンタクトバイアを有する、ポリシリコン及び金属ストリップが集積回路操作で異なるレベルで形成される。バラスティング抵抗器60及び64は、ポリシリコン、バイア及び金属の直列結合によって形成される。各々のバラスティング抵抗器のコンポーネントを絶縁する同じ機構によって、バラスティング抵抗器60及び64は、絶縁される。装置のドレイン側の上で、垂直曲折非交差ストリップ60は、接続ターミナル4によってシリサイド化したドレイン領域2に連結される。垂直曲折非交差ストリップ60は、間隔72によって分離される。垂直に曲折非交差ストリップ64は、ソース装置の側で、接続ターミナル8でシリサイド化したソース領域6に連結される。ストリップ64は、非交差するために構成されて及び間隔76によって分離される。

30

## 【0032】

図7Bは、発明の第三実施形態に従う一つの垂直に曲折ストリップ60の断面図である。この曲折ストリップは、ESD装置3のドレイン領域2に、共通端子17を接続する。外部コネクタ17で始まり、ストリップ60は、ポリシリコン78のセグメントまで下に向かってコネクタ41、上にもう一つのコネクタ41、金属層50、バイア81、第二の金属層83のセグメント、第二バイア84、及び第三金属層82のセグメントを含む。第三金属層82のセグメントは、ポリシリコン層78のもう一つのセグメントに、バイアの直列結合を通して、第二の金属層のセグメント、もう一つのバイア、第一の金属層のセグメント及びコネクタに接続される。ポリシリコンのこの第二のセグメントは、第三金属層82の第二のセグメントに、コネクタ、第一の金属層、バイア、第二の金属層のセグメント及びもう一つのバイアのセグメントを通して接続される。最後に、この例示的な実施形態で、第三金属層82の第二のセグメントはバイア84、第二の金属層83のセグメント、もう一つのバイア81、第一の金属層50のセグメント及び接続ターミナル4の直列結合を通して、ESD装置3のドレイン領域2に接続される。本発明の例示的な実施形態で、第一の、第二の及び第三金属層はアルミニウム又は銅膜であることができ、バイア及び

40

50

接続ターミナルはタングステン・プラグであることができる。これらの直列結合は、バラスティング抵抗器 60 を形成する。本実施形態において、バイアの各々は、かなりの抵抗（例えば進んだ深いサブミクロン技術で 5 ~ 10 オーム）をバラスティング抵抗器 60 に加える。他の層の各々も抵抗を加え、一般的に、金属層の抵抗は、ポリシリコン層 78、コネクタ 41 及びバイア 81 及び 84 の合成抵抗と比較して無視してよい。7A 図及び 7B で表される本発明の例示的な実施形態の利点は、形状のコンパクト性である。

### 【0033】

曲折の数及び層の数は、例示的なだけである。満足なバラスティング抵抗器がより多いかより少ない層及び / 又はより多いかより少しの曲折を使って製造されることができることは、企図される。

10

### 【0034】

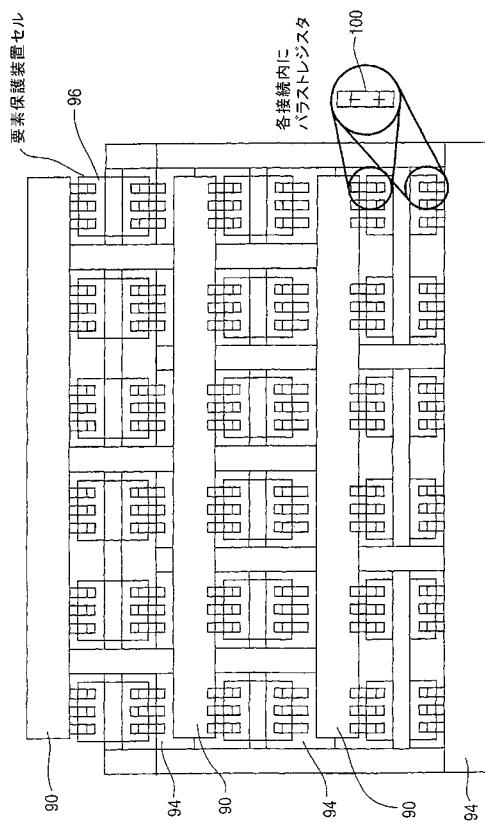

図 8 は、各個にバラストされた保護装置電池の配列を図で示した発明の第 4 の例示的な実施形態の平面図である。各々の要素保護装置電池 96 は、それぞれの非交差ストリップ 100 によって第一のターミナル 90 及び第二のターミナル 94 に連結される。非交差ストリップ 100 は、バラスティング抵抗を提供する。非交差ストリップ 100 は、前に説明した又は下で説明する実施形態の何でも含み、金属、ポリシリコン、垂直曲折ストリップ又はそれらの組合せを使って**バラスト抵抗器 100 を形成する**ことができる。図 8 で表される例示的な実施形態の利点は、比較的小さい領域において実行されることができ、多数の ESD 装置の上に ESD 電流を均一に分散し、従って比較的大きい ESD 現象を扱うことができる点である。

20

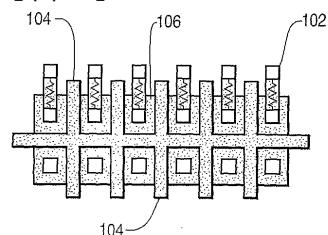

### 【0035】

図 9 は、発明の第 5 の実施形態の平面図であって、セグメント化されたドレイン及びソース領域を利用することによる、追加の側部絶縁及び改良されたトリガーを提供している ESD 保護装置である。図 9 で示される装置は、ポリシリコン伝導性の素子 104 及び下にある誘電及びウェル又は基板材料によって分離される活性領域 106 を含む。伝導性の素子 104 は、ゲート電極に接続されることを要求されず、従って、発明の代替実施形態で、伝導性の素子は、ゲート電極に接続されるか又は接続されない。非交差ストリップ 102 は、バラスト抵抗を提供する。非交差ストリップ 102 は、金属、シリサイド化ポリシリコン、垂直曲折ストリップ又はそれらのどんな組合せをも含む、前に説明した実施形態の何でも含むことができる。図 9 で示される装置は、ESD 装置で密に形成している別個の保護装置電池によって、能率的に領域を利用する。ポリシリコン素子 104 は、ソース及びドレイン領域で、側部電流を妨げ、非交差ストリップ 102 の間で絶縁を提供する。保護装置電池のごく近傍は、ESD 装置の改良されたトリガーを提供する。MOS テクノロジーを利用している図 9 で示される発明の実施形態で、トリガーは、増加するドレイン接合周辺部によって高められる（すなわち寄生的な n-p-n トランジスタの dV/dt（過渡状態）トリガリングを増加させることによって）。更なるトリガーの改善は、増加するドレインゲート・オーバラップ・キャパシタンスは、高いオーム抵抗を通してアースにゲート電極が接続されることをできるようにすることによって図 9 で示される実施形態で得られる。セグメント化されたドレイン領域が長いゲート領域の下でチャネル領域の延長部分によって更に分離されることが予想される。

30

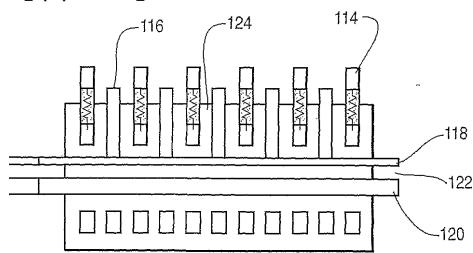

### 【0036】

図 10 は、局部的な高い電界密度を更に低減するために構成される ESD 装置を図で示した発明の第 6 の実施形態の平面図である。図 10 で表される配列は、ポリシリコン伝導性の素子 116 によって分離される活性領域 124 を含む。非交差ストリップ 114 は、バラスト抵抗を提供する。非交差ストリップ 114 は、金属、ポリシリコン、垂直曲折ストリップ又はそれらのいかなる組合せでも含む、前に説明した実施形態の何でも含むことができる。ポリシリコン素子 116 は、側部電流フローを妨げ、従って非交差ストリップ 114 の間で絶縁を提供する。しかし、ポリシリコン素子 112 の垂直線及び水平物セグメントの交わりで形成されるコーナーは、比較的高い局部的な電界密度を引き起こす可能性がある。図 10 で示される分割ゲート形状は、局部的な電界密度を低減する。この代

40

50

替形状でメインのポリシリコン・ストリップ(ゲート)120が、公称トランジスタ・ゲート長で形成される。ポリシリコン素子116は、狭いポリシリコン・ストリップ118によって接続され、該ストリップは、望ましくは、ドレイン領域内に完全に形成され、集積回路プロセスのために望ましくは最小のデザインルールより少ないゲート長を有している。スペース122は、ポリシリコン・ストリップ118及び120の間で、また、できるだけ狭く形成される。活性領域124、ポリシリコン・ストリップ118及び領域がスペース122で位置した活性領域(N+)は、更なるMOS/バイポーラトランジスタを形成する。このトランジスタ(それはESD装置のMOSトランジスタと直列にある)は、その短いゲート長のため、漏れるように故意に形成される。従って、この更なるトランジスタは、抵抗器として作動し、メイントランジスタのゲートのエッジと接触したドレインからのESD電流をそらす。装置で密集している電流を防ぐために、側部電流フローは、先に述べたようにポリシリコン素子116によって更に妨げられる。

#### 【0037】

本発明が複合の例示的な実施形態について説明されるが、先に述べたように、添付の請求項の範囲内で、行うことができる意図される。

#### 【図面の簡単な説明】

【図1】 図1(先行技術)は、完全にシリサイド化されたNMOS装置の平面図である。

【図2】 図2(先行技術)は、シリサイドの局所プロッキングを実行しているシリサイド化したNMOS装置の平面図である。

【図3】 図3は、回路図であって、部分的に平面図图形で、バラスティング抵抗及び横方向抵抗を説明した本発明の例示的な実施形態の図である。

【図4A】 図4Aは、寄生バイポーラ・デバイスに適用したものを示した本発明の例示的な実施形態の回路図である。

【図4B】 図4Bは、図4Aで示される例示的実施形態等価回路図であり、寄生的なバイポーラ・デバイスの可変抵抗を図で示し、電圧源のキャパシティをクランプしている電圧を示す。

【図5】 図5は、金属の非交差ストリップを図で示した本発明の例示的な実施形態の平面図である。

【図6】 図6は、ポリシリコンの非交差ストリップを図で示している本発明の例示的な実施形態の平面図である。

【図7A】 図7Aは、垂直に曲折非交差ストリップを図で示した、本発明の例示的な実施形態の平面図である。

【図7B】 図7Bは、一つの垂直曲折ストリップの断面図であり、実例の目的のために、垂直に曲折非交差ストリップ60のうちの一つが、図7Bで示される。

【図8】 図8は、各個の安定保護装置電池の配列を図で示した本発明の例示的な実施形態の平面図である。

【図9】 図9は、セグメント化されたドレイン及びソース領域を利用した改良されたトリガーを提供する安定保護装置電池の配列を図で示した本発明の実施形態の平面図である。

【図10】 図10は、安定保護装置電池の配列を図で示した本発明の実施形態の平面図であり、セグメント化されたドレイン領域を利用している改良されたトリガーを提供し、局所高電流密度を縮小するために構成される。

【図1】

【図2】

【図3】

【図4A】

【図4B】

【図5】

【図 6】

FIG. 6

【図 7 B】

【図 7 A】

FIG. 7A

【図 8】

【図 9】

FIG. 9

【図 10】

FIG. 10

---

フロントページの続き

(72)発明者 ヴァーヘージ , コーエン , ジェラード , マリア

アメリカ合衆国 , ニュージャージー州 , プリンストン , キャッスルトン ロード 7

7

審査官 宇多川 勉

(56)参考文献 特開平11-087631(JP,A)

特開平10-242296(JP,A)

特開平10-050933(JP,A)

特開昭60-136359(JP,A)

特開平02-273971(JP,A)

特開平02-105562(JP,A)

特開平11-103021(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/06

H01L 21/822

H01L 21/8234

H01L 27/04

H01L 27/088