### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2007/0108629 A1

Chang et al.

May 17, 2007 (43) Pub. Date:

### (54) WAFER LEVEL CHIP SCALE PACKAGING STRUCTURE AND METHOD OF FABRICATING THE SAME

(75) Inventors: **Shu-Ming Chang**, Hsinchu (TW); Lee-Cheng Shen, Hsinchu (TW); Wei-Chung Lo, Hsinchu (TW)

Correspondence Address:

BIRCH STEWART KOLASCH & BIRCH **PO BOX 747 FALLS CHURCH, VA 22040-0747 (US)**

(73) Assignee: Industrial Technology Research Insti-

(21) Appl. No.: 11/652,088

(22) Filed: Jan. 11, 2007

### Related U.S. Application Data

(63) Continuation-in-part of application No. 10/765,961, filed on Jan. 29, 2004, now Pat. No. 6,998,718.

#### **Publication Classification**

(51) Int. Cl. H01L 23/48 (2006.01)

#### ABSTRACT (57)

A wafer level chip scale packaging structure and the method of fabricating the same are provided to form a sacrificial layer below the bump using a normal semiconductor process. The bump is used to connect the signals between the Si wafer and the PCB. The interface between the sacrificial layer and the adjacent layers is the weakest part in the whole structure. When the stress applied to the bump is overloaded, the interface between the sacrificial layer and the adjacent layers will crash to remove the stress generated by different thermal expansion coefficients of the Si wafer and the PCB. The sacrificial layer would help avoid the crash occurring to the bump to protect the electrical conduction between the Si wafer and the PCB.

FIG.1(PRIOR ART)

FIG.2(PRIOR ART)

FIG.3(PRIOR ART)

FIG.4(PRIOR ART)

FIG.5

FIG.6

FIG.7A

FIG.7B

FIG.7D

FIG.7E

FIG.7F

FIG.8

FIG.9

FIG.10

-300

FIG.12E

311

FIG.12F

FIG.12G

FIG.14B

432

FIG.14C

FIG.14D

FIG.15C

FIG.15D

FIG.16A

FIG.16D

FIG.16E

FIG.16F

### WAFER LEVEL CHIP SCALE PACKAGING STRUCTURE AND METHOD OF FABRICATING THE SAME

## CROSS REFERENCE TO RELATED APPLICATION

[0001] This is a continuation-in-part of Ser. No. 10/765, 961, filed Jan. 29, 2004, entitled "WAFER LEVEL CHIP SCALE PACKAGING STRUCTURE AND METHOD OF FABRICATING THE SAME".

### BACKGROUND OF THE INVENTION

[0002] 1. Field of Invention

[0003] The invention relates to a wafer level chip scale packaging structure and the method of fabricating the same. In particular, the invention relates to a wafer level chip scale packaging structure that uses a specially designed sacrificial layer material to remove the stress generated due to differential thermal expansion coefficients between-the silicon (Si) wafer and the printed circuit board (PCB).

### [0004] 2. Related Art

[0005] The wafer level chip scale packaging is a very important technique for the packaging of wafers and PCB. The main difference from the conventional flip chip in package technique is: as the thermal expansion coefficients between the wafer (Si) and the PCB material is very large, it is likely to have some cracks at the solder ball joints during the reliability test after the wafer is assembled.

[0006] Therefore, one usually includes an underfill step in the technique of flip chip in package to protect the solder ball joint from being damaged. However, the underfill step is very time-consuming and it is very hard to repair once the process is completed. Therefore, the wafer level chip scale packaging is developed to replace the conventional flip chip in package technique. Since this kind of wafer level chip scale packaging techniques has superior electrical performance and lower manufacturing costs than other packaging forms and belongs to re-workable packaging techniques, it will play an important role in the production of future electronics.

[0007] We describe the developed wafer level chip scale packaging techniques in the following paragraphs. FIG. 1 shows the packaging structure disclosed by the Japanese Hitachi, Ltd in Electronic Components and Technology Conference (p.40 to p.46) in 2001. This technique is used in the packaging of Si wafer 10 and organic PCB 20. Its main spirit is to put an extremely soft elastic layer 40 at the bottom of the solder ball 30. The elastic layer 40 releases the stress generated due to the differential thermal expansion coefficients between the Si wafer 10 and the organic PCB 20. However, there are not many choices suitable for the elastic layer 40. It has its technical bottleneck in manufacturing. Therefore, its applications are limited to the packaging of integrated circuits (IC) with a wide pitch (low number of pins).

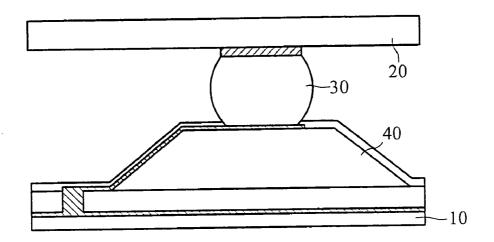

[0008] FIG. 2 shows a chip-scale carrier for semiconductor devices including mounted spring contacts disclosed in the U.S. Pat. No. 6,023,103. The technique uses an elastic metal wire 50 as the channel connecting a Si wafer 10 and an organic PCB 20. Using the elasticity of the metal wire 50,

the stress generated by the differential thermal expansion coefficients between the Si wafer 10 and the organic PCB 20 can be removed. However, the metal wire is formed by bonding. To enhance its strength, one has to employ a special process to strengthen the metal. This inevitably increases the manufacturing cost.

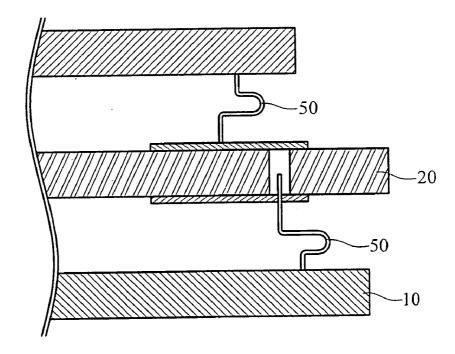

[0009] FIG. 3 shows the Super CSP structure proposed by Fujitsu, Ltd. The technique uses a semiconductor process to grow a copper post 60 of about 100 micrometer high as the electrical contact between the Si wafer 10 and the organic PCB 20. However, using this structure to alleviate the stress is not perfect. Moreover, to grow such a copper post 60 and to protect the copper from being oxidized will increase the cost. Therefore, it is not practical.

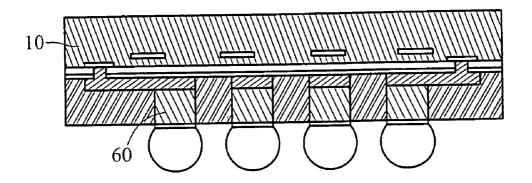

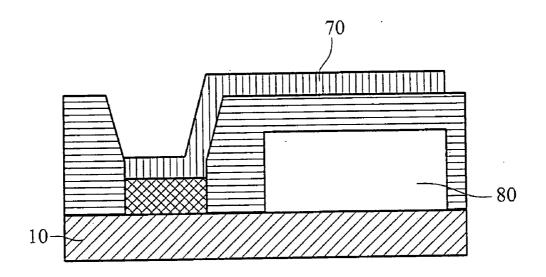

[0010] FIG. 4 shows the wafer level packaging structure disclosed in the U.S. Pat. Application No. 2002/0127768 A1. Its main technical feature is to form a vent hole 80 below a conductive bump 70. Using the vent hole 80 to replace the elastic layer 40 in FIG. 1 can obtain a better elastic effect. However, the vent hole 80 requires a special material and an accompanying fabricating process. Therefore, it has some limitation in mass production.

[0011] In considering the reliability of the products, most packaging techniques can be applied to IC elements with a small pin number (smaller than 100 I/O ports) and area and cannot be used for future IC elements with a large pin number and area.

[0012] Therefore, for an optimized packaging (such as wafer level packaging) of future electronic devices that have a larger pin number, many functions, and a large chip size (such as system of single chip or system packaging), it is imperative to find a method to minimize the manufacturing cost and the packaging volume/surface.

#### SUMMARY OF THE INVENTION

[0013] In view of the foregoing, an objective of the invention is to provide a wafer level packaging structure and the method of fabricating it. The invention uses the usual semiconductor process to form a sacrificial layer below the bump using a normal semiconductor process. The bump is used to connect the signals between the Si wafer and the PCB. The interface between the sacrificial layer and the adjacent layers or the sacrificial layer material is the weakest part in the whole structure. When the stress applied to the bump is overloaded, the interface between the sacrificial layer and the adjacent layers or the sacrificial layer material will crash to remove the stress generated by different thermal expansion coefficients of the Si wafer and the PCB. The sacrificial layer can help avoid the crash occurring to the bump to protect the electrical conduction between the Si wafer and the PCB.

[0014] In one embodiment of the invention, a wafer level packaging structure includes a substrate; an insulating layer formed on the substrate, wherein the insulating layer has a pad formed therein; a sacrificial layer formed on the insulating layer; and a metal wire formed on the insulating layer and the sacrificial layer, wherein one side of the metal wire contacts the pad, and the other side of the metal wire contacts the sacrificial layer.

[0015] According to the embodiment, the wafer level packaging structure further includes a bump formed at a position corresponding to the sacrificial layer on the metal wire.

[0016] According to the embodiment, the wafer level packaging structure further includes an insulating layer formed on the metal wire, wherein the insulating layer has a space formed at a position corresponding to the sacrificial layer; and a bump formed in the space of the insulating layer.

[0017] In one embodiment of the invention, a wafer level packaging structure includes a substrate; an insulating layer formed on the substrate, wherein the insulating layer has a pad formed therein; a first metal wire formed on the pad; a sacrificial layer formed on the first metal wire; a second metal wire formed on the sacrificial layer; and a connecting metal wire formed at one side of the sacrificial layer to connect with the first metal wire and the second metal wire.

[0018] According to the embodiment, the wafer level packaging structure further includes a bump formed at a position corresponding to the sacrificial layer on the second metal wire.

[0019] According to the embodiment, the wafer level packaging structure further includes an insulating layer formed on the second metal wire, wherein the insulating layer has a space formed at a position corresponding to the sacrificial layer; and a bump formed in the space of the insulating layer.

[0020] According to the embodiment, the wafer level packaging structure further includes a first insulating layer formed between the sacrificial layer and the first metal wire; a second insulating layer formed on the second metal wire and the connecting metal wire, wherein the second insulating layer has a space formed at a position corresponding to the sacrificial layer; and a bump formed in the space of the second insulating layer.

[0021] Since the wafer level packaging structure is fabricated using mature semiconductor processes, the structure and method can be used for mass production.

[0022] Further scope of the applicability of the invention will become apparent from the detailed description given hereinafter. However, it should be understood that the detailed description and specific examples, while indicating preferred embodiments of the invention, are given by way of illustration only, since various changes and modifications within the spirit and scope of the invention will become apparent to those skilled in the art from this detailed description.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0023] The accompanying drawings, which are included to provide a further understanding of the invention and constitute a part of this specification, illustrate embodiments of the invention and together with the description serve to explain the principles of the invention. In the drawings:

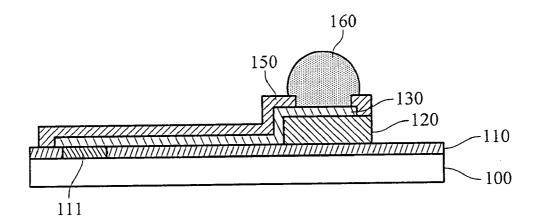

[0024] FIG. 1 is a schematic view of the conventional packaging structure that utilizes an elastic layer to release the stress generated by the differential thermal expansion coefficients between the Si wafer and the PCB;

[0025] FIG. 2 is a schematic view of the conventional wafer level carrier structure for semiconductor devices;

[0026] FIG. 3 is a schematic view of the Super CSP structure proposed by Fujitsu, Ltd;

[0027] FIG. 4 is a schematic view of the wafer level packaging structure disclosed by the U.S. Pat. Application No. 2002/0127768 A1;

[0028] FIG. 5 is a cross-sectional view of the packaging according to the first embodiment;

[0029] FIG. 6 is a cross-sectional view of the packaging according to the second embodiment;

[0030] FIG. 7A to 7D illustrates the fabricating process for the first embodiment of the invention;

[0031] FIGS. 7E and 7F illustrates the fabricating process for the second embodiment of the invention;

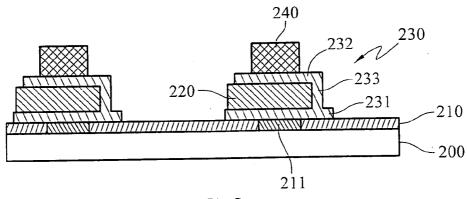

[0032] FIG. 8 illustrating the packaging structure according to the third embodiment of the invention;

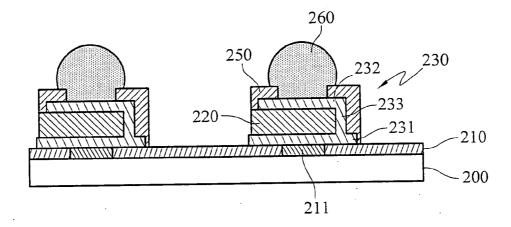

[0033] FIG. 9 illustrating the packaging structure according to the forth embodiment of the invention;

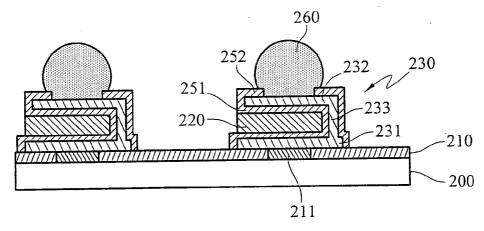

[0034] FIG. 10 illustrating the packaging structure according to the fifth embodiment of the invention;

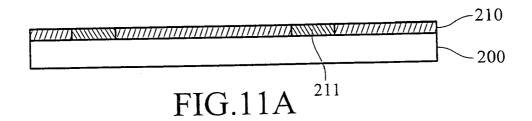

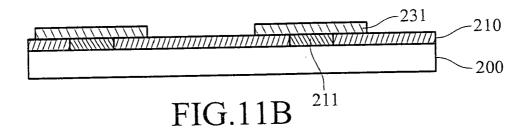

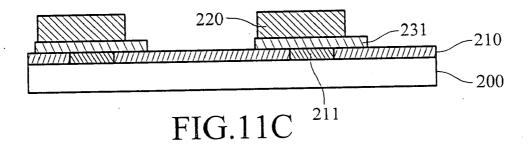

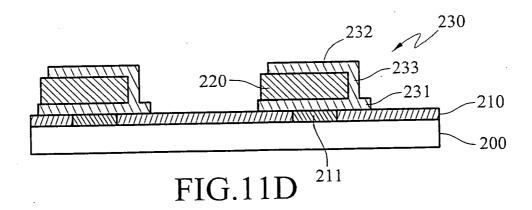

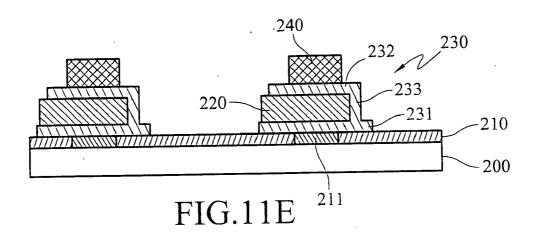

[0035] FIG. 11A to 11E illustrates the fabricating process for the third embodiment of the invention;

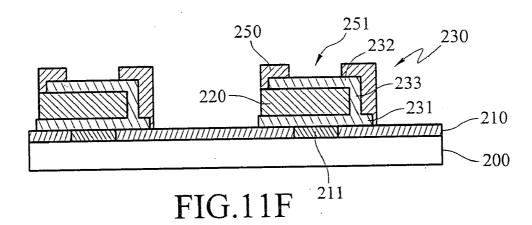

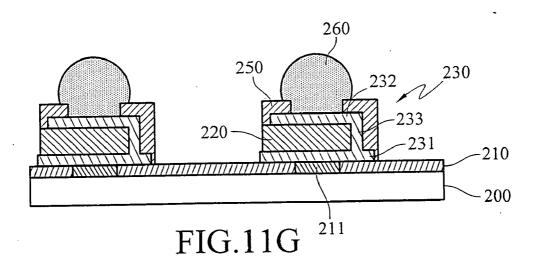

[0036] FIGS. 11F and 11G illustrating the fabricating process for the forth embodiment of the invention;

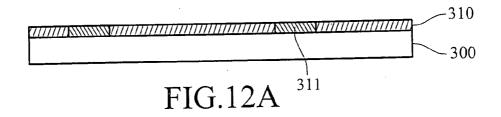

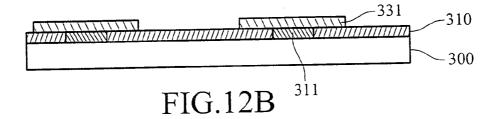

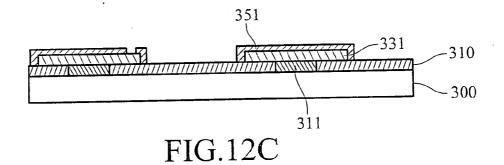

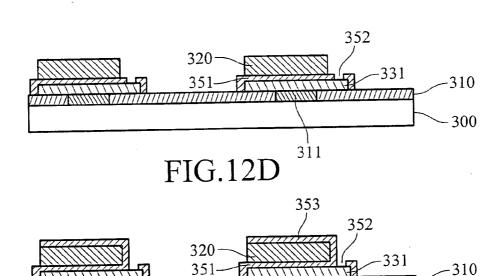

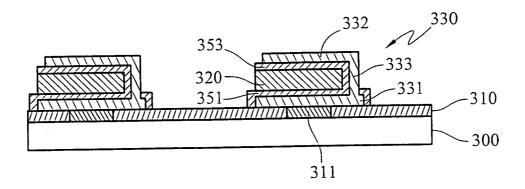

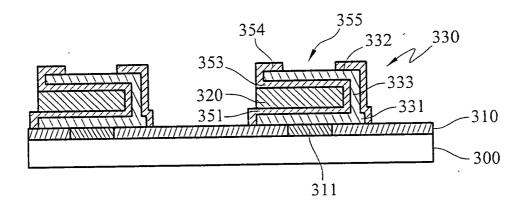

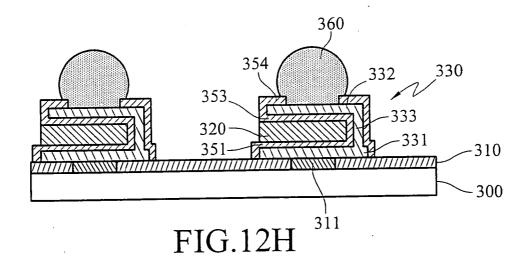

[0037] FIGS. 12A to 12H illustrating the manufacturing processes of the fifth embodiment;

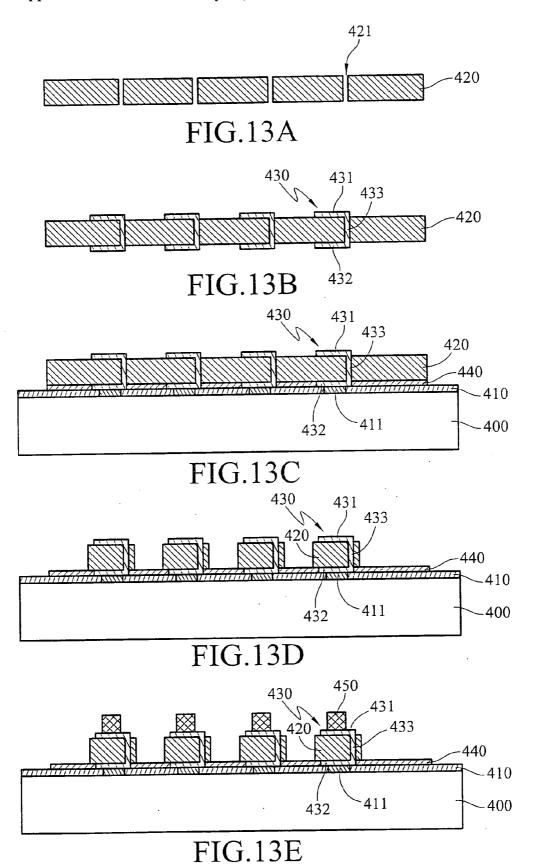

[0038] FIGS. 13A to 13E illustrating another manufacturing process of the tnird embodiment;

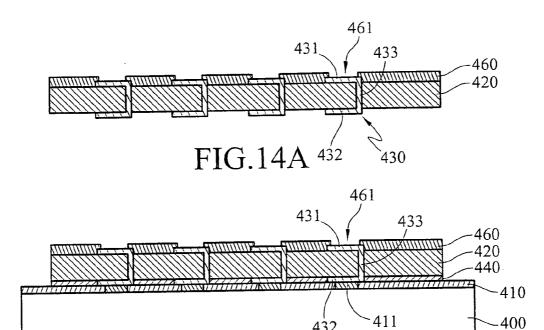

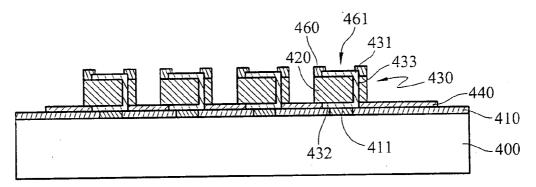

[0039] FIGS. 14A to 14D illustrating another manufacturing process of the fourth embodiment;

[0040] FIG. 15A to 15D illustrating another manufacturing process of the fourth embodiment; and

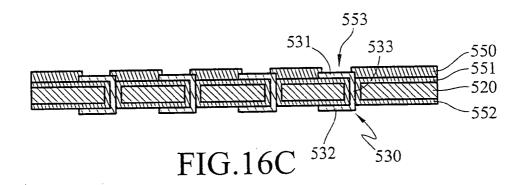

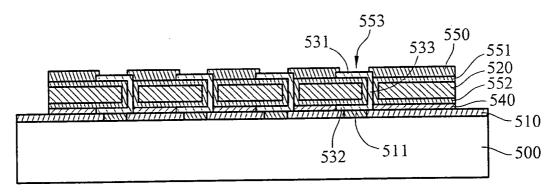

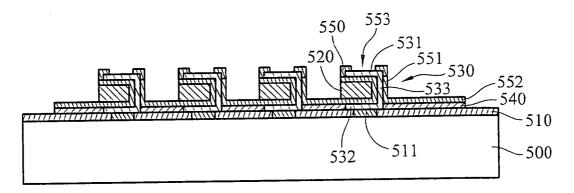

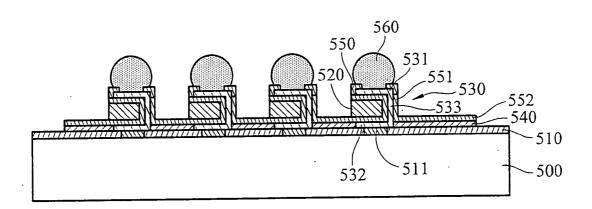

[0041] FIG. 16A to 16F illustrating another manufacturing processes of the fifth embodiment.

### DETAILED DESCRIPTION OF THE INVENTION

[0042] Reference will now be made in greater detail to a preferred embodiment of the invention, an example of which is illustrated in the accompanying drawings. Wherever possible, the same reference numerals are used throughout the drawings and the description to refer to the same or like parts. Reference in the specification to "one embodiment" or "an embodiment" means that a particular feature, structure, or characteristic described in connection with the embodiment is included in at least one embodiment of the invention. The appearances of the phrase "in one embodiment" in various places in the specification are not necessarily all referring to the same embodiment.

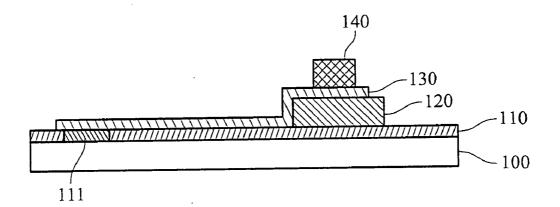

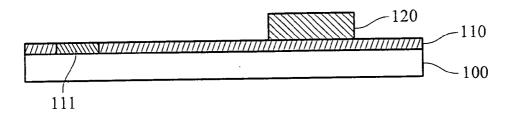

[0043] Refer to FIG. 5 illustrating the cross-sectional views of the packaging structure according to the first embodiment of the invention.

[0044] The packing structure includes a substrate 100, an insulating layer 110, a sacrificial layer 120 and a metal wire 130. A bump 140 formed on the metal wire 130 is used as a metal contact for electrical connection between the substrate 100 and a PCB (not show).

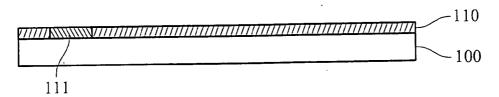

[0045] In an exemplary embodiment, the substrate 100 is a Si wafer. After forming the required circuit layout on the substrate 100 using semiconductor processes, external signals can enter through the pads 111 on the surface of the substrate 100 to control the operations of the substrate 100. In the embodiment, the metal wire 130 directly contacts the sacrificial layer 120. An insulating layer is not necessary to be provided between the sacrificial layer 120 and the metal wire 130. In another exemplary embodiment, the substrate 100 is a printed circuit board, or a flexible printed circuit board

[0046] The sacrificial layer 120 formed between the insulating layer 110 and the metal wire 130. The position is right below the bump 140. The metal wire 130 is pulled from the pads 111 to above the sacrificial layer 120 using the circuit RDL technique. The bump 140 is formed at a position on the metal wire 130 above the sacrificial layer 120 to electrically connect the pad 111. The substrate 100 and the PCB thereabove are thus in electrical communications.

[0047] The connection part of the sacrificial layer 120 and the insulating layer 110 or the interface between the sacrificial layer 120 and the metal wire 130 is weakest in the interfacial adhesive force or in the material of the structure. Therefore, when the stress on the bump 140 is too large, the connection part between the insulating layer 110 and the sacrificial layer 120 or the connection part between the sacrificial layer 120 and the metal wire 130 will break to release the stress between the substrate 100 and the PCB 130 while still keeping the electrical connection between the pads 111 on the substrate 90 and the bump 140. In another embodiment, the material of the sacrificial layer 120 may be adequately selected such that the sacrificial layer 120 may break to release the stress.

[0048] The material of the sacrificial layer 120 can be metals, epoxy, organic polymers, inorganic oxides, etc, as long as the interfacial adhesive force with the substrate 100 or the sacrificial layer material has the weakest mechanical strength in the complete structure.

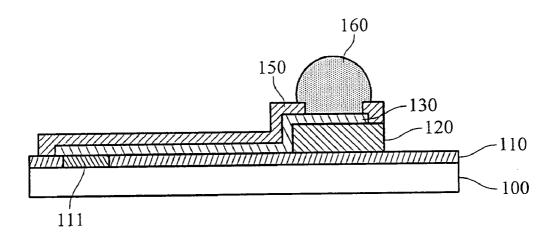

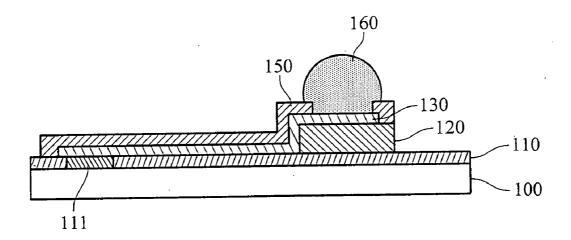

[0049] Refer to FIG. 6 illustrating the cross-sectional views of the packaging structure according to the second embodiment of the invention. The elements having the same/similar reference numbers as/with those in FIG. 5 operates the same/similar function as/with those in FIG. 5. In this embodiment, a solder ball 160 used for the metal contact between the substrate 100 and the printed circuit board is formed on the metal wire 130. A passivation layer 150 is formed above the metal wire 130 to protect the substrate 100 and the packaging structure from being damaged. In an exemplary embodiment, the substrate 100 is a Si wafer. In another exemplary embodiment, the substrate 100 is a printed circuit board, or a flexible printed circuit board. It is appreciated that the metal contact may be the form of a solder ball and a bump by the embodiments respectively illustrated in FIGS. 5 and 6. Although FIG. 6 uses a solder ball as a metal contact, the solder ball in FIG. 6 and hereinafter is substantially a form of a bump.

[0050] FIG. 7A to 7D illustrates the fabricating process for the first embodiment of the invention. As shown in FIG. 7A, an insulating layer 110 and a pad 111 are formed on the substrate 100. In one embodiment, the insulating layer 110 is formed first and then a portion is etched to deposit material to form the pad 111. In another embodiment, the

pad 111 is formed first and then the insulting layer 110 is deposited on the substrate 100. As shown in FIG. 7B, a sacrificial layer 120 is formed at a position on the substrate 100 corresponding to the position of the bump 140 to be formed.

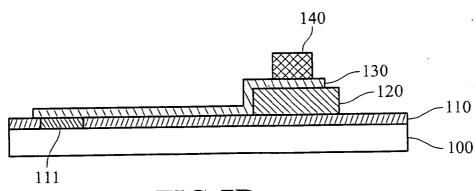

[0051] As shown in FIG. 7C, a metal wire 130 is formed on the substrate 100 and the sacrificial layer 120. One end of the metal wire 130 is connected to the pad 111 and the other end of the metal wire 130 is connected to the sacrificial layer 120 and corresponds to the position of the bump 140.

[0052] As shown in FIG. 7D, a bump 140 is formed at the position on the metal wire 130 corresponds to the sacrificial layer 120.

[0053] Refer to FIGS. 7E and 7F illustrates the fabricating process for the second embodiment of the invention. The preceding processes are the same as that of the first embodiment. A passivation layer 150 is formed above the metal wire 130. An opening 151 is formed at a position corresponding to the sacrificial layer 120 in the passivation layer 150. A solder ball 160 for metal contact is formed in the space 151 to contact with the metal wire 130.

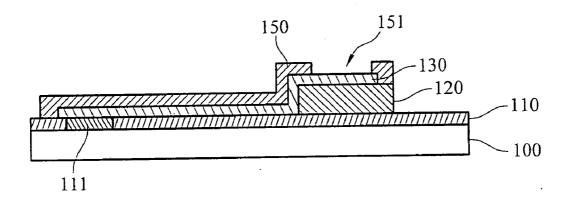

[0054] Refer to FIG. 8 illustrating the packaging structure according to the third embodiment of the invention. The metal wire in this embodiment is different from that in the aforementioned embodiments.

[0055] The package structure includes a substrate 200, an insulating layer 210, a sacrificial layer 220, and a metal wire 230. A bump 240 formed on the metal wire 230 is used as a metal contact for electrical connection between the substrate 200 and a PCB (not show). In an exemplary embodiment, the substrate 200 is a Si wafer. In another exemplary embodiment, the substrate 200 is a printed circuit board, or a flexible printed circuit board.

[0056] In the embodiment of FIG. 8, the similar structure has similar/same functions to/as the structure of the embodiment of FIG. 5 or FIG. 6. However, the metal wire 230 is different. In this embodiment, the metal wire 230 includes a first metal wire 231, a second metal wire 232 and a connecting metal wire 233 connecting the first metal 231 and the second metal wire 232.

[0057] The first metal wire 231 formed on the pad 211. The sacrificial layer 220 is formed on the first metal wire 231. The connecting metal 233 is formed adjacent to one side of the sacrificial layer 220. The second metal wire 232 is formed on the sacrificial layer 220. The bump 240 is formed on the second metal wire 232.

[0058] Refer to FIG. 9 illustrating the packaging structure according to the forth embodiment of the invention.

[0059] In the embodiment of FIG. 9, the similar structure has similar/same functions to/as the structure of the embodiment of FIG. 8. A passivation layer 250 having a space (will be illustrated in the fabricating process as follows) is formed on the second metal wire 232.

[0060] In this embodiment, a solder ball 260 used for the metal contact between the substrate 200 and the printed circuit board is formed on the second metal wire 232. The passivation layer 250 is used as for passivation to protect the substrate 200 and the packaging structure from being damaged.

[0061] Refer to FIG. 10 illustrating the packaging structure according to the fifth embodiment of the invention. In the embodiment of FIG. 10, the similar structure has similar/same functions to/as the structure of the embodiment of FIG. 8.

[0062] A first insulating layer 251 is formed between the sacrificial layer 220 and the metal wire 230. A second insulating layer 252 is formed on the second metal wire 232 and the connecting metal wire 233. The second insulating layer 252 has a space formed at a position corresponding to the sacrificial layer 220. The solder ball 260 is formed in the space of the second insulating layer 252.

[0063] The structure in the left portion of the figures is the same as or similar to that in the right portion of the drawing. Only one is illustrated and explained.

[0064] FIG. 11A to 11D illustrates the fabricating process for the third embodiment of the invention. As shown in FIG. 11A, an insulating layer 210 and a plurality of pads 211 (only one pad is given with reference number) are formed on the substrate 200. In one embodiment, the insulating layer 210 is formed first and then a portion is etched to deposit material to form the pads 211. In another embodiment, the pads 211 are formed first and then the insulting layer 210 is deposited on the substrate 200. As shown in FIG. 11B, a plurality of first metal wires 231 are formed on the corresponding pad 211. Then, as shown in FIG. 11C, a plurality of sacrificial layers 220 are formed at the corresponding first metal wire 231.

[0065] In FIG. 11D, a second metal wire 232 and a connecting metal wire 233 are then formed. Refer to FIG. 11E, a plurality of bumps 240 are formed on the second metal wires 232.

[0066] Refer to FIGS. 11F and 11G illustrating the fabricating process for the forth embodiment of the invention. The preceding processes of the forth embodiment are the same as those of the third embodiment and are illustrated in FIGS. 11A to 11G.

[0067] A passivation layer 250 is formed above the second metal wire 232. A space 251 is formed at a position corresponding to the sacrificial layer 220 in the passivation layer 250. A solder ball 260 is formed in the space 251 to contact with the second metal wire 232.

[0068] Refer to FIG. 12A to 12H illustrating the manufacturing processes of the fifth embodiment. The preceding processes shown in FIG. 12A and 12B are the same as the processes of the aforementioned processes in FIGS. 11A and 11B.

[0069] In FIG. 12C, a first insulating layer 351 is formed on the first metal wire 331.

[0070] Refer to FIG. 12D. A sacrificial layer 320 is then formed on the first insulating layer 351. Refer to FIG. 12E, a second insulating layer 353 is then deposited on the sacrificial layer 320. A space 352 is also formed in the first insulating layer 351.

[0071] Refer to FIG. 12F to 12H. A second metal wire 332 and a connecting metal wire 333 are formed. A third insulating layer 354 is then formed on the second metal wire 332 and the connecting metal wire 333. A space 355 is

formed in the third insulating layer 354. A solder ball 360 is formed in the space 355 to contact with the second metal wire 332.

[0072] Refer to FIG. 13A to 13D illustrating another manufacturing process of the third embodiment.

[0073] A sacrificial layer 420 with a plurality of through holes 421 is provided, as shown in FIG. 13A. Metal are then deposited in the through holes 421 for formed the connecting metal wire 433 as mentioned above. A plurality of first metal wires 431 and a plurality of second metal wires 432 are formed on the two surfaces of the sacrificial layer 420. Each of the first metal wires 431 and each of the second metal wires 432 connect with one connecting metal wire 433 such that a metal wire for electrical connection between a substrate and a circuit board is formed, as shown in FIG. 13R

[0074] In FIG. 13C, a substrate 400 having an insulating layer 410 formed thereon is provided. In the insulating layer 410, a plurality of pads 411 are formed. The processes for forming the pads are the same as those aforementioned. The sacrificial layer 420 formed with metal wires 430 are bonded together by a bonding layer 440. An anisotropic conductive film (ACF) or a non-conductive film (NCF) may be used for the bonding layer 440.

[0075] The bonded structures are then insulated by etching to form individual package structures, as illustrated in FIG. 13D. A plurality of bumps 450 for metal contact are formed on the corresponding metal wires, as illustrated in FIG. 13E.

[0076] In another embodiment, the plurality of bumps 450 may be formed on the corresponding metal wires before the bonded structures are insulated.

[0077] Refer to FIG. 14A to 14D illustrating another manufacturing process of the fourth embodiment.

[0078] In FIG. 14A, a sacrificial layer 420 formed with a plurality of metal wires 430 is provided. In one surface of the sacrificial layer 420, an insulating layer 460 is formed. A plurality of spaces 461 are also formed in the insulating layer 460.

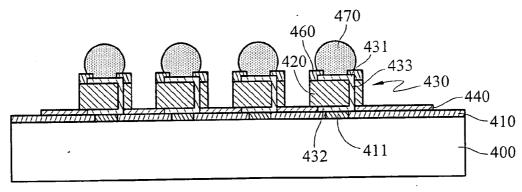

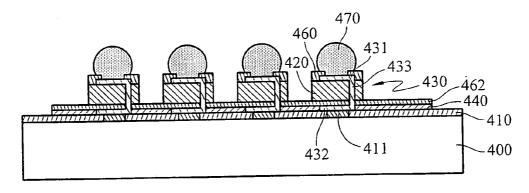

[0079] In FIG. 14B, the sacrificial layer 420 formed with metal wires 430 are bonded together by a bonding layer 440. An anisotropic conductive film (ACF) or a non-conductive film (NCF) may be used for the bonding layer 440. in FIG. 14C, the bonded structures are then insulated to form individual package structures. A plurality of solder balls 470 for metal contact are formed on the corresponding metal wires, as illustrated in FIG. 14D.

[0080] In another embodiment, the plurality of solder balls 470 may be formed on the corresponding metal wires before the bonded structures are insulated.

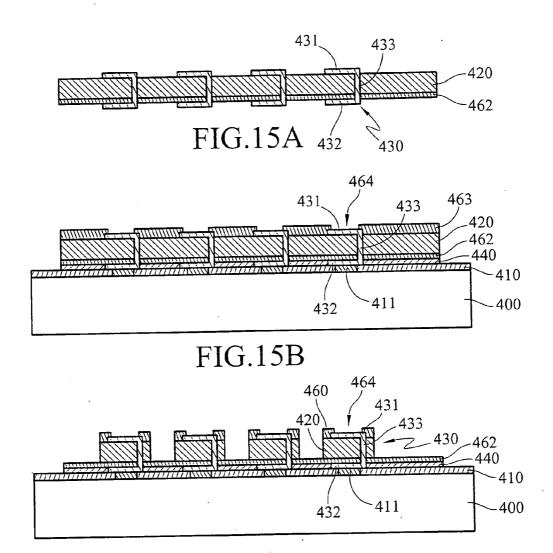

[0081] Refer to FIG. 15A to 15D illustrating another manufacturing process of the fourth embodiment. The processes in this embodiment are very similar to those in the embodiment in FIG. 14.

[0082] In FIG. 15A, a first insulating layer 462 is formed on one surface of the sacrificial layer 420.A pluralty of metal wires 430 is then formed.

[0083] In FIG. 15B, the sacrificial layer 420 formed with metal wires 430 are bonded together by a bonding layer 440.

An anisotropic conductive film (ACF) or a non-conductive film(NCF) may be used for the bonding layer **440**. The bonding layer **440** bonded the first insulating layer **462** and the insulating layer **410** formed on the substrate **400**. A second insulating layer **463** is then formed the other surface of the sacrificial layer **420**. A pluralty of spaces **464** are also formed in the second insulating layer **463**.

[0084] In FIG. 15C, the bonded structures are then insulated to form individual package structures. A plurality of solder balls 470 for metal contact are formed on the corresponding metal wires, as illustrated in FIG. 15D.

[0085] In another embodiment, the plurality of solder balls 470 may be formed on the corresponding metal wires before the bonded structures are insulated.

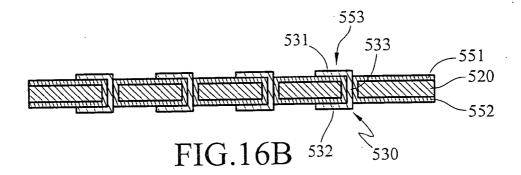

[0086] Refer to FIG. 16A to 16F illustrating another manufacturing processes of the fifth embodiment.

[0087] In FIG. 16A, a sacrificial layer 520 having a first insulating layer 551 and a second insulating 552 is provided. Some portions of the sacrificial layer 520 are also filled with insulating materials. A sacrificial layer 520 with a plurality of through holes (not shown) is provided. Insulated material is then deposited in the through holes, then the first insulating layer 551 and the second insulating 552 are formed on the two surfaces of the sacrificial layer 520.

[0088] The portions filled with insulating materials are etched to form a plurality of through holes such that connecting metal wires 533 are formed therein, as shown in FIG. 16B. A plurality of first metal wires 531 and a plurality of second metal wires 532 are formed on the surfaces of the first insulating layer 551 and the second insulating layer 552 respectively. Each of the first metal wires 531 and each of the second metal wires 532 connect with one connecting metal wire 533 such that a metal wire for electrical connection between a substrate and a circuit board is formed, as shown in FIG. 16B.

[0089] In FIG. 16C, one of the two insulating layers 551, 552 is deposited with a third insulating layer 550 to form a plurality of spaces 553. The other insulating layers that do not have spaces formed thereon are boned with the substrate 500 having a insulating layer 510 formed thereon. The insulating layer 510 has a plurality of pads 511 and each of the pad 511 connects to a corresponding metal wire, as shown in FIG. 16D.

[0090] In FIG. 16E, the bonded structures are then insulated to form individual package structures A plurality of solder balls 560 for metal contact are formed on the corresponding metal wires, as illustrated in FIG. 16F.

[0091] The invention uses the usual semiconductor process to form a sacrificial layer below the bump using a normal semiconductor process. The interface between the sacrificial layer and the adjacent layers or the sacrificial layer material is the weakest part in the whole structure. When the stress applied to the bump is overloaded, the interface between the sacrificial layer and the PCB or the sacrificial layer material will crash to remove the stress generated by different thermal expansion coefficients of the Si wafer and the PCB. The sacrificial layer can help avoid the crash occurring to the bump to protect the electrical conduction between the Si wafer and the PCB.

[0092] Further, when the substrate in the above-mentioned embodiments is a PCB or a flexible PCB, the packaging structure may protect the juncture between the bump and the PCB which contacts with the bump. When the substrate in the above-mentioned embodiments bonds with a PCB or a flexible PCB, the packaging structure may protect the juncture between the substrate and the PCB or the flexible PCB

[0093] The invention being thus described, it will be obvious that the same may be varied in many ways. Such variations are not to be regarded as a departure from the spirit and scope of the invention, and all such modifications as would be obvious to one skilled in the art are intended to be included within the scope of the following claims.

What is claimed is:

- 1. A packaging structure comprising:

- a substrate;

- an insulating layer formed on the substrate, wherein the insulating layer has a pad formed therein;

- a sacrificial layer formed on the insulating layer; and

- a metal wire formed on the insulating layer and the sacrificial layer, wherein one end of the metal wire contacts the pad, and the other end of the metal wire contacts the sacrificial layer.

- 2. The packaging structure of claim 1 further comprises a bump formed at a position corresponding to the sacrificial layer on the metal wire.

- 3. The packaging structure of claim 1 further comprises:

- a passivation layer formed on the metal wire, wherein the insulating layer has a space formed at a position corresponding to the sacrificial layer; and

- a bump formed in the space of the passivation layer.

- **4**. The packaging structure of claim 1, wherein the material of the sacrificial layer is selected from the group consisting of metals, epoxy, organic polymers, and inorganic oxides.

- 5. A packaging structure comprising:

- a substrate;

- an insulating layer formed on the substrate, wherein the insulating layer has a pad formed therein;

- a first metal wire formed on the pad;

- a sacrificial layer formed on the first metal wire;

- a second metal wire formed on the sacrificial layer; and

- a connecting metal wire formed at one side of the sacrificial layer to connect with the first metal wire and the second metal wire.

- **6**. The packaging structure of claim 5 further comprises a bump formed at a position corresponding to the sacrificial layer on the second metal wire.

- 7. The packaging structure of claim 5 further comprises:

- a passivation layer formed on the second metal wire, wherein the insulating layer has a space formed at a position corresponding to the sacrificial layer; and

- a bump formed in the space of the insulating layer.

- **8**. The packaging structure of claim 5 further comprises:

- a first insulating layer formed between the sacrificial layer and the first metal wire;

- a second insulating layer formed on the second metal wire and the connecting metal wire, wherein the second insulating layer has a space formed at a position corresponding to the sacrificial layer; and

- a bump formed in the space of the second insulating layer.

- **9**. The packaging structure of claim 5, wherein the material of the sacrificial layer is selected from the group consisting of metals, epoxy, organic polymers, and inorganic oxides.

- 10. A method for fabricating packaging structure comprising steps of:

providing a substrate;

forming an insulating layer having a pad therein on the substrate;

forming a sacrificial layer on the insulating layer; and

- forming a metal wire on the insulating layer and the sacrificial layer, wherein one end of the metal wire contacts the pad, and the other end of the metal wire contacts the sacrificial layer.

- 11. The method of claim 10 further comprises a step of forming a bump at a position corresponding to the sacrificial layer on the metal wire.

- 12. The method of claim 10 further comprises steps of:

forming a passivation layer on the metal wire, wherein the passivation layer has a space formed at a position corresponding to the sacrificial layer; and

forming a bump in the space of the insulating layer.

13. A method for manufacture a packaging structure comprising:

providing a substrate;

forming an insulating layer on the substrate, wherein the insulating layer has a pad formed therein;

forming a first metal wire on the pad;

forming a sacrificial layer on the first metal wire; and

forming a second metal wire and a connecting metal wire connectecing with the second metal wire.

- **14**. The method of claim 13 further comprises a step of forming a bump at a position corresponding to the sacrificial layer on the second metal wire.

- 15. The method of claim 13 further comprises steps of:

forming a passivation layer on the second metal wire, wherein the passivation layer has a space formed at a position corresponding to the sacrificial layer; and

forming a bump in the space of the insulating layer.

**16**. A method for fabricating packaging structure comprising steps of:

providing a substrate:

forming an first insulating layer on the substrate, wherein the insulating layer has a pad formed therein;

forming a first metal wire on the pad;

forming a first insulating layer;

forming a sacrificial layer on the first insulating layer;

forming a second insulating layer on the sacrificial layer having a space on the first metal wire; and

- forming a second metal wire and a connecting metal wire connecting with the second metal wire.

- forming a third insulating layer having a space on the second metal wire and the connecting metal wire; and

- forming a bump in the space of the third insulating layer to contact with the second metal wire.

- 17. A method for fabricating packaging structure comprising steps of:

- providing a sacrificial layer with a plurality of through holes:

- forming a plurality of connecting metal wires in the through holes;

- forming a plurality of first metal wires and a plurality of second metal wires on the two surfaces of the sacrificial layer, wherein each of the first metal wires and each of the second metal wires connect with each of the connecting metal wires respectively;

- providing a substrate, wherein the substrate comprises an insulating layer formed thereon, a plurality of pads are formed in the insulating layer;

- bonding the insulating layer and the metal wires by a bonding layer;

- etching the insulating layer and metal wires which are bonded by the bonding layer to form individual package structures; and

- forming a plurality of bumps for metal contact on the corresponding metal wires.

- **18**. The method of claim 17, wherein the bonding layer is an anisotropic conductive film (ACF) or a non-conductive film (NCF).

- 19. A method for fabricating packaging structure comprising steps of:

- providing a sacrificial layer with a plurality of through holes:

- forming a plurality of connecting metal wires in the through holes;

- forming a plurality of first metal wires and a plurality of second metal wires on the two surfaces of the sacrificial layer, wherein each of the first metal wires and each of the second metal wires connect with each of the connecting metal wires respectively;

- forming a insulating layer having a plurality of spaces on one surface of the sacrificial layer

- providing a substrate, wherein the substrate comprises an insulating layer formed thereon, a plurality of pads are formed in the insulating layer;

- bonding the other surface of the sacrificial layer formed with metal wires and the substrate formed with the insulating layer by a bonding layer;

- etching the sacrificial layer and substrate which are bonded by the bonding layer to form individual package structures; and

- forming a plurality of bumps for metal contact on the corresponding metal wires.

- **20**. The method of claim 19, wherein the bonding layer is an anisotropic conductive film (ACF) or a non-conductive film (NCF).

- 21. A method for fabricating packaging structure comprising steps of:

providing a sacrificial layer;

forming a first insulating layer on one surface of the sacrificial layer;

forming a plurality of through holes in the sacrificial layer:

forming a plurality of connecting metal wires in the through holes;

forming a plurality of first metal wires and a plurality of second metal wires on the two surfaces of the sacrificial layer, wherein each of the first metal wires and each of the second metal wires connect with each of the connecting metal wires respectively;

providing a substrate, wherein the substrate comprises an insulating layer formed thereon, a plurality of pads are formed in the insulating layer;

bonding the first insulating layer and the substrate formed with the insulating layer by a bonding layer;

forming a second insulating layer having a plurality of spaces on the other surface of the sacrificial layer;

etching the bonded the sacrificial layer and substrate which are bonded by the bonding layer to form individual package structures; and

forming a plurality of bumps for metal contact on the corresponding metal wires.

**22.** The method of claim 20, wherein the bonding layer is an anisotropic conductive film (ACF) or a non-conductive film (NCF).

23. A method for fabricating packaging structure comprising steps of:

providing a sacrificial layer with a plurality of through holes:

forming a first insulating layer and a second insulating layer on the two surfaces of the sacrificial layer, wherein the plurality of through holes are filled with insulating material;

etching portions filled with insulating materials to form a plurality of through holes such that a plurality of connecting metal wires are formed therein;

forming a plurality of first metal wires and a plurality of second metal wires on the surfaces of the first insulating layer and the second insulating layer respectively, wherein each of the first metal wires and each of the second metal wires connect with one connecting metal wire respectively;

forming a third insulating layer having a plurality of spaces on one of the first and second insulating layers;

providing a substrate, wherein the substrate comprises an insulating layer formed thereon, a plurality of pads are formed in the insulating layer;

bonding the substrate and the sacrificial layer;

etching the bonded the sacrificial layer and substrate which are bonded by the bonding layer to form individual package structures; and

forming a plurality of bumps for metal contact on the corresponding metal wires.

\* \* \* \* \*