(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년08월05일

(11) 등록번호 10-1293381

(24) 등록일자 2013년07월30일

- (51) 국제특허분류(Int. C1.)

*G01R 31/26* (2006.01) *G01R 1/073* (2006.01)

- (21) 출원번호 10-2007-7018038

- (22) 출원일자(국제) 2005년12월15일

심사청구일자 2010년12월15일

- (85) 번역문제출일자 2007년08월06일

- (65) 공개번호 10-2007-0097095

- (43) 공개일자 2007년10월02일

- (86) 국제출원번호 PCT/US2005/045583

- (87) 국제공개번호 WO 2006/073737

국제공개일자 2006년07월13일

- (30) 우선권주장

11/031,504 2005년01월07일 미국(US)

- (56) 선행기술조사문현

JP2001296335 A\*

- \*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 23 항

심사관 : 정종한

(54) 발명의 명칭 전자 장치를 테스트하기 위한 시스템의 동작 주파수를 증가시키는 방법 및 장치

### (57) 요 약

테스트 시스템은 테스트될 전자 장치의 입력 단자와 접촉하는 프로브에서 종단되는 통신 채널을 포함한다. 저항기는 프로브 근처의 통신 채널과 접지 사이에 접속된다. 저항기(resistor)는 단자의 입력 저항을 감소시켜, 입력 단자의 상승 및 하강 시간을 감소시킨다. 채널은, 각 경로가 테스트될 전자 장치 상의 단자와 접촉하기 위한 프로브에서 종단되는 다중 경로를 갖는 분기에서 종단될 수 있다. 아이솔레이션 저항기들은 하나의 입력 단자에서의 결함이 다른 입력 단자들로 전달되는 것을 방지하기 위해 분기 내에 포함된다. 분로 저항기(shunt resistor)는 각 분기 내에 제공되고, 이는 단자의 입력 저항을 감소시켜, 입력 단자의 상승 및 하강 시간을 감소시킨다. 분로 저항기의 크기는 또한 채널로 되돌아오는 신호 반사를 감소, 최소화, 또는 제거하도록 조정된다.

대 표 도 - 도4

## 특허청구의 범위

### 청구항 1

테스터(tester) 및 테스트되는 전자 장치 사이에 테스트 신호를 인터페이싱(interfacing)하는 장치에 있어서, 프로브 보드, 인터포저(interposer) 및 프로브 기판을 포함하는 프로브 카드 어셈블리;

상기 프로브 카드 어셈블리 상에 배치되고, 상기 테스터로부터의 통신 채널과 전기적으로 접속하도록 구성되는 복수의 단자(terminal)들;

상기 프로브 카드 어셈블리 상에 배치되고, 상기 전자 장치의 단자들과 접촉하도록 구성되는 복수의 프로브(probe);

상기 복수의 단자들 중 일부 단자들을 상기 프로브들 중 일부 프로브들과 접속시키는, 복수의 전기 전도성 경로; 및

상기 프로브 카드 어셈블리 상에 배치된 복수의 분로 저항기(shunt resistor)를 포함하며, 상기 분로 저항기들은 각각 상기 전도성 경로들 중 하나에 전기적으로 접속된 것이고,

상기 경로들 중 일부 경로들은 복수의 분기(branch)를 포함하며, 상기 경로들 중 하나는 상기 단자들 중 하나를 상기 복수의 프로브와 전기적으로 접속시키는 것이고,

상기 분기들 내에 배치된 복수의 아이솔레이션 저항기(isolation resistor)를 더 포함하며, 상기 아이솔레이션 저항기들은 각각 상기 분기들 중 하나의 분기 상의 프로브를 상기 분기들 중 다른 분기 상의 프로브로부터 전기적으로 분리시키도록 구성되는 것이며,

상기 분로 저항기들은 각각 아이솔레이션 저항기 및 상기 분기 내의 프로브 사이에 있는 상기 분기들 중 하나의 분기로부터 접지(ground)로 전기적 경로(electrical path)를 제공하는 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 2

제1항에 있어서, 상기 분로 저항기들은 박막 저항기(thin film resistor)인 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 3

제1항에 있어서, 상기 프로브 카드 어셈블리는 제1 기판을 포함하고 상기 프로브들이 상기 제1 기판 상에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 4

제3항에 있어서, 상기 분로 저항기들은 상기 제1 기판 상에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 5

제4항에 있어서, 상기 분로 저항기들은 박막 저항기들인 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 6

제4항에 있어서, 상기 프로브들 및 상기 분로 저항기들은 상기 제1 기판의 제1 표면 상에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 7

제4항에 있어서, 상기 분로 저항기들은 상기 제1 기판의 범위 내에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

### 청구항 8

제3항에 있어서, 상기 프로브 보드, 인터포저 및 프로브 기판을 포함하는 프로브 카드 어셈블리는 제2 기판을 더 포함하고 상기 단자들이 상기 제2 기판 상에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 9

제1항에 있어서, 상기 분로 저항기들을 차단하도록 구성되는 스위치를 더 포함하는, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 10

제9항에 있어서, 상기 스위치는 상기 프로브 카드 어셈블리 상에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 11

삭제

#### 청구항 12

삭제

#### 청구항 13

삭제

#### 청구항 14

삭제

#### 청구항 15

삭제

#### 청구항 16

제4항에 있어서, 상기 아이솔레이션 저항기들은 상기 제1 기판 상에 배치되는 것인, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 17

삭제

#### 청구항 18

제4항에 있어서, 상기 분로 저항기들은 박막 저항기들이고, 상기 아이솔레이션 저항기들은 상기 제1 기판 상에 배치된 박막 저항기들인 것인, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 19

삭제

#### 청구항 20

제1항에 있어서, 상기 분로 저항기는 각각 상기 전자 장치의 상기 단자를 중 하나의 단자의 입력 저항을 감소시키기 위해, 상기 전도성 경로들 중 하나의 경로에 접속되는 것인, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 21

제1항에 있어서, 상기 각각의 분로 저항기는 상기 전도성 경로들 중 하나의 경로로부터 접지로 접속되는 것인, 테스트 신호를 인터페이싱하는 장치.

#### 청구항 22

전자 장치를 테스트하는데 사용되는 장치로서,

테스터와 상기 전자 장치 사이의 통신 채널의 일부를 각각 포함하는 복수의 전기적 경로로서, 상기 경로들 중 일부의 경로들은 상기 전자 장치의 입력 단자들과 접촉하기 위한 프로브를 포함하는 것인 상기 복수의 전기적 경로; 및

상기 입력 단자들에서 상기 전자 장치의 스위칭 속도를 증가시키기 위해 상기 경로들 중 일부의 경로들에 접속되는 분로 저항기(shunt resistor)를 포함하고,

상기 경로들 중 일부 경로들은 복수의 분기(branch)를 포함하며, 상기 경로들 중 하나는 상기 입력 단자들 중 하나를 상기 복수의 프로브와 전기적으로 접속시키는 것이고,

상기 분기들 내에 배치된 복수의 아이솔레이션 저항기(isolation resistor)를 더 포함하며, 상기 아이솔레이션 저항기들은 각각 상기 분기들 중 하나의 분기 상의 프로브를 상기 분기들 중 다른 분기 상의 프로브로부터 전기적으로 분리시키도록 구성되는 것이며,

상기 분로 저항기들은 각각 아이솔레이션 저항기 및 상기 분기 내의 프로브 사이에 있는 상기 분기들 중 하나의 분기로부터 접지(ground)로 전기적 경로(electrical path)를 제공하는 것인, 전자 장치를 테스트하는데 사용되는 장치.

### 청구항 23

제22항에 있어서, 상기 분로 저항기는 상기 입력 단자들의 상승 시간(rise time)을 감소시키는 것인, 전자 장치를 테스트하는데 사용되는 장치.

### 청구항 24

제22항에 있어서, 상기 장치는 반도체 다이들을 테스트하기 위한 프로브 카드 조립체를 포함하는 것인, 전자 장치를 테스트하는데 사용되는 장치.

### 청구항 25

제24항에 있어서, 상기 프로브들이 부착되는 기판을 더 포함하며, 상기 분로 저항기는 상기 기판 상에 배치되는 것인, 전자 장치를 테스트하는데 사용되는 장치.

### 청구항 26

프로브들에서 종단되는 복수의 드라이브 채널을 포함하는 테스트 시스템에서 사용하기 위한 방법으로서, 복수의 입력 단자들을 포함하는 전자 장치를 테스트하는 방법에 있어서,

상기 프로브들을 상기 입력 단자들과 접촉하도록 하는 단계;

분로 저항기들을 상기 드라이브 채널들에 접속시키는 단계; 및

상기 전자 장치에 대해 상기 드라이브 채널들을 통한 기능 테스트를 수행하는 단계를 포함하고,

상기 분로 저항기들이 상기 드라이브 채널들에 접속되어 있는 동안, 상기 분로 저항기는 각각 상기 드라이브 채널들 중 하나의 채널과 접지 사이에 전기적 경로를 제공하는 것인, 전자 장치를 테스트하는 방법.

### 청구항 27

제26항에 있어서,

상기 분로 저항기들을 상기 드라이브 채널들로부터 차단하는 단계; 및

상기 전자 장치에 대해 상기 드라이브 채널들을 통한 파라메트릭(parametric) 테스트를 수행하는 단계를 더 포함하는, 전자 장치를 테스트하는 방법.

### 청구항 28

제26항에 있어서, 상기 분로 저항기들은 상기 기능 테스트들이 상기 전자 장치에 대해 수행될 수 있는 동작 주파수를 증가시키도록 구성되는 것인, 전자 장치를 테스트하는 방법.

## 청구항 29

제26항에 있어서, 상기 분로 저항기들은 상기 입력 단자들의 상승 시간을 감소시키는 것인, 전자 장치를 테스트 하는 방법.

## 청구항 30

제29항에 있어서, 상기 분로 저항기들은 상기 입력 단자들의 하강 시간을 감소시키는 것인, 전자 장치를 테스트 하는 방법.

## 청구항 31

삭제

## 명세서

### 기술 분야

[0001] 본 발명은 일반적으로 데이터가 하나 이상의 통신 채널을 통해 이동되는 임의의 시스템에 적용 가능하다. 그러한 시스템의 일례로 반도체 장치와 같은 전자 장치를 테스트하기 위한 테스트 시스템이 있다.

### 배경기술

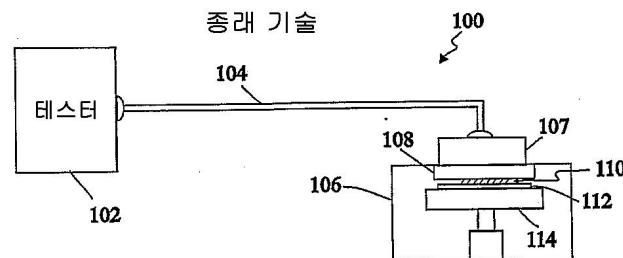

[0002] 도 1은 전자 장치 테스트용 테스트 시스템(100)의 간략화된 블록도를 도시한다. 도 1의 테스트 시스템(100)은 단일화되지 않은 반도체 웨이퍼의 다이(die)들, 단일화된 다이들(패키지된(packaged), 또는 패키지되지 않은), 또는 멀티칩 모듈(multi-chip module)들을 테스트할 수 있다. 그러한 시스템(100)은 인쇄 회로 기판과 같은 다른 유형의 전자 장치들도 테스트하도록 구성될 수 있다. 도시된 바와 같이, 시스템(100)은 테스터(tester)(102), 통신 접속부(104)(예컨대, 동축 케이블, 광섬유 링크, 무선 통신 링크 등), 프로브 헤드(107), 및 테스터(102)와 테스트될 전자 장치(electronic Device Under Test; DUT)(112) 사이에 테스트 신호를 전달하기 위한 프로브 카드(108)를 포함한다. 테스트 시스템(100)은 또한, DUT(112)를 지지하고 이동시키기 위해 이동 가능한 척(chuck)(114)을 구비하는 하우징(housing)(106)을 포함한다. 프로브 카드의 프로브(110)는 DUT(112)와 접촉하여 DUT와 전기적 접속을 형성한다.

[0003] 테스터(102)는 테스트 데이터를 발생시키고, 이 테스트 데이터는 통신 접속부(104), 프로브 헤드(107), 및 프로브 카드(108)를 경유한 전기 전도성 경로를 포함하는 통신 채널을 통해 DUT(112)의 입력 단자(도 1에 도시되지 않음)로 이동된다. DUT(112)에 의해 발생되는 응답 데이터는 DUT의 출력 단자(terminal)를 통해 출력되고, 비교 채널(역시 통신 접속부(104), 프로브 헤드(107), 및 프로브 카드(108)를 경유한 전기 전도성 경로를 포함)을 통해 테스터(102)로 전달된다. 통상적으로, 테스터(102)는 그 후 DUT(112)의 양부를 판정하기 위해 DUT(112)에 의해 발생된 응답 데이터를 예상 응답 데이터와 비교한다. (그러한 테스트는 추가적으로 또는 대안적으로 DUT의 가동율 측정에 사용될 수 있다.)

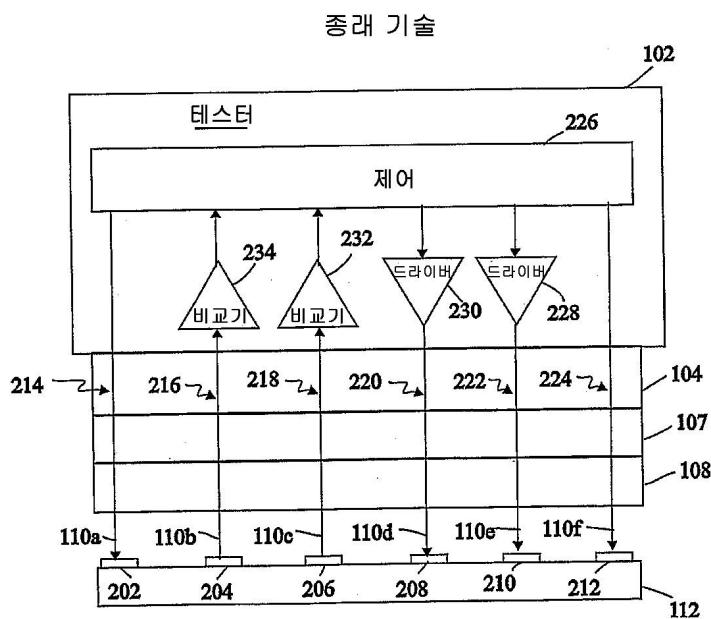

[0004] 도 2는 2개의 입력 단자(208,210), 2개의 출력 단자(204,206), 하나의 전원 단자(212), 및 하나의 접지 단자(ground terminal)(202)를 가진 대표적인 DUT(112)를 도시한다. (통상의 DUT는 더 많은 단자들을 가질 수 있지만, 도 2에서는 예시 및 설명의 용이함을 위해 6개의 단자가 도시되어 있다.) 도 2에 도시된 바와 같이, 전력은 통신 접속부(104), 프로브 헤드(107), 및 전원 단자(212)와 접촉하는 프로브(110f)를 포함하는 프로브 카드(108)를 경유한 전기 전도성 경로를 포함하는 전원 채널(power channel)(224)을 통해 테스터(102)로부터 전원 단자(212)로 제공된다. 이와 유사하게 접지 접속부(ground connection)는 프로브(110a)에서 종단되는 접지 채널(214)을 통해 테스터(102)로부터 제공된다. 테스터(102) 내의 드라이버(228,230)는 각각 프로브(110d,110e)에서 종단되는 드라이브 채널(222,224)을 통해 테스트 데이터를 입력 단자(208,210)로 이동시킨다. DUT(112)에 의해 발생되어 출력 단자(204,206)를 통해 출력되는 응답 데이터는 테스터(102) 내에서 비교기(232,234)에 의해 수신된다. (비교기(232,234)는 응답 데이터를 예상 응답 데이터와 비교한다.) 제어 모듈(226)은 테스터(102)의 전체 동작을 제어하고, 전원 및 접지를 제공하고, 테스트 데이터를 발생시키고, 실제 응답 데이터와 예상 응답 데이터를 비교한 결과값을 획득하고, 그리고/또는 다른 것들 사이에 타이밍 신호를 발생시킨다.

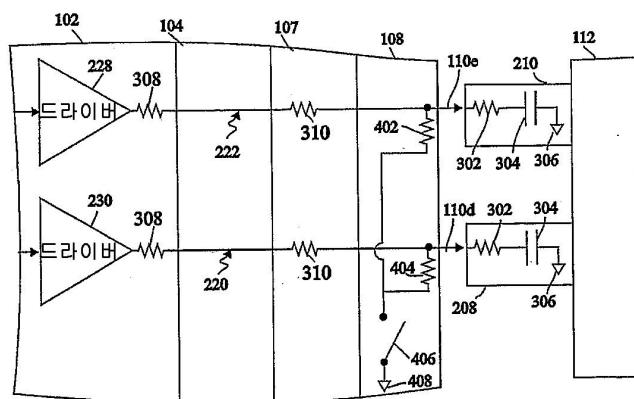

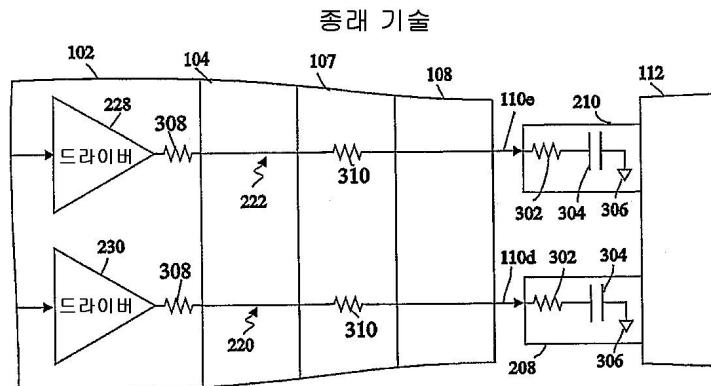

[0005] 도 3은 채널(222,220)을 구동하는 드라이버(228,230)만을 도시하는 테스터(102)의 부분도이다. 도 3에서 저항기(resistor)(308)는 드라이버(228 또는 230)의 출력 임피던스를 나타내고, 저항기(310)는 통신 채널(220 또는

222)의 특성 임피던스를 나타낸다. 도 3에서 DUT(112)는 상보형 금속 산화 반도체(CMOS) 장치인 것으로 가정된다. 알려진 바와 같이, CMOS 장치(예컨대 112)의 입력 단자(예컨대, 208 또는 210)는 주로 용량성(capacitive)이다. 입력 단자(208,210)에 대한 간략화된 등가 회로는 캐패시터(304)(입력 단자(208,210)의 주로 용량성인 특성을 나타냄)와 직렬로 연결된 저항기(302)(입력 단자(예컨대, 208 또는 210)의 입력 저항을 나타냄)로서 도 3에 도시되어 있다. (306은 접지를 나타냄)

[0006] 알려진 바와 같이, 입력 단자(208 또는 210)에서 로우(low) 신호로부터 하이(high) 신호로의 변화는 충분한 전하가 캐패시터(304)에 축적되기 전에 DUT(112)에 기록(register)되지 않는다. 이와 유사하게 입력 단자(208 또는 210)에서 하이 신호로부터 로우 신호로의 변화는 캐패시터(304)의 전하가 분산되기 전에 DUT(112)에 기록되지 않는다. 캐패시터(304)를 충전하는데 필요한 시간은 보통 상승 시간(rise time)이라 지칭하고, 캐패시터(304)를 방전하는데 필요한 시간은 하강 시간(fall time)이라 지칭한다.

[0007] 알려진 바와 같이, 직렬로 연결된 저항기 및 캐패시터의 상승 시간은 저항과 캐패시턴스의 곱에 비례한다. 상승 시간의 시간 상수( $\tau$ )는 다음과 같다:

[0008]  $\tau = R * C$ (여기서  $\tau$ 는 상승 시간 또는 하강 시간의 시간 상수이고, R은 저항기의 저항이고, C는 캐패시터의 캐패시턴스이며, \*는 곱을 가리킴). 캐패시터(304)에 걸리는 전압은 다음과 같다:  $v_c(t) = C * v_d * (1 - e^{-t/\tau})$

[0009] 여기서:

[0010] ·  $v_c(t)$ 는 시간 t에서의 캐패시터(304)에 걸리는 전압,

[0011] ·  $v_d$ 는 드라이버(228 또는 230)의 출력 전압,

[0012] · t는  $v_d$ 의 상승 에지(rising edge)로부터의 시간(로우 전압 레벨로부터 하이 전압 레벨까지),

[0013] ·  $\tau$ 는 시간 상수이고,  $\tau = R * C$ ,

[0014] · R은 각 드라이버(228,230) 및 각 입력 단자(208,210)의 캐패시턴스(304) 사이의 총 저항(따라서, R은 드라이버의 출력 임피던스(308)와 드라이브 채널의 특성 임피던스(310)와 DUT(112)의 입력 단자의 입력 저항(302)의 합), 그리고

[0015] · C는 캐패시터(304)의 캐패시턴스.

[0016] 직렬로 연결된 저항기 및 캐패시터의 하강 시간은 역시 저항과 캐패시턴스의 곱에 비례하며, 동일한 시간 상수( $\tau$ )가 적용가능하다. 캐패시터(304)에 걸리는 전압은 다음과 같다:  $v_c(t) = C * v_o * e^{-t/\tau}$ , 여기서  $v_o$ 는 캐패시터의 초기 전하이며 다른 파라미터는 위에서 정의한 바와 같다.

[0017] 명백하듯이, 입력 단자(208,210)의 상승 시간 및 하강 시간은 DUT(112)로의 입력 신호가 전환(switch)되는 주파수를 제한한다. 또한 명백하듯이, 테스트 시스템(100)은 DUT(112)의 입력 단자(208,210)의 상승 및 하강 시간을 추가할 수 있다. 이는 각 드라이버(228,230) 및 드라이브 채널(220,222)에서, 드라이버(228,230)의 출력 임피던스(308) 및 채널(220,222)의 특성 임피던스(310)가 DUT(112)의 입력 단자(208,210)의 입력 저항(302)을 효과적으로 증가시키기 때문이다.

[0018] DUT(112)가 전환되는 주파수 상의 또 다른 잠재적인 제한은 채널(220,222) 상의 신호 반사로부터 발생된다. 드라이버(228 또는 230)에 의해 채널(222 또는 220)로 이동되는 테스트 신호는 입력 단자(210 또는 208)에서 반사해(적어도 부분적으로) 드라이버(228 또는 230)를 향해 채널(222 또는 220)로 다시 돌아갈 것이다. 드라이버 출력 임피던스(308)가 채널(222 또는 220)의 특성 임피던스(310)와 정합하는 경우, 반사된 신호는 드라이버 출력 임피던스(308)에 의해 흡수되고 더이상 DUT(112)를 향해 채널(222 또는 220)로 다시 반사되지 않는다. 드라이버(또는 신호의 소스(source))의 출력 임피던스가 채널의 특성 임피던스와 정합하는 구성은 보통 "소스 종단(source termination)"으로 지칭된다. 도 3에 도시된 시스템이 소스 종단되었다 할지라도 채널(222,220)로 다시 돌아오는 반사는 입력 단자(210,208)가 전환되는 주파수를 제한하는 지터(jitter), 노이즈, 또는 심볼간 간섭을 유발할 수 있다.

[0019] 다수의 테스트 적용에 있어서, DUT가 테스트되는 주파수를 증가시키는 것이 바람직할 것이다.

## 발명의 상세한 설명

- [0020] 본 발명의 일 실시예에서, 테스트 시스템은 프로브에서 종단되는 통신 채널을 포함한다. 프로브는 테스트될 전자 장치의 입력 단자와 접촉하고, 테스트 데이터는 통신 채널을 통해 테스트되는 중인 전자 장치로 이동된다. 저항기는 프로브 근처의 통신 채널과 접지 사이에 접속되어 있다. 입력 단자의 입력 저항 및 캐패시턴스와 병렬로 연결된 저항기는 단자의 입력 저항을 감소시켜, 입력 단자의 상승 및 하강 시간을 감소시킨다. 저항기는 또한 통신 채널로 다시 신호가 반사되는 것을 감소, 최소화, 또는 제거하도록 그 크기가 조정된다.

- [0021] 본 발명의 제2 실시예에서, 테스트 시스템은 각각 프로브에서 종단되는 복수의 경로로 분기되는 통신 채널을 포함한다. 프로브는 테스트될 전자 장치의 입력 단자와 접촉한다. 아이솔레이션 저항기(isolation resistor)는 하나의 입력 단자에서의 결함(fault)이 다른 입력 단자로 전달되는 것을 방지하기 위해서 분기(branch) 내에 포함된다. 각 분기 내에 분로 저항기(shunt resistor)가 제공된다. 분로 저항기는 프로브에서 접지로 전기적 접속되어 있으며, 다시 단자의 입력 저항을 감소시켜, 입력 단자의 상승 및 하강 시간을 감소시킨다. 분로 저항기는 또한 통신 채널로 다시 신호가 반사하는 것을 감소, 최소화, 또는 제거하도록 그 크기가 조정된다.

## 실시예

- [0037] 본원은 본 발명의 전형적인 실시예 및 적용에 대해 설명하고 있지만, 본 발명은 전형적인 실시예 및 적용에 제한되는 것은 아니며, 전형적인 실시예 및 적용이 동작하는 방법으로 제한되는 것도 아니다.

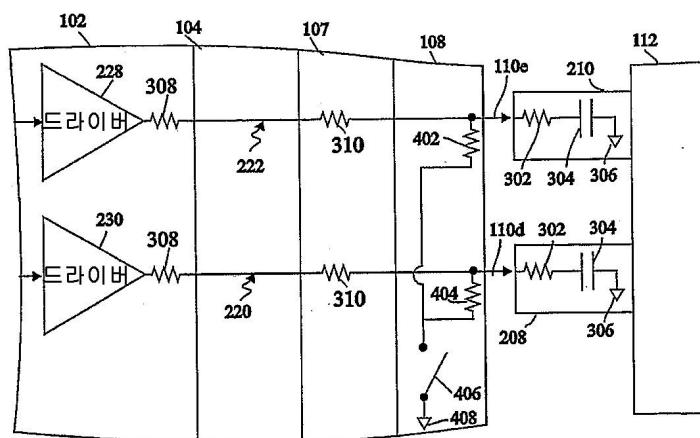

- [0038] 도 4는 DUT(112)의 입력 단자(208, 210)의 상승 및 하강 시간을 감소시키기 위해 분로 저항기(402, 404)가 포함되는 본 발명의 제1 실시예를 도시한다. 도 4는 도 3에서 도시된 바와 같이 도 2의 테스트 시스템(100)의 동일한 부분도를 도시한다. 2개의 드라이버(228, 230)는 통신 접속부(104), 프로브 헤드(107), 및 프로브 카드 조립체(108)(프로브(110d, 110e)를 포함)를 경유한 전도성 경로를 포함하는 2개의 채널(220, 222)을 구동한다. 프로브(110d, 110e)는 접촉하여, DUT(112)의 입력 단자(210, 208)와 전기적 접속을 한다.

- [0039] 도 4에서 도시된 바와 같이, 분로 저항기(402, 404)는 각 드라이브 채널(220, 222)의 프로브 단부(probe-end) 또는 그 근처에 배치된다. 분로 저항기(402, 404) 양자 모두 접지(408)에 접속된다. (도 4에서, 분로 저항기(402, 404)는 스위치(406)를 통해 접지(408)에 선택적으로 접속되며, 이는 이하에서 설명될 것이다.) 각 채널의 분로 저항기(402, 404)로 인해 입력 단자(208, 210)의 상승 시간 및 하강 시간을 모두 개선시킨다.

- [0040] 명백하듯이, 스위치(406)가 닫히면, 각 분로 저항기(402, 404)는 일반적으로 각 단자(208, 210)의 입력 저항기(302)와 병렬로 연결된다. 알려진 바와 같이, 병렬로 연결된 2개의 저항기의 총 저항은 어느 하나의 저항기 단독의 저항보다 작다. (잘 알려진 병렬 저항 계산 식은  $R_T = (R_1 * R_2) / (R_1 + R_2)$ , 여기서  $R_T$ 는 병렬로 연결된 저항기  $R_1$  및  $R_2$ 의 총 저항이며,  $*$ 는 곱을 나타낸다.) 따라서, 분로 저항기(402, 404)는 드라이버(228, 230) 및 입력 단자(210, 208) 사이의 총 저항을 감소시키며, 이는 차례로 시간 상수  $\tau = R * C$ 와 각 입력 단자(208, 210)의 상승 및 하강 시간을 감소시킨다. 입력 단자(208, 210)의 입력 저항기(302)의 유효 저항을 감소시킴으로써, 분로 저항기(402, 404)는, 양자 모두가 단자의 입력 저항기(302)와 직렬로 연결되어 입력 단자의 상승 및 하강 시간을 증가시키는 드라이버 출력 임피던스(308) 및 드라이브 채널 임피던스(310)의 효과를 효과적으로 감소시키거나 제거한다. 따라서, DUT(112)의 입력 단자(208, 210)의 상승 및 하강 시간을 감소시키기 위해 분로 저항기(402, 404)의 크기를 적당히 조정함으로써, DUT(112)가 테스트될 수 있는 주파수가 증가될 수 있다.

- [0041] 신호 반사를 감소, 최소화, 또는 제거시키기 위해 분로 저항기(402, 404)의 크기를 조정함으로써 도 4에서 도시된 시스템과 같은 시스템의 동작 주파수를 더 개선할 수 있다. 채널(222 또는 220)의 단부(end)에서의 임피던스와 채널 임피던스(310)를 정합 또는 거의 정합시킴으로써 채널(222 또는 220)의 DUT 단부에서의 반사는 감소, 최소화 또는 제거될 수 있다.(드라이버 출력 임피던스(308)와 채널 임피던스(310)는 정합된다고 가정한다(이는 동일하거나 거의 동일한 값임).) 이는 채널 임피던스(310)와 동일 또는 거의 동일한, 채널(222 또는 220) 단부에서의 DUT 단자 입력 저항(302)을 가지는 총 저항을 제공하도록 분로 저항기(402 또는 404)의 크기를 조정함으로써 수행된다. 분로 저항기(402 또는 404)는 DUT 단자 입력 저항기(302)와 병렬로 연결되어 있고, 알려진 바와 같이 병렬로 연결된 저항기들의 총 저항은 병렬의 저항기들의 곱을 병렬의 저항기들의 합으로 나눈 값임을 알아야 한다. 따라서, 반사를 제거하기 위해, 분로 저항기(402 또는 404)의 크기는 분로 저항기(402 또는 404)와 DUT 입력 단자 저항기(302)의 총 저항이 채널 임피던스(310)와 동일하도록 조정되어야 한다. 분로 저항기(402 또는 404)와 이와 병렬인 DUT 입력 단자 저항기(302)의 총 저항이 채널 임피던스(310)와 거의 동일하거나 적어도 더 동일한 값에 가깝도록 함으로써 반사는 감소되거나 최소화될 수 있다. CMOS 장치와 같은 다수의

장치에서, 장치의 입력 임피던스(302)는 무시될 수 있는 전송 선로(transmission line) 임피던스(310)보다 충분히 크기 때문에, 분로 저항기(402, 404)는 적절한 정합을 위해 전송 선로 임피던스(310)와 동일하게 될 수 있다.

[0042] 각 채널(222, 220)에 대해, 분로 저항기(402 또는 404)는 채널 임피던스(310)와 함께 전압 분배기를 형성하는 것은 명백하다. DUT 입력 단자(210 또는 208)가 하이 상태(high state)로 전환되고, 캐패시터(304)가 완전히 충전된 후에, 상당한 전류가 DUT 입력 단자(210 또는 208)로 흐르는 것을 멈추고, 분로 저항기(402 또는 404)를 통해 흐른다. 드라이버(228 또는 230)에 의한 전압 출력은 분로 저항기(402 또는 404)에 걸리는 전압이 하이 상태에서 DUT 입력 단자(210 또는 208)를 유지하기에 충분하도록 되어야 한다. 예컨대, 분로 저항기(402 또는 404)가 채널 임피던스(310)와 같은 크기인 경우, 드라이버(228 또는 230)의 출력 전압(드라이버는 출력 임피던스(308)를 포함하고 드라이버 출력 전압은 채널(222 또는 220) 상으로 구동되는 전압임)은 하이 상태에서 DUT 입력 단자(210 또는 208)를 유지하기 위해 필요한 전압의 2배가 되어야 한다.(알려진 바와 같이, 전압 소스와, 직렬로 연결된 제1 및 제2 저항기로 구성되는 전압 분배 회로 내의 제2 저항기에 걸리는 전압은 소스 전압과 제2 저항기의 저항값의 곱을 제1 및 제2 저항기의 합으로 나눈 값이다.)

[0043] 스위치(406)는 분로 저항기(402, 404)가 사용되거나 사용되지 않도록 전환한다. 스위치(406)가 닫힌 동안에, 분로 저항기(402, 404)는 접지(408)에 접속되고 상술한 바와 같이 입력 단자(208, 210)의 상승 및 하강 시간을 감소시킨다. 스위치(406)가 열린 동안에, 분로 저항기(402, 404)는 도 4에서 도시된 테스트 시스템에서 효과적으로 나와 있다.

[0044] 파라메트릭(parametric) 테스트와 같은 일부 테스트는 스위치(406)가 열려 있는 동안에 최상으로 동작한다. 파라메트릭 테스트는 하나 이상의 DUT(112) 단자가 접지 또는 다른 단자에 쇼트(short)되었는지를 결정하는 테스트와 단자를 통한 누설 전류(leakage current)를 결정하는 테스트를 포함한다. 상술한 바와 같이, 스위치(406)가 닫힌 상태에서, 테스트 시스템은 고주파수 기능 테스트를 수행하도록 준비된다.

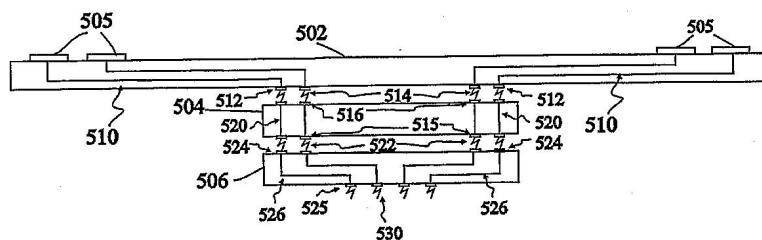

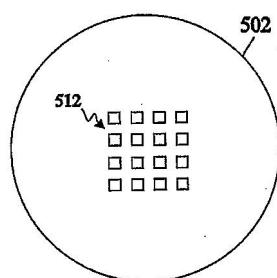

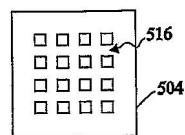

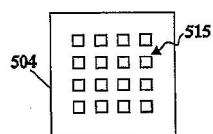

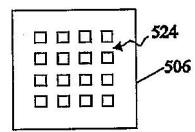

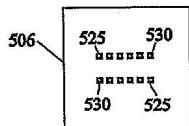

[0045] 도 5는 반도체 웨이퍼, 또는 단일화된 다이들(패키지된, 또는 패키지되지 않은)이나 멀티칩 전자 모듈 등을 포함하나 이들에 제한되지 않는 다른 전자 장치의 다이들을 테스트하는데 사용될 수 있는 전형적인 프로브 카드 조립체를 도시한다. 도 5에서 도시된 프로브 카드 조립체는 도 1의 테스트 시스템(100)과 같은 테스트 시스템에서 사용될 수 있다. 도 5에서 도시된 전형적인 프로브 카드 조립체는 프로브 헤드(예컨대, 도 1의 프로브 헤드(107))에 접촉하기 위해 일면에 단자들(505)을 가지는 프로브 보드(502)를 포함한다. 전기적 접속부(510)는 프로브 보드(502)를 통해 단자(505)를 단자(512)에 접속시킨다. 인터포저(504)는 프로브 보드 단자(512)를 프로브 기판(506)과 전기적으로 접속시킨다. 인터포저(504)는 단자들(512)을 체결하는 전기 콘택트(514)(연장된(elongate) 스프링 콘택트일 수 있음)을 포함한다. 인터포저의 전기 콘택트(514)은 인터포저(504)의 일면 상의 단자들(516)에 부착되고 커넥터(connector)(520)에 의해 인터포저(504)의 이면 상의 단자들(515)에 전기적으로 접속된다. 전기 콘택트(522)(전기 콘택트(514)와 유사할 수 있음)는 프로브 기판(506) 상의 단자들(524)을 체결한다. 단자(524)는 프로브 기판(506)을 지나는 접속부(526)를 통해 전기적으로 접속되고, DUT(도 5에서 도시되지 않음)를 접촉시키는 프로브(530)는 프로브 단자(525)에 부착된다. 따라서, 프로브 보드(502) 상의 단자들(505)과 프로브 기판(506) 상의 프로브들(530) 사이에 전기적 경로가 제공된다. 프로브 보드(502), 인터포저(504), 및 프로브 기판(506)은 임의의 적절한 수단을 사용하여 서로 고정될 수 있다. 그러한 프로브 카드 조립체에 대한 더 자세한 설명은, 참조에 의해 본원에 완전히 통합되어 있는 미국 특허 제 5,974,662호에 제공되어 있다.

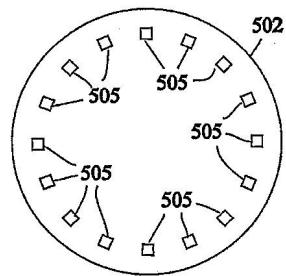

[0046] 도 6a 및 6b는 각각 프로브 보드(502)의 상부도 및 하부도이다. 도 6a에서 도시된 바와 같이, 단자들(505)은 프로브 보드(502)의 일면 상에 배치되고, 단자(512)는 프로브 보드(502)의 반대면 상에 배치된다. 이와 유사하게, 도 7a 및 7b는 각각, 일면 상에 단자들(516)과 반대면 상에 단자들(515)을 가지는 인터포저(504)의 상부도 및 하부도이다. 인터포저(504) 상의 단자(516)는 프로브 보드(502) 상의 단자(512)에 대응하도록 배열된다. 이와 유사하게 도 8a 및 8b는, 일면 상에 배치된 단자(524)와 이면 상의 프로브 단자(525)를 가진 프로브 기판(506)의 상부도 및 하부도이다. 프로브 기판(506) 상의 단자(524)는 인터포저(504) 상의 단자(515)에 대응하도록 배열된다. 프로브 단자(525)는 하나 이상의 DUT의 입력, 출력, 전원, 및 접지 단자의 위치에 대응하도록 배열되고, 프로브(530)는 프로브 단자(525)에 부착된다.

[0047] 분로 저항기(402, 404)는 바람직하게는 가능한 한 프로브(530)에 가깝도록 도 5의 프로브 카드 조립체 상에 배치된다. 따라서, 분로 저항기(402, 404)는 바람직하게는 프로브 기판(506) 상에 배치된다. 그럼에도 불구하고, 분로 저항기(402, 404)는 하나 이상의 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506) 중 어디에도 위치할 수 있다. 게다가, 분로 저항기(402, 404)는 프로프 보드(502), 인터포저(504), 또는 프로브 기판(506)의

어느 한쪽면 상이라도 배치될 수 있다. 실제로, 분로 저항기(402,404)는 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506) 내에 배치될 수 있다. (예컨대, 접속부(510)를 따라 프로브 보드(502) 내에, 접속부(520)를 따라 인터포저(504) 내에, 또는 접속부(526)를 따라 프로브 기판(506) 내에). 마찬가지로 스위치(406)는 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506) 상에 어디든지 위치할 수 있다. 분로 저항기(402,404)는 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506) 중 임의의 것 내에 또는 그들 상에 제조된 박막 저항기로서, 또는 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506) 중 임의의 것에 부착된 분리된 저항기 회로 소자로서 구현될 수 있다.

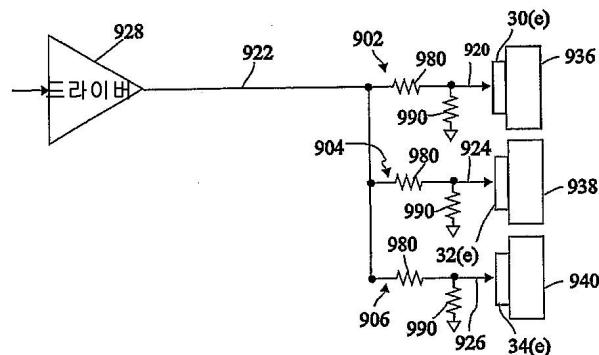

[0048] 도 9는 본 발명의 또 다른 전형적인 실시예를 도시한다. 도 9는 3개의 프로브(920,924,926)를 통해 3개의 DUT(936,938,940)의 입력 단자(30(e),32(e),34(e))에 접속된 채널(922)를 구동하도록 구성된 드라이버(928)를 도시한다. 드라이버(928) 및 드라이브 채널(922)은 도 2의 드라이버(228) 및 드라이브 채널(222)과 유사하고, 드라이버(928) 및 드라이브 채널(922)은 도 2의 테스트 시스템과 같은 테스트 시스템에서의 다수의 드라이버 및 드라이브 채널 중 하나일 수 있다.

[0049] 도 9에서 도시된 바와 같이, 드라이브 채널(922)은 드라이버(928)를 3개의 프로브(920,924,926) 통해 3개의 DUT(936,938,940)의 입력 단자(30(e),32(e),34(e))에 접속하는 3개의 분기(902,904,906)를 포함한다. 이러한 방법에서, 하나의 DUT를 위한 테스터(102)(도 1 참조)에서 발생된 테스트 데이터는 3개의 DUT를 테스트하는데 사용될 수 있다. 당연히, 드라이브 채널은 3보다 작은 수 또는 큰 수의 단자들로 팬 아웃되고, 일부 또는 모든 단자들은 선택적으로 동일 DUT 상에 있을 수 있다. 또한 명백하듯이, 다수의 DUT에 의해 발생된 응답 데이터를 테스터로 돌려 보내기 위해 추가적인 비교 채널 또는 멀티플렉싱 방식(multiplexing scheme)이 사용될 수 있다.

[0050] 도 9에서 아이솔레이션 저항기(980)는 한 단자(예컨대 30(e))에서의 결함이 다른 단자(예컨대 32(e))에 역효과를 미치는 것을 방지하기 위해 각 분기(902,904,906)에 배치된다. 예컨대, 아이솔레이션 저항기(980)가 없으면, 단자(30(e))가 접지에 쇼트되는 결함은 분기(902,904,906)를 통해 단자(32(e),34(e))를 접지에 쇼트시킬 것이며, 이는 DUT(938,940)가 DUT(936)와 동일한 결함을 갖는 것처럼 잘못된 테스트를 유발한다. 그러나, 아이솔레이션 저항기(980)는 단자(30(e))에서의 결함을 단자(32(e),34(e))로부터 분리시킨다.

[0051] 추가적인 저항기인 아이솔레이션 저항기(980)의 존재로 단자(30(e),32(e),34(e))의 상승 및 하강 시간에 역효과를 가져온다.(상술한 바와 같이, 추가적인 저항은 각 입력 단자(30(e),32(e),34(e))에 대한 식  $\tau = R * C$ 에서 R 값을 증가시킬 수 있어, 각 입력 단자의 상승 및 하강 시간을 증가시킨다. 사실상, 분기(예컨대, 902,904,906)의 개수가 많아질수록, 입력 단자(30(e),32(e),34(e))의 상승 및 하강 시간에 잠재적인 영향을 더 크게 미친다. 도 9에서 도시된 바와 같이, 접지에 접속된 분로 저항기(990)는 각 분기(902,904,906)에 배치된다. 상술한 바와 같이, 각 단자(30(e),32(e),34(e))의 입력 저항과 효과적으로 병렬로 연결된 분로 저항기(990)는 아이솔레이션 저항기(980)의 효과를 감소시키고, 일반적으로 입력 단자(30(e),32(e),34(e))의 상승 및 하강 시간을 개선한다.

[0052] 명백하듯이, 각 분기(902,904,906) 내의 분로 저항기(990)는 각 분기(902,904,906) 내의 아이솔레이션 저항기(980)와 함께 전압 분배 회로를 형성한다. 도 4에 대해서 상술한 바와 같이, 각 분기(902,904,906) 내의 분로 저항기(990) 및 아이솔레이션 저항기(980)의 크기는, 드라이버(928)가 하이 신호를 출력하는 동안 DUT(936,938,940)의 각 입력 단자(30(e),32(e),34(e))를 하이 상태로 유지하기 위해 각 프로브(920,924,926)에서 충분한 전압이 유지되도록 조정되어야 한다. 도시의 단순화 및 용이성을 위해 드라이버(928)에 대한 출력 임피던스 및 채널(922)에 대한 채널 임피던스는 모두 도 9에서 나타나 있지 않지만, 그러한 임피던스는 존재한다. 도 4에 대해 상술한 바와 같이, 분로 저항기(990) 및 아이솔레이션 저항기(980)의 크기는 드라이버(928)에 의해 채널(922)로 이동되는 신호의 반사를 감소, 최소화, 또는 제거시키기 위해 조정될 수 있다. 도 4의 스위치(406)와 같은 하나 이상의 스위치들은 분로 저항기(990)와 분기(902,904,906)와 유효 접속 상태에 있거나, 이 상태로부터 벗어나도록 전환하기 위해 도 9에서 포함될 수 있으며, 이는 도 4에 대해 상술한 바와 같이 파라메트릭 테스트를 용이하게 할 수 있다.

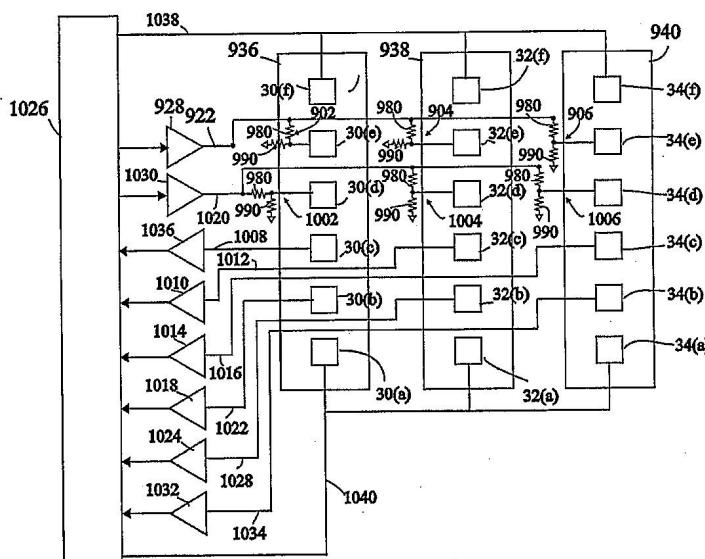

[0053] 도 10은 아이솔레이션 저항기와 함께 분로 저항기의 사용에 대한 전형적인 구현예를 도시한다. 도 10에서 도시되는 전형적인 테스트 시스템은 도 9에 도시된 3개의 DUT(936,938,940)을 테스트하기 위한 테스트 시스템에서 도 9의 드라이버(928) 및 드라이브 채널(922)을 도시한다.

[0054] 도 10에서 도시된 바와 같이, 2개의 드라이버(928,1030)는 2개의 드라이브 채널(922,1020)을 구동한다. 드라이브 채널(922)은 3개의 분기(902,904,906)를 통해 각각의 DUT(936,938,940) 상의 3개의 입력 단자(30(e),32(e),34(e))에 팬 아웃된다. 각 분기(902,904,906)는 아이솔레이션 저항기(980) 및 접지에 접속된 분

로 저항기(990)를 포함한다. 드라이브 채널(1020)은 유사하게 3개의 분기(1002, 1004, 1006)를 통해 각각의 DUT(936, 938, 940) 상의 3개의 입력 단자(30(d), 32(d), 34(d))에 팬 아웃되며, 각 분기(1002, 1004, 1006)는 또한 아이솔레이션 저항기(980) 및 접지에 접속된 분로 저항기(990)를 포함한다. 비교기(1036, 1010, 1014, 1018, 1024, 1032)는 비교 채널(1008, 1012, 1016, 1022, 1028, 1034)을 통해 도 10에 도시된 DUT(936, 938, 940)의 출력 단자(30(c), 30(b), 32(c), 32(b), 34(c), 34(b))에 접속된다. 제어기(위의 도 2의 제어기(226)와 유사할 수 있음)는 드라이버(928, 1030)에 대한 테스트 데이터의 입력을 제어하고, 비교기(1036, 1010, 1014, 1018, 1024, 1032)로부터 응답 데이터를 수신한다. 제어기(1026)는 또한 전원 채널(power channel)(1038)을 통해 DUT(936, 938, 940)의 전원 단자(30(f), 32(f), 34(f))에 전원을 공급하고, 접지 채널(1040)을 통해 DUT(936, 938, 940)의 접지 단자(30(a), 32(a), 34(a))에 접지를 제공한다. 이러한 방법에서, 오직 하나의 DUT를 테스트하기에 충분한 드라이버 및 드라이브 채널은 3개의 DUT를 테스트하는데 이용된다; 아이솔레이션 저항기는 하나의 DUT 상의 결함이 다른 DUT들이 불량으로 잘못 테스트되게 하는 것을 방지하기 위해 제공된다; 그리고 분로 저항기는 DUT의 입력 단자의 상승 및 하강 시간을 증가시키기 위해 제공된다.

[0055] 도 9 및 도 10에서 도시된 아이솔레이션 저항기(980) 및 분로 저항기(990)는 도 5에서 도시된 전형적인 프로브 카드 조립체와 같은 프로브 카드 조립체 상에서 구현될 수 있다. 도 4의 분로 저항기(402, 404)와 같이, 아이솔레이션 저항기(980) 및 분로 저항기(990)는 도 5에서 도시된 것과 같은 프로브 카드 조립체의 하나 이상의 프로브 보드(502), 인터포저(504) 또는 프로브 기판(506) 중 어디든지 배치될 수 있다. 게다가, 아이솔레이션 저항기(980) 및 분로 저항기(990)는 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506)의 어느 면에라도 배치될 수 있다. 실제로, 아이솔레이션 저항기(980) 및 분로 저항기(990)는 프로브 보드(502), 인터포저(504), 또는 프로브 기판(506) 내에 배치될 수 있다(예컨대, 접속부(510)를 통해 프로브 보드(502) 내에, 접속부(520)를 통해 인터포저(504) 내에, 또는 접속부(526)를 통해 프로브 기판(506) 내에). 아이솔레이션 저항기(980) 및 분로 저항기(990)는 박막 저항기 또는 분리된 저항기 회로 소자로서 구현될 수 있다.

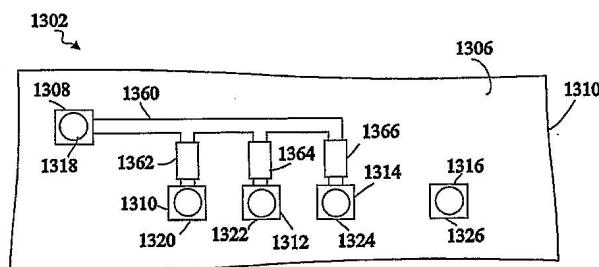

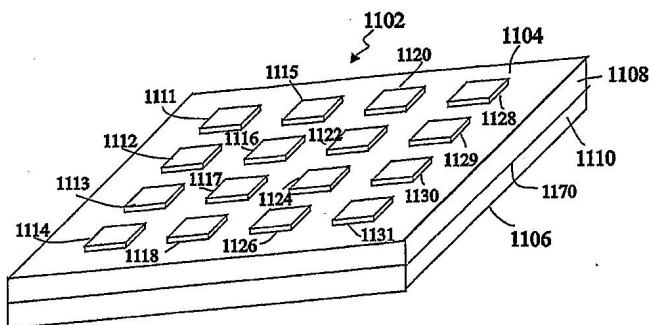

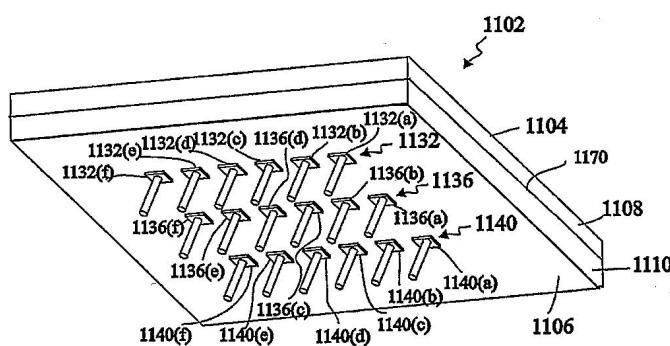

[0056] 도 11a 내지 13b는 아이솔레이션 저항기(980) 및 분로 저항기(990)가 도 5의 프로브 기판(506)을 대신할 수 있는 프로브 기판(1102 또는 1302) 상의 박막 저항기로서 구현되는 실시예를 도시한다. 도 11a 내지 도 12b에 도시된 실시예에서, 아이솔레이션 저항기(980) 및 분로 저항기(990)는 프로브 기판(1102)을 포함하는 2개의 층(1108, 1110) 사이에(1170) 박막 저항기(1280, 1290)로서 구현된다. 도 13a 및 도 13b에서, 아이솔레이션 저항기(980)는 프로브 기판(1302) 내에 박막 저항기(1340, 1342, 1343)로서 구현되고, 분로 저항기(990)는 프로브 기판(1302)의 하부면(1306) 상의 박막 저항기(1362, 1364, 1366)로서 구현된다.

[0057] 도 11a 및 도 11b는 각각 전형적인 프로브 기판(1102)(도 5의 프로브 기판(506)과 유사하고 그 대신 사용될 수 있음)의 상부 사시도 및 하부 사시도이다. 도시된 바와 같이, 프로브 기판(1102)는 도 10에서 도시된 전형적인 테스트 시스템을 구현하도록 구성된다. 프로브 기판(1102)의 표면(1104) 상의 단자(1111, 1112, 1113, 1114, 1115, 1116, 1117, 1118, 1120, 1122, 1124, 1126, 1128, 1129, 1130, 1131)은 인터포저(504)(도 5에 도시됨)로부터 접속부(522)와 접촉하도록 배치되고, 편의를 위해 이하에서 "인터포저 단자(interposer-terminal)"로 언급될 것이다.

[0058] 이 예에서, 인터포저 단자(1112, 1113, 1114)는 도 5의 프로브 카드 조립체의 인터포저(504) 및 프로브 보드(502)를 통해 도 10의 전원 채널(1040)로 배선된다(wired). 인터포저 단자(1128, 1130, 1131)는 유사하게 인터포저(504) 및 프로브 보드(502)를 통해 접지 채널(1038)로 배선된다. 인터포저 단자(1118, 1120, 1122, 1124, 1126, 1129)는 유사하게 인터포저(504) 및 프로브 보드(502)를 통해 비교 채널(1008, 1012, 1016, 1022, 1028, 1034)로 배선되고, 인터포저 단자(1111, 1115)는 인터포저(504) 및 프로브 보드(502)를 통해 드라이브 채널(922, 1020)로 배선된다. (이 예에서 인터포저 단자(1116, 1117)는 사용되지 않는다.)

[0059] 프로브 단자(프로브가 부착되는)는 프로브 기판(1102)의 하부면(1106) 상에 배치된다. 프로브 단자는 각 열마다 6개의 단자를 가진 상태로 3개의 열(1132, 1136, 1140)로 구성된다. 각 열(1132, 1136, 1140)은 하나의 DUT(936, 938, 940)에 대응하고, 각 열에 있는 각 단자는 하나의 DUT 상의 하나의 단자에 대응한다. 이 예에서 (프로브 기판(1102)이 도 10의 DUT(936, 938, 940)를 테스트하도록 구성되는), 프로브 단자(1132(f), 1136(f), 1140(f))에 부착되는 프로브는 DUT(936, 938, 940)의 전원 단자(30(f), 32(f), 34(f))에 전원을 제공하기 위한 전원 프로브이다. 프로브 단자(1132(a), 1136(a), 1140(a))에 부착되는 프로브는 DUT(936, 938, 940)의 접지 단자(30(a), 32(a), 34(a))에 접지를 제공하기 위한 접지 프로브이다. 프로브 단자(1132(c), 1132(b), 1136(c), 1136(b), 1140(c), 1140(b))에 부착되는 프로브는 DUT(936, 938, 940)의 출력 단자(30(c), 30(b), 32(c), 32(b), 34(c), 34(b))를 접촉하도록 배치된다.

(1132(e), 1132(d), 1136(e), 1136(d), 1140(e), 1140(d))에 부착되는 프로브는 DUT(936, 938, 940)의 입력 단자(30(e), 30(d), 32(e), 32(d), 34(e), 34(d))와 접촉하도록 배치된다.

[0060] 도 11a 및 11b에서 도시되는 프로브 기판은 다층(multi layer)으로 만들어질 수 있다. 도시 및 설명을 위해, 프로브 기판(1102)은 도 11a 및 도 11b에서, 서로 부착된 2개의 기판이 될 수 있는 2개의 층(1108, 1110)을 가지는 것으로 도시되어 있다. 표면(1104) 상의 인터포저 단자들(예컨대, 1111) 및 표면(1106) 상의 프로브 단자(예컨대, 1140(f)) 사이의 전기적 경로는 제1 층(1108)을 통한 비아(vias)(도 11a 및 도 11b에서 도시되지 않음), 제1 층(1108)과 제2 층(1110) 사이(1170)에 위치한 트레이스(trace)(도 11a 및 도 11b에서 도시되지 않음), 및 제2 층(1110)을 통한 비아(vias)(도 11a 및 도 11b에서 도시되지 않음)에 의해 제공될 수 있다. 도 12는 전술한 예를 도시한다.

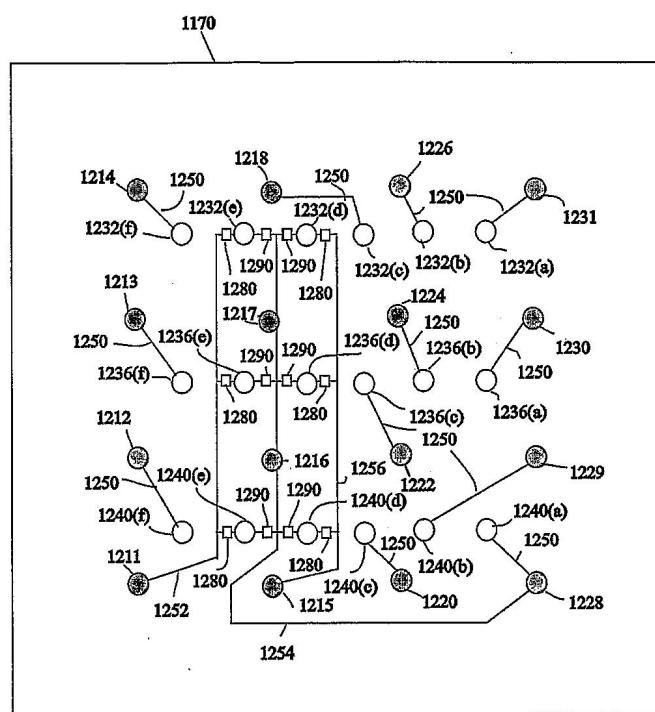

[0061] 도 12는 프로브 기판(1102)의 제1 층(1108)과 제2 층(1110) 사이의 계면(1170)에 대한 전형적인 구성을 도시한다. 도 12에서, 제1 층(1108)을 관통하고 표면(1104) 상의 인터포저 단자(예컨대, 1111)에 전기적으로 접속하는 비아는 어둡게 된 원(예컨대, 소자 1211, 1212, 1213, 1214, 1215, 1216, 1217, 1218, 1220, 1222, 1224,

[0062] 1226, 1228, 1229, 1230, 1231)에 의해 표시된다. 제2 층(1110)을 관통하고 표면(1106) 상의 프로브 단자(예컨대, 1140(f))에 전기적으로 접속하는 비아는 어둡게 되지 않은 원(예컨대, 1232(a)-(f), 1236(a)-(f), 1240(a)-(f))에 의해 표시된다. 전기 전도성의 트레이스는 도 12에서 1250, 1252, 1254, 1256으로 도시되고, 그러한 트레이스는 어느 하나의 층(1108 또는 1110)의 내부 표면 상에 배치되어, 도 11a 및 11b에서 도시된 것과 같이 층들(1104, 1106)이 함께 부착되면서 층(1108)을 경유하는 비아를 층(1110)을 경유하는 비아와 접속시킨다.

[0063] 비교 채널에 전원, 접지, 또는 접속부를 제공하는 프로브 기판(1102)의 표면(1104) 상의 인터포저 단자(예컨대, 1111)는 프로브 기판(1102)의 표면(1106) 상의 프로브 단자(예컨대, 1140(f))에 일대일 관계로 접속된다. 현재 예에서(프로브 기판(1102)이 도 10에서 도시된 시스템에서 사용되도록 구성되는), 인터포저 단자(1112, 1113, 1114)(상술한 바와 같이 도 10에서 도시된 전원 채널(1140)에 접속되는)는 도 12에서 도시된 비아 쌍(1214 및 1232(f), 1213 및 1236(f), 1212 및 1240(f))들을 통해 전원 프로브 단자(1132(f), 1136(f), 1140(f))에 접속된다. (트레이스(1250)는 도 12에서 도시된 바와 같이 전술한 각각의 비아 쌍들을 전기적으로 접속시킨다.) 이와 유사하게, 인터포저 단자(1128, 1130, 1131)(상술한 바와 같이 도 10에서 도시된 접지 채널(1138)에 접속되는)는 도 12에서 도시된 비아 쌍(1228 및 1240(a), 1230 및 1236(a), 1231 및 1232(a))들을 통해 접지 프로브 단자(1132(a), 1136(a), 1140(a))에 접속된다. (다시, 트레이스(1250)는 도 12에서 도시된 바와 같이 전술한 각각의 비아 쌍들을 전기적으로 접속시킨다.) 유사한 방식으로, 인터포저 단자(1118, 1120, 1122, 1124, 1126, 1129)(도 10에서 비교 채널(1008, 1012, 1016, 1022, 1028, 1034)에 접속되는)는 도 12에서 도시된 비아 쌍(1218 및 1232(c), 1226 및 1232(b), 1222 및 1236(c), 1224 및 1236(b), 1220 및 1240(c), 1229 및 1240(b))들을 통해 프로브 단자(1132(b), 1132(c), 1136(b),

[0064] 1136(c), 1140(b), 1140(c))에 접속된다.

[0065] 반면에, 드라이브 채널과의 접속을 제공하는 프로브 기판(1102)의 표면(1104) 상의 각 인터포저 단자는 프로브 기판(1102)의 표면(1106) 상의 다수의 프로브 단자에 접속된다. 도 12에서 도시된 예에서, 인터포저 단자(1111)(상술한 바와 같이 드라이브 채널(922)에 접속되는)는 비아(1211)를 통해 트레이스(1252)에 접속되며, 이 트레이스(1252)는 각각 차례로 프로브 단자(1140(e), 1136(e), 1132(e))에 접속되는 비아(1240(e), 1236(e), 1232(e))에 전기적으로 접속된다. 따라서, 비아(1211), 트레이스(1252), 및 비아(1140(e), 1136(e), 1132(e))는 인터포저 단자(1111)를 3개의 프로브 단자(1140(e), 1136(e), 1132(e))와 접속시킨다. 이와 유사하게, 인터포저 단자(1115)(상술한 바와 같이 드라이브 채널(1020)에 접속되는)는 비아(1215)를 통해 트레이스(1256)에 접속되며, 이 트레이스(1256)는 각각 차례로 프로브 단자(1140(d), 1136(d), 1132(d))에 접속되는 비아(1240(d), 1236(d), 1232(d))에 전기적으로 접속된다. 따라서, 비아(1215), 트레이스(1256), 및 비아(1140(d), 1136(d), 1132(d))는 인터포저 단자(1115)를 3개의 프로브 단자(1140(d), 1136(d), 1132(d))와 접속시킨다.

[0066] 도 12에서 도시된 바와 같이, 박막 저항기(1280)는 트레이스(1252)와 각각의 비아(1240(e), 1236(e), 1232(e)) 사이에 배치된다. 박막 저항기(1280)는 또한 트레이스(1256)와 각각의 비아(1240(d), 1236(d), 1232(d)) 사이에 배치된다. 따라서, 박막 저항기(1280)는 도 10의 아이솔레이션 저항기(980)를 구현한다. 박막 저항기(1290)는 각각의 비아(1240(e), 1236(e), 1232(e), 1240(d), 1236(d), 1232(d))와, 접지(예컨대, 인터포저 단자(1128)를 통해 접지 채널(1040)(도 10 참조) 중 하나에 접속되는 비아(1228))에 접속된 트레이스(1254) 사이에 배치된다. 따라서, 박막 저항기(1290)는 도 10의 분로 저항기(990)를 구현한다.

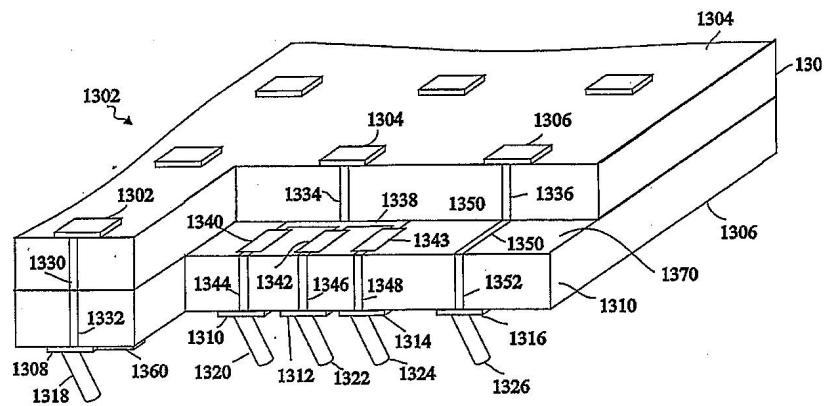

- [0067] 위에서 언급한 바와 같이, 도 13a 및 13b는 프로브 기판(1302) 상에 아이솔레이션 저항기(980) 및 분로 저항기(910)를 구현하는 또 다른 전형적인 방법을 도시한다. 도 13a는 일반적으로 도 11a 및 11b의 프로브 기판(1102)과 유사할 수 있는 프로브 기판(1302)의 일부에 대한 절단된 사시도를 나타낸다. 도 13b는 프로브 기판(1302) 일부의 하부도를 나타낸다.

- [0068] 프로브 기판(1102)과 같이, 프로브 기판(1302)(도 5의 프로브 기판(506)을 대신할 수 있는)은 2개의 층(1308, 1310)을 포함하고, 제1 표면(1304) 상에 인터포저 단자(1302, 1304, 1306이 도시됨) 및 제2 표면(1306) 상의 프로브(1318, 1320, 1322, 1324, 1326이 도시됨)가 부착되는 프로브 단자(1308, 1310, 1312, 1314, 1316이 도시됨)를 가진다. 도 13a에서, 인터포저 단자(1302)는 DUT(도 13a 및 13b에 도시되지 않음)에 접지 접속을 제공하고, 도 13a에서 도시된 바와 같이 비아(1330, 1332)를 통해 프로브 단자(1308) 및 접지 프로브(1318)에 접속된다. 인터포저 단자(1306)는 비교 채널에 접속되도록 구성되어 DUT(도 13a 및 도 13b에서 도시되지 않음)에 의해 생성된 출력 데이터를 비교 채널의 단부에 있는 비교기로 전달한다. 도 13a에서 도시된 바와 같이, 인터포저 단자(1306)는 층(1308)을 관통하는 비아(1336), 제2 층(1310)의 표면(1370)에 배치되는 트레이스(1350), 및 제2 층(1310)을 관통하는 비아(1352)에 의해 프로브 단자(1316)(출력 프로브(1326)가 부착되는)에 접속된다.

- [0069] 인터포저 단자(1304)는 드라이브 채널에 접속되도록 구성되어 DUT(도 13a 및 도 13b에서 도시되지 않음)에 테스트 데이터를 제공한다. 도 10에 도시된 테스트 구성은 구현하기 위하여, 인터포저 단자(1304)는 3개의 DUT(도 13a 및 13b에 도시되지 않음)의 입력 단자와 접촉하도록 구성된 3개의 입력 프로브(1320, 1322, 1324)가 부착된 3개의 프로브 단자(1310, 1312, 1314)에 접속된다. 도 13a에서 도시된 바와 같이, 비아(1334)는 인터포저 단자(1304)를 프로브 기판(1302)의 제2 층(1310)의 표면(1370) 상의 트레이스(1338)에 접속시킨다. 표면(1370) 상의 박막 저항기(1340, 1342, 1343)는 트레이스(1338)를, 프로브 터미널(1310, 1312, 1314)에 차례대로 접속되는 3개의 비아(1344, 1346, 1348)에 접속시킨다. 박막 저항기(1340, 1342, 1343)는 도 9 및 도 10에서 도시된 아이솔레이션 저항기(980)를 구현한다. 도 13b에서 도시된 바와 같이, 프로브 기판(1302)의 제2 표면(1310) 상에서, 박막 저항기(1362, 1364, 1366)는 각각의 프로브 단자(1310, 1312, 1324)를 접지 단자(1308)로부터 트레이스(1360)로 전기적으로 접속시킨다. 박막 저항기(1362, 1364, 1366)는 도 9 및 도 10에서 도시된 분로 저항기(990)를 구현한다.

- [0070] 본원은 본 발명의 전형적인 실시예 및 적용에 대해 기술되어 있지만, 본 발명은 전형적인 실시예 및 적용에 제한되는 것은 아니며, 전형적인 실시예 및 적용이 동작하는 방법으로 제한되는 것도 아니다. 실제로, 전형적인 실시예에서 다양한 변화 및 변경이 가능하다. 예컨대, 전술한 실시예는 도 5에서 도시된 프로브 카드 조립체가 아닌 장치 상에 구현될 수 있다. 예컨대, 전술한 실시예는 단일화된 다이들을 테스트하기 위한 로드 보드(load board) 상에 구현될 수 있다. 다른 예로서, 실시예는 도 5에서 도시된 전형적인 프로브 카드 조립체보다 더 많거나 더 작은 수의 소자를 포함하는 프로브 카드 조립체와 같이, 상이한 유형의 프로브 카드 조립체 상에서 구현될 수 있다(예컨대, 인터포저가 없거나, 인터포저 및 프로브 기판이 없는(프로브(530)가 프로브 보드(502)에 직접 부착되는 경우) 프로브 카드 조립체).

## 도면의 간단한 설명

- [0022] 도 1은 종래의 전형적인 테스트 시스템을 도시한다.

- [0023] 도 2는 도 1의 테스트 시스템의 일부 구성요소들의 간략화된 블록도이다.

- [0024] 도 3은 도 2에서 도시된 테스트 시스템의 부분도(partial view)이다.

- [0025] 도 4는 테스트 시스템이 동작하는 주파수를 증가시키기 위해 테스트 시스템에 분로 저항기가 포함되는 발명의 전형적인 제1 실시예이다.

- [0026] 도 5는 전형적인 프로브 카드 조립체(assembly)를 도시한다.

- [0027] 도 6a 및 6b는 도 5의 프로브 보드의 상부도(top view) 및 하부도(bottom view)이다.

- [0028] 도 7a 및 7b는 도 5의 인터포저(interposer)의 상부도 및 하부도이다.

- [0029] 도 8a 및 8b는 도 5의 프로브 기판의 상부도 및 하부도이다.

- [0030] 도 9는 테스트 시스템이 동작하는 주파수를 증가시키기 위해 테스트 시스템에 분로 저항기가 포함되는 발명의 전형적인 제2 실시예이다.

- [0031] 도 10은 테스트 데이터를 하나 이상의 테스트되는 장치에 팬 아웃(fan out) 하는 테스트 시스템에서의 분로 저항기의 사용을 도시한다.

- [0032] 도 11a는 도 10의 테스트 시스템에서의 사용을 위한 프로브 카드 조립체를 위해 구성되는 프로브 기판의 상부 사시도(perspective view)이다.

- [0033] 도 11b는 도 11a의 프로브 기판의 하부 사시도이다.

- [0034] 도 12는 도 11a의 프로브 기판을 구성하는 두 층 사이의 계면(interface)을 도시한다.

- [0035] 도 13a는 프로브 기판 일부의 획단면의 상부 사시도이다.

- [0036] 도 13b는 도 13a의 프로브 기판 일부의 하부도이다.

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

도면6a

도면6b

도면7a

도면7b

도면8a

## 도면8b

## 도면9

### 도면10

도면11a

도면11b

도면12

도면13a

도면13b