## **PCT**

# WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification 5:

G06F 11/00

A1

(11) International Publication Number: WO 93/15459

(43) International Publication Date: 5 August 1993 (05.08.93)

(21) International Application Number: PCT/US93/01051

(22) International Filing Date: 3 February 1993 (03.02.93)

(30) Priority data: 07/829,396 3 February 1992 (03.02.92) US

(71) Applicant: MICRO INDUSTRIES [US/US]; 8399 Green Meadows Drive North, Westerville, OH 43081-9486 (US).

(72) Inventor: FINGER, Roger; 7720 S.W. Linden Road, Portland, OR 97225 (US).

(74) Agent: STANDLEY, Jeffrey, S.; Porter, Wright, Morris & Arthur, 41 South High Street, Columbus, OH 43215 (US).

(81) Designated States: CA, JP, European patent (AT, BE, CH, DE, DK, ES, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

#### Published

With international search report.

(54) Title: LIVE INSERTION OF COMPUTER MODULES

#### MULTIBUS II BACKPLANE INTERCONNECT STRUCTURE

#### (57) Abstract

A method for the insertion or removal of a board (P101) without shutting down system power. A detect signal (DETECT 1\*) indicates the insertion or removal of a board. Once a board has been detected, the slot controller will arbitrate for the bus, wait for existing bus traffic to subside, then power up (PWRCTR1\*) and reset (RST1\*) the new board.

### FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AT | Austria                  | FR  | France                       | MR | Mauritania               |

|----|--------------------------|-----|------------------------------|----|--------------------------|

| ΑU | Australia                | GA  | Gabon                        | MW | Malawi                   |

| BB | Barhados                 | GB  | United Kingdom               | NL | Netherlands              |

| BE | Belgium                  | GN  | Guinea                       | NO | Norway                   |

| BF | Burkina Faso             | GR  | Greece                       | NZ | New Zealand              |

| BC | Bulgaria                 | HU  | Hungary                      | PL | Poland                   |

| Вj | Benin                    | ΙĒ  | Ireland                      | PT | Portugal                 |

| BR | Brazil                   | ΙT  | Italy                        | RO | Romania                  |

| CA | Canada                   | JP  | Japan                        | RU | Russian Federation       |

| CF | Central African Republic | КР  | Democratic People's Republic | SD | Sudan                    |

| CG | Congo                    |     | of Korea                     | SE | Sweden                   |

| CH | Switzerland              | KR  | Republic of Korea            | SK | Slovak Republic          |

| CI | Côte d'Ivoire            | KZ  | Kazakhstan                   | SN | Senegal                  |

| CM | Cameroon                 | LI  | Liechtenstein                | SU | Soviet Union             |

| CS | Czechoslovakia -         | LK  | Sri Lanka                    | TD | C'had                    |

| CZ | Czech Republic           | 1.U | I uxembourg                  | TG | Togo                     |

| DE | Germany                  | MC  | Monaco                       | UA | Ukraine                  |

| DK | Denmark                  | MG  | Madagascar                   | US | United States of America |

| ES | Spain                    | ML. | Mali                         | VN | Viet Nam                 |

| Fl | Finland                  | MN  | Mongolia                     |    |                          |

- 1 -

#### LIVE INSERTION OF COMPUTER MODULES

#### BACKGROUND AND SUMMARY OF THE INVENTION

The present invention relates generally to the insertion and the removal of a circuit device into a bus network, and more particularly, but not exclusively, to the insertion and removal of computer modules from a system which is under power.

Computers are becoming an ever increasing part of modern society. There have already been numerous examples where major disruption has occurred when a computer system has failed. Nonstop computer operation is already a requirement for many banks, hospitals, airlines, military applications, and communication systems. Up to now the solution to preventing disruption when a computer system fails is to provide a redundant system in conjunction with a primary system to go into operation when the primary system fails. This requires using two or more independent computer systems linked together. When one fails the other is ready to take its place.

Redundancy is one way of solving the failure problem and there are currently numerous commercial applications of this approach. However, there are drawbacks such as the expense (could be several hundred thousand dollars), the technical

- 2 -

complexity of setting up such a system, and adverse affects on the speed of operation when redundant systems are connected. Examples of reasons for some computer system failures are such things as earthquakes, fires, power disruptions, and communication network failures.

Sometimes only one board or module mounted on a computer backplane may fail while the others remain functional. A computer module may also be replaced simply to change the programming function of the computer system. Conventional computer systems provide power for the boards in the system through connectors in a backplane. The backplane not only provides power to each board but it also provides the signals used to communicate between boards. In the past, in order to insert or remove boards from a system, it was necessary to turn off the main power to the system. In large system configurations or critical real time applications, it is not always possible to shut down a system to add or replace boards. This has resulted in the development of complex redundant systems as described above which allow the user to switch from one system to another to facilitate the upgrade or repair of equipment. The need for equipment that can be easily serviced and maintained without shutting down the entire system is becoming critical.

The present invention facilitates board insertion and removal without shutting down system power. The present

- 3 -

invention is accomplished by: switching of power to the board when it is inserted or removed; and, controlling the communications between boards as the power to the board is turned on and off. To control the power to the board it is necessary to switch all power connections either on or off when there are no board-to-board communications occurring. To accomplish this a controller with a terminal interface will provide the user with the ability to notify the system that a board is to be either inserted or removed and to identify the location. The controller will use a bus master priority scheme to assume control of the board to board communication. Once the controller has secured communications control, it will provide a signal to either turn on or off the power to the appropriate board location and allow board-to-board communications to proceed.

Each family of computer systems typically have a unique definition of the connector associated with a board location in the system. To implement the live insertion feature, the computer system must support multimaster communications capability. Therefore, the present invention should be specifically designed for each family of computers. The specific computer communications system (bus) currently addressed by the present invention is Multibus II. Multibus II is a reliable backplane system which is well suited for multiprocessing. If one node on the backplane fails, it is usually possible for the remainder of the system to continue

- 4 -

functioning in a diminished capacity. Bus traffic can be rerouted to another available server, pending replacement of the faulty module. The present invention enables live insertion (i.e.- while the power remains on) of faulty boards to be replaced. Downtime will be minimal and users of the system which are currently logged on to the system will be allowed to continue their work without significant disruption. The live insertion feature is implemented through an intelligent slot controller module on the backplane. This circuitry is capable of detecting changes in configuration, safely controlling power, and independently resetting a newly-inserted board. The Multibus system architecture also includes firmware which allows the newly-inserted board to run its own diagnostics and locate a boot server so that the entire process can be fully automated. The present live insertion technique is compatible with the firmware which exists on most Multibus II boards. The interconnect subsystem remains unchanged, and boards which implement the Multibus system architecture will function correctly in a special live insertion backplane.

The foregoing and other objects and advantages will become more apparent when viewed in light of the accompanying drawings and following detailed description.

#### BRIEF DESCRIPTION OF THE DRAWINGS

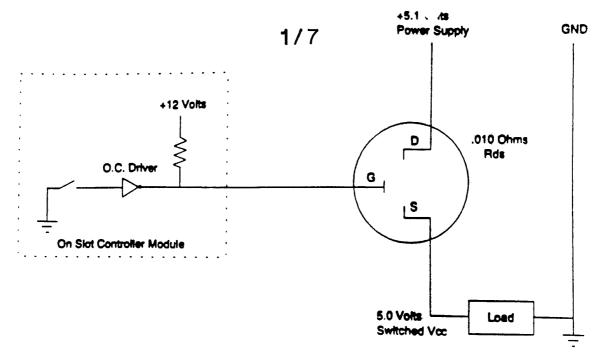

- FIG. 1 is a schematic view of an FET used in the present invention;

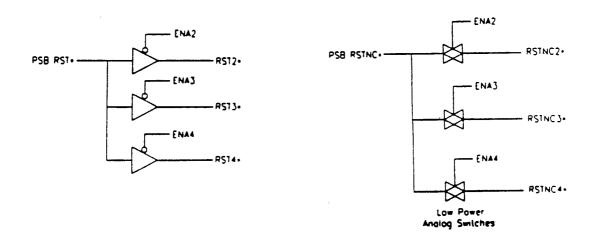

- FIG. 2 is a schematic representation of a slot controller which isolates RST on each board;

- FIG. 3 is a schematic representation of a slot controller which isolates RNC on each board;

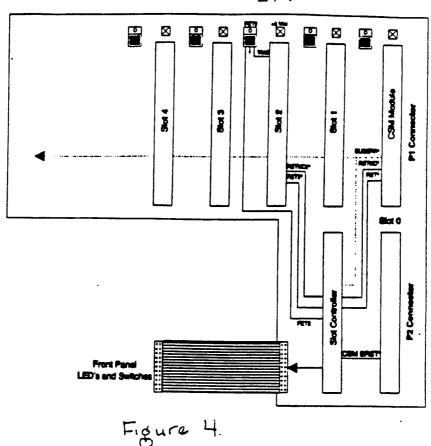

- FIG. 4 is a backplane layout of the present invention;

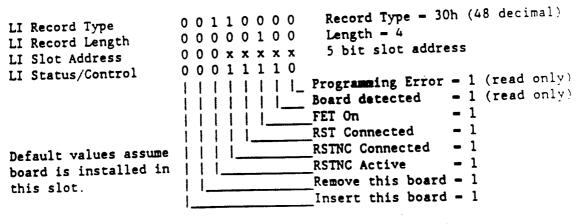

- FIG. 5 is a chart showing the interconnect record for slot control of the present invention;

- FIG. 6 is a view of a front panel of an HBI system having LED's and switches;

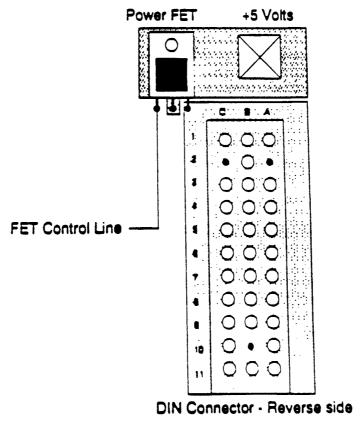

- FIG. 7 is a view of an FET mounting showing power plane connections;

- FIG. 8 is a table showing a MULTIBUS II CENTRAL SERVICES MODULE;

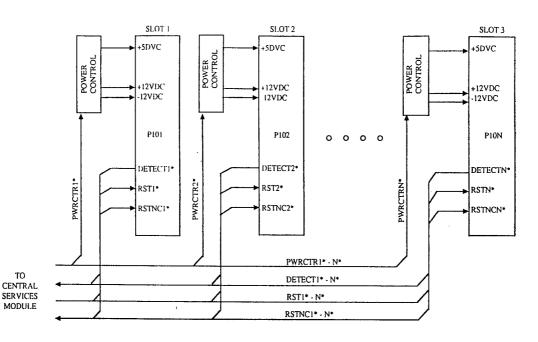

- FIG. 9 is a schematic representation of a Multibus II Backplane Interconnect Structure;

- FIG. 10 is a table showing a Multibus II Central Services Module Connector Specification; and

FIGURE 11 is a table showing a Multibus II Connector Specification.

- 6 -

## DESCRIPTION OF PREFERRED EMBODIMENT(S)

Referring now to the drawings, a preferred feature of the present invention is the ability of the backplane resident slot controller to automatically detect the presence of a new board in the system. This is accomplished by isolating one of the ground pins on the backplane and attaching a pull-up resistor to plus five volts. When a board is inserted, the pin will be grounded and this signal becomes the detect line for the slot controller. Redefinition of a ground pin will cause no incapability or reliability problems since there are fourteen other ground pins on the Pl connector alone. Multibus II uses nine pins for plus five volts and two pins each for plus and minus twelve volts, so there is still ample grounding relative to the number of supply pins. The detect signal allows the slot controller to know within a few microseconds that a board has been inserted or removed. Empty card slots are not supplied with power, so it is safe to insert a board in any open position. Once a board has been detected, the slot controller will arbitrate for the bus, wait for existing bus traffic to subside, then power up and reset the new board.

With most commercial backplanes, the insertion of a board into the system while under power can damage the board and disrupt the operation of the system. There are several possible mechanisms for how this can happen. Component

damage can occur if the ground pins and the signal pins are connected before the power pins, then a device will have voltage applied to its I/O pins before a supply voltage is present. Another possibility is that the plus twelve and plus five voltages make contact before the ground pins. This will lead to a shift in ground potential as the by-pass capacitors charge up. The actual voltage on the ground pins will fall somewhere between plus five and plus twelve volts, depending on the ratio of the capacitances. Damage to on board logic can occur quite rapidly since power to these devices will be reversed. This highlights the need for power sequencing, current limiting, and voltage clamping when boards are inserted into a backplane under power. One solution is to control power on a slot-by-slot basis at the backplane.

An ideal device for this application is a power field effect transistor (FET). One embodiment of an FET is shown in FIG. 1. Power FET's are capable of switching up to fifty amps at fifty volts, and are stable over a broad temperature range. One disadvantage of power FET's is that the internal resistance of the device will cause a slight drop in the supply voltage. This affect can be minimized since FET's with .01 ohm internal resistance are now available. FET's can also be connected in parallel to increase their current handling capacity while reducing the voltage drop due to internal resistance.

- 8 -

The Multibus II reset initialization sequence involves writing a card slot ID and an arbitration ID to each slot in the backplane while the RST (reset) signal is held active low preferably for a minimum of fifty msec. When the RST signal is removed, each board will be driving an open collector RSTNC (reset not complete) signal for a period of time preferably not to exceed thirty seconds. The RSTNC signal tells other bus agents that there are boards in the system which have not yet completed their power-on testing sequence. When a new board is inserted into a system which is already running, the problem becomes how to assign a valid card slot and arbitration ID to the newly inserted board without forcing other boards into a reset cycle. solution is to connect independent RST and RSTNC lines to each slot in the backplane and gather them at the P2 connector of one of the boards in the system. This module would serve as a "slot controller" as shown in FIG. 4. slot controller is also responsible for the FET power controls and the front panel LED's which help guide the operator through a live insertion or removal sequence.

Selective reset works because agents which actually receive the RST signal are receptive to receiving a new arbitration and slot ID. The RST line is isolated from other boards in the system, and they will ignore the reset event, provided there are no other transactions pending on the system bus. The RSTNC signal must also be isolated for each

board because other agents will not resume bus traffic until this line is cleared.

The RST signal is unidirectional (input only) so it may be controlled with a tristate gate or AND gate. RSTNC is bi-directional and therefore much more difficult to control. Various solutions such as relays and FET's have been suggested, but in the preferred embodiment of the present invention analog switches are used. These devices act as interruptable bi-directional lines, however the DC output current is only twenty five m-A much less than the IEEE 1296 specified 60 m-AP. Since the RSTNC signal is no longer bussed, much lighter termination can be used rather than 330 over 220 as is currently specified for RSTNC termination. To reduce pin out requirements of the slot controller, the RST and RNC signals can be combined on a per slot basis. Both pins will be isolated when a live insertion sequence takes place and this board is not selected. FIG's. 2 and 3 show the recommended circuitry for control of RST and RNC for each slot.

As the new board enters the backplane, there will be a small amount of stray capacitance on each of the signal lines (about 20 pf) whether the board is under power or not. If there is active bus traffic while the board is being inserted, there is a possibility of introducing bus errors due to capacitative effects. When a board is inserted or removed, it may glitch the signal lines when power is

disconnected by the FET device, because it is not possible to guarantee the state of the bus transceivers and control lines until operating voltages have stabilized. Ideally, there should be no bus traffic allowed until the new board has completed power on initialization.

The Multibus II arbitration scheme provides a mechanism of insuring the bus is inactive. Under normal operation, a board signals its desire to use the bus by activating an open collector bus request line (BREQ). If more than one request occurs in the same bus cycle, the agent with the higher arbitration ID number wins, and the other agents must wait their turn. Note that because of the principle of fairness, no new arbitration requests can be issued until the bus request line is clear. The slot controller takes advantage of this fact by holding down BREQ as if it were a low priority requesting agent. The slot controller monitors the system control lines until at least two cycles have passed with no bus traffic. This indicates that all existing arbitration requests have been honored, and that the bus will be quiet as long as the slot controller holds BREQ. This works unless the high priority mode of arbitration is used. High priority allows an agent to drive BREQ any time it wants -- potentially in the middle of a live insertion sequence. Fortunately, there is a hardware mechanism which can be used to eliminate (and cancel) all existing bus arbitration requests. The BUSERR line is an open collector bus error

signal which is normally driven by the parity checkers on each board. The effect of a BUSERR is that all boards must remove their arbitration requests from the bus and suspend all activity until the BUSERR is cleared. Once BUSERR is removed, agents can resume arbitration and continue with normal operations. It is preferred to request the bus first using BREQ then after getting the bus grant, drive BUSERR until the live insertion sequence is completed.

In an actual application, a service technician would identify which board has failed by running diagnostics. The service technician would press a momentary contact switch to warn the system that the bus must be cleared. replacement board is inserted or a failed board is removed and the slot controller automatically restarts bus traffic. System downtime could be as short as five seconds or less from a user's perspective. In another embodiment of the present invention, individual on/off switches could be placed at each slot. Signal lines only glitch when they undergo a power transition. The slot controller arbitrates, and gains control of the bus, then power cycles the selected board. This technique is different from the above method in that a board can be placed into any empty slot and it won't turn on until the power switch for that slot is enabled. Likewise, a board can be powered off while the system is running and remain in the card cage until it is removed some time later.

System downtime using this technique could potentially be as little as fifty Msec which is the minimum reset duration.

In one embodiment of the present invention, a full sized Multibus II board was used along with forty six TTL packages. A large gate array or EPLD (erasable programmable logic device) was selected as a cost effective device to control a large number of lines with component count. With the present invention existing computer systems can be retrofit for live insertion by replacing the backplane(s) with a backplane modified as above.

The slot controller is programmed by writing control information to registers and interconnect address space. Only five bytes are needed for a slot address. A second register is used to indicate whether this is an insertion or removal and to indicate system status. This is shown in FIG. 5. For board insertions, it is not necessary to program the slot controller registers, all functions will be handled automatically. Likewise, removals can be done automatically, but the system needs some warning so that the bus can be cleared of traffic. This warning could come from a single systemwide momentary contact switch, or from an interconnect command to power cycle a board. Removal of boards without warning the system should be avoided, but at worst will only cause a BUSERR.

To initiate an HBI event, a system programmer first writes the slot address to interconnect, followed by a

controlled byte to differentiate between insertion or removal and to start the process. An HBI error is signalled if both the removal and insertion bits are set, or if you request removal from an empty slot or insertion in a slot which is currently occupied. An HBI error will also be signalled if an illegal slot number is entered or if you attempt to insert or remove a board in slot 0.

Suggested console commands for initiating a sequence of events which enable board removal and insertion are:

Insert (slot number)

Board Found

Passed Diagnostics

Booting

Complete

WO 93/15459

Remove (slot number)

Check for Removal

Complete.

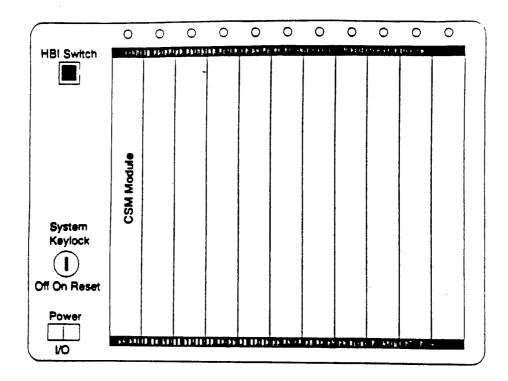

Preferably, the front panel of an HBI system will have LED indicators positioned above each of the card slots so that it is very clear which board has been selected. If spacing is a problem, the LED indicators could be located on the slot controller board, but it is preferable that each slot be clearly numbered to prevent operator confusion. FIG. 6 shows an example of a typical front panel layout.

FIG. 7 shows an example of a backplane layout for placement of the FET device. The drain of the FET should be directly connected to the power supply, and the source to the plus five volt power layer of that slot. A zener diode is

shown as protection for the gate of the FET, however this diode is internal on some types of FET's.

The original specifications of Multibus II were designed to isolate the operation of the system bus from local processors at the board level. This is accomplished with the Message Passing Coprocessor (MPC), which manages system bus traffic rates up to 80 Mbytes per second without intervention from the local processor. The MPC also provides a communications path for a local configuration processor called the interconnect controller. The primary purpose of the interconnect controller is to manage the power-up and reset operation of the board, as well as provide configuration data about the board to the CSM. This makes it possible to implement both the hardware and software requirements of Live Insertion Technology, utilizing the capabilities of the interconnect controller.

The interconnect communication for each board are coordinated by the CSM. To support Live Insertion Technology, the CSM must be able to detect the presence of a board in the system, arbitrate for control of the system bus, switch power on or off to a specific slot and initialize new boards in the system. The Multibus II initialization sequence involves writing a card slot ID and an arbitration ID to each slot in the backplane while the RST\* (RESET) signal is held active low. When the RST\* signal is removed, each board in the system will drive the open collector RSTNC\*

(Reset Not Complete) signal for a period of time up to about 30 seconds. All boards in the system release RSTNC\* to complete the initialization process. By using individual RST\* and RSTNC\* signals for each slot, the CSM can control the initialization process of a board on a slot-by-slot basis. This allows a board inserted into a system to be assigned a slot and arbitration ID without disrupting the operation of other boards in the system. (Table 1)

To initiate the live board insertion process, it is necessary to detect a board when it is inserted into the system. (Figure 2) Board detection is accomplished by isolating one of the ground pins (Al) on the backplane and running individual detect lines to this pin for each slot. The CSM will use a pull-up resistor attached to this line to determine when a board ID is present in the system. Up to 20 boards can be configured in Multibus II system, so the CSM can support up to 20 detect lines.

Once a board is inserted into a Multibus II system and detected by the CSM (Figure 3), the CSM arbitrates for the system bus and suspends system bus communications during the period when power is supplied to the board. Each slot in the system must be powered separately to allow the CSM to manage the insertion and removal process. This requires the CSM to manage 20 signals for power control to each slot. (Table 2) The CSM then initiates the RST\* sequence and monitors the RSTNC\* signal when powered to determine when it is fully

functional. As soon as the RSTNC\* signal is released by the new board, it can be integrated into systems operation.

The process of removing a board from the system relies on the CSM to coordinate activities between system operations and the board to be removed. Interconnect communications are used to identify the board to be powered down and to initiate the CSM board removal sequence. The CSM arbitrates for the system bus, turns off power to the board to be removed, and relinquishes control of the system bus once the board is no longer active. A powered down board can then be removed at any time without impacting system operations.

It is thought that the techniques of the present invention and many of its attendant advantages will be understood from the foregoing description. It will be apparent that various changes may be made in the form and construction of the components thereof without departing from the spirit and scope of the invention or sacrificing all of its material advantages. The form of the invention described herein is merely a preferred or exemplary embodiment.

#### What is Claimed is:

- 1. A method of inserting a circuit device into a bus network of a computer system having a plurality of powered circuit devices interconnected by a communication bus of said network, said method comprising the steps of: providing a controller having means to notify the system that a circuit device is to be inserted; identifying the location for said circuit device in said system; and inserting said circuit device into a slot in a backplane of said system while said system remains powered.

- 2. The method of Claim 1, wherein said means to notify is accomplished by isolating a ground pin on said backplane and attaching a pull-up resistor such that when a circuit device is inserted said pin will be grounded thereby providing a detect signal.

- The method of Claim 1, wherein said circuit device is a printed circuit board.

- 4. The method of Claim 1, further comprising the step of: Controlling power to individual ones of said slots on said backplane.

- 18 -

- 5. The method of Claim 4, wherein a power field effect transistor (FET) is used to control power to said slots.

- 6. The method of Claim 1, wherein said bus is Multibus II.

- 7. The method of Claim 1, wherein said controller is a board of said system having RST and RSTNC lines to each slot in said backplane, gathered at the P2 connector of said board.

- 8. The method of Claim 7, further comprising the steps of: Writing a board slot ID and writing an arbitration ID to each slot while an RST signal is held active low; and removing said RST signal.

**:** .

- 9. The method of Claim 8, further comprising the steps of:

Requesting said bus through one of said boards

activating an open collector bus request line; and

driving an open collector bus error line until the

live insertion sequence is completed.

- 10. The method of Claim 1, further comprising the step of: Providing individual on/off switches at each of said slots.

- 11. A method of removing a circuit device from a bus network having a plurality of powered circuit devices and said circuit device interconnected by a communication bus of said network, said method comprising the steps of:

PCT/US93/01051

Activating a momentary contact switch to warn the system that the bus must be cleared; disconnecting said circuit device from said network; and automatically activating a slot controller to restart bus traffic.

Figure I

Reset Control Circuit

**RSTNC Control Circuit**

Figure 2.

Figure 3.

:" ..

Interconnect Record for Slot Control

Figure 5.

Figure 6.

Figura 7

**►** MULTIBUS II ◆ PWRCTR1\*.N\* - DETECT1\*.N\* RSTNC1 \* - N\* → RSTI\* - N\* BOARD DETECTION PSB INTERFACE BOARD CONTROL BUS TIMING POWER CONTROL Figure 8 MICROCONTROLLER RESET CONTROL AC FAIL DETECT REAL TIME CLOCK STATUS INDICATORS SERIAL PORT 00

MULTIBUS II CENTRAL SERVICES MODULE

SLOT 3

PION

**DETECTN\*** RSTNCN\* +12VDC -12VDC +5DVC RSTN\* CONTROL POWER **₽WRCTRN**∗ 0 MULTIBUS II BACKPLANE INTERCONNECT STRUCTURE 0 0 PWRCTR1\* - N\* DETECT1\* - N\* RSTNC1\*: N\* 0 RST1\* - N\* DETECT2\* SLOT 2 RSTNC2\* +12VDC -12VDC P102 +5DVC RST2\* CONTROL POWER **₽WRCTR2**∗ DETECT1\* SLOT 1 RSTNC1\* +12VDC + -12VDC P101 +5DVC RST1\* CONLKOF FOWER **₽WRCTR1**∗ TO CENTRAL SERVICES MODULE

·;• .:

6/7

|                                                             |                   | Row C          | DETECT3* DETECT6* DETECT9* DETECT12* | DETECT15* DETECT18* +5 Volts  | BCLK3*  | RSTNC3*<br>RSTNC6* | RSTNC9*<br>RSTNC12* | RSTNC15* | RSTNC18* | +5 volts<br>BCLK6* | RST3* | RST6*   | RST9* | RST12*  | RS113*           | +12 volts           | BCLK9* | PWRCTR3* | PWRCTR9* | PWRCTR12*        | PWRCTR15* | PWRCTR18* | -12 volts | CCLK2*     |        |  |

|-------------------------------------------------------------|-------------------|----------------|--------------------------------------|-------------------------------|---------|--------------------|---------------------|----------|----------|--------------------|-------|---------|-------|---------|------------------|---------------------|--------|----------|----------|------------------|-----------|-----------|-----------|------------|--------|--|

| NO                                                          | ATIONS            | Row B          | DETECT2* DETECT5* DETECT8* DETECT8*  | DETECT14* DETECT17* DETECT20* | BCLK2*  | RSTNC2*<br>RSTNC5* | RSTNC8*<br>RSTNC11* | RSTNC14* | RSTNC17* | RSTNC20*<br>BCLK5* | RST2* | RST5*   | RST8* | RST11*  | KS114*<br>PCT17* | RST20*              | BCLK8* | PWRCTR2* | PWRCIR3* | PWRCTR11*        | PWRCTR14* | PWRCTR17* | PWRCTR20* | ('('I.K'I* |        |  |

| SPECIFICATI                                                 | P2 SPECIFICATIONS | Row A          | DETECT1* DETECT4* DETECT7*           | DETECT13* DETECT16* DETECT19* | BCLK1*  | RSTNC1*<br>RSTNC4* | RSTNC7*             | RSTNC13* | RSTNC16* | RSTNC19*<br>BLCK4* | RST1* | RST4*   | RST7* | RST10*  | KS113*           | RST19*              | BCLK7* | PWRCTR1* | PWKC1K4* | PWRCTR 10*       | PWRCTR13* | PWRCTR16* | PWRCTR19* | BCLK10*    |        |  |

| MULTIBUS II CENTRAL SERVICES MODULE CONNECTOR SPECIFICATION |                   | Pin<br>Number  | - 2 & 4                              | 5 7                           | · œ     | 9                  | 11                  | 13       | 14       | 15<br>16           | 17    | 18      | 61    | 20      | 17.              | 23                  | 24     | 25       | 97.6     | 7.8              | 29        | 30        | 31        | 32         |        |  |

| ICES MODULI                                                 |                   |                |                                      |                               |         |                    |                     |          |          |                    |       |         |       |         |                  |                     |        |          |          |                  |           |           | -         |            | 0) 3   |  |

| NTRAL SERV                                                  |                   | Row C          | 0 Volts                              | 0 Volts                       | AD03*   | ADO6*<br>PARO*     | AD10*               | AD15*    | AD16*    | AD19*<br>AD21*     | PAR2* | AD25*   | AD28* | AD30*   | PAR3*            | RESCIVED<br>BUSERR* | ARB4*  | ARB2*    | ARB()*   | 3C / 3           | SC2*      |           |           | 0 Volts    | Figure |  |

| ILTIBUS II CE                                               | FICATIONS         | Row B          | PROT* DCLOW* +5 Battery SDA          | SDB<br>0 Volts<br>AD01*       | 0 Volts | AD05*              | AD09*               | AD14*    | 0 Volts  | AD18*<br>0 Volts   | AD23* | 0 Volts | AD27* | 0 Volts | Reserved         |                     |        | :        | 0 Volts  | o'Co'            | SC3*      |           | *1.JS     | \$C.0+     |        |  |

| MU                                                          | P1 SPECIF         | Row A          |                                      | TIMOUT*                       | AD02*   | AD04*<br>AD07*     | AD08*               | AD13*    | PAR1*    | AD17*<br>AD20*     | AD22* | AD24*   | AD26* | AD29*   | AD31*            | BREQ*               | ARB5*  | ARB3*    | ARB1*    | \$5.50<br>\$5.50 | SC4*      | :         |           | 0 Volts    |        |  |

|                                                             |                   | Pin.<br>Number | 1 2 2 4                              | . 20 20 -                     | - ∞     | 6                  | = 2                 | 13       | 14       | 15<br>16           | 17    | . 81    | 61    | 20      | 21               | 23                  | 24     | 25       | 26       | 77               | 50        | . e.      | 31        | 32         |        |  |

# 7/7

|                                     | <sub>KS</sub>              | Row C          | 0 Volte  | +5 Volts | +12 Volts  | BCLK*   | 0 Volts      | CCLK*   | 0 Volts       | AD03*        | AD06* | PAR0*    | AD10* | AD12*    | AD15* | AD16*   | AD19* | AD21*   | PAR2* | AD25*   | AD28* | AD30*   | PAR3*    | Reserved | BUSERR* | ARB4*    |         | ARB0*   | SC7* | SC5*    | SC2* | -12 Volts  | +5 Volts | 0 Volts |

|-------------------------------------|----------------------------|----------------|----------|----------|------------|---------|--------------|---------|---------------|--------------|-------|----------|-------|----------|-------|---------|-------|---------|-------|---------|-------|---------|----------|----------|---------|----------|---------|---------|------|---------|------|------------|----------|---------|

|                                     | CIFICATION                 | Row B          | PR0T*    | DCL0W*   | +5 Battery | SDA     | SDB          | 0 Volts | <b>AD01</b> * | 0 Volts      | AD05* | +5 Volts | AD09* | +5 Volts | AD14* | 0 Volts | 4D18* | 0 Volts | AD23* | 0 Volts | AD27* | 0 Volts | Reserved | +5 Volts | RSTN*   | +5 Volts | RSTNCN* | 0 Volts | SC8* | 0 Volts | SC3* | +5 Battery | SC1*     | SC:0*   |

| NOI                                 | PROPOSED PI SPECIFICATIONS | Row A          | DETECTN* | +5 Volts | +12 Volts  | 0 Volts | *TUOMIT      | LACHn*  | AD00*         | AD02*        | AD04* | AD07*    | AD08* | AD11*    | AD13* | PAR1*   | AD17* | AD20*   | AD22* | AD24*   | AD26* | AD29*   | AD31*    | +5 Volts | BREQ*   | ARB5*    | ARB3*   | ARB1*   | *62S | SC6*    | SC4* | -12 Volts  | +5 Volts | 0 Volts |

| SPECIFICATI                         | 짋                          | Pin.<br>Number | -        | . 2      | 3          | 4       | 5            | 9       | 7             | <b>&amp;</b> | 6     | 01       | 11    | 12       | 13    | 14      | 15    | 91      | 1.1   | 18      | 16    | 20      | 21       | 22       | 23      | 24       | 25      | 26      | 27   | 28      | 56   | 30         | 31       | 32      |

| MULTIBUS II CONNECTOR SPECIFICATION |                            | Row C          | 0 Volts  | +5 Volts | +12 Volts  | BCLK*   | 0 Volts      | CCLK    | 0 Volts       | AD03*        | AD06* | PAR0*    | AD10* | ADI2*    | AD15* | AD16*   | AD19* | AD21*   | PAR2* | AD25*   | AD28* | AD30*   | PAR3*    | Reserved | BUSERR* | ARB4*    | ARB2*   | ARB()*  | SC7* | SC5*    | SC2* | -12 Volts  | +5 Volts | 0 Volts |

| 2                                   | CIFICATIONS                | Row B          | PROT*    | DCLOW*   | +5 Battery | SDA     | SDB          | 0 Volts | 4D01*         | 0 Volts      | AD05* | +5 Volts | AD09* | +5 Volts | AD14* | 0 Volts | AD18* | 0 Volts | AD23* | 0 Volts | AD27* | 0 Volts | Reserved | +5 Volts | RST*    | +5 Volts | RSTNC*  | 0 Volts | SC8* | 0 Volts | SC3* | +5 Battery | SC1*     | +0.3S   |

|                                     | CURRENT PL SPECIFICATIONS  | Row A          | O Volte  | +5 Volts | +12 Volts  | 0 Volts | *TUMIT*      | LACHn*  | <b>AD00</b> * | AD02*        | AD04* | AD07*    | AD08* | AD11*    | AD13* | PAR1*   | AD17* | AD20*   | AD22* | AD24*   | AD26* | AD29*   | AD31*    | +5 Volts | BREQ*   | ARB5*    | ARB3*   | ARB1*   | *62S | SC6*    | SC4* | -12 Volts  | +5 Volts | 0 Volts |

|                                     | a                          | Pin<br>Number  | -        | 2        | ٠,         | 4       | · <b>v</b> 7 | . 9     | 7             | 8            | 6     | 10       | 11    | 12       | 13    | 14      | 15    | 16      | 17    | 18      | 19    | 20      | 21       | 22       | 23      | 24       | 25      | 26      | 27   | 28      | 29   | 30         | 31       | Ç       |

Figure 11

P

٠.

## INTERNATIONAL SEARCH REPORT

International application No. PCT/US93/01051

|                     | SIFICATION OF SUBJECT MATTER                                                                           |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|--|--|--|

| He CI ·             | G06F 11/00<br>395/575                                                                                  |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| According to        | International Patent Classification (IPC) or to both na                                                | ational classification and IPC                                                   |                                                                     |  |  |  |  |  |  |  |

|                     | DS SEARCHED                                                                                            |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| Minimum do          | cumentation searched (classification system followed l                                                 | by classification symbols)                                                       |                                                                     |  |  |  |  |  |  |  |

|                     | 95/575 395/575,750; 364/231.31,935.4                                                                   |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| Documentati         | on searched other than minimum documentation to the                                                    | extent that such documents are included                                          | in the fields searched                                              |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     | in the second from                                                                                     | as of data base and, where practicable                                           | search terms used)                                                  |  |  |  |  |  |  |  |

|                     | ata base consulted during the international search (nam                                                | le of data base and, where procheders,                                           |                                                                     |  |  |  |  |  |  |  |

| Please See          | Extra Sheet.                                                                                           |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| C. DOC              | UMENTS CONSIDERED TO BE RELEVANT                                                                       |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| Category*           | Citation of document, with indication, where app                                                       | propriate, of the relevant passages                                              | Relevant to claim No.                                               |  |  |  |  |  |  |  |

| Y                   | "An Introduction To Operating Systems                                                                  | " Second Edition by Harvey                                                       | 1-11                                                                |  |  |  |  |  |  |  |

| 1                   | M. Deitel 1990 by Addison-Wesley Pu                                                                    | blishing Company, Inc. pp.                                                       |                                                                     |  |  |  |  |  |  |  |

|                     | 536.                                                                                                   |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| Y                   | "Computer Architecture And Organizat                                                                   | ion" Second Edition by John                                                      | 1-11                                                                |  |  |  |  |  |  |  |

|                     | P. Hayes 1988 by McGraw-Hill Inc. pp. 484-491.                                                         |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        | Turn 1000 Can Cal 9 lines                                                        | 1 11                                                                |  |  |  |  |  |  |  |

| Α                   | US,A, 4,750,136 (Arpin et al.) 07 I                                                                    | June 1988 See Col. 8, lines                                                      | 1-11                                                                |  |  |  |  |  |  |  |

|                     | 17-62.                                                                                                 |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     | 770 4 4 925 727 (Homic et al.) 30                                                                      | May 1080 See Col 3 lines                                                         | 1-11                                                                |  |  |  |  |  |  |  |

| A                   | US,A, 4,835,737 (Herrig et al.) 30                                                                     | Way 1989 See Coi. 5, mies                                                        | 1 11                                                                |  |  |  |  |  |  |  |

|                     | 23-50.                                                                                                 |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        |                                                                                  |                                                                     |  |  |  |  |  |  |  |

| Furt                | her documents are listed in the continuation of Box C                                                  | . See patent family annex.                                                       |                                                                     |  |  |  |  |  |  |  |

| * s                 | pecial categories of cited documents:                                                                  | "T" inter document published after the indate and not in conflict with the appli | ternational filing date or priority                                 |  |  |  |  |  |  |  |

| •A• d               | ocument defining the general state of the art which is not considered                                  | principle or theory underlying the in                                            | vention                                                             |  |  |  |  |  |  |  |

|                     | be part of particular relevance<br>arlier document published on or after the international filing date | "X" document of particular relevance; t                                          | he claimed invention cannot be<br>ered to involve an inventive step |  |  |  |  |  |  |  |

| l.,. ,              | ocument which may throw doubts on priority claim(s) or which is                                        | when the document is taken alone                                                 |                                                                     |  |  |  |  |  |  |  |

| l c                 | ited to establish the publication date of another citation or other<br>pecial reason (as specified)    | "Y" document of particular relevance; t<br>considered to involve an inventiv     | e step when the document is                                         |  |  |  |  |  |  |  |

|                     | ocument referring to an oral disclosure, use, exhibition or other                                      | combined with one or more other su<br>being obvious to a person skilled in       | ch documents, such combination                                      |  |  |  |  |  |  |  |

| P d                 | ocument published prior to the international filing date but later than<br>be priority date claimed    | *&* document member of the same pater                                            | at family                                                           |  |  |  |  |  |  |  |

|                     | e actual completion of the international search                                                        | Date of mailing of the international se                                          | earch report                                                        |  |  |  |  |  |  |  |

|                     | .CH 1993                                                                                               | 19 APR 1993                                                                      |                                                                     |  |  |  |  |  |  |  |

|                     |                                                                                                        | Authorized officer                                                               | ie Wille                                                            |  |  |  |  |  |  |  |

| Name and<br>Commiss | mailing address of the ISA/US ioner of Patents and Trademarks                                          |                                                                                  | ce www                                                              |  |  |  |  |  |  |  |

| Box PCT             |                                                                                                        | VINCENT CANNEY                                                                   |                                                                     |  |  |  |  |  |  |  |

|                     | No. NOT APPLICABLE                                                                                     | Telephone No. (703) 305-9682                                                     |                                                                     |  |  |  |  |  |  |  |

## INTERNATIONAL SEARCH REPORT

International application No. PCT/US93/01051

|   |      |    |     | _ |    |    |

|---|------|----|-----|---|----|----|

| R | FIFE | פח | SFA | R | СН | ED |

Electronic data bases consulted (Name of data base and where practicable terms used):

APS L1 S(BOZRO? (5A) REMOVE?)

- L2 S(POWER AND RESET)

- L3 S L1 & L2

- L4 S(INSERT? OR INSTALL?) AND SLOT

- L5 S L3 & L4

Form PCT/ISA/210 (extra sheet)(July 1992)\*