(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7090412号

(P7090412)

(45)発行日 令和4年6月24日(2022.6.24)

(24)登録日 令和4年6月16日(2022.6.16)

(51)国際特許分類

|         |                 |     |         |              |

|---------|-----------------|-----|---------|--------------|

| G 0 9 G | 3/3233(2016.01) | F I | G 0 9 G | 3/3233       |

| G 0 9 G | 3/20 (2006.01)  |     | G 0 9 G | 3/20 6 1 1 D |

|         |                 |     | G 0 9 G | 3/20 6 1 1 H |

|         |                 |     | G 0 9 G | 3/20 6 2 4 B |

|         |                 |     | G 0 9 G | 3/20 6 4 1 D |

請求項の数 9 (全21頁) 最終頁に続く

(21)出願番号 特願2017-209327(P2017-209327)

(22)出願日 平成29年10月30日(2017.10.30)

(65)公開番号 特開2019-82548(P2019-82548A)

(43)公開日 令和1年5月30日(2019.5.30)

審査請求日 令和2年10月12日(2020.10.12)

前置審査

(73)特許権者 316005926

ソニーセミコンダクタソリューションズ

株式会社

神奈川県厚木市旭町四丁目14番1号

(74)代理人 110002147

特許業務法人酒井国際特許事務所

豊村 直史

神奈川県厚木市旭町四丁目14番1号

ソニーセミコンダクタソリューションズ

株式会社内

塚本 丈二

審査官

最終頁に続く

(54)【発明の名称】 画素回路、表示装置、画素回路の駆動方法および電子機器

## (57)【特許請求の範囲】

## 【請求項1】

発光素子と、

前記発光素子のアノードにソースが接続される駆動トランジスタと、

前記駆動トランジスタのゲートにソースが接続され、前記駆動トランジスタへ書き込まれる信号電圧をサンプリングするサンプリングトランジスタと、

所定のタイミングで前記発光素子のアノードを所定の電位にリセットするリセットトランジスタと、

前記駆動トランジスタのドレインにソースが接続され、前記発光素子が発光する期間においてオフからオンに切り替わる発光制御トランジスタと、

を備え、

前記リセットトランジスタは、前記駆動トランジスタへの前記信号電圧の書き込み前にオンからオフに切り替わり、該切り替わりの後で前記駆動トランジスタへの前記信号電圧の書き込みが行われている間にオフからオンに切り替わり、該書き込みの後にオンからオフに切り替わる、画素回路。

## 【請求項2】

前記リセットトランジスタは、前記サンプリングトランジスタがオフからオンに切り替わって前記駆動トランジスタへの前記信号電圧の書き込みが行われている間にオフからオンに切り替わる、請求項1に記載の画素回路。

## 【請求項3】

前記リセットトランジスタは、前記駆動トランジスタへの前記信号電圧の書き込みが終わり、前記サンプリングトランジスタがオンからオフに切り替わった後にオンからオフに切り替わる、請求項1または2に記載の画素回路。

【請求項4】

前記発光制御トランジスタは、Pチャネル型のトランジスタである、請求項1に記載の画素回路。

【請求項5】

前記リセットトランジスタは、Pチャネル型のトランジスタである、請求項1～4のいずれか1項に記載の画素回路。

【請求項6】

前記駆動トランジスタは、Pチャネル型のトランジスタである、請求項1～5のいずれか1項に記載の画素回路。

10

【請求項7】

請求項1～6のいずれか1項に記載の画素回路が配置される画素アレイ部と、前記画素アレイ部を駆動させる駆動回路と、を備える、表示装置。

【請求項8】

請求項7に記載の表示装置を備える、電子機器。

【請求項9】

発光素子と、

20

前記発光素子のアノードにソースが接続される駆動トランジスタと、前記駆動トランジスタのゲートにソースが接続され、前記駆動トランジスタへ書き込まれる信号電圧をサンプリングするサンプリングトランジスタと、所定のタイミングで前記発光素子のアノードを所定の電位にリセットするリセットトランジスタと、

前記駆動トランジスタのドレインにソースが接続され、前記発光素子が発光する期間においてオフからオンに切り替わる発光制御トランジスタと、を備える画素回路において、

前記駆動トランジスタへの前記信号電圧の書き込み前に前記リセットトランジスタがオンからオフに切り替わることと、

30

前記駆動トランジスタへの前記信号電圧の書き込みが行われている間に前記リセットトランジスタがオフからオンに切り替わることと、

前記書き込みの後に前記リセットトランジスタがオンからオフに切り替わることと、を含む、画素回路の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、画素回路、表示装置、画素回路の駆動方法および電子機器に関する。

【背景技術】

【0002】

近年、表示装置の分野では、発光部を含む画素が行列状（マトリクス状）に配置されて成る平面型（フラットパネル型）の表示装置が主流となっている。平面型の表示装置の一つとして、発光部に流れる電流値に応じて発光輝度が変化する、所謂、電流駆動型の電気光学素子、例えば、有機エレクトロルミネッセンス（Electro Luminescence：EEL）素子を用いる有機EEL表示装置がある。

40

【0003】

この有機EEL表示装置に代表される平面型の表示装置にあっては、電気光学素子を駆動する駆動トランジスタのトランジスタ特性（例えば、閾値電圧）が、プロセスの変動などによって画素毎にばらつく場合がある。その駆動トランジスタの特性の補正動作を行うに当たって、駆動トランジスタのゲートノードに対する初期化電圧の書き込み時間の短縮化を可

50

能にした表示装置の技術が、例えば特許文献 1 に開示されている。

【先行技術文献】

【特許文献】

【0004】

【文献】特開 2015-34861 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

駆動トランジスタの特性の補正動作を行う際に、コントラスト（黒階調における輝度）を改善する為に信号を駆動させると、横クロストークと呼ばれる、白表示部分に輝度差が発生する現象が生じ、横クロストークを改善する為に信号を駆動させると、逆にコントラストが悪化してしまっていた。

10

【0006】

そこで、本開示では、コントラストと横クロストークとを同時に良化させることが可能な、新規かつ改良された画素回路、表示装置、画素回路の駆動方法および電子機器を提案する。

【課題を解決するための手段】

【0007】

本開示によれば、発光素子と、前記発光素子のアノードにソースが接続される駆動トランジスタと、前記駆動トランジスタのゲートにソースが接続され、前記駆動トランジスタへ書き込まれる信号電圧をサンプリングするサンプリングトランジスタと、所定のタイミングで前記発光素子のアノードを所定の電位にリセットするリセットトランジスタと、を備え、前記リセットトランジスタは、前記駆動トランジスタへの前記信号電圧の書き込み前にオンからオフに切り替わり、該切り替わりの後で前記駆動トランジスタへの前記信号電圧の書き込みが行われている間にオフからオンに切り替わり、該書き込みの後で前記発光素子が発光する期間の前にオンからオフに切り替わる、画素回路が提供される。

20

【0008】

また本開示によれば、上記画素回路が配置される画素アレイ部と、前記画素アレイ部を駆動させる駆動回路と、を備える、表示装置が提供される。

【0009】

30

また本開示によれば、上記表示装置を備える、電子機器が提供される。

【0010】

また本開示によれば、発光素子と、前記発光素子のアノードにソースが接続される駆動トランジスタと、前記駆動トランジスタのゲートにソースが接続され、前記駆動トランジスタへ書き込まれる信号電圧をサンプリングするサンプリングトランジスタと、所定のタイミングで前記発光素子のアノードを所定の電位にリセットするリセットトランジスタと、を備える画素回路において、前記駆動トランジスタへの前記信号電圧の書き込み前に前記リセットトランジスタがオンからオフに切り替わることと、前記駆動トランジスタへの前記信号電圧の書き込みが行われている間に前記リセットトランジスタがオフからオンに切り替わることと、前記書き込みの後で前記発光素子が発光する期間の前に前記リセットトランジスタがオンからオフに切り替わることと、を含む、画素回路の制御方法が提供される。

40

【発明の効果】

【0011】

以上説明したように本開示によれば、コントラストと横クロストークとを同時に良化させることが可能な、新規かつ改良された画素回路、表示装置、画素回路の駆動方法および電子機器を提供することが出来る。

【0012】

なお、上記の効果は必ずしも限定的なものではなく、上記の効果とともに、または上記の効果に代えて、本明細書に示されたいずれかの効果、または本明細書から把握され得る他

50

の効果が奏されてもよい。

【図面の簡単な説明】

【0013】

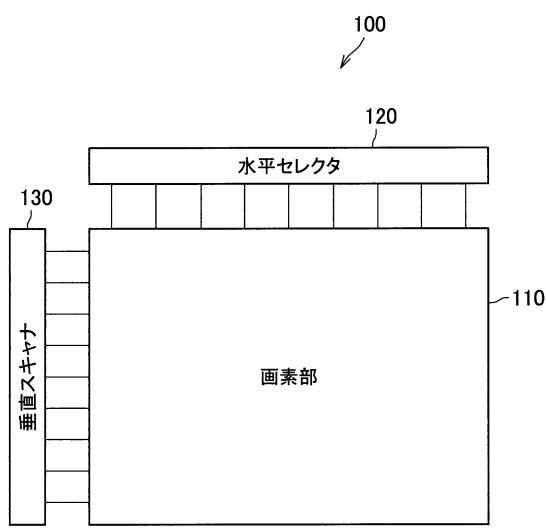

【図1】本開示の実施の形態に係る表示装置100の構成例を示す説明図である。

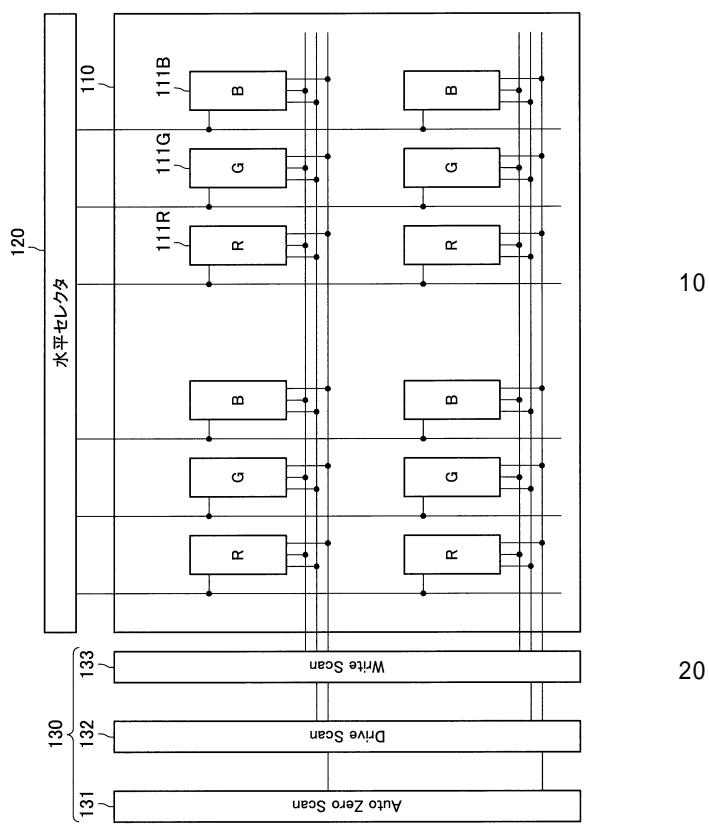

【図2】同実施の形態に係る表示装置100のより詳細な構成例を示す説明図である。

【図3】同実施の形態に係る表示装置100のより詳細な構成例を示す説明図である。

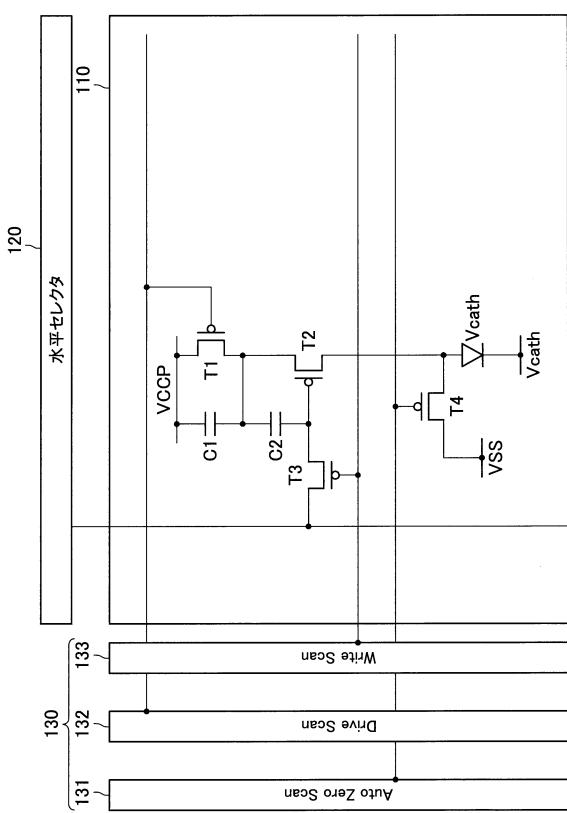

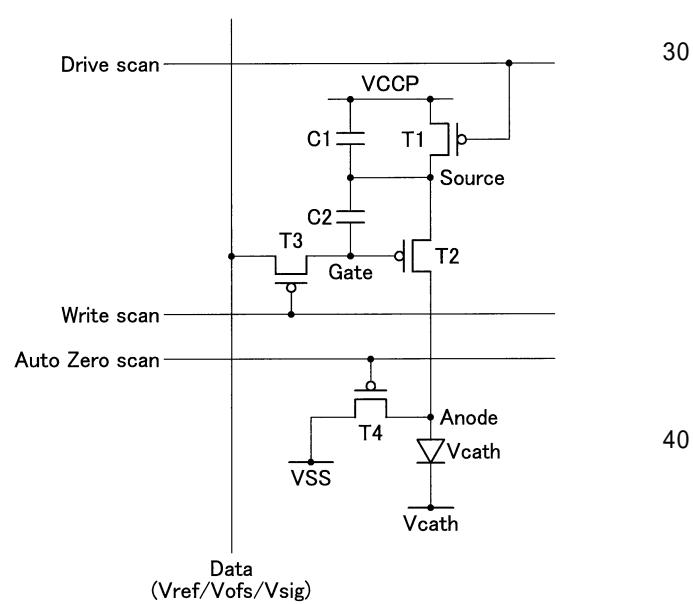

【図4】図3に示した画素回路を抜き出して示した説明図である。

【図5】同実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図6】同実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図7】同実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図8】同実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図9】横クロストークについて説明する説明図である。

【図10】横クロストークについて考察する際に用いる画素回路を示す説明図である。

【図11】同実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図12】同実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図13】本開示の実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。

【図14】同実施の形態に係る表示装置100の駆動方法を示す説明図である。

【図15】同実施の形態に係る表示装置100の駆動方法を示す説明図である。

【図16】同実施の形態に係る表示装置100の画素部110に形成される画素回路の変形例を示す説明図である。

【図17】図16に示した画素回路を駆動させる信号の推移を示す説明図である。

【図18】同実施の形態に係る表示装置100の画素部110に形成される画素回路の変形例を示す説明図である。

【図19】図18に示した画素回路を駆動させる信号の推移を示す説明図である。

【発明を実施するための形態】

【0014】

以下に添付図面を参照しながら、本開示の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0015】

なお、説明は以下の順序で行うものとする。

1. 本開示の実施の形態

1.1. 本開示の表示装置、表示装置の駆動方法、及び、電子機器、全般に関する説明

1.2. 構成例および動作例

1.3. 変形例

2. まとめ

【0016】

<1. 本開示の実施の形態>

[1.1. 本開示の表示装置、表示装置の駆動方法、及び、電子機器、全般に関する説明] 40

本開示の表示装置は、発光部を駆動する駆動トランジスタの他に、サンプリングトランジスタ及び保持容量を有する画素回路が配置されて成る平面型（フラットパネル型）の表示装置である。平面型の表示装置としては、有機EL表示装置、液晶表示装置、プラズマ表示装置などを例示することができる。これらの表示装置のうち、有機EL表示装置は、有機材料のエレクトロルミネッセンスを利用し、有機薄膜に電界をかけると発光する現象を用いた有機EL素子を画素の発光素子（電気光学素子）として用いている。

【0017】

画素の発光部として有機EL素子を用いた有機EL表示装置は次のような特長を持っている。すなわち、有機EL素子が10V以下の印加電圧で駆動できるために、有機EL表示装置は低消費電力である。有機EL素子が自発光型の素子であるために、有機EL表示装

10

20

30

40

50

置は、同じ平面型の表示装置である液晶表示装置に比べて、画像の視認性が高く、しかも、バックライト等の照明部材を必要としないために軽量化及び薄型化が容易である。更に、有機EL素子の応答速度が数マイクロ秒程度と非常に高速であるために、有機EL表示装置は動画表示時の残像が発生しない。

【0018】

有機EL素子は、自発光型の素子であるとともに、電流駆動型の電気光学素子である。電流駆動型の電気光学素子としては、有機EL素子の他に、無機EL素子、LED素子、半導体レーザー素子などを例示することができる。

【0019】

有機EL表示装置等の平面型の表示装置は、表示部を備える各種の電子機器において、その表示部（表示装置）として用いることができる。各種の電子機器としては、テレビジョンシステムの他、ヘッドマウントディスプレイ、デジタルカメラ、ビデオカメラ、ゲーム機、ノート型パーソナルコンピュータ、電子書籍等の携帯情報機器、PDA（Personal Digital Assistant）や携帯電話機等の携帯通信機器などを例示することができる。

10

【0020】

本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、駆動部について、駆動トランジスタのゲートノードをフローティング状態にした後ソースノードをフローティング状態にする構成とすることができる。また、駆動部について、駆動トランジスタのソースノードをフローティング状態にしたままサンプリングトランジスタによる信号電圧の書き込みを行う構成とすることができる。初期化電圧については、信号電圧と異なるタイミングで信号線に供給され、信号線からサンプリングトランジスタによるサンプリングによって駆動トランジスタのゲートノードに書き込まれる構成とすることができる。

20

【0021】

上述した好ましい構成を含む本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、画素回路について、シリコンのような半導体上に形成する構成とすることができる。また、駆動トランジスタについて、Pチャネル型のトランジスタから成る構成とすることができる。駆動トランジスタとして、Nチャネル型のトランジスタではなく、Pチャネル型のトランジスタを用いるのは次の理由による。

30

【0022】

トランジスタをガラス基板のような絶縁体上ではなく、シリコンのような半導体上に形成する場合、トランジスタは、ソース／ゲート／ドレインの3端子ではなく、ソース／ゲート／ドレイン／バックゲート（ベース）の4端子となる。そして、駆動トランジスタとしてNチャネル型のトランジスタを用いた場合、バックゲート（基板）電圧が0Vとなり、駆動トランジスタの閾値電圧の画素毎のばらつきを補正する動作などに悪影響を及ぼすことになる。

【0023】

また、トランジスタの特性ばらつきは、LDD（Lightly Doped Drain）領域を持つNチャネル型のトランジスタに比べて、LDD領域を持たないPチャネル型のトランジスタの方が小さく、画素の微細化、ひいては、表示装置の高精細化を図る上で有利である。このような理由などから、シリコンのような半導体上への形成を想定した場合、駆動トランジスタとして、Nチャネル型のトランジスタではなく、Pチャネル型のトランジスタを用いるのが好ましい。

40

【0024】

上述した好ましい構成を含む本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、サンプリングトランジスタについても、Pチャネル型のトランジスタから成る構成とすることができる。

【0025】

あるいは又、上述した好ましい構成を含む本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、画素回路について、発光部の発光／非発光を制御する発光制御ト

50

ランジスタを有する構成とすることができる。このとき、発光制御トランジスタについても、Pチャネル型のトランジスタから成る構成とすることができる。

【0026】

あるいは又、上述した好ましい構成を含む本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、保持容量について、駆動トランジスタのゲートノードとソースノードとの間に接続された構成とすることができる。また、画素回路について、駆動トランジスタのソースノードと固定電位のノードとの間に接続された補助容量を有する構成とすることができる。

【0027】

あるいは又、上述した好ましい構成を含む本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、画素回路について、駆動トランジスタのドレインノードと発光部のカソードノードとの間に接続されたスイッチングトランジスタを有する構成とすることができる。このとき、スイッチングトランジスタについても、Pチャネル型のトランジスタから成る構成とすることができる。また、駆動部について、発光部の非発光期間にスイッチングトランジスタを導通状態にする構成とすることができる。

10

【0028】

あるいは又、上述した好ましい構成を含む本開示の表示装置、表示装置の駆動方法、及び、電子機器にあっては、駆動部は、スイッチングトランジスタを駆動する信号を、サンプリングトランジスタによる初期化電圧のサンプリングタイミングよりも前にアクティブ状態にする。そして、発光制御トランジスタを駆動する信号をアクティブ状態にした後に非アクティブ状態にする構成とすることができる。このとき、駆動部について、発光制御トランジスタを駆動する信号を非アクティブ状態にする前に、サンプリングトランジスタによる初期化電圧のサンプリングを完了する構成とすることができる。

20

【0029】

[1.2.構成例および動作例]

続いて、本開示の実施の形態に係る表示装置の構成例を説明する。図1は、本開示の実施の形態に係る表示装置100の構成例を示す説明図である。以下、図1を用いて本開示の実施の形態に係る表示装置100の構成例を説明する。

【0030】

画素部110は、有機EL素子その他の自発光素子がそれぞれ設けられた画素がマトリックス状に配置された構成を有する。画素部110は、マトリックス状に配置した画素に対して、走査線がライン単位で水平方向に設けられ、また走査線と直交するように信号線が列毎に設けられる。

30

【0031】

水平セレクタ120は、所定のサンプリングパルスを順次転送し、このサンプリングパルスで画像データを順次ラッチすることにより、この画像データを各信号線に振り分ける。また水平セレクタ120は、各信号線に振り分けた画像データをそれぞれアナログディジタル変換処理し、これにより各信号線に接続された各画素の発光輝度を時分割により示す駆動信号を生成する。水平セレクタ120は、この駆動信号を対応する信号線に出力する。

40

【0032】

垂直スキャナ130は、この水平セレクタ120による信号線の駆動に応動して、各画素の駆動信号を生成して走査線SCNに出力する。これにより表示装置100は、垂直スキャナ130により画素部110に配置された各画素を順次駆動し、水平セレクタ120より設定される各信号線の信号レベルで各画素を発光させ、所望の画像を画素部110で表示する。

【0033】

図2は、本開示の実施の形態に係る表示装置100のより詳細な構成例を示す説明図である。以下、図2を用いて本開示の実施の形態に係る表示装置100の構成例を説明する。

【0034】

画素部110には、赤色を表示する画素111R、緑色を表示する画素111G、青色を

50

表示する画素 111B がマトリクス状に配置されている。

【0035】

そして垂直スキャナ 130 は、オーバーゼロスキャナ 131、駆動スキャナ 132 及び書き込みスキャナ 133 を有する。それぞれのスキャナから信号が画素部 110 にマトリクス状に配置された画素に供給されることで、それぞれの画素に設けられる TFT のオン、オフ動作が行われる。

【0036】

図 3 は、本開示の実施の形態に係る表示装置 100 のより詳細な構成例を示す説明図である。以下、図 3 を用いて本開示の実施の形態に係る表示装置 100 の構成例を説明する。

10

【0037】

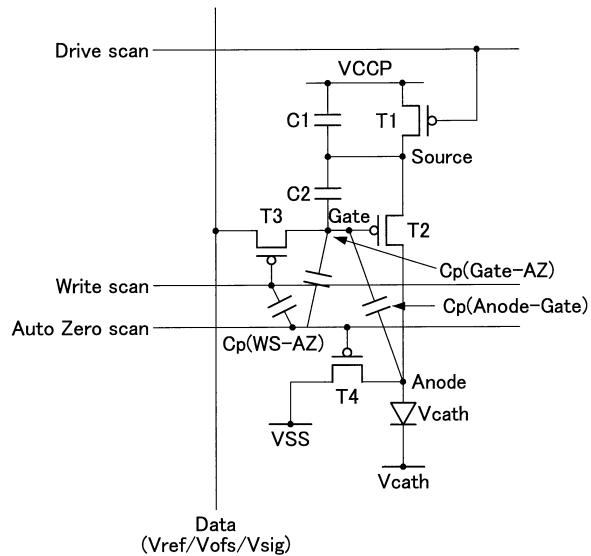

図 3 には、画素部 110 にマトリクス状に配置された 1 つの画素に対する画素回路を図示している。画素回路は、トランジスタ T1 ~ T4 と、キャパシタ C1、C2 と、有機 EL 素子 EL と、を含んで構成される。図 4 は、図 3 に示した画素回路を抜き出して示した説明図である。

【0038】

トランジスタ T1 は有機 EL 素子 EL の発光を制御する発光制御トランジスタである。トランジスタ T1 は、電源電圧 VCCP の電源ノードと、トランジスタ T2 のソースノード（ソース電極）との間に接続され、駆動スキャナ 132 から出力される発光制御信号による駆動の下に、有機 EL 素子 EL の発光 / 非発光を制御する。

【0039】

トランジスタ T2 は、キャパシタ C2 の保持電圧に応じた駆動電流を有機 EL 素子 EL に流すことによって有機 EL 素子 EL を駆動する駆動トランジスタである。

20

【0040】

トランジスタ T3 は、書き込みスキャナ 133 から供給される信号電圧 Vsig をサンプリングすることによって、トランジスタ T2 のゲートノード（ゲート電極）に信号電圧 Vsig を書き込む。

【0041】

トランジスタ T4 は、トランジスタ T2 のドレインノード（ドレイン電極）と電流排出先ノード（例えば、電源 VSS）との間に接続されるリセットトランジスタである。トランジスタ T4 は、オーバーゼロスキャナ 131 からの駆動信号による駆動の下に、有機 EL 素子 EL の非発光期間に有機 EL 素子 EL が発光しないように制御する。トランジスタ T1 ~ T4 は、いずれも P チャネル型のトランジスタから成る構成とすることができる。

30

【0042】

キャパシタ C2 は、トランジスタ T2 のゲートノードとソースノードとの間に接続されており、トランジスタ T3 によるサンプリングによって書き込まれた信号電圧 Vsig を保持する。キャパシタ C1 は、トランジスタ T2 のソースノードと、固定電位のノード（例えば、電源電圧 VCCP の電源ノード）との間に接続されている。このキャパシタ C1 は、信号電圧を書き込んだときにトランジスタ T2 のソース電圧が変動するのを抑制するとともに、トランジスタ T2 のゲートソース間電圧 Vgs をトランジスタ T2 の閾値電圧 Vth にする作用をなす。

40

【0043】

この種の表示装置 100 では、ポリシリコン TFT を用いてガラス基板等による透明絶縁基板上に画素部 110、水平セレクタ 120、垂直スキャナ 130 等がまとめて形成される。ポリシリコン TFT は、しきい値電圧、移動度にばらつきを避け得ず、有機 EL 素子を用いたディスプレイ装置では、これらのばらつきにより画質が劣化する問題がある。

【0044】

そこで、例えば図 4 に示す回路構成により画素回路を構成し、駆動用トランジスタのしきい値電圧、移動度のばらつきを補正することが考えられる。

【0045】

上記の構成の表示装置 100 の駆動方法に関して、まず、本開示の技術（即ち、実施形態

50

に係る駆動方法)よりも前の技術について、比較例に係る駆動方法を説明する。

【0046】

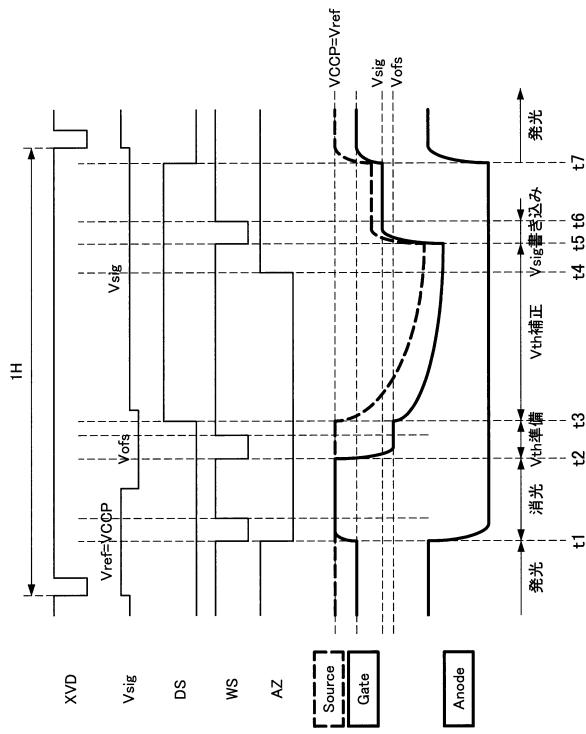

図5は、本開示の実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。図5には、水平同期信号XVD、信号電圧Vsig、駆動スキャナ132からの信号DS、書き込みスキャナ133からの信号WS、オーバーゼロスキャナ131からの信号AZの時間的推移が示されている。また図5には、トランジスタT2のソース電位Sourceおよびゲート電位Gate、ならびに有機EL素子ELのアノード電位Anodeの時間的推移も示されている。

【0047】

時刻t1において信号WS、AZがハイからローになり、発光期間が終了する。AZをハイからローに遷移させるのは、後述のVth補正期間中に有機EL素子ELに電流が流れ込み、有機EL素子ELが発光することを防ぐためである。また、後述のVth補正期間においてコントラストを改善するためにトランジスタT4をオンにするために信号AZがローになる。時刻t1からt2の時間において信号WSが再びハイになり、また信号電圧Vsigが所定の電圧Vofsに低下する。時刻t2において信号WSがローになり、トランジスタT2の閾値電圧の補正の準備期間に入る。ここでトランジスタT2のゲート電位がVofsまで低下する。

10

【0048】

時刻t3になり、信号DSがハイになることでVth補正期間に入る。Vth補正期間において、トランジスタT2のゲートソース間電圧VgsがトランジスタT2の閾値電圧Vthに設定される。また、Vth補正期間の間の時刻t4において信号AZがローからハイになる。

20

【0049】

その後、時刻t5において信号WSがハイからローになり、信号電圧VsigのトランジスタT2への書き込み期間となる。この書き込み期間において、トランジスタT2のゲート電位がVsigになる。時刻t6において信号WSがローからハイになり、信号電圧VsigのトランジスタT2への書き込み期間が終了する。そして時刻t7において信号DSがローになり、トランジスタT1がオンになることで有機EL素子ELが発光する発光期間となる。発光期間では、トランジスタT2のソース電位が電源電圧VCCPとなる。

【0050】

30

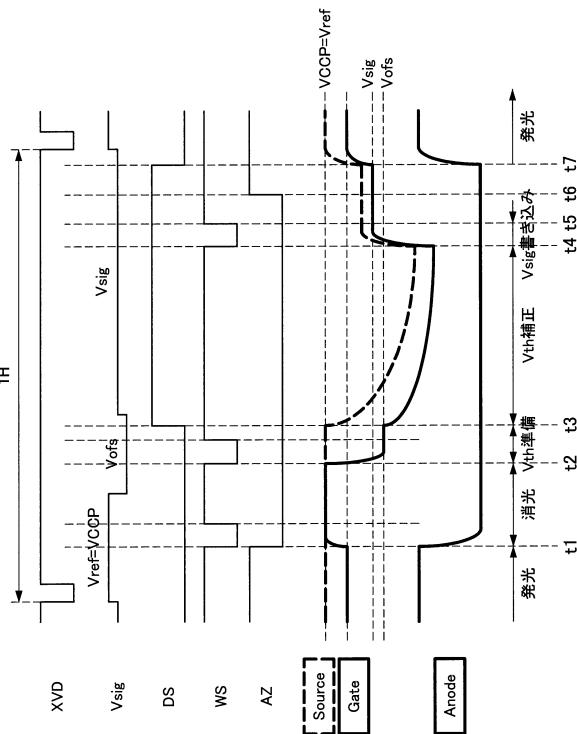

図6は、本開示の実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。図6には、水平同期信号XVD、信号電圧Vsig、駆動スキャナ132からの信号DS、書き込みスキャナ133からの信号WS、オーバーゼロスキャナ131からの信号AZの時間的推移が示されている。また図6には、トランジスタT2のソース電位Sourceおよびゲート電位Gate、ならびに有機EL素子ELのアノード電位Anodeの時間的推移も示されている。

【0051】

図6に示した駆動方法は、図5に示した駆動方法と比較して、信号AZがローからハイになるタイミングがVth補正期間ではなく、信号電圧Vsigの書き込み期間の後になっている。すなわち、時刻t4において信号WSがハイからローになり、信号電圧VsigのトランジスタT2への書き込み期間となり、時刻t5において信号WSがローからハイになり、信号電圧VsigのトランジスタT2への書き込み期間が終了した後に、時刻t6において信号AZがローからハイになる。

40

【0052】

このように、信号AZがローからハイになるタイミングの違いによってVth補正や映像信号の書き込みに影響を及ぼすことはない。ところが、信号AZがローからハイになるタイミングの違いによって、コントラストが悪化したり、横クロストーク現象が生じたりすることが分かっている。具体的には、図5に示したようにVth補正期間で信号AZをローからハイにするとコントラストは悪化、つまり黒輝度が高くなるが、その一方で横クロストーク現象は良化する。反面、図6に示したように信号電圧Vsigの書き込み期間の

50

後に信号 A\_Z をローからハイにすると横クロストークは悪化するが、その一方でコントラストは良化する。このような現象が生じる理由について説明する。

#### 【 0 0 5 3 】

$V_{th}$  補正後、映像信号の書き込み時に、トランジスタ T\_2 のゲートノードには黒電位に相当する信号電圧  $V_{sig}$  が書きこまれる。 $V_{th}$  補正後、映像信号書き込み後のゲートノードの電位を  $V_g'$ 、黒電位に相当する信号電圧  $V_{sig}$  を  $V_{CCP}$  とすると、 $V_g' = V_{CCP}$  となる。ここでトランジスタ T\_2 のゲートノードの電位変動  $V_g$  は、 $V_{th}$  補正後、映像信号書き込み前のゲートノードの電位を  $V_g$  とすると、

$$V_g = V_g' - V_g = V_{CCP} - V_g$$

で表される。

10

#### 【 0 0 5 4 】

一方、キャパシタ C\_2 を介して接続されているトランジスタ T\_2 のソースノードの電位変動  $V_s$  は、キャパシタ C\_1 の容量を  $C_{sub}$ 、キャパシタ C\_2 の容量を  $C_s$ 、トランジスタ T\_1 がオフの時にトランジスタ T\_2 のソースノードの生成される寄生容量を  $C_{ps}$  とすると、

$$V_s = V_g * C_s / (C_s + C_{sub} + C_{ps}) = (V_{CCP} - V_g) * C_s / (C_s + C_{sub} + C_{ps}) \quad \dots \quad (\text{式 1})$$

で表される。

#### 【 0 0 5 5 】

ここで、 $C_s / (C_s + C_{sub} + C_{ps}) < 1$  であるから、トランジスタ T\_2 のソースノードの電位変動  $V_s$  は、ゲートノードの電位変動  $V_g$  より小さくなる。すなわち、トランジスタ T\_2 のゲートノードが電圧  $V_{CCP}$  まで上昇する間に、トランジスタ T\_2 のゲートソース間電圧  $V_{gs}$  は小さくなる。

20

#### 【 0 0 5 6 】

続いて  $V_g'$  とトランジスタ T\_2 のゲートソース間電位の相関について考察する。 $V_{th}$  補正後、映像信号書き込み前の、トランジスタ T\_2 のゲートノード、ソースノード、ゲートソース間電位をそれぞれ  $V_g$ 、 $V_s$ 、 $V_{gs}$ 、映像信号書き込み後の、トランジスタ T\_2 のゲートノード、ソースノード、ゲートソース間電位をそれぞれ  $V_g'$ 、 $V_s'$ 、 $V_{gs}'$  とする。ここで、 $V_{gs} = V_s - V_g$ 、 $V_{gs}' = V_s' - V_g'$  と表される。また映像信号書き込み後の、トランジスタ T\_2 のソースノード電位  $V_s'$  は、

$$V_s' = V_s + (V_g' - V_g) * (C_s / (C_s + C_{sub} + C_{ps}))$$

となる。

30

#### 【 0 0 5 7 】

ここで、 $(C_s / (C_s + C_{sub} + C_{ps})) = (X)$  と表すと、 $V_{gs}' = V_s + (V_g' - V_g) * (X) - V_g' = V_s - ((1 - X)V_g' + V_g(X))$  である。

#### 【 0 0 5 8 】

$V_{gs}$  と  $V_{gs}'$  を比較すると、 $V_g < V_g'$  より、 $V_{gs} > V_{gs}'$  となる。また  $V_g'$  が大きいほど、つまり映像信号書き込み後のゲートノードの電位が高いほど、トランジスタ T\_2 のゲートソース間電位  $V_{gs}'$  が小さくなる。

40

#### 【 0 0 5 9 】

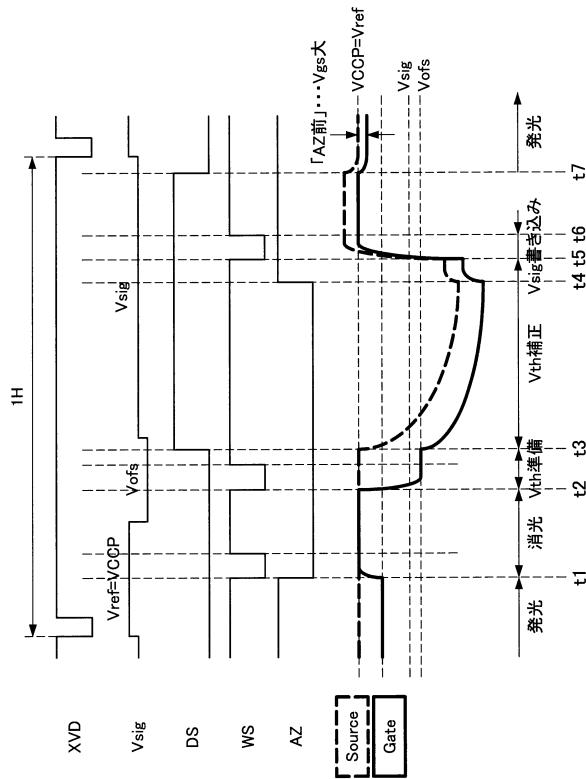

以上を踏まえ、表示装置 100 の駆動とコントラストとの相関について説明する。まず、 $V_{th}$  補正期間で信号 A\_Z をローからハイにする場合について説明する。図 7 は、本開示の実施の形態に係る表示装置 100 の駆動方法の比較例を示す説明図である。図 7 では、 $V_{th}$  補正期間で信号 A\_Z をローからハイにする場合の例が示されている。

#### 【 0 0 6 0 】

$V_{th}$  補正後、 $V_{sig}$  書き込みの前に信号 A\_Z がローからハイに遷移するが、その際、オーバーゼロスキャナ 131 からの信号線 (A\_Z ゲートライン) と、トランジスタ T\_2 のゲートノードとの間に存在する寄生容量  $C_{ps}$  (Gate - A\_Z) を介して、信号 A\_Z の変動

50

がトランジスタ T 2 のゲートノードに入る。信号 A Z の変動によるトランジスタ T 2 のゲート電位の電位変動  $V_g (A Z)$  は、

$$V_g (A Z) = V (A Z) * C_p (Gate - A Z) / (C_p (Gate - A Z) + (1 / C_s) + (1 / C_{sub}) + C_p_g) \dots \text{ (数式3)}$$

で表される。ここで  $V (A Z)$  は信号 A Z の変振幅、 $C_p_g$  はトランジスタ T 3 がオフの時の、トランジスタ T 2 のゲートノードに生成される寄生容量である。

#### 【0061】

その後、トランジスタ T 2 のゲートノードに黒信号が書きこまれ、トランジスタ T 2 のゲートノードの電位が V CCP まで上昇する。

#### 【0062】

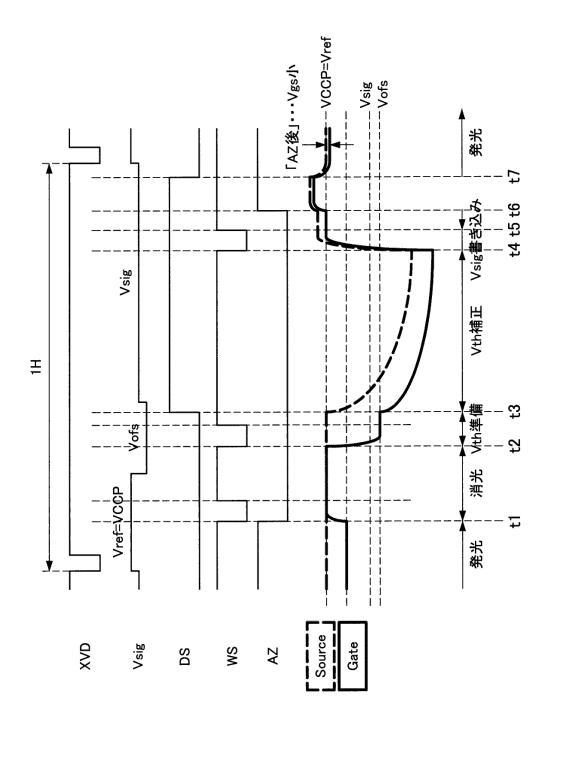

図 8 は、本開示の実施の形態に係る表示装置 100 の駆動方法の比較例を示す説明図である。図 8 では、 $V_{sig}$  書き込みの後に信号 A Z をローからハイにする場合の例が示されている。この場合、トランジスタ T 2 のゲートノードに黒信号が書きこまれ、トランジスタ T 2 のゲートノードの電位が V CCP に変動した後、A Z パルスがハイになることでトランジスタ T 2 のゲートノードの電位が更に上昇する。この場合、 $V_{th}$  補正期間で信号 A Z をローからハイにする場合よりもトランジスタ T 2 のゲートノードの到達電位が高い事が分かる。

#### 【0063】

数式 2 によると、トランジスタ T 2 のゲートノードの到達電位が高いほど、トランジスタ T 2 のゲートソース間電圧  $V_{gs}$  が小さくなる。すなわち、 $V_{th}$  補正期間で信号 A Z をローからハイにする場合より、 $V_{sig}$  書き込みの後に信号 A Z をローからハイにする場合の方が、トランジスタ T 2 のゲートソース間電圧  $V_{gs}$  は小さくなり、黒輝度が低くなる。すなわち、 $V_{sig}$  書き込みの後に信号 A Z をローからハイにする場合の方がコントラストは良化する。

#### 【0064】

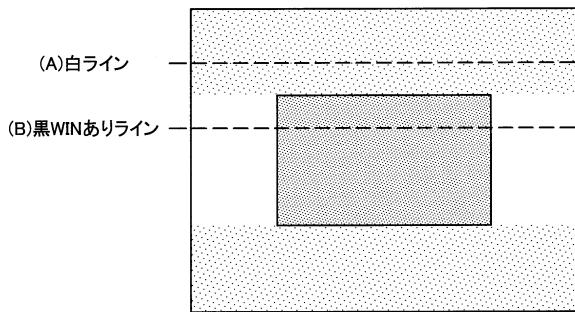

次に、横クロストークについて考察する。図 9 は、横クロストークについて説明する説明図である。図 9 の (A) のラインのように、暗い場所で白い線を表示する場合には問題ないが、(B) のラインのように、白い背景に黒のウインドウのような映像を表示する際に、白い背景の部分に輝度差が発生する現象が横クロストークである。

#### 【0065】

また、図 10 は横クロストークについて考察する際に用いる画素回路を示す説明図であり、信号線とノードとの間に発生する寄生容量を図示したものである。

#### 【0066】

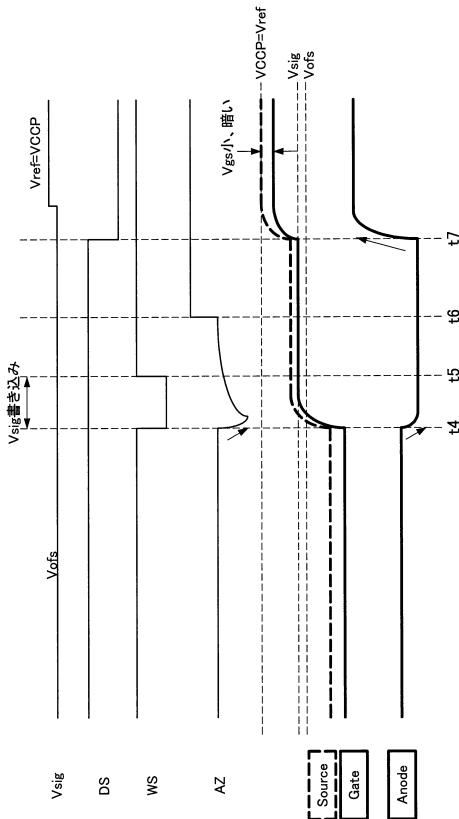

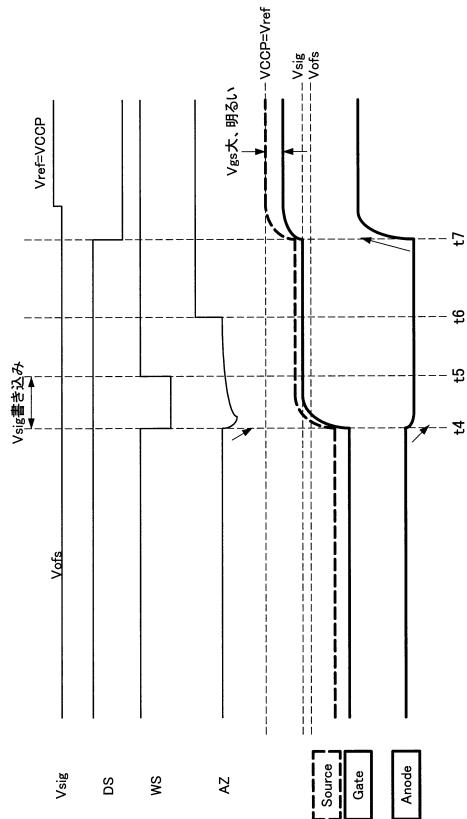

図 11、12 は、本開示の実施の形態に係る表示装置 100 の駆動方法の比較例を示す説明図である。図 11、12 では、 $V_{th}$  補正期間の後で信号 A Z をローからハイにする場合の例が示されている。また図 11 は、図 9 に示した (A) のラインの領域におけるトランジスタ T 2 のゲートノード、ソースノード、有機 EL 素子 EL のアノードノードの電位の変化を示している。そして図 12 は、図 9 に示した (B) のラインの領域におけるトランジスタ T 2 のゲートノード、ソースノード、有機 EL 素子 EL のアノードノードの電位の変化を示している。

#### 【0067】

A Z ゲートラインの電位は、信号 W S のゲートノードへの書き込み前はローの状態となっている。映像信号書き込みのタイミングで、信号 W S がハイからローに遷移すると、書き込みスキヤナ 133 からの信号線 (W S ゲートライン) と A Z ゲートラインとの間に生じている寄生容量  $C_p (W S - A Z)$  を介して、A Z ゲートラインに負のカップリングが入り、信号 A Z の電位が下がる。

#### 【0068】

一方、映像信号書き込み時、トランジスタ T 2 のゲートノードの電位が  $V_{sig}$  に遷移する。このゲートノードの変動により、ゲートノードと A Z ゲートラインとの間に生じている寄生容量  $C_p (Gate - A Z)$  を介して、A Z ゲートラインに正のカップリングが入

10

20

30

40

50

る。このカップリング量は当然映像信号によって変わるが、図9に示した(B)のラインの方が(A)のラインより電圧上昇量が大きい。すなわち、WSゲートラインからの負のカップリングと相殺する為に(B)のラインの方がAZゲートラインの電位の低下が小さくなる。

#### 【0069】

すなわち、(A)のラインは信号書き込み時におけるトランジスタT2のゲートノードの電位の上昇が小さいので、AZゲートラインの電位の低下が大きい。一方、(B)のラインは信号書き込み時におけるトランジスタT2のゲートノードの電位の上昇が大きいので、AZゲートラインの電位の低下が小さい。

#### 【0070】

AZゲートラインの電位が下がることにより、トランジスタT4の動作点が下がり、有機EL素子ELのアノードノードの電位も下がる。トランジスタT4はPチャネルのトランジスタである為、トランジスタT4がオンの時の有機EL素子ELのアノード電位は、トランジスタT4がオンになるAZゲートラインの電位にトランジスタT4の閾値電圧を加えたものである。すなわちトランジスタT4がオン時のAZゲートラインの電位が低下すると、有機EL素子ELのアノード電位もその分低下する。

#### 【0071】

よって(A)のラインの方が(B)のラインよりもAZゲートラインの電位の低下が大きいので、有機EL素子ELのアノード電位も、(A)のラインの方が(B)のラインよりも低下する。

#### 【0072】

その後、発光開始時に有機EL素子ELのアノード電位は有機EL素子ELの発光電位まで上昇する。このアノード電位の変動は、トランジスタT2のゲートノードと有機EL素子ELのアノードとの間に生成する寄生容量Cp(Gate-Anode)を介してGateに正のカップリングを及ぼし、トランジスタT2のゲートノードの電位が上昇する。この時、トランジスタT2のゲートソース間電圧Vgsは小さくなる。このアノード電位の上昇量は、発光前にアノード電位がより下がっている(A)白ラインの方が大きい。すなわち(B)黒ラインよりも(A)白ラインの方が、トランジスタT2のゲートソース間電圧Vgsが小さくなり、よってクロストークが生じる原因となる。

#### 【0073】

図13は、本開示の実施の形態に係る表示装置100の駆動方法の比較例を示す説明図である。図13では、Vth補正期間内で信号AZをローからハイにする場合の例が示されている。また図13は、図9に示した(A)のラインの領域におけるトランジスタT2のゲートノード、ソースノード、有機EL素子ELのアノードノードの電位の変化を示している。

#### 【0074】

Vth補正期間内で信号AZをローからハイにする場合、AZゲートラインの変動までは、図11及び図12を用いて説明したメカニズムと同様である。しかし、Vth補正期間内で信号AZをローからハイにする場合では、その後に信号WSがハイからローになるため、トランジスタT4はオフ状態となっていることで、有機EL素子ELのアノードノードの動作点に影響を及ぼさない。したがって、Vth補正期間内で信号AZをローからハイにする場合、(A)のラインでも(B)のラインでも、アノードノードの電位は変化せず、またその後の発光時においても、トランジスタT2のゲートソース間電圧Vgsは(A)のラインでも(B)のラインでも差が生じない。よって、Vth補正期間内で信号AZをローからハイにする場合では、横クロストークは発生しない。

#### 【0075】

以上説明したように、信号AZがローからハイになるタイミングの違いによって、コントラストが悪化したり、横クロストーク現象が生じたりすることになる。そこで本実施形態に係る表示装置100は、信号AZの遷移タイミングを変化させて、コントラストの良化と横クロストークの抑止の両方を実現する。

10

20

30

40

50

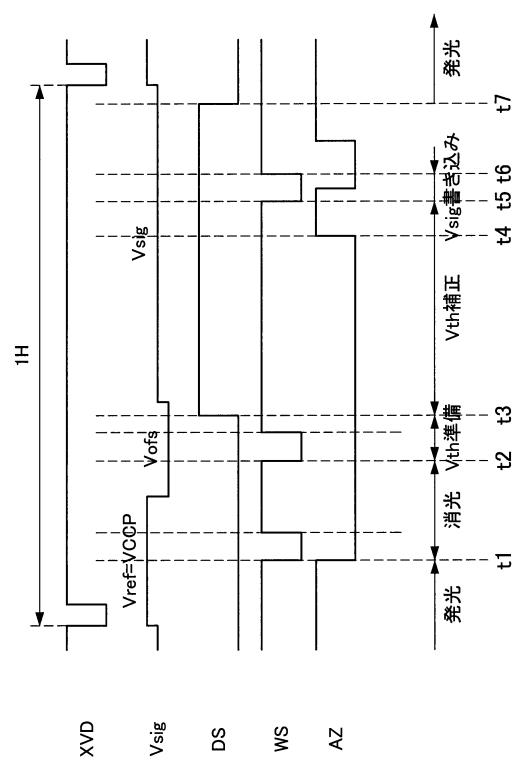

## 【0076】

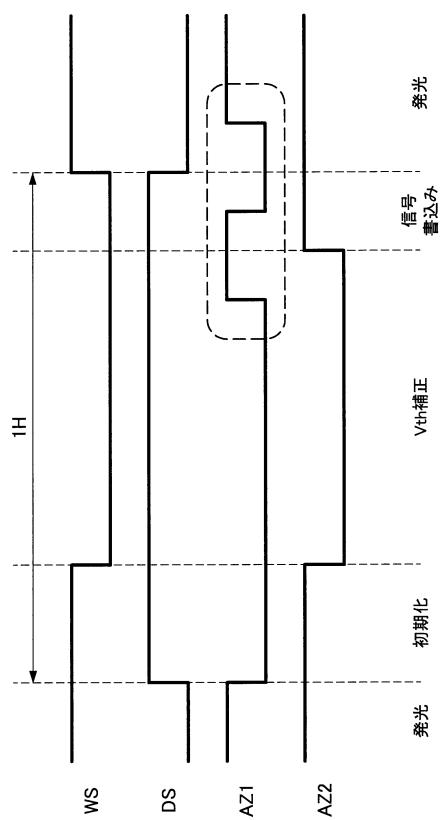

図14は、本開示の実施の形態に係る表示装置100の駆動方法を示す説明図である。図14には、水平同期信号XVD、信号電圧Vsig、駆動スキャナ132からの信号DS、書き込みスキャナ133からの信号WS、オーバーゼロスキャナ131からの信号AZの時間的推移が示されている。

## 【0077】

本開示の実施の形態に係る表示装置100は、図14に示した各信号の時間的推移において、信号AZが、Vth補正期間の間と、映像信号書き込み期間の後の2度、ローからハイに遷移していることを特徴としている。すなわち、信号AZは、Vth補正期間の間にローからハイに遷移した後、映像信号書き込み期間の間にハイからローに戻る。そして信号AZは、映像信号書き込み期間の後に再びローからハイに遷移する。本開示の実施の形態に係る表示装置100は、このように信号AZを遷移させることにより、コントラストの良化と横クロストークの抑止の両方を実現することができる。その原理について説明する。

10

## 【0078】

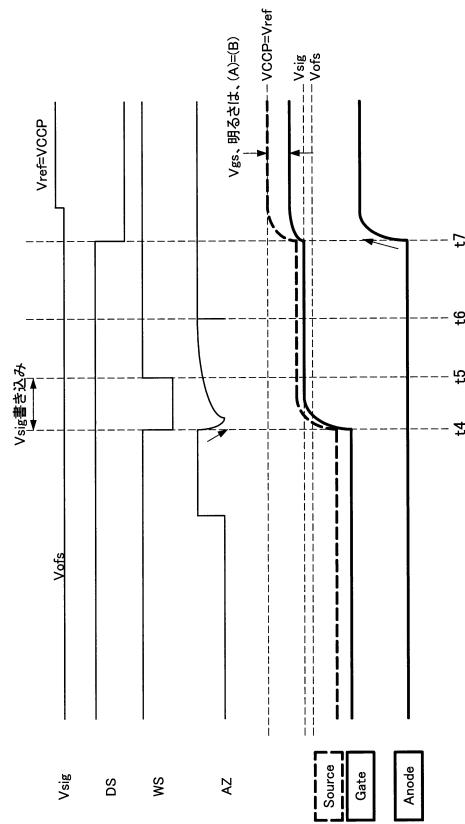

図15は、本開示の実施の形態に係る表示装置100の駆動方法を示す説明図である。図15には、水平同期信号XVD、信号電圧Vsig、駆動スキャナ132からの信号DS、書き込みスキャナ133からの信号WS、オーバーゼロスキャナ131からの信号AZの時間的推移が示されている。また図15は、図9に示した(A)のラインの領域におけるトランジスタT2のゲートノード、ソースノード、有機EL素子ELのアノードノードの電位の変化を示している。

20

## 【0079】

本開示の実施の形態に係る表示装置100は、Vth補正期間の間に信号AZをローからハイに遷移させている。これにより、上述したように、映像信号書き込み時に信号WSがハイからローになっても、トランジスタT4はオフ状態となっていることで、有機EL素子ELのアノードノードの動作点に影響を及ぼさない。

## 【0080】

続いて本開示の実施の形態に係る表示装置100は、映像信号書き込み期間内に、信号AZをハイからローに遷移させている。このタイミングでは、トランジスタT2のゲートノードは映像信号電圧で接地されており、トランジスタT2の動作点に影響を及ぼすことはない。

30

## 【0081】

そして本開示の実施の形態に係る表示装置100は、映像信号書き込み期間が終わった後、発光期間の前に信号AZをローからハイに遷移させている。これにより、上述したようにトランジスタT2のゲートノードに映像信号が書きこまれる。トランジスタT2のゲートノードの電圧VCCPに変動した後、信号AZをローからハイに遷移することで、トランジスタT2のゲートノードが更に上昇するのは上述した通りである。トランジスタT2のゲートノードの到達電位が高いほどトランジスタT2のゲートソース間電圧Vgsが小さくなることから、このように信号AZを遷移させることで、コントラストを良化させることが可能となる。

40

## 【0082】

## [1.3.変形例]

本開示に係る技術は、自発光素子のアノードに、消光用のPチャネル型トランジスタを接続する構成を有する画素回路であれば同様に適用可能である。

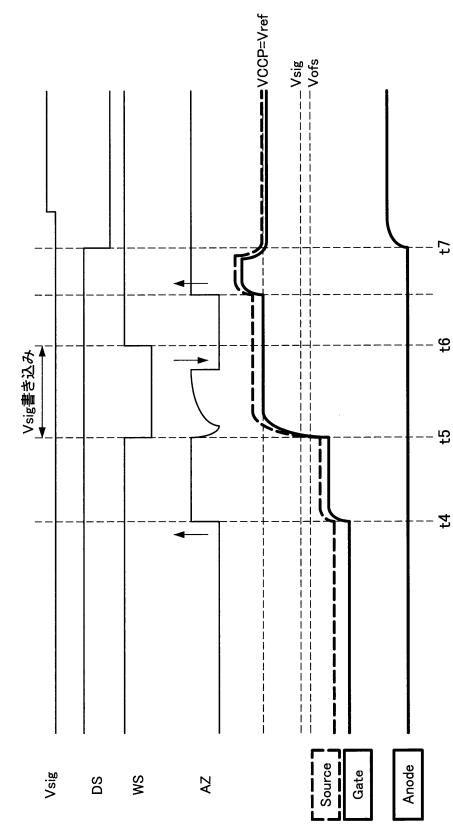

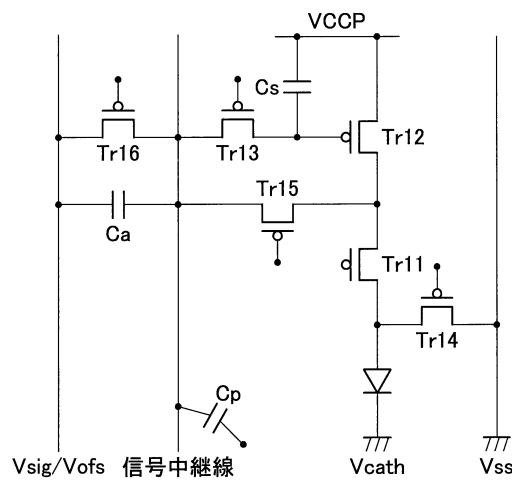

## 【0083】

図16は、本開示の実施の形態に係る表示装置100の画素部110に形成される画素回路の変形例を示す説明図である。図16に示した画素回路は、トランジスタT11～T16と、キャパシタ(寄生容量)Cs、Ca、Cpと、有機EL素子ELと、を含んで構成される。

## 【0084】

50

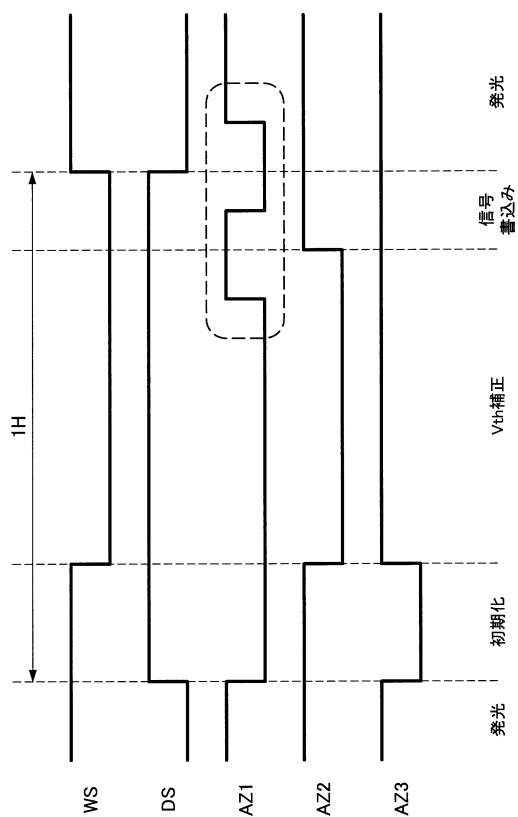

図17は、図16に示した画素回路を駆動させる信号の推移を示す説明図である。WSはトランジスタT13のゲートに供給される信号を、DSはトランジスタT11のゲートに供給される信号を、AZ1はトランジスタT14のゲートに供給される信号を、AZ2はトランジスタT15のゲートに供給される信号を、AZ3はトランジスタT16のゲートに供給される信号を、それぞれ示す。

【0085】

トランジスタT14は、図4等で示したトランジスタT4と同様に、有機EL素子ELの非発光期間に有機EL素子ELが発光しないように制御するものである。従って、トランジスタT14を駆動させるタイミングを制御することで、コントラストの良化と横クロストークの防止の2つの効果をもたらす。

10

【0086】

すなわち、図17に示したように、Vth補正期間内に一度、信号AZ1をローからハイにすることでトランジスタT14をオフし、信号書き込み期間内に信号AZ1をハイからローにすることでトランジスタT14をオンし、信号書き込み期間後に信号AZ1をローからハイにすることでトランジスタT14をオフする。このように信号AZ1を制御することにより、本開示の実施の形態に係る表示装置100は、画素回路として図16に示したような構成を採った場合であっても、コントラストの良化と横クロストークの防止の2つの効果をもたらす。

【0087】

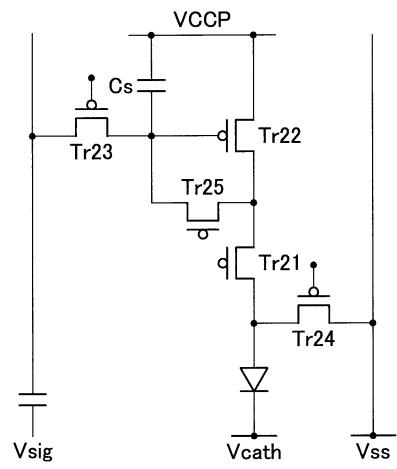

図18は、本開示の実施の形態に係る表示装置100の画素部110に形成される画素回路の変形例を示す説明図である。図18に示した画素回路は、トランジスタT21～T25と、キャパシタCsと、有機EL素子ELと、を含んで構成される。

20

【0088】

図19は、図18に示した画素回路を駆動させる信号の推移を示す説明図である。WSはトランジスタT23のゲートに供給される信号を、DSはトランジスタT21のゲートに供給される信号を、AZ1はトランジスタT24のゲートに供給される信号を、AZ2はトランジスタT25のゲートに供給される信号を、それぞれ示す。

【0089】

トランジスタT24は、図4等で示したトランジスタT4と同様に、有機EL素子ELの非発光期間に有機EL素子ELが発光しないように制御するものである。従って、トランジスタT24を駆動させるタイミングを制御することで、コントラストの良化と横クロストークの防止の2つの効果をもたらす。

30

【0090】

すなわち、図19に示したように、Vth補正期間内に一度、信号AZ1をローからハイにすることでトランジスタT24をオフし、信号書き込み期間内に信号AZ1をハイからローにすることでトランジスタT24をオンし、信号書き込み期間後に信号AZ1をローからハイにすることでトランジスタT24をオフする。このように信号AZ1を制御することにより、本開示の実施の形態に係る表示装置100は、画素回路として図18に示したような構成を採った場合であっても、コントラストの良化と横クロストークの防止の2つの効果をもたらす。

40

【0091】

<2.まとめ>

以上説明したように本開示の実施の形態によれば、自発光素子のアノードに、非発光期間に自発光素子が発光しないように制御するためのトランジスタを設けた画素回路を有する表示装置において、コントラストの良化と横クロストークの防止の2つの効果をもたらす表示装置が提供される。

【0092】

そして、本開示の実施の形態に係る表示装置を備えた電子機器も同様に提供される。本開示の実施の形態に係る表示装置を備えた電子機器は、コントラストの良化と横クロストークの防止の2つの効果を奏する。そのような電子機器には、テレビ、スマートフォン等の

50

携帯電話、タブレット型携帯端末、パーソナルコンピュータ、携帯型ゲーム機、携帯型音楽再生装置、デジタルスチルカメラ、デジタルビデオカメラ、腕時計型携帯端末、ウェアラブルデバイスなどがある。

【0093】

以上、添付図面を参照しながら本開示の好適な実施形態について詳細に説明したが、本開示の技術的範囲はかかる例に限定されない。本開示の技術分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本開示の技術的範囲に属するものと了解される。

【0094】

また、本明細書に記載された効果は、あくまで説明的または例示的なものであって限定的ではない。つまり、本開示に係る技術は、上記の効果とともに、または上記の効果に代えて、本明細書の記載から当業者には明らかな他の効果を奏しうる。

【0095】

なお、以下のような構成も本開示の技術的範囲に属する。

(1)

発光素子と、

前記発光素子のアノードにソースが接続される駆動トランジスタと、

前記駆動トランジスタのゲートにソースが接続され、前記駆動トランジスタへ書き込まれる信号電圧をサンプリングするサンプリングトランジスタと、

所定のタイミングで前記発光素子のアノードを所定の電位にリセットするリセットトランジスタと、

を備え、

前記リセットトランジスタは、前記駆動トランジスタへの前記信号電圧の書き込み前にオンからオフに切り替わり、該切り替わりの後で前記駆動トランジスタへの前記信号電圧の書き込みが行われている間にオフからオンに切り替わり、該書き込みの後で前記発光素子が発光する期間の前にオンからオフに切り替わる、画素回路。

(2)

前記リセットトランジスタは、前記サンプリングトランジスタがオフからオンに切り替わって前記駆動トランジスタへの前記信号電圧の書き込みが行われている間にオフからオンに切り替わる、前記(1)に記載の画素回路。

(3)

前記リセットトランジスタは、前記駆動トランジスタへの前記信号電圧の書き込みが終わり、前記サンプリングトランジスタがオンからオフに切り替わった後にオンからオフに切り替わる、前記(1)または(2)に記載の画素回路。

(4)

前記駆動トランジスタのドレインにソースが接続され、前記発光素子が発光する期間においてオフからオンに切り替わる発光制御トランジスタをさらに備える、前記(1)～(3)のいずれかに記載の画素回路。

(5)

前記発光制御トランジスタは、Pチャネル型のトランジスタである、前記(4)に記載の画素回路。

(6)

前記リセットトランジスタは、Pチャネル型のトランジスタである、前記(1)～(5)のいずれかに記載の画素回路。

(7)

前記駆動トランジスタは、Pチャネル型のトランジスタである、前記(1)～(6)のいずれかに記載の画素回路。

(8)

前記(1)～(7)のいずれかに記載の画素回路が配置される画素アレイ部と、

10

20

30

40

50

前記画素アレイ部を駆動させる駆動回路と、

を備える、表示装置。

( 9 )

前記 ( 8 ) に記載の表示装置を備える、電子機器。

( 10 )

発光素子と、

前記発光素子のアノードにソースが接続される駆動トランジスタと、

前記駆動トランジスタのゲートにソースが接続され、前記駆動トランジスタへ書き込まれる信号電圧をサンプリングするサンプリングトランジスタと、

所定のタイミングで前記発光素子のアノードを所定の電位にリセットするリセットトランジスタと、

10

を備える画素回路において、

前記駆動トランジスタへの前記信号電圧の書き込み前に前記リセットトランジスタがオンからオフに切り替わることと、

前記駆動トランジスタへの前記信号電圧の書き込みが行われている間に前記リセットトランジスタがオフからオンに切り替わることと、

前記書き込みの後で前記発光素子が発光する期間の前に前記リセットトランジスタがオンからオフに切り替わることと、

を含む、画素回路の制御方法。

【符号の説明】

20

【 0 0 9 6 】

1 0 0 : 表示装置

1 1 0 : 画素部

1 1 1 B : 画素

1 1 1 G : 画素

1 1 1 R : 画素

1 2 0 : 水平セレクタ

1 3 0 : 垂直スキャナ

1 3 1 : オー上ゼロスキャナ

1 3 2 : 駆動スキャナ

30

1 3 3 : 書き込みスキャナ

C 1 : キャパシタ

C 2 : キャパシタ

C p : 寄生容量

C s : キャパシタ

D S : 信号

E L : 有機 E L 素子

G a t e : ゲート電位

S C N : 走査線

T 1 : トランジスタ

40

T 2 : トランジスタ

T 3 : トランジスタ

T 4 : トランジスタ

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図9】

【図10】

### 【図11】

【図12】

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図 1 7】

【図 1 8】

10

20

【図 1 9】

30

40

50

## フロントページの続き

## (51)国際特許分類

F I

G 0 9 G 3/20 6 4 2 A

G 0 9 G 3/20 6 4 2 E

## (56)参考文献

特開2016-212418 (JP, A)

特開2014-228863 (JP, A)

特開2010-282223 (JP, A)

特開2011-164133 (JP, A)

特開2008-287140 (JP, A)

特開2008-145647 (JP, A)

特表2011-507005 (JP, A)

米国特許出願公開第2017/0124939 (US, A1)

米国特許出願公開第2016/0005356 (US, A1)

米国特許出願公開第2016/0104423 (US, A1)

米国特許出願公開第2017/0053595 (US, A1)

米国特許出願公開第2016/0125808 (US, A1)

中国実用新案第205920745 (CN, U)

## (58)調査した分野 (Int.Cl. , DB名)

G 0 9 G 3 / 3 2 3 3

G 0 9 G 3 / 2 0

H 0 1 L 2 7 / 3 2

H 0 1 L 5 1 / 5 0