(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6294838号

(P6294838)

(45) 発行日 平成30年3月14日(2018.3.14)

(24) 登録日 平成30年2月23日(2018.2.23)

(51) Int.Cl.

G02B 6/42 (2006.01)

H01L 31/0232 (2014.01)

H01S 5/022 (2006.01)

F 1

G02B 6/42

H01L 31/02

H01S 5/022

C

請求項の数 15 (全 14 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2014-560046 (P2014-560046)  |

| (86) (22) 出願日 | 平成25年2月28日 (2013.2.28)        |

| (65) 公表番号     | 特表2015-511027 (P2015-511027A) |

| (43) 公表日      | 平成27年4月13日 (2015.4.13)        |

| (86) 國際出願番号   | PCT/US2013/028355             |

| (87) 國際公開番号   | W02013/130831                 |

| (87) 國際公開日    | 平成25年9月6日 (2013.9.6)          |

| 審査請求日         | 平成27年12月21日 (2015.12.21)      |

| (31) 優先権主張番号  | 13/410,113                    |

| (32) 優先日      | 平成24年3月1日 (2012.3.1)          |

| (33) 優先権主張国   | 米国(US)                        |

前置審査

|           |                                                                 |

|-----------|-----------------------------------------------------------------|

| (73) 特許権者 | 502303739<br>オラクル・インターナショナル・コーポレーション                            |

| (74) 代理人  | 110001195<br>特許業務法人深見特許事務所                                      |

| (72) 発明者  | ラジ, カナン<br>アメリカ合衆国、92127 カリフォルニア州、サン・ディエゴ、ファルコン・クリスト・ドライブ、16162 |

最終頁に続く

(54) 【発明の名称】高密度に実装された光インターフェクトを有するチップアセンブリ構成

## (57) 【特許請求の範囲】

## 【請求項 1】

チップアセンブリ構成であって、

基板を備え、

前記基板は、第1の表面と、前記基板の、前記第1の表面と反対側の第2の表面とを有し、

第1のコネクタが前記第1の表面上に配置され、

第2のコネクタが前記第2の表面上に配置され、

前記第1のコネクタおよび前記第2のコネクタは、前記基板を通るインターフェクトによって電気的に結合され、

前記第1の表面に隣接するように配置され前記第1のコネクタに電気的に結合された集積回路と、

前記第2の表面に隣接するように配置され前記第2のコネクタに電気的に結合された変換機構とを備え、

前記変換機構は、前記集積回路からの電気信号を対応する第1の光信号に変換し前記集積回路への第2の光信号を対応する第2の電気信号に変換するように構成され、

前記第1の光信号および前記第2の光信号は、前記チップアセンブリ構成の中で光ファイバを用いて伝達され、

前記光ファイバは、前記変換機構に直接結合されており、

前記インターフェクトは、前記集積回路と前記変換機構との間ににおける3つの電気的接

続に対応しており、

前記 3 つの電気的接続は、ドライバまたは受信機への電気的接続、電源への電気的接続および接地への電気的接続を含む、チップアセンブリ構成。

**【請求項 2】**

前記基板は、プリント回路基板およびインターポーザのうちの 1 つを含む、請求項 1 に記載のチップアセンブリ構成。

**【請求項 3】**

前記基板は、半導体、有機材料、セラミック、ガラス、およびプラスチックのうちの 1 つを含む、請求項 2 に記載のチップアセンブリ構成。

**【請求項 4】**

前記光ファイバに光学的に結合された光源および検出器をさらに備える、請求項 1 ~ 3 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 5】**

前記変換機構に熱的に結合された第 1 のヒートシンクをさらに備える、請求項 1 ~ 4 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 6】**

前記第 1 のコネクタと前記集積回路とは、半田およびボールグリッドアレイのうちの 1 つによって電気的に結合されている、請求項 1 ~ 5 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 7】**

前記第 2 のコネクタと前記変換機構とは、半田、ボールグリッドアレイ、ソケット、インターポーザ、およびランドグリッドアレイのうちの 1 つによって電気的に結合されている、請求項 1 ~ 6 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 8】**

前記第 1 のコネクタ、前記第 2 のコネクタ、および前記インターロケクタと関連付けられた電気経路の平均インピーダンスは、前記集積回路および前記変換機構内のドライバの平均インピーダンスとほぼ一致する、請求項 1 ~ 7 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 9】**

前記平均インピーダンスは約 50 である、請求項 8 に記載のチップアセンブリ構成。

**【請求項 10】**

前記第 1 のコネクタおよび前記第 2 のコネクタのうちの 1 つを含み得る所定のコネクタは、前記第 1 の表面および前記第 2 の表面からの信号線によって電気的に結合された 1 つの直線状のビアを含み、

前記ビアは、前記第 1 の表面から前記第 2 の表面まで前記基板を通って延びている、請求項 1 ~ 9 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 11】**

前記集積回路の、前記基板と反対側において、前記集積回路に熱的に結合された第 2 のヒートシンクをさらに備える、請求項 1 ~ 10 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 12】**

所定のインターロケクタは、前記第 1 の表面および前記第 2 の表面のうちの一方にはほぼ平行な領域を含む信号線によって電気的に結合された 2 つのビアを含み、

前記ビアは、その一部が前記基板を通って延びている、請求項 1 ~ 11 のいずれか 1 項に記載のチップアセンブリ構成。

**【請求項 13】**

前記領域の長さは 1 mm 以下である、請求項 12 に記載のチップアセンブリ構成。

**【請求項 14】**

システムであって、

プロセッサと、

10

20

30

40

50

前記プロセッサによって実行されるように構成されたプログラムモジュールを格納するメモリと、

チップアセンブリ構成とを備え、

前記チップアセンブリ構成は、基板を含み、

前記基板は、第1の表面と、前記基板の、前記第1の表面と反対側の第2の表面とを有し、

第1のコネクタが前記第1の表面上に配置され、

第2のコネクタが前記第2の表面上に配置され、

前記第1のコネクタおよび前記第2のコネクタは、前記基板を通るインターロケクタによって電気的に結合され、

10

前記チップアセンブリ構成は、

前記第1の表面に隣接するように配置され前記第1のコネクタに電気的に結合された集積回路と、

前記第2の表面に隣接するように配置され前記第2のコネクタに電気的に結合された変換機構とをさらに含み、

前記変換機構は、前記集積回路からの電気信号を対応する第1の光信号に変換し前記集積回路への第2の光信号を対応する第2の電気信号に変換するように構成され、

前記第1の光信号および前記第2の光信号は、前記チップアセンブリ構成の中で光ファイバを用いて伝達され、

前記光ファイバは、前記変換機構に直接結合されており、

20

前記インターロケクタは、前記集積回路と前記変換機構との間における3つの電気的接続に対応しており、

前記3つの電気的接続は、ドライバまたは受信機への電気的接続、電源への電気的接続および接地への電気的接続を含む、システム。

#### 【請求項15】

チップアセンブリ構成において情報を伝達する方法であって、

前記方法は、集積回路からの電気信号を、前記チップアセンブリ構成内の集積回路に隣接する基板を通る電気経路に駆動することを含み、

前記電気経路は、前記基板の第1の表面上に配置された第1のコネクタと、前記基板の、前記第1の表面と反対側の第2の表面上に配置された第2のコネクタと、前記第1のコネクタと前記第2のコネクタとを電気的に結合する、前記基板を通るインターロケクタとを含み、

30

前記方法は、

前記電気信号を、前記第2の表面に隣接するように配置され前記第2のコネクタに電気的に結合された変換機構で受けることと、

前記変換機構を用いて、前記電気信号を光信号に変換することと、

前記光信号を前記チップアセンブリ構成内の光ファイバで伝達することとをさらに含み、

前記光ファイバは、前記変換機構に直接結合されており、

前記インターロケクタは、前記集積回路と前記変換機構との間における3つの電気的接続に対応しており、

40

前記3つの電気的接続は、ドライバまたは受信機への電気的接続、電源への電気的接続および接地への電気的接続を含む、方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

背景

分野

本開示は、概して、半導体チップを収容するチップアセンブリ構成に関する。より具体的には、本開示は、高密度に実装された光インターロケクトを容易にする短距離伝送線を

50

有する基板を含むチップアセンブリ構成に関する。

**【背景技術】**

**【0002】**

関連技術

集積回路（I C）技術は臨界寸法（critical dimension）の縮小化を進めており、それに伴い、高帯域幅、低レイテンシ、低消費電力、信頼性、および低コスト等の好適な通信および集積化特性を既存の配線で得ることが益々困難になっている。これら課題は、多数のマルチコアプロセッサおよびメモリ間の高速通信を必要とする次世代マルチプロセッサアーキテクチャを含むコンピュータシステムでは特に厳しい。

**【0003】**

コンピュータシステム内のコンポーネント間におけるより高い帯域幅での通信は、インターフェクトの信号線の数の増大および／または1信号線当たりのデータレートの増大によって実現できる。しかしながら、半導体チップ上のピンの数は今のところ、限定されたレジカルサイズ、チップ構成、製造、およびアセンブリの制約によって、制限されている。また、このピンの数の制約は、プロセッサの入出力（I / O）ポートの性能の改善を制限している。たとえば、データレート 20 G b p s 以上の場合、高帯域幅通信に必要な差動ピンの数は 1000 を超えると予測される。

10

**【0004】**

加えて、伝送線におけるデータレートが増すと、有効通信距離が減少する。その原因は、反射、吸収、散乱、クロストーク、トレースの交差、およびチャネル間におけるスキューのばらつきによって生じる、損失である。たとえ低損失（および高コスト）の誘電材料を使用しても、電気伝送線は、有限伝送距離帯域幅の製品である。送信機 F I R フィルタ、アナログ線形等化、適応判定帰還等化、およびタイミングリカバリ等のその他の通信技術を用いて通信性能を改善することは可能であるが、これら通信技術では一般的に消費電力およびレイテンシが増大する。結果として、伝送線のデータレートが制限され、それによって計算システムの性能が一層制限される。

20

**【0005】**

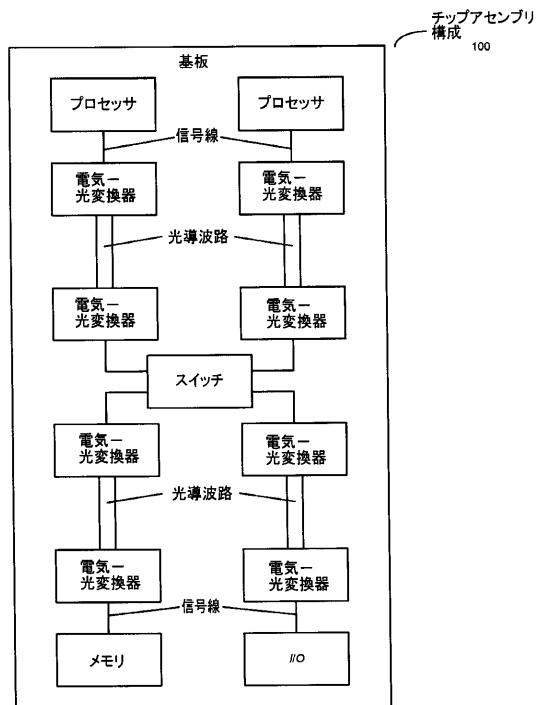

基本的に、光インターフェクトは、上記電気インターフェクトの障害を克服する方法を提供することによって、高帯域幅、長距離にわたる通信、低損失、低クロストーク、低消費電力、および電磁耐性を可能にする。図1は、コンポーネント（プロセッサ、メモリ、ルータ、スイッチ等）間の通信を容易にする光インターフェクトを用いる既存のチップアセンブリ構成 100 の上面図を示すブロック図を示している。

30

**【0006】**

しかしながら、このチップアセンブリ構成にはいくつかの短所がある。特に、光インターフェクトはチップアセンブリ構成における貴重なスペースを占めるので、コストが増す可能性がある。加えて、コンポーネントの密度に制約があるので、コンポーネント間の距離が大きくなる可能性があり、そのためにレイテンシが増す可能性がある。さらに、チップアセンブリ構成内の隣接する光学要素と電気要素の熱管理が難しくなる可能性がある。

**【0007】**

よって、必要なのは上記の問題のないチップアセンブリ構成である。

40

**【発明の概要】**

**【課題を解決するための手段】**

**【0008】**

概要

本開示の一実施の形態は、基板を含むチップアセンブリ構成を提供する。基板は、第1の表面と、この基板の、第1の表面と反対側の第2の表面とを有する。基板はまた、第1の表面上に配置された第1のコネクタと、第2の表面上に配置された第2のコネクタとを含み、第1のコネクタおよび第2のコネクタは、基板を通るインターフェクトによって電気的に結合されている。加えて、チップアセンブリ構成は、第1の表面に隣接するように配置され第1のコネクタに電気的に結合された集積回路を含む。さらに、チップアセンブ

50

リ構成は、第2の表面に隣接するように配置され第2のコネクタに電気的に結合された変換機構を含む。この変換機構は、集積回路からの電気信号を、対応する第1の光信号に変換し、集積回路への第2の光信号を、対応する第2の電気信号に変換する。なお、第1の光信号および第2の光信号は、チップアセンブリ構成の中で光インターフェースを用いて伝達される。

#### 【0009】

加えて、基板は、プリント回路基板および／またはインターポーラを含み得る。たとえば、基板は、半導体、有機材料、セラミック、ガラス、および／またはプラスチックを含み得る。

#### 【0010】

いくつかの実施の形態において、チップアセンブリ構成は、光インターフェースに光学的に結合された光源および検出器を含む。これに代えて、光インターフェースに関連付けられた光源および検出器がチップアセンブリ構成の外部にあってもよい。

#### 【0011】

さらに、光インターフェースは、光ファイバおよび／または光導波路を含み得る。

なお、第1のコネクタと集積回路とは、半田、ボールグリッドアレイ、ソケット、インターポーラ、および／またはランドグリッドアレイによって電気的に結合されてもよい。加えて、第2のコネクタと変換機構とは、半田、ボールグリッドアレイ、ソケット、インターポーラ、および／またはランドグリッドアレイによって電気的に結合されてもよい。

#### 【0012】

いくつかの実施の形態において、第1のコネクタ、第2のコネクタ、およびインターフェースと関連付けられた電気経路の平均インピーダンスは、集積回路および変換機構内のドライバの平均インピーダンスとほぼ一致する。たとえば、この平均インピーダンスは約50Ωであってもよい。さらに、第1のコネクタ、第2のコネクタ、およびインターフェースに関する伝達特性におけるドミナントポールは、集積回路と変換機構との間の10Gb/sを超えるデータレートでの通信を容易にし得る。

#### 【0013】

加えて、チップアセンブリ構成は、集積回路の、基板と反対側において、集積回路に熱的に結合されたヒートシンクを含み得る。

#### 【0014】

いくつかの実施の形態において、所定のインターフェースは、第1の表面および第2の表面のうちの一方にほぼ平行な領域を含む信号線によって電気的に結合された2つのビアを含む。これらのビアは、その一部が基板を通じて延びてもよい。さらに、上記領域の長さは1mm以下であってもよい。

#### 【0015】

ある実施の形態において、所定のコネクタは、第1の表面および第2の表面からの信号線によって電気的に結合された直線状のビアを含み、このビアは、第1の表面から第2の表面まで基板を通じて延びている。

#### 【0016】

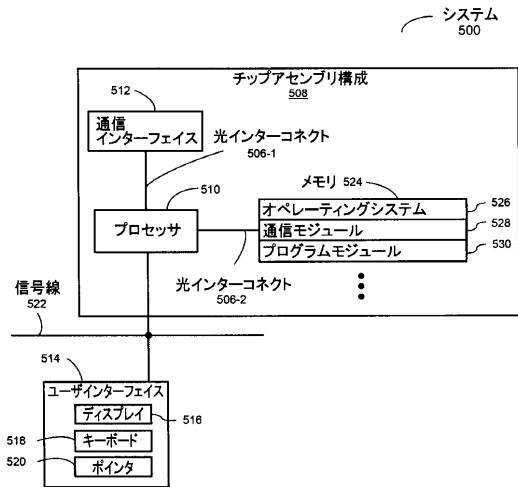

別の実施の形態は、チップアセンブリ構成を含むシステムを提供する。このシステムはプロセッサとメモリを含んでもよいし含まなくてもよい。

18もう1つの実施の形態は、チップアセンブリ構成において情報を伝達する方法を提供する。動作中、集積回路からの電気信号を、チップアセンブリ構成内の集積回路に隣接する基板を通じて電気経路に駆動する。この電気経路は、基板の第1の表面上に配置された第1のコネクタと、基板の、第1の表面と反対側の第2の表面上に配置された第2のコネクタと、第1のコネクタと第2のコネクタとを電気的に結合する、基板を通じてインターフェースとを含む。次に、電気信号を、第2の表面に隣接するように配置された第2のコネクタに電気的に結合された変換機構が受けける。加えて、この変換機構を用いて、電気信号を光信号に変換する。次に、この光信号をチップアセンブリ構成の光インターフェースで伝達する。

10

20

30

40

50

## 【図面の簡単な説明】

## 【0017】

【図1】既存のチップパッケージの上面図を示すブロック図である。

【図2】本開示のある実施の形態に従うチップアセンブリ構成の側面図を示すブロック図である。

【図3】本開示のある実施の形態に従う図2のチップアセンブリ構成の底面図を示すブロック図である。

【図4】本開示のある実施の形態に従うマルチチップモジュール(multi-chip module)(MCM)の側面図を示すブロック図である。

【図5】本開示のある実施の形態に従う図2のチップアセンブリ構成を含むシステムを示すブロック図である。 10

【図6】本開示のある実施の形態に従うチップアセンブリ構成において情報を伝達する方法を示すフロー図である。 25 なお、これら図面を通して、対応する部分には同様の参考番号が付されている。加えて、同一部分が複数ある場合は冒頭部分を共通にしダッシュ記号の後に数字を付して区別している。

## 【発明を実施するための形態】

## 【0018】

## 詳細な説明

チップアセンブリ構成、このチップアセンブリ構成を含むマルチチップモジュール(MCM)、このチップアセンブリ構成を含むシステム、および、このチップアセンブリ構成において情報を伝達する技術の実施の形態について説明する。このチップアセンブリ構成は基板を含み、基板の一方側に集積回路があり他方側に変換機構がある。集積回路と変換機構とは、基板を通る短距離電気伝送線によって電気的に結合される。加えて、変換機構は、信号を電気ドメインと光ドメインとの間で変換し、それにより、集積回路とその他のコンポーネントおよび装置との間で、光通信を用いて(たとえば光ファイバまたは光導波路で)高速通信を行なうことができる。 20

## 【0019】

変換機構(すなわち光入出力またはI/Oポート)を集積回路の極めて近くであるが集積回路の反対側に配置することによって、チップアセンブリ構成は、無駄に使用されるスペース、レイテンシ、および熱管理に関連する課題に対処することができ、それによって、光I/Oポートの高密度の構成を利用できる。結果として、このチップアセンブリ構成は、既存の実装例に関連する問題を伴わない光インターフェクトに関連する利点をもたらすことができる。よって、このチップアセンブリ構成は、高性能コンピュータシステムにおける次世代マルチプロセッサーアーキテクチャに利用される好適な通信および集積化特性を提供することができる。 30

## 【0020】

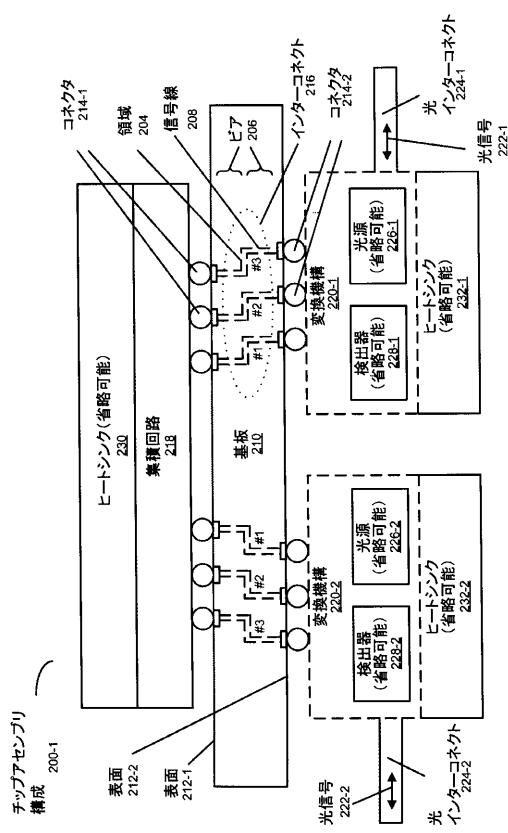

次にチップアセンブリ構成について説明する。図2は、チップアセンブリ構成200-1の側面図を示すブロック図を示している。このチップアセンブリ構成は基板210(プリント回路基板、ガラス基板、無機基板、セラミック基板、またはプラスチック基板等)を含む。基板210の両側に表面212があり、コネクタ214-1が表面212-1上に配置され、コネクタ214-2が表面212-2上に配置される。これらコネクタは、基板210を通るインターフェクト216(伝送線等)によって電気的に結合されている。所定のインターフェクトと一対のコネクタ214との組合せが、電気経路を構成し得る。

## 【0021】

なお、所定のインターフェクトは、表面212のうちの一方にほぼ平行である領域204(すなわち近接した横方向の飛越し(hop)を与える)を含む信号線208によって電気的に結合された2つのビア206を含み得る。これらビアは、その一部が基板210を通っていてもよい。さらに、領域204の長さは1mm以下でもよく、それによって、シグナルインテグリティが良好な高速通信を容易にする。 40 50

**【0022】**

なお、所定のコネクトが、表面212-1から表面212-2までまたはその逆に、直線状に信号線によって電気的に結合された1つのビアを含んでもよい。

**【0023】**

加えて、チップアセンブリ構成200-1は、表面212-1に隣接するように配置されコネクタ214-1に（たとえば半田および／またはボールグリッドアレイによって）電気的に結合された集積回路218を含む。さらに、チップアセンブリ構成200-1は、表面212-2に隣接するように配置されコネクタ214-2に（たとえば半田および／またはボールグリッドアレイによって）電気的に結合された変換機構220を含む。これら変換機構は、集積回路218からの電気信号を対応する光信号222-1に変換し、集積回路218への光信号222-2を対応する電気信号に変換する。なお、光信号222は、チップアセンブリ構成200-1内において、光ファイバおよび／または光導波路等（シリコンオン－インシュレータ技術を用いて実装される光導波路等）の1つ以上の光インターフェクト224を用いて伝達される。10

**【0024】**

いくつかの実施の形態において、チップアセンブリ構成は、1つ以上の光インターフェクト224に光学的に結合された光源226および／または光検出器228を含む。これに代えて、1つ以上の光インターフェクト224と関連付けられた光源および検出器がチップアセンブリ構成200-1の外部にあってもよい。

**【0025】**

コネクタ214-1、コネクタ214-2、およびインターフェクト216と関連付けられた電気経路の平均インピーダンスは、集積回路218におけるおよび変換機構220のうちの1つにおけるドライバの平均インピーダンスとほぼ一致してもよい。たとえば、この平均インピーダンスは、関連するキャパシタンスが大きい状態で、約50 であってもよい。さらに、コネクタ214-1、コネクタ214-2、およびインターフェクト216に関連する伝達特性におけるドミナントポールは、集積回路218と変換機構220との間の10Gb/sを超えるデータレートでの通信を容易にし得る。20

**【0026】**

さらに、チップアセンブリ構成200-1は、集積回路218の、基板210と反対側において、集積回路218に熱的に結合された省略可能なヒートシンク230を含み得る。光学要素にとって熱安定性は重要なので、これは有用であろう。この構成はまた、クロストークの低減および／またはコンポーネント密度の増大のために使用できる、表面212-1上の貴重なスペースを空ける。30

**【0027】**

ある代表的な実施の形態において、変換機構220のうちの所定の1つの変換機構における各光-チャネルドライバまたは受信機I/Oは、対応する、集積回路218上の高速ドライバ／受信機ピンに、電気的に結合される（経路#1）。加えて、電源への接続（経路#2）および接地への接続（経路#3）がなされる。先に述べたように、これら接続は、2つの短いビア（高さ約150～300μm）と、プラットフォームボード層上の、関連する伝送線の小さな方向転換部分（たとえば長さ1mm未満）とによって可能になるであろう。（すべての接続には適さないかもしれない、表面212-1から表面212-2までのビアを介した降下（drop）を除いて）この電気的な飛越し（hop）は、表面212同士を物理的に相互接続できる最小の電気的な飛越しであろう。このような小さな電気的な接続によって、集積回路218におけるシリアルライザ／デシリアルライザI/Oブロックへのおよびそこからの最高データレートでのシグナリングが容易になるであろう。たとえば、必要な追加のビアに関連する電気的な交差および信号劣化を回避できる。加えて、I/Oドライバについての電力要求を減じることができ、および／または他の通信技術（プリエンファシスおよび等化等）の使用を減じるかまたはなくすことができる。40

**【0028】**

いくつかの実施の形態において、変換機構220のうちの所定の1つにおける光サブア

10

20

30

40

50

センブリの各光I/Oポートは、4、8、12または16のチャネルをサポートできる。一般的には、各レーンについて可能な最大データレートを想定した場合、必要な空間チャネルの数は通常、集積回路218へのインターフェイスに必要な空間的多重化または集約によって必然的に決まる。これら光I/Oポートを集積回路218等の集積回路の極めて近くに設けつつ、変換機構220は各々、小さな面積の中で複数のチャネル（たとえば一次元または二次元フォーマットにおいて4、8、12、または16のチャネル）をサポートするのに十分な幅を有し得る。

#### 【0029】

さらに、このレイアウトにおいて可能なシグナルインテグリティに応じて、各レーンをシングルエンドと差動のうちのいずれかにしてもよい。なお、変換機構220のうちの所定の1つにおける光I/Oポートは、光源（電流または電圧モードで動作する一次元または二次元垂直キャビティ面発光レーザアレイ等）、検出器（一次元または二次元フォトダイオードアレイ、たとえば逆バイアスpn接合ダイオード、pinダイオード、金属-半導体-金属検出器または共振キャビティ強化検出器等）、ならびに（光ファイバリボンによって光学要素に結合し得る）40Gbpsまでのデータレートに対応できる電気集積回路の形態の、関連するドライバおよび受信機（トランスインピーダンス増幅器および制限増幅器等）を含み得る。光学要素は、基材としてIII-V半導体化合物（GaAsまたはInP等）を用いて実現してもよい。

#### 【0030】

さらに、光学要素は、電気集積回路と同一基板上にあってもよい。たとえば、変換機構220における光I/Oポートは、リフローアセンブリプロセスまたはマイクロピングリッドアレイ（μ-PGA）コネクタのMEG-array（登録商標）コネクタ（FCI社、Guyancourt、フランス）等の再結合可能な接続を用いて、基板210に物理的に装着されてもよい。加えて、光コネクタ／光ヘッダを用いて、個々の送信または受信チャネルに対するパッシブアライメント（passive alignment）を介し、標準MPO/MTPコネクタ（Molex（登録商標）社、Lisle、イリノイ）上の光インターフェース224における光ファイバリボンに結合してもよい。これら光ヘッダは、適切な光多重／多重分離素子を用いた空間分割多重（たとえば光ファイバの並列チャネル）および／または波長分割多重をサポートしてもよい。

#### 【0031】

熱的な制約があるので、変換機構220における光I/Oポートは、動作中に集積回路218から生じる熱から分離してもよい。同時に、変換機構220における電気集積回路内のドライバおよび受信機から熱を取り除く必要がある。さもなければ、熱的ロールオフが高温での光源の出力を低下させるかもしれない。ゆえに、変換機構220は、フィンを備える機械加工されたアルミニウムまたは銅ブロック等の省略可能なヒートシンク232に熱的に結合されてもよい。

#### 【0032】

集積回路218がプロセッサである実施の形態では、数十の高速シリアルライザ／デシリアルライザの電気的I/O伝送線をなくすことができる。たとえば、典型的なプロセッサは、チップの周囲にシリアルライザ／デシリアルライザI/Oブロックを含み、差動伝送線がシリアルライザ／デシリアルライザI/Oピンに接続されている。典型的には、必要な差動対線の数は、二分割帯域幅をピン1当たりの最大データレートで除算したものに等しい。一例として、必要な、プロセッサに対する集約帯域幅が、2Tbps（二分割帯域幅は4Tbps）であり、各シリアルライザ／デシリアルライザI/Oピンが20Gbpsをサポートする場合、必要なピンまたは伝送線の数は、2Tbpsを20Gbpsで除算したもの、すなわち100である。差動シグナリングのために2で乗算すると、200のピンまたは伝送線となる。

#### 【0033】

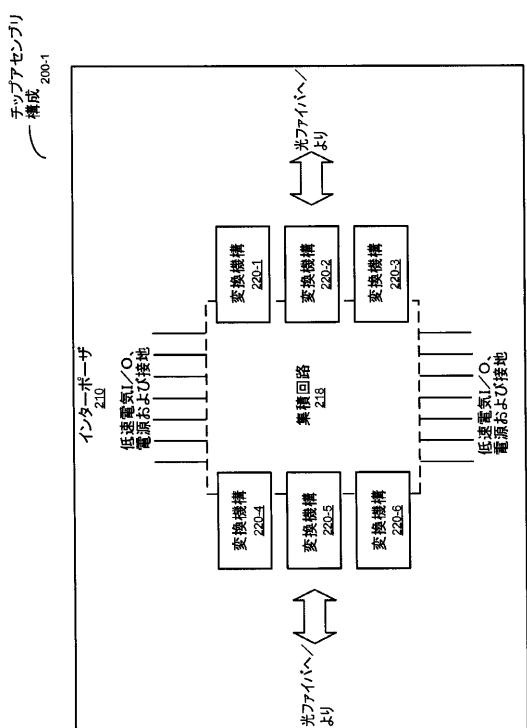

チップアセンブリ構成200-1の底面図を示すブロック図を示している図3に示される構成を用いて、変換機構220における光アセンブリの複数のアレイは、ピンまたは伝

10

20

30

40

50

送線の数を大幅に減じることができる。加えて、この構成によって、基板 210 の上面に 1 つ以上のプロセッサおよびメモリチップをより高密度に実装することで、ルーティングの輻輳をなくしましたは減じ、シグナルインテグリティを改善する。

#### 【 0 0 3 4 】

代表的な実施の形態において、チップアセンブリ構成 200 - 1 は、送信チャネルおよび受信チャネルが変換機構 220 にある全二重実装例である。この構成における、送信機 (Tx) および受信機 (Rx) 光 I/O ポート (または光アセンブリ) は、(たとえば変換機構 220 - 1 および 220 - 2 各々において) 隣り合っていてもよい。加えて、この構成によって 2 ~ 16 のチャネルが容易になる。しかしながら、いくつかの実施の形態では、送信または受信チャネルが所定の変換機構の所定の光 I/O ポートにある半二重実装例を用いる。なお、変換機構 220 における送信機および受信機光アセンブリは物理的に分離してもよく、多岐にわたるやり方で配置し得る (たとえば Tx と Rx を交互にする、Tx、Tx、Tx、Tx に続いて Rx、Rx、Rx, Rx を配置する等)。

10

#### 【 0 0 3 5 】

図 2において、チップアセンブリ構成 200 - 1 の表面 212 - 2 上の光 I/O ポートを、数個の列にまたはジグザグの列に配置することができる。集積回路 218 はこれらの経路を妨げずインターフェクタ 216 は基板 210 を通る垂直経路に沿っているので、物理空間にこれらを配置できる。なお、インターフェクタ 216 はこの垂直経路に沿っているので、シリアルライザ / デシリアルライザ I/O ブロックは、集積回路 218 の周囲に限定されなくてもよい。結果として、設計者は、プロセッサチップの周囲近くにシリアルライザ / デシリアルライザ I/O ブロックを配置することを選択することができ、変換機構 220 - 1 等の所定の変換機構に、対応する垂直方向のインターフェクト経路を設けなくてもよくなる。さらに、プロセッサの下のいくつかの領域は、ボルスタープレートがプロセッサパッケージを基板 210 に接続する場所のために空けておくことができる。

20

#### 【 0 0 3 6 】

ある代表的な実施の形態において、変換機構 220 における光 I/O ポートは、波長 850、1301、または 1550 nm の垂直キャビティ面発光レーザ技術、および、対応する GaAs または InP 検出器技術に基づいている。さらに、変換機構 220 における光 I/O ポートは、数を減らした分布帰還型レーザアレイを用いてシングルモード (すなわち波長分割多重) および / またはマルチモード (すなわち空間分割多重) 光ファイバをサポートできるシリコンフォトニクス技術に基づいていてもよい。

30

#### 【 0 0 3 7 】

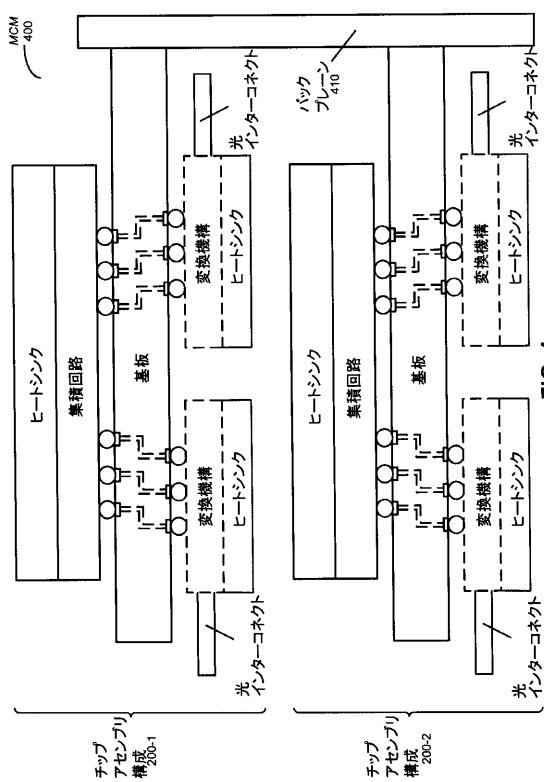

チップアセンブリ構成 200 - 1 の複数のインスタンスがマルチチップモジュール (MCM) に含まれていてもよい。これは図 4 に示されている。図 4 は、チップアセンブリ構成 200 がバックプレーン 410 に接続されているマルチチップモジュール MCM400 の側面図を示すブロック図を示している。なお、変換機構における光 I/O ポートを基板の下側に配置し、厚い銅ケーブルを、すべて高密度でコンパクトな光ファイバコネクタパッチパネルに集約させることができる、薄い光ファイバリボンに置換えてもよい。

#### 【 0 0 3 8 】

この構成により、電気および / または光スイッチを用いて、光信号を MCM400 内部でおよび / または外部から MCM400 に再分配することができる。加えて、この構成によって、集積回路に対しても変換機構に対しても、基板と基板との間に自然な空気の流れを生じさせることができる。さらに、厚い銅ケーブルを取り除くことによって、追加のケーブル管理サポートハーネスは不要になるであろう。(よってチップアセンブリ構成 200 の信頼性を高めることができる)。加えて、変換機構における光 I/O ポートを他のチップ、スイッチ、メモリ等の直下に配置することによって、これらコンポーネントへの電気信号線の長さを減じることができる。

40

#### 【 0 0 3 9 】

このチップアセンブリ構成は、さまざまな用途で使用できる。これは図 5 に示されている。図 5 は、チップアセンブリ構成 200 - 1 (図 2) 等のチップアセンブリ構成 508

50

を含むシステム 500 を示すブロック図を示している。チップアセンブリ構成 508 内の変換機構上のまたは変換機構に光学的に結合された光インターフェイス 506 は、1つ以上のプロセッサ 510、メモリ 524 および / または通信インターフェイス 512 を結合し得る。加えて、1つ以上のプロセッサ 510 を、1本以上の信号線 522 によってユーザインターフェイス 514 に結合してもよい。なお、1つ以上のプロセッサ（またはプロセッサコア）510 は並列処理および / またはマルチスレッドオペレーションをサポートしてもよく、通信インターフェイス 512 は永続通信接続を有していてもよく、1本以上の信号線 522 は通信バスを構成してもよい。さらに、ユーザインターフェイス 514 は、ディスプレイ 516、キーボード 518、および / またはマウス等のポインタ 520 を含み得る。

10

#### 【 0040 】

システム 500 内のメモリ 524 は、揮発性メモリおよび / または不揮発性メモリを含み得る。より具体的には、メモリ 524 は、ROM、RAM、EPROM、EEPROM、フラッシュ、1つ以上のスマートカード、1つ以上の磁気ディスク記憶装置、および / または1つ以上の光記憶装置を含み得る。メモリ 524 は、ハードウェア依存タスクを実行するためのさまざまな基本システムサービスを扱うための手順（または命令セット）を含むオペレーティングシステム 526 を格納してもよい。加えて、メモリ 524 はまた、通信モジュール 528 に通信手順（または命令セット）を格納してもよい。これら通信手順は、システム 500 から離れた場所に位置するコンピュータ、装置、および / またはサーバを含む、1つ以上のコンピュータ、装置、および / またはサーバと通信するために使用してもよい。

20

#### 【 0041 】

メモリ 524 はまた、1つ以上のプログラムモジュール 530（または命令セット）を含み得る。なお、プログラムモジュール 530 のうちの1つ以上がコンピュータプログラム機構を構成してもよい。メモリ 524 内のさまざまなモジュールにおける命令は、高レベル手続型言語、オブジェクト指向プログラミング言語、および / またはアセンブリもしくはマシン言語で実現されてもよい。プログラミング言語は、1つ以上のプロセッサ（またはプロセッサコア）510 による実行のために、コンパイルまたは解釈されてもよい、すなわち構成可能または構成されてもよい。

30

#### 【 0042 】

システム 500 は、VLSI 回路、スイッチ、ハブ、ブリッジ、ルータ、通信システム（波長分割多重等）、ストレージエリアネットワーク、データセンター、ネットワーク（ローカルエリアネットワーク等）、および / またはコンピュータシステム（マルチコアプロセッサコンピュータシステム等）を含み得る。たとえば、チップアセンブリ構成は、複数のプロセッサブレードに結合されたバックプレーンに含まれるものであってもよく、または、図 4 に示されるように、種類が異なるコンポーネント（プロセッサ、メモリ、I/O デバイス、および / または周辺装置等）を結合する MCM に含まれるものであってもよい。いくつかの実施の形態において、この MCM は、スイッチ、ハブ、ブリッジ、および / またはルータの機能を果たす。

40

#### 【 0043 】

さらに、このコンピュータシステムは、サーバ（マルチソケット、マルチラックサーバ等）、ラップトップコンピュータ、通信装置またはシステム、パーソナルコンピュータ、ワークステーション、メインフレームコンピュータ、ブレード、エンタープライズコンピュータ、データセンター、携帯型計算装置、タブレット、スーパーコンピュータ、ネットワークアッタッチドストレージ（network-attached-storage）（NAS）システム、ストレージエリアネットワーク（storage-area-network）（SAN）システム、および / または別の電子計算装置を含み得るが、これらに限定されない。

#### 【 0044 】

一般的に、システム 500 は、1つの場所にあってもよく、または、地理的に分散した複数の場所にまたがっていてもよい。加えて、システム 500 の機能のうちの一部または

50

すべてを、1つ以上の特定用途向け集積回路（ASIC）および／または1つ以上のデジタル信号プロセッサ（DSP）に実装してもよい。さらに、当該技術では周知のように、上記実施の形態における機能の、ハードウェアで実装する部分をソフトウェアで実装する部分より多くしてもよく、または、ハードウェアで実装する部分をソフトウェアで実装する部分より少なくしてもよい。

#### 【0045】

前述の実施の形態には、より少ないコンポーネントが含まれていてもよく、または追加のコンポーネントが含まれていてもよい。加えて、チップアセンブリ構成およびシステムは多数のディスクリート部品を有するものとして示されているが、これら実施の形態は、本明細書に記載の実施の形態の構造的模式図ではなく、存在し得るさまざまな特徴の機能的説明となることを意図している。よって、これら実施の形態において、2つ以上のコンポーネントを組み合わせて1つのコンポーネントにしてもよく、および／または1つ以上のコンポーネントの位置を変更してもよい。さらに、前述の実施の形態の2つ以上における特徴を互いに組み合わせてもよい。

10

#### 【0046】

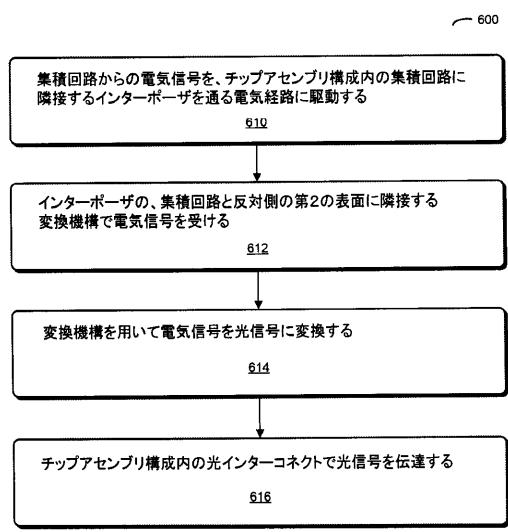

次にこの方法の実施の形態について説明する。図6は、チップアセンブリ構成200-1(図2)であってもよいチップアセンブリ構成において情報を伝達する方法600を示すフロー図を示している。動作中、集積回路からの電気信号を、チップアセンブリ構成内の集積回路に隣接する基板を通る電気経路に駆動する(動作610)。この電気経路は、基板の第1の表面上に配置された第1のコネクタと、基板の、第1の表面と反対側の第2の表面上に配置された第2のコネクタと、第1のコネクタと第2のコネクタとを電気的に結合する、基板を通るインターロネクタとを含む。次に、電気信号を、第2の表面に隣接するように配置され第2のコネクタに電気的に結合された変換機構が受ける(動作612)。加えて、この変換機構を用いて、電気信号を光信号に変換する(動作614)。次に、この光信号をチップアセンブリ構成内の光インターロネクトで伝達する(動作616)。

20

#### 【0047】

実施の形態によっては、方法600はこれよりも多いまたは少ない動作を含む。加えて、上記動作の順序は変更してもよく、および／または2つ以上の動作を組み合わせて1つの動作にしてもよい。

30

#### 【0048】

上記説明は、この開示を当業者が利用できるようにすることを意図しており、特定の用途およびその必要条件という文脈の中で行なっている。加えて、本開示の実施の形態に関する上記説明は、例示と説明のみを目的としてなされている。上記説明はすべてを網羅することを意図している訳でも本開示を開示された形態に限定することを意図している訳でもない。よって、数多くの変更および変形が当業者には明らかであろう。また、本明細書で定義されている一般的な原理は、本開示の精神および範囲から逸脱することなくその他の実施の形態および用途に適用し得る。加えて、上記実施の形態に関する記載は本開示を限定することを意図しているのではない。よって、本開示は、示されている実施の形態に限定されることを意図しているのではなく、本明細書に開示された原理および特徴に従う最も広い範囲に即してなされている。

40

【図1】

FIG. 1

(PRIOR ART)

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

(72)発明者 ファン , ダーウェイ

アメリカ合衆国、92129 カリフォルニア州、サン・ディエゴ、ジュンカス・コート、737

5

(72)発明者 アンシャンズリー , ニコラス・イー

アメリカ合衆国、92064 カリフォルニア州、ポーウェイ、ソウル・ストリート、12725

(72)発明者 シー , テレサ

アメリカ合衆国、92122 カリフォルニア州、サン・ディエゴ、レッド・ディア・ストリート

、6636

(72)発明者 マケルフレッシュ , デイビッド・ケイ

アメリカ合衆国、92129 カリフォルニア州、サン・ディエゴ、セロム・コート、7176

審査官 野口 晃一

(56)参考文献 特開2006-259682(JP,A)

特開2009-080204(JP,A)

特開2005-085844(JP,A)

特表平08-501657(JP,A)

特開2005-159060(JP,A)

特開2002-050821(JP,A)

(58)調査した分野(Int.Cl. , DB名)

|        |                  |

|--------|------------------|

| G 02 B | 6 / 02 - 6 / 036 |

|        | 6 / 10 - 6 / 14  |

|        | 6 / 26 - 6 / 27  |

|        | 6 / 30 - 6 / 34  |

|        | 6 / 42 - 6 / 44  |

| G 02 F | 1 / 00 - 1 / 125 |

|        | 1 / 21 - 7 / 00  |