(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7007092号

(P7007092)

(45)発行日 令和4年1月24日(2022.1.24)

(24)登録日 令和4年1月11日(2022.1.11)

(51)国際特許分類

|         |                  |     |         |         |         |

|---------|------------------|-----|---------|---------|---------|

| G 0 6 F | 12/02 (2006.01)  | F I | G 0 6 F | 12/02   | 5 9 0 A |

| G 1 1 C | 7/10 (2006.01)   |     | G 1 1 C | 7/10    | 4 6 0   |

| G 1 1 C | 11/4096(2006.01) |     | G 1 1 C | 7/10    | 5 1 5   |

|         |                  |     | G 1 1 C | 11/4096 | 3 0 0   |

|         |                  |     | G 1 1 C | 11/4096 | 5 5 0   |

請求項の数 28 (全33頁)

(21)出願番号 特願2017-28878(P2017-28878)

(22)出願日 平成29年2月20日(2017.2.20)

(65)公開番号 特開2017-157209(P2017-157209

A)

(43)公開日 平成29年9月7日(2017.9.7)

審査請求日 令和2年2月20日(2020.2.20)

(31)優先権主張番号 62/303,353

(32)優先日 平成28年3月3日(2016.3.3)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/347,569

(32)優先日 平成28年6月8日(2016.6.8)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 15/227,911

最終頁に続く

(73)特許権者 390019839

三星電子株式会社

Samsung Electronics

Co., Ltd.

大韓民国京畿道水原市靈通区三星路 1 2

9

1 2 9 , Samsung - ro , Yeo

n g t o n g - g u , Suw o n - si

, Gyeonggi - do , Repub

lic of Korea

(74)代理人 110000051

特許業務法人共生国際特許事務所

張 牧 天

(72)発明者 アメリカ合衆国 カリフォルニア州 9 5

0 5 1 サンタクララ ビアトリノブレー

最終頁に続く

(54)【発明の名称】 メモリ装置のデータアドレッシング方法及びメモリ装置並びにメモリモジュール

## (57)【特許請求の範囲】

## 【請求項 1】

メモリ装置内のデータは、第1の数の行アドレスビットと第2の数の列アドレスビットによって各々インデックスされる行と列のアレイ内に配列され、前記データは、第3の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第4の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされる前記メモリ装置の前記データのアドレッシング方法において、

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビットの第2サブセットとに分離し、前記第1サブセットを前記行アドレス命令語で特定し、前記第2サブセットを後続(next)アドレス命令語で特定する段階と、

前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行する段階と、

前記行アドレス命令語の発行後、前記後続アドレス命令語を発行する段階と、を有し、前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、

前記第2の数の列アドレスビットを列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットは、前記列アドレス命令語で特定し

、前記第3サブセットを以前( p r e v i o u s )アドレス命令語で特定する段階と、前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行する段階と、前記列アドレス命令語の発行前に、前記以前アドレス命令語を発行する段階と、を有し、前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、

前記列アドレス命令語を発行する段階は、前記行アドレス命令語を発行する段階の直後に行われ、

前記後続アドレス命令語の発行は前記行アドレス命令語の発行の直後に実行され、前記以前アドレス命令語の発行は前記列アドレス命令語の発行の直前に実行されることを特徴とするメモリ装置のデータアドレッシング方法。

10

#### 【請求項2】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記アーキテクチャは、前記列アドレス命令語とデータバスへのデータアクセス可能時点との間の遅延を示す第1アクセス時間によって定義され、

前記第1アクセス時間より長い第2アクセス時間内に前記行のイニシャル( i n i t i a l )列アクセスを実行する段階と、

前記第1アクセス時間内に前記行への後続( s u b s e q u e n t )列アクセスを実行する段階と、をさらに有することを特徴とする請求項1に記載のメモリ装置のデータアドレッシング方法。

20

#### 【請求項3】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記第2の数の列アドレスビットを前記列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前アドレス命令語で特定する段階をさらに有することを特徴とする請求項1に記載のメモリ装置のデータアドレッシング方法。

#### 【請求項4】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第3の数の行アドレスビットと前記第2の数の列アドレスビットとによってインデックスされ、前記行アドレスビットの前記第1サブセットは、前記行アドレスビットの前記第3の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第1サブセットによって特定されるサブアレイからの行データを対応する行バッファにロード( l o a d )する段階をさらに有することを特徴とする請求項1に記載のメモリ装置のデータアドレッシング方法。

30

#### 【請求項5】

前記後続アドレス命令語の行アドレスビットの中の前記第2サブセットによって特定されるサブアレイの中の1つを選択する段階をさらに有することを特徴とする請求項4に記載のメモリ装置のデータアドレッシング方法。

#### 【請求項6】

前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットとによってインデックスされ、前記列アドレスビットの前記第4サブ

40

50

セットは、前記列アドレスビットの前記第4の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記サブアレイ各々において、前記行アドレス命令語に応答して対応する前記第1の数の

行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファに

ロードする段階をさらに有することを特徴とする請求項1に記載のメモリ装置のデータア

ドレッシング方法。

**【請求項7】**

前記以前アドレス命令語の列アドレスビットの中の前記第3サブセットによって特定され

るサブアレイの中の1つを選択する段階をさらに有することを特徴とする請求項6に記載

のメモリ装置のデータアドレッシング方法。 10

**【請求項8】**

メモリ装置であって、

各々、第1の数の行アドレスビットによってインデックスされる行と、第2の数の列アド

レスビットによってインデックスされる列とによって配列されるデータを格納するストレ

ージセルを含み、

前記メモリ装置のデータは、第3の数の行アドレスビットを特定する行アドレス命令語と

、前記行アドレス命令語に後続する第4の数の列アドレスビットを特定する列アドレス命

令語によって定義されるアーキテクチャを使用してアドレッシングされ、

前記メモリ装置は、前記データのアドレッシングとして、

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大き

く、かつ、前記第2の数と前記第4の数が同じ場合、 20

前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビット

の第2サブセットとに分離し、前記第1サブセットを前記行アドレス命令語で特定し、

前記第2サブセットを後続アドレス命令語で特定し、

前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語と

して発行し、

前記行アドレス命令語の発行後、前記後続アドレス命令語の発行を行うことを実行し、

前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大き

く、かつ、前記第1の数と前記第3の数が同じ場合、

前記第2の数の列アドレスビットを列アドレスビットの第3サブセットと列アドレスビット

の第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、

前記第3サブセットを以前アドレス命令語で特定し、 30

前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行し、

前記列アドレス命令語の発行前に、以前アドレス命令語の発行を行うことを実行し、

前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス

命令語であり、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する

前記行アドレス命令語であり、

前記列アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われ、

前記後続アドレス命令語の発行は前記行アドレス命令語の発行の直後に行われ、

前記以前アドレス命令語の発行は前記列アドレス命令語の発行の直前に行われることを特

徴とするメモリ装置。 40

**【請求項9】**

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大き

く、かつ、前記第2の数と前記第4の数が同じ場合、

前記アーキテクチャは、前記列アドレス命令語とデータバスのデータアクセス可能時点と

の間の遅延を示す第1アクセス時間によって定義され、

前記データのアドレッシングとして、

前記第1アクセス時間より長い第2アクセス時間内に前記行のイニシャル列アクセスを実

行することと、

前記第1アクセス時間内に前記行への後続列アクセスを実行することと、をさらに含むこ 50

とを特徴とする請求項 8 に記載のメモリ装置。

**【請求項 10】**

前記第 1 の数が前記第 2 の数より大きく、かつ、前記第 1 の数が前記第 3 の数より大きく、かつ、前記第 2 の数と前記第 4 の数が同じ場合、

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第 3 の数の行アドレスビットと前記第 2 の数の列アドレスビットによってインデックスされ、前記行アドレスビットの前記第 1 サブセットは、前記行アドレスビットの前記第 3 の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第 1 サブセットによって特定されるサブアレイからの行データを対応する行バッファにロードすることを含むことを特徴とする請求項 8 に記載のメモリ装置。 10

**【請求項 11】**

前記データのアドレッシングは、前記後続アドレス命令語の行アドレスビットの中の前記第 2 サブセットによって特定されるサブアレイの中の 1 つを選択することをさらに含むことを特徴とする請求項 10 に記載のメモリ装置。

**【請求項 12】**

前記第 2 の数が前記第 1 の数より大きく、かつ、前記第 2 の数が前記第 4 の数より大きく、かつ、前記第 1 の数と前記第 3 の数が同じ場合、 20

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第 1 の数の行アドレスビットと前記第 4 の数の列アドレスビットによってインデックスされ、前記列アドレスビットの前記第 4 サブセットは、前記列アドレスビットの前記第 4 の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記第 1 の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードすることをさらに含むことを特徴とする請求項 8 に記載のメモリ装置。 30

**【請求項 13】**

前記データのアドレッシングは、前記以前アドレス命令語の列アドレスビットの中の前記第 3 サブセットによって特定されるサブアレイの中の 1 つを選択することをさらに含むことを特徴とする請求項 12 に記載のメモリ装置。

**【請求項 14】**

複数のメモリ装置を有し、

前記複数のメモリ装置の各々は、各々の第 1 の数の行アドレスビットによってインデックスされる行と、第 2 の数の列アドレスビットによってインデックスされる列とによって配列されるデータを格納するストレージセルを含み、

前記メモリ装置のデータは、第 3 の数の行アドレスビットで特定される行アドレス命令語と、前記行アドレス命令語に後続する第 4 の数の列アドレスビットで特定される列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされ、 40

前記複数のメモリ装置の各々は、前記データのアドレッシングとして、

前記第 1 の数が前記第 2 の数より大きく、かつ、前記第 1 の数が前記第 3 の数より大きく、かつ、前記第 2 の数と前記第 4 の数が同じ場合、

前記第 1 の数の行アドレスビットを行アドレスビットの第 1 サブセットと行アドレスビットの第 2 サブセットとに分離し、前記第 1 サブセットを前記行アドレス命令語で特定し、前記第 2 サブセットを後続アドレス命令語で特定し、

前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行し、

前記第 2 の数が前記第 1 の数より大きく、かつ、前記第 2 の数が前記第 4 の数より大きく 50

、かつ、前記第1の数と前記第3の数が同じ場合、

前記第2の数の列アドレスビットを列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前アドレス命令語で特定し、

前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行する、ことを実行し、

前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、

前記列アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われ、

10

前記後続アドレス命令語の発行は前記行アドレス命令語の発行の直後に行われ、

前記以前アドレス命令語の発行は前記列アドレス命令語の発行の直前に行われる特徴とするメモリモジュール。

#### 【請求項15】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記アーキテクチャは、前記列アドレス命令語とデータバスのデータアクセス可能時点の遅延を示す第1アクセス時間によって定義され、

前記データのアドレッシングとして、

前記第1アクセス時間より長い第2アクセス時間内に前記行のイニシャル列アクセスを実行することと、

20

前記第1アクセス時間内に前記行への後続列アクセスを実行することと、をさらに含むことを特徴とする請求項14に記載のメモリモジュール。

#### 【請求項16】

前記メモリ装置の各々において、

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第3の数の行アドレスビットと前記第2の数の列アドレスビットによってインデックスされ、前記行アドレスビットの前記第1サブセットは、前記行アドレスビットの前記第3の数になり、

30

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第1サブセットによって特定されるサブアレイからの行データを対応する行バッファにロードすることを含むことを特徴とする請求項14に記載のメモリモジュール。

#### 【請求項17】

前記メモリ装置の各々において、

前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、

40

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットによってインデックスされ、前記列アドレスビットの前記第4サブセットは、前記列アドレスビットの前記第4の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記データのアドレッシングは、前記サブアレイの各々に対し、前記行アドレス命令語に応答して対応する前記第1の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードすることをさらに含むことを特徴とする請求項14に記載のメモリモジュール。

#### 【請求項18】

50

前記メモリ装置の各々は、相変化ランダムアクセスメモリ( phase - change random access memory、P R A M )装置を含むことを特徴とする請求項 1 4 に記載のメモリモジュール。

**【請求項 1 9】**

メモリ装置内のデータは、第 1 の数の行アドレスビットと第 2 の数の列アドレスビットによって各々インデックスされる行と列のアレイ内に配列され、前記データは、第 3 の数の行アドレスビットを特定する行アドレス命令語と、第 4 の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされる前記メモリ装置の前記データのアドレッシング方法において、

前記第 1 の数が前記第 2 の数より大きく、かつ、前記第 1 の数が前記第 3 の数より大きく、かつ、前記第 2 の数と前記第 4 の数が同じ場合、

前記第 1 の数の行アドレスビットを行アドレスビットの第 1 サブセットと行アドレスビットの第 2 サブセットとに分離する段階と、

前記第 1 サブセットを前記行アドレス命令語で特定し、前記第 2 サブセットを後続( n e x t )アドレス命令語で特定する段階と、

前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行する段階と、を有し、

前記後続アドレス命令語は、前記第 4 の数の列アドレスビットを特定する前記列アドレス命令語であり、

前記行アドレス命令語を発行する段階の直後に、前記列アドレス命令語を発行する段階をさらに有し、

前記後続アドレス命令語の発行は、前記行アドレス命令語の発行の直後に実行されることを特徴とするメモリ装置のデータアドレッシング方法。

**【請求項 2 0】**

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、前記アレイのサブセットであり、各々前記第 3 の数の行アドレスビットと前記第 2 の数の列アドレスビットとによってインデックスされ、前記行アドレスビットの前記第 1 サブセットは、前記行アドレスビットの前記第 3 の数であり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第 1 サブセットによって特定されるサブアレイからの行データを対応する行バッファにロード( l o a d )する段階をさらに有することを特徴とする請求項 1 9 に記載のメモリ装置のデータアドレッシング方法。

**【請求項 2 1】**

前記後続アドレス命令語の行アドレスビットの中の前記第 2 サブセットによって特定されるサブアレイの中の 1 つを選択する段階をさらに有することを特徴とする請求項 2 0 に記載のメモリ装置のデータアドレッシング方法。

**【請求項 2 2】**

メモリ装置内のデータは、第 1 の数の行アドレスビットと第 2 の数の列アドレスビットによって各々インデックスされる行と列のアレイ内に配列され、前記データは、第 3 の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第 4 の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされる前記メモリ装置の前記データのアドレッシング方法において、

前記第 2 の数が前記第 1 の数より大きく、かつ、前記第 2 の数が前記第 4 の数より大きく、かつ、前記第 1 の数と前記第 3 の数が同じ場合、

前記第 2 の数の列アドレスビットを、列アドレスビットの第 3 サブセットと列アドレスビットの第 4 サブセットとに分割する段階と、

前記第 4 サブセットを前記列アドレス命令語で特定し、前記第 3 サブセットを以前( p r e v i o u s )アドレス命令語で特定する段階と、

10

20

30

40

50

前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行する段階と、前記列アドレス命令語の発行前に、前記以前アドレス命令語を発行する段階と、を有し、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、

前記列アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われ、

前記データのアドレッシングとして、前記行アドレス命令語の発行後、直ちに後続アドレス命令語を発行するか、或いは前記以前アドレス命令語は、前記列アドレス命令語の発行直前に発行されることを特徴とするメモリ装置のデータアドレッシング方法。

#### 【請求項23】

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットによってインデックスされ、前記列アドレスビットの前記第4サブセットは、前記列アドレスビットの前記第4の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファを含み、

前記サブアレイ各々において、前記行アドレス命令語に応答して対応する前記第1の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードする段階をさらに有することを特徴とする請求項22に記載のメモリ装置のデータアドレッシング方法。

#### 【請求項24】

前記以前アドレス命令語の列アドレスビットの中の前記第3サブセットによって特定されるサブアレイの中の1つを選択する段階をさらに有することを特徴とする請求項23に記載のメモリ装置のデータアドレッシング方法。

#### 【請求項25】

メモリ装置であって、

各々、第1の数の行アドレスビットによってインデックスされる行と、第2の数の列アドレスビットによってインデックスされる列とによって配列されるデータを格納するストレージセルを含み、

前記メモリ装置のデータは、第3の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第4の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされ、

前記メモリ装置は、前記データのアドレッシングとして、

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、

前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビットの第2サブセットとに分離し、前記第1サブセットを前記行アドレス命令語で特定し、前記第2サブセットを後続アドレス命令語で特定し、

前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行することを実行し、

前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、

前記行アドレス命令語を発行した直後に、前記列アドレス命令語の発行を行って、前記データをアドレス指定し、

前記後続アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われることを特徴とするメモリ装置。

#### 【請求項26】

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第3の数の行アドレスビットと前記第2の数の列アドレスビットによってインデックスされ、前記行アドレスビットの前記第1サブセットは、前記行アドレスビットの前記第3の数になり、

前記メモリ装置は、前記サブアレイごとに行バッファをさらに含み、

10

20

30

40

50

前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第1サブセットによって特定されるサブアレイからの行データを対応する行バッファにロードすることをさらに含むことを特徴とする請求項25に記載のメモリ装置。

#### 【請求項27】

前記データのアドレッシングは、前記後続アドレス命令語の行アドレスビットの中の前記第2サブセットによって特定されるサブアレイの中の1つを選択することをさらに含むことを特徴とする請求項26に記載のメモリ装置。

#### 【請求項28】

前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、

10

前記第2の数の列アドレスビットを、列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前( previous )アドレス命令語で特定し、

前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行し、

前記列アドレス命令語の発行前に、前記以前アドレス命令語を発行し、

前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、

前記行アドレス命令語を発行した直後に、前記列アドレス命令語の発行を行って、前記データをアドレス指定し、

20

前記以前アドレス命令語の発行は、前記列アドレス命令語の発行直前に発行され、

前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットによってインデックスされ、

前記メモリ装置は、前記サブアレイごとに行バッファをさらに含み、

前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記第1の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードすることをさらに含むことを特徴とする請求項27に記載のメモリ装置。

#### 【発明の詳細な説明】

30

#### 【技術分野】

#### 【0001】

本発明はメモリ装置のデータアドレッシング方法に関し、特に追加的なピンの増加又はピン形成費用の増加無しで高容量SDRAMライクメモリのアドレッシング方法を提供するメモリ装置とのそのデータアドレッシング方法及びメモリモジュールに関する。

#### 【背景技術】

#### 【0002】

J E D E C D D R 4 S D R A M 標準で、C I D (チップID、又はランク)のために3つのピンが、バンクのために4つのピンが、行と列(命令語に依存的な)のためには18個の共有されるピンが存在する(命令語に依存)。

40

現在のピン使用方式とアドレッシング方式とは、D R A Mチップデータサイズ、幅、及び構成の正確な組み合わせが選択されて組み立てられたことを仮定すれば(そうでない場合、D I M Mの容量が低くなり、アドレッシング可能な領域が減少する結果をもたらす)、D I M M (Dual In line Memory Module、1つのパッケージに複数のD R A Mチップの集合)当たり256 G Bまでの容量を支援することができる。

#### 【0003】

しかしながら、これよりさらに大きいモジュール容量又はアドレッシング可能性は支援されないという問題がある(例えば、メモリがモジュールに物理的に追加されたとしてもメモリはアドレッシングが不可である)。

#### 【先行技術文献】

50

**【特許文献】****【0004】**

【文献】米国特許第9,251,874号明細書

米国特許第9,183,920号明細書

米国特許第9,104,646号明細書

米国特許第9,030,899号明細書

米国特許第8,130,576号明細書

米国特許第7,093,059号明細書

**【発明の概要】****【発明が解決しようとする課題】**

10

**【0005】**

本発明は上記従来のメモリ装置における問題点に鑑みてなされたものであって、本発明の目的は、ピン費用又はピン数の増加無しで高容量 SDRAM ライクメモリのアドレッシング方法を提供できるメモリ装置とのそのデータアドレッシング方法及びメモリモジュールを提供することにある。

**【課題を解決するための手段】****【0006】**

本発明の実施形態は、SDRAM 命令語、タイミング、及び構造を提供する。

一例として、本発明はピン費用又はピン数の増加無しで高容量 SDRAM ライクメモリのアドレッシング方法及びシステムを提供するためのものである。

20

本発明のその他の特徴によれば、本発明は SDRAM - 1 i k e ( 例えば、DDR4 ) のアドレスピン標準を維持しながら、高容量メモリモジュールを支援するためのものである。本発明の他の特徴は、アクティブ命令語 ( ACT+ ) 又は読み出し / 書込み命令語 ( RD / WR+ ) の拡張をためのことである。

本発明のその他の特徴は、バックツーバック ( back to back ) RAS / CAS ( 行アドレスストロボ / 列アドレスストロボ ) 命令語、バックツーバック CAS / CAS 、及びタイミング調整のことである。

その他の本発明の特徴は、命令語調整及び装置再構成を含むマルチ行又はマルチ列バッファ構造を提供することである。

**【0007】**

30

上記目的を達成するためになされた本発明によるメモリ装置のデータアドレッシング方法は、メモリ装置内のデータは、第 1 の数の行アドレスビットと第 2 の数の列アドレスビットによって各々インデックスされる行と列のアレイ内に配列され、前記データは、第 3 の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第 4 の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされる前記メモリ装置の前記データのアドレッシング方法において、前記第 1 の数が前記第 2 の数より大きく、かつ、前記第 1 の数が前記第 3 の数より大きく、かつ、前記第 2 の数と前記第 4 の数が同じ場合、前記第 1 の数の行アドレスビットを行アドレスビットの第 1 サブセットと行アドレスビットの第 2 サブセットとに分離し、前記第 1 サブセットを前記行アドレス命令語で特定し、前記第 2 サブセットを後続 ( next ) アドレス命令語で特定する段階と、前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行する段階と、前記行アドレス命令語の発行後、前記後続アドレス命令語を発行する段階と、を有し、前記第 2 の数が前記第 1 の数より大きく、かつ、前記第 2 の数が前記第 4 の数より大きく、かつ、前記第 1 の数と前記第 3 の数が同じ場合、前記第 2 の数の列アドレスビットを列アドレスビットの第 3 サブセットと列アドレスビットの第 4 サブセットとに分離し、前記第 4 サブセットは、前記列アドレス命令語で特定し、前記第 3 サブセットを以前 ( previous ) アドレス命令語で特定する段階と、前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行する段階と、前記列アドレス命令語の発行前に、前記以前アドレス命令語を発行する段階と、を有し、前記後続アドレス命令語は、前記第 4 の数の列アドレスビットを

40

50

特定する前記列アドレス命令語であり、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、前記列アドレス命令語を発行する段階は、前記行アドレス命令語を発行する段階の直後に行われ、前記後続アドレス命令語の発行は前記行アドレス命令語の発行の直後に実行され、前記以前アドレス命令語の発行は前記列アドレス命令語の発行の直前に実行されることを特徴とする。

#### 【0008】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記アーキテクチャは、前記列アドレス命令語とデータバスへのデータアクセス可能時点との間の遅延を示す第1アクセス時間によって定義され、前記第1アクセス時間より長い第2アクセス時間内に前記行のイニシャル(*initial*)列アクセスを実行する段階と、前記第1アクセス時間内に前記行への後続(*subsequent*)列アクセスを実行する段階と、をさらに有することが好ましい。

10

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記第2の数の列アドレスビットを前記列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前アドレス命令語で特定する段階をさらに有することが好ましい。

#### 【0009】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第3の数の行アドレスビットと前記第2の数の列アドレスビットとによってインデックスされ、前記行アドレスビットの前記第1サブセットは、前記行アドレスビットの前記第3の数になり、前記メモリ装置は、前記サブアレイごとに行バッファを含み、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第1サブセットによって特定されるサブアレイからの行データを対応する行バッファにロード(oad)する段階をさらに有することが好ましい。

20

前記後続アドレス命令語の行アドレスビットの中の前記第2サブセットによって特定されるサブアレイの中の1つを選択する段階をさらに有することが好ましい。

30

#### 【0010】

前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットによってインデックスされ、前記列アドレスビットの前記第4サブセットは、前記列アドレスビットの前記第4の数になり、前記メモリ装置は、前記サブアレイごとに行バッファを含み、前記サブアレイ各々において、前記行アドレス命令語に応答して対応する前記第1の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードする段階をさらに有することが好ましい。

40

前記以前アドレス命令語の列アドレスビットの中の前記第3サブセットによって特定されるサブアレイの中の1つを選択する段階をさらに有することが好ましい。

#### 【0011】

上記目的を達成するためになされた本発明によるメモリ装置は、メモリ装置であって、各々、第1の数の行アドレスビットによってインデックスされる行と、第2の数の列アドレスビットによってインデックスされる列とによって配列されるデータを格納するストレージセルを含み、前記メモリ装置のデータは、第3の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第4の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされ、前記メモリ装置は、前記データのアドレッシングとして、前記第1の数が前記第2の数よ

50

り大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビットの第2サブセットとに分離し、前記第1サブセットを前記行アドレス命令語で特定し、前記第2サブセットを後続アドレス命令語で特定し、前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語として発行し、前記行アドレス命令語の発行後、前記後続アドレス命令語の発行を行うことを実行し、前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、前記第2の数の列アドレスビットを列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前アドレス命令語で特定し、前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行し、前記列アドレス命令語の発行前に、以前アドレス命令語の発行を行うことを実行し、前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、前記列アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われ、前記後続アドレス命令語の発行は前記行アドレス命令語の発行の直後に行われ、前記以前アドレス命令語の発行は前記列アドレス命令語の発行の直前に行われることを特徴とする。

#### 【0012】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記アーキテクチャは、前記列アドレス命令語とデータバスのデータアクセス可能時点との間の遅延を示す第1アクセス時間によって定義され、前記データのアドレッシングとして、前記第1アクセス時間より長い第2アクセス時間内に前記行のイニシャル列アクセスを実行することと、前記第1アクセス時間内に前記行への後続列アクセスを実行することと、をさらに含むことが好ましい。

#### 【0013】

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第3の数の行アドレスビットと前記第2の数の列アドレスビットによってインデックスされ、前記行アドレスビットの前記第1サブセットは、前記行アドレスビットの前記第3の数になり、前記メモリ装置は、前記サブアレイごとに行バッファを含み、前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第1サブセットによって特定されるサブアレイからの行データを対応する行バッファにロードすることを含むことが好ましい。

前記データのアドレッシングにおいて、前記後続アドレス命令語の行アドレスビットの中の前記第2サブセットによって特定されるサブアレイの中の1つを選択することをさらに含むことが好ましい。

#### 【0014】

前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットによってインデックスされ、前記列アドレスビットの前記第4サブセットは、前記列アドレスビットの前記第4の数になり、前記メモリ装置は、前記サブアレイごとに行バッファを含み、前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記第1の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードすることをさらに含むことが好ましい。

前記データのアドレッシングは、前記以前アドレス命令語の列アドレスビットの中の前記第3サブセットによって特定されるサブアレイの中の1つを選択することをさらに含むこ

とが好ましい。

**【 0 0 1 5 】**

上記目的を達成するためになされた本発明によるメモリモジュールは、複数のメモリ装置を有し、前記複数のメモリ装置の各々は、各々の第1の数の行アドレスビットによってインデックスされる行と、第2の数の列アドレスビットによってインデックスされる列とによって配列されるデータを格納するストレージセルを含み、前記メモリ装置のデータは、第3の数の行アドレスビットで特定される行アドレス命令語と、前記行アドレス命令語に後続する第4の数の列アドレスビットで特定される列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされ、前記複数のメモリ装置の各々は、前記データのアドレッシングとして、前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビットの第2サブセットとに分離し、前記第1サブセットを前記行アドレス命令語で特定し、前記第2サブセットを後続アドレス命令語で特定し、前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行し、前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、前記第2の数の列アドレスビットを列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分離し、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前アドレス命令語で特定し、前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行する、ことを実行し、前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、前記列アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われ、前記後続アドレス命令語の発行は前記行アドレス命令語の発行の直後に行われ、前記以前アドレス命令語の発行は前記列アドレス命令語の発行の直前に行われることを特徴とする。

**【 0 0 1 6 】**

前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記アーキテクチャは、前記列アドレス命令語とデータバスのデータアクセス可能時点の遅延を示す第1アクセス時間によって定義され、前記データのアドレッシングとして、前記第1アクセス時間より長い第2アクセス時間内に前記行のイニシャル列アクセスを実行することと、前記第1アクセス時間内に前記行への後続列アクセスを実行することと、をさらに含むことが好ましい。

**【 0 0 1 7 】**

前記メモリ装置の各々において、前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々前記第3の数の行アドレスビットと前記第2の数の列アドレスビットによってインデックスされ、前記行アドレスビットの前記第1サブセットは、前記行アドレスビットの前記第3の数になり、前記メモリ装置は、前記サブアレイごとに行バッファを含み、前記データのアドレッシングは、前記サブアレイの各々において、前記行アドレス命令語に応答して対応する前記行アドレスビットの前記第1サブセットによって特定されるサブアレイからの行データを対応する行バッファにロードすることを含むが好ましい。

前記メモリ装置の各々において、前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、前記データは、複数の行と列を有する複数のサブアレイに配列され、各々の前記サブアレイは、行と列のサブセットになり、各々の前記第1の数の行アドレスビットと前記第4の数の列アドレスビットによってインデックスされ、前記列アドレスビットの前記第4サブセットは、前記列アドレスビットの前記第4の数になり、前記メモリ装置は、前記サブアレイ

10

20

30

40

50

ごとに行バッファを含み、前記データのアドレッシングは、前記サブアレイの各々に対し、前記行アドレス命令語に応答して対応する前記第1の数の行アドレスビットによって特定されるサブアレイからの行データを対応する行バッファにロードすることをさらに含むことが好ましい。

前記メモリ装置の各々は、相変化ランダムアクセスメモリ (phase-change random access memory、PRAM) 装置を含むことが好ましい。

また、上記目的を達成するためになされた本発明によるメモリ装置のデータアドレッシング方法は、メモリ装置内のデータは、第1の数の行アドレスビットと第2の数の列アドレスビットによって各々インデックスされる行と列のアレイ内に配列され、前記データは、第3の数の行アドレスビットを特定する行アドレス命令語と、第4の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされる前記メモリ装置の前記データのアドレッシング方法において、前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビットの第2サブセットとに分離する段階と、前記第1サブセットを前記行アドレス命令語で特定し、前記第2サブセットを後続 (next) アドレス命令語で特定する段階と、前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行する段階と、を有し、前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、前記行アドレス命令語を発行する段階の直後に、前記列アドレス命令語を発行する段階をさらに有し、前記後続アドレス命令語の発行は、前記行アドレス命令語の発行の直後に実行されることを特徴とする。

また、上記目的を達成するためになされた本発明によるメモリ装置のデータアドレッシング方法は、メモリ装置内のデータは、第1の数の行アドレスビットと第2の数の列アドレスビットによって各々インデックスされる行と列のアレイ内に配列され、前記データは、第3の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第4の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされる前記メモリ装置の前記データのアドレッシング方法において、前記第2の数が前記第1の数より大きく、かつ、前記第2の数が前記第4の数より大きく、かつ、前記第1の数と前記第3の数が同じ場合、前記第2の数の列アドレスビットを、列アドレスビットの第3サブセットと列アドレスビットの第4サブセットとに分割する段階と、前記第4サブセットを前記列アドレス命令語で特定し、前記第3サブセットを以前 (previous) アドレス命令語で特定する段階と、前記列に対する列アクセスの一部又は全部として前記列アドレス命令語を発行する段階と、前記列アドレス命令語の発行前に、前記以前アドレス命令語を発行する段階と、を有し、前記以前アドレス命令語は、前記第3の数の行アドレスビットを特定する前記行アドレス命令語であり、前記列アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われ、前記データのアドレッシングとして、前記行アドレス命令語の発行後、直ちに後続アドレス命令語を発行するか、或いは前記以前アドレス命令語は、前記列アドレス命令語の発行直前に発行されることを特徴とする。

また、上記目的を達成するためになされた本発明によるメモリ装置は、メモリ装置であつて、各々、第1の数の行アドレスビットによってインデックスされる行と、第2の数の列アドレスビットによってインデックスされる列とによって配列されるデータを格納するストレージセルを含み、前記メモリ装置のデータは、第3の数の行アドレスビットを特定する行アドレス命令語と、前記行アドレス命令語に後続する第4の数の列アドレスビットを特定する列アドレス命令語によって定義されるアーキテクチャを使用してアドレッシングされ、前記メモリ装置は、前記データのアドレッシングとして、前記第1の数が前記第2の数より大きく、かつ、前記第1の数が前記第3の数より大きく、かつ、前記第2の数と前記第4の数が同じ場合、前記第1の数の行アドレスビットを行アドレスビットの第1サブセットと行アドレスビットの第2サブセットとに分離し、前記第1サブセットを前記行

10

20

30

40

50

アドレス命令語で特定し、前記第2サブセットを後続アドレス命令語で特定し、前記メモリ装置の行に対する行アクセスの一部又は全部として前記行アドレス命令語を発行することを実行し、前記後続アドレス命令語は、前記第4の数の列アドレスビットを特定する前記列アドレス命令語であり、前記行アドレス命令語を発行した直後に、前記列アドレス命令語の発行を行って、前記データをアドレス指定し、前記後続アドレス命令語の発行は、前記行アドレス命令語の発行の直後に行われることを特徴とする。

**【発明の効果】**

**【0018】**

容量問題とアドレッシングの問題との解決のためにアドレスピンの追加が1つの方法であるが、ピンは費用が掛かり、そしてSDRAM(例えば、DDR4)ピンの規定を維持することが一般的に望ましく、本発明に係るメモリ装置のデータアドレッシング方法及びメモリ装置並びにメモリモジュールによれば、ピン費用又はピン数の増加無しで高容量SDRAMライクメモリのアドレッシング方法を提供することができる。

10

また、本発明の方法によれば、モジュールからの支援と情報に基づいて初期化動作で設定されることができる。

**【図面の簡単な説明】**

**【0019】**

【図1】本発明の実施形態に係るメモリモジュールとメモリ装置とを示す概略図である。

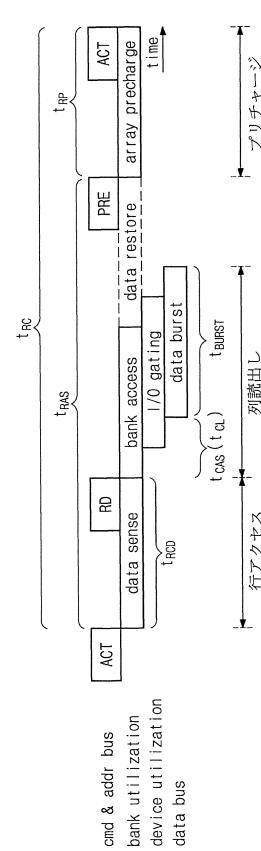

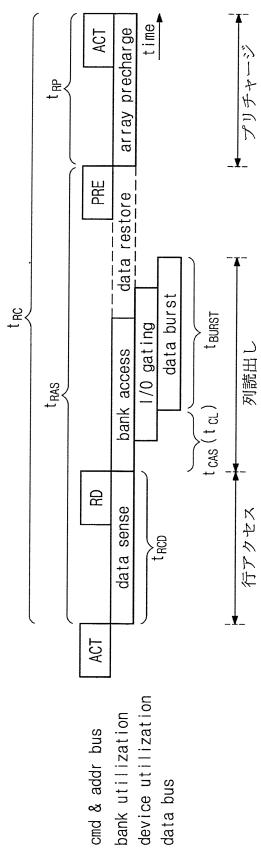

【図2A】本発明の実施形態に係る拡張されたアクティブ(ACT+)命令語を使用するデータ接続動作の例を示す図である。

20

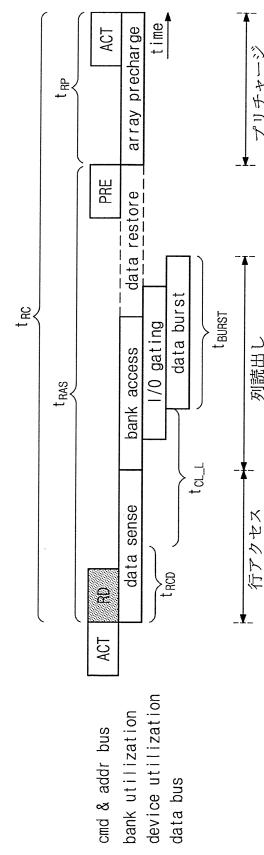

【図2B】本発明の実施形態に係る拡張されたアクティブ(ACT+)命令語を使用するデータ接続動作の例を示す図である。

【図3】本発明の実施形態に係る拡張読出し命令語(RD+)を使用したデータアクセス動作の例を示す図である。

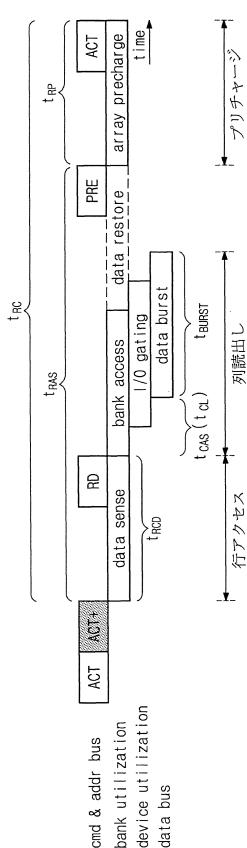

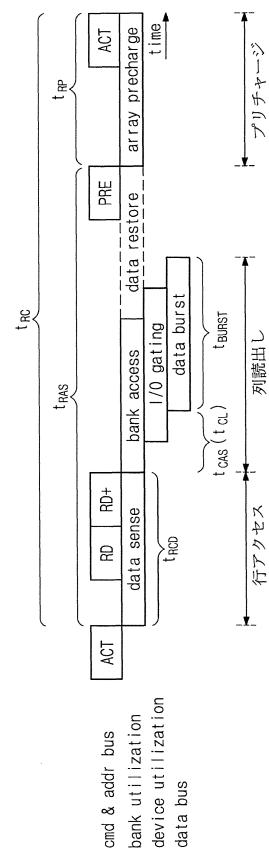

【図4A】本発明の実施形態に係るバックツーバックRAS/CAS命令語シーケンスを使用するデータアクセス動作の例を示す図である。

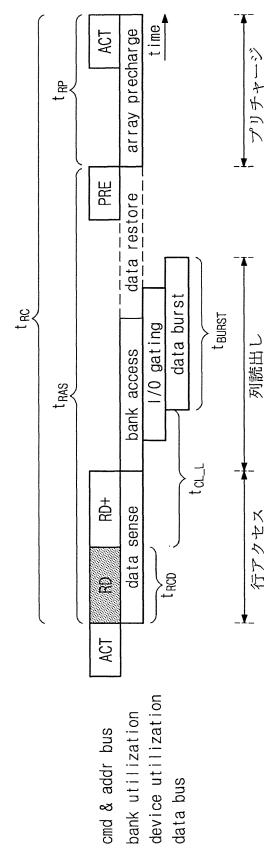

【図4B】本発明の実施形態に係るバックツーバックRAS/CAS命令語シーケンスを使用するデータアクセス動作の例を示す図である。

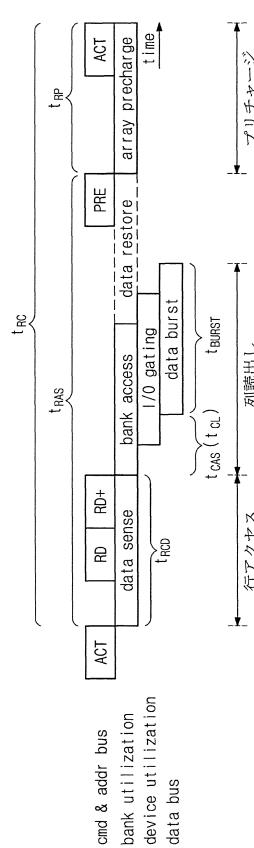

【図5】本発明の実施形態に係るバックツーバックCAS/CAS(二重CAS)命令語シーケンスを使用するデータアクセス動作の例を示す図である。

30

【図6】本発明の実施形態に係るバックツーバックRAS/CAS又はCAS/CAS命令語シーケンスを使用するデータアクセス動作の例を示す図である。

【図7】本発明の実施形態に係る例示的な拡張された読出し(RD+)命令語のためのDDR4 SDRAMの真理表である。

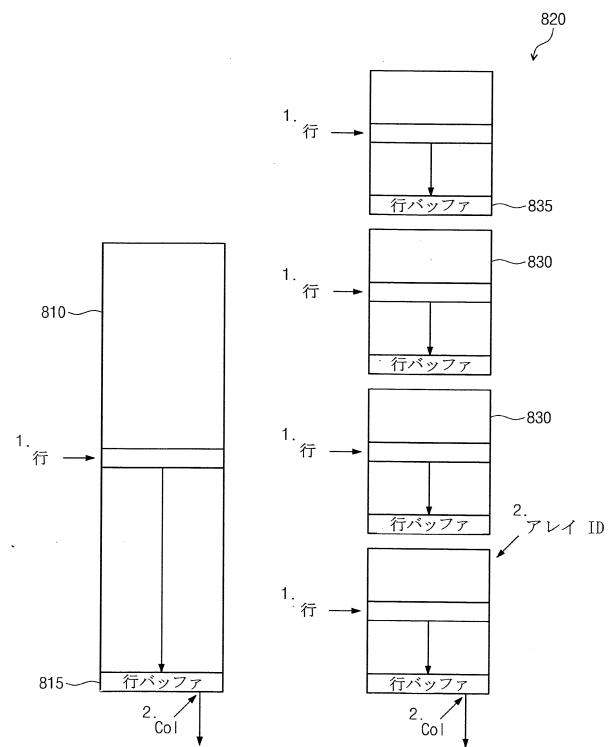

【図8】本発明の実施形態に係るメモリチップの行構造を例示的に示す図である。

【図9】本発明の実施形態に係る例示的な拡張された書き込み(WR+)命令語のためのDDR4 SDRAMの真理表である。

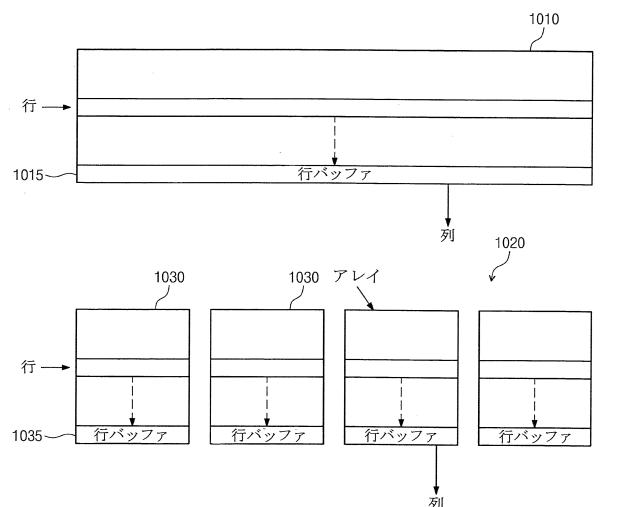

【図10】本発明の実施形態に係るメモリチップの列構造を例示的に示す図である。

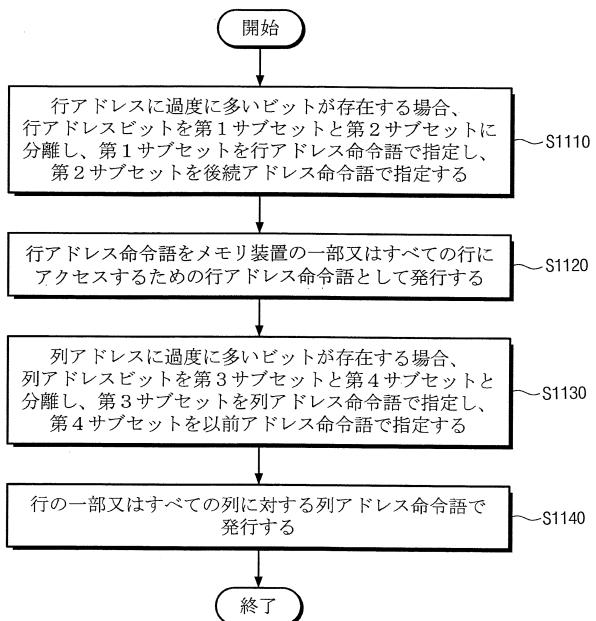

【図11】本発明の実施形態に係るメモリ装置のアドレッシング方法の例を説明するためのフローチャートである。

40

**【発明を実施するための形態】**

**【0020】**

次に、本発明に係るメモリ装置のデータアドレッシング方法及びメモリ装置並びにメモリモジュールを実施するための形態の具体例を図面を参照しながら説明する。

**【0021】**

ここで、本発明の実施形態を説明するのに使用される用語“～できる”の使用は“本発明の1つ又はそれ以上の実施形態”を示す。その上で、本発明の実施形態を説明するのに使用される代案を意味する用語“又は”は各々リストされた項目に対応する“本発明の1つ又はそれ以上の実施形態”を示す。

**【0022】**

50

本発明の実施形態に係る、ここで説明する電子又は電気装置及び／又は他の関連する装置又は構成は、適切なハードウェア、ファームウェア（例えば、A S I C）、ソフトウェア、又はソフトウェア、ファームウェア、及びハードウェアの組み合わせを使用して具現することができる。

例えば、これら装置の多様な構成は1つの集積回路（I C）チップ上に又は分離された集積回路チップに形成されることがある。

また、これら装置の多様な構成はフレキシブル印刷回路フィルム上に、テープキャリヤーパッケージ（T C P）、印刷回路基板（P C B）、又は1つの基板上に形成することができる。

#### 【 0 0 2 3 】

加えて、これらの装置の多様な構成は1つ又はそれ以上のコンピュータ装置内に装着された1つ又はそれ以上のコンピュータプロセッサ（マイクロプロセッサのような）で駆動され、コンピュータプログラム命令語を実行し、ここに開示される多様な機能を遂行するための他のシステム構成と相互作用するプロセスやスレッドである。

コンピュータプログラム命令語は、ランダムアクセスメモリ（R A M）のような標準メモリ装置を使用するコンピューティング装置内に装着されたメモリに格納することができる。コンピュータプログラム命令語は、また他の非一時的（n o n - t r a n s i t o r y）であるコンピュータ読出し可能記録媒体（例えば、C D - R O M、フラッシュドライブ等のような）に格納することができる。

加えて、この分野の技術に熟練された人は本発明の思想及び範囲を逸脱しなくて多様なコンピューティング装置の機能が1つのコンピュータ装置に組み合わせ又は集積されるか、或いは特定コンピューティング装置の機能が1つ又はそれ以上のコンピューティング装置に分散されることをよく理解できる。

#### 【 0 0 2 4 】

D D R 4 S D R A Mで、メモリ装置（例えば、チップ）は行と列とのアレイで構成される。

行はS D R A M装置でのアクセスの大きさの単位（G r a n u l a r i t y、即ち5 1 2、1 0 2 4、又は2 0 4 8バイトのような）、例えば装置の行内のメモリ位置が読み出されるか、或は書き込まれる時、アクセスされるデータ量を示す。

列は読み出されるか、或は書き込まれる行内で特定部分（例えば、4、8、1 6ビット、データワードであると称される）を示す。

S D R A M装置の行を行バッファに持ってくるために行アドレスが優先的（A C T命令語と共に）に提供され、行データが行バッファに存在する間に行の特定部分を読み出すか、或いは書き込むために列アドレス（例えば、読み出し（R D）又は書き込み（W R）命令語と共に）が後続される。

各行D M S装置の全体容量に比べて相対的に小さいバイト数であるので、列に比べてはるかに多い行が存在する。したがって、行内の列をアドレッシングするためのビット数より行をアドレッシングするためにさらに多いビット数（又はハードウェアでのピン数）が使用される。

#### 【 0 0 2 5 】

その上に、列アドレスより大きいアドレスである行アドレスが先ず提供されるので、D D R 4 S D R A Mの行アドレスピンの一部は列アドレスを提供するために再使用されることもある。

基本的なメモリチップの行と列の数がこのような関係に対して均衡をなす時、アドレスピンは列アドレス命令語が提供される間に効率的に再使用され、このアーキテクチャ（行と列アドレスピンの共有）の効率的な使用が可能である。

しかし、行と列の数の均衡がとれていない場合、アドレスピンは効率的に再使用されることできなく、アドレッシングを通じて提供されるメモリ容量は制限される。

例えば、D D R 4で行の数は1 8ビットでアドレッシング可能であり、列の数は1 0ビットでアドレッシング可能である。

10

20

30

40

50

これは対応するメモリチップのサイズのみならず、アドレッシングを通じて最大に活用可能なデータシステム（行と列の数）を制限する。

例えば、多い数の行（例えば、18ビット値以上）を支援するが、相対的に少ない数の列を支援するメモリチップはこのようなアドレッシング方式の充分な長所を活用することを難しくする。

#### 【0026】

本発明の1つ又はそれ以上の実施形態で、高容量メモリモジュール（例えば、DDR4 SDRAMメモリモジュール）を支援するための方法と構造を提供する。

例えば、所定の実施形態は不揮発性ストレージ（PRAMのような）アクセスのためにSDRAMライク（例えば、DDR4）アドレスピン定義を提供する。 10

本発明の1つ又はそれ以上の実施形態で、アクティブ命令語（ACT）が拡張された命令語（例えば、（ACT+））が提供される。

この新しいアクティブ命令語（ACT+）は、拡張されたアドレッシング能力（拡張された行アドレス）のために既存のアクティブ命令語（ACT）に1つの追加的なサイクルが付加することができる。

他の実施形態で、この拡張アクティブ命令語（ACT+）は、拡張されたアドレッシング機能のための全く新しい（分離された）命令語である。

#### 【0027】

本発明の1つ又はそれ以上の実施形態によれば、拡張された読み出し／書き込み命令語（RD/（WR+））又は他の列アドレス命令語が提供される。

これらの新しい命令語は既存に存在する読み出し／書き込み命令語（RD/WR）に拡張されたアドレッシング機能（拡張された列アドレス）のために1つのサイクルをさらに含むことができる。 20

他の実施形態で、この拡張読み出し／書き込み命令語（RD/（WR+））は拡張されたアドレッシング機能のための新しい（分離された）命令語である。

#### 【0028】

本発明の他の実施形態によれば、変形されたバックツーバック行アクセス／列アクセス（RAS/CAS、以下、「行アクセスストロボ’、及び‘列アクセスストロボ’と称する）命令語（変形された読み出し又は書き込み命令語）が対応するタイミング調整と共に提供される。

例示的に、新しいRD/WRCAS（読み出し／書き込み命令語とそれに対応する列選択ビット）定義が提供されて、非使用ビット（例えば、列アドレス命令語区間で使用されない行又は列アドレスビット）が拡張された行アドレスを伝達するために用途変更され、異なって設定されるか、或いは予め決定された（即ち、アーキテクチャに付加された）制限を超えてアドレッシングビットの数を効果的に増加させる。 30

例えば、1つ又はそれ以上の実施形態で、このような新しい（又は用途変更された）読み出し／書き込み命令語を支援するために変形されたアクティブ（ACT）及び読み出し／書き込みタイミングに依存する新しいタイミングパラメーターが使用される。

#### 【0029】

他の実施形態によれば、変形されたバックツーバック列アクセス（CAS/CAS）命令語が提供される。

例えば、新しい読み出し／書き込み命令語（RD/WR）が2つのCAS命令語の中でいずれか1つに拡張された列又は行アドレスビットの提供を通じて拡張された列（又は行）機能の支援が提供される。 40

本発明の他の実施形態によれば、マルチ行バッファ構造（例えば、命令語調整及び装置再構成と共に）が提供される。

例えば、基本アーキテクチャがあまりにも多い数の行アドレスを単なる支援する反面、新しい装置構造によって追加的な行アドレスのインデックスが提供される。

一例として、1つ又はそれ以上の実施形態で、新しい読み出し／書き込みCAS命令語が提供され、拡張された行アドレス又は拡張された列アドレスのような拡張されたアドレスを伝達するために非使用ビット（例えば、列アドレス命令語区間で非使用行又は列アドレスビ

10

20

30

40

50

ット)の用途が変更される。

#### 【0030】

他の実施形態によれば、マルチ列バッファ構造(例えば、命令語調整及び装置再構成と共に)が提供される。

例えば、基本アーキテクチャがあまりにも多い数の列アドレスを単なる支援する反面、新しい装置構造によって追加的な列アドレスのインデックスが提供される。

一例として、1つ又はそれ以上の実施形態で、新しいアクティブ命令語R A Sが提供され、拡張された列アドレスのような拡張されたアドレスを伝達するために非使用ビット(例えば、行アドレス命令語区間で非使用行アドレスビット)の用途が変更される。

本発明の実施形態に係る先に説明されるか、或いは他の方法はモジュールから情報又は支援に基づいてメモリモジュールのメモリ装置の各々の初期化の時に設定することができる。

#### 【0031】

説明の簡易化のために、以下で記述される内容は、主に4-ビット、8-ビット、又は16-ビット幅のD R A Mチップに適用されるJ E D E C D D R 4 S D R A M標準(簡単に、D D R 4)に基づくが、本発明はここに制限されない。

他の実施形態で、例えば、他のS D R A M標準(他のD D R標準を含む)のような他の標準で本発明の思想と範囲が適用されることはこの分野で一般的な技術を習得した者には明確である。

異なって説明されない限り、D D R 4の言及は“J E D E C S t a n d a r d f o r D D R 4 S D R A M, v o l u m e J E S D 7 9 - 4 A ( N o v e m b e r 2 0 1 3 ) o f t h e J E D E C S o l i d S t a t e T e c h n o l o g y A s s o c i a t i o n g o v e r n s”を指称し、本発明のレファレンスとして含まれる。

#### 【0032】

加えて、詳細な説明の全般にわたって、用語“K B”、“M B”、“G B”、及び“T B”は2の累乗に対応するバイト(B、又はコンピュータアーキテクチャ標準で8-ビット)を示す。

即ち、1 K B = 1 0 2 4 b y t e s 、 1 M B = 1 0 2 4 K B 、 1 G B = 1 0 2 4 M B 、 及び 1 T B = 1 0 2 4 G B を意味する。

説明を簡単にするために、たとえば、実際には他の数のチップ(例えば、8データチップ当たり1つの追加チップ)がエラー検出や訂正のような機能のために使用されるが、D R A Mチップはデータチップであり、2の累乗(例えば、4チップ、8チップ、16チップ)に対応する数ぐらいで提供されることと仮定する。

説明を簡単にするために、用語“ページ”がここでは“行”と同意語として使用するが、これらの用語の全ては特定行に対応するメモリチップのメモリ部分に関連されたものである。

このように、“チップ”と“装置”との全てがメモリハードウェアを指す時、同意語として使用するが、この2つは全てのメモリモジュールに脱/付着することができる(或いは積層されたメモリチップのように、場合によってはアドレッシング可能な)最小メモリ要素を示す。

#### 【0033】

図1は、本発明の実施形態に係るメモリモジュール100とメモリ装置120とを示す概略図である。

例えば、メモリモジュール100は、D D R 4 S D R A M D I M Mのようなデュアルラインメモリモジュール(D I M M)である。

メモリモジュール100は、ピン相互接続構造を有する印刷回路基板110(以下、P C Bと記す)、P C B 1 1 0に実装されるメモリ装置120(例えば、R A Mチップのようなメモリチップ)、及びメモリ装置120と、ワークステーションや個人用コンピュータのマイクロプロセッサのようなメモリモジュール100を使用する電子装置とを接続するためのピン130とを含む。

P C B 1 1 0は、両面に形成されるピン130とメモリ装置120と、貫通するピン配線構造を含み、メモリ装置120は積層(貫通シリコンビア又はT S Vを使用して)され得る。

10

20

30

40

50

**【 0 0 3 4 】**

図 2 A 及び図 2 B は、各々本発明の実施形態に係る拡張されたアクティブ（又は A C T + ）命令語を使用するデータ接続動作の例を示す図である。

図 2 A 及び図 2 B で、多様なタイミングパラメーター（例えば、 t R C 、 t R A S ）を示す。

これらのパラメーターは、関連された部分でより詳細に説明されるが、これらの定義と使用は、 J E D E C D D R 4 S D R A M 標準によって提供され、当業者に広く公知された事項である。

**【 0 0 3 5 】**

D D R 4 標準で、 C I D （チップ I D 、又はランク）のために 3 つのピンが、バンク（メモリチップ内の行と列の分離されたアレイ）アドレッシングのために 4 つのピンが、行（そして、列）アドレッシングのためには 18 個のピンが使用される。 10

D D R 4 S D R A M のアドレスピンは、行と列のアドレッシングのために再使用される。 D D R 4 標準で、メモリコントローラは互いに異なるサイクルの間に同一のピンに伝達される 2 つの命令語（ A C T ( a c t i v a t e ) と R D / W R ( r e a d / w r i t e ) ）を使用して S D R A M アドレスにアクセスする。

**【 0 0 3 6 】**

アクティブ命令語（ A C T ）は、行アドレス（ 18 ピン）を使用して行を活性化させ、活性化された行を行バッファにロードさせる一方、読み出し / 書込み命令語（ R D / W R ）は行バッファから対応する列を選択するために列アドレス（ 10 ピン）を使用する。 20

ここで、“ R D / W R ” は読み出し命令語（ R e a d c o m m a n d ）と書込み命令語（ W r i t e c o m m a n d ）（又は他の列アドレス命令語）の縮約された表現であり、これらの 2 つの命令語の形態又は分類は特定的に言及（例えば、“ R D / W R ” 、 “ R D ” 、及び“ W R ” は読み出し又は書込み命令語を示すための同意語として使用される）しない以上区分されなく、使用される。

**【 0 0 3 7 】**

D D R 4 標準で、現在のピン使用及びアドレッシング方式は高容量メモリを支援しない。例えば、現在の D D R 4 標準は、 D R A M チップ当たり 2 G B 容量であり、ランク当たり（同時にアドレッシング可能な） 16 D R A M チップ（例えば、各々の D R A M チップはランク内で 1 回に総  $16 \times 4 = 64$  ビットのデータアクセスのために 4 ビットデータを提供する）、及び 8 個ランク（又は積層可能である D R A M チップのセット）のようなチップ構成を仮定すれば、 D I M M 当たり 256 G B のみを支援することができる。 30

**【 0 0 3 8 】**

しかし、この容量はこのような厳格な設定条件のみで得られる。多くの場合、アーキテクチャによって規定された（意図された）行と列の数と基底のハードウェアで支援される実際の行と列の数の間には不均衡が存在し（例えば、アーキテクチャの効率的な具現のために設計されたことより過度に多い数の行と過度に少ない数の列がハードウェアに存在するか、又は逆に、過度に少ない行と過度に多い数の列が存在する場合）、これは必然的にピンの消耗を引き起こす。

全体の容量の増加や不均一な行 / 列の数を許容するために 1 つの解決策はさらに多いピンを追加することである。 40

しかし、このような解決策は費用を過度に必要とし、現在の D D R 4 標準の変更を必要とする。

**【 0 0 3 9 】**

本発明の実施形態によれば、図 2 B に示すように、 1 つの可能な解決策は 2 サイクルのアクティブ（ A C T ）命令語（通常の 1 サイクルアクティブ命令語の代わりに）である、拡張アクティブ命令語（ A C T + ）を使用することである。

比較として、図 2 A は D D R 4 での標準アクティブ命令語（ A C T ）を示す。

図 2 A と図 2 B （そして、他のタイミング図）で、上方から下方に [ ( i ) メモリ命令語及びアドレスバス、 ( i i ) メモリバンク、 ( i i i ) メモリ装置（例えば、 D R A M チ 50

ップ)、及び(i v)メモリデータバス]であるアクセスされる4つの別の水平リソースと共にタイミング(時間)は左側から右側に進行する。

要約すれば、メモリモジュール(DIMMのような)上にランクを構成するメモリ(DRAM)チップのセットはバンク単位(メモリチップ内の論理的区分)にアクセスされ、各々のバンクは行で構成され、そして各々の行は複数の列で構成される。

#### 【0040】

各々のDIMMはランクやDRAMチップのセットを複数に含む。

説明を簡単にするために、DIMMにアクセスする時、1つのランク内に1つのシングルバンクのみを含む單一ランク構成のみを考慮する。

アクティブ命令語(ACT)は、バンク(例えば、3又は4ビット)とバンク内の行(例えば、18ビットまで)を指定することができる。 10

図2Aと図2Bで左側から右側の時間軸に沿って行が先にアクセスされ(ACT命令語によって指定される)、列(RDのような読み出し/書き込み(RD/WR)命令語によって指定される)が続いてアクセスされる。

#### 【0041】

これは装置当たり4又は8データワード又はDIMM当たり32又は64バイトのデータバースト(Burst)が読み出されるか、或は書き込まれるようにする。

各々の装置の同一の行で4又は8データワード(DIMMで32又は64バイトの連続バイト)の追加的なアクセスは迅速に遂行される。

しかし、他の行へのアクセスのために、プリチャージ命令語(PRE)を使用することができ、後続するアクティブ命令語(ACT)によってアクセスされる次の行の準備のために現在の行が再びメモリアレイ内に書き込まれる。 20

#### 【0042】

図2Bの実施形態で、拡張されたアクティブ命令語(ACT+)が使用される。

ここで、アクティブ命令語(ACT)は1つのクロックサイクルから2つのクロックサイクルに拡張される。

即ち、アクティブ命令語(ACT)は第2クロックサイクル(ACT+)で追加的なアドレスビットを提供することができるので、提供される行アドレスビットの数を増加させることができる。

例えば、DDR4標準で、追加されるクロックサイクル(ACT+)は同一の行アドレスピンを通じて行アドレス(総36ビット)の他の18ビット(拡張ビット)を伝送するのに使用され、これは相変わらず同一(又はそれ以上の)である量のデータをアドレッシングできながらも、はるかに狭い行(即ち、さらに少ない数の列)を許容する。 30

他の実施形態で、拡張されたアクティブ命令語(ACT+)が適切な演算コード(opcode)を有するように10又は12行アドレスビットが拡張されたアクティブ命令語(ACT+)によって提供することができる。

#### 【0043】

例えば、所定の実施形態で、拡張されたアクティブ命令語(ACT+)を支援するメモリ装置は、標準ACT(单一サイクル)RAC命令語と、又は新しい(2個サイクル)ACT/(ACT+)プロトコルを認識するために初期化時に設定することができる。

このような方式には、単なる1つのACT命令語のみが存在し、メモリ装置は標準DDR4アーキテクチャによって、発行される單一アクティブ命令語(ACT)を受信するか、又は拡張されたACT(ACT+)プロトコルが使用される場合、連続されるサイクルの間に発行される2回のアクティブ命令語を受信することを予測することができる。 40

#### 【0044】

各行が単なる1つの4ビットの列を有する極端の場合でも、先に説明した2サイクルの間に36行アドレスビットを有する拡張されたアクティブ命令語(ACT+)を使用すれば、この拡張された行アドレス機能を使用する單一DRAMチップはピン数やピン費用の変更や増加無しでこのような4-ビット列(ニブル又はハーフバイト)の240又はDDR4アーキテクチャ規格の512GBデータ(即ち、4ビットのバンクアドレス及び36ビ 50

ットの拡張された行アドレスを使用して)にアクセスすることができる。

これはDDR4標準が全体DIMM(128個のDRAMチップまで含む)のために提供することより単一メモリチップで既にさらに大きい容量値である。

#### 【0045】

所定の実施形態で、さらに狭い行はDDR4DIMMでこのようなアクティブ命令語(AC<sub>T</sub>+ )の拡張のために従来のSDRAMチップを相変化RAM(以下、PRAM)に代替するのに適用することができる。

例えば、PRAMは、4-ビット幅(1024列)に対して512バイトサイズの行を有するDRAMチップを含む比較できるSDRAMチップに比べて狭い行(例えば、少ない数の列)の数を増加させるのに容易である。

拡張されたアクティブ(AC<sub>T</sub>)命令語の他の実施形態で、アクティブ(AC<sub>T</sub>)命令語は変更されなく、追加的なアドレッシングビット(10又は12ビット)を伝達するために“AC<sub>T</sub>”と称される新しい1サイクルの命令語が単純に後続され得る。

#### 【0046】

例えば、図2Bに示したように、(AC<sub>T</sub>+ )命令語は拡張された行情報を伝達するために第1ACT命令語に直ちに続く(即ち、先に説明した2サイクルの(AC<sub>T</sub>+ )命令語のような方式に動作)。

新しい(AC<sub>T</sub>+ )命令語それ自体は、ACT命令語(DDR4で専用命令語ビットを有する)に比べて著しく多いビット数が要求されるので、標準ACT命令語が1サイクルで2サイクルに長くなる時、使用可能なアドレスビットの長さより残っている可用アドレスビットの数は若干減少(18ビットの代わりに10又は12ビット)することができる。

#### 【0047】

図3は本発明の実施形態に係る拡張された読み出し(RD+)命令語を使用したデータアクセス動作の例を示す図である。

図3に示すような他の実施形態で、読み出し/書き込み(RD/WR)命令語(又は他の列アドレス命令語)は先に説明した追加された列情報を伝達するためのACT命令語に対する変更方式と同一の方式に変更することができる。

例えば、DRAMサイズは、ピン費用やピン数の増加無しで追加的なアドレッシングビット(10又は12のさらに多い列アドレスビット)を指定するためのRD/(WR+)命令語を使用することによって列サイズが10列アドレスビットで20又は22列アドレスビットに増加する方式に増加することができる。

#### 【0048】

上述した技術の中でいずれか1つ(又は2つの技術の組み合わせ)はピン費用やピン数の変更無しでメモリチップのアドレス機能(即ち、TBサイズやそれ以上に)を画期的に増加させることができる。

(AC<sub>T</sub>+ )又はRD/(WR+)の特別な具現は、DIMMの固定された機能である必要はない。

例えば、所定の実施形態では、拡張されたACT命令語又は拡張されたRD/WR命令語を使用するためのシステムの選択は初期化動作(そして、後続される初期化動作で変更可能な)で実行することができる。

#### 【0049】

図4A及び図4Bは、各々本発明の実施形態に係るバックツーバック(back-to-back)RAS/CAS命令語シーケンスを使用するデータアクセス動作の例を示す図である。

ここで使用するように、RASは“行アドレスストロボ”、CASは“列アドレスストロボ”的本来の意味を有するが、これらの用語の各々はメモリチップの読み出し又は書き込み動作で行アドレスと列アドレスを提供する意味として大部分使用される。

追加的なアドレスビットを提供するための二重CAS(即ち、バックツーバックCAS)シーケンスの例としては、後述する説明及び図6を参照すればよい。

#### 【0050】

10

20

30

40

50

図 4 A、4 B は、本発明の実施形態に係る追加的な行 / 列情報を提供するための追加的な技術、即ち新しいバックツーバック R A S / C A S システムを使用する例を示す。

このメカニズムで、非使用アドレスビット（列又は行）が拡張されたアドレス情報を伝達し、標準読み出し / 書込み（R D / W R）命令語より先に命令語が提供される新しいR D / W R C A S が定義される。

一例として、DDR4 で、行アドレスビットの中の 3 個上位 - ビットが読み出し（R D）及び書込み（W R）命令のために C A S ビットと共に使用可能である。

他の実施形態で、基底のメモリ装置は 10 個列アドレスビットが提供することより少ない列を支援し、したがってこれら余分の列アドレスビットは拡張された行アドレスビットを伝達するのに再割り当てすることができる。

10

#### 【 0 0 5 1 】

他の実施形態で、列アドレス命令語で動的に選択可能な特徴（オンザフライ（o n - t h e - f l y）データバースト長さのような）を制御するために提供される上位行アドレスビットが追加的な拡張されたアドレスビット及び静的設定にデフォルトされた（d e f a u l t e d \_ t o）特定な動的特徴として用途変更することができる。

これらの列アドレスの変更と共に、読み出し / 書込み（R D / W R）命令語の用途変更を支援するために新しいタイミングパラメーターと変更されたアクティブ（A C T）及び読み出し / 書込み（R D / W R）タイミングが提供される。

このような特徴は、標準読み出し / 書込み（R D / W R）プロトコル（R D / W R インストラクションは R D で表現される）を示した図 4 A、及び変更された R A S / C A S 命令語シーケンスを示した図 4 B に説明される。

20

#### 【 0 0 5 2 】

さらに詳細には、図 4 A に示した標準 DDR4 で、後続される読み出し / 書込み（R D / W R）命令語は列アドレス（C A S、10 ビット）を提供する一方、アクティブ（A C T）命令語は行アドレス（R A S、18 ビット）を提供する。

4 個までのバンクビットと共に提供されるこれら 28（18 + 10）ビットはランクへの特定（64 ビット）読み出し又は書き込みアクセスのためにランクを構成する各々の D R A M チップ（例えば、4、8、或いは 16 メモリチップデータ幅（例えば、4、8、或いは 16 ビット）をアドレッシングする。

30

#### 【 0 0 5 3 】

しかし、R A S と C A S をバックツーバック方式に伝達することによって、任意の非使用アドレスビット（例えば、R D 又は W R のような C A S 命令語の 3 つの非使用行アドレスビット共に提供される R A S と C A S のためのビット）は、DDR4 で定義されたことと異なる行及び列配列を有するメモリチップを最大に活用する場合のような異なるフォーマット又は分類にアドレッシングする拡張された行や列を提供するために再設定することができる。

加えて、拡張された行アドレスのために、メモリ装置はアクティブ（A C T）命令語（例えば、データアクセスの遅延を避けるために利用可能である 18 行アドレスビットと共に）によって指定されたすべての行に初期にアクセスするように設定され、（できる限り直ちに）後続する読み出し命令語（R D）に残余（拡張された）行アドレスビットを使用して選択を減少させる。

40

#### 【 0 0 5 4 】

例えば、メモリ装置は、最初提供される 18 行アドレスビットによってアドレッシングできるすべての行のための行バッファを含む。

他の実施形態で、メモリ装置は、すべてのこのような行を 1 つの行バッファにロードすることを開始するが、行アドレスの余りが一旦提供されれば、実際の行が行バッファにロードされるようにただ許諾することができる。

例えば、バックツーバック R A S / C A S 命令語シーケンスでアドレッシングのために利用可能である 31 ビット（18 R A S + 10 C A S + 3 非使用）を使用して、18 ビットの拡張された行アドレスが A C T 命令語に提供され、3 ビット（8 個列）の列アドレス

50

と共に直ちに後続される R D / W R 命令語に残る 10 ビットの拡張された行アドレスの提供が続く。

#### 【 0 0 5 5 】

したがって、何らかのピン数の増加無しでも総アドレス性能は 8 倍増加し、基本的な行と列のサイズが基本メモリチップ技術 ( P R A M のような ) に最適化されるように調整され得る。

他の実施形態で、 C A S ( 可能には非使用アドレスビットの一部によって拡張された ) が列アドレスと共に拡張された行アドレスの余りを伝達する一方、 R A S は単なる行アドレスの一部を伝達することができる ( 又は逆に拡張された列アドレスに対して他の実施形態で具現することができる ) 。

この命令語シークエンスの変更は、メモリモジュールにアクセスするためにメモリコントローラによって使用されるタイミングパラメーターの調整を要求することができる。

#### 【 0 0 5 6 】

例えば、 D D R 4 で、 t R C D と t C L が影響を受ける。

ここで、 t R C D ( R A S と C A S との間の遅延 ) はアクティブ ( A C T ) 命令語と後続する最初読出し ( R D ) 又は書込み ( W R ) 命令語が提供される時間の最小時間 ( 即ち、クロックサイクル ) を意味する ( 即ち、 A C T 命令語の開始 ( 又は終了 ) から対応する R D / W R 命令語の開始 ( 又は終了 ) まで測定される時間 ) 。

その上に、 t C L ( 又は t C A S 、 C A S レイテンシと公知される ) は、 C A S の供給時点とデータバス上で最初列に対応するデータアクセスが可能な時点との間の時間を意味する。

図 4 B で t R C D + t C L に対応する全体時間が図 4 A の対応する時間と同一である ( 即ち、 t R C D の減少量が t C L の増加量と同一 ) 。

#### 【 0 0 5 7 】

図 4 B で、さらに長い t C L 時間にしたがう性能イッシュを避けることを助けるために、幾つかの実施形態ではオープンページ ( オープン行 ) 方策と共に新しいタイミングパラメーター t C L \_ L ( l o n g ) と t C L \_ S ( S h o r t ) とが定義される。

ここで、 t C L \_ L ( 例えば、図 4 B の t C L と示した ) がページ内で列に最初アクセスするために t R C D と共に使用され、 t C L \_ S はオープンページで後続の行バッファ ( 同一行の他の列 ) アクセスのために使用することができる。

これは長短の相違点 ( 例えば、 t R R D \_ L と t R R D \_ S ) を有する D D R 4 に既に存在する一部のタイミングパラメーターと似ているか、又は同様であり、メモリコントローラはいつ t C L \_ L と t C L \_ S を使用するかを追跡することができる。

このような技術の具現には追加的な命令語が必要としなく、メモリ構成は他の t C L を認知する必要がない。

#### 【 0 0 5 8 】

図 5 は、本発明の実施形態に係るバックツーバック C A S / C A S ( 二重 C A S ) 命令語シークエンスを使用するデータアクセス動作の例を示す図である。

図 5 で、 2 つの C A S 命令語 ( 例えば、バックツーバック C A S 又は二重 C A S 命令語、 2 つの R D 命令語 ( R D と R D + ) に示した ) がアドレスの拡張のために使用することができる。

#### 【 0 0 5 9 】

例えば、 1 つ又は 2 つの C A S 命令語は、追加 ( 拡張 ) アドレスビットを提供することができる。

アドレスビットの割り当ては、基本メモリ装置に基づいて設定することができ、メモリ装置の特性を活用するときのためにアドレスビットを 2 つの C A S 命令語の中でさらに適切なところに移動するように割り当てることができる。

例えば、メモリ装置が单一 C A S 命令語によってアドレッシングされることよりさらに多い列を有する大きい行を支援する場合、追加的な列アドレスビットは “ 論理行 ” アドレス拡張として機能するように第 1 C A S 命令語に提供されるが、 “ 論理行 ” アドレス拡張は大き

10

20

30

40

50

い行の各々を多いさらに小さい行に効率的に分割し、さらに小さい行の各々は標準アーキテクチャで最も大きい可能な行サイズである。

第2 C A S 命令語は、以後、標準 C A S 命令語と同様に機能することができる。

#### 【 0 0 6 0 】

その他の例をあげれば、メモリ装置が大きい数の小さい行を支援する場合（即ち、アドレス可能なことよりさらに多い行）、第1 C A S 命令語は、最初の R A S 命令語にマッチングする各々の可能な対応行アドレスのための分離された行バッファと共に、行内で特定列を選択するための標準 C A S 命令語である。

第2 C A S 命令語は、以後のどの行バッファが実際にデータを供給（又は受信）するかを選択するための行バッファ選択に使用される。

他の実施形態で、増加されたアドレッシング機能を使用するために拡張されたアドレスビットは、他の論理方式（例えば、二重 C A S 命令語内で再分配）で整列させることができる。

#### 【 0 0 6 1 】

図6は、本発明の実施形態に係るバックツーバック R A S / C A S 又は C A S / C A S 命令語シーケンスを使用するデータアクセス動作の例を示す図である。

ここで、2つのC A S 命令語（例えば、バックツーバック C A S 又は二重 C A S 命令語、例として、2つのR D 命令語として示したように）が図4 B の実施形態でさらにアドレスを拡張するために使用することができる。

図6で第2 R D 命令語は、( R D + ) 命令語として示している。

先に説明した図2 B の( A C T + ) 命令語と同様に、余分の命令語が余分のアドレスビットを提供するために使用され、したがって10又は12ビットのアドレスビットの追加が可能である。また、これは以前の技術と組み合わせることができる。

#### 【 0 0 6 2 】

限定されない例として、拡張された行アドレスの残余行アドレスビットを提供するための第1 R D 命令語と共に、( R D + ) 命令語が列アドレスを提供するために使用することができる。

他の実施形態で、最初列アドレスビットが第1 R D 命令語と共に提供され、( R D + ) 命令語は拡張された列アドレスの残余アドレスビットを提供するために使用することができる。

他の実施形態で、( R D + ) 命令語（又は、第2 R D 命令語）が列アドレスの全て或いは一部を提供するための一般列アクセス時間まで遅延されるのに反して、第1 R D 命令語は A C T 命令語に直ちに続く（例えば、余分の行アドレスビットと可能には一部の列アドレスビットをバックツーバック R A S / C A S シーケンスの一部に提供）。

#### 【 0 0 6 3 】

他の実施形態で、アドレスビット（列アドレスビットのような）は基本的なハードウェアを適切に収容するために2つのC A S ( R D 又はW R のような) 命令語の間で再分配することができる。

例えば、（拡張された）列アドレスが单一命令語に収容されない同一の（広い）行への連続的なアクセスは、それらの拡張された列アドレスが連續されるR D 又はW R C A S 命令語の対にわたって分離されるようにすることができる。

図6では隣接するA C T 、R D 、及び( R D + ) 命令語を示しているが、実施形態に係つて隣接する命令語の間には（例えば、A C T 命令語とR D 命令語との間又はR D 命令語と( R D + ) 命令語との間）遅延又はギャップが存在することができる。

#### 【 0 0 6 4 】

図7は、本発明の実施形態に係る例示的な拡張された読出し( R D + ) 命令語のためのD D R 4 S D R A M の真理表である。

図7を参照すれば、( R D + ) 命令語は2つの命令語サイクルに掛けて伝達されるように計画される。

この実施形態で、( R D + ) 命令語は初期化時間で設定することができ、第3チップI D

10

20

30

40

50

ビット C 2 を使用する（例えば、（ R D + ）は C 2 = H で、 R D は C 2 = L ）ことによって R D 命令語と区分することができる。

#### 【 0 0 6 5 】

これはメモリチップの積層を単なる 4 つに制限する一方、他の実施形態で、他のビットが 2 つの命令語を区分するために使用することができる。

加えて、図 7 で、オンザフライ（ o n - t h e - f l y ）バーストモードビット（ B C \_ n ）が拡張アドレスビット（ A 1 2 ）の定義に用途変更することができる。

このような実施形態は、オンザフライ（ o n - t h e - f l y ）バーストモード選択を不可能にするが、バーストモードは必要な時にモードレジスター設定を通じて相変わらず変更することができ、他の実施形態では他のビットがアドレスを拡張するために使用することができる。

10

#### 【 0 0 6 6 】

したがって、図 7 の（ R D + ）命令語は、一般的な 10 ビットの列アドレス（ C A ）、2 ビットのバンクグループ（ B G ）、及び 2 ビットのバンクアドレス（ B A ）に加えて 4 ビットの追加的な拡張されたアドレス（ E A ）を伝達することができる。

拡張されたアドレス（ E A ）ビットは、例えばアクティブ命令語 A C T によって指定される 18 ビットの行アドレス（ R A ）や 10 ビットの列アドレス（ C A ）以外の行アドレスや列アドレス情報をさらに指定するのに使用することができる。

#### 【 0 0 6 7 】

加えて、図 7 の（ R D + ）命令語は、第 1 命令語サイクルに直ちに続く第 2 命令語サイクルを有し、この時間は 2 ビットの優先順位フィールドと 10 ビットの読出し ID フィールド（ R I D ）と共に非使用命令語コード（ D D R 4 アーキテクチャでは予備未来フィールド又は R F U ）を利用する。

20

したがって、図 7 に示した残余 3 ビットは R F U になる。

優先順位フィールドと読出し ID フィールド（ R I D ）とは、例えば、メモリ装置が D D R 4 アーキテクチャで定義されたことに追加的な機能又はストレージ（即ち、追加的な行やバッファ）を有する場合、追加的な情報（例えば、追加的なアドレスビットやバッファ選択ビット）を提供することができる。

#### 【 0 0 6 8 】

図 8 は本発明の実施形態に係るメモリチップの行構造を例示的に示す図である。

30

所定の実施形態で、ピン数やピン費用の増加無しで追加的な行 / 列情報を提供するための追加技術はマルチ行バッファ構造を採択することができる。

ここで、メモリ装置は追加アドレスインデックスを支援するために新しい内部組織を有し、追加的な情報を伝達するために新しい R D / W R C A S 命令語システムを使用することができる（拡張された行アドレスの一部に指定するために使用されない C A S ビットを用途変更するように）。

#### 【 0 0 6 9 】

さらに詳細に説明すれば、図 8 で示すように、単なる 1 つのバッファ 8 1 5 （行バッファ）と共に提供される比較的 “ 狹いが、高い（即ち、行の数は多いが、相対的に列の数が少ない） ” メモリアレイ 8 1 0 は各々が自分のバッファ 8 3 5 （行バッファ）を有する複数のさらに小さいアレイ 8 3 0 を有する同様のアレイ構造 8 2 0 に分割することができる。

40

ここで、複数の小さいアレイ 8 3 0 の各々は、メモリアレイ 8 1 0 より行の数は少ないが、列の数は同一の “ 狹くて短い ” 構造を有する。

例えば、アレイ構造 8 2 0 は、すべての行のアドレッシングが可能（即ち、 1 7 又は 1 8 ビットのアドレス空間より小さいか、或いは同一）であるアレイ 8 3 0 を含む一方、メモリアレイ 8 1 0 は通常のアドレッシング可能行より多い行（即ち、 1 7 又は 1 8 ビットのアドレス空間より多い）を有する。

#### 【 0 0 7 0 】

所定の実施形態では、行バッファ 8 3 5 のアドレッシング及びアクセスのためにターゲットデータアレイの行アドレスと共に A C T 命令語が小さいアレイ 8 3 0 の各々に伝達する

50

ことができる。

アレイ 830 の各々は、その行からの情報を対応する自身のバッファ 835 に提供することによって応答する。

次に、列アドレス、アレイ ID と共に RD / WR 命令語が伝達され、これは図 8 の最も下方のアレイ 830 に図に示したようにターゲットアレイ 830 のバッファにデータを書き込むか、或いは読み出すようとする。

#### 【0071】

言い換えれば、拡張された行アドレスは、ACT 命令語に下位行アドレスビット（行 ID）を提供し、そして RD / WR 命令語と共に上位行アドレスビット（アレイ ID）を（CAS フィールドの非使用部分に、或いは図 7 に示した（RD+）命令語の EA、又は RID ビットのような他の非使用アドレスビットに）提供するように支援することができる。このような方式によれば、ピン数やピン費用の増加無しで又は ACT 命令語の発行から対応する行への最初データアクセスまでの遅延の増加無しで他の技術のメモリチップ（RAM のような）に画期的に増加された容量を提供することができる。

10

#### 【0072】

その上に、同一のグループの行（例えば、同一の行 ID を共有する）の追加的な RD / WR 命令語は、追加的なその他の ACT 命令語無しで、他のアレイ ID（最初 ACT 命令語によって対応するバッファに既にロードされた）を特定するための同一の非使用ビット（例えば、EA、RID、非使用 CA）を使用することによって達成することができる。

20

#### 【0073】

図 9 は、本発明の実施形態に係る例示的な拡張された書き込み（WR+）命令語のための DDR4 SDRAM の真理表である。

図 9 を参照すれば、（WR+）命令語は单一サイクル命令語である。

この実施形態で、（WR+）命令語は初期化時間で設定することができ、第 3 チップ ID ビット C2 を使用すること（例えば、（WR+）は C2 = H で、WR は C2 = L）として WR 命令語と区分することができる。

このような特徴は、メモリチップの積層を 4 個に制限する一方、他の実施形態では、他のビットが 2 つの命令語を区分するために使用することができる。

#### 【0074】

加えて、図 9 で、オンザフライ（on - the - fly）バーストモードビット（BC\_n）が拡張されたアドレスビット（A12）の定義のために用途変更することができる。このような実施形態は、オンザフライ（on - the - fly）バーストモード選択を不可能にするが、バーストモードは必要な時にモードレジスター設定を通じて相変わらず変更することができ、他の実施形態では他のビットが拡張されたアドレスビットのために使用することができる。

30

#### 【0075】

したがって、図 9 の（WR+）命令語は、一般的な 10 ビットの列アドレス（CA）、2 ビットのバンクグループ（BG）、及び 2 ビットのバンクアドレス（BA）に加えて 4 ビットの追加的な拡張されたアドレス（EA）を伝達することができる。

EA ビットは、例えば ACT 命令語によって指定される 18 ビットの行アドレス（RA）や 10 ビットの列アドレス（CA）以外の行アドレスや列アドレス情報を追加的に指定するのに使用することができる。

40

#### 【0076】

図 10 は、本発明の実施形態に係るメモリチップの列構造を例示的に示す図である。

図 8 のマルチ行バッファ構造のように、図 10 に示すように、ピン数やピン費用の増加無しで追加的な行 / 列情報を提供するための追加技術はマルチ列バッファ構造を採択することができる。

ここで、メモリ装置は追加アドレスインデックスを支援するために新しい内部構造を有することができ、余分の情報を伝達するために新しい ACT (RAS) 命令語システムを使用することができる（拡張された列アドレスの一部を指定するために使用されない RAS

50

ビットを用途変更するように)。

#### 【0077】

さらに詳細に説明すれば、図10で示すように、単なる1つのバッファ1015(行バッファ)と共に提供される比較的“広いが、短い(即ち、行の数は少ないが、相対的に列の数が多い)”メモリアレイ1010は各々が自分のバッファ1035(行バッファ)を有する複数のさらに小さいアレイ1030を有する同様な構造1020に分割することができる。ここで、複数の小さいアレイ1030の各々は、メモリアレイ1010と行の数は同一であり、列の数はさらに少ない“狭くて短い”構造を有する。

例えば、アレイ構造1010は、一般的にアドレッシング可能(即ち、10ビットより多いアドレス空間を有する)であることより多い列を有するが、アレイ構造1020は各々すべての列のアドレッシングが可能なアレイ1030を含む(即ち、10ビット以下のアドレス空間を有する)。

#### 【0078】

所定の実施形態では、行バッファ1035のアドレッシング及びアクセスのためにターゲットデータアレイの(相対的に小さい)行アドレスと共にACT命令語が小さいアレイ1030の各々に伝達することができる。

小さいアレイ1030の各々は、対応する行バッファ1035にターゲット行を順にロードする。

加えて、アレイ1030内のターゲット列とターゲットアレイ1030(図10の左側から3番目のアレイ1030の同一)を識別するために列アドレス、アレイIDが提供(例えば、1つ又は2つの後続されるCAS命令語や、また場合によっては、アクティブ命令語(ACT)の部分に含まれ、1つ又は2つの後続されるCAS命令語を使用)される。

#### 【0079】

言い換えれば、拡張された列アドレスは、ACT命令語に行アドレスビット(行ID)を提供し、後続されるRD/WR命令語(下位列アドレスビット(列ID)及び上位列アドレスビット(アレイID))を提供することによって、また場合によっては、ACT命令語内の任意の非使用アドレスビットを使用(ACT命令語にアレイIDを提供することの同一)することによって支援することができる。

これは、ピン数やピン費用の増加無しで、又はACT命令語の発行から対応する列への最初データアクセスまでの遅延の増加無しで幾つのメモリチップ(多い数の列を収容する)を使用して容量を画期的に増加させることができる。

これらの技術及び他の技術が適用可能な分野、即ち、オープンページと広い列が組み合わされることによって同一の広い行に(即ち、同一又は異なるアレイIDに)連続的にアクセスすることが追加的なRASディレイの誘発無しでこの通常のCASレイテンシ(tCL)時間内に達成されるよう組み合わせることができる。

#### 【0080】

図11は、本発明の実施形態に係るメモリ装置のアドレッシング方法の例を説明するためのフローチャートである。

ここで、メモリ装置は、特定アーキテクチャ(DDR4 SDRAMのような)を使用してアクセスされ、使用されるアーキテクチャが一般設定で支援(即ち、アドレス可能な)することより多い行や列を有するものとみなされる。

しかし、本発明の実施形態によれば、メモリ装置の行は、拡張された行アドレスやメモリ装置の列は拡張された列アドレスを使用してアクセスされ、これらの拡張された行アドレスや列アドレスは基本アーキテクチャの組み合わされた行アドレスと列アドレス部分(即ち、2以上の連続されるRAS/CAS命令語)に適合する。

#### 【0081】

図11を参照すると、まず、S1110段階で、もし行アドレスが過度に多いビット数を有する場合(即ち、メモリ装置が支援するアーキテクチャより多い行を有する場合)、行アドレスビットは第1サブセットと第2サブセットとに分離され、第1サブセットは行アドレス命令語(例えば、ACT)によって特定され、第2サブセットは後続されるアドレ

10

20

30

40

50

ス命令語（例えば、(ACT+) 又は RD / WR）によって特定される。

#### 【0082】

次に、S1120段階で、行アドレス命令語がメモリ装置の行に対する行アクセスの一部又は全部として発行される。

例えば、メモリ装置がアーキテクチャによって支援される行より少ない数の行を有する場合、すべての行アドレスは行アドレス命令語によって特定することができるが、メモリ装置がアーキテクチャによって支援される行より多い数の行を有する場合には行アドレスの一部のみが（即ち、第1サブセット）行アドレス命令語によって特定され、残る行アドレス（即ち、第2サブセット）は後続アドレス命令語によって特定される。

#### 【0083】

同様に、S1130段階で、もし列アドレスが過度に多いビット数を有する場合（即ち、メモリ装置が支援するアーキテクチャより多い列を有する場合）、列アドレスビットは第3サブセットと第4サブセットとに分離され、第4サブセットは列アドレス命令語（例えば、RD / WR や RD / (WR+)）によって特定され、第3サブセットは以前アドレス命令語（例えば、ACT、(ACT+) 又は RD / WR）によって特定される。

#### 【0084】

次に、S1140段階で、列アドレス命令語が行に対する列アクセスの一部又は全部として発行する。

例えば、メモリ装置がアーキテクチャによって支援される列より少ない数の列を有する場合、すべての列アドレスは列アドレス命令語によって特定することができるが、メモリ装置がアーキテクチャによって支援される列より多い数の列を有する場合には列アドレスの一部（第4サブセット）のみが列アドレス命令語によって特定され、残る列アドレス（第3サブセット）は以前アドレス命令語によって特定される。

#### 【0085】

もし、メモリ装置で必要である全体アドレスビット（行及び列数が行アドレス命令語（例えば、ACT）と列アドレス命令語（例えば、RD / WR）によって特定される数より大きい場合、後続アドレス命令語は列アドレス命令語になるか、或いは以前アドレス命令語は行アドレス命令語になる（バックツーバック RAS / CAS のように）。

このようにすれば、2つのアドレス命令語（可能には、バックツーバック方式の）としてもメモリ装置のアドレッシングのために十分である。

#### 【0086】

一方、メモリ装置で必要である全体アドレスビット（行及び列数が行アドレス命令語と列アドレス命令語によって特定される数より大きい場合、後続アドレス命令語や以前アドレス命令語（例えば、(ACT+) 又は RD / WR）は行アドレス命令語と列アドレス命令語との間で発行される。

例えば、後続アドレス命令語と以前アドレス命令語とは同一の命令語であり、そして拡張された行アドレスビットや拡張された列アドレスビット、また場合によっては、これらの全てを特定することができる。

この後続アドレス命令語は、また行アドレス命令語を直ちに続くか（例えば、(ACT+) 又はバックツーバック RAS / CAS のように）、列アドレス命令語の直前に直ちに発行することができる（例えば、バックツーバック CAS / CAS のように）。

#### 【0087】

整理すれば、本発明は、SDRAMライクアーキテクチャの新しい命令語及びタイミング定義を提供するためのものであり、現在のSDRAMアーキテクチャに比べてさらに良いアドレス性能を可能にする。

例えば、幾つかの実施形態では、現在のSDRAMアーキテクチャに比べてさらに良いアドレス性能を可能にするための新しいメモリ構造とアドレス定義を提供することができる。加えて、他の実施形態では、設定可能なアドレス拡張方法（例えば、メモリチップの初期化やパワーオンの時に活性化される）を提供することができる。

これらの実施形態はピン数やピン費用の増加無しで高容量メモリを支援することができる

10

20

30

40

50

。これらの実施形態はまたアドレスピンの再利用率を高くすることができる。

【0088】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

【符号の説明】

【0089】

100 メモリモジュール

110 印刷回路基板（P C B）

120 メモリ装置

130 ピン

10

20

30

40

50

【図面】

【図 1】

【図 2 A】

10

20

【図 2 B】

【図 3】

30

40

50

【図 4 A】

【図 4 B】

【図 5】

【図 6】

【図 7】

| Function      |                      |

|---------------|----------------------|

| Extended READ |                      |

| 1st clock     |                      |

| 2nd clock     |                      |

| H             | = CKE Previous Cycle |

| H             | = CKE Current Cycle  |

| H             | = ACT_n              |

| L             | = RAS_n/A16          |

| H             | = CAS_n/A15          |

| H             | = WE_n/A14           |

| L             | BG0-BG1              |

| L             | BA0-BA1              |

| L             | C2                   |

| L             | < C0-C1              |

|               | BC_n/A12             |

| RFU           | A17                  |

| EA            | A13                  |

|               | A11                  |

|               | A10/AP               |

| Priority      | A9-A7                |

| RID           | A6-A0                |

【図 8】

【図 9】

| Function       |                      |

|----------------|----------------------|

| Extended WRITE |                      |

| 1st clock      |                      |

| H              | = CKE Previous Cycle |

| H              | = CKE Current Cycle  |

| H              | = ACT_n              |

| L              | = RAS_n/A16          |

| H              | = CAS_n/A15          |

| H              | = WE_n/A14           |

| L              | BG0-BG1              |

| L              | BA0-BA1              |

| H              | C2                   |

| L              | < C0-C1              |

|                | BC_n/A12             |

| EA             | A17                  |

|                | A13                  |

|                | A11                  |

|                | A10/AP               |

| CA             | A9-A7                |

|                | A6-A0                |

【図 10】

【図 1 1】

10

20

30

40

50

---

フロントページの続き

(32)優先日 平成28年8月3日(2016.8.3)

(33)優先権主張国・地域又は機関

米国(US)

早期審査対象出願

ス 2 9 2 0

(72)発明者 牛 迪 民

アメリカ合衆国 カリフォルニア州 9 4 0 8 7 サニーベール ホルトハウステラス 5 2 7

(72)発明者 ツエン 宏 忠

アメリカ合衆国 カリフォルニア州 9 5 0 3 2 ロスガトス カールトンアベニュー # 6 1 2 0

(72)発明者 林 サン ヨン

大韓民国 京畿道 華城市 半月洞 山 1 6

(72)発明者 金 寅 東

大韓民国 京畿道 華城市 半月洞 山 1 6

(72)発明者 チェ , ジャン ソク

アメリカ合衆国 カリフォルニア州 9 5 0 0 8 キャンベル ブレースブリッジコート 1 2 2 6

審査官 酒井 恭信

(56)参考文献 特開2 0 0 1 - 0 1 4 8 4 2 ( J P , A )

特開2 0 0 1 - 1 0 1 8 6 5 ( J P , A )

(58)調査した分野 (Int.Cl. , DB名)

G 0 6 F 1 2 / 0 2

G 1 1 C 7 / 1 0

G 1 1 C 1 1 / 4 0 9 6