(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6443794号

(P6443794)

(45) 発行日 平成30年12月26日(2018.12.26)

(24) 登録日 平成30年12月7日(2018.12.7)

(51) Int.Cl.

F 1

G06F 12/00 (2006.01)

G06F 12/04 (2006.01)G06F 12/00 542K

G06F 12/00 511A

G06F 12/00 597U

G06F 12/04 530

請求項の数 19 外国語出願 (全 40 頁)

(21) 出願番号 特願2014-152477 (P2014-152477)

(22) 出願日 平成26年7月28日 (2014.7.28)

(65) 公開番号 特開2015-36982 (P2015-36982A)

(43) 公開日 平成27年2月23日 (2015.2.23)

審査請求日 平成29年2月2日 (2017.2.2)

(31) 優先権主張番号 61/866,672

(32) 優先日 平成25年8月16日 (2013.8.16)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/873,357

(32) 優先日 平成25年9月3日 (2013.9.3)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/888,681

(32) 優先日 平成25年10月9日 (2013.10.9)

(33) 優先権主張国 米国(US)

(73) 特許権者 508243639

エルエスアイ コーポレーション

アメリカ合衆国カリフォルニア州9513

1, サンノゼ, リッダー・パーク・ドライ

ヴ 1320

(74) 代理人 100087642

弁理士 古谷 聰

(74) 代理人 100082946

弁理士 大西 昭広

(74) 代理人 100121061

弁理士 西山 清春

(74) 代理人 100195693

弁理士 細井 玲

最終頁に続く

(54) 【発明の名称】ホストとコントローラとの間でパーティション化された変換レイヤ

## (57) 【特許請求の範囲】

## 【請求項 1】

区分化されたフラッシュ変換レイヤを使用したデータ格納方法であって、書き込まれるべき第1のデータをホストから受信し、

該第1のデータから生成された第2のデータをメモリに格納し、該第1のデータが圧縮されて該第2のデータが生成され、該第2のデータが可変サイズを有し、該第2のデータが前記メモリ内の複数の物理口케ーションに格納され、該第2のデータを保持する該複数の物理口케ーションのうちの最初の物理口케ーションが前記メモリ内の次の未書き込み口케ーションであり、該第2のデータのサイズが、該メモリにとってローカルな前記フラッシュ変換レイヤの第1の区分内に格納され、該メモリ内の該第2のデータの前記最初の物理口케ーションが、前記ホストにおいて前記フラッシュ変換レイヤの第2の区分内に格納される、

区分化されたフラッシュ変換レイヤを使用したデータ格納方法。

## 【請求項 2】

前記第2のデータの前記最初の物理口케ーションを有する読み出しコマンドを前記ホストから受信し、

前記第2のデータの前記サイズを前記フラッシュ変換レイヤの前記第1の区分から読み出し、及び、

前記第2のデータの前記最初の物理口케ーション及び前記サイズに基づいて前記メモリの一部を読み出すことにより前記第2のデータを取り出す

10

20

ことを更に含む、請求項 1 に記載の方法。

【請求項 3】

前記メモリから取り出された前記第 2 のデータを解凍することにより前記第 1 のデータを再形成し、

該再形成された該第 1 のデータを前記ホストへ返す

ことを更に含む、請求項 2 に記載の方法。

【請求項 4】

前記第 2 のデータに関連付けられたヘッダの少なくとも一部として、前記第 1 のデータに関連付けられた識別子を前記メモリ内に格納する

ことを更に含む、請求項 1 ないし請求項 3 の何れか一項に記載の方法。 10

【請求項 5】

前記識別子を前記メモリ内の前記第 2 のデータの前記最初の物理口ケーションに関連付けるマップを前記ホスト内に維持する

ことを更に含む、請求項 4 に記載の方法。

【請求項 6】

前記識別子が論理ロックアドレスであり、前記最初の物理口ケーションが、前記第 2 のデータを保持する前記メモリ内の複数の読み出しユニットのうちの 1 つ内のアドレスであり、該複数の読み出しユニットの各々が、前記第 2 のデータのそれぞれの部分と、該第 2 のデータの該それぞれの部分を保護するそれぞれの誤り訂正情報を含む、請求項 4 又は請求項 5 に記載の方法。 20

【請求項 7】

前記メモリが複数のページを有しており、前記アドレスが、前記第 2 のデータを保持する前記複数のページのうちの第 1 のページ内のものであり、該第 1 のページが、前記第 2 のデータを保持する前記複数の読み出しユニットのうちの第 1 の個数の読み出しユニットを含み、前記複数のページのうちの第 2 のページが、前記第 2 のデータを保持する前記複数の読み出しユニットのうちの第 2 の個数の読み出しユニットを含み、前記第 1 の個数が前記第 2 の個数とは異なる、請求項 6 に記載の方法。

【請求項 8】

前記次の未書き込み口ケーションが、前記メモリの物理アドレス空間内の前に書き込まれたデータに隣接する、請求項 1 ないし請求項 7 の何れか一項に記載の方法。 30

【請求項 9】

区分化されたフラッシュ変換レイヤを使用したデータ格納方法であって、

書き込まれるべきデータをホストから受信し、該データが可変サイズを有し、及び、

該データをメモリ内に格納し、該データが、該メモリ内の複数の物理口ケーションに格納され、該データを保持する該複数の物理口ケーションのうちの最初の物理口ケーションが該メモリ内の次の未書き込み口ケーションであり、該データのサイズが、該メモリにとってローカルな前記フラッシュ変換レイヤの第 1 の区分内に格納され、及び該メモリ内の前記データの前記最初の物理口ケーションが、前記ホストにおいて前記フラッシュ変換レイヤの第 2 の区分内に格納される、

区分化されたフラッシュ変換レイヤを使用したデータ格納方法。 40

【請求項 10】

前記データを保持する前記メモリ内の前記最初の物理口ケーションを有する読み出しコマンドを前記ホストから受信し、

前記データのサイズを前記フラッシュ変換レイヤの前記第 1 の区分から読み出し、及び、

前記データの前記最初の物理口ケーション及び前記サイズに基づいて前記メモリの一部を読み出すことにより前記データを取り出す

ことを更に含む、請求項 9 に記載の方法。

【請求項 11】

前記ホストへ前記データを返すことを更に含む、請求項 10 に記載の方法。 50

**【請求項 1 2】**

前記データに関連付けられたヘッダの少なくとも一部として前記データに関連付けられた識別子を前記メモリ内に格納する

ことを更に含む、請求項 9 ないし請求項 1 1 の何れか一項に記載の方法。

**【請求項 1 3】**

前記識別子を前記メモリ内の前記データの前記最初の物理口ケーションに関連付けるマップを前記ホスト内に維持することを更に含む、請求項 1 2 に記載の方法。

**【請求項 1 4】**

前記識別子が論理ブロックアドレスであり、前記最初の物理口ケーションが、前記データを保持する前記メモリ内の複数の読み出しユニットのうちの 1 つ内のアドレスからなり、該複数の読み出しユニットの各々が、それぞれのデータ部分と該それぞれのデータ部分を保護するそれぞれの誤り訂正情報を含む、請求項 1 2 又は請求項 1 3 に記載の方法。10

**【請求項 1 5】**

前記メモリが複数のページを有しており、前記アドレスが、前記データを保持する該複数のページのうちの第 1 のページ内のものであり、該第 1 のページが、前記データを保持する前記複数の読み出しユニットのうちの第 1 の個数の読み出しユニットを含み、前記複数のページのうちの第 2 のページが、前記データを保持する前記複数の読み出しユニットのうちの第 2 の個数の読み出しユニットを含み、前記第 1 の個数が前記第 2 の個数とは異なる、請求項 1 4 に記載の方法。

**【請求項 1 6】**

前記次の未書き込み口ケーションが、前記メモリの物理アドレス空間内の前に書き込まれたデータに隣接する、請求項 9 ないし請求項 1 5 の何れか一項に記載の方法。20

**【請求項 1 7】**

前記方法が半導体ドライブ (solid-state drive) コントローラで実施される、請求項 1 ないし請求項 1 6 の何れか一項に記載の方法。

**【請求項 1 8】**

メモリとの間で複数の読み出し / 書き込み動作を処理するよう構成されたインターフェイスと、

ホストから第 1 のデータを受信し、及び該第 1 のデータから生成された第 2 のデータを前記メモリに格納するよう構成された制御回路と30

を備えた装置であって、前記第 1 のデータが圧縮されて前記第 2 のデータが生成され、該第 2 のデータが可変サイズを有し、該第 2 のデータが前記メモリ内の複数の物理口ケーションに格納され、該第 2 のデータを保持する該複数の物理口ケーションのうちの最初の物理口ケーションが前記メモリ内の次の未書き込み口ケーションであり、該第 2 のデータのサイズが、前記メモリにとってローカルなフラッシュ変換レイヤの第 1 の区分内に格納され、前記メモリ内の該第 2 のデータの前記最初の物理口ケーションが、前記ホストにおいて前記フラッシュ変換レイヤの第 2 の区分内に格納される、装置。

**【請求項 1 9】**

前記インターフェイス及び前記制御回路が、半導体ドライブコントローラの一部である、請求項 1 8 に記載の装置。40

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本出願は、2013年10月21日出願の米国仮出願第61/893,383号、2013年10月9日出願の米国仮出願第61/888,681号、2013年9月3日出願の米国仮出願第61/873,357号、2013年8月16日出願の米国仮出願第61/866,672号、及び2013年1月22日出願の米国仮出願第61/755,169号に関連するものである。

**【0 0 0 2】**

本出願は、2010年3月22日出願の米国仮出願第61/316,373号に関連する2011年3月21日出願の米国出願第13/053,175号に関連するものである。50

**【 0 0 0 3 】**

本出願はまた、2011年10月5日出願の米国仮出願第61/543,707号を優先権主張の基礎とする国際出願第PCT/US2012/058583号（国際出願日：2012年10月4日）に関連するものである。

**【 0 0 0 4 】**

本出願は、2011年9月6日出願の米国仮出願第61/531,551号及び2011年8月9日出願の米国仮出願第61/521,739号を優先権主張の基礎とする国際出願第PCT/US2012/049905号（国際出願日：2012年8月8日）に関連する2013年7月10日出願の米国出願第13/936,010号に関連するものである。

**【 0 0 0 5 】**

10

本発明は、一般にコンピューティングホスト及び入出力装置の技術に関し、特に、ホストとコントローラとの間でパーティション化された変換レイヤを提供する方法及び／又は装置に関するものである。

**【背景技術】****【 0 0 0 6 】**

従来の半導体デバイスは、固定の整数個のホスト論理ブロックを不揮発性メモリの各ページに格納している。該不揮発性メモリの各ページのユーザデータサイズ又は利用可能サイズが固定されていない場合には記憶効率の問題が発生する。半導体ドライブ（SSD）における可変サイズのフラッシュ変換レイヤに関するアーキテクチャは、強烈な負荷をハードウェアに与えるものである。該半導体ドライブの複数のページ内の多数の読み出しユニット（read unit）間でユーザデータが記憶されている場所を識別するためにページヘッダが使用され、該データの抽出は、最初に該ページヘッダを読み出してペースすることを伴う。

20

**【発明の概要】****【課題を解決するための手段】****【 0 0 0 7 】**

本発明は、パーティション化されたフラッシュ変換レイヤを使用するための方法に関するものである。ステップ（A）は、所与の装置において第1の書き込みデータを有する書き込みコマンドをホストから受信する。ステップ（B）は、該装置において該第1の書き込みデータを圧縮することにより第2の書き込みデータを生成する。該第2のデータは一般に可変サイズを有する。ステップ（C）は、該第2の書き込みデータを不揮発性メモリ内の所与の物理位置に格納する。該物理位置は、次の書き込まれていない位置である。ステップ（D）は、該物理位置の指示を前記書き込みコマンドに応じて前記装置から前記ホストへと返す。

30

**【図面の簡単な説明】****【 0 0 0 8 】**

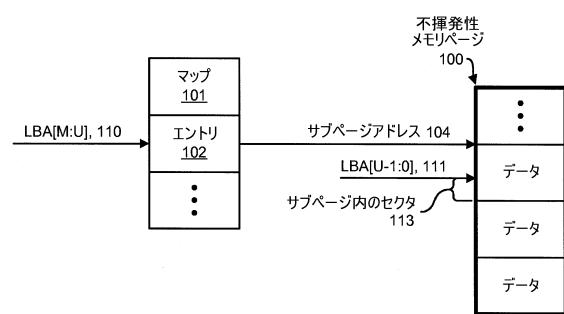

【図1】論理ブロックアドレスから不揮発性メモリページ内の複数の固定サイズ領域へのマッピングの一実施形態の特定の細部を示す図である。

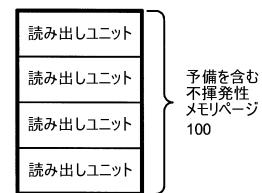

【図2】論理ブロックアドレスから複数の不揮発性メモリページに随意選択的にまたがる可変サイズ領域へのマッピングの一実施形態の特定の細部を示す図である。

40

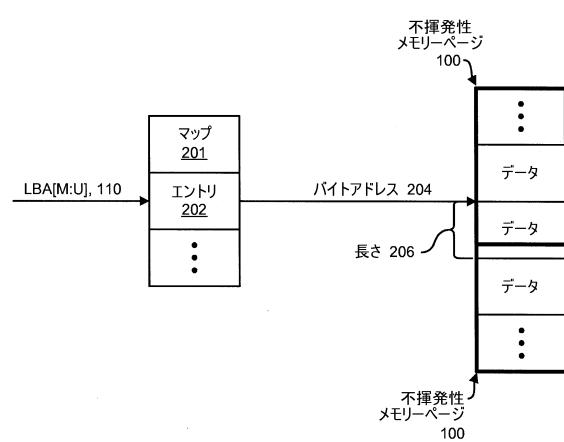

【図3】整数個の読み出しユニットからなる不揮発性メモリページの一実施形態を示す図である。

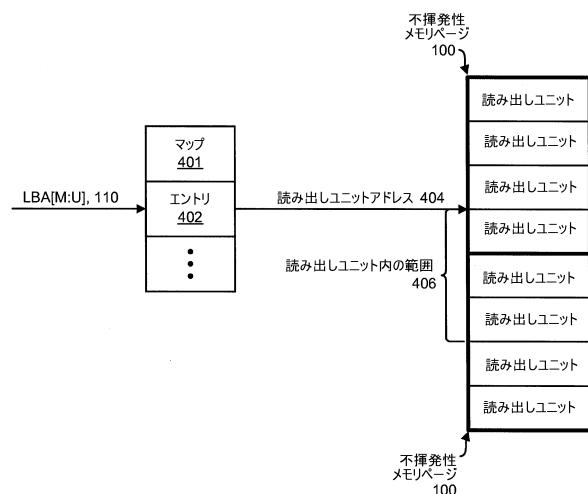

【図4】論理ブロックアドレスから1つ以上の読み出しユニットにまたがる可変サイズ領域へのマッピングの一実施形態の特定の細部を示す図である。

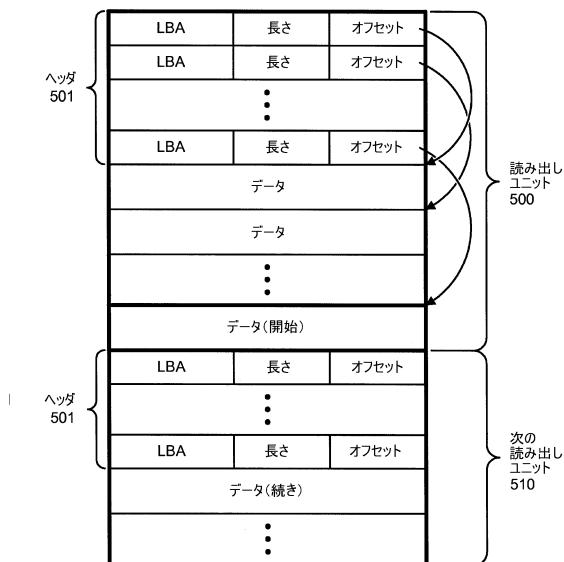

【図5】複数のヘッダ及び複数のデータからなる読み出しユニットの一実施形態の特定の細部を示す図である。

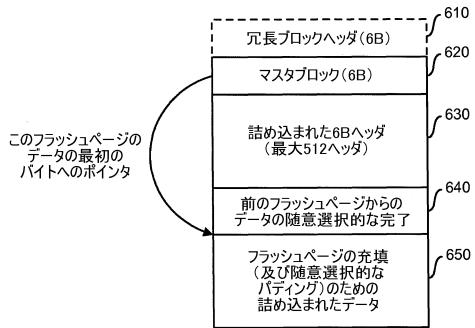

【図6】複数のヘッダ及び複数のデータからなる不揮発性メモリページの一実施形態の特定の細部を示す図である。

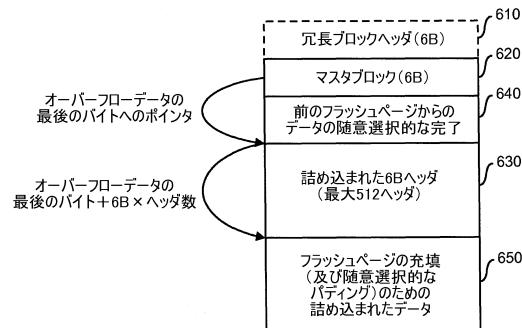

【図7】複数のヘッダ及び複数のデータからなる不揮発性メモリページの別の実施形態の特定の細部を示す図である。

50

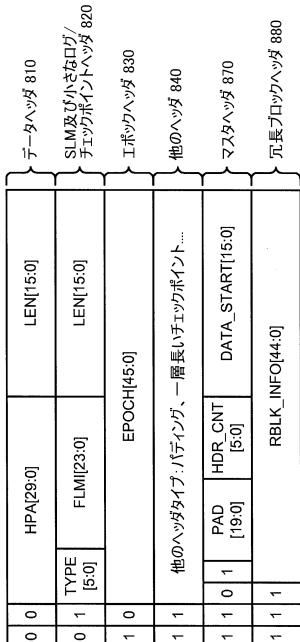

【図8】様々なタイプの一実施形態の特定の細部を示す図である。

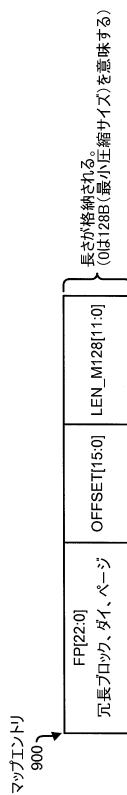

【図9】マップエントリの一実施形態の特定の細部を示す図である。

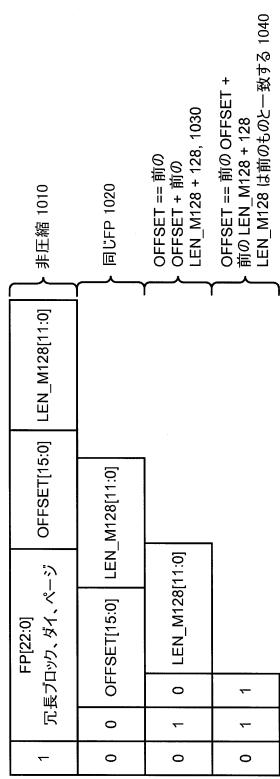

【図10】様々な圧縮されたマップエントリの一実施形態の特定の細部を示す図である。

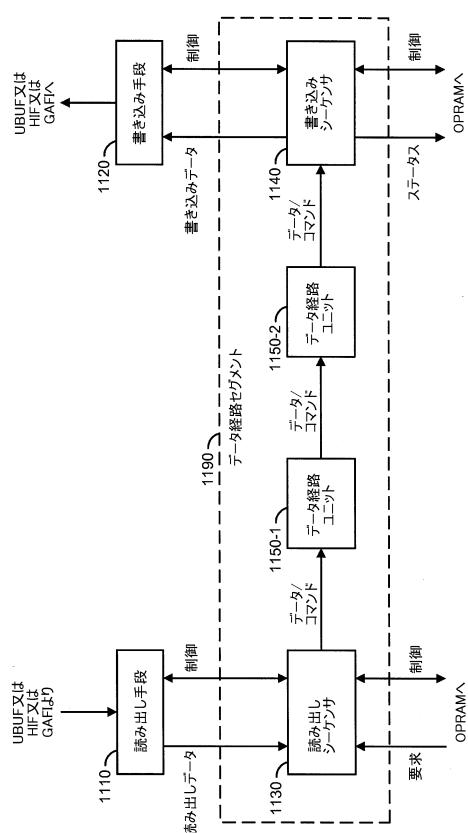

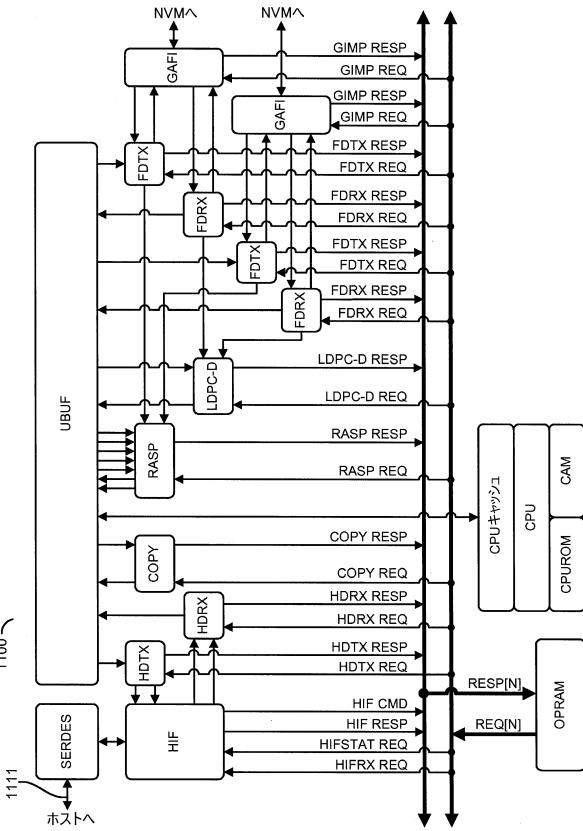

【図11A】半導体ドライブコントローラの一実施形態の特定の細部を示す図である。

【図11B】データパスセグメントの一実施形態の特定の細部を示す図である。

【図11C】本発明の一実施形態によるシステムの様々な実施形態の特定の細部を示す図である。

【図12】不揮発性メモリへのデータの書き込み処理のフローチャートである。

【図13】不揮発性メモリからのデータの読み出し処理のフローチャートである。

【図14】不揮発性メモリ内のデータのリサイクル処理のフローチャートである。 10

#### 【発明を実施するための形態】

##### 【0009】

本発明の実施形態は、以下の詳細な説明、特許請求の範囲、及び図面から明らかとなろう。

##### 【0010】

本発明の実施形態は、ホストとコントローラとの間でパーティション化された変換レイヤを提供することであって、該変換レイヤは、(i)広範囲のデータサイズをサポートし、(ii)非ブロックベースのデータで動作し、(iii)データの書き込みに応じてホストへハンドルを返し、(iv)該ハンドルを使用して該データを読み出し、及び/又は(v)1つ以上の集積回路及び/又はそれに関連するファームウェアとして実施することが可能なものである。 20

##### 【0011】

ホストは、(半導体ドライブ(例えばSSD)コントローラ等の)入出力装置に接続され、該入出力装置は、不揮発性メモリ(例えばNVM)に接続され及び/又は不揮発性メモリを含む。ホストの一例として、コンピューティングホスト、サーバ、パーソナルコンピュータ、ラップトップコンピュータ、ノートブックコンピュータ、ワークステーションコンピュータ、PDA(Personal Digital Assistant)、スマートフォン、携帯電話、メディアプレーヤ又はレコーダ、入出力コントローラ、安価な/独立した複数のディスクの冗長アレイ(例えばRAID)のオンチップコントローラ(例えばROC)、及びプロセッサ又はコンピュータからなる他のあらゆる装置が挙げられる。該ホストは、入出力装置を介して不揮発性メモリにアクセスするための要求を発し、該要求が、該ホストの組み合わせにより(例えば、少なくとも部分的には該ホスト上で実行しているソフトウェアにより)、及び前記入出力装置により(例えば、少なくとも部分的には該入出力装置上で実行しているファームウェアにより)実行される。 30

##### 【0012】

実施形態によつては、フラッシュ変換レイヤ(例えばFTL)が、(入出力装置に対する入出力操作を実行するためにホストにより使用されるような)論理ブロックアドレス空間内の論理ブロックアドレス(例えばLBA)を、NANDフラッシュ不揮発性メモリ等の不揮発性メモリ内の物理ロケーション(例えば、物理アドレス空間内の物理ストレージアドレス)へとマッピング(又は変換)する。様々な実施形態によれば、論理ブロックアドレス空間内の論理ブロックアドレスのマッピングは、1レベルマップ、2レベルマップ、マルチレベルマップ、ダイレクトマップ、アソシティブマップ、ハッシュテーブル、B木、トライ木、マップの一部のキャッシュ、及び論理ブロックアドレスを不揮発性メモリ内の物理ロケーションに関連付ける他のあらゆる手段のうちの1つ以上を介したものとなる。更なる実施形態では、該マップは、複数のエントリ(例えば、論理ブロックアドレス空間内の各論理ブロックアドレス毎の1つのエントリ)からなる。 40

##### 【0013】

別の実施形態では、フラッシュ変換レイヤは、個々のデータのラベルその他の一意の識別子を、不揮発性メモリ内の物理ロケーションへとマッピングする。例えば、該ラベルは、個々のデータのハッシュ(例えば、SHA-256又はSHA-512ハッシュ)とすることが可能で 50

あり、又は個々のデータとして格納され又は個々のデータ内に格納された個々のオブジェクトのオブジェクト識別子とすることが可能であり、又は個々のデータのファイルシステム識別子（例えばinode）とすることが可能である（この場合、該個々のデータはファイルシステムオブジェクトである）。様々な実施形態によれば、個々のデータのラベルその他の一意の識別子のマッピングは、1レベルマップ、2レベルマップ、マルチレベルマップ、ダイレクトマップ、アソシティップマップ、ハッシュテーブル、B木、トライ木、マップの一部のキャッシュ、及び該ラベルその他の一意の識別子を不揮発性メモリの物理口케ーション内に関連付ける他のあらゆる手段のうちの1つ以上を介したものとなる。更なる実施形態では、該マップは、複数のエントリ（例えば、現存するラベルその他の一意の識別子の各々毎の1つのエントリ）からなる。更に別の実施形態では、該マップは、動的なサイズを有し、現存するラベルその他の一意の識別子の数が増減するにつれて拡大又は縮小する。一例として、現存するラベルその他の一意の識別子の数が増減する際に、該マップのサイズが線形的に拡大し又は縮小する。別の例では、現存するラベルその他の一意の識別子の数がそれぞれのしきい値を超えて増減する際に、該マップのサイズが階段状に（離散的な量で）拡大し又は縮小する。

#### 【0014】

様々な実施形態において、一意の識別子を提供するために及び／又は該一意の識別子の範囲を制限するために、マルチレベルマップが使用される。例えば、第1のアソシティップマップにおいて1つのラベルがルックアップされ、該ラベルよりも長さが短い一意の識別子が生成される。次いで、該一意の識別子が第2のマップにおいてルックアップされて、不揮発性メモリ内の物理口ケーションが生成される。更なる実施形態では、該第2のマップは複数のマップ（例えば（複数の異なる半導体ディスク内に存在するような）複数の物理的に別個の部分及び／又は（例えば異なる種類の）不揮発性メモリの機能的に異なる部分の各々毎の1つのマップ）である。

#### 【0015】

複数のラベル（又はハンドル又は論理ブロックアドレス又は識別子又はその他の同様の用語）の各々は、一般に個々のデータオブジェクト（又はセクタ又はクロック又はアイテム又はその他の同様の用語）に対応し、フラッシュ変換レイヤは、該ラベルの各々を、該対応するデータオブジェクトの不揮発性メモリ内の物理口ケーションに関連付ける。該ラベルと該対応するデータオブジェクトの不揮発性メモリ内の物理口ケーションとの関連付けは、該関連付けが行われる態様にかかわらず、マップを介したものであることができる。本書における様々な実施形態は、論理ブロックアドレスのマッピングを使用し、別の実施形態は、オブジェクトラベル又はオブジェクト識別子のマッピングを使用するが、本書で教示する思想では、多くの同様のデータラベリング技術並びにそれに関連するマッピング技術を使用することが可能である。

#### 【0016】

本書で使用する場合、用語「マッピングユニット」とは、フラッシュ変換レイヤによりマッピングされるデータオブジェクトのサイズを意味する。実施形態によっては該マッピングユニットは固定サイズであり、別の実施形態ではデータオブジェクトは可変サイズである（このためマッピングユニットは固定サイズでなくなる）。

#### 【0017】

実施形態によっては、マッピングは、1つ以上の論理セクタ又はブロックが整列されてなる単位で行われる。各マッピングユニットは、1つ以上の論理セクタ又はブロックの整列された単位である。各マッピングユニットは、対応する物理口ケーションを有し、該物理口ケーションに該マッピングユニットのデータが格納される（マッピングユニットが書き込まれたこと又は調整されたことがない場合における空の（NULL）物理口ケーションの可能性を含む）。例えば、4キロバイト（例えばKB）のマッピングユニットの場合には、8つの連続する（及び典型的には整列した8セクタの）シリアルATA（Serial Advanced Technology Attachment）（例えばSATA）512バイトセクタが、一単位としてマッピングされる。一般に、論理ブロックアドレスのためのマップは、マッピングユニットに関連づけ

10

20

30

40

50

られた論理ブロックアドレスから不揮発性メモリ内の物理アドレスへのそれぞれの変換及び／又はその他の制御情報を格納するために、1つのマッピングユニットにつき1つのエントリを有する。

#### 【0018】

様々な実施形態において、マッピングされるデータオブジェクトのサイズ（各マッピングユニットのサイズ）及び／又は不揮発性メモリ内に格納されるデータオブジェクトのサイズは変化する。一実施形態では、マップ中の各エントリは、それぞれのデータオブジェクトのサイズを格納する。この場合、キー／値ストア内に、該マップのエントリにアクセスするために使用されたラベルが該キーに従って格納され、該値のサイズは、該キーが異なると変化する。別の実施形態では、マップ中の各エントリは、格納されているデータオブジェクトを取り出すために読み出すべき不揮発性メモリの量の指示を格納する。別の実施形態による变形例では、マップのエントリにより指定される不揮発性メモリの量は、該マップのエントリにより指定される不揮発性メモリの該量内における1つ以上の格納済みデータオブジェクト間又はそれらの一部間ににおけるそれぞれの格納済みデータオブジェクトを特定するヘッダからなる。更に別の実施形態による变形例では、それぞれのデータオブジェクトを取り出すために読み出すべき不揮発性メモリの量は、該不揮発性メモリの1ページ内に格納されている個々のデータオブジェクトの正確なサイズ及び位置を指定する（但し、該不揮発性メモリの誤り訂正には関わらない）。不揮発性メモリから読み出したデータについて誤り訂正を実行するのに十分な個々の格納済みデータオブジェクト及びその他の情報を取り出すために読み出すべき不揮発性メモリの更に大きな量を決定するためには、追加の計算が使用される。10

#### 【0019】

様々な実施形態によれば、不揮発性メモリは、1（例えばシングルレベルセル）、2（例えばマルチレベルセル）、3（例えばトリプルレベルセル）、又はより多くのビット／セルをを収容し、及び平面（2次元）又は3次元（例えば3D）である、NANDフラッシュメモリ、NORフラッシュメモリ、他のあらゆるタイプのフラッシュメモリ又は電気的に消去可能なメモリ、相変化メモリ（例えばPCM）、磁気ランダムアクセスメモリ（例えばMRAM）、レーストラックメモリ、抵抗型ランダムアクセスメモリ（例えばReRAM）、バッテリによりバックアップされたスタティックランダムアクセスメモリ（例えばSRAM）又はダイナミックランダムアクセスメモリ（例えばDRAM）、任意の磁気又は光学記憶媒体、又はその他のあらゆる不揮発性メモリのうちの1つ以上である。20

#### 【0020】

実施形態によっては、不揮発性メモリは、例えば、（例えば、異なる半導体ディスク内の）異なる入出力装置において物理的に分離されることにより、又は異なる物理ロケーション又はアクセス機構を有する（例えば、不揮発性メモリの一部がNANDフラッシュであり、第2の部分が相変化メモリである）ことにより、もう1つのグループに編成されることが可能である。実施形態によっては、マップは、グローバルマップ（各エントリが入出力装置の識別子（例えばID）及び該入出力装置内の物理ロケーションを指定するもの）である。別の実施形態では、マップは、複数の部分（例えば、1つの入出力装置につき1つの部分及びより高レベルのマップ）へとパーティション化され、及び／又は個々のラベルの機能が複数の入出力装置のうちの特定の1つを判定する。30

#### 【0021】

NANDフラッシュといった不揮発性メモリによっては、不揮発性メモリページ（又は、例えばNANDフラッシュの場合にはフラッシュページ）と呼ばれる書き込み可能な（又はプログラマブルな）単位を提供する。不揮発性メモリページは、一般に不揮発性メモリの最小の書き込み可能な単位である。実施形態及び／又は使用形態によっては、不揮発性メモリページは、複数のユーザ（非誤り訂正符号）データバイトと、メタデータ及び誤り訂正符号化（例えばECC）のための一一定量の予備領域とからなる。典型的なNANDフラッシュページサイズは、ユーザデータの8KB又は32KBであり、一方、論理ブロックアドレスのための典型的なマッピングユニットサイズは、4KB又は8KBである。（不揮発性メモリページに關4050

して用語「ユーザ」を使用するが、不揮発性メモリページによってはマップデータ及び／又はチェックポイントデータといった「システム」データを格納する。ユーザデータとは、一般に不揮発性メモリページの非誤り訂正符号化部分を示すことを意図したものである。) NANDフラッシュページは、複数のブロックに編成され、典型的には128、256、又は512フラッシュページ／ブロックとなる。1ブロックは、消去することができる最小サイズの単位であり、1NANDフラッシュページは、該ページに(再び)書き込むことが可能となる前に消去される。

#### 【0022】

NANDフラッシュといった不揮発性メモリによっては、複数のプレーン及び／又はバンクを有し、及び2つ以上のプレーンの各々から並行して1ページ及び／又は1ブロックにアクセスする(読み出し又はプログラミング又は消去を行う)「マルチプレーン」操作を可能にする。マルチプレーンプログラミングを使用することにより、書き込み帯域幅が有利に増大し、及び書き込み処理の基本単位が单一の1プレーンページではなくマルチプレーンページとなる。本書で用いる用語「不揮発性メモリページ(又は不揮発性メモリブロック)」は、不揮発性メモリが使用される態様に従って、单一の不揮発性メモリページ(又はブロック)又はマルチプレーン不揮発性メモリページ(又はブロック)の何れかを表すものである。

#### 【0023】

本書では「フラッシュ」変換レイヤ(例えばFTL)なる用語を用いるが、論理アドレスと物理アドレスとの間における変換レイヤの思想は、多くの種類の不揮発性メモリに適用可能なものである。一実施形態では、特定のタイプの不揮発性メモリ(例えばNANDフラッシュ)は、書き換えを行う前に大きな単位で消去される。別の実施形態では、不揮発性メモリの種類によっては消耗し、消耗平滑化(wear-leveling)(不揮発性メモリの消耗の多い部分から消耗の一層少ない部分へデータを移動すること)に通ずるものとなる。更に別の実施形態では、新しい形態のハードディスク磁気記録(例えば瓦記録方式)は、以前に書き込まれたデータよりも遙かに大量の他のデータを消去せずに該以前に書き込まれたデータを上書きすることができないものである。様々な実施形態において、粗粒度型の又は有限の耐久性を有する種類の不揮発性メモリは、(フラッシュ)変換レイヤの恩恵を受けるものとなる。

#### 【0024】

図1を参照すると、論理ブロックアドレスから不揮発性メモリページ内の固定サイズ領域へのマッピングの一実施形態の特定の細部が示されている。従来のフラッシュ変換レイヤの中には、所与の不揮発性メモリページ(例えば不揮発性メモリページ100)内の複数のユーザデータバイトの数が2のべき乗(及び／又はセクタサイズの倍数)であることを前提とし、及び不揮発性メモリページを整数個のマッピングユニット(図1に「データ」と示す)へと分割するものがある。例えば、1つの不揮発性メモリページについてのユーザデータが16KBであり、マッピングユニットが4KBである場合、各不揮発性メモリページは4つのマッピングユニットを含み、フラッシュ変換レイヤは、各マッピングユニットのアドレス(例えば、LBA[M:U] 110)を、個々の不揮発性メモリページ、及び該個々の不揮発性メモリページ内の4つのマッピングユニットのうちの1つへとマッピングする。すなわち、各マップエントリは、次に示すように、それぞれのフィールドを含む。

#### 【0025】

不揮発性メモリページアドレス[n-1:0]、不揮発性メモリページ内のマッピングユニット[k-1:0]

ここで、「不揮発性メモリページアドレス」とは、不揮発性メモリ内の一意の不揮発性メモリページを示すものであり、「不揮発性メモリページ内のマッピングユニット」とは、各不揮発性メモリページの $2^k$ 個( $k$ は不揮発性メモリ全体について固定)のマッピングユニットのサイズの部分を示すものである。サブページアドレス104は、「不揮発性メモリページアドレス」と「不揮発性メモリページ内のマッピングユニット」との組み合わせである。セクタベースの(例えば、マッピングユニットよりも細かい粒度の)アドレシン

10

20

30

40

50

グの場合には、論理ブロックアドレスの一層下位のビット（例えば、LBA[U-1:0] 111）がサブ部分（例えばマッピングユニット内のセクタ（例えばサブページ113内のセクタ）の数）を指定する。

#### 【0026】

図2を参照すると、論理ブロックアドレスから、随意選択的に複数の不揮発性メモリページにまたがる可変サイズ領域へのマッピングの一実施形態の特定の細部が示されている。可変サイズのフラッシュ変換レイヤ（例えばVFTL）は、（例えば、マッピングユニットのデータが不揮発性メモリ内への格納に先立って圧縮されるため、及び／又は別の実施形態ではマッピングユニットが可変サイズ片としてホストにより書き込まれるため（オブジェクトストアの場合など））マッピングユニットのアドレス（又はラベル）（例えば、LA[M:U] 110）を、1つ以上の不揮発性メモリページの可変サイズ領域へと概念的にマッピングする。しかし、各マップエントリ内で完全なバイトアドレス204及びバイトデータ長206を提供すると、従来のフラッシュ変換レイヤの場合と比較して該マップエントリが大きくなる。10

#### 【0027】

図3を参照すると、整数個の読み出しユニットからなる不揮発性メモリページの一実施形態が示されている。実施形態によっては、可変サイズフラッシュ変換レイヤが、Epage（例えば、誤り訂正符号化ページ）アドレス（「読み出しユニット」アドレスとも呼ばれる）へのマッピングを行うことにより、マッピングユニットのアドレス（又はラベル）から物理アドレスへのマッピングを行う。Epage（又は読み出しユニット）は、不揮発性メモリから読み出して、該不揮発性メモリの内容を保護するために使用される誤り訂正符号により訂正することができる、最小のデータ量である。すなわち、各読み出しユニットは、一定量のデータと該データを保護するための対応する誤り訂正符号化チェックバイトとを含む。実施形態によっては、不揮発性メモリページ（例えば不揮発性メモリページ100）が、又は別の実施形態では、書き込むための一単位として扱われる1グループの不揮発性メモリページが、図3に示すように、整数個の読み出しユニットへと分割される。20

#### 【0028】

NANDフラッシュ等の不揮発性メモリの種類によっては、該不揮発性メモリ内に格納されるデータは、ユーザデータバイトと誤り訂正符号バイト（誤り訂正情報）とを混合したものとなり、該不揮発性メモリにアクセスする高レベルコントローラが、該不揮発性メモリ内のどのバイトがどのような数だけユーザデータのために使用され、及び該不揮発性メモリ内のどのバイトがどのような数だけ誤り訂正符号化のために使用されるかを判定する。様々な実施形態において、1つの不揮発性メモリページあたりの読み出しユニットの個数は変化することが可能である。例えば、不揮発性メモリの幾つかの部分が、（誤り訂正符号化情報のために不揮発性メモリページ内の一層多くのバイトを使用して）他の部分よりも強力な誤り訂正符号を使用し、及び一層少数の読み出しユニット及び／又は一層少ない使用可能データ／読み出しユニットを有する。別の実施形態では、プログラム／消去サイクルが不揮発性メモリを弱体化させる傾向を有するため、1つの不揮発性メモリページあたりの読み出しユニットの個数が、不揮発性メモリが使用される際に変化し、その結果として、不揮発性メモリが使用される（消耗する）につれて一層強力な誤り訂正符号が必要となる。3040

#### 【0029】

様々な実施形態によれば、使用される誤り訂正符号は、リード・ソロモン（例えばRS）符号、Bose Chaudhuri Hocquenghem（例えばBCH）符号、ターボ符号、硬判定及び／又は軟判定・低密度パリティ検査（例えばLDPC）符号、Polar符号、非バイナリ符号、安価な／独立した複数のディスクの冗長アレイ（例えばRAID）符号、消失（erasure）符号、その他の任意の誤り訂正符号、及び上記符号の（合成、結合、及び交互配置を含む）任意の組み合わせのうちの1つ以上である。典型的なコードワードサイズは、512バイト（+誤り訂正符号化バイト）から2176バイト（+誤り訂正符号化バイト）までの範囲となる。典型的な誤り訂正符号化バイト数は、数バイトから数百バイトまでの範囲となる。マルチレ

50

ペルセルNANDフラッシュデバイスによっては、誤り訂正基準は、1KBのユーザデータにつき40ビットとなる。マルチレベルセルNANDフラッシュデバイスによっては、符号化率（読み出しユニット内の全バイトに対するユーザバイトの比）は、典型的には94%未満となる。例えば、MLC NANDフラッシュデバイスは、サイズ17664バイトのページを有し、そのうち、16384バイトはマッピングされたデータを格納するために名目上使用され、1280バイトはメタデータ及び誤り訂正符号化バイトを格納するために名目上使用される「予備」バイトである。MLC NANDフラッシュデバイスに推奨される誤り訂正符号化強度は、1KBにつき40ビットの訂正であり、これは、1KBのマッピングされたデータバイトにつき70バイトの予備バイトを使用するものとなる。

## 【0030】

10

図4を参照すると、論理ブロックアドレスを、1つ以上の読み出しユニットにまたがる可変サイズ領域へとマッピングする一実施形態の特定の細部が示されている。実施形態によっては、VFTLマッピングが、可変サイズの（例えば圧縮された）マッピングユニットのアドレス（又はラベル）（例えば、LBA[M:U] 110）を、該マップの各エントリにおいて読み出しユニットアドレス404及びスパン（読み出しユニットの個数）406として表される読み出しユニットの個数へとマッピングする。複数のマップエントリのうちの1つにより参照される読み出しユニットは、1つ以上の（論理的及び／又は物理的に）シーケンシャルな不揮発性メモリページ内にあり、例えば、読み出しユニットの個数は、随意選択的に及び／又は選択的に不揮発性メモリページの境界をまたぐものとなる。複数の読み出しユニット内にデータを詰め込む様々な実施形態において、一般にマップの1つのエントリだけでは（該エントリが読み出しユニットを参照するだけのものであって該読み出しユニット内のデータの位置を参照するものではないため）それに関連づけられたデータを特定するには不十分であり、該関連づけられたデータを正確に特定するには、参照される読み出しユニット内の更なる情報（例えばヘッダ）が使用される。

## 【0031】

20

実施形態によっては、データは、不揮発性メモリの複数のダイにわたってストライプ化された様様で複数の不揮発性メモリページ内に書き込まれる。複数のダイにわたる書き込みデータのストライプ化は、1つのストライプにつき1回だけ所与の1つのダイ内に1つの不揮発性メモリページを書き込むことのみにより一層大きな書き込み帯域幅を有利にも可能とするものである。複数のダイにわたる複数のブロックのストライプは、冗長ブロックと呼ばれる。これは、更なる実施形態及び／又は使用様様において、例えば1つの冗長ダイを使用して、RAIDのような冗長性が冗長ブロックベースで付与されるからである。様々な実施形態において、不揮発性メモリのブロックによっては、故障して書き込み時にスキップされるものがあり、このため、ストライプ化は、（該不良ブロックの不揮発性メモリページ内に書き込みを行うのではなく）ダイがスキップされる「穴」を有する場合がある。かかる実施形態では、「シーケンシャルな」不揮発性メモリページは、該不揮発性メモリページが書き込まれる順序によって決まる論理的な順序でシーケンシャルなものとなる。

## 【0032】

30

図5を参照すると、ヘッダ及びデータからなる読み出しユニットの一実施形態の特定の細部が示されている。様々な実施形態において、図4に示すマッピングは、該読み出しユニット内の可変サイズデータを特定するための基準を生み出すものである。図5に示すように、各読み出しユニット（例えば読み出しユニット500,510）は、一組の0個以上のヘッダ501を有し、該ヘッダは、可変サイズデータが1つ以上の読み出しユニット内に「タイル状に配置される」（例えば、無駄なスペースを伴うことなく密に詰め込まれる）際に、典型的にはハードウェアによって書き込まれる。不揮発性メモリが読み出される際に、該ヘッダが典型的には他のハードウェアによって解釈されて可変サイズデータが抽出される。可変サイズデータは、一致する論理ブロックアドレス（又はラベル）を有する複数のヘッダのうちの1つにおける個々のオフセット及び長さによって特定され、該データは、随意選択的に及び／又は選択的に複数の読み出しユニットにまたがるものとなる（例えば

40

50

、「データ, 開始」及び「データ, 繼続」で示す可変サイズデータ)。

#### 【0033】

様々な実施形態において、ヘッダは、リサイクル処理(例えば、不要データ収集及び/又は消耗平滑化)の一部としても使用され、該ヘッダ内に論理ブロックアドレス(又は等価的にはマッピングユニットアドレス又はラベル)を含み、これは、読み出しユニット内の可変サイズデータを発見することを可能とし、及び複数の読み出しユニットのうちの特定の1つが読み出される際に、(マップ内の論理ブロックアドレス又はラベルをルックアップして、該マップが依然として該特定の読み出しユニットの物理アドレスを参照しているか、又は複数の読み出しユニットのうちの別の読み出しユニットを参照するよう更新されているかを判定することにより、)内部の可変サイズデータが依然として有効であるか、又は上書きされたものであるかを判定するための手段を提供するものとなる。このため、ヘッダは(物理ロケーションから論理ブロックアドレス(又はラベル)へと関連付けされたものであるが)、読み出しユニットの物理ロケーションと結合されたヘッダがマップ内のそれと同様の情報を有するという点で、「逆マップ」を形成するものであるということができる。10

#### 【0034】

実施形態によっては、論理ブロックアドレス(又はラベル)に基づいて読み出しユニットからデータを抽出するための専用ハードウェアが、ランダム読み出しに関して高い効率で動作するよう実施される。該専用ハードウェアは、1つ以上の読み出しユニット内の複数のヘッダをパースして、該複数のヘッダのうちで所与の論理ブロックアドレス(又はラベル)を有するヘッダを見出し、次いで個々の長さ及びオフセットを使用して、関連付けられた可変サイズデータを抽出する。しかし、ハードウェアベースのソリューションは、(シリコン面積及び電力の点で)高コストを要するものとなる。ランダム性能よりもシーケンシャル性能の方が重要であるローエンド及び/又はモバイル環境では、シリコン面積を削減し、節電し、及び高いシーケンシャルスループット率を達成するように、可変サイズフラッシュ変換レイヤに変更が加えられる。20

#### 【0035】

実施形態によっては、シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤ(例えば、SR0-VFTL)が、不揮発性メモリページ(又は実施形態によっては書き込みのために1ユニットとして扱われる1グループの不揮発性メモリページ)内にデータを(該データ内にヘッダ用のギャップを伴うことなく)タイル状に配置し(密に詰め込み)、該ヘッダの全ては不揮発性メモリページの一部内にグループ化される。更なる実施形態では、ヘッダは、(特定の可変サイズフラッシュ変換レイヤの場合のように)データにアクセスするために動的に使用されることなく、リサイクル及び(例えば予期せぬ停電からの)回復のためにのみ使用される。代替的に、マップのエントリは、不揮発性メモリページ内の可変サイズ(例えば圧縮された)データを発見するために使用される完全な情報から構成される。不揮発性メモリページの異なる部分へのヘッダ及びデータの分離は、ヘッダのみからなる読み出しユニット、ヘッダ及びデータを混合したものからなる読み出しユニット(但し、図6に示すように1つの不揮発性メモリページにつきかかる読み出しユニットは1つのみ)、及びデータのみからなる読み出しユニットへと通ずるものである30。

#### 【0036】

低コストでのシーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤは、ランダム読み出し入出力操作数/秒(例えば、10Ps)、ランダム書き込み入出力操作数/秒、及びシーケンシャル書き込みスループットといった他の測定基準についても、比較的良好に機能することが可能なものである。しかし、各読み出しユニット内にヘッダを有するVFTL型のデータタイル状配置といった機能のためのハードウェア支援をなくすと、制御プロセッサに大きな負荷が加わることになる。代替的に、実施形態によっては、シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤは、データのタイル状配置、データの抽出4050

、又はその他の操作のためにハードウェア支援を使用する。

#### 【0037】

図6を参照すると、SRO-VFTL不揮発性メモリページの一実施形態が示されている。図7を参照すると、SRO-VFTL不揮発性メモリページの別の実施形態が示されている。図6及び図7の実施形態の違いは、前の不揮発性メモリページからの継続データ640がヘッダの前にあるかヘッダの後にあるかの違いである。該不揮発性メモリページ内のデータの様々な実施形態及び構成が考えられる。

#### 【0038】

様々な実施形態によれば、不揮発性メモリページは、以下に示すものの1つ以上からなる。

10

#### 【0039】

- ヘッダ：マスタヘッダ610、随意選択的及び／又は選択的な冗長ブロックヘッダ620（例えば、冗長ブロック内の各ブロックの最初のページ内に追加されるヘッダ）、及びゼロ個以上の追加の充填ヘッダ630を含む。あらゆる不揮発性メモリページは、後続のヘッダの個数のカウントと、不揮発性メモリページ内の（ヘッダに関連付けされた）データが開始する位置へのポインタとを少なくとも有している。実施形態によっては、ヘッダは、バイト数を揃えることが可能であるが、その各々は6バイトのみとなる。ヘッダは、データヘッダ、エポックヘッダ、及びパディングを含むことが可能である（が、これには限定されない）。データヘッダは、マッピングユニットアドレス及び長さを使用する。全てのデータが連續して詰め込まれるため、オフセットは暗に示される。

20

#### 【0040】

- 前の不揮発性メモリページ（マッピングユニットの可変サイズデータの一部）から随意選択的及び／又は選択的な継続データ640。

#### 【0041】

- 不揮発性メモリページを満たすための1つ以上のマッピングユニットの充填（例えば、随意選択的及び／又は選択的に圧縮された）データ650。該不揮発性メモリページの最後は、後続の不揮発性メモリページ内に随意選択的及び／又は選択的に続く。

#### 【0042】

- 不揮発性メモリページの終わりにおける随意選択的なパディング（650に含まれる）。様々な実施形態において、該データは、バイトが詰め込まれたものであり（byte-packet）（例えば穴は存在せず）、高度に圧縮される（例えばヘッダが多すぎる）場合に不揮発性メモリページの終わりにパディングされる可能性がある。パディングは、例えば、(i) 不揮発性メモリページに追加されたデータの最後の可変サイズ片が、ヘッダのサイズよりも少ない未使用バイトを残す（このため、新しいヘッダを追加してデータの別の可変サイズ片を開始することができない）場合、及び(ii) 随意選択的及び／又は選択的に、所定のヘッダ数／不揮発性メモリページを超過する（このため、不揮発性メモリページ内に格納されるマッピングユニットの個数が、該マッピングユニットのデータのサイズではなく該所定のヘッダ数により制限される）場合に使用される。

30

#### 【0043】

実施形態によっては、シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤを用いて回復及び／又はリサイクル処理（例えば、不要データの収集）を有利に行って（シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤでない場合のように全ての読み出しユニットではなく）不揮発性メモリページの各々のヘッダ部分のみの読み出し及び／又は誤り訂正及び／又は検査を行うことが可能となる。

40

#### 【0044】

リサイクル処理が、不揮発性メモリページのデータを書き換えることが可能であると判定した場合、該データを読み出すことも可能であり、また該データの誤り訂正を行うことも可能である。実施形態によっては、リサイクル処理のために不揮発性メモリページ全体が読み出されるが、該不揮発性メモリページ内の何れかのデータがリサイクルされるべきであるという判定がなされるまで、ヘッダ部分のみが誤り訂正される。

50

**【 0 0 4 5 】**

様々な実施形態において、不揮発性メモリから全てのヘッダが読み出されることを確実にするために、1つの不揮発性メモリページあたりのヘッダ数は、読み出すことが可能な1つの不揮発性メモリページあたりの読み出しユニット数を抑制するよう制限される。図6の実施形態では、最大数のヘッダを含むのに十分な個数の読み出しユニットのみが読み出される。図7の実施形態では、前の不揮発性メモリページから完成するデータ（例えば継続データ640）の最大サイズを説明するために追加の個数の読み出しユニットが読み出される。しかし、図7の実施形態は、前の不揮発性メモリページからのデータの完成（例えば継続データ640）にアクセスするための読み出しユニット数を、関連付けされたマップエントリから判定することを可能にする。これは、データの完成におけるバイト数が、関連付けされたマップエントリのそれぞれのオフセット及び長さと、前の不揮発性メモリページ内のユーザ（非誤り訂正符号）データのバイト数に基づいて判定されるからである。更に、データの完成よりも前にあるヘッダは、（各ブロック内の最初のページといった特定の不揮発性メモリページ内にのみ存在する）随意選択的な冗長ブロックヘッダと（各不揮発性メモリページ内に常に存在する）マスタヘッダのみである。図6の実施形態では、不揮発性メモリに2回アクセスすることを必要とせずにデータの完成を読み出すために最大ヘッダ数が存在する（又は不揮発性メモリページ全体が読み出される）ものと仮定される。

**【 0 0 4 6 】**

実施形態によっては、シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤは、複数のマップエントリを有するシングルレベルマップを使用する。別の実施形態では、シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤは、第2レベルマップ（例えばSLM）ページを指示示す第1レベルマップ（例えばFLM）を有する2レベルマップといったマルチレベルマップを使用し、該2レベルマップの場合、第2レベルマップページの各々は、複数のリーフ（leaf）レベルマップエントリからなる。更なる実施形態では、マルチレベルマップは2レベルよりも多くのレベル（例えば3レベル）を有する。実施形態及び／又は使用態様によっては、マルチレベルマップの使用は、該マップの関連する（例えば使用中の）部分のみをローカルメモリ（例えば、半導体ドライブコントローラのオンチップSRAM又はホストのローカルDRAM）内に格納することを可能とし、これにより該マップを維持するコストが削減される。例えば、典型的な使用パターンは、任意の時点でアクティブである1ギガバイト（例えばGB）の論理ブロックアドレス空間を有し、次いで該論理ブロックアドレス空間のアクティブな1GB部分にアクセスするのに十分なマップの一部が（不揮発性メモリ内に格納されるのではなく）高速アクセスのためにローカルに格納される。該論理ブロックアドレス空間のアクティブな部分以外の参照は、不揮発性メモリからマルチレベルマップの1以上のレベルの要求された部分をフェッチし、該マップの他のローカルに格納されている部分を随意選択的及び／又は選択的に置き換える。

**【 0 0 4 7 】**

複数のリーフレベルマップエントリの各々は、複数のマッピングユニットのうちの1つのアドレス（又はラベル）に関連付けられる（対応する）。一実施形態では、論理ブロックアドレスは、例えば、論理ブロックアドレスのゼロ以上の最下位ビット（例えばLSB）を削除すること及び／又はアライメントのために論理ブロックアドレスに定数を加算することにより、マッピングユニットアドレスへと変換され、該マッピングユニットアドレスがマップ内でルックアップされて該マップの対応するエントリが判定される。別の実施形態では、ラベルがハッシュテーブル（又は他の連想データ構造）内でルックアップされて、マッピングユニットアドレスとして使用される一意の識別子が判定される。

**【 0 0 4 8 】**

図8を参照すると、様々なタイプのヘッダの実施形態の細部が示されている。図8の例では、ヘッダは、それぞれ6バイトに適合するようフォーマットされている。様々な実施形態によれば、様々なタイプのヘッダは、全て同一サイズのもの、随意選択的及び／又は

選択的に異なるサイズのもの、それぞれヘッダのサイズを指定する個々のフィールドを含むもの、異なる不揮発性メモリページ内でサイズが変動するもの、及び上述したものの任意の組み合わせのうちの1つ以上である。

#### 【0049】

様々な実施形態によれば、不揮発性メモリページ内のヘッダは、以下に示すもののうちの1つ以上である。

#### 【0050】

- 可変サイズデータ部分に関する情報を示すデータヘッダ(810)。実施形態によっては、データヘッダに関連付けされたデータは、該データヘッダが現れる不揮発性メモリページと同一の不揮発性メモリページ内で開始する。更なる実施形態及び/又は使用形態では、不揮発性メモリページがデータヘッダ用の残りの空間しか有していない場合に、関連付けされたデータの全てが後続の不揮発性メモリページ内で開始する。10

#### 【0051】

- 第2レベルマップ(例えばSLM)ヘッダ(820)等のマップヘッダ。該第2レベルマップヘッダは、(例えば第2レベルマップのリサイクル及び/又は回復のために)どの第2レベルマップページが格納されているかを示すための第1レベルマップインデックス(例えばFLMI)を含む。

#### 【0052】

- ログ/チェックポイントヘッダ(820)。ログ/チェックポイントヘッダは、リサイクル、回復、誤り操作、デバッグ、又はその他の特別な条件のために使用されるデータを示す。20

#### 【0053】

- エポックヘッダ(830)は、データを対応するマップ/チェックポイント情報に関連付けるために回復の一部として使用される。典型的には、1つの不揮発性メモリページにつき少なくとも1つのエポックヘッダが存在する。

#### 【0054】

- マスタヘッダ(870)は、不揮発性メモリページ内のヘッダの数と不揮発性メモリページ内において非ヘッダデータが開始する場所とに関する情報を提供するために、1つの不揮発性メモリページにつき1回使用される。図6及び図7に示すように、様々な技術が非ヘッダデータの始まりを判定する。30

#### 【0055】

- 冗長ブロックヘッダ(880)は、冗長ブロック内の各ブロックにおける第1の不揮発性メモリページといった特定の不揮発性メモリページで使用される。

#### 【0056】

- パディングヘッダ、より大きな長さをサポートするチェックポイントヘッダといった、他のタイプのヘッダ(840)。

#### 【0057】

実施形態によっては、ヘッダは、該ヘッダの複数のサブタイプを提供するTYPEフィールドを含む。様々な実施形態において、ヘッダは、該ヘッダに関連付けされたデータの長さを含むLEN(長さ)フィールドを含む。様々な実施形態において、LENフィールドではなく、又はLENフィールドに加えて、ヘッダは、該ヘッダに関連付けされたデータの終わりへの(不揮発性メモリページ内の)オフセットを含むOFFSET(オフセット)フィールド(図示せず)を含む。(実施形態によっては、可変サイズデータ片のうちの少なくとも1つが1つの不揮発性メモリページをまたぐ場合、該OFFSETは、後続の不揮発性メモリページ内のオフセット、又は後続の不揮発性メモリページ内のバイト数となる。)LENフィールド又はOFFSETフィールドの一方のみが一般に実施される。これは、無駄な空間なしで詰め込まれる可変サイズデータ片を用いる場合には、不揮発性メモリページ内の各可変サイズデータ片の開始位置及び終了位置が、該不揮発性メモリページ内の第1の可変サイズデータ片の開始位置(例えば、図7の場合のようにヘッダの直後)とLEN又はOFFSETフィールドのリストによって暗に示されるからである。40

**【 0 0 5 8 】**

図9を参照すると、マップエントリ900の一実施形態の特定の細部が示されている。様々な実施形態によれば、該マップのエントリは、以下に示すものの1つ以上からなる。

**【 0 0 5 9 】**

- 物理的な不揮発性メモリページアドレス

- 可変サイズデータアイテムに対する不揮発性メモリページ内のオフセット（例えば、OFFSET）

- 該可変サイズデータアイテムの長さ（例えば、LEN\_M128）

- その他の制御情報

実施形態によっては、長さは、例えば、値0が特定の最小長さに対応するようにオフセットされることにより、エンコードされる。例えば、最小長さが128バイトである場合、LEN\_M128の値0は、128バイトを表す。更なる実施形態では、特定の最小長さ未満に圧縮されたデータは、そのサイズが少なくとも該特定の最小長さとなるようにパディングされる。

10

**【 0 0 6 0 】**

様々な実施形態において、SR0-VFTLマップエントリは、対応するデータの完全なオフセット及びバイト長さを格納するため、VFTLマップエントリよりも大きい。したがって、不揮発性メモリ内に格納する際にマップエントリのサイズを縮小させるのが有利である。典型的な用途では、データは、少なくとも一定の粒度で、及び／又は1よりも大きい平均シーケンシャルマッピングユニット数で、シーケンシャルに読み書きされることが多い。書き込みのシーケンシャルな性質を利用したマップエントリの圧縮フォーマットは、比較的安価に実施することが可能であり、及び高いマップ圧縮率を生じさせるものである。マップエントリの圧縮は、不揮発性メモリページの境界を越えるまで、同じ不揮発性メモリページ内にシーケンシャルに書き込まれていくデータによって更に支援される。

20

**【 0 0 6 1 】**

図10を参照すると、様々な圧縮されたマップエントリの一実施形態の特定の細部が示されている。該様々なマップエントリは、非圧縮のマップエントリ(1010)、前のマップエントリと同じ不揮発性メモリページアドレスを有するマップエントリ(1020)、前のマップエントリと同じ不揮発性メモリページアドレスを有し、且つ前のデータが終了するオフセットで開始するマップエントリ(1030)、及び前のマップエントリと同じ不揮発性メモリページアドレスを有し、前のデータが終了するオフセットで開始し、且つ前のマップエントリと同じ長さを有するマップエントリ(1040)を含む。

30

**【 0 0 6 2 】**

マルチレベルマップを有する実施形態によっては、低レベル（例えばリーフレベル）マップページのキャッシュが維持される。該キャッシュされたマップページは、非圧縮形態にあり、プロセッサ（例えばホスト又は半導体ドライブコントローラの制御プロセッサ）による迅速なアクセスを提供するものである。マップページが（例えば不揮発性メモリ又はダイナミックランダムアクセスメモリ（例えばDRAM）から）キャッシュ内に移動される場合、該マップページは圧縮されない。該マップページが（例えば変更されることにより）該キャッシュからフラッシュされる場合には、該マップページは圧縮されて（例えば不揮発性メモリ内に）格納される。ダイナミックランダムアクセスメモリ内にマップページの一部又は全部を格納することによりレイテンシを低減させるべくDRAMを使用する様々な実施形態によれば、該ダイナミックランダムアクセスメモリ内のマップページは、圧縮形態、非圧縮形態、選択的な圧縮又は非圧縮状態のうちの1つ以上で格納され、及び／又はダイナミックランダムアクセスメモリ内の（可変サイズの）圧縮形態のマップページへのアクセスに使用される間接テーブルを用いて格納される。

40

**【 0 0 6 3 】**

実施形態によっては、ホスト書き込みコマンドのホスト書き込みデータは、該ホスト書き込みデータが半導体ドライブコントローラに到達する際に、随意選択的及び／又は選択的に圧縮されて、ファースト・イン・ファースト・アウト（例えばFIFO）様様でローカル

50

(例えばオンチップ)メモリ内に格納される。例えば、実施形態によっては、ホスト書き込みデータは、ファームウェアデータ構造、フラッシュ統計データ、マップの一部(例えばマップの1ページ以上を保持するキャッシュ)、リサイクル用の読み出しデータを含む不揮発性メモリからの読み出しデータ、不揮発性メモリに書き込むべきデータのヘッダ、ソフトウェアコード、ファームウェアコード及びその他と共に、統合(unified)バッファ(例えば図11A中のUBUF)内に格納される。様々な実施形態において、半導体ドライブの様々なローカル格納基準のために、1つ以上の専用メモリが使用される。

#### 【0064】

実施形態によっては、ホスト書き込みコマンドのホスト書き込みデータは、半導体ドライブコントローラへの送信に先立ち、ホストにより随意選択的及び/又は選択的に圧縮される。例えば、データベースレコードは、その入出力装置への書き込みに先立ち、ホストデータベースにより圧縮される。10

#### 【0065】

様々な実施形態において、ホストから到達するデータの各マッピングユニットを用いて、それぞれのマッピングユニットアドレス、該それぞれのマッピングユニットアドレスに関するデータが格納されるそれぞれのローカルメモリアドレス、及び/又は可変サイズの(例えば圧縮された)ホストデータの各マッピングユニットのそれぞれの長さのうちの1つ以上が、半導体ドライブの制御プロセッサ(例えば図11A中の中央処理装置CPU)に通知される。該制御プロセッサは、不揮発性メモリページの書き込み順、及び不揮発性メモリページの各々において利用可能な非誤り訂正符号化バイトの総数を判定することが可能である。複数の不揮発性メモリページのうちの所与の1つにおける利用可能な非誤り訂正符号化バイトの総数に従って、制御プロセッサは、該所与の不揮発性メモリページ内に配置されるヘッダの量及びデータの量を判定することが可能となる。例えば、制御プロセッサは、該所与の不揮発性メモリページについてヘッダを蓄積し(及び今まで使用したヘッダのバイト数を追跡し)、該所与の不揮発性メモリページが一杯になるまでマッピングユニットの可変サイズデータとヘッダを該所与の不揮発性メモリページに1つずつ追加する。該所与の不揮発性メモリページが一杯になった際に、該所与の不揮発性メモリページに追加される複数のマッピングユニットのうちの最後の1つのデータの最後の部分は、おそらくは該所与の不揮発性メモリページに適合せず、該複数の不揮発性メモリページのうちの後続の1つの不揮発性メモリページのデータ完成部分(例えば継続データ640)として使用され、新しいヘッダ及びデータについて該後続の不揮発性メモリページで利用可能となる非誤り訂正符号化バイトの総数が削減される。20

#### 【0066】

実施形態によっては、特定の時点で、ゼロ以上の不揮発性メモリページをホスト書き込みデータで満たすことが可能となり、及びゼロ以上の不揮発性メモリページをリサイクルデータで満たすことが可能となる。例えば、少なくとも2つのバンド(例えば、FIFOのような一連の冗長ブロック)のうちの1つのバンドを(例えば、ホストから到着したばかりの)「ホット」データで満たし、他のバンドを(リサイクルされた)「コールド」データで満たすことが可能であり、ゼロ以上の不揮発性メモリページに相当する空間がバッファから各バンドへと割り当てられる。この例では、様々な実施形態において、ホスト書き込みデータを随意選択的及び/又は選択的に前記ホットバンド又は前記コールドバンドに送ることが可能であり、及びリサイクルデータを随意選択的及び/又は選択的に前記ホットバンド又は前記コールドバンドに送ることが可能である。40

#### 【0067】

実施形態によっては、制御プロセッサは、一連の個々のマッピングユニットアドレス、ローカルメモリアドレス、及び個々の長さを、以下に示すもののうちの1つ以上へと変換することが可能である:不揮発性メモリページのヘッダ部分として該不揮発性メモリページに書き込まれるべき一連のヘッダ;不揮発性メモリページのユーザデータ部分(少なくとも1つのマッピングユニットのデータの少なくとも一部を含む)として該不揮発性メモリページに書き込まれるべきローカルメモリのシーケンシャル部分の第1の開始アドレス50

及び第1の長さ；後続の不揮発性メモリページのユーザデータ完成部分（1つのマッピングユニットのデータの一部を含み又は空である）として該後続の不揮発性メモリページに書き込まれるべきローカルメモリのシーケンシャル部分の第2の開始アドレス及び第2の長さ；不揮発性メモリページに書き込まれるべきゼロ以上のパディングバイトの個数（該パディングバイトは、例えば、ユーザデータ完成部分が空であり及び不揮発性メモリページが一杯でない場合に使用される）。有利なことに、制御プロセッサは、該一連の個々のマッピングユニットアドレス、個々のローカルメモリアドレス、及び個々の長さを、一連のヘッダへと単純に変換することが可能であり、該変換は、再フォーマットを行い、及び少数のダイレクトメモリアクセス（例えばDMA）コマンドを生成して、不揮発性メモリページを構成する部分（一連のヘッダ、前の不揮発性メモリページの完成部分、ユーザデータ部分、及びあらゆるパディングバイト）を不揮発性メモリへ転送することにより行うことが可能である。10

#### 【0068】

様々な実施形態において、ホスト書き込みデータの圧縮は、随意選択的及び／又は選択的に行なうことが可能である。一例では、ホスト書き込みコマンドの情報が選択的に圧縮を行うことを可能にする。別の例では、ホスト書き込みコマンドの論理ブロックアドレス（又はラベル）の関数として選択的に圧縮を行なうことが可能となる。更に別の例では、ホスト書き込みデータの圧縮によって該ホスト書き込みデータのサイズが縮小しない場合に、圧縮が選択的に利用不能となる。圧縮が可能とならない場合には、ホスト書き込みデータは非圧縮状態で格納される。様々な実施形態によれば、マップのエントリは、以下に示すもののうちの1つ以上により、対応するデータが圧縮されているか圧縮されていないかを示すものである：マップの各エントリ内の個々のビット；及び／又は各マップエントリ内に格納されている長さの値。例えば、マッピングユニットが4KBである場合、マップエントリ中の4KBの長さは、該マップの関連付けされたデータが圧縮されていないことを示し、一方、4KB未満の長さは、関連付けされたデータが圧縮されていることを示す。実施形態及び／又は使用形態によっては、格納されている随意選択的及び／又は選択的に圧縮されるホスト書き込みデータに関連付けされたヘッダは、該格納されているホスト書き込みデータが圧縮されているか否かを指定するものとなる。20

#### 【0069】

実施形態によっては、リサイクルすべき冗長ブロックを選択し、該冗長ブロックの不揮発性メモリページを該不揮発性メモリページが書き込まれた順に読み出し、該不揮発性メモリページのヘッダを含む読み出しうニットのみを処理し、マップ内のデータヘッダである各ヘッダの論理ブロックアドレス（又は等価的にはマッピングユニットアドレス又はラベル）をルックアップしてデータが依然として有効であるか否かを確認し、該データが依然として有効である場合には、適当な新しいヘッダ及びDMAコマンドを構築し、新しい不揮発性メモリページの一部としてリサイクルされるようデータを構成することにより、データがリサイクルされる。次いで、該新しい不揮発性メモリページが不揮発性メモリに書き込まれる。30

#### 【0070】

図11Aを参照すると、半導体ドライブコントローラ1100の一実施形態の特定の細部が示されている。実施形態によっては、該半導体ドライブコントローラ1100は、例えば、ホストと協働してフラッシュ変換レイヤを実施することにより、1つ以上のフラッシュ変換レイヤ又はその一部を実施することが可能である。様々な実施形態において、コントローラ1100は、1つ以上の集積回路として実施することが可能である。40

#### 【0071】

図11Aに示すように、半導体ドライブコントローラ1100のSerDes（例えばシリアルライザ・デシリアルライザ）等の入出力レシーバが、外部インタフェイス1111を介してホストに接続される。ホストインターフェイス（例えばHIF）は、SerDesを介して、読み出しこマンド及び書き込みコマンド等のコマンドを受信し、書き込みデータを受信し、及び読み出しだデータを送信する。該コマンドは、共有メモリ（例えばOpRAM）を介して中央処理装置へ50

送信される。該中央処理装置は、該コマンドを解釈し、及び前記共有メモリを介して該半導体ドライブコントローラの他の部分を制御する。例えば、中央処理装置は、共有メモリを介して、様々なデータ経路の送受信ユニット（例えば、ホストデータ経路受信セグメント（例えばHDRx）又はフラッシュデータ経路送信セグメント（例えばFDTx））との間でDMAコマンドを通信し及び応答を受信する。

#### 【0072】

ホストインターフェイスからの書き込みデータは、ホストデータ経路受信セグメント（例えばHDRx）を介して統合バッファ（例えばUBUF）へ転送される。様々な実施形態において、該ホストデータ経路受信セグメントは、ホスト書き込みデータを随意選択的及び／又は選択的に圧縮し及び／又は暗号化するためのロジックを含む。該随意選択的及び／又は選択的に圧縮され及び／又は暗号化されたホスト書き込みデータは、次いで、統合バッファからフラッシュデータ経路送信セグメント及び汎用フラッシュインターフェイス（例えばGAFI）を介して不揮発性メモリへ送られる。様々な実施形態において、該フラッシュデータ経路送信セグメントは、暗号化及び／又はスクランブリング及び／又は誤り訂正符号化を実行するためのロジックを含む。ホスト読み出しコマンドに応じて、データが汎用フラッシュインターフェイスを介して不揮発性メモリから読み出され、フラッシュデータ経路受信セグメント（例えばFDRx）を介して統合バッファへ送信される。様々な実施形態において、該フラッシュデータ経路受信セグメントは、誤り訂正復号化及び／又は暗号解読及び／又はデスクランブリング（de-scrambling）を含む。別の実施形態では、別個の誤り訂正復号化手段（例えばLDPC符号を実施するためのLDPC-D）が、フラッシュデータ経路受信セグメントにより統合バッファ内に格納された「生（raw）」データを操作することが可能である。次いで、統合バッファ内の復号化された読み出しデータが、ホストデータ経路送信セグメント（例えばHDTx）を介してホストインターフェイスへ送信される。様々な実施形態において、ホストデータ経路送信セグメントは、復号化された読み出しデータの暗号解読及び／又は解凍を随意選択的及び／又は選択的に行うためのロジックを含む。実施形態によっては、RAIDのような軟判定処理装置（例えばRASP）が、RAIDのような冗長性を提供して、不揮発性メモリに格納されたホスト書き込みデータ及び／又はシステムデータの更なる保護を行うこと、及び／又はLDPC-Dと共に使用するための軟判定処理の操作を行うことが可能である。

#### 【0073】

様々な実施形態によれば、半導体ドライブコントローラは、1つ以上のフラッシュ変換レイヤの一部または全てを実施することが可能であり、又はフラッシュ変換レイヤを実施しないことが可能である。一例では、フラッシュ変換レイヤの高レベルマッピング部分がホスト上で実行され、該フラッシュ変換レイヤの下位レベルマッピング部分が半導体ドライブコントローラ内で実行される。別の例では、半導体ドライブコントローラは、抽象化された物理ユニットアドレス（例えばホストとの間での読み出しユニットアドレス及びスパン）を送受信し、ホストは、論理ロックアドレス（又はラベル）を該抽象化された物理ユニットアドレスへとマッピングする。半導体ドライブコントローラは、該抽象化された物理ユニットアドレスに関する特定のデータを、ヘッダに格納されている該特定のデータの識別子（例えば論理ロックアドレス（又はラベル））を介して探し出すことを可能にする。更に別の実施形態では、論理ロックアドレス（又はラベル）のホストでのマッピングは、不揮発性メモリページアドレス、該不揮発性メモリページ内のオフセット、及びバイト長さを生成する。半導体ドライブコントローラは、1つ以上の不揮発性メモリページ内の特定のデータを取り出すためにアクセスすべき不揮発性メモリ内の複数の読み出しユニットを判定することが可能である。有利なことに、1つ以上の例では、誤り訂正符号化の細部（例えば、1つの不揮発性メモリページあたりのユーザデータバイト数又は読み出しユニットのサイズ）が半導体ドライブコントローラによって維持され、これによりホストにおけるオーバーヘッドが低減される。

#### 【0074】

図11Bを参照すると、データ経路セグメントの一実施形態の特定の細部が示されてい

10

20

30

40

50

る。データ経路セグメント1190は、図11Aのホストデータ経路受信セグメント又はフラッシュデータ経路送信セグメントを示し得るものである。データ経路セグメント1190は、読み出しシーケンサ1130、書き込みシーケンサ1140、及びゼロ以上のデータ経路ユニット（例えばDPU）を含む。図11Bは、2つのデータ経路ユニット1150-1, 1150-2を有する一例を示している。

#### 【0075】

読み出しシーケンサ1130は、読み出され／アクセスされるべきデータを特定する制御情報を受信するためにOpRAM（図11A参照）に接続されている。例えば、該情報は、統合バッファ内のアドレス及び／又は長さ、又はホストインタフェイス若しくは汎用フラッシュユインタフェイスに対するコマンドとすることが可能であり、またデータと混合されるべきコマンドを指定することが可能である。読み出しシーケンサ1130はまた（例えばUBUF、ホストインタフェイス、又は汎用フラッシュユインタフェイスから）データを読み出し及び／又はアクセスするために読み出し手段1110に接続されている。読み出しシーケンサ1130は、OpRAMから受信した要求に従って、読み出しデータ及びコマンドのインタリーブされたストリームを、ゼロ以上のデータ経路ユニット1150-1, 1150-2及び書き込みシーケンサ1140へ送信することが可能である。10

#### 【0076】

書き込みシーケンサ1140は、読み出しシーケンサ1130により送信されたデータ及びコマンドのインタリーブされたストリームを受信することが可能である。書き込みシーケンサ1140は、（例えばUBUF、ホストインタフェイス、又は汎用フラッシュユインタフェイスへ）データを書き込むために書き込み手段1120に接続されている。データは、書き込みシーケンサ1140により受信されたデータストリーム内のコマンドに従って（例えば、アドレス及び／又は長さを指定するコマンドにより）書き込まれる。書き込みシーケンサ1140はまた、受信したコマンドに従って、書き込まれたデータに関するステータス情報を送信するために、OpRAM（図11A参照）に接続されている。例えば、ステータス情報は、データストリームの特定部分（例えば、1つの4KBマッピングユニット）の書き込みが完了したことを示すためにOpRAM内に書き込まれる。20

#### 【0077】

データ経路ユニット1150-1, 1150-2は、読み出しシーケンサ1130と書き込みシーケンサ1140との間を移動する間にデータを変換することが可能である。データストリーム内の読み出しシーケンサ1130により生成されたコマンドは、データ経路ユニット1150-1, 1150-2又は書き込みシーケンサ1140のうちの1つ以上により受信されるように、随意選択的及び／又は選択的にその宛先が設定される。データ経路ユニット1150-1, 1150-2の例として、以下のものが挙げられる：

- 暗号化に使用すべきソルト（初期化ベクトル）を含むコマンドを受信し、該ソルトに従ってそれに続くデータを暗号化する暗号化ユニット。更なる実施形態では、該コマンドは暗号化鍵の仕様も含む。

#### 【0078】

- 復号化に使用すべきソルト（初期化ベクトル）を含むコマンドを受信し、該ソルトに従ってそれに続くデータを復号化する復号化ユニット。更なる実施形態では、該コマンドは復号化鍵の仕様も含む。

#### 【0079】

- 圧縮ユニット（例えばマッピングユニット）の境界の始まりを示すコマンドを受信し、それに続くデータを圧縮する、圧縮ユニット。様々な実施形態において、該コマンドはまた、1つのユニットとして圧縮されるべきデータの量、圧縮形式、圧縮のための最大実行時間、及びその他の圧縮制御のうちの1つ以上を含む。

#### 【0080】

- 圧縮ユニットの境界の始まりを示すコマンドを受信し、それに続くデータを解凍する、解凍ユニット。様々な実施形態において、該コマンドはまた、1つのユニットとして解凍されるべきデータの量、解凍データの予想サイズ、解凍形式、解凍のための最大実行時4050

間、及びその他の解凍制御のうちの 1 つ以上を含む。

**【 0 0 8 1 】**

- 巡回冗長検査値を計算するために使用すべきソルト（初期化ベクトル）を含むコマンドを受信し、該ソルトに従ってそれに続くデータについて巡回冗長検査値を計算する、巡回冗長検査（例えばCRC）ユニット。更なる実施形態では、該コマンドは、巡回冗長検査ユニットが、前に計算した巡回冗長検査値を、該巡回冗長検査値によりカバーされる前に受信したデータに随意選択的及び／又は選択的に付加することを可能にする。

**【 0 0 8 2 】**

- 符号化率を含むコマンドを受信し、該符号化率の誤り訂正符号に従って該コマンドに続くデータを符号化し及び／又は復号化する、誤り訂正符号化及び／又は復号化ユニット。更なる実施形態では、該コマンドは、例えば、軟判定処理情報、使用すべき最大反復数、及びその他の符号化器及び／又は復号化器制御情報といった、追加の制御を随意選択的及び／又は選択的に含むことが可能である。

**【 0 0 8 3 】**

処理の一例では、ホストからの書き込みコマンドの受信に応じて、ホストデータ経路受信セグメントの読み出しシーケンサのためのコマンドリストが中央処理装置により構築され、該コマンドリストに従って、ホストデータ経路受信セグメントが、該書き込みコマンドの書き込みデータをホストからホストインターフェイスを介して統合バッファへと送信することが可能となる。ホストデータ経路受信セグメント内のデータ経路ユニットは、（圧縮された）書き込みデータが統合バッファに書き込まれる前に該書き込みデータを圧縮することが可能である。複数の（圧縮された）マッピングユニットを無駄な空間を伴うことなく統合バッファ内に緊密に詰め込むことが可能である。中央処理装置には、（ホストデータ経路受信セグメントの書き込みシーケンサを介して）OpRAMに書き込まれたステータス情報によって、各マッピングユニットのロケーション及びサイズが通知される。中央処理装置は、該ステータス情報に従ってヘッダを構築し、及び 1 つの不揮発性メモリページを満たすヘッダ及び（圧縮された）マッピングユニットの量を判定することが可能である。中央処理装置は更に、フラッシュデータ経路送信セグメントの読み出しシーケンサがヘッダ及びデータからなる不揮発性メモリページを不揮発性メモリへ送信するため、コマンドリストを構築することが可能である。該フラッシュデータ経路送信セグメント内のデータ経路ユニットは、不揮発性メモリへ送信されるヘッダ及びデータを符号化し、誤り訂正符号化保護のための追加バイトを複数の読み出しユニットの各々に追加することが可能である。NVMページ書き込みが完了したフラッシュデータ経路送信セグメントの書き込みシーケンサからのステータスの受信時に、（圧縮された）マッピングユニットにより統合バッファ内で使用されている空間が再要求可能（再使用可能）となる。

**【 0 0 8 4 】**

別の処理の一例では、ホストからの読み出しコマンドの受信に応じて、フラッシュデータ経路受信セグメントの読み出しシーケンサのためのコマンドリストが中央処理装置により構築され、該コマンドリストに従って、該フラッシュデータ経路受信セグメントは、不揮発性メモリから汎用フラッシュインターフェイスを介して統合バッファへと読み出された 1 つ以上の読み出しユニットを受信することが可能である。実施形態によっては、フラッシュデータ経路受信セグメント内のデータ経路ユニットは、各読み出しユニットが有する誤り訂正符号化保護のための追加バイトを使用して、不揮発性メモリへ送信されるデータを復号化することが可能である。別の実施形態では、誤り訂正是、別個のデータ経路セグメント（例えば、図 11 A 中の LDPC-D）を介して生じることが可能である。中央処理装置は、フラッシュデータ経路受信セグメントの書き込みシーケンサから、また別の実施形態では LDPC-D データ経路セグメントの書き込みシーケンサから、ステータスを受信することにより、統合バッファ内の（訂正済み）データを受信したことが通知される。中央処理装置は更に、ホストデータ経路送信セグメントが訂正済みデータの少なくとも一部を統合バッファからホストインターフェイスを介してホストへ送信するため、コマンドリストを構築することが可能である。ホストデータ経路送信セグメント内のデータ経路ユニットは、

10

20

30

40

50

ホストへの送信に先立って訂正済みデータを解凍することが可能である。訂正済みデータの送信が成功裏に完了したホストデータ経路送信セグメントの書き込みシーケンサからのステータスの受信時に、該訂正済みデータにより統合バッファ内で使用されていた空間が再要求可能（再使用可能）となる。

【0085】

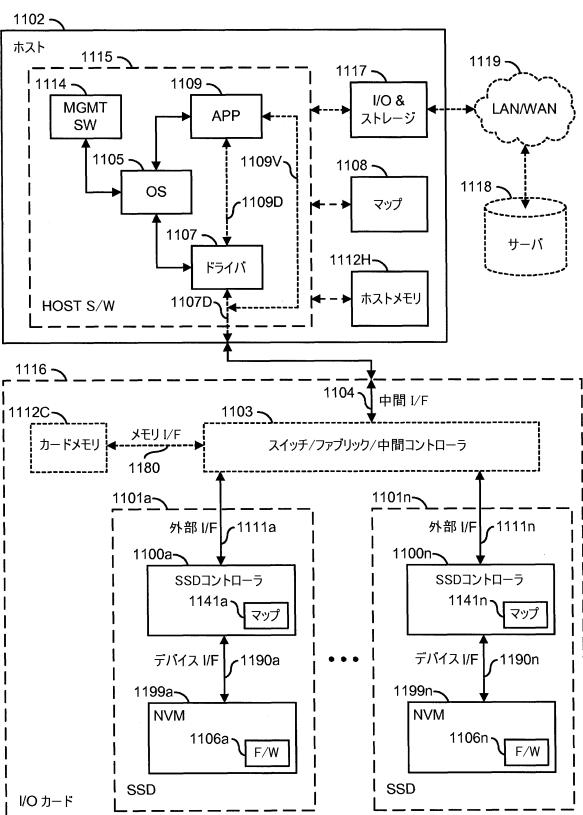

図11Cを参照すると、本発明の一実施形態によるシステムの様々な実施形態の特定の細部が示されている。該実施形態は一般に、図11Aの半導体ドライブコントローラ1100の1つ以上の実例を含む。複数の半導体ドライブ1101a-1101nは一般に、それぞれ、デバイスインターフェイス1190a-1190nを介して不揮発性メモリ1199a-1199nに接続された半導体ドライブコントローラ1100a-1100nを含む。同図は、様々な種類の実施形態を示しており、すなわち、ホスト1102に直接接続された单一の半導体ドライブ、それぞれの外部インターフェイス1111a-1111nを介してホスト1102にそれぞれ直接接続された複数の半導体ドライブ、及び様々な相互接続要素を介してホスト1102に間接的に接続された1つ以上の半導体ドライブを示している。10

【0086】

ホストに直接接続された单一の半導体ドライブの一実施形態として、半導体ドライブ1101aの実例は、外部インターフェイス1111aを介して（例えば、スイッチ／ファブリック／中間コントローラ1103を省略し、バイパスし、または通過して）ホスト1102に直接接続される。それぞれの外部インターフェイスを介してホストにそれぞれ直接接続される複数の半導体ドライブの一実施形態として、複数の半導体ドライブ1101a-1101nの実例の各々は、外部インターフェイス1111a-1111nのそれぞれの実例を介して（例えば、スイッチ／ファブリック／中間コントローラ1103を省略し、バイパスし、または通過して）それぞれホスト1102に直接接続される。様々な相互接続要素を介してホストに間接的に接続される1つ以上の半導体ドライブの一実施形態として、半導体ドライブ1101の1つ以上の実例がそれぞれホスト1102に間接的に接続される。各々の間接的な接続は、スイッチ／ファブリック／中間コントローラ1103に接続された外部インターフェイス1111a-1111nと、ホスト1102に接続された中間インターフェイス1104とのそれぞれの実例を介して行われる。20

【0087】

スイッチ／ファブリック／中間コントローラ1103を含む実施形態によっては、メモリインターフェイス1180を介して接続されると共に半導体ドライブ1101a-1101nにより及び／又はホスト1102によりアクセスすることが可能なカードメモリ1112cも含む。様々な実施形態において、1つ以上の半導体ドライブ1101a-1101n、スイッチ／ファブリック／中間コントローラ1103、及び／又はカードメモリ1112cは、物理的に識別可能なモジュール、カード、またはプラグ脱着可能な要素（例えば、入出力カード1116）上に含めることが可能である。実施形態によっては、半導体ドライブ1101a-1101n（及びその変種）は、ホスト1102として動作するイニシエータに接続されたシリアル接続SCSI（例えばSAS）ドライブ又はシリアル・アドバンスト・テクノロジー・アタッチメント（例えばSATA）ドライブに対応するものである。30

【0088】

ホスト1102は、ホストソフトウェア1115の様々な要素（例えば、オペレーティングシステム（例えばOS）1105、ドライバ1107、アプリケーション1109、及びマルチデバイス管理ソフトウェア1114の様々な組み合わせ）を実行することが可能である。破線の矢印1107dは、ホストソフトウェアと入出力装置との間の双方向通信（例えば、半導体ドライブ1101a-1101nの1つ以上の実例との間、及び、ドライバ1107を介したオペレーティングシステム1105、ドライバ1107、及びアプリケーション1109のうちの1つ以上との間で、ドライバ1107を介して又は（例えばPCIe）仮想機能（例えばVF）として直接に送受信される、データ）を表している。40

【0089】

実施形態及び／又は使用形態によっては、ホストソフトウェア1115は、半導体ドライブ1101a-1101nと共に使用されるフラッシュ変換レイヤーの一部、全部、又は複数部分を含む50

。一例では、様々な実施形態において、ドライバ1107は、半導体ドライブ1101a-1101nと共に使用されるフラッシュ変換レイヤの少なくとも一部を実施する。別の例では、様々な実施形態において、マルチデバイス管理ソフトウェア1114が、半導体ドライブ1101a-1101nと共に使用されるフラッシュ変換レイヤの少なくとも一部を実施する。

#### 【0090】

オペレーティングシステム1105は、（ドライバ1107により概念的に示される）ドライバを含み及び／又は該ドライバと共に動作して半導体ドライブ1101a-1101nとインタフェイスすることが可能となる。様々なバージョンのWindows（例えば、95、98、ME、NT、XP、2000、Server、Vista、7 及び 8）、様々なバージョンのLinux（例えば、Red Hat、Debian 及び Ubuntu）、及び様々なバージョンのMacOS（例えば、8、9 及び X）が、オペレーティングシステム1105の例である。様々な実施形態において、ドライバは、SATA、アドバンスト・ホスト・コントローラ・インターフェイス（例えばAHCI）、又はNVM Expressといった標準的なインターフェイス及び／又はプロトコルで動作することができる標準及び／又は汎用ドライバ（「市販の」又は「プリインストールされた」と称する場合もある）であり、又は、半導体ドライブ1101a-1101nに固有のコマンド及び／又はフラッシュ変換レイヤを使用することが可能となるように随意選択的にカスタマイズされた及び／又はベンダ固有のものである。ドライブ及び／又はドライバによっては、アプリケーションレベルプログラム（例えば、最適化NANDアクセス（ONAとも呼ばれる）又は直接NANDアクセス（DNAとも呼ばれる）を介したアプリケーション1109）技術が半導体ドライブ1101a-1101nにコマンドを直接通信することを可能にするバススルーモードを有し、これにより、カスタマイズされたアプリケーションが、半導体ドライブ1101a-1101nに固有のコマンド及び／又はフラッシュ変換レイヤを、汎用ドライバと同等に使用することが可能となる。ONA技術は、以下に示すもののうちの1つ以上を含む：非標準的な修飾子（ヒント）の使用、ベンダ独自のコマンドの使用、非標準的な統計データ（例えば、圧縮率に従った実際の不揮発性メモリの使用量）の通信、フラッシュ変換レイヤに固有のプロトコル（例えば、読み出しユニットアドレス及びスパンの通信、又は不揮発性メモリページアドレス、オフセット、及びバイト長の通信）の使用、及びその他の技術。DNA技術は、以下に示すもののうちの1つ以上を含む：不揮発性メモリに対するマッピングなしの読み出し、書き込み、及び／又は消去アクセスを提供する非標準的なコマンド又はベンダ独自のコマンドの使用、（例えば入出力装置が行うことになるデータのフォーマット処理をバイパスすることにより）不揮発性メモリに対する一層直接的なアクセスを提供する非標準的なコマンド又はベンダ独自のコマンドの使用、及びその他の技術。ドライバの例として、ONA又はDNAサポートなしのドライバ、ONA対応ドライバ、DNA対応ドライバ、ONA/DNA対応ドライバが挙げられる。更なるドライバの例として、ベンダにより提供されたドライバ、ベンダにより開発されたドライバ、及び／又はベンダにより改良されたドライバ、及びクライアントにより提供されたドライバ、クライアントにより開発されたドライバ、及び／又はクライアントにより改良されたドライバが挙げられる。

#### 【0091】

アプリケーションレベルプログラムの例として、ONA又はDNAサポートなしのアプリケーション、ONA対応アプリケーション、DNA対応アプリケーション、及びONA/DNA対応アプリケーションが挙げられる。破線の矢印1109Dは、（例えばオペレーティングシステムを媒介として使用することなく）半導体ドライブと通信するONA対応アプリケーション及びONA対応ドライバといったアプリケーションについての該アプリケーションと入出力装置との間の双方向通信（例えばドライバ経由のバイパス又は仮想機能経由のバイパス）を表している。破線の矢印1109Vは、（例えばオペレーティングシステム又はドライバを媒介として使用することなく）半導体ドライブと通信するDNA対応アプリケーション及びDNA対応ドライバといったアプリケーションについての該アプリケーションと入出力装置との間の双方向通信（例えば仮想機能経由のバイパス）を表している。

#### 【0092】

実施形態によっては、不揮発性メモリ1199a-1199nのうちの1つ以上の部分は、ファ-

10

20

30

40

50

ムウェア(例えばファームウェア1106a-1106n)を格納するために使用される。該ファームウェアの格納は、1つ以上のファームウェアイメージ(又はその一部)を含む。ファームウェアイメージは、例えば、(例えば半導体ドライブコントローラ1100a-1100nの中央処理装置により)実行されるファームウェアの1つ以上のイメージを有する。別の例では、ファームウェアイメージは、(例えば、該ファームウェアの実行中に中央処理装置により参照される)定数、パラメータ値、及び不揮発性メモリデバイス情報の1つ以上のイメージを有する。ファームウェアのイメージは、例えば、現在のファームウェアイメージとゼロ以上の(ファームウェア更新に関する)前のファームウェアイメージに対応するものとなる。様々な実施形態において、ファームウェアは、汎用的、標準的、ONA、及び/又はDNA動作モードを提供し、並びに1つ以上のフラッシュ変換レイヤと共に動作する。実施形態によっては、1つ以上のファームウェア動作モードが使用可能となる(例えば、隨意選択的にドライバにより通信され及び/又は提供されるキー又は様々なソフトウェア技術を介して1つ以上のアプリケーションプログラムインターフェイス(例えばAPI)が「アンロック」される)。更なる実施形態では、複数の異なるファームウェアのそれぞれが、複数の異なる動作モードのそれぞれに使用され、及び/又は複数の異なるフラッシュ変換レイヤのそれぞれに使用される。10

#### 【0093】

実施形態によっては、ホスト1102は、マップを実施する別個のハードウェア資源としてマップ1108を含む。別の実施形態では、マップは、マップ1108及び/又はホストメモリ1112Hを介して、及び/又は半導体ドライブコントローラ1100内のマップ1141を介して、及び/又はカードメモリ1112Cを介して、部分的に又は全体的に実施される。マップ1108、ホストメモリ1112H、半導体ドライブコントローラ1108内のマップ1141、及びカードメモリ1112Cの例として、1つ以上の揮発性及び/又は不揮発性メモリ要素(例えば、DRAM、SRAM、及び/又はフラッシュ又はその他の不揮発性メモリデバイスを介して実施されたもの)が挙げられる。ホストメモリの更なる例として、システムメモリ、ホストメインメモリ、ホストキャッシュメモリ、ホストによりアクセス可能なメモリ、及び入出力装置によりアクセス可能なメモリが挙げられる。実施形態及び/又は使用形態(例えば、図11Cの入出力カード1116を有し及び隨意選択的なカードメモリ1112Cを(マップの少なくとも一部のための)格納手段として使用する実施形態)によっては、1つ以上の入出力装置及び/又はホスト1102が、カードメモリ1112C内のマップにアクセスする。20

#### 【0094】

様々な実施形態において、ホスト1102及び/又は半導体ドライブ1101の1つ以上の実例は、論理ブロックアドレス(又はラベル等の別の指定子)を、(入出力装置の不揮発性メモリの1つ以上の部分(例えば不揮発性メモリ1199a-1199nの実例の1つ以上の要素)を宛先とする)不揮発性メモリロケーション(例えばブロック及び/又はページアドレス及び/又は読み出しユニットアドレス)へと変換するために使用することができるマッピング情報の全て又は任意の部分を保存し及び取り出すために、マップ1108、ホストメモリ1112H、カードメモリ1112C、及び/又はマップ1141にアクセスすることが可能である。概念的には、単一のマップが存在することが可能であり、様々な実施形態によれば、該マップの制御及び/又は格納及び/又は使用が、1つ以上のホスト1102により提供され、及び/又は半導体ドライブコントローラ1100a-1100nにより提供される。30

#### 【0095】

スイッチ/ファブリック/中間コントローラ1103が存在しない実施形態では、半導体ドライブ1101a-1101nは、外部インタフェイス1111a-1111nを介してホスト1102に直接接続される。様々な実施形態において、半導体ドライブコントローラ1100a-1100nは、1つ以上の中間レベルの他のコントローラ(例えばRAIDコントローラ又は入出力コントローラ)を介してホスト1102に接続される。実施形態によっては、半導体ドライブ1101a-1101n(又はその変種)はSASドライブ又はSATAドライブに対応し、スイッチ/ファブリック/中間コントローラ1103はエキスパンダに対応し、該エキスパンダが次いでイニシエータに接続され、又は代替的にはスイッチ/ファブリック/中間コントローラ1103はエキスパンダを40

介してイニシエータに間接的に接続されたブリッジに対応する。実施形態によっては、スイッチ／ファブリック／中間コントローラ1103は1つ以上のPCIeスイッチ及び／又はファブリックを含む。

#### 【0096】

様々な実施形態において、コンピューティングホスト（例えば、コンピュータ、ワークステーションコンピュータ、サーバコンピュータ、ストレージサーバ、パーソナルコンピュータ、ラップトップコンピュータ、ノートブックコンピュータ、ネットブックコンピュータ、及び／又はタブレットコンピュータ）としてホスト1102を有する実施形態によっては、該コンピューティングホストは、随意選択的に（例えば、随意選択的な入出力及びストレージデバイス／リソース1117及び随意選択的なローカルエリアネットワーク／ワイドエリアネットワーク（例えばLAN/WAN）1119を介して）1つ以上のローカル及び／又はリモートサーバ（例えば随意選択的なサーバ1118）と通信することが可能である。該通信は、例えば、1つ以上の半導体ドライブ要素のローカル及び／又はリモートアクセス、管理、及び／又は使用を可能にする。実施形態によっては、該通信は、完全に又は部分的にEthernetを介して行われる。実施形態によっては、該通信は、完全に又は部分的にファイバチャネルを介して行われる。ローカルエリアネットワーク／ワイドエリアネットワーク1119は、様々な実施形態において、1つ以上のローカルエリアネットワーク及び／又はワイドエリアネットワーク（例えば、1つのサーバファーム内のネットワーク、複数のサーバファームを接続するネットワーク、メトロエリアネットワーク、及びインターネットのうちの1つ以上のネットワーク）を表すものである。10

#### 【0097】

様々な実施形態において、1つ以上の不揮発性メモリと組み合わされた半導体ドライブコントローラ及び／又はコンピューティングホストの不揮発性メモリコントローラが、不揮発性記憶要素（例えば、ユニバーサルシリアルバス（例えばUSB）記憶要素、ユニバーサルフラッシュストレージ（例えばUFS）記憶要素、コンパクトフラッシュ（例えばCF）記憶要素、マルチメディアカード（例えばMMC）記憶要素、セキュアディジタル（例えばSD）記憶要素、メモリスティック記憶要素、及びxDピクチャカード記憶要素）として実施される。20

#### 【0098】

様々な実施形態において、半導体ドライブコントローラ（又はコンピューティングホストの不揮発性メモリコントローラ）又はその機能の全て若しくは何れかの部分は、該コントローラが接続されることになるホスト（例えば、図11Cのホスト1102）において実施される。様々な実施形態において、半導体ドライブコントローラ（又はコンピューティングホストの不揮発性メモリコントローラ）又はその機能の全て若しくは何れかの部分は、ハードウェア（例えば論理回路）、ソフトウェア、及び／又はファームウェア（例えばドライバソフトウェア又は半導体ドライブ制御ファームウェア）、又はそれらの任意の組み合わせにより実施される。30

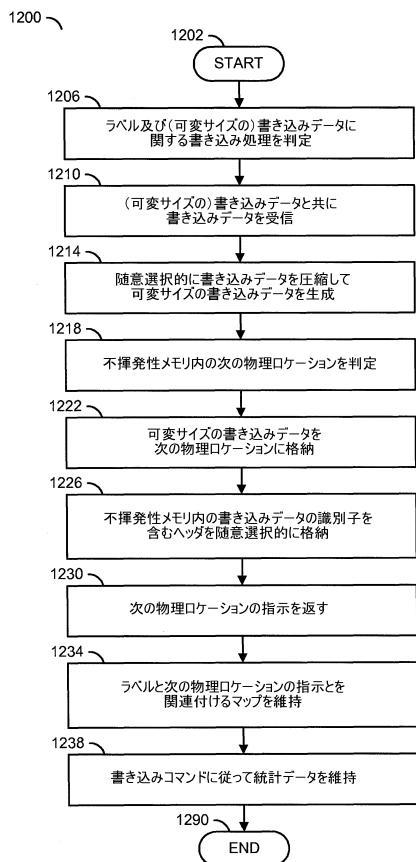

#### 【0099】

図12を参照すると、不揮発性メモリへのデータの書き込み処理のフローチャート1200が示されている。該プロセスは、ステップ1202で開始し、ステップ1206で、複数のラベル（又はその他の一意の識別子（例えばオブジェクト識別子又は論理ロックアドレス））のうちの特定の1つに関連付けされたデータを不揮発性メモリに書き込む（格納する）ことが決定される。該決定は、例えば、アプリケーションプログラム、オペレーティングシステム、ハイパーバイザ、又は他の任意のソフトウェア又はファームウェアモジュールのうちの1つ以上により行うことが可能である。実施形態によっては、書き込みデータは（例えば各書き込み動作毎に変動し得る）可変サイズのものとなる。別の実施形態では、書き込みデータは、複数の固定サイズユニット（例えば複数のSATAセクタ）となる。40

#### 【0100】

ステップ1210で、書き込みコマンド及びそれに関連付けされた（おそらく可変サイズの）書き込みデータが受信される。一例では、アプリケーションが、書き込みコマンド及び50

(例えはデータへのポインタを介して)書き込みデータを、システムコールを使用してドライバへ送信する。別の例では、ホストが、書き込みコマンドを、半導体ドライブコントローラが関連付けされた書き込みデータを取り出すことを可能にする情報と共に、該半導体ドライブコントローラへ送信する。例えは、書き込みコマンドはSATAネイティブコマンドキュー(例えはNCQ)タグを含み、該ネイティブコマンドキューを使用して、関連付けされた書き込みデータがフェッチされる。

#### 【0101】

ステップ1214で、(おそらく可変サイズの)書き込みデータが、随意選択的に及び/又は選択的に圧縮され又はその他の態様でサイズが縮小される。関連付けされた書き込みデータが既に可変サイズである場合であっても、おそらくは圧縮を行って該関連付けされた書き込みデータのサイズを更に縮小することが可能である。実施形態によっては、(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータが、随意選択的及び/又は選択的に暗号化される。10

#### 【0102】

ステップ1218で、データを書き込みための不揮発性メモリの次の未書き込みの物理口ケーションが判定される。一例では、判定された次の未書き込みの物理口ケーションは、前に書き込まれた可変サイズデータにすぐ隣接する(不揮発性メモリ内の空間を無駄にしない)。別の例では、判定された次の未書き込みの物理口ケーションは、前に書き込まれた可変サイズデータと同じ読み出しユニット内で開始する。実施形態によっては、判定された次の未書き込みの物理口ケーションは、書き込みコマンドで指定されたバンドに従うものとなる。20

#### 【0103】

ステップ1222で、(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータが、判定された次の未書き込みの物理口ケーションで不揮発性メモリ内に格納される。実施形態によっては、ハードウェアユニットが、(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータを、不揮発性メモリページのイメージ(例えは、不揮発性メモリページに書き込まれることになるバッファの一部)内にタイル状に配置する。

#### 【0104】

ステップ1226で、書き込みデータの識別子を含むヘッダが、該(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータの少なくとも一部と同じ不揮発性メモリページ内に格納される。例えは、該ヘッダは、図6の場合のように(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータの少なくとも一部と同じ不揮発性メモリページ内に格納され、及び/又は、該ヘッダは、図5の場合のように(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータの少なくとも一部と同じ読み出しユニット内に格納される。様々な実施形態によれば、前記識別子は、以下に示すもののうちの1つ以上となる:書き込みデータの特定のラベルと同じ;書き込みデータの特定のラベルの機能;テーブルを介した書き込みデータの特定のラベルに関連付けされた識別子、不揮発性メモリに格納されている全てのデータ間の一意の識別子;及びそれらの任意の組み合わせ。30

#### 【0105】

様々な実施形態によれば、(おそらく可変サイズの、おそらく圧縮済みの)書き込みデータ及び/又はヘッダの格納は、ステップ1222及び/又はステップ1226で発生し、及び/又は(例えは複数の書き込み処理からの)複数のヘッダ及びデータの不揮発性メモリページが蓄積されるまで延期される。実施形態によっては、不揮発性メモリへの格納処理の一部として誤り訂正符号化が実行される。更に別の実施形態では、誤り訂正符号化は、読み出しユニットが不揮発性メモリに格納される際に、各読み出しユニットのユーザ部分に複数の誤り訂正符号化バイトを付加して該読み出しユニットを形成する。更に別の実施形態では、誤り訂正符号化に先立ってスクランブリングが実行される。40

#### 【0106】

ステップ1230で、判定された次の未書き込みの物理口ケーションの指示が返される。一例では、該判定された次の未書き込みの物理口ケーションの指示は、読み出しユニットア50

ドレス（例えば（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータを格納するために使用した最初の読み出しユニットのアドレス）を含む。この例の場合、実施形態によっては、判定された次の未書き込みの物理口ケーションの指示は、更に、（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータがまたがる読み出しユニットの個数、例えば、（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータの全てであってそれを超えないデータを取り出すために読み出す必要のある読み出しユニットの個数を含む。該個数の読み出しユニットのうちの1つ以上は、随意選択的及び／又は選択的に、他のラベルに関するデータを含むが、該個数の読み出しユニットの各々は、（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータの少なくとも幾つかを含む。別の例では、判定された次の未書き込みの物理口ケーションは、（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータの少なくとも一部を格納するために使用された不揮発性メモリページのアドレス及び／又は不揮発性メモリページ内のオフセットを含む。かかる別の例の場合、実施形態によっては、判定された次の未書き込みの物理口ケーションの指示は、（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータのバイト単位での長さを更に含む。更に、該別の例の場合、更に別の実施形態では、（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータは、2つ以上の不揮発性メモリページにまたがる（例えば、第1の不揮発性メモリページで始まり、1つ以上の後続の不揮発性メモリページへと続く）。例えば、第1の不揮発性メモリページ内のオフセットにおけるユーザデータ及び該オフセットに続くユーザデータの残量が（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータのバイト単位での長さよりも少ない場合には、該（おそらく可変サイズの、おそらく圧縮済みの）書き込みデータは、2つ以上の不揮発性メモリページをまたぐことになる。10

#### 【0107】

ステップ1234で、判定された次の未書き込みの物理口ケーションの指示に特定のラベルを関連づけてマップが維持される。例えば、該マップの維持は、該特定のラベルに関連付けされたデータを後続の読み出し操作により取り出すことを可能にする。20

#### 【0108】

ステップ1238で、書き込みコマンドに従って統計データが維持される。例えば、特定のラベルに関連付けされたデータの書き込み処理は、データが書き込まれていた冗長ブロック内の特定量の空間を使用し、及び／又は該特定のラベルに関連付けされた旧バージョンのデータが格納されていた冗長ブロック内の特定量の空間を随意選択的及び／又は選択的に解放する。該統計データは、各冗長ブロック内の使用空間量（又は別の実施形態では等価的に解放空間量）を追跡する。当該処理はステップ1290で終了する。30

#### 【0109】

実施形態によっては、プロセス1200の少なくとも一部におけるマップの少なくとも一部に対するアクセスを防止するためにロック（例えばセマフォ）が使用される。例えば、実施形態によっては、特定のラベルに関連付けされたマップのエントリが、ステップ1210からステップ1234までロックされて、該エントリの更新中における該エントリへの他のアクセスが阻止される。

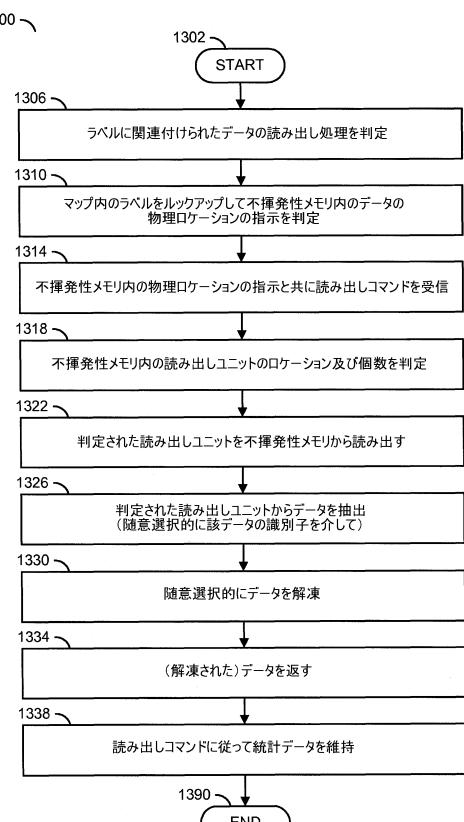

#### 【0110】

図13を参照すると、不揮発性メモリからのデータの読み出し処理のフローチャート1300が示されている。該プロセスは、ステップ1302で開始し、ステップ1306で、不揮発性メモリから複数のラベル（又はオブジェクト識別子又は論理ブロックアドレス等といった他の一意の識別子）のうちの特定の1つに関連付けされたデータを読み出す（取り出す）ことが判定される。例えば、該判定は、アプリケーションプログラム、オペレーティングシステム、ハイパーバイザ、又は他の任意のソフトウェア又はファームウェアモジュールのうちの1つ以上により行うことが可能である。実施形態によっては、該データは（例えば各読み出し動作毎に変動し得る）可変サイズのものとなる。別の実施形態では、該データは、複数の固定サイズユニット（例えば複数のSATAセクタ）となる。

#### 【0111】

50

20

30

40

50

ステップ1310で、特定のラベルがマップ中でロックアップされて、該ラベルに関連付けされた格納バージョンのデータの不揮発性メモリ内における物理口ケーションの指示が判定される。様々な実施形態によれば、該マップのロックアップは、読み出し動作を生じさせるソフトウェアモジュールによって行われ、又は読み出し動作を生じさせるソフトウェアモジュールにより呼び出された別のソフトウェアモジュールによって行われる。例えば、アプリケーションが読み出し動作を生じさせ、ホスト上のドライバレイヤ又は半導体ドライブコントローラ上のファームウェアレイヤがマップのロックアップを行う。

#### 【0112】

ステップ1314で、不揮発性メモリ内の物理口ケーションの指示を有する読み出しコマンドが受信される。一例では、ホスト上のドライバレイヤがマップのロックアップを行い、該ドライバレイヤが読み出しコマンドと不揮発性メモリ中の物理口ケーションの指示とを半導体ドライブコントローラへ送信する。別の例では、半導体ドライブコントローラ内の第1のプロセッサがマップのロックアップを行った後、該第1のプロセッサが、読み出しコマンドと不揮発性メモリ中の物理口ケーションの指示とを、該不揮発性メモリに対するアクセスを制御する該半導体ドライブコントローラ内の第2のプロセッサへ送信する。

#### 【0113】

ステップ1318で、不揮発性メモリ内の物理口ケーションの指示を使用して、特定のラベルに関連付けられた格納バージョンのデータを含む不揮発性メモリ内の読み出しユニットの口ケーションと個数を判定する。一例では、物理口ケーションの指示は、読み出しユニットアドレス（例えば、特定のラベルに関連付けられた格納バージョンのデータを格納するために使用される1つ以上の読み出しユニットのうちの最初の1つのアドレス）を含む。この例の場合、実施形態によっては、物理口ケーションの指示は、1つ以上の読み出しユニットの個数（例えば、特定のラベルに関連付けられた格納バージョンのデータの全てであってそれを超えないデータを取り出すために読み出す必要のある読み出しユニットの個数）を更に含む。（該1つ以上の読み出しユニットのうちの1つ以上は、随意選択的及び／又は選択的に、前記複数のラベルのうちの別のラベルに関連付けされたデータを含むが、該1つ以上の読み出しユニットの各々は、前記特定のラベルに関連付けされた格納バージョンのデータの少なくとも一部を含む。）別の例では、物理口ケーションの指示は、特定のラベルに関連付けされた格納バージョンのデータの少なくとも一部を格納するために使用される不揮発性メモリページのアドレス及び／又は不揮発性メモリページ内のオフセットを含む。該別の例の場合、実施形態によっては、物理口ケーションの指示は更に、特定のラベルに関連付けされた格納バージョンのデータのバイト単位での長さを含む。更に該別の例の場合、更に別の実施形態によっては、特定のラベルに関連付けされた格納バージョンのデータは、2つ以上の不揮発性メモリページをまたぐものとなる（例えば、第1の不揮発性メモリページで始まり、1つ以上の後続の不揮発性メモリページ内へと続く）。例えば、第1の不揮発性メモリページ内のオフセットにおけるユーザデータ及び該オフセットに続くユーザデータの残量が特定のラベルに関連付けされた格納バージョンのデータのバイト単位での長さよりも少ない場合には、該特定のラベルに関連付けされた該格納バージョンのデータは、2つ以上の不揮発性メモリページをまたぐことになる。該別の例の場合には更に、該第1の不揮発性メモリページ内の読み出しユニットの個数及び／又はサイズに従って、及び該特定のラベルに関連付けされた格納バージョンのデータのオフセット及びバイト単位での長さに従って、該第1の不揮発性メモリページ内の1つ以上の読み出しユニットのうちの最初の1つと、該第1の不揮発性メモリページ内の読み出しユニットの個数とが判定される。該特定のラベルに関連付けされた格納バージョンのデータが2つ以上の不揮発性メモリページをまたぐ場合には、1つ以上の後続の不揮発性メモリページに同様の処理を使用して、（該特定のラベルに関連付けされた格納バージョンのデータの少なくとも一部を含む）該後続の不揮発性メモリページ内の更なる読み出しユニットを判定する。

#### 【0114】

ステップ1322で、判定された読み出しユニットが不揮発性メモリから読み出される。実

10

20

30

40

50

施形態によっては、読み出しユニックについて誤り訂正復号化が行われて、不揮発性メモリへの格納時及び／又は不揮発性メモリとの間での転送時に発生するあらゆる誤りが訂正される。更なる実施形態では、誤り訂正復号化に続いてデスクランプリングが行われる。判定された読み出しユニックの誤り訂正符号化のため、不揮発性メモリページから読み出すよう判定されたバイト数は、複数の読み出しユニック内のユーザデータと、その各読み出しユニック内の誤り訂正符号化バイトとの両方を含むものとなる。実施形態によっては、各読み出しユニック内の誤り訂正符号化バイト数は（例えば、不揮発性メモリの消耗に起因して半導体ドライブコントローラの制御下で）動的に変動する。様々な実施形態及び／又は使用形態において、判定された読み出しユニック内のユーザデータの総バイト数は、特定のラベルに関連付けされた格納バージョンのデータのバイト単位での長さを（例えば、該判定された読み出しユニックのうちの少なくとも1つが別のラベルに関連付けされたデータの少なくとも一部を含む場合に）超える。10

#### 【0115】

ステップ1326で、特定のラベルに関連付けされた格納バージョンのデータが、判定された読み出しユニックから抽出される。実施形態によっては、該抽出は、読み出しコマンドと共に提供される識別子に従って行われる。様々な実施形態によれば、該識別子は、以下に示すもののうちの1つ以上となる：データの特定のラベルと同じ；データの特定のラベルの機能；テーブルを介したデータの特定のラベルに関連付けされた識別子、不揮発性メモリに格納されている全てのデータ間の一意の識別子；及びそれらの任意の組み合わせ。一例では、読み出しユニックは（図5に示すように）1つ以上のヘッダを含み、識別子を使用して一致するヘッダを判定し、次いで該ヘッダを使用して、判定された読み出しユニック内の特定のラベルに関連付けされた格納バージョンのデータを特定する。別の例では、物理ロケーションの指示は、判定された読み出しユニック内の特定のラベルに関連付けされた格納バージョンのデータのロケーションを指定する情報からなる。様々な実施形態によれば、特定のラベルに関連付けされた格納バージョンのデータは可変サイズを有するものとなる。例えば、特定のラベルに関連付けされたデータはその格納に先立って圧縮され、及び／又は特定のラベルに関連付けされたデータ自体が可変サイズのものとなる。20

#### 【0116】

ステップ1330で、特定のラベルに関連付けされた格納バージョンのデータは、随意選択的及び／又は選択的に復号化され、及び／又は随意選択的及び／又は選択的に解凍されて、特定のラベルに関連付けされたデータが生成される。30

#### 【0117】

ステップ1334で、特定のラベルに関連付けされたデータが読み出し動作に応じて返される。

#### 【0118】

ステップ1338で、読み出しコマンドに従って統計データが維持される。一例では、読み出しコマンドが、特定の個数の不揮発性メモリブロックにアクセスして、判定された読み出しユニックを取り出し、1つの不揮発性メモリブロックあたりの読み出し妨害イベントの回数をカウントして統計データが維持される。別の例では、読み出しコマンドは、特定の個数の不揮発性メモリブロックにアクセスして、判定された読み出しユニックを取り出し、該判定された読み出しユニックの誤り訂正により、該判定された読み出しユニックの各々におけるそれぞれの複数の誤りが訂正され、各不揮発性メモリブロック内のあらゆるリードユニックにおいて訂正された誤りの最大数についての統計データが維持される。該プロセスはステップ1390で終了する。40

#### 【0119】

典型的には、複数の不揮発性メモリページにまたがらない单一のマッピングユニックのデータを読み出す場合、該マッピングユニックの格納バージョンのデータを取得するためにアクセスすべき不揮発性メモリページ内の読み出しユニックの個数は、該不揮発性メモリページ内の全ての読み出しユニックの個数よりも少ない。更に、該マッピングユニックの格納バージョンのデータは可変サイズを有するものであり、第1の論理ブロックアドレ50

ス（又はラベル）を参照する第1の読み出しコマンドに関してアクセスすべき不揮発性メモリページ内の読み出しユニックの個数は、第2の論理ロックアドレス（又はラベル）を参照する第2の読み出しコマンドに関してアクセスすべき不揮発性メモリページ内の読み出しユニックの個数とは異なり、該第2の論理ロックアドレスは、該第1の論理ロックアドレスとは異なる。実施形態によっては、不揮発性メモリページ内のアクセスすべき読み出しユニックの個数のみが、該不揮発性メモリページから読み出される。すなわち、マッピングユニックの格納バージョンのデータの一部を含む複数の読み出しユニックのうちの一部のみが、該マッピングユニックの格納バージョンのデータにアクセスして該データを取り出すために、該不揮発性メモリから読み出される。

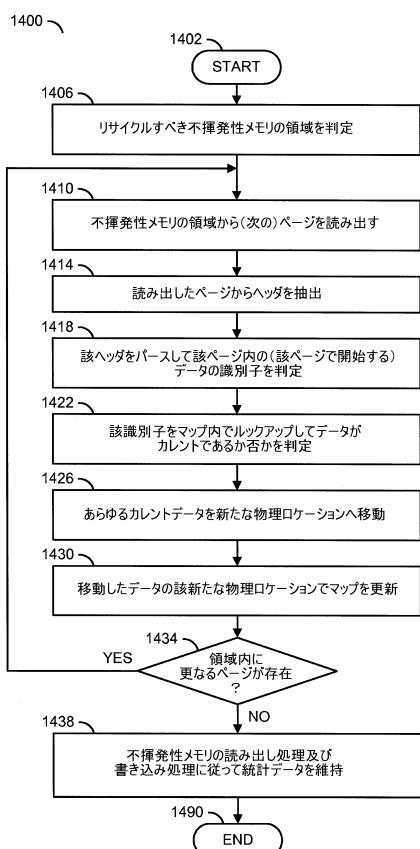

## 【0120】

10

図14を参照すると、不揮発性メモリ内のデータのリサイクル処理のフローチャートが示されている。該プロセスはステップ1402で開始し、ステップ1406で、リサイクルすべき不揮発性メモリの領域について判定が行われる。様々な実施形態及び／又は使用形態によれば、該領域は、以下に示すもののうちの1つ以上となる：冗長ブロック；1つ以上の不揮発性メモリブロック；解放されている空間及び／又は使用されている空間に関する統計データが維持されることになる不揮発性メモリの一部；消耗平滑化に関する統計データが維持されることになる不揮発性メモリの一部；及び上記の任意の組み合わせ。様々な実施形態及び／又は使用形態によれば、リサイクル処理は、以下に示すもののうちの1つ以上のために実行される：不揮発性メモリ内の不要データ収集（解放空間の統合）；不揮発性メモリの消耗平滑化（不揮発性メモリのブロックをそれぞれのプログラム／消去カウント数と相対的に等しく維持するため）；及び不揮発性メモリに関するプロセスエラー及び／又は例外（例えば、プログラム障害、過度の読み出し妨害、及び／又は過度の誤り率）。更なる実施形態によれば、リサイクル処理はグローバルに（例えば、ホストにより複数の半導体ドライブにわたって）実行される。

20

## 【0121】

ステップ1410で、1つ以上の不揮発性メモリページが不揮発性メモリの一領域から読み出される。実施形態によっては、複数の不揮発性メモリページ全体の誤り訂正が行われる。該複数の不揮発性メモリページ内の複数の読み出しユニックの全ての誤り訂正が行われる。別の実施形態では、（図6に示すように）ヘッダを含むと判定された不揮発性メモリページの一部のみ最初に誤り訂正が行われ、該不揮発性メモリページのそれ以外の部分については、リサイクルする必要のあるデータを該不揮発性メモリページが含むと判定された場合（例えばステップ1426）に必要に応じて誤り訂正が行われる。

30

## 【0122】

ステップ1414で、不揮発性メモリページからヘッダが抽出される。一例では、図5に示すような実施形態において、各不揮発性メモリページ内の各読み出しユニックからヘッダが抽出される。別の例では、図6に示すような実施形態において、各不揮発性メモリページの一部（例えば、各不揮発性メモリページ内の最初の1つ以上の読み出しユニック）からヘッダが抽出される。

## 【0123】

40

ステップ1418で、不揮発性メモリページから抽出されたヘッダがパースされて、該不揮発性メモリページに関連付けされたデータ（例えば開始データ）の識別子が判定される。

## 【0124】

ステップ1422で、該識別子がマップ中でルックアップされて、該識別子に関連付けされたデータの不揮発性メモリ内の物理ロケーションのそれぞれの指示が判定される。実施形態によっては、該識別子は、該不揮発性メモリが書き込まれる際に使用されたデータのラベルと同一となる。別の実施形態では、該識別子が他の情報（例えば半導体ドライブ識別子）と組み合わされて、マップ中でルックアップされるラベルが形成される。更に別の実施形態では、該識別子をラベルに関連付けて、及び／又は該識別子に関連付けされたデータの不揮発性メモリ内の物理ロケーションの指示に該識別子を関連付けて、マップが維持される。

50

**【 0 1 2 5 】**

ステップ1426で、依然としてカレントな（リサイクルされている不揮発性メモリページ内にある）識別子に関連付けされているあらゆるデータが、不揮発性メモリ内の新たな物理口케ーションに書き込まれる。例えば、識別子に関連付けられているデータの不揮発性メモリ内の物理口ケーションのそれぞれの指示がそれぞれの読み出しユニットアドレスへと変換され、該それぞれの読み出しユニットアドレスがリサイクル中の不揮発性メモリページ内に存在する場合には、該リサイクル中の不揮発性メモリページは、該識別子に関連付けられている最新バージョンのデータを含んでいる。様々な実施形態において、識別子に関連付けされている依然としてカレントな（最新の）データの不揮発性メモリ内の新たな物理口ケーションへの書き込みは、プロセス1200のステップ1218-1230と同様に実行される。様々な実施形態において、依然としてカレントなデータが圧縮され及び／又は暗号化されている場合には、該依然としてカレントなデータは、該圧縮され及び／又は暗号化された形態で「そのまま」書き換えられる。実施形態によっては、該依然としてカレントなデータは、リサイクル中の不揮発性メモリページから半導体ドライブコントローラ内の新たな不揮発性メモリページへと移動される（及び該依然としてカレントなデータをリサイクルするために該依然としてカレントなデータはホストへは送信されない）。別の実施形態では、リサイクル処理は、該依然としてカレントなデータをホストへ送信して該データをプロセス1200と同様に書き換えることからなる。更なる実施形態では、リサイクル処理は、複数の半導体ドライブにわたってグローバルに行われ、以前に該複数の半導体ドライブのうちの1つ以上に格納された依然としてカレントなデータは、該複数の半導体ドライブのうちの別の1つに対するリサイクルのために書き換えられる。10

**【 0 1 2 6 】**

ステップ1430で、リサイクルされたあらゆるデータの新たな物理口ケーションの指示を反映するようにマップが更新される。

**【 0 1 2 7 】**

ステップ1434で、更なる不揮発性メモリページが前記領域内で更に処理されるべきか否かが判定される。更なる不揮発性メモリページが前記領域内で更に処理されるべきと判定された場合には、該プロセスはステップ1410に戻って更なる不揮発性メモリページのリサイクル処理を続行する。20

**【 0 1 2 8 】**

ステップ1438で、リサイクルプロセス中の不揮発性メモリの読み出し処理及び書き込み処理に従って統計データが維持される。一例では、不揮発性メモリの読み出し処理は、特定の個数の不揮発性メモリブロックにアクセスして不揮発性メモリページを取り出し、一不揮発性メモリブロックあたりの読み出し妨害イベントの回数をカウントして統計データが維持される。別の例では、不揮発性メモリの読み出し処理は、特定の個数の不揮発性メモリブロックにアクセスして不揮発性メモリページを取り出し、該不揮発性メモリページの誤り訂正により、誤り訂正復号化された不揮発性メモリページの読み出しユニットの各々におけるそれぞれの複数の誤りを訂正し、該不揮発性メモリブロックの各々におけるあらゆる読み出しユニット内で訂正された最大誤り数に関する統計データが維持される。更に別の例では、不揮発性メモリに書き込むことによるデータのリサイクル処理は、リサイクルされるデータが書き込まれた冗長ブロック内の特定量の空間を使用し、及びリサイクルされる該冗長ブロック内の特定量の空間を随意選択的及び／又は選択的に解放する。統計データは、各冗長ブロック内の使用空間の量（又は実施形態によっては等価的に解放空間の量）を追跡する。実施形態によっては、リサイクルされる領域内の使用空間の量がゼロになった際に、該領域内の依然としてカレントなデータ（まだ上書きされていないもの）はそれ以上リサイクルされなくなり、プロセス1400は、リサイクルされている領域内の全ての不揮発性メモリページの読み出しを行う前に完了することが可能となる。該プロセスはステップ1490で終了する。30

**【 0 1 2 9 】**

実施形態によっては、プロセス1400の少なくとも一部においてマップの少なくとも一部

50

に対するアクセスを阻止するためにロック（例えばセマフォ）が使用される。例えば、実施形態によつては、カレントデータを有する複数の識別子のうちの1つに関連付けされたマップのエントリは、その更新時における該エントリへの他のアクセスを阻止するためにステップ1422-1430においてロックされる。

#### 【0130】

様々な実施形態によれば、ホストが、リサイクルされるべき不揮発性メモリの領域を選択し；半導体ドライブコントローラが、リサイクルされるべき不揮発性メモリの領域を選択し；ホストが、第1の理由のためにリサイクルされるべき不揮発性メモリの領域を選択し；及び半導体ドライブコントローラが、第2の異なる理由のためにリサイクルされるべき不揮発性メモリの領域を選択する。一例では、リサイクルされるべき不揮発性メモリの領域の全ての選択がホスト上で行われる。別の例では、ホストが、不要データ収集に関してリサイクルされるべき不揮発性メモリの領域を選択し、半導体ドライブコントローラが、消耗平滑化に関してリサイクルされるべき不揮発性メモリの領域を選択する。更に別の例では、ホストが、不要データ収集及び消耗平滑化に関してリサイクルされるべき不揮発性メモリの領域を選択し、半導体ドライブコントローラが、例外的な条件及び／又は誤り（例えば、プログラム障害、過度の誤り訂正符号化誤り、又は読み出し妨害イベント）に関してリサイクルされるべき不揮発性メモリの領域を選択する。更なる実施形態では、半導体ドライブコントローラは、不揮発性メモリの1つ以上の統計データ（例えば、プログラム／消去カウント及び／又は使用空間の統計データ）をホストに対して通信することが可能である。例えば、統計データは、半導体ドライブコントローラの論理ブロックアドレス空間の予約済み部分を介して、又は統計データの読み出し及び／又は書き込みを行うための特殊コマンドにより、ログ（例えば、SMARTログ）として通信される。実施形態及び／又は使用形態によつては、ホストに対する統計データの通信は、該ホストがリサイクルされるべき不揮発性メモリの領域を選択することを可能にする一方、半導体ドライブコントローラがホストを統計データの維持から解放することが可能となる。

#### 【0131】

実施形態によつては、半導体ドライブコントローラは、ホストとは無関係に不揮発性メモリの少なくとも一部をリサイクルすることが可能であり、及び更新された物理口케ーションをホストへ通信することが可能である。例えば、例外的な条件及び／又は誤り（例えば、プログラム障害、過度の誤り訂正符号化誤り、又は読み出し妨害イベント）に応じて、半導体ドライブコントローラは、リサイクルされなければならない不揮発性メモリの領域を判定する。半導体ドライブコントローラは、不揮発性メモリの該領域内のヘッダを読み出し、該不揮発性メモリ内の該領域内のあらゆる依然としてカレントなデータを、該不揮発性メモリの異なる部分におけるそれぞれの新たな物理口ケーションに再配置する。様々な実施形態によれば、1つ以上の実施形態において、半導体ドライブが、マップを維持し、及び依然としてカレントなデータのそれぞれの新たな物理口ケーションを反映するようには該マップを更新することが可能であり；半導体ドライブコントローラが、該半導体ドライブコントローラにより再配置されたデータの別個の部分的なマップを維持し、該別個の部分的なマップが、不揮発性メモリの領域内の依然としてカレントなデータの物理口ケーションの指示をそれぞれの新たな物理口ケーションに関連付けるものであり；該半導体ドライブコントローラが、それぞれの新たな物理口ケーションを前記ヘッダからの情報（例えば、依然としてカレントなデータのそれぞれの識別子）と共にホストへ通信し、及び該ホストがマップを更新し、及び上記の任意の組み合わせを実施することが可能である。有利なことに、依然としてカレントなデータは、不揮発性メモリの領域が消去されるまで、該不揮発性メモリの領域とそれとの新たな物理口ケーションとの両方でアクセスすることが可能である。更なる実施形態では、それぞれの新たな物理口ケーションでマップが更新される後まで、不揮発性メモリの領域は消去されない。例えば、半導体ドライブコントローラは、マップが更新されたことがホストにより通知され、その場合にのみ、半導体ドライブコントローラは、不揮発性メモリの領域を消去することが可能となる。

#### 【0132】

10

20

30

40

50

様々な実施形態において、ホストは、（例えば、読み出すべき不揮発性メモリページの個数、又はホストへ送信すべき抽出されるヘッダの個数を要求することにより）リサイクル処理（ステップ1410）のための不揮発性メモリからの不揮発性メモリページの読み出しを制御する。様々な実施形態によれば、（例えば、抽出されたヘッダの前処理及び／又は再フォーマット処理及び／又はフィルタ処理を実行することにより）ホストが少なくとも何らかのヘッダパース処理（ステップ1418）を実行し及び／又は半導体ドライブコントローラが少なくとも何らかのヘッダパース処理を実行する。更なる実施形態では、ホストが、マップのルックアップ（ステップ1422）を実行して、何れかのデータを書き換える必要があるか否かを判定する。該書き換え（ステップ1426）は、（例えば、ホストが全ての依然としてカレントなデータのための「書き換え」コマンドを送信することにより）ホストの制御下で半導体ドライブコントローラにより実行される。書き換えコマンドは、書き込みコマンドと類似しているが、書き込みデータを有するものではなく、書き換えコマンドは、読み出しコマンドの場合のように不揮発性メモリ内の物理ロケーション（データがリサイクルされているロケーション）の指示を含む。書き込みコマンドと同様に、書き換えコマンドは、書き換えデータの新たな物理ロケーションの指示を返し、ホストは、ステップ1430を実行してマップを更新させる。ホストがプロセス1400の大部分を実行する関連する実施形態では、書き換えコマンドは、依然としてカレントなデータのバッファロケーションを半導体ドライブコントローラ内に含む。10

#### 【0133】

実施形態によっては、非標準的なコマンド及び／又はベンダ独自のコマンドが、ホストと半導体ドライブコントローラとの間の通信プロトコルの一部として使用される。様々な実施形態によれば、該通信プロトコルは、以下に示すもののうちの1つ以上となる：SATA、小型コンピュータ用周辺機器インタフェイス（例えばSCSI）、SAS、周辺機器高速相互接続（例えばPCIe）、NVM Express（例えば不揮発性メモリ）、SCSI Over PCIe（例えばSOP）、Mobile Express、USB、埋込型マルチメディアカード（eMMC）、Ethernet、Fibre Channel、又は2つの電子装置間の通信に適した他の任意のプロトコル。一例では、ホストと半導体ドライブコントローラとの間での物理ロケーションの指示の通信は、ベンダ独自のコマンド（例えば、標準的な読み出しコマンド及び書き込みコマンドのベンダ独自バージョン）を使用する。別の例では、リサイクルのために抽出されたヘッダがログページ（例えばSMARTログページ）内で半導体ドライブコントローラからホストへと通信される。20

更に別の例では、抽出されたヘッダは、読み出しデータと同様に扱われるが、ベンダ独自の「抽出ヘッダ読み出し」コマンドにより読み出される。30

#### 【0134】

様々な実施形態によれば、プロセス1200及び／又はプロセス1400のあらゆるステップは、半導体ドライブコントローラに接続されたホスト、ホストに接続された半導体ドライブコントローラ、及びそれらの任意の組み合わせのうちの1つ以上により実行される。一例では、マップルックアップ及びマップ維持がホスト上で実行される。別の例では、読み出しユニークの個数の判定が、ホスト及び半導体ドライブコントローラの何れか一方又は両方で実行される。更に別の例では、不揮発性メモリページ内への書き込みデータのタイル状配置（例えばステップ1222）が、半導体ドライブコントローラ上で実行される。一例では、半導体ドライブコントローラのバッファ内での書き込みデータが、ホストの制御下で、不揮発性メモリページイメージ内にタイル状に配置される。別の例では、読み出しユニークからのデータの抽出（例えばステップ1326）が半導体ドライブコントローラ上で実行される。更に別の例では、圧縮処理（例えばステップ1214）及び解凍処理（例えばステップ1330）が半導体ドライブコントローラ上で実行される。一例では、統計データが半導体ドライブコントローラ上で維持される（例えばステップ1238又はステップ1338）。別の例では、リサイクルすべき不揮発性メモリの領域の判定（例えばステップ1406）がホスト上で実行される。更に別の例では、リサイクルされるべき依然としてカレントなデータの旧ロケーションから新ロケーションへの移動（例えばステップ1426）が半導体ドライブコントローラ上で実行される。4050

## 【0135】

実施形態によっては、ホスト及び／又は半導体ドライブコントローラは、不揮発性メモリの複数の領域の各々を特定の特性及び／又は特徴に関連付けるテーブルを維持する。一例では、該テーブルは、不揮発性メモリの複数の領域の各々を複数の符号化率（誤り訂正符号強度）のうちの特定の1つに関連付けし、これにより、該各領域に格納されるデータの量を該各領域の「健全性（health）」に従って変更することが可能となる。健全性の一層高い領域は、一層高い（一層弱い）符号化率を使用して一層多くのユーザデータを格納することが可能となり、健全性の一層低い領域は、一層低い（一層強力な）符号化率を使用して一層少ないユーザデータを格納するものとなる（が一層多くの誤りを訂正することが可能となる）。別の例では、該テーブルは、欠陥があり又は機能せず及び使用すべきでない1つ以上の領域を示すものとなる。例えば、NANDフラッシュの場合、該NANDフラッシュが新品であっても、該NANDフラッシュの複数のブロックのうちの幾つかは欠陥を有しており、他のブロックは該NANDフラッシュの寿命中におそらく機能不全となる。該テーブルは、複数のNANDフラッシュデバイスにわたってデータをシーケンシャルに書き込む際にスキップしなければならないブロックを示す。

10

## 【0136】

実施形態によっては、該マップの一層高レベルの部分がホスト上で維持され、該マップの一層低レベルの部分が半導体ドライブコントローラ上で維持される。該マップの一層高レベルの部分は、ラベル（又は論理ブロックアドレス）を不揮発性メモリ中の複数の物理ロケーションのそれぞれの指示に関連付ける。次いで、該不揮発性メモリ中の物理ロケーションの指示は、半導体ドライブコントローラが該マップの低レベルの部分を使用して読み出し及び／又は書き込みが行われるべき不揮発性メモリの物理ロケーションを判定することにより、更に変換される。ホストの観点からすれば、書き込み時に半導体ドライブコントローラが複数の物理ロケーションの指示のうちの1つを特定のデータオブジェクトに割り当て、及び該半導体ドライブコントローラが該物理ロケーションの指示が戻された際に該指示に対応する特定のデータオブジェクトを返すことが可能となるという点で、物理ロケーションの指示は不透明ハンドル（opaque handle）として働くものである。換言すれば、不揮発性メモリ内のユーザデータ編成の詳細に関する知識はホストから隠される。有利なことに、半導体ドライブコントローラは、不揮発性メモリの少なくとも一部の管理（例えば、符号化率の選択、又はホストにより使用されていない不揮発性メモリの不良ブロックその他の部分の判定）を実行することが可能である。

20

## 【0137】

一例では、不揮発性メモリの複数のブロックのうちの特定の1つが最初に使用された際に、半導体ドライブコントローラは、該特定のブロックの複数のページの各々を、複数の（例えば8つの）個々の読み出しユニットへと分割し、及び該特定のブロックの誤り訂正に複数の符号化率のうちの特定の1つを使用する。その後、該特定のブロックが一層消耗した後に該特定のブロックが再使用される際に、半導体ドライブコントローラは、該特定のブロックの複数のページの各々を複数の（例えば7つの）個々の読み出しユニットへと分割し、及び該特定のブロックの誤り訂正に複数の符号化率のうち一層強度の高いものを使用する。何れの場合も、ホストが該特定のブロックに格納されるデータを書き込む場合、該特定のブロック内の物理ロケーションの指示は、該特定のブロックのページが分割されてなる読み出しユニットの個数とは無関係のものである。

30

## 【0138】

別の例では、可変サイズデータが不揮発性メモリの複数ブロックにまたがる場合、ホストにより使用される物理ロケーションの指示は、該不揮発性メモリの何れかの特定のブロックが使用中であるか不良としてマークされて使用されていないかに関する知識とは無関係なものである。該別の例において、不揮発性メモリの複数のダイのうちの特定の1つのブロック7が不良であって使用されていないものと仮定する。該ダイの1つ前のブロック6内のデータが後続のブロックにまたがる場合、半導体ドライブコントローラは該特定のダイのブロック6を使用する。該前のダイのブロック7内のデータが後続のブロックにま

40

50

たがる場合、半導体ドライブコントローラは、該特定のダイのブロック7をスキップし、次のダイのブロック7内のデータについて処理を続行する。ホストは、どのブロックへとデータがまたがっているかに関する知識を有さない。

#### 【0139】

様々な実施形態によれば、ホスト、半導体ドライブコントローラ、及びそれらの任意の組み合わせのうちの1つ以上により、バックグラウンド処理（例えば読み出しスクラップ及びリサイクル処理）が実行される。

#### 【0140】

様々な実施形態によれば、ホストの処理及び／又は半導体ドライブコントローラのプロセッサの処理は、1つ以上の中央処理装置、1つ以上のハードウェア装置、及び／又はそれらの任意の組み合わせのうちの1つ以上により実行される。10

#### 【0141】

様々な実施形態によれば、ホスト及び／又は半導体ドライブコントローラは、以下に示すもののうちの1つ以上を使用することが可能である：従来のフラッシュ変換レイヤ；可変サイズフラッシュ変換レイヤ；シーケンシャル読み出しが最適化された可変サイズフラッシュ変換レイヤ；他のあらゆるタイプのフラッシュ変換レイヤ；不揮発性メモリに対する直接アクセス；不揮発性メモリの異なる物理的な部分での上記の任意の組み合わせ；半導体ドライブコントローラの論理アドレス空間の異なる論理的な部分での上記の任意の組み合わせ；不揮発性メモリに対する生の（raw）物理的アクセス；及び上記の任意の組み合わせ。20

#### 【0142】

様々な実施形態によれば、ホスト書き込みデータは、随意選択的及び／又は選択的に不揮発性メモリへの書き込みに先立って暗号化され、及び随意選択的及び／又は選択的に該不揮発性メモリから読み出しされた後に復号化される。更なる実施形態では、暗号化は、随意選択的及び／又は選択的なホスト書き込みデータの圧縮に続いて行われ、復号化は、ホストへ返すべく読み出されたデータの随意選択的及び／又は選択的なデータの解凍に先立って行われる。

#### 【0143】

本書では幾つかの例示的な実施形態は半導体ドライブ及び半導体ドライブコントローラを使用したが、本書で開示した技術は一般に、他の入出力装置及び／又はデータ記憶装置（例えばハードディスクドライブ）に適用することが可能である。かかる入出力装置で使用される不揮発性メモリは、様々な実施形態では、「半導体」不揮発性メモリ以外にも、ハードディスクドライブ（例えば、瓦磁気記録方式を用いたハードディスクドライブ）の磁気プラッタ等とすることが可能である。30

#### 【0144】

実施形態によっては、マルチノード記憶装置又はその一部（例えば、ハードディスクドライブ又は半導体ディスク又はプロセッサ（例えばCPU）と協働することが可能な入出力装置の不揮発性メモリコントローラ、入出力コントローラ（例えばRAIDオンチップダイ）、及びプロセッサの一部、マイクロプロセッサ、システム・オン・チップ、特定用途集積回路、ハードウェアアクセラレータ、又は上述の処理の全部又は一部を提供するその他の回路）により実行される処理の全部又は一部の様々な組み合わせは、コンピュータシステムによる処理と互換性を有する仕様によって指定される。該仕様は、様々な記述（例えば、ハードウェア記述言語、回路記述、ネットリスト記述、マスク記述、又はレイアウト記述）に従うものである。例示的な記述として、Verilog、VHDL（very high speed integrated circuit hardware description language）、SPICE（simulation program with integrated circuit emphasis）、SPICEの変種（例えば、PSpice）、IBIS（input/output buffer information specification）、LEF（library exchange format）、DEF（design exchange format）、GDS-II（graphic database system-II）、OASIS（open artwork system interchange standard）、又はその他の記述が挙げられる（が、これらには限定されない）。様々な実施形態において、前記処理は、解釈、コンパイル処理、シミュレーション、4050

並びに 1 つ以上の集積回路上に含めるのに適したロジック及び / 又は回路の生成、検証、又は指定を行うための合成の任意の組み合わせを含む。各集積回路は、様々な実施形態によれば、様々な技術に従って設計可能であり及び / 又は製造可能である。該技術は、プログラマブル技術（例えばフィールド又はマスクプログラマブルゲートアレイ集積回路）、セミカスタム技術（例えば完全に又は部分的にセルベースの集積回路）、及びフルカスタム技術（例えば実質的に専用設計の集積回路）、それらの任意の組み合わせ、又は集積回路の設計及び / 又は製造に適合する他のあらゆる技術を含む。

#### 【 0 1 4 5 】

図 1 ないし図 14 の図面により実行される機能は、従来の汎用プロセッサ、ディジタルコンピュータ、マイクロプロセッサ、マイクロコントローラ、RISC ( reduced instruction set computer ) プロセッサ、CISC ( complex instruction set computer ) プロセッサ、SIMD ( single instruction multiple data ) プロセッサ、シグナルプロセッサ、中央処理装置 ( CPU ) 、算術論理ユニット ( ALU ) 、ビデオディジタルシグナルプロセッサ ( VDSP ) 、及び / 又は当業者には自明であるようにそれらと同様の（前記仕様の教示に従ってプログラミングされた）計算機のうちの 1 つ以上を使用して実施することが可能である。更に、当業者には自明であるように、適當なソフトウェア、ファームウェア、符号化、ルーチン、命令コード、マイクロコード、及び / 又はプログラムモジュールは、本開示の教示に基づいて熟練したプログラマにより容易に用意することが可能なものである。ソフトウェアは、一般に、マシンによる実施形態の 1 つ以上のプロセッサにより 1 つ以上の媒体から実行される。

10

#### 【 0 1 4 6 】

本発明はまた、ASIC、FPGA ( field programmable gate array ) 、PLD ( programmable logic device ) 、CPLD ( complex programmable logic device ) 、SOG ( sea of gate ) 、RF IC ( radio frequency integrated circuit ) 、ASSP ( application specific standard product ) 、1 つ以上のモノリシック集積回路、フリップチップモジュール及び / 又はマルチチップモジュールとして構成され又は（本書で説明するように）従来の複数の回路要素の適當なネットワークを相互接続することにより構成された 1 つ以上のチップ又はダイを用意することにより実施することが可能であり、その修正は当業者には自明であろう。

20

#### 【 0 1 4 7 】

したがって、本発明はコンピュータ製品を含むことが可能であり、該コンピュータ製品は、本発明に従って 1 つ以上のプロセス又は方法を実行するようマシンをプログラミングするために使用することが可能な複数の命令を含む 1 つ以上の記憶媒体及び / 又は 1 つ以上の送信媒体とすることが可能なものである。該コンピュータ製品内に格納された命令の前記マシンによる実行並びにその周辺回路の動作は、入力データを、記憶媒体上の 1 つ以上のファイル及び / 又は物理オブジェクト又は物体を表す 1 つ以上の出力信号（例えば、音響的及び / 又は視覚的な表現）へと変換することが可能なものとなる。該記憶媒体は、フロッピーディスク、ハードディスクドライブ、磁気ディスク、光ディスク、CD-ROM、DVD、及び光磁気ディスクを含む、あらゆるタイプのディスク、及び、ROM ( read-only memory ) 、RAM ( random access memory ) 、EPROM ( erasable programmable ROM ) 、EEPROM ( electrically erasable programmable ROM ) 、UVPROM ( ultra-violet erasable programmable ROM ) 、フラッシュメモリ、磁気カード、及び光カードといった回路、及び / 又は電子的な命令を格納するのに適したあらゆるタイプの媒体を含むことが可能である（但し、それらには限定されない）。

30

#### 【 0 1 4 8 】

本発明の要素は、装置、ユニット、コンポーネント、システム、マシン、及び / 又は機器のうちの 1 つ以上又はその全てを構成することが可能である。該装置は、サーバ、ワークステーション、ストレージアレイコントローラ、ストレージシステム、パーソナルコンピュータ、ラップトップコンピュータ、ノートブックコンピュータ、パームコンピュータ、携帯情報端末 ( PDA ) 、携帯型電子装置、バッテリー駆動式装置、セットトップボックス、エンコーダ、デコーダ、トランスコーダ、コンプレッサ、デコンプレッサ、プリプロ

40

50

セッサ、ポストプロセッサ、トランスマッタ、レシーバ、トランシーバ、暗号化回路、携帯電話、ディジタルカメラ、ポジショニング及び／又はナビゲーションシステム、医療機器、ヘッドアップディスプレイ、無線装置、録音装置、オーディオ記憶装置、及び／又はオーディオ再生装置、録画装置、ビデオ記憶装置、及び／又はビデオ再生装置、ゲームプラットフォーム、周辺機器、及び／又はマルチチップモジュールを含むことが可能である（但し、それらには限定されない）。

#### 【0149】

本発明の要素は、特定の用途の基準を満たすように他のタイプの装置で実施することが可能である、ということが当業者には理解されよう。

#### 【0150】

用語「可能である」及び「一般に」は、「～である」及び動詞と共に本書で用いる場合、その記述が例示であって、本開示で提示した特定の実例並びに本開示に基づいて導出し得る代替例の両方を包含する広範なものであることを伝えることを意図したものである。用語「可能である」及び「一般に」は、対応する要素を省略することの望ましさ又は可能性を必ずしも示唆するものではないと解釈されるべきである。

#### 【0151】

本発明の特定の実施形態について説明してきたが、本発明の思想から逸脱することなくその形態及び細部について様々な変更を加えることが可能である、ということが当業者には理解されよう。

10

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11B】

【図 1 1 A】

【図 1-1-C】

【図12】

【図13】

【図14】

---

フロントページの続き

(31)優先権主張番号 61/893,383

(32)優先日 平成25年10月21日(2013.10.21)

(33)優先権主張国 米国(US)

(31)優先権主張番号 14/060,799

(32)優先日 平成25年10月23日(2013.10.23)

(33)優先権主張国 米国(US)

(72)発明者 アール・ティー・コーエン

アメリカ合衆国カリフォルニア州95131,サンノゼ,リダー・パーク・ドライブ・1320

(72)発明者 シュミット・プリ

アメリカ合衆国カリフォルニア州95131,サンノゼ,リダー・パーク・ドライブ・1320

審査官 田中 啓介

(56)参考文献 國際公開第2012/099937 (WO, A1)

國際公開第2009/110377 (WO, A1)

特開2001-101071 (JP, A)

特開2000-076117 (JP, A)

特開平11-065921 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 3 / 06 - 3 / 08

G 06 F 12 / 00 - 12 / 06

G 06 F 13 / 10 - 13 / 18、17 / 30