(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2018-503919

(P2018-503919A)

(43) 公表日 平成30年2月8日(2018.2.8)

(51) Int.Cl.

G 0 6 T 3/40 (2006.01)

F 1

G O 6 T 3/40

7 0 5

テーマコード(参考)

5 B 0 5 7

審査請求 未請求 予備審査請求 有 (全 34 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2017-539400 (P2017-539400) |

| (86) (22) 出願日 | 平成28年1月14日 (2016.1.14)       |

| (85) 翻訳文提出日   | 平成29年9月20日 (2017.9.20)       |

| (86) 國際出願番号   | PCT/US2016/013468            |

| (87) 國際公開番号   | W02016/122896                |

| (87) 國際公開日    | 平成28年8月4日 (2016.8.4)         |

| (31) 優先権主張番号  | 62/108,986                   |

| (32) 優先日      | 平成27年1月28日 (2015.1.28)       |

| (33) 優先権主張国   | 米国(US)                       |

| (31) 優先権主張番号  | 14/836,449                   |

| (32) 優先日      | 平成27年8月26日 (2015.8.26)       |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 595020643<br>クアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人 | 100108855<br>弁理士 蔡田 昌俊                                                                                        |

| (74) 代理人 | 100109830<br>弁理士 福原 淑弘                                                                                        |

| (74) 代理人 | 100158805<br>弁理士 井関 守三                                                                                        |

| (74) 代理人 | 100112807<br>弁理士 岡田 貴志                                                                                        |

最終頁に続く

(54) 【発明の名称】ペイヤーマッピングを備えたグラフィックス処理ユニット

## (57) 【要約】

グラフィックス処理のための方法および製造物であつて、その中で、第1のラインの生ペイヤーデータおよび第2のラインの生ペイヤーデータが受け取られる。第1のラインの生ペイヤーデータおよび第2のラインの生ペイヤーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列は、複数のテクセルを提供するために、別個の対応するテクセルとしてマッピングされる。少なくとも1つの動作が、複数のテクセルのうちの少なくとも1つに対して実行される。

FIG. 9

**【特許請求の範囲】****【請求項 1】**

グラフィックス処理のための方法であって、

第1のラインの生ベイヤーデータおよび第2のラインの生ベイヤーデータを受け取ることと、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイヤーデータおよび前記第2のラインの生ベイヤーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングすることと、

前記複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行することと

を備える方法。

**【請求項 2】**

前記少なくとも1つの動作は、ベイアービニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも1つを含む、請求項1に記載の方法。

**【請求項 3】**

前記複数のテクセルの各テクセルは、RGBAフォーマットである、請求項1に記載の方法。

**【請求項 4】**

前記複数のテクセルのうちの少なくとも1つに対して前記少なくとも1つの動作を実行した後、画像信号プロセッサに前記複数のテクセルを送信することをさらに備える、請求項1に記載の方法。

**【請求項 5】**

前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイヤーデータおよび前記第2のラインの生ベイヤーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列を前記マッピングすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、請求項1に記載の方法。

**【請求項 6】**

前記生ベイヤーデータがMIPIMフォーマットであるかどうかについての決定を行うことと、

前記生ベイヤーデータがMIPIMフォーマットであると決定された場合、前記生ベイヤーデータをアンパックするために、グラフィックス処理ユニットのテクスチャパイプラインにおけるハードウェアを用いることと

をさらに備える、請求項1に記載の方法。

**【請求項 7】**

前記テクスチャパイプラインにおける前記ハードウェアによって実行される前記生ベイヤーデータを前記アンパックすることは、対応するテクスチャデータタイプを有する、請求項6に記載の方法。

**【請求項 8】**

前記テクスチャパイプラインにおける前記ハードウェアによって実行される前記生ベイヤーデータを前記アンパックすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、請求項6に記載の方法。

**【請求項 9】**

グラフィックス処理のためのデバイスであって、

キャッシュと、

前記キャッシュから第1のラインの生ベイヤーデータ、および前記キャッシュから第2のラインの生ベイヤーデータを受け取り、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイヤーデータおよび前記第2のラインの生ベイヤーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングし、

前記複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行す

10

20

30

40

50

る

ように構成されたテクスチャパイプラインと

を備えるデバイス。

【請求項 10】

前記テクスチャパイプラインは、前記少なくとも 1 つの動作が、ベイヤーピニング動作

、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも 1 つを含む

ように構成される、請求項 9 に記載のデバイス。

【請求項 11】

前記テクスチャパイプラインは、前記複数のテクセルの各テクセルが、RGBAFORMATT

であるように構成される、請求項 9 に記載のデバイス。 10

【請求項 12】

画像信号プロセッサをさらに備え、ここにおいて、前記画像信号プロセッサは、テクス

チャプロセッサが前記複数のテクセルのうちの少なくとも 1 つに対して前記少なくとも 1

つの動作を実行した後に、前記複数のテクセルを受け取るように構成される、請求項 9 に

記載のデバイス。

【請求項 13】

前記テクスチャパイプラインは、アプリケーションプログラムインタフェースを介して

アクセス可能である手法で、前記複数のテクセルを提供するために、別個の対応するテク

セルとして、前記第 1 のラインの生ベイヤーデータおよび前記第 2 のラインの生ベイヤー

データの複数の重複してない  $2 \times 2$  配列の各  $2 \times 2$  配列をマッピングするように構成され

る、請求項 9 に記載のデバイス。 20

【請求項 14】

前記テクスチャパイプラインは、

前記生ベイヤーデータが MIPIMFORMAT であるかどうかについての決定を行い、

前記生ベイヤーデータが MIPIMFORMAT であると決定された場合、前記生ベイヤ

ーデータをアンパックする

ようにさらに構成される、請求項 9 に記載のデバイス。

【請求項 15】

前記テクスチャパイプラインは、前記アンパックすることが、対応するテクスチャデー

タタイプを有するように、前記生ベイヤーデータをアンパックすることが達成され

るように構成される、請求項 14 に記載のデバイス。 30

【請求項 16】

前記テクスチャパイプラインは、前記生ベイヤーデータをアンパックすることがアプ

リケーションプログラムインタフェースを介してアクセス可能であるように構成される、請

求項 14 に記載のデバイス。

【請求項 17】

前記キャッシュは、レベル 2 キャッシュであり、前記テクスチャパイプラインは、

ローカルキャッシュと、

前記レベル 2 キャッシュから前記第 1 のラインの生ベイヤーデータ、および前記レベル

2 キャッシュから前記第 2 のラインの生ベイヤーデータを受け取り、前記複数のテクセル

を提供するために、別個の対応するテクセルとして、前記第 1 のラインの生ベイヤーデー

タおよび前記第 2 のラインの生ベイヤーデータの前記複数の重複してない  $2 \times 2$  配列の各

$2 \times 2$  配列をマッピングし、前記ローカルキャッシュに前記複数のテクセルを送信するよ

うに構成されたアンパッキング回路と

を含む、請求項 9 に記載のデバイス。 40

【請求項 18】

前記アンパッキング回路は、

前記生ベイヤーデータが MIPIMFORMAT であるかどうかについての決定を行い、

前記生ベイヤーデータが MIPIMFORMAT であると決定された場合、前記生ベイヤ

ーデータをアンパックする 50

ようにさらに構成される、請求項 17 に記載のデバイス。

**【請求項 19】**

前記アンパッキング回路は、別個のキャッシュを含む、請求項 17 に記載のデバイス。

**【請求項 20】**

グラフィックス処理のためのデバイスであって、

第 1 のラインの生ベイユーデータおよび第 2 のラインの生ベイユーデータを受け取るための手段と、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第 1 のラインの生ベイユーデータおよび前記第 2 のラインの生ベイユーデータの複数の重複しない  $2 \times 2$  配列の各  $2 \times 2$  配列をマッピングするための手段と、

前記複数のテクセルのうちの少なくとも 1 つに対して少なくとも 1 つの動作を実行するための手段と

を備えるデバイス。

**【請求項 21】**

前記少なくとも 1 つの動作は、ベイユービニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも 1 つを含む、請求項 20 に記載のデバイス。

**【請求項 22】**

前記複数のテクセルの各テクセルは、RGBA フォーマットである、請求項 20 に記載のデバイス。

**【請求項 23】**

前記複数のテクセルのうちの少なくとも 1 つに対して前記少なくとも 1 つの動作を実行した後、画像信号プロセッサに前記複数のテクセルを送信するための手段をさらに備える、請求項 20 に記載のデバイス。

**【請求項 24】**

前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第 1 のラインの生ベイユーデータおよび前記第 2 のラインの生ベイユーデータの複数の重複しない  $2 \times 2$  配列の各  $2 \times 2$  配列を前記マッピングすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、請求項 20 に記載のデバイス。

**【請求項 25】**

前記生ベイユーデータが MIPI フォーマットであるかどうかについての決定を行うための手段と、

前記生ベイユーデータが MIPI フォーマットであると決定された場合、前記生ベイユーデータをアンパックするために、グラフィックス処理ユニットのテクスチャパイプラインにおけるハードウェアを用いるための手段と

をさらに備える、請求項 20 に記載のデバイス。

**【請求項 26】**

前記テクスチャパイプラインにおける前記ハードウェアによって実行される前記生ベイユーデータを前記アンパックすることは、対応するテクスチャデータタイプを有する、請求項 25 に記載のデバイス。

**【請求項 27】**

前記テクスチャパイプラインにおける前記ハードウェアによって実行される前記生ベイユーデータを前記アンパックすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、請求項 25 に記載のデバイス。

**【発明の詳細な説明】**

**【関連出願の説明】**

**【0001】**

[0001] 本願は、その内容全体が参照により本明細書に組み込まれる、2015年1月28日に出願された米国仮特許出願第 62/108,986 号の利益を主張する。

**【技術分野】**

**【0002】**

10

20

30

40

50

[0002]本開示は、グラフィックス処理に関し、具体的には、グラフィックス処理ユニット( G P U )による生画像データ( raw image data )の処理に関する。

#### 【背景技術】

##### 【0 0 0 3】

[0003]デジタルカメラによって使用される C M O S 画像センサの出力は、典型的に、ベイバー生データ( Bayer raw data )である。ベイバー生データは、典型的に、50%緑、25%赤、および25%青であるフィルタパターンを含むベイバーフィルタからキャプチャされた、さらなる処理なしの、生画像データである。ベイバーデータは、データがデモザイキング( demosaicing )のようなさらなる処理以前にセンサによって提供されるフォーマットであるという点で、「生( raw )」である。画像センサは、典型的に、任意の所与のロケーション( location )における1色のみを感知する - 上記で説明されたように、ベイバーフィルタは、典型的に、50%緑センサ、25%赤センサ、および25%青センサであるフィルタパターンを使用する。画像が表示される前に、それは典型的に、それによってフルカラー画像が各ロケーションにおいて1色のみをキャプチャするセンサからの画像から再構成される、デモザイキングのような様々な処理を行う。

10

##### 【0 0 0 4】

[0004]ベイバー生画像データはまた、M I P I フォーマットであり得、これは、各行の終わりまでパディングのない、6 - 14ビットの深度における生センサデータの標準化された密なパッキングである(ここで、「各行( each row )」は、画像データの各行を意味し、ここで、画像データは、行および列において存在する2次元配列である)。M I P I フォーマットのデータは、よりコンパクトであるが、データ構造アラインメントの目的のために通常使用されるパディングを欠く。「データ構造アラインメント」は、メモリにおける特定のデータ構造がどこで( when )開始および終了するかを決定することが可能になるように、データがメモリにおいてアクセスおよび配置( arranged )される方法を指す。標準データフォーマットは、データ構造アラインメントを確実にするためにパディングを使用する。M I P I フォーマットにおけるデータは、各行の終わりまでパディングを有しないので、M I P I フォーマットデータのストライド長は、予め決定されなければならない(例えば、アラインされた128または256ビット)。

20

#### 【発明の概要】

##### 【0 0 0 5】

[0005]いくつかの例では、グラフィックス処理のためのデバイスが、キャッシュと、キャッシュから第1のラインの生ベイバーデータ、およびキャッシュから第2のラインの生ベイバーデータを受け取り、複数のテクセル( texels )を提供するために、別個の対応するテクセルとして、第1のラインの生ベイバーデータおよび第2のラインの生ベイバーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングし、複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作( operation )を実行するように構成( arranged )されたテクスチャパイプラインとを備える。

30

##### 【0 0 0 6】

[0006]いくつかの例では、グラフィックス処理のための方法が、第1のラインの生ベイバーデータおよび第2のラインの生ベイバーデータを受け取ることと、複数のテクセルを提供するために、別個の対応するテクセルとして、第1のラインの生ベイバーデータおよび第2のラインの生ベイバーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングすることと、複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行することとを備える。

40

##### 【0 0 0 7】

[0007]いくつかの例では、グラフィックス処理のためのデバイスが、第1のラインの生ベイバーデータおよび第2のラインの生ベイバーデータを受け取るための手段と、複数のテクセルを提供するために、別個の対応するテクセルとして、第1のラインの生ベイバーデータおよび第2のラインの生ベイバーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするための手段と、複数のテクセルのうちの少なくとも1つに対して

50

少なくとも1つの動作を実行するための手段とを備える。

#### 【0008】

[0008]本開示の1つまたは複数の態様の詳細は、添付の図面および以下の説明において示される。本開示で説明される技法の他の特徴、目的、および利点は、説明および図面から、および特許請求の範囲から明らかになるであろう。

#### 【図面の簡単な説明】

##### 【0009】

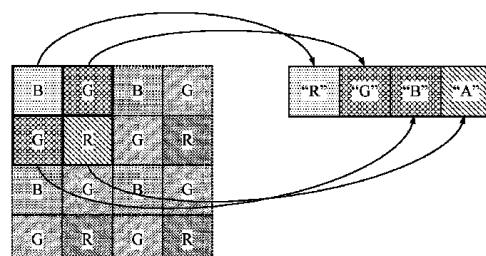

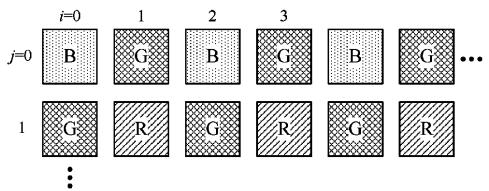

【図1】[0009]図1は、カメラセンサを示す概念図である。

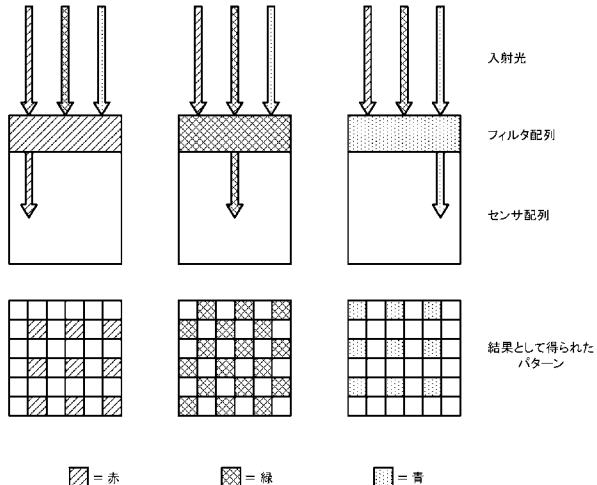

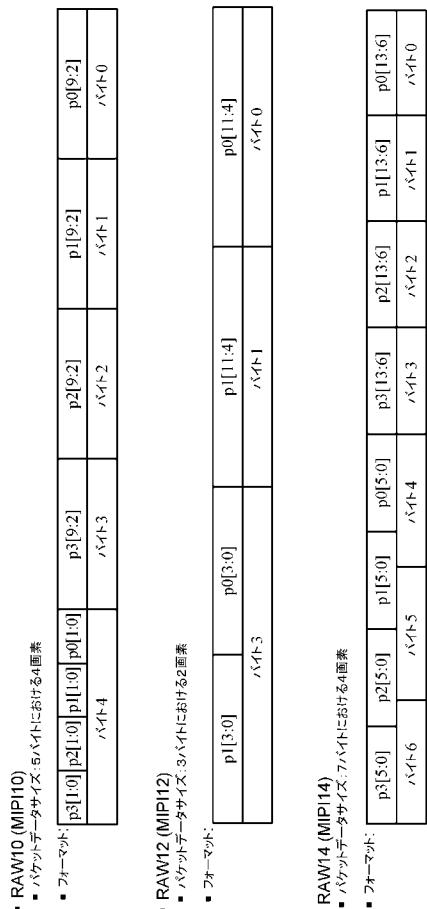

【図2】[0010]図2は、生センサデータの処理を示す概念図である。

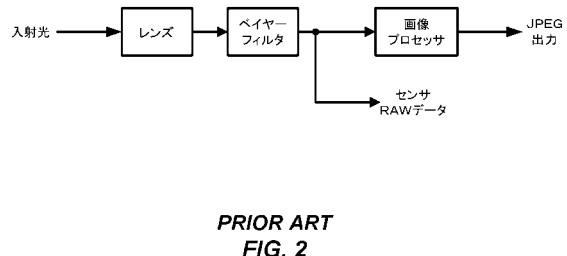

【図3】[0011]図3は、MIPPI10、MIPPI12、およびMIPPI14フォーマットにおけるビットパッキングの例を示す概念図である。

10

【図4】[0012]図4は、ベイヤーデータのための実例的なレイアウトを示す概念図である。

。

【図5】[0013]図5は、本開示の技法による実例的なデバイスを例示するブロック図である。

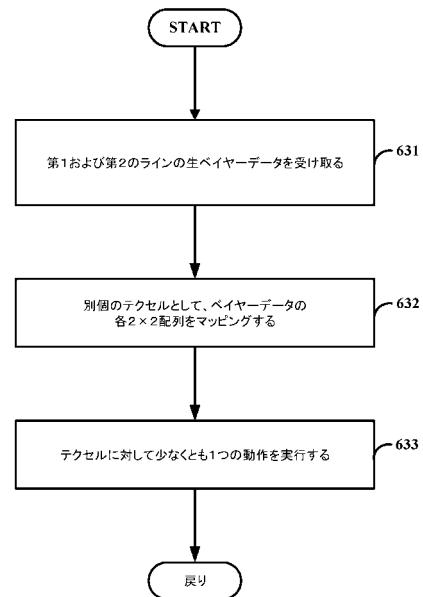

【図6】[0014]図6は、本開示の技法による実例的なプロセスを例示するフロー図である。

。

【図7】[0015]図7は、本開示の技法をインプリメントし得る実例的なシステムを例示するブロック図である。

【図8】[0016]図8は、本開示の技法をインプリメントし得る図7のシステムの例を例示するブロック図である。

20

【図9】[0017]図9は、本開示の技法による図6のプロセスの動作(acts)のうちの1つの例に従って、各ベイヤーパターンをテクセルにマッピングする例を例示する概念図である。

【図10】[0018]図10は、本開示の技法による図9のマッピングされたテクセルをアドレス指定(addressing)するためのプロセスを例示する概念図である。

【図11】[0019]図11は、本開示の技法による図6のプロセスの動作(acts)のうちの1つの例に従って、テクセルに対して収集動作を実行する例を例示する概念図である。

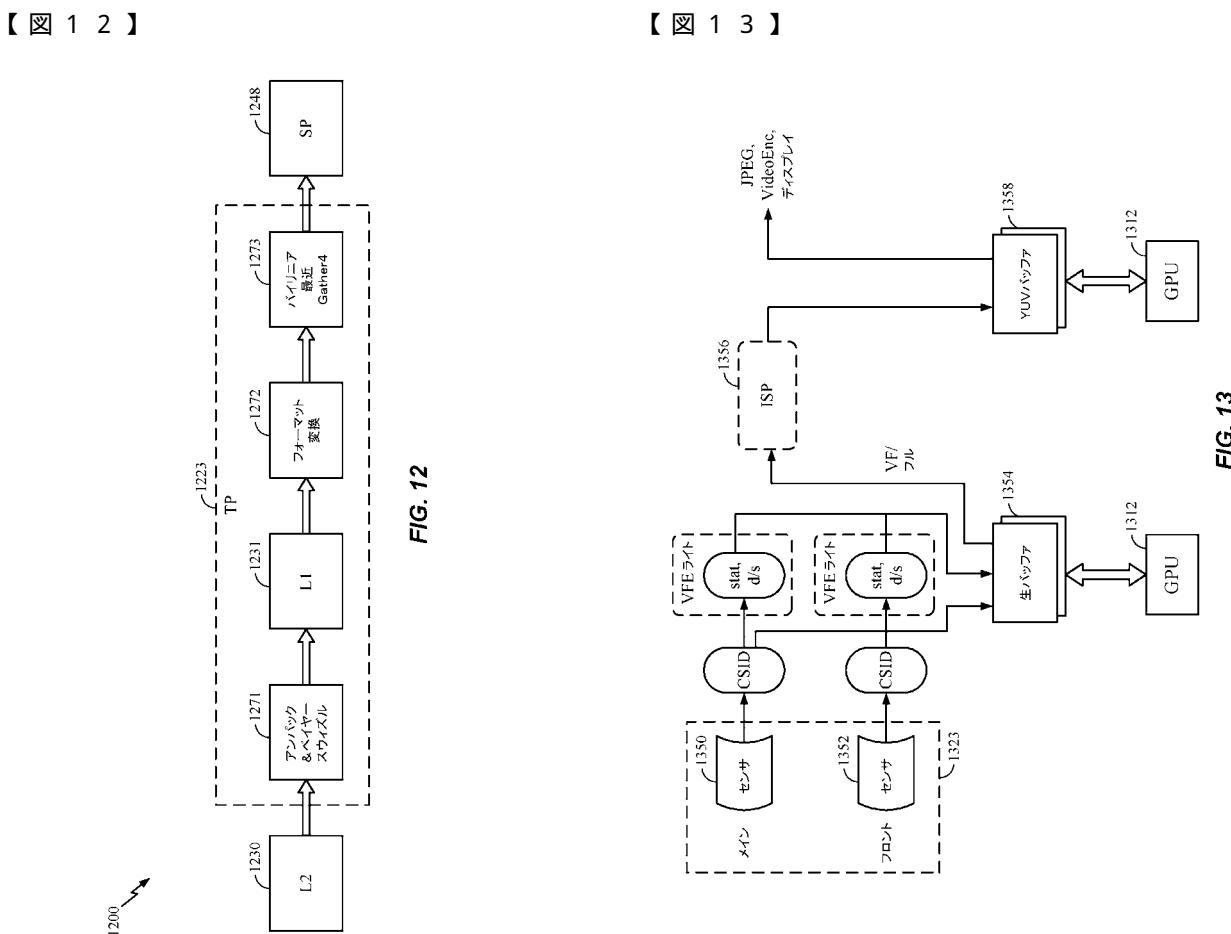

【図12】[0020]図12は、本開示の技法による図8のシステムの一部の例を例示するブロック図である。

30

【図13】[0021]図13は、本開示の技法による、図7のデバイスの例を示す機能ブロック図である。

#### 【発明の詳細な説明】

##### 【0010】

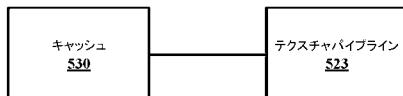

[0022]いくつかの例では、グラフィックス処理のためのデバイスが、キャッシュおよびテクスチャパイプラインを備える。(例えば、GPUの)テクスチャパイプラインは、キャッシュから第1のラインの生ベイヤーデータ、およびキャッシュから第2のラインの生ベイヤーデータを受け取るように構成される。テクスチャパイプラインは、複数のテクセルを提供するために、別個の対応するテクセルとして、第1のラインの生ベイヤーデータおよび第2のラインの生ベイヤーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするようにさらに構成される。「 $2 \times 2$ (two by two)」は、 $2 \times 2$ 配列が1つのラインにおける2つの隣接する画素(pixels)(例えば、第1のラインにおける2つの隣接する画素)および隣接するラインにおける2つの隣接する画素(例えば、第2のラインにおける2つの隣接する画素)を含むように、2次元の画像データを指す。 $2 \times 2$ パターンは、例えば、このような $2 \times 2$ 配列のテクセルを例示する以下の図9-図11に関して、以下でより詳細に説明される。

40

##### 【0011】

[0023]別個の対応するテクセルとして、第1のラインの生ベイヤーデータおよび第2のラインの生ベイヤーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングすることは、マッピング後に、各個別の画素が、データに対して実行される動作の基本単

50

位として扱われるのとは対照的に、 $2 \times 2$  マトリクスにおける 4 つの画素の各まとまり (bundle) が、データに対して実行される動作の基本単位として扱われるよう、生ベイヤーデータの各  $2 \times 2$  配列における 4 つの画素がひとまとめにされる (bundled) ことを意味する。複数のテクセルを提供するために、別個の対応するテクセルとして、第 1 のラインの生ベイヤーデータおよび第 2 のラインの生ベイヤーデータの複数の重複してない  $2 \times 2$  配列の各  $2 \times 2$  配列をマッピングすることは、定義上、テクセルに  $2 \times 2$  配列をマッピングすることのより短い参照手段として「ベイヤースウィズリング (Bayer swizzling)」と呼ばれる。(ベイヤースウィズルの具体例が、以下の図 9 に例示され、図 9 に関してより詳細に説明される。) テクスチャパイプラインは、複数のテクセルのうちの少なくとも 1 つに対して少なくとも 1 つの動作を実行するようにさらに構成される。

10

## 【0012】

[0024] テクスチャパイプラインは、より詳細に説明されるように、例えば、位相検出オートフォーカス (PDAF) センサ、赤青緑クリア (RGBC) センサ、インターリードハイダイナミックレンジ (iHDR) センサ、コンピュテーションナルフォトグラフィ (computational photography)、およびライトフィールドコンピュテーション (light field computation) などの、ある特定のカスタムセンサアプリケーションのためのある特定の前処理タスクを遂行するために、これら動作を実行する。ベイヤースウィズリングは、このようなカスタムセンサアプリケーションのために実行されるある特定の動作が、個々の画素のレベルではなく、各々が画素の  $2 \times 2$  配列に対応するテクセルのレベルで実行されるので、これら動作が、より一層効率的になることを可能にする。ベイヤースウィズリング後は、アクセスされる各テクセルが 4 つのベイヤー画素を含むので、読み取り動作は、さもなければ 4 回の読み取りを必要とするであろうものを、1 回の読み取りで遂行することができる。同様の理由で、ベイヤースウィズリング後のこれらテクセルに対する収集動作は、さもなければ 4 回のロードを必要とするであろうものを、1 回のロードで遂行することができる。

20

## 【0013】

[0025] さらに、ベイヤースウィズリング後、これらテクセルは、以下でより詳細に説明される理由から、テクスチャパイプラインにおけるバイリニアフィルタリング (bilinear filtering) の効率的なパフォーマンスによく適している (バイリニアフィルタリングは、ここでの後続するセクションにおいて説明される)。このようにして、ベイヤースウィズリング後、ベイヤービニング (Bayer Binning) を含むいくつかのアプリケーションは、テクスチャパイプラインのバイリニアフィルタリング能力を使用して、テクスチャパイプラインにおいて非常に効率的に実行されることができる。追加として、ベイヤースウィズリングは、グラフィックス処理ユニット (GPU) におけるシェーダプロセッサ上の負荷が低減されるように、ベイヤーデータをひとまとめにし、ここで、テクスチャパイプラインおよびシェーダプロセッサは、いくつかの例では、両方とも GPU に含まれる。シェーダプロセッサは、以下でより詳細に説明される。テクスチャパイプラインがテクセルに対して実行する動作の具体例およびこのような実例的な動作のさらなる詳細が、ここでの後のセクションにおいて詳細に説明される。

30

## 【0014】

[0026] テクスチャパイプラインはまた、生 MIP データをアンパックする (unpack) ために使用されることがある。(例えば、位相検出オートフォーカス (PDAF) センサ、赤青緑クリア (RGBC) センサ、インターリードハイダイナミックレンジ (iHDR) センサ、コンピュテーションナルフォトグラフィ、およびライトフィールドコンピュテーションを含む) ある特定のカスタムセンサアプリケーションにとっては、これらカスタムアプリケーションによって必要とされる動作を実行する前にアンパックされた MIP データへのアクセスを有することが有利であり得る。テクスチャパイプラインにおいて MIP データをアンパックすることは、MIP データをアンパックする従来の方法に対して、著しい速度の優位性を有することができる。

40

## 【0015】

50

[0027]上記で説明されたように、M I P I データは、密にパックされている - 各行の終りまで M I P I データにおけるパディングがない。M I P I データが標準のパディング (normal padding) を欠いているので、データ構造アラインメントは困難であり、M I P I データのストライド長は、予め決定されなければならない。M I P I データを「アンパックする」ことは、データが、予め決定されたストライド長を必要とせずに、プロセッサによるアクセスと適正にアラインメントされることができるよう、十分なデータ構造パディングを有するフォーマットに M I P I データを変換することを指す。ほとんどの標準的な (most standard) データフォーマットは、「アンパック」されている。アンパッキングが必要とするのは、(標準的な量のデータ構造パディングを欠く) M I P I のような密にパックされたデータフォーマットのみである。本開示によるテクスチャパイプラインの例によって実行される M I P I アンパッキングについてのさらなる詳細は、ここでの後のセクションにおいて説明される。

10

## 【0016】

[0028]本説明のこの段階では、本開示のある特定の態様がより良く理解され得るように、ベイヤーデータおよび M I P I データなどの、様々なタイプの生データフォーマットをさらに説明することが有用であり得る。

## 【0017】

[0029]このセクションにおける説明は、ここで説明される画像データフォーマット (例えば、ベイヤーおよび M I P I ) のより詳細な説明を与える。デジタルカメラは、レンズと、光を検出し、カラー画素値 (例えば、R G B 値) を生成するように構成されたカメラセンサとを含み得る。図 1 は、カメラセンサの結果として得られたカラー画素値の例を示し、ここで、これらカラー画素値は、センサによる可視光の検出によって作成される。センサによって生成される、結果として得られたカラー画素値は、しばしば生センサデータと呼ばれる。以下でより詳細に説明されるように、生センサデータは、典型的に、ベイヤーフィルタモザイク画素フォーマットのような、密にパックされたフォーマットであり、または、M I P I データフォーマット (例えば、M I P I 1 0、M I P I 1 2、および M I P I 1 4) でパックされた、ベイヤーフィルタモザイク画素フォーマットを含む、生センサデータである。

20

## 【0018】

[0030]カメラは、画像信号プロセッサをさらに含み得る。いくつかの例では、画像信号プロセッサは、レンズおよびカメラセンサと同じパッケージ中に共に含まれる。他の例では、画像信号プロセッサは、レンズおよびカメラセンサとは別個にパッケージ化され得る。いくつかの例では、画像信号プロセッサは、グラフィックス処理ユニット (G P U) を含むシステムオンチップ (S o C) 上に含まれ得る。画像信号プロセッサは、生センサデータを受け取り、生センサデータを圧縮されたデータフォーマット (例えば、J P E G ファイル) に変換し、ピクチャファイルにおいて、結果として得られた圧縮されたデータを記憶するように構成され得る。他の例では、画像信号プロセッサは、生センサデータを保持し、別個のファイルにおいて生センサデータを保存するように構成され得る。図 2 は、画像プロセッサを備えた実例的なカメラシステムを示す。

30

## 【0019】

[0031]しばしば、密にパックされたフォーマットにおける生センサデータは、(例えば、画像信号プロセッサによって) 追加の処理が実行される前にアンパックされる。生ベイヤーフィルタモザイクセンサデータは、典型的に、1 画素当たり 1 0 または 1 2 ビットであり、密にパックされている (すなわち、各行の終りまで、いかなるパディングもなしにパックされる)。

40

## 【0020】

[0032]ここで、M I P I データフォーマットが説明される。M I P I アライアンスは、モバイル業界向けのインタフェース仕様を開発する団体である。M I P I アライアンスによって開発された実例的な仕様は、カメラシリアルインターフェース (C S I) 仕様およびディスプレイシリアルインターフェース (D S I) 仕様を含む。C S I 仕様は、カメラセン

50

サと画像信号プロセッサの間のインターフェースのためのプロトコルを指定する。C S I の一般的に使用されるバージョンが、C S I - 2 である。D S I 仕様は、ディスプレイプロセッサとディスプレイパネルの間のインターフェースのためのプロトコルを指定する。

#### 【0021】

[0033] M I P I フォーマットは、6 - 14 ビットの深度の生センサデータの密なパッキングを規格化する (standardize)。生センサデータのためのM I P I フォーマットは、10 ビット、12 ビット、および 14 ビットのフォーマットを含む。図 3 は、M I P I 10、M I P I 12、および M I P I 14 フォーマットにおけるビットパッキングの例を示す。M I P I フォーマットの各々について、各行の画素データは、行の終わりにおけるパディングとともに、密にパックされている。

10

#### 【0022】

[0034] 10 ビットのフォーマットを使用する 1 つの例が、R A W 10 フォーマット、または M I P I 10 と呼ばれる。図 3 に示されるように、M I P I 10 フォーマットでは、4 画素 (40 ビット) ごとに、5 バイトのチャンク (chunks) にパックされる。各画素の 8 つの最上位ビット (M S B) が最初にパックされ、その後、2 つの最下位ビット (L S B) が、最終バイトに連結される。パケットデータサイズは、5 バイトにおける 4 画素である (4 pixels in 5 bytes)。

#### 【0023】

[0035] 12 ビットのフォーマットを使用する 1 つの例が、R A W 12 フォーマット、または M I P I 12 と呼ばれる。図 3 に示されるように、M I P I 12 フォーマットでは、2 画素 (24 ビット) ごとに、3 バイトのチャンクにパックされる。各画素の 8 つの最上位ビット (M S B) が最初にパックされ、その後、4 つの最下位ビット (L S B) が、最終バイトに連結される。パケットデータサイズは、3 バイトにおける 2 画素である。

20

#### 【0024】

[0036] 14 ビットのフォーマットを使用する 1 つの例が、R A W 14 フォーマット、または M I P I 14 と呼ばれる。図 3 に示されるように、M I P I 14 フォーマットでは、4 画素 (56 ビット) ごとに、7 バイトのチャンクにパックされる。各画素の 8 つの最上位ビット (M S B) が最初にパックされ、その後、6 つの最下位ビット (L S B) が、最終バイトに連結される。パケットデータサイズは、7 バイトにおける 4 画素である。

30

#### 【0025】

[0037] 図 4 は、M I P I フォーマットのための実例的なレイアウトを示す。M I P I 10 フォーマットでは、アドレス指定の計算 (addressing calculation) は、次のように実行される。各行またはスキャニングライン (例えば、「B G B G B G . . .」または「G R G R G R . . .」) は、終わりにおいてパディングされる。したがって、ストライドは、予め決定されなければならない (例えば、アラインされた 128 または 256 ビット)。各行内では、画素  $i$  について:  $(i / 4) * 5 = 5$  バイトセグメントのバイトアドレス。

#### 【0026】

[0038] この計算は、加算器および組合せ論理回路を使用してインプリメントされ得る。しかしながら、計算を実行することの複雑さは、5 バイトの境界をまたぐ (cross) 2 画素が必要とされる場合に増大される。その場合には、2 つの 5 バイトのチャンクがフェッチされなければならない。

40

#### 【0027】

[0039] 関連のある画像データフォーマットが説明されたので、本開示によるデバイスおよび方法の例の大まかな説明 (high-level description) が、ここで説明される。このセクションの意図は、実例的なデバイスおよび方法の大まかな説明を与えることであるので、実例的なデバイスおよび方法が含まれ得る特定の環境の例および図 5 のデバイス 501 内の特定の実例的な要素のさらなる詳細、ならびに実例的なデバイスおよび方法によって達成される利益は、このセクションでは説明されず、その代わりに、ここでの開示の他のセクションにおいて説明される。

#### 【0028】

50

[0040]図5は、グラフィックス処理のためのデバイス501の例を例示するブロック図である。デバイス501は、キャッシュ530およびテクスチャパイプライン523を含む。テクスチャパイプライン523は、キャッシュ530から第1のラインの生ベイユーデータ、およびキャッシュ530から第2のラインの生ベイユーデータを受け取るように構成される。テクスチャパイプライン523は、複数のテクセルを提供するために、別個の対応するテクセルとして、第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするようにさらに構成される。テクスチャパイプライン523は、複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行するようにさらに構成される。

【0029】

10

[0041]いくつかの例では、テクスチャパイプライン523は、GPUの一部である。いくつかの例では、第1および第2のラインのデータは、画像センサによって生成された、隣接するラインの生画像データであり、「 $2 \times 2$ 」は、 $2 \times 2$ 配列が1つのラインにおける2つの隣接する画素（例えば、第1のラインにおける2つの隣接する画素）および隣接するラインにおける2つの隣接する画素（例えば、第2のラインにおける2つの隣接する画素）を含むように、2次元の画像データを指す。

【0030】

20

[0042]図6は、グラフィックス処理のためのプロセス630の例を例示するフロー図である。開始ブロック後、テクスチャパイプライン（例えば、図5のテクスチャパイプライン523）は、第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータを受け取る（631）。いくつかの例では、第1および第2のラインのデータは、画像センサによって生成された、隣接するラインの生画像データである。次に、テクスチャパイプラインは、複数のテクセルを提供するために、別個の対応するテクセルとして、第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングする（632）。複数のテクセルを提供するために、別個の対応するテクセルとして、第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするために、テクスチャパイプラインによって実行されるマッピングは、「ベイユースウィズリング」としてここで定義される。ベイユースウィズリング後、テクスチャパイプラインは、複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行する（633）。その後、プロセスは、戻りブロックに進み、ここで、他の処理が再開される。

【0031】

30

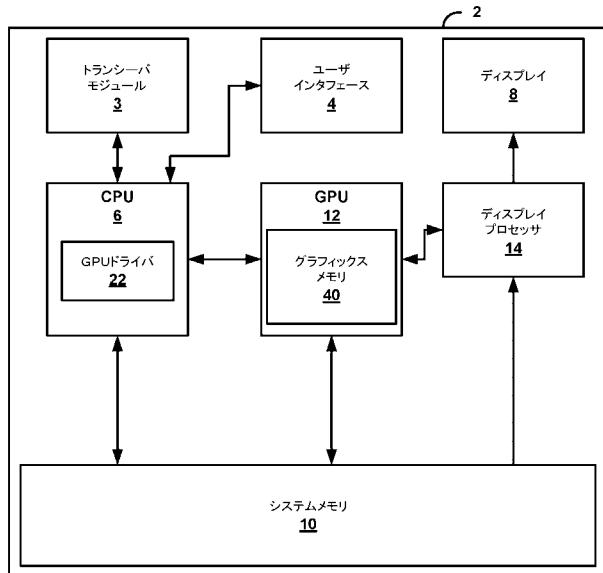

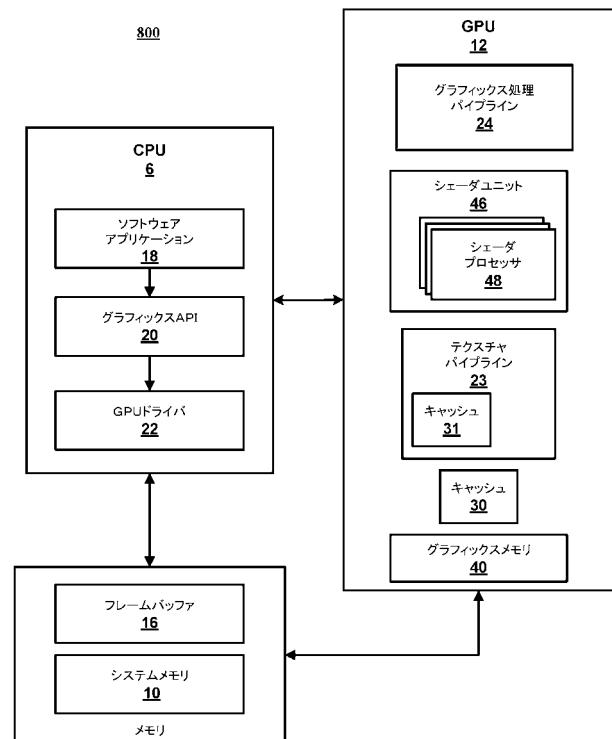

[0043]図7は、本開示の1つまたは複数の態様をインプリメントするように構成され得る実例的なシステム／デバイスを例示するブロック図である。図7に示されるように、システム／デバイス2は、パーソナルコンピュータ、デスクトップコンピュータ、ラップトップコンピュータ、タブレットコンピュータ、コンピュータワークステーション、ビデオゲームプラットフォームまたはコンソール、例えば、セルラまたは衛星電話のようなモバイル電話、ランドライン電話、インターネット電話、ポータブルビデオゲームデバイスまたは携帯情報端末（PDA）のようなハンドヘルドデバイス、パーソナルミュージックプレーヤ、ビデオプレーヤ、ディスプレイデバイス、テレビジョン、テレビジョンセットトップボックス、サーバ、中間ネットワークデバイス、メインフレームコンピュータ、任意のモバイルデバイス、あるいはグラフィカルデータを処理するおよび／または表示するその他任意のタイプのデバイスであり得る。図7の例では、デバイス2は、中央処理ユニット（CPU）6、システムメモリ10、およびGPU12を含み得る。デバイス2はまた、ディスプレイプロセッサ14、トランシーバモジュール3、ユーザインタフェース4、およびディスプレイ8を含み得る。トランシーバモジュール3およびディスプレイプロセッサ14は、両方がCPU6および／またはGPU12と同じ集積回路（IC）の一部であり得るか、両方がCPU6および／またはGPU12を含むICまたは複数のICの外部にあり得るか、またはCPU6および／またはGPU12を含むICの外部にあるIC内に形成され得る。

40

50

## 【0032】

[0044] デバイス 2 は、明確さを目的として図 7 に示されていない追加のモジュールまたはユニットを含み得る。例えば、デバイス 2 は、デバイス 2 がモバイルワイアレス電話である例において電話通信を実施するために、そのいずれもが図 7 に示されていないスピーカおよびマイクロホン、またはデバイス 2 がメディアプレーヤである場合にはスピーカを含み得る。デバイス 2 はまた、ビデオカメラを含み得る。デバイス 2 はまた、画像信号プロセッサ (ISP) を含み得る。さらに、デバイス 2 において示される様々なモジュールおよびユニットは、デバイス 2 のすべての例において必ずしも必要ではない。例えば、ユーザインタフェース 4 およびディスプレイ 8 は、デバイス 2 が外部ユーザインタフェースまたはディスプレイとインタフェースするように装備されたデスクトップコンピュータまたは他のデバイスである例では、デバイス 2 の外部にあり得る。

10

## 【0033】

[0045] ユーザインタフェース 4 の例は、それに限定されるものではないが、トラックボール、マウス、キーボード、および他のタイプの入力デバイスを含む。ユーザインタフェース 4 はまた、タッチスクリーンであり得、ディスプレイ 8 の一部として組み込まれ得る。トランシーバモジュール 3 は、デバイス 2 と別のデバイスまたはネットワークとの間のワイアレスまたはワイヤード通信を可能にするための回路を含み得る。トランシーバモジュール 3 は、変調器、復調器、増幅器、およびワイヤードまたはワイヤレス通信のための他のそのような回路を含み得る。

20

## 【0034】

[0046] CPU 6 は、実行のためにコンピュータプログラムの命令を処理するように構成された中央処理ユニット (CPU) のような、マイクロプロセッサであり得る。CPU 6 は、デバイス 2 の動作を制御する汎用または専用プロセッサを備え得る。ユーザは、CPU 6 に、1つまたは複数のソフトウェアアプリケーションを実行することを行わせるために、デバイス 2 に入力を提供し得る。CPU 6 上で実行されるソフトウェアアプリケーションは、例えば、オペレーティングシステム、ワードプロセッサアプリケーション、電子メールアプリケーション、スプレッドシートアプリケーション、メディアプレーヤアプリケーション、ビデオゲームアプリケーション、グラフィカルユーザインタフェースアプリケーション、または別のプログラムを含み得る。追加として、CPU 6 は、GPU 12 の動作を制御するための GPU ドライバ 2 を実行し得る。ユーザは、キーボード、マウス、マイクロホン、タッチパッド、またはユーザインタフェース 4 を介してデバイス 2 に結合された別の入力デバイスのような、1つまたは複数の入力デバイス（図示せず）を介してデバイス 2 への入力を提供し得る。

30

## 【0035】

[0047] CPU 6 上で実行されるソフトウェアアプリケーションは、ディスプレイ 8 へのグラフィックスデータのレンダリングを生じさせるように CPU 6 に命令する1つまたは複数のグラフィックスレンダリング命令を含み得る。いくつかの例では、ソフトウェア命令は、例えば、OpenGL (登録商標) (Open Graphics Library) API、OpenGLES (Open Graphics Library Embedded Systems) API、Direct3D API、X3D API、RenderMan API、WebGL API、あるいはその他任意の公的または独自の標準グラフィックス API などの、グラフィックスアプリケーションプログラムインターフェース (API) に準拠し得る。グラフィックスレンダリング命令を処理するために、CPU 6 は、GPU 12 に、グラフィックスデータのレンダリングの一部または全てを実行することを行わせるために、（例えば、GPU ドライバ 2 を通じて）GPU 12 に1つまたは複数のグラフィックスレンダリングコマンドを発行し得る。いくつかの例では、レンダリングされるグラフィックスデータは、例えば、点、線、三角形、四角形、トライアングルストリップ (triangle strips) などの、グラフィックスプリミティブのリストを含み得る。

40

## 【0036】

[0048] 他の例では、CPU 6 上で実行されるソフトウェア命令は、GPU 12 に、G

50

P U ハードウェアの高度な並列性によって実行されるように適用可能な (applicable to be executed) 、より一般的な計算を実行するための汎用シェーダを実行させ得る。このような汎用アプリケーションは、いわゆる汎用グラフィックス処理ユニット (G P G P U ) であり得、 O p e n C L のような、汎用 A P I に準拠し得る。

### 【 0 0 3 7 】

[0049] G P U 1 2 は、ディスプレイ 8 に 1 つまたは複数のグラフィックスプリミティブをレンダリングするためにグラフィックス動作を実行するように構成され得る。したがって、 C P U 6 上で実行中のソフトウェアアプリケーションのうちの 1 つがグラフィックス処理を必要とするとき、 C P U 6 は、ディスプレイ 8 へのレンダリングのために、 G P U 1 2 にグラフィックスコマンドおよびグラフィックスデータを提供し得る。グラフィックスデータは、例えば、描画コマンド、状態情報、プリミティブ情報、テクスチャ情報などを含み得る。 G P U 1 2 は、いくつかの事例では、 C P U 6 に比べて、複雑なグラフィック関連動作のより効率的な処理を提供する高度な並列構造を用いて構築され得る。例えば、 G P U 1 2 は、並列的に (in a parallel manner) 複数の頂点または画素に対して動作するように構成された、複数のシェーダユニットのような複数の処理要素を含み得る。 G P U 1 2 の高度な並列性は、いくつかの事例では、 G P U 1 2 が、グラフィックス画像 (例えば、 G U I および 2 次元 (2 D ) および / または 3 次元 (3 D ) グラフィックスシーン) を、 C P U 6 を使用してディスプレイ 8 にこれらのシーンを直接描画するよりも迅速に、ディスプレイ 8 上に描画することを可能にし得る。

10

### 【 0 0 3 8 】

[0050] G P U 1 2 は、いくつかの事例では、デバイス 2 のマザーボードに組み込まれ得る。他の事例では、 G P U 1 2 は、デバイス 2 のマザーボードにおけるポートでインストールされるグラフィックスカード上に存在し得るか、さもなければデバイス 2 と相互動作するように構成された周辺デバイス内に組み込まれ得る。 G P U 1 2 は、 1 つまたは複数のマイクロプロセッサ、特定用途向け集積回路 (A S I C ) 、フィールドプログラマブルゲートアレイ (F P G A ) 、デジタルシグナルプロセッサ (D S P ) 、または他の同等の集積回路またはディスクリート論理回路などの、 1 つまたは複数のプロセッサを含み得る。 G P U 1 2 はまた、 G P U 1 2 がマルチコアプロセッサと呼ばれ得るように、 1 つまたは複数のプロセッサコアを含み得る。

20

### 【 0 0 3 9 】

[0051] G P U 1 2 は、グラフィックスメモリ 4 0 に直接結合され得る。したがって、 G P U 1 2 は、バスを使用することなく、グラフィックスメモリ 4 0 からデータを読み取り、また、それにデータを書き込み得る。換言すると、 G P U 1 2 は、オフチップメモリの代わりに、ローカル記憶装置を使用してローカルにデータを処理し得る。このようなグラフィックスメモリ 4 0 は、オンチップメモリと呼ばれ得る。これは、 G P U 1 2 がバスを介してデータを読み取るおよび書き込む必要性、これは重いバストラフィックを経験し得る、を除去することによって、 G P U 1 2 がより効率的な手法で動作することを可能にする。しかしながら、いくつかの事例では、 G P U 1 2 は、別個のメモリを含まず、代わりに、バスを介してシステムメモリ 1 0 を利用し得る。グラフィックスメモリ 4 0 は、例えば、ランダムアクセスメモリ (R A M ) 、 static RAM (S R A M ) 、ダイナミック R A M (D R A M ) 、消去可能なプログラマブル R O M (E P R O M ) 、電気的に消去可能なプログラマブル R O M (E E P R O M (登録商標)) 、フラッシュメモリ、磁気データ媒体または光記憶媒体などの、 1 つまたは複数の揮発性または不揮発性メモリまたは記憶デバイスを含み得る。グラフィックスメモリ 4 0 は、キャッシュ 3 0 を含むおよび / またはキャッシュ 3 0 に結合され得る。キャッシュ 3 0 は、図 5 のキャッシュ 5 3 0 の例として用いられ得る。いくつかの例では、キャッシュ 3 0 は、 G P U 1 2 によって実行されるメモリフェッティング動作のためのレベル 2 キャッシュである (すなわち、 G P U 1 2 におけるキャッシュミスは、キャッシュ 3 0 へのアクセスをもたらし得る) 。他の例では、キャッシュ 3 0 は、レベル 3 キャッシュまたは同様のものであり得る。

30

40

50

## 【0040】

[0052] いくつかの例では、G P U 1 2 は、システムメモリ 1 0 に完全に形成された画像を記憶し得る。ディスプレイプロセッサ 1 4 は、システムメモリ 1 0 から画像を取り出し、画像を表示するためにディスプレイ 8 の画素を点灯させる値を出力し得る。ディスプレイ 8 は、G P U 1 2 によって生成される画像コンテンツを表示する、デバイス 2 のディスプレイであり得る。ディスプレイ 8 は、液晶ディスプレイ (L C D)、有機発光ダイオードディスプレイ (O L E D)、陰極線管 (C R T) ディスプレイ、プラズマディスプレイ、または別のタイプのディスプレイデバイスであり得る。

## 【0041】

[0053] 本開示の技法によると、G P U 1 2 は、生ベイヤーデータを受け取り、複数のテクセルを提供するために、別個の対応するテクセルとして、第 1 のラインの生ベイヤーデータおよび第 2 のラインの生ベイヤーデータの複数の重複しない  $2 \times 2$  配列の各  $2 \times 2$  配列をマッピングするように構成され得る。追加として、本開示の技法によると、G P U 1 2 は、カメラセンサデータがM I P I のような密にパックされたフォーマットであるとき、カメラセンサデータをアンパックするようにさらに構成され得る。

## 【0042】

[0054] 例えば、G P U 1 2 は、テクスチャパイプライン 5 2 3 を含み得、したがって、本開示で説明される実例的な技法を実行するように構成され得る。G P U 1 2 は、グラフィックス処理のためのメカニズムを提供し、これは、テクセル処理を含む。したがって、G P U 1 2 は、複数の画素の生ベイヤーデータが単一の基本単位（例えば、G P U 1 2 のためのテクセル）として処理されることができるように、本開示で説明される技法を実行するのによく適し得る。このようにして、テクセルを基本単位として処理する G P U 1 2 の能力は、ベイヤー画像データの 4 つの異なる画素を処理するために利用されることができる。

## 【0043】

[0055] 図 8 は、システム 8 0 0 の例を例示するブロック図であり、これは、さらなる詳細において、図 7 のC P U 6、G P U 1 2、およびシステムメモリ 1 0 の実例的なインプリメンテーションを含む。図 8 に示されるように、C P U 6 は、少なくとも 1 つのソフトウェアアプリケーション 1 8、グラフィックス API 2 0、および G P U ドライバ 2 2 を含み得、これらの各々は、C P U 6 上で実行される 1 つまたは複数のソフトウェアアプリケーションまたはサービスであり得る。

## 【0044】

[0056] C P U 6 および G P U 1 2 に利用可能なメモリは、システムメモリ 1 0 およびフレームバッファ 1 6 を含み得る。フレームバッファ 1 6 は、システムメモリ 1 0 の一部であり得るか、またはシステムメモリ 1 0 とは別個であり得る。フレームバッファ 1 6 は、レンダリングされた画像データを記憶し得る。

## 【0045】

[0057] ソフトウェアアプリケーション 1 8 は、G P U 1 2 の機能性を利用する任意のアプリケーションであり得る。例えば、ソフトウェアアプリケーション 1 8 は、G U I アプリケーション、オペレーティングシステム、ポータブルマッピングアプリケーション、工学および芸術アプリケーションのためのコンピュータ支援型設計プログラム、ビデオゲームアプリケーション、あるいは 2 D または 3 D グラフィックスを使用する別のタイプのソフトウェアアプリケーションであり得る。

## 【0046】

[0058] ソフトウェアアプリケーション 1 8 は、グラフィカルユーザインターフェース (G U I) および / またはグラフィックスシーンをレンダリングするように G P U 1 2 に命令する 1 つまたは複数の描画命令を含み得る。例えば、描画命令は、G P U 1 2 によってレンダリングされる 1 つまたは複数のグラフィックスプリミティブのセットを定義する命令を含み得る。いくつかの例では、描画命令は、集合的に、G U I において使用される複数のウィンドウサーフェス (windowing surfaces) の全てまたは一部を定義し得る。追

加の例では、描画命令は、集合的に、アプリケーションによって定義されるモデル空間またはワールド空間内に1つまたは複数のグラフィックスオブジェクトを含むグラフィックスシーンの全てまたは一部を定義し得る。

#### 【0047】

[0059]ソフトウェアアプリケーション18は、1つまたは複数のグラフィックスプリミティブを、表示可能なグラフィックス画像へとレンダリングするための1つまたは複数のコマンドをGPU12へ発行するために、グラフィックスAPI20を介して、GPUドライバ22を起動(invoked)し得る。いくつかの例では、これらプリミティブは、グラフィックスメモリ40に記憶され得る。

#### 【0048】

[0060]GPU12がCPU6からコマンドを受け取ると、グラフィックス処理パイプライン24は、コマンドを復号し、コマンドにおいて指定される動作を実行するようにグラフィックス処理パイプライン24を構成する。

#### 【0049】

[0061]フレームバッファ16は、GPU12のためのデスティネーション画素(destination pixels)を記憶する。各デスティネーション画素は、一意のスクリーン画素口ケーションに関連付けられ得る。いくつかの例では、フレームバッファ16は、デスティネーション画素ごとに色成分およびデスティネーションアルファ値を記憶し得る。

#### 【0050】

[0062]いくつかの例では、GPU12は、シェーダユニット46、グラフィックス処理パイプライン24、テクスチャパイプライン23、およびグラフィックスメモリ40を含む。いくつかの例では、テクスチャパイプライン23は、図5のテクスチャパイプライン523の例として用いられ得る。1つまたは複数のシェーダプログラムは、GPU12におけるシェーダユニット46上で実行され得る。シェーダユニット46は、シェーダプログラムサ48を含み得、その各々は、フェッチングおよび復号動作(fetching and decoding operations)のための1つまたは複数の構成要素、算術演算を行うための1つまたは複数の算術論理演算ユニット、1つまたは複数のメモリ、キャッシュ、およびレジスタを含み得る。

#### 【0051】

[0063]GPU12は、グラフィックス処理パイプライン24における頂点シェーダステージ、ハルシェーダステージ(a hull shader stage)、ドメインシェーダステージ、ジオメトリシェーダステージ、およびピクセルシェーダステージのうちの1つまたは複数を実行するために、シェーダユニット46にコマンドを送ることによって、頂点シェーディング、ハルシェーディング、ドメインシェーディング、ジオメトリシェーディング、ピクセルシェーディング、および同様のことなどの様々なシェーディング動作を実行するようにシェーダユニット46を指示し得る。いくつかの例では、GPUドライバ22は、GPU12内に含まれる1つまたは複数のプログラマブルシェーダユニット上にシェーダプログラムをダウンロードするように構成され得る。シェーダプログラムは、例えば、OpenGLシェーディング言語(GLSL)、上位レベルシェーディング言語(HLSL)、Cg(C for Graphics)シェーディング言語などの、上位レベルシェーディング言語で記述され得る。コンパイルされたシェーダプログラムは、GPU12内のシェーダユニット46の動作を制御する1つまたは複数の命令を含み得る。例えば、シェーダプログラムは、頂点シェーダステージの機能(functions)を行うためにシェーダユニット46によって実行され得る頂点シェーダプログラム、ハルシェーダステージの機能を行うためにシェーダユニット46によって実行され得るハルシェーダプログラム、ドメインシェーダステージの機能を行うためにシェーダユニット46によって実行され得るドメインシェーダプログラム、ジオメトリシェーダステージの機能を行うためにシェーダユニット46によって実行され得るジオメトリシェーダプログラム、および/またはピクセルシェーダの機能を行うためにシェーダユニット46によって実行され得るピクセルシェーダプログラムを含み得る。頂点シェーダプログラムは、プログラマブル頂点シェーダユニットまたは

10

20

30

40

50

統合型 (unified) シェーダユニットの実行を制御し得、1つまたは複数の頂点当たり (per-vertex) の動作を指定する命令を含む。

#### 【0052】

[0064] いくつかの例では、生ベイダー画像データは、システムメモリ 10 へ転送され得る。いくつかの例では、デバイス 800 は、生ベイダー画像データを提供する画像センサを有するデジタルカメラに結合され得るか、それを含み得るか、またはその一部であり得、ここで、生ベイダー画像データは、システムメモリ 10 に送信され得る。いくつかの例では、システムメモリ 10 における生ベイダー画像データは、キャッシュ 30 に送信され、キャッシュ 30 に記憶され得る。

#### 【0053】

[0065] テクスチャパイプライン 23 は、テクスチャリング機能 (functions) を実行するハードウェアユニットのプログラマブルパイプラインである。テクスチャパイプライン 23 は、シェーダプロセッサ 48 と通信状態にある。いくつかの例では、テクスチャパイプライン 23 は、ローカルキャッシュ 31 を含み得る。いくつかの例では、ローカルキャッシュ 31 は、レベル 1 キャッシュである。この例では、ローカルキャッシュ 31 が「レベル 1 キャッシュ」であることは、メモリ転送動作が実行されるときにローカルキャッシュ 31 が最初にチェックされて、レベル 1 キャッシュにおいてキャッシュミスが存在した場合にのみ、他のロケーションがチェックされることを意味する。

#### 【0054】

[0066] いくつかの例では、テクスチャパイプライン 23 は、図 6 のプロセス 630 の動作 (acts) のような、動作 (acts) を実行し得る。いくつかの例では、テクスチャパイプライン 23 は、いくつかの例における図 6 のプロセスに従って、キャッシュ 30 から第 1 のラインの生ベイダーデータ、およびキャッシュ 30 から第 2 のラインの生ベイダーデータを受け取り、複数のテクセルを提供するために、別個の対応するテクセルとして、第 1 のラインの生ベイダーデータおよび第 2 のラインの生ベイダーデータの複数の重複しない  $2 \times 2$  配列の各  $2 \times 2$  配列をマッピングし、複数のテクセルのうちの少なくとも 1 つに對して少なくとも 1 つの動作を実行し得る。

#### 【0055】

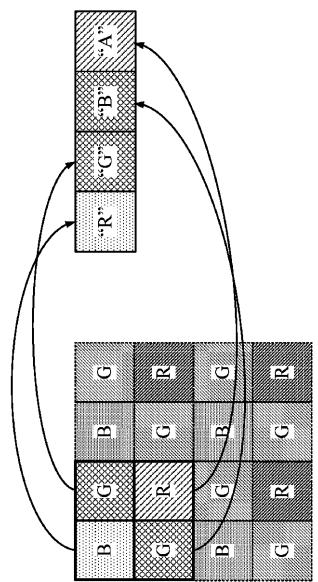

[0067] 例えば、いくつかの例では、テクスチャパイプライン 23 は、生ベイダー画像データの  $2 \times 2$  画素のセットにアクセスするために、キャッシュ 30 から 2 つのラインの生ベイダー画像データを読み取る。次に、テクスチャパイプライン 23 は、例えば、図 9 に示される（および図 9 - 図 11 と併せて、直後に続くセクションでより詳細に説明される）手法で、キャッシュ 30 からの生データにおける各  $2 \times 2$  B G G R（青緑緑赤）パターンの画素を、単一のテクセルの「R G B A」フォーマットにマッピングし得る。このようにして、各  $2 \times 2$  ベイダーパターンは、単一の「R G B A」色として扱われる。

#### 【0056】

[0068] 図 9 は、ベイダーパターンをテクセルにマッピングする例を例示する概念図である。いくつかの例では、入力データは、生ベイダー MIP 1 データであり、また、他の例では、入力データは、例えば、代わりに 8 ビットのフォーマットまたは 16 ビットのフォーマットである、MIP 1 フォーマットでない生ベイダーデータである。いくつかの例では、 $2 \times 2$  ベイダーパターンからのデータは、例えば、いくつかの例では、図 9 に示されるように、常に「R」として左上をマッピングし、常に「G」として右上をマッピングするなどのように、常に同じ手法でマッピングされる。

#### 【0057】

[0069] 示されるように、ベイダースウィズリングを実行するために、テクスチャパイプラインは、各  $2 \times 2$  パターンの画素が別個のテクセルにマッピングされることができるように、一度に 2 つのラインのデータを受け取る。対照的に、従来、各画素は、別個のテクセルであり、したがって、従来、一度に 1 つのラインのデータのみが受け取られる必要があった。

#### 【0058】

10

20

30

40

50

[0070] テクスチャパイプラインは、ベイヤーデータが、 $2 \times 2$  BGGR（青緑緑赤）ベイヤーパターンとして知られるフォーマットである、図9に例示される例で示され、また図1にも例示されたような、典型的なベイヤーフォーマットにおける $2 \times 2$ 配列当たり2つの緑画素、1つの赤画素、および1つの青画素などの、 $2 \times 2$ 配列関数(function)でパターン化されるので、 $2 \times 2$ 配列のためのベイアスウィズリングを実行する。しかしながら、他のベイヤーパターンが本開示の技法に従って使用され得、それに限定されるものではないが、RGGB（赤緑緑青）、GBRG（緑青赤緑）、GRBG（緑赤青緑）、RGBC（赤青緑クリア）、およびRGBW（赤青緑白）を含む。RGBCおよびRGBWベイヤーフォーマットは、BGGRベイヤーパターンと同様に $2 \times 2$ 配列でパターン化され、したがって、これらフォーマットの各々は、本開示の技法によるここで説明されるようなベイヤー画素の各 $2 \times 2$ 配列を単一のテクセルにマッピングするベイアスウィズリングから利益を得る。

10

## 【0059】

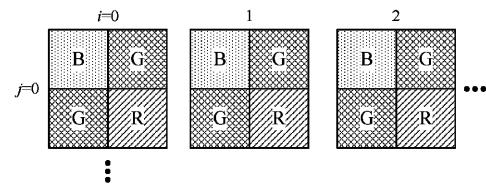

[0071] 図10は、図9のマッピングされたテクセルのアドレス指定を例示する概念図である。いくつかの例では、この場合のベイヤー順序における画像座標(i, j)アドレス指定は、図10に示されるとおりである。例示されるように、テクセルのテクスチャの幅および高さは、標準ベイヤーテクセルフォーマットの半分になり得る。各テクセルインデックスは、4つの色値の $2 \times 2$ マトリクスを含む。

20

## 【0060】

[0072]  $2 \times 2$ ベイヤー画素を対応するRGBAテクセルにマッピングした後、いくつかの例では、テクスチャパイプラインは、これらテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行する。テクスチャパイプラインは、メモリフェッチ当たり、4つの色値の $2 \times 2$ マトリクスを返す。

## 【0061】

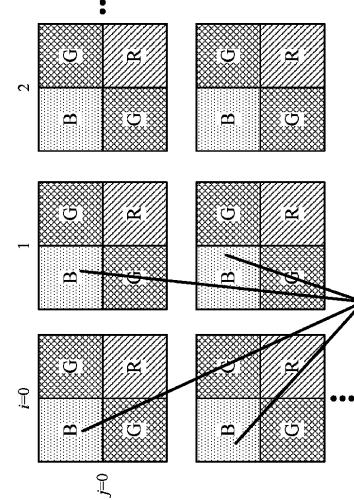

[0073]さらなる例として、ベイヤービニングは、テクスチャパイプラインのバイリニアフィルタリング能力を使用して実行され得、ここで、ベイヤービニングは、テクスチャパイプラインによって実行されるバイリニアフィルタリング動作を含み得る。テクスチャパイプラインはまた、RGBAテクセルに対して読み取りのような動作を実行し得る。他の例では、テクスチャパイプラインは、適応型ベイヤーフィルタリングおよび/またはベイヤー統計(Adaptive Bayer Filtering and/or Bayer statistics)を実行し得、ここで、適応型ベイヤーフィルタリングおよび/またはベイヤー統計は、RGBAテクセルのうちの1つまたは複数に対して実行され得る「Gather 4」のような収集動作を含み得る。いくつかの例では、Gather 4動作は、4つのロードではなく、1つロードで所望のチャネルをフェッチするために使用され得る。このような収集動作の例が、図11に例示される。

30

## 【0062】

[0074] 図11は、テクセルに対して収集動作を実行するテクスチャパイプラインの例を例示する概念図である。図11は、 $2 \times 2$ ベイヤー配列からスウィズリングされた「RGBA」テクセルに対するテクスチャパイプラインの動作Gatherの例の影響(effect)を例示する。具体的には、図11は、Bチャネルに対して実行される収集動作を例示する。上記で説明されたように、各別個のテクセルは、動作が個々のベイヤー画素のレベルではなく、テクセルのレベルで実行されるように、各セットのアドレス座標が、単一のベイヤー画素ではなく、 $2 \times 2$ ベイヤー配列テクセル全体を指し示す、別個の $2 \times 2$ ベイヤー配列である。例示される例で示されるように、収集動作の例は、4つの隣接する $2 \times 2$ ベイヤー配列テクセルの各々から $2 \times 2$ ベイヤーパターンの単一のチャネルをフェッチする。テクスチャパイプラインはまた、ベイヤーデータに対して実行されることが可能なその他任意の機能を実行し得、特に、最近点サンプリング(Nearest and Point Sampling)を含み、これは、ベイヤーデータが、個々の画素のレベルではなく、 $2 \times 2$ 配列の画素のレベルで動作されるという事実を除いて、従来の内容(matter)で $2 \times 2$ ベイヤー配列に対して実行され得、これは動作をより効率的にする。

40

50

## 【0063】

[0075]上記および以下で説明されるように、バイリニアフィルタリングはまた、 $2 \times 2$  ベイナー配列からスウィズリングされた「RGB A」テクセルに対して実行されることができる。バイリニアフィルタリングは、それによって画素値が、同じ色の隣接する画素値に基づいて平均化されるプロセスである。リニアフィルタリングは、同じラインにおける隣接する画素値に基づく平均化を指す（したがって、水平に隣接する画素または垂直に隣接する画素のいずれかが、リニアフィルタリングで平均化される）。バイリニアフィルタリングは、垂直に隣接するものと水平に隣接するものとの両方にに基づいて画素値を平均化することを指す。バイリニアフィルタリングの使用は、隣接する画素に基づいて平均化することによって、アーティファクトをよりゆるやか（less severe）にし、その結果、外れ値を有する誤りのある画素の影響を低減させることによって、視覚アーティファクトの低減を達成する。

## 【0064】

[0076]バイリニアフィルタリングは、テクスチャパイプラインのバイリニアフィルタリング機能を利用するため隣接する画素を平均化するとき、著しく少ないロードが必要とされるので、 $2 \times 2$  ベイナー配列からスウィズリングされた「RGB A」テクセルにより（with）、著しくより効率的である。

## 【0065】

[0077]図12は、実例的なデバイス1200を例示する機能ブロック図であり、これは、図8のシステム800の一部として用いられ得る。デバイス1200は、レベル2キャッシュ1230、テクスチャパイプライン1223およびシェーダプロセッサ1248を含み、これらは、それぞれ図8のキャッシュ30、パイプライン23、およびシェーダプロセッサ48の例として用いられ得る。テクスチャパイプライン1223は、アンパックおよびベイースウィズルブロック1271、レベル1キャッシュ1231、フォーマット変換ブロック1272、およびバイリニア最近gather4（bilinear nearest gather4）ブロック1273を含む。キャッシュ1231は、図8のキャッシュ31の例として用いられ得る。図12に示されるように、アンパックおよびベイースウィズルブロック1271、レベル1キャッシュ1231、フォーマット変換ブロック1272、およびバイリニア最近gather4ブロック1273は、全てテクスチャパイプライン1223に存在する。

## 【0066】

[0078]いくつかの例では、ブロック1271は、ブロック1271に提供される画像データがMIP1データであるか否かを認識し（すなわち、画像データがMIP1フォーマットであるかどうかについての決定を行い）、画像データがMIP1生データである場合、ブロック1271におけるハードウェアを介してMIP1生データをアンパックするように構成されたハードウェアを含む。ブロック1271は、ハードウェアを含むアンパッキング回路であり得る。デバイス1200のいくつかの例は、MIP1パックされたベイーデータまたはアンパックされたベイナー画像のいずれかとして生ベイーデータを送ることが可能であるカメラと連携して使用され、したがって、デバイス1200は、MIP1パックされたベイーデータおよびアンパックされたベイーデータの両方を効率的にサポートする。いくつかの例では、正規化データタイプおよび整数データタイプの両方が、ブロック1271によってサポートされる。いくつかの例では、ブロック1271は、16ビットのデータフォーマット（すなわち、画素当たり16ビット）にMIP1生データをアンパックする。このようにして、生ベイーミップ1データは、ブロック1271がアンパッキングおよびベイースウィズリングを実行した後、テクセル当たり64ビット（4つの16ビット画素）にアンパックされる。他の例では、ブロック1271は、16ビットのフォーマット以外の適切なフォーマットにMIP1生データをアンパックし得る。

## 【0067】

[0079]いくつかの例では、テクスチャパイプライン1223は、異なるタイプの処理用

10

20

30

40

50

の異なるタイプのテクスチャを識別するために、「テクスチャデータタイプ」または単に「テクスチャタイプ」と呼ばれるものを利用し、様々なテクスチャに、テクスチャに従って適切なテクスチャタイプを割り当て、その後、識別されたテクスチャデータタイプに基づいてグラフィック処理機能を実行する。しかしながら、いくつかの例では、テクスチャパイプライン1223におけるハードウェアによって実行される機能は、テクスチャを實際には表さないデータにテクスチャデータタイプを割り当てるこことによってアクセスされ得、したがって、テクスチャパイプライン1223におけるハードウェアは、割り当られたテクスチャデータタイプに基づいて、このデータに対して機能を実行することができる。いくつかの例では、新しいテクスチャデータタイプが、生画像データに対して処理を実行するために、テクスチャパイプライン1223のために割り当られる。例えば、いくつかの例では、MIP1生データは、1つ（または複数）の別個のテクスチャデータタイプである。テクスチャパイプライン1223は、全てのデータフォーマットについて、テクスチャとして読み取りアクセスを提供するように構成される。

#### 【0068】

[0080]いくつかの例では、ブロック1271は、ブロック1271内に内蔵キャッシュを含む。いくつかの例では、レベル2キャッシュ1230からの応答が、将来のレベル1キャッシュミスのために、ブロック1271の内蔵キャッシュに記憶される。いくつかの例では、レベル1キャッシュ1231におけるキャッシュミスは、アドレスをタグとして使用してブロック1271における内蔵キャッシュを最初にチェックするであろう。このようにして、いくつかの例では、ブロック1271の内蔵キャッシュは、それがレベル1キャッシングとレベル2キャッシングの中間であるので、レベル1.5キャッシュとして効果的に動作する。1271におけるキャッシュの使用は、いくつかの例では、レベル2キャッシュ1230が、アンパックされたMIP1データを含むので、効率を増大させる。ブロック1271におけるレベル1.5キャッシュが使用されない場合には、レベル1ローカルキャッシュ1231のキャッシュミスに際して、レベル2キャッシュ1230におけるデータが、密にパックされたフォーマットであり、したがって、アラインされていないので、レベル2キャッシュ1230におけるキャッシュラインへの複数のアクセスが必要とされ得る。ブロック1271のレベル1.5キャッシュにおけるデータがアンパックされている、ブロック1271におけるレベル1.5キャッシュを使用することによって、レベル2キャッシュ1230におけるアラインされていないデータへのフェッチの回数は低減される。また、従来、レベル2キャッシュ1230は、スプリッティング（splitting）の要求（例えば、アラインされていないデータをアラインする要求）を扱うであろう。しかしながら、ブロック1271がアンパッキングを実行するので、レベル2キャッシュ1230は、スプリッティングの要求を扱う必要がなく、これは、レベル2キャッシュ1230の効率を増大させる。

#### 【0069】

[0081]生MIP1データをアンパックするために、（図8の）グラフィックスメモリ40を使用することが可能であるが、これは、MIP1データが密にパックされており、したがって、アラインされていないので、追加の同期を必要とする。アンパックされた画素を保持するレベル1キャッシュ1231を用いて（with）、テクスチャパイプライン1223によって実行されるMIP1アンパッキングは、データが利用可能であることを確実にするための（図8の）グラフィックスメモリ40との同期を必要とすることなく、テクスチャパイプライン1223における複数のワークアイテムにわたって生MIP1画像データのアンパックされた画素を共有することを可能にする。特にレベル1キャッシュ1231からデータを受け取ることは、生画像データに対する処理が並列に行われるように、テクスチャパイプライン1223における複数のワークアイテムによるアクセスのためにアンパックされた画素を保持することを可能にし、これは増大された効率を可能にする。また、上記で説明された階層的なキャッシュ構造は、上述された理由から、増大された効率を可能にする。

#### 【0070】

10

20

30

40

50

[0082] いくつかの例では、フォーマット変換ブロック 1272 は、データを F P (浮動小数点) フォーマットに変換する。ブロック 1273 は、図 11 に関する説明において上記で説明されたように、バイリニア、最近点サンプリング、および G a t h e r 4 機能などの様々な機能をテクセルに対して実行し得る。

#### 【 0 0 7 1 】

[0083] 様々な例では、テクスチャパイプライン 1223 は、B のみ、G のみ、および R のみの画素をフェッチするために、マッピングされたベイヤー R G B A テクセルに対してテクスチャ収集動作を使用し得る。追加で、テクスチャパイプライン 1223 は、B、G、および R チャネルに別々に適用され得るバイリニアフィルタリングを適用し得る。

#### 【 0 0 7 2 】

[0084] 上記で説明されたように、ベイヤースウィズリングにより、単一の動作は、一度に 4 つのベイヤー画素に対して動作が (テクスチャパイプライン 1223 によって) 実行されることを効果的に可能にし得る。例えば、ベイヤースウィズル後の R G B A テクセルに対する読み取り動作は、一度に 1 つのベイヤー画素ではなく、一度に 4 つのベイヤー画素を効果的に読み取り、G a t h e r 4 動作は、4 つのロードではなく、1 つのロードにおいて所望のチャネルをフェッチするために使用され得、以下同様である。

#### 【 0 0 7 3 】

[0085] いくつかの例では、デバイス 1200 は、様々な機能が A P I を介してアクセス可能になるように、それによってそれが、A P I を介して、ブロック 1271 によって実行されるアンパッキング機能およびベイヤー 2 × 2 画素から R G B A テクセルへのマッピング (すなわち、ベイヤースウィズリング) を含む、ブロック 1271 の様々な機能を実行することが可能である A P I を (例えば、フレームワーク拡張を介して) 提供する。したがって、いくつかの例では、ブロック 1271 は、テクスチャタイプを介してではなく、A P I に応答してアンパッキングを実行し得る。いくつかの例では、A P I は、テクスチャタイプの代わりに使用され得、一方で、他の例では、テクスチャタイプと A P I 拡張の両方が使用され得るとともに、A P I 拡張は、テクスチャデータを含む。他の例では、テクスチャパイプライン 1223 は、アンパッキング機能およびベイヤースウィズル機能のためにテクスチャデータタイプを使用する。いくつかの例では、A P I は、テクスチャタイプの代わりに使用され得、一方で、他の例では、テクスチャタイプと A P I 拡張の両方が使用され得るとともに、A P I 拡張は、テクスチャデータを含む。他の例は、A P I ではなく、テクスチャタイプを使用し得る。いくつかの例では、シェーダプロセッサ 1248 は、デモザイキング動作を実行するためにテクセルをフェッチし得る。

#### 【 0 0 7 4 】

[0086] いくつかの例では、シェーダプロセッサ 1248 は、その後、さらなる処理のために画像信号プロセッサ (I S P) (図示せず) に画像データを送信し得る。M I P I アンパッキングおよびベイヤースウィズリングを含む、テクスチャパイプライン 1223 におけるハードウェアによって実行される様々な機能、およびアンパックされた「R G B A」テクセルに対して実行される様々な動作 (特に、収集機能およびバイリニアフィルタリングを含む) は、I S P によって実行される画像信号処理より前に実行される画像前処理として機能し得る。ここで説明されるテクスチャパイプライン 1223 におけるハードウェアによって実行される前処理は、特に、P D A F (位相検出オートフォーカス)、R G B C (赤緑青クリア)、インターリーブドハイダイナミックレンジ (i H D R)、コンピュテーショナルフォトグラフィ、およびライトフィールドコンピュテーションと併せると、これらのアプリケーションが、M I P I アンパッキングおよび / またはバイリニアフィルタを使用するまたはそれらから利益を得て、したがって、より効率的な M I P I アンパッキングおよび / またはより効率的なバイリニアフィルタリングから利益を得るので、特に有用であり得る。テクスチャパイプライン 1223 におけるハードウェアによって実行される様々な機能はまた、後処理として行われることができる。すなわち、機能が I S P で実行された後、画像データは、上記に説明された様々な動作の実行のために、テクスチャパイプライン 1223 に送られることができる。

10

20

30

40

50

## 【0075】

[0087]図13は、実例的なデバイス1302の機能的な態様の例を示す機能ブロック図であり、これは、さらなる詳細において、カメラ1323および図7のデバイス2の一部の例として用いられ得る。GPU1312は、図7のGPU12の例として用いられ得る。いくつかの例では、生バッファ(raw buffers)1354およびYUVバッファ1358は、各々が図8のシステムメモリ10の一部の例である。図13は、正確な構造ではなく、実例的な機能プロセスフローを示す機能ブロック図であり - 例えば、GPU1312は、図13において2度示されている - これは2つのGPUがあるのではなく、例示される特定の例では、図13は、機能ブロック図であり、同じGPU1312が機能プロセスフローにおける2つの別個のポイントにおいて機能を実行するからである。

10

## 【0076】

[0088]カメラ1323は、(例えば、現代のスマートフォン上に配置されるような)主センサ1350およびフロントセンサ1352を含む1つまたは複数のカメラセンサを含み得る。(例えば、MIPPI0ペイヤーパターンフォーマットにおける)センサ1350および/またはセンサ1352によって生成される生センサデータは、生バッファ1354に記憶され得る。生センサデータは、1つまたは複数のカメラシリアルインターフェース(CSI)デコーダCSI-Dによって生バッファ1354にルーティングされ得る。CSIデコーダCSI-Dは、統計およびダウンスケーラユニットを組み込み得る。本開示の技法によると、GPU1312は、GPU1312におけるテクスチャパイプラインを使用して、生センサデータをアンパックおよび/またはフィルタリングし、アンパックされたデータを生バッファ1354に記憶するように構成され得る。その後、アンパックされたデータは、圧縮されたフォーマット(例えば、JPEG)で画像ファイルを生成するために、画像信号プロセッサ1356によって使用され得る。その後、圧縮されたカメラデータは、YUVバッファ1358に記憶され得る。その後、このようなデータは、GPU1312、図7のディスプレイプロセッサ23、または図7のCPU6によってさらに操作され、および/または図7のディスプレイ18上に表示され得る(上記で説明されたように、図13のデバイスは、図13のデバイス2の一部として用いられ得る)。

20

## 【0077】

[0089]例に依存して、ここで説明された任意の技法のある特定の動作(acts)またはイベントは、異なるシーケンスで実行されることができ、概して追加、統合、または省略され得る(例えば、すべての説明された動作(acts)またはイベントは、これら技法の実施に必ずしも必要ではない)ことが認識されるべきである。さらに、ある特定の例では、動作(acts)またはイベントは、順次ではなく、例えば、マルチスレッド処理、割込み処理、または複数のプロセッサを通じて、同時並行(concurrently)に実行され得る。

30

## 【0078】

[0090]1つまたは複数の例では、説明された機能は、ハードウェア、ソフトウェア、ファームウェア、またはこれらの任意の組合せでインプリメントされ得る。ソフトウェアでインプリメントされる場合、これら機能は、コンピュータ可読媒体上で1つまたは複数の命令またはコードとして記憶または送信され、ハードウェアベースの処理ユニットによって実行され得る。コンピュータ可読媒体は、例えば、通信プロトコルに従って、1つの場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体、またはデータ記憶媒体のような有形の媒体に対応するコンピュータ可読記憶媒体を含み得る。

40

## 【0079】

[0091]このように、コンピュータ可読媒体は一般に、(1)それ自体が信号を伝搬することを含まない有形のコンピュータ可読記憶媒体、または(2)信号または搬送波のような通信媒体に対応し得る。データ記憶媒体は、本開示で説明された技法のインプリメンテーションのための命令、コードおよび/またはデータ構造を取り出すために、1つまたは複数のコンピュータまたは1つまたは複数のプロセッサによってアクセスされることができる任意の利用可能な媒体であり得る。コンピュータプログラム製品は、コンピュータ可

50

読媒体を含み得る。

【0080】

[0092]限定ではなく例として、このようなコンピュータ可読記憶媒体は、RAM、ROM、EEPROM、CD-ROMまたは他の光ディスク記憶装置、磁気ディスク記憶装置、または他の磁気記憶デバイス、フラッシュメモリ、あるいは、データ構造または命令の形式で所望のプログラムコードを記憶するために使用されることができ、かつコンピュータによってアクセスされることができるその他任意の媒体を備えることができる。また、任意の接続は、厳密にはコンピュータ可読媒体と称される。例えば、命令が、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線(DSL)、または赤外線、無線、およびマイクロ波などのワイヤレス技術を使用して、ウェブサイト、サーバ、またはその他の遠隔ソースから送信される場合には、この同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、または赤外線、無線、およびマイクロ波などのワイヤレス技術は、媒体の定義に含まれる。10

【0081】

[0093]しかしながら、コンピュータ可読記憶媒体およびデータ記憶媒体は、接続、搬送波、信号、または同様のものを含まないが、その代りに有形の記憶媒体に向けられることが理解されるべきである。ここで使用される場合、ディスク(disk)およびディスク(disks)は、コンパクトディスク(CD)、レーザーディスク(登録商標)、光ディスク、デジタル多目的ディスク(DVD)、フロッピー(登録商標)ディスクおよびBlu-ray(登録商標)ディスクを含み、ここでディスク(disks)は、通常磁気的にデータを再生し、一方ディスク(disks)は、レーザーを用いて光学的にデータを再生する。上記の組合せもまた、コンピュータ可読媒体の範囲内に含まれるべきである。20

【0082】

[0094]命令は、1つまたは複数のデジタルシグナルプロセッサ(DSP)、汎用マイクロプロセッサ、特定用途向け集積回路(ASIC)、フィールドプログラマブル論理アレイ(FPGA)、または他の同等の集積されたまたはディスクリートな論理回路などの、1つまたは複数のプロセッサによって実行され得る。したがって、ここで使用される場合、「プロセッサ」という用語は、任意の前述の構造またはここで説明された技法のインプリメンテーションに適したその他任意の構造を指し得る。加えて、いくつかの態様では、ここで説明された機能は、符号化および復号のために構成された専用のハードウェアモジュールおよび/またはソフトウェアモジュール内に提供され得、または、組み合わされたコーデックに組み込まれ得る。また、これら技法は、1つまたは複数の回路または論理要素において完全にインプリメントされることができる。30

【0083】

[0095]本開示の技法は、ワイヤレスハンドセット、集積回路(IC)またはICのセット(例えば、チップセット)を含む、幅広い様々なデバイスまたは装置でインプリメントされ得る。様々な構成要素、モジュール、またはユニットが、開示された技法を実行するように構成されたデバイスの機能的な態様を強調するために、本開示において説明されているが、異なるハードウェアユニットによる実現を必ずしも必要とするわけではない。むしろ、上記で説明されたように、様々なユニットは、コーデックハードウェアユニットにおいて組み合わせられるか、または、適切なソフトウェアおよび/またはファームウェアと併せて、上記で説明されたような1つまたは複数のプロセッサを含む、相互運用ハードウェアユニットの集合によって提供され得る。40

【0084】

[0096]様々な例が説明された。これらおよび他の例は、以下の特許請求の範囲内にある。

【図1】

【図2】

PRIOR ART

FIG. 2PRIOR ART

FIG. 1

【図3】

PRIOR ART

FIG. 3

【図4】

PRIOR ART

FIG. 4

【図5】

501

FIG. 5

【図6】

630

FIG. 6

【図7】

FIG. 7

【図8】

FIG. 8

【 四 9 】

FIG. 9

【 図 1 0 】

FIG. 10

【 図 1 1 】

FIG. 11

【図13】

**【手続補正書】**

【提出日】平成29年9月27日(2017.9.27)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

グラフィックス処理のための方法であって、

第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータを含むMIP

Iフォーマットにおける生ベイユーデータをキャッシュから受け取ることと、

グラフィックス処理ユニットのテクスチャパイプラインハードウェアを使用して、前記MIP Iフォーマットにおける前記生ベイユーデータをアンパックすることと、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複していない $2 \times 2$ 配列の各 $2 \times 2$ 配列を、前記テクスチャパイプラインハードウェアを用いてマッピングすることと、

前記複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行することと

を備える方法。

**【請求項2】**

前記少なくとも1つの動作は、ベイユーピニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも1つを含む、請求項1に記載の方法。

**【請求項3】**

前記複数のテクセルの各テクセルは、RGBAフォーマットである、請求項1に記載の方法。

**【請求項4】**

前記複数のテクセルのうちの少なくとも1つに対して前記少なくとも1つの動作を実行した後、画像信号プロセッサに前記複数のテクセルを送信することをさらに備える、請求項1に記載の方法。

**【請求項5】**

前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複していない $2 \times 2$ 配列の各 $2 \times 2$ 配列を前記マッピングすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、請求項1に記載の方法。

**【請求項6】**

前記MIP I Pフォーマットにおける前記生ベイユーデータを前記アンパックすることは、対応するテクスチャデータタイプに関連する、請求項1に記載の方法。

**【請求項7】**

前記MIP I Pフォーマットにおける前記生ベイユーデータを前記アンパックすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、請求項1に記載の方法。

**【請求項8】**

グラフィックス処理のためのデバイスであって、

キャッシュと、

第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータを含むMIP

Iフォーマットにおける生ベイユーデータを前記キャッシュから受け取り、

前記MIP I Pフォーマットにおける前記生ベイユーデータをアンパックし、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のライ

ンの生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングし、

前記複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行する

ように構成されたテクスチャパイプラインハードウェアと

を備えるデバイス。

#### 【請求項9】

前記テクスチャパイプラインハードウェアは、前記少なくとも1つの動作が、ベイユーピニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも1つを含むように構成される、請求項8に記載のデバイス。

#### 【請求項10】

前記テクスチャパイプラインハードウェアは、前記複数のテクセルの各テクセルが、RGB Aフォーマットであるように構成される、請求項8に記載のデバイス。

#### 【請求項11】

画像信号プロセッサをさらに備え、ここにおいて、前記画像信号プロセッサは、テクスチャプロセッサが前記複数のテクセルのうちの少なくとも1つに対して前記少なくとも1つの動作を実行した後に、前記複数のテクセルを受け取るように構成される、請求項8に記載のデバイス。

#### 【請求項12】

前記テクスチャパイプラインハードウェアは、アプリケーションプログラムインタフェースを介してアクセス可能である手法で、前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするように構成される、請求項8に記載のデバイス。

#### 【請求項13】

前記テクスチャパイプラインハードウェアは、前記MIPIPフォーマットにおける前記生ベイユーデータをアンパックすることが、対応するテクスチャデータタイプに関連するように構成される、請求項8に記載のデバイス。

#### 【請求項14】

前記テクスチャパイプラインハードウェアは、前記MIPIPフォーマットにおける前記生ベイユーデータをアンパックすることがアプリケーションプログラムインタフェースを介してアクセス可能であるように構成される、請求項8に記載のデバイス。

#### 【請求項15】

前記キャッシュは、レベル2キャッシュであり、前記テクスチャパイプラインハードウェアは、

ローカルキャッシュと、

前記レベル2キャッシュから前記第1のラインの生ベイユーデータ、および前記レベル2キャッシュから前記第2のラインの生ベイユーデータを受け取り、前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイユーデータおよび前記第2のラインの生ベイユーデータの前記複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングし、前記ローカルキャッシュに前記複数のテクセルを送信するように構成されたアンパッキング回路と

を含む、請求項8に記載のデバイス。

#### 【請求項16】

前記アンパッキング回路は、

前記生ベイユーデータがMIPIPフォーマットであるかどうかについての決定を行い、前記生ベイユーデータがMIPIPフォーマットであると決定された場合、前記生ベイユーデータをアンパックする

ようにさらに構成される、請求項15に記載のデバイス。

#### 【請求項17】

前記アンパッキング回路は、別個のキャッシュを含む、請求項1\_5に記載のデバイス。

【請求項 1\_8】

グラフィックス処理のためのデバイスであって、

第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータを含むMIP

Iフォーマットにおける生ベイユーデータを受け取るための手段と、

グラフィックス処理ユニットのテクスチャパイプラインハードウェアを使用して、前記

MIP Iフォーマットにおける前記生ベイユーデータをアンパックするための手段と、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のライン

の生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列を、前記テクスチャパイプラインハードウェアを用いてマッピング

するための手段と、

前記複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行する

ための手段と

を備えるデバイス。

【請求項 1\_9】

前記少なくとも1つの動作は、ベイユービニング動作、バイリニアフィルタ動作、読み

取り動作、または収集動作のうちの少なくとも1つを含む、請求項1\_8に記載のデバイス。

【請求項 2\_0】

前記複数のテクセルの各テクセルは、RGBAフォーマットである、請求項1\_8に記載

のデバイス。

【請求項 2\_1】

前記複数のテクセルのうちの少なくとも1つに対して前記少なくとも1つの動作を実行

した後、画像信号プロセッサに前記複数のテクセルを送信するための手段をさらに備える

、請求項1\_8に記載のデバイス。

【請求項 2\_2】

前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のライン

の生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複しない $2 \times 2$ 配列の各 $2 \times 2$ 配列を前記マッピングすることは、アプリケーションプログラム

インターフェースを介してアクセス可能である、請求項1\_8に記載のデバイス。

【請求項 2\_3】

前記MIP Iフォーマットにおける前記生ベイユーデータを前記アンパックすることは、

対応するテクスチャデータタイプに関連する、請求項1\_8に記載のデバイス。

【請求項 2\_4】

前記MIP Iフォーマットにおける前記生ベイユーデータを前記アンパックすることは、

アプリケーションプログラムインターフェースを介してアクセス可能である、請求項1\_8

に記載のデバイス。

【手続補正 2】

【補正対象書類名】明細書

【補正対象項目名】0084

【補正方法】変更

【補正の内容】

【0084】

[0096]様々な例が説明された。これらおよび他の例は、以下の特許請求の範囲の範囲内

にある。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

[C1] グラフィックス処理のための方法であって、

第1のラインの生ベイユーデータおよび第2のラインの生ベイユーデータを受け取ることと、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のライン

の生ベイユーデータおよび前記第2のラインの生ベイユーデータの複数の重複しない $2 \times 2$

× 2 配列の各 2 × 2 配列をマッピングすることと、

前記複数のテクセルのうちの少なくとも 1 つに対して少なくとも 1 つの動作を実行することと

を備える方法。

[ C 2 ] 前記少なくとも 1 つの動作は、ベイヤービニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも 1 つを含む、C 1 に記載の方法。

[ C 3 ] 前記複数のテクセルの各テクセルは、RGBA フォーマットである、C 1 に記載の方法。

[ C 4 ] 前記複数のテクセルのうちの少なくとも 1 つに対して前記少なくとも 1 つの動作を実行した後、画像信号プロセッサに前記複数のテクセルを送信することをさらに備える、C 1 に記載の方法。

[ C 5 ] 前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第 1 のラインの生ベイヤーデータおよび前記第 2 のラインの生ベイヤーデータの複数の重複してない 2 × 2 配列の各 2 × 2 配列を前記マッピングすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、C 1 に記載の方法。

[ C 6 ] 前記生ベイヤーデータが MIPIF フォーマットであるかどうかについての決定を行うことと、

前記生ベイヤーデータが MIPIF フォーマットであると決定された場合、前記生ベイヤーデータをアンパックするために、グラフィックス処理ユニットのテクスチャバイオペレーションにおけるハードウェアを用いることと

をさらに備える、C 1 に記載の方法。

[ C 7 ] 前記テクスチャバイオペレーションにおける前記ハードウェアによって実行される前記生ベイヤーデータを前記アンパックすることは、対応するテクスチャデータタイプを有する、C 6 に記載の方法。

[ C 8 ] 前記テクスチャバイオペレーションにおける前記ハードウェアによって実行される前記生ベイヤーデータを前記アンパックすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、C 6 に記載の方法。

[ C 9 ] グラフィックス処理のためのデバイスであって、

キャッシュと、

前記キャッシュから第 1 のラインの生ベイヤーデータ、および前記キャッシュから第 2 のラインの生ベイヤーデータを受け取り、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第 1 のラインの生ベイヤーデータおよび前記第 2 のラインの生ベイヤーデータの複数の重複してない 2 × 2 配列の各 2 × 2 配列をマッピングし、

前記複数のテクセルのうちの少なくとも 1 つに対して少なくとも 1 つの動作を実行する

ように構成されたテクスチャバイオペレーションと

を備えるデバイス。

[ C 10 ] 前記テクスチャバイオペレーションは、前記少なくとも 1 つの動作が、ベイヤービニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも 1 つを含むように構成される、C 9 に記載のデバイス。

[ C 11 ] 前記テクスチャバイオペレーションは、前記複数のテクセルの各テクセルが、RGBA フォーマットであるように構成される、C 9 に記載のデバイス。

[ C 12 ] 画像信号プロセッサをさらに備え、ここにおいて、前記画像信号プロセッサは、テクスチャプロセッサが前記複数のテクセルのうちの少なくとも 1 つに対して前記少なくとも 1 つの動作を実行した後に、前記複数のテクセルを受け取るように構成される、C 9 に記載のデバイス。

[ C 13 ] 前記テクスチャバイオペレーションは、アプリケーションプログラムインターフェースを介してアクセス可能である手法で、前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第 1 のラインの生ベイヤーデータおよび前記第 2 のラインの

生ベイアーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするよう構成される、C 9に記載のデバイス。

[C 14] 前記テクスチャパイプラインは、

前記生ベイアーデータがM I P Iフォーマットであるかどうかについての決定を行い、

前記生ベイアーデータがM I P Iフォーマットであると決定された場合、前記生ベイアーデータをアンパックする

ようにさらに構成される、C 9に記載のデバイス。

[C 15] 前記テクスチャパイプラインは、前記アンパックすることが、対応するテクスチャデータタイプを有するように、前記生ベイアーデータをアンパックすることが達成されるように構成される、C 14に記載のデバイス。

[C 16] 前記テクスチャパイプラインは、前記生ベイアーデータをアンパックすることがアプリケーションプログラムインタフェースを介してアクセス可能であるように構成される、C 14に記載のデバイス。

[C 17] 前記キャッシュは、レベル2キャッシュであり、前記テクスチャパイプラインは、

ローカルキャッシュと、

前記レベル2キャッシュから前記第1のラインの生ベイアーデータ、および前記レベル2キャッシュから前記第2のラインの生ベイアーデータを受け取り、前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイアーデータおよび前記第2のラインの生ベイアーデータの前記複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングし、前記ローカルキャッシュに前記複数のテクセルを送信するように構成されたアンパッキング回路と

を含む、C 9に記載のデバイス。

[C 18] 前記アンパッキング回路は、

前記生ベイアーデータがM I P Iフォーマットであるかどうかについての決定を行い、

前記生ベイアーデータがM I P Iフォーマットであると決定された場合、前記生ベイアーデータをアンパックする

ようにさらに構成される、C 17に記載のデバイス。

[C 19] 前記アンパッキング回路は、別個のキャッシュを含む、C 17に記載のデバイス。

[C 20] グラフィックス処理のためのデバイスであって、

第1のラインの生ベイアーデータおよび第2のラインの生ベイアーデータを受け取るための手段と、

複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイアーデータおよび前記第2のラインの生ベイアーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列をマッピングするための手段と、

前記複数のテクセルのうちの少なくとも1つに対して少なくとも1つの動作を実行するための手段と

を備えるデバイス。

[C 21] 前記少なくとも1つの動作は、ベイアービニング動作、バイリニアフィルタ動作、読み取り動作、または収集動作のうちの少なくとも1つを含む、C 20に記載のデバイス。

[C 22] 前記複数のテクセルの各テクセルは、R G B A フォーマットである、C 20に記載のデバイス。

[C 23] 前記複数のテクセルのうちの少なくとも1つに対して前記少なくとも1つの動作を実行した後、画像信号プロセッサに前記複数のテクセルを送信するための手段をさらに備える、C 20に記載のデバイス。

[C 24] 前記複数のテクセルを提供するために、別個の対応するテクセルとして、前記第1のラインの生ベイアーデータおよび前記第2のラインの生ベイアーデータの複数の重複してない $2 \times 2$ 配列の各 $2 \times 2$ 配列を前記マッピングすることは、アプリケーション

プログラムインターフェースを介してアクセス可能である、C 2 0 に記載のデバイス。

[ C 2 5 ] 前記生ベイヤーデータがM I P I フォーマットであるかどうかについての決定を行うための手段と、

前記生ベイヤーデータがM I P I フォーマットであると決定された場合、前記生ベイヤーデータをアンパックするために、グラフィックス処理ユニットのテクスチャパイプラインにおけるハードウェアを用いるための手段と

をさらに備える、C 2 0 に記載のデバイス。

[ C 2 6 ] 前記テクスチャパイプラインにおける前記ハードウェアによって実行される前記生ベイヤーデータを前記アンパックすることは、対応するテクスチャデータタイプを有する、C 2 5 に記載のデバイス。

[ C 2 7 ] 前記テクスチャパイプラインにおける前記ハードウェアによって実行される前記生ベイヤーデータを前記アンパックすることは、アプリケーションプログラムインターフェースを介してアクセス可能である、C 2 5 に記載のデバイス。

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                   | International application No<br>PCT/US2016/013468 |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------|------------------------------------------------------------------------------------|-----------------------|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>INV. G06T3/40<br>ADD.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>G06T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br><br>EPO-Internal, WPI Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category*</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="padding: 2px;">X</td> <td style="padding: 2px; vertical-align: top;">         MORGAN MC GUIRE: "Efficient, High-Quality Bayer Demosaic Filtering on GPUs", JOURNAL OF GRAPHICS TOOLS, ASSOCIATION FOR COMPUTING MACHINERY, NEW YORK, US, vol. 13, no. 4, 1 January 2008 (2008-01-01), pages 1-16, XP009189618, abstract<br/>         page 6, paragraph 1<br/>         -----<br/>         -/-/       </td> <td style="padding: 2px; text-align: center;">1-27</td> </tr> </tbody> </table> |                                                                                                                                                                                                                                                                                   |                                                   | Category* | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | MORGAN MC GUIRE: "Efficient, High-Quality Bayer Demosaic Filtering on GPUs", JOURNAL OF GRAPHICS TOOLS, ASSOCIATION FOR COMPUTING MACHINERY, NEW YORK, US, vol. 13, no. 4, 1 January 2008 (2008-01-01), pages 1-16, XP009189618, abstract<br>page 6, paragraph 1<br>-----<br>-/-/ | 1-27 |

| Category*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                | Relevant to claim No.                             |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MORGAN MC GUIRE: "Efficient, High-Quality Bayer Demosaic Filtering on GPUs", JOURNAL OF GRAPHICS TOOLS, ASSOCIATION FOR COMPUTING MACHINERY, NEW YORK, US, vol. 13, no. 4, 1 January 2008 (2008-01-01), pages 1-16, XP009189618, abstract<br>page 6, paragraph 1<br>-----<br>-/-/ | 1-27                                              |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| <input checked="" type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/> See patent family annex.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| * Special categories of cited documents :<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent but published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| *T* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention<br>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone<br>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art<br>"&" document member of the same patent family                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                   |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| Date of the actual completion of the international search<br><br>2 May 2016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Date of mailing of the international search report<br><br>11/05/2016                                                                                                                                                                                                              |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

| Name and mailing address of the ISA/<br>European Patent Office, P.O. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel: (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Authorized officer<br><br>Pierfederici, A                                                                                                                                                                                                                                         |                                                   |           |                                                                                    |                       |   |                                                                                                                                                                                                                                                                                   |      |

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2016/013468 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                           | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | "glTexImage2D - specify a two-dimensional texture image",<br>, 2006, pages 1-10, XP55266843,<br>Retrieved from the Internet:<br>URL: <a href="https://www.opengl.org/sdk/docs/man/html/glTexImage2D.xhtml">https://www.opengl.org/sdk/docs/man/html/glTexImage2D.xhtml</a><br>[retrieved on 2016-04-20]<br>page 3, paragraph 2<br>-----                                                                                                                      | 1-27                  |

| X         | PATRIK GOORTS ET AL: "Raw Camera Image Demosaicing using Finite Impulse Response Filtering on Commodity GPU Hardware using CUDA", SIGMAP AND WINSYS 2012, 1 January 2012 (2012-01-01), pages 96-101, XP55267938, Title; page 98, left-hand column, paragraph 3<br>page 99, left-hand column, paragraph 3<br>-----                                                                                                                                            | 1-27                  |

| A         | SHANE RYOO ET AL: "Optimization principles and application performance evaluation of a multithreaded GPU using CUDA", PROCEEDINGS OF THE 13TH ACM SIGPLAN SYMPOSIUM ON PRINCIPLES AND PRACTICE OF PARALLEL PROGRAMMING , PPOPP '08, 1 January 2008 (2008-01-01), pages 73-82, XP055042951, New York, New York, USA<br>page 77, left-hand column, last paragraph - page 78, left-hand column, paragraph 1<br>-----                                            | 1-27                  |

| A         | PATRIK GOORTS ET AL: "Optimal Data Distribution for Versatile Finite Impulse Response Filtering on Next-Generation Graphics Hardware Using CUDA", PARALLEL AND DISTRIBUTED SYSTEMS (ICPADS), 2009 15TH INTERNATIONAL CONFERENCE ON, IEEE, PISCATAWAY, NJ, USA, 8 December 2009 (2009-12-08), pages 300-307, XP031616972, page 300, left-hand column, paragraph 1 - right-hand column, paragraph 1<br>page 303, left-hand column, paragraph 2<br>-----<br>-/- | 1-27                  |

| 2         |                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

## INTERNATIONAL SEARCH REPORT

|                                                   |

|---------------------------------------------------|

| International application No<br>PCT/US2016/013468 |

|---------------------------------------------------|

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                                                                                                                                              | Relevant to claim No. |