(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3972270号

(P3972270)

(45) 発行日 平成19年9月5日(2007.9.5)

(24) 登録日 平成19年6月22日(2007.6.22)

(51) Int.C1.

F 1

|             |              |                  |      |       |      |

|-------------|--------------|------------------|------|-------|------|

| <b>G09G</b> | <b>3/20</b>  | <b>(2006.01)</b> | G09G | 3/20  | 622E |

| <b>G02F</b> | <b>1/133</b> | <b>(2006.01)</b> | G09G | 3/20  | 623U |

| <b>G09G</b> | <b>3/36</b>  | <b>(2006.01)</b> | G09G | 3/20  | 650B |

| <b>HO4N</b> | <b>5/66</b>  | <b>(2006.01)</b> | G09G | 3/20  | 660E |

|             |              |                  | GO2F | 1/133 | 550  |

請求項の数 4 (全 18 頁) 最終頁に続く

(21) 出願番号

特願平10-94508

(22) 出願日

平成10年4月7日(1998.4.7)

(65) 公開番号

特開平11-296129

(43) 公開日

平成11年10月29日(1999.10.29)

審査請求日

平成17年1月5日(2005.1.5)

(73) 特許権者 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100098785

弁理士 藤島 洋一郎

(72) 発明者 前川 敏一

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

(72) 発明者 野田 和宏

東京都品川区北品川6丁目7番35号 ソ

ニー株式会社内

審査官 福村 拓

最終頁に続く

(54) 【発明の名称】画素駆動回路および駆動回路一体型画素集積装置

## (57) 【特許請求の範囲】

## 【請求項 1】

異なる2つの方向に配列された複数の画素を駆動するための回路であって、前記2つの方向のうちの1の方向に沿って第1のパルス信号を複数画素分ずつ移動させながら順次出力するパルス移動手段と、

前記パルス移動手段から出力された第1のパルス信号を基に、前記2つの方向のうちの他の方向に沿って配列された画素列を個別に駆動するためのより多くの第2のパルス信号を生成する個別駆動パルス生成手段と、

前記パルス移動手段と前記個別駆動パルス生成手段との間に設けられ、パルス移動手段から個別駆動パルス生成手段に対して前記第1のパルス信号を供給するか否かを切替可能な切替手段と

を備えたことを特徴とする画素駆動回路。

## 【請求項 2】

前記切替手段は、表示切替信号に応じて、前記他の方向に沿って配列された画素列のうちの一部の画素列が選択的に非駆動状態となるように、前記第1のパルス信号を供給するか否かの切替を行う

ことを特徴とする請求項1記載の画素駆動回路。

## 【請求項 3】

異なる2つの方向に配列された複数の画素と、

前記2つの方向のうちの1の方向に沿って第1のパルス信号を複数画素分ずつ移動させ

10

20

ながら順次出力するパルス移動手段と、

前記パルス移動手段から出力された第1のパルス信号を基に、前記2つの方向のうちの他の方向に沿って配列された画素列を個別に駆動するためのより多くの第2のパルス信号を生成する個別駆動パルス生成手段と、

前記パルス移動手段と前記個別駆動パルス生成手段との間に設けられ、パルス移動手段から個別駆動パルス生成手段に対して前記第1のパルス信号を供給するか否かを切替可能な切替手段と

を備えたことを特徴とする駆動回路一体型画素集積装置。

【請求項4】

前記切替手段は、表示切替信号に応じて、前記他の方向に沿って配列された画素列のうちの一部の画素列が選択的に非駆動状態となるように、前記第1のパルス信号を供給するか否かの切替を行う

10

ことを特徴とする請求項3記載の駆動回路一体型画素集積装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、例えばマトリクス状に配置された画素を選択的に駆動するための画素駆動回路、およびそのような画素駆動回路を含んで構成された駆動回路一体型画素集積装置に関する。

【0002】

20

【従来の技術】

近年、CRT(陰極線管)に並ぶ画像表示装置として、液晶表示装置の普及が著しい。この装置は、水平方向および垂直方向に画素をマトリクス状に配置すると共に、水平および垂直方向のそれぞれについてシフトレジスタを配置して構成したもので、垂直方向のシフトレジスタから垂直方向選択パルスを垂直方向に順次転送しながら出力して画素ライン(水平方向に並んだ画素配列)を選択するごとに、水平方向のシフトレジスタから水平方向選択パルスを水平方向に順次転送しながら出力して垂直方向選択パルスにより選択された画素ラインの画素を水平方向に走査しながら順次選択するという動作を繰り返すことにより、全画素に信号を書き込むようになっている。

【0003】

30

ところで、この種の画像表示装置においては、CRTを用いた画像表示装置と同様に様々な規格の画像信号に対応し得るようにすべく、画像信号の種類に応じて表示領域のサイズを変化させることができるようにしたマルチスキャン対応の表示装置が知られている。この種の装置で用いられる方法には、全画面のうち表示を行わない非表示領域(例えば画面の上下部分)については、垂直方向選択パルスを供給しないようにして黒くすることにより、表示領域サイズを調整する方法がある。この方法によれば、画像信号自体に手を加える必要がないので、画像信号処理のための制御回路や画像メモリ等が不要であり、さほどコストアップを伴わずに済むという利点がある。

【0004】

【発明が解決しようとする課題】

40

上記した従来の画像表示装置では、垂直方向のシフトレジスタにおける各転送段は垂直方向の各画素ラインにそれぞれ対応して設けられており、垂直方向に1段ずつパルスを転送しながらこれを出力する構成となっていた。しかしながら、最近では、表示画像の高精細化の要請に伴って画素ピッチの一層の狭小化が求められると、従来のように1画素ライン分の幅のなかにシフトレジスタの1つの転送段の回路を配置しようとしても面積が不十分となり、実現は困難である。仮に、半導体素子の微細化技術の向上により、そのような高密度配置が可能になったとしても、各画素ラインごとにシフトレジスタの転送段を配置するようにした場合には、シフトレジスタ全体として必要なトランジスタ等の半導体素子の数を削減できないので、消費電流を低減できない。さらに、従来のように各画素ラインごとにシフトレジスタのパルス転送を行うようにした場合には、画素ラインの数を増加しよ

50

うとするとシフトレジスタの各転送段間の転送速度を高速化する必要が生じるため、各転送段の回路やその他の部分の回路を構成する半導体素子の動作速度をより高速化する（駆動周波数をより高くする）必要が生じる。

#### 【0005】

また、上記した従来のマルチスキャン対応の表示装置では、全画面のうち非表示領域の画素ラインへの選択パルス供給を停止させるために、各画素ラインごとに開閉用のスイッチ素子を設けるようになっていたので、各段ごとの素子数が増大し、駆動回路全体としての消費電流が増大する。特に、画素ピッチの一層の狭小化が求められている状況下では、上記のように1画素ライン分の幅のなかにシフトレジスタの1つの転送段の回路を配置することさえ困難であるところ、さらにスイッチ素子を各画素ラインごとに配置することは不可能に近い。

#### 【0006】

このように、従来の画像表示装置では、現状以上に画素ピッチの狭小化と画素数の増大とを図ることが困難であると共に、駆動回路を構成する素子を高速化する必要があるという問題があった。

#### 【0007】

本発明はかかる問題点に鑑みてなされたもので、その目的は、駆動用の構成素子の数の増加と動作速度のさらなる高速化とを必要とせずに、画素ピッチの狭小化と画素数の増大とを容易に実現することができる画素駆動回路および駆動回路一体型画素集積装置を提供することにある。

#### 【0008】

##### 【課題を解決するための手段】

本発明の画素駆動回路は、異なる2つの方向に配列された複数の画素を駆動するための回路であって、2つの方向のうちの1の方向に沿って第1のパルス信号を複数画素分ずつ移動させながら順次出力するパルス移動手段と、パルス移動手段から出力された第1のパルス信号を基に、2つの方向のうちの他の方向に沿って配列された画素列を個別に駆動するためのより多くの第2のパルス信号を生成する個別駆動パルス生成手段と、パルス移動手段と個別駆動パルス生成手段との間に設けられ、パルス移動手段から個別駆動パルス生成手段に対して第1のパルス信号を供給するか否かを切替可能な切替手段とを備えている。ここで、切替手段が、表示切替信号に応じて、他の方向に沿って配列された画素列のうちの一部の画素列が選択的に非駆動状態となるように第1のパルス信号を供給するか否かの切替を行うように構成することが可能である。

#### 【0009】

本発明の駆動回路一体型画素集積装置は、異なる2つの方向に配列された複数の画素と、2つの方向のうちの1の方向に沿って第1のパルス信号を複数画素分ずつ移動させながら順次出力するパルス移動手段と、パルス移動手段から出力された第1のパルス信号を基に、2つの方向のうちの他の方向に沿って配列された画素列を個別に駆動するためのより多くの第2のパルス信号を生成する個別駆動パルス生成手段と、パルス移動手段と個別駆動パルス生成手段との間に設けられ、パルス移動手段から個別駆動パルス生成手段に対して第1のパルス信号を供給するか否かを切替可能な切替手段とを備えている。ここで、切替手段が、表示切替信号に応じて、他の方向に沿って配列された画素列のうちの一部の画素列が選択的に非駆動状態となるように第1のパルス信号を供給するか否かの切替を行うように構成することが可能である。

#### 【0010】

本発明の画素駆動回路または駆動回路一体型画素集積装置では、パルス移動手段によって1の方向に沿って第1のパルス信号が複数画素分ずつ移動しながら順次出力されると共に、個別駆動パルス生成手段によって第1のパルス信号を基に2つの方向のうちの他の方向に沿って配列された画素列を個別に駆動するための第2のパルス信号が生成される。また、パルス移動手段と個別駆動パルス生成手段との間に切替手段が設けられているため、パルス移動手段から個別駆動パルス生成手段に対して第1のパルス信号を供給するか否か

10

20

30

40

50

を切り替えることが可能となり、これにより、上記の他の方向に沿って配列された画素列のうちの有効な画素列の範囲、すなわち、表示可能領域の切り替えが可能となる。この場合、切替手段では、例えば、表示切替信号に応じて他の方向に沿って配列された画素列のうちの一部の画素列が選択的に非駆動状態となるように、第1のパルス信号を供給するか否かの切替がなされる。

#### 【0011】

##### 【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して詳細に説明する。なお、以下の説明では、本発明を、画素部と画素駆動回路とを同一基板上に一体に形成したカラー液晶表示装置に適用する場合について説明する。

10

#### 【0012】

##### 【第1の実施の形態】

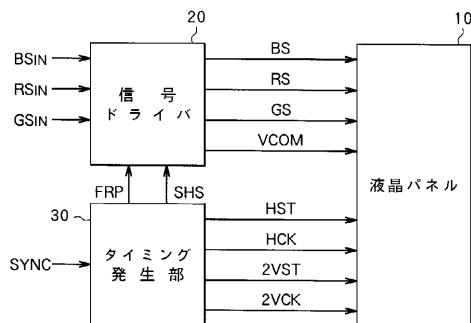

図1は本発明の一実施の形態に係るカラー液晶表示装置（以下、単に液晶表示装置という。）の概略構成を表すもので、いわゆるアクティブマトリクス方式で駆動されるものである。図1に示したように、この装置は、液晶パネル10と、信号ドライバ20と、タイミング発生部30とを備えている。液晶パネル10には、後述する画素部11（図2）等が搭載されている。信号ドライバ20は、入力されるビデオ入力信号BS<sub>IN</sub>, RS<sub>IN</sub>, GS<sub>IN</sub>に所定の信号変換を行って、液晶パネル10におけるB（青）、R（赤）、G（緑）の各色用画素（本図では図示せず）を駆動するためのビデオ信号BS, RS, GSを出力すると共に、液晶パネル10の図示しない対向電極に印加される共通電位信号VCOMを出力するようになっている。タイミング発生部30は、複合同期信号等の同期信号SYNCに基づいて各種のタイミング信号HST, HCK, 2VST, 2VCK, FRP, SHSを発生するようになっている。

20

#### 【0013】

ここで、HSTは、液晶パネル10の後述する水平方向シフトレジスタのスタートパルス（以下、Hスタートパルスという。）を示し、HCKは、水平方向シフトレジスタを駆動するクロックパルス（以下、Hクロックパルスという。）を示す。2VSTは、液晶パネル10の後述する垂直方向シフトレジスタのスタートパルス（以下、Vスタートパルスという。）を示し、2VCKは、垂直方向シフトレジスタを駆動するクロックパルス（以下、Vクロックパルスという。）を示す。また、FRPは、信号ドライバ20がビデオ入力信号BS<sub>IN</sub>, RS<sub>IN</sub>, GS<sub>IN</sub>を所定の直流電圧を中心とする交流のビデオ信号BS, RS, GSに変換するのに用いられる反転・非反転選択信号を示し、SHSは、信号ドライバ20がビデオ信号BS, RS, GSの位相を設定するのに用いるサンプルホールド信号を示す。

30

#### 【0014】

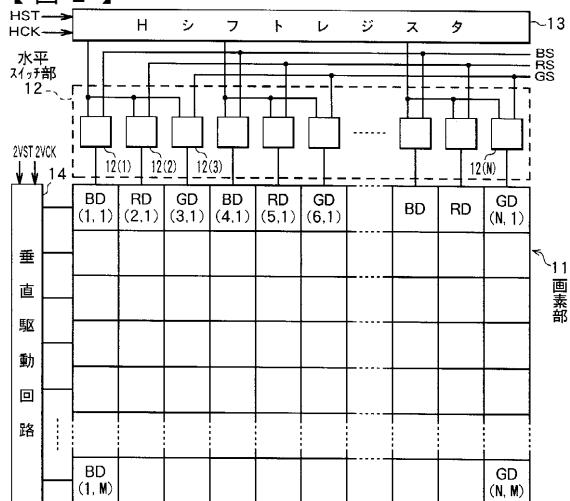

図2は液晶パネル10の一構成例を表すものである。この図に示したように、液晶パネル10は、画素部11と、水平スイッチ部12および水平方向シフトレジスタ13（以下、Hシフトレジスタ13という。）を含む水平駆動回路と、垂直方向シフトレジスタ141（以下、Vシフトレジスタ141という。本図では図示せず）を含む垂直駆動回路14とを備えている。Hシフトレジスタ13には、図1に示したHスタートパルスHSTおよびHクロックパルスHCKが入力され、垂直駆動回路14のVシフトレジスタには、図1に示したVスタートパルス2VSTおよびVクロックパルス2VCKが入力されるようになっている。

40

#### 【0015】

画素部11は、液晶セルやスイッチング素子等からなる画素をマトリクス状に配列して構成され、これらの各画素を選択的に駆動することにより画像を表示できるようになっている。スイッチング素子としては、例えば薄膜トランジスタ（TFT）等が用いられる。図2に示した例では、画素部11は、水平方向にN個の画素BD(1, j), RD(2, j), GD(3, j), ……, GD(N, j) [j = 1 ~ M]を配列すると共に、垂直方向にM個の画素BD(1, 1) ~ (1, M), RD(2, 1) ~ (2, M), GD(3, 1)

50

) ~ ( 3 , M ) , ..... , G D ( N , 1 ) ~ ( N , M ) を配列して構成されている。ここで、B D , R D , G D はそれぞれ青 , 赤 , 緑用の画素であることを示す。

【 0 0 1 6 】

水平スイッチ部 1 2 は、N 個の水平スイッチ 1 2 ( 1 ) ~ 1 2 ( N ) を含んで構成され、信号ドライバ 2 0 ( 図 1 ) から入力されたビデオ信号 B S , R S , G S を画素部 1 1 に選択的に供給する機能を有している。N 個の水平スイッチ 1 2 ( 1 ) ~ 1 2 ( N ) は 3 個ずつのグループに分けられている。各グループの 3 個の水平スイッチは H シフトレジスタ 1 3 の各転送段に共通 ( 並列 ) 接続されている。そして、これらのグループのそれぞれに対して、H シフトレジスタ 1 3 の各転送段から所定の時間間隔で水平方向選択パルスが順次供給されるようになっている。ここにいう所定の時間間隔は、タイミング発生部 3 0 ( 10 図 1 ) から H シフトレジスタ 1 3 に供給される H クロックパルス H C K の周期によって定まるものである。各グループの 3 個の水平スイッチには、それぞれに対応して、図 1 の 信号ドライバ 2 0 からビデオ信号 B S , R S , G S が供給されるようになっている。

【 0 0 1 7 】

H シフトレジスタ 1 3 は複数のパルス転送段からなり、各段から順次出力する水平方向選択パルスによって駆動対象の画素列 ( 垂直方向に延びる画素配列 ) を選択可能である。より具体的には、H シフトレジスタ 1 3 は、タイミング発生部 3 0 から供給される H スタートパルス H S T をトリガとして動作を開始し、H クロックパルス H C K によって定まる時間間隔で水平方向選択パルスを各転送段から順次出力することにより水平方向の画素選択走査を行うようになっている。水平スイッチ部 1 2 における各グループ内の 3 個の水平スイッチは、H シフトレジスタ 1 3 から水平方向選択パルスが供給されるごとに同時に開状態となり、ビデオ信号 B S , R S , G S を画素部 1 1 の対応する 3 つの画素列に並列に供給する。 20

【 0 0 1 8 】

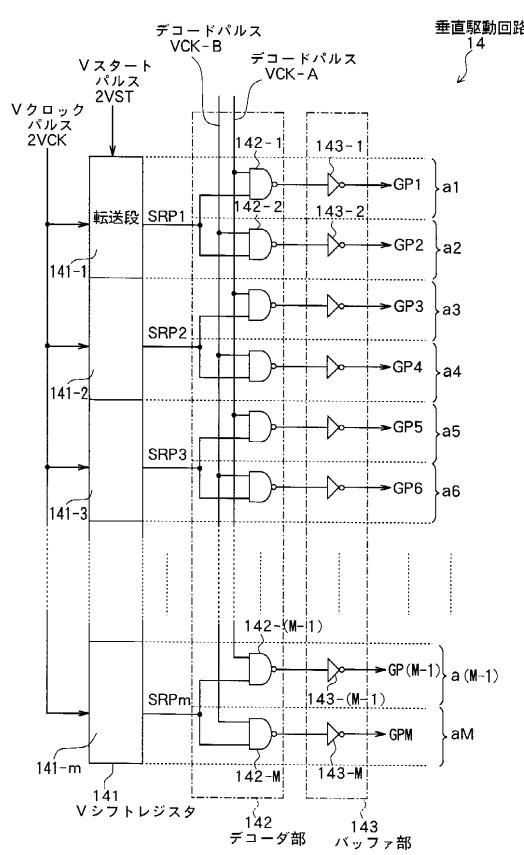

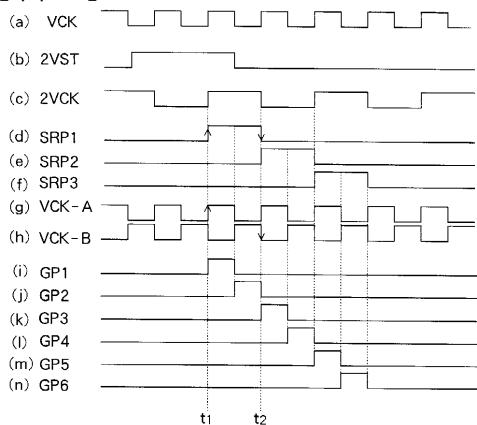

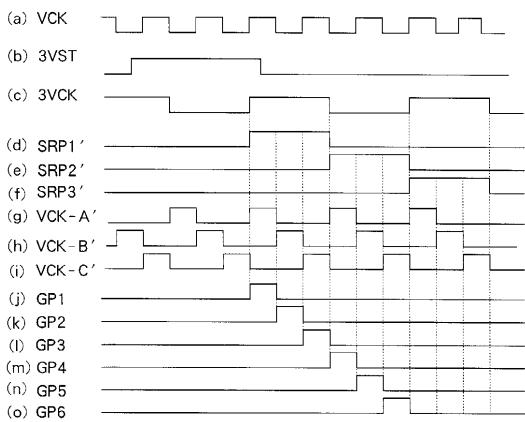

次に、図 3 ~ 図 5 を参照して、垂直駆動回路 1 4 の構成について説明する。ここで、図 3 は垂直駆動回路 1 4 の全体構成を表し、図 4 は図 3 の V シフトレジスタ 1 4 1 の構成を表し、図 5 は垂直駆動回路 1 4 における各種信号波形を表す。図 3 に示したように、垂直駆動回路 1 4 は、V シフトレジスタ 1 4 1 と、デコーダ部 1 4 2 と、バッファ部 1 4 3 とを含んで構成されている。

【 0 0 1 9 】

V シフトレジスタ 1 4 1 は複数のパルス転送段 1 4 1 - 1 ~ 1 4 1 - m から構成される。ここで、後述するように、m = M / 2 である。先頭のパルス転送段 1 4 1 - 1 には、図 1 のタイミング発生部 3 0 から、図 5 ( b ) に示したような V スタートパルス 2 V S T が供給され、また、各パルス転送段 1 4 1 - 1 ~ 1 4 1 - m には、タイミング発生部 3 0 から、図 5 ( c ) に示したような V クロックパルス 2 V C K が並列に入力されるようになっている。各パルス転送段 1 4 1 - 1 ~ 1 4 1 - m は、後述するように、1 個のインバータと V クロックパルス V C K に同期して動作する 2 個のクロックトインバータとを用いて構成され、相互に直列接続されている。図示のように、1 つのパルス転送段は、画素部 1 1 ( 図 2 ) における 2 つの画素ラインに対応して設けられている。より具体的には、パルス転送段 1 4 1 - 1 は画素ライン a 1 , a 2 に対応し、パルス転送段 1 4 1 - 2 は画素ライン a 3 , a 4 に対応し、パルス転送段 1 4 1 - m は画素ライン a ( M - 1 ) , a M に対応している。ここで、画素ライン a j ( j = 1 ~ M ) は、画素部 1 1 における画素 B D ( 1 , j ) ~ G D ( N , j ) からなる画素配列を示す。このような構成の V シフトレジスタ 1 4 1 は、タイミング発生部 3 0 から供給される V スタートパルス 2 V S T をトリガとして各転送段間のパルス転送動作を開始し、V クロックパルス 2 V C K によって定まる時間間隔で、各パルス転送段 1 4 1 - 1 ~ 1 4 1 - m から、それぞれ、図 5 ( d ) ~ ( f ) に示したようなシフトレジスタパルス S R P 1 ~ S R P m ( 但し、図 5 では S R P 1 ~ S R P 3 のみを図示 ) を順次出力するようになっている。ここで、V シフトレジスタ 1 4 1 が本発明における「パルス移動手段」に対応し、シフトレジスタパルス S R P 1 ~ S R P m が本発明における「第 1 のパルス信号」に対応する。 40 50

## 【0020】

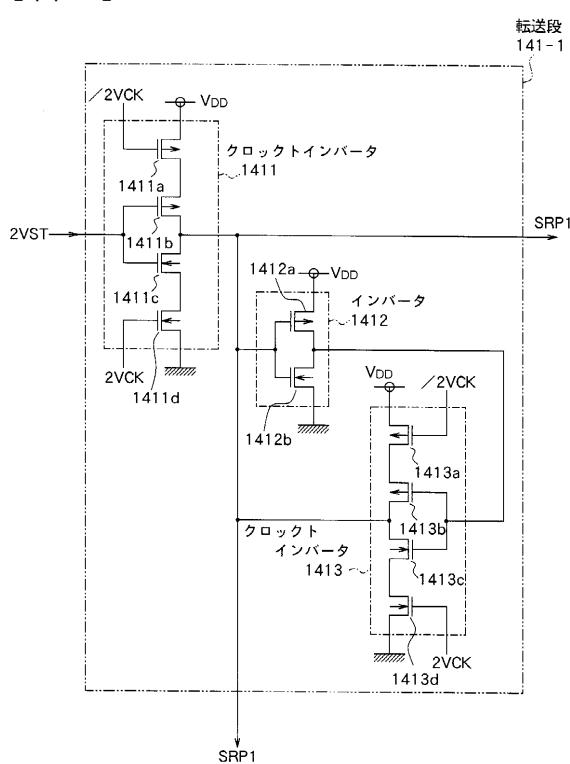

図4に示したように、Vシフトレジスタ141のパルス転送段141-1は、クロックトインバータ1411と、クロックトインバータ1411の出力端側に設けられたインバータ1412およびクロックトインバータ1413からなるラッチ回路とを含んでいる。

## 【0021】

クロックトインバータ1411は、2つのPMOS型のトランジスタ1411a, 1411bと、2つのNMOS型のトランジスタ1411c, 1411dとを含んで構成されている。トランジスタ1411a, 1411bのソース・ドレイン間は相互に接続され、また、トランジスタ1411c, 1411dのソース・ドレイン間も相互に接続されている。トランジスタ1411b, 1411cはCMOS構造をなし、両者のゲートにはVスタートパルス2VSTが入力されるようになっている。両者のドレインは相互に接続され、出力端として、次段のパルス転送段の入力端（パルス転送段141-2のトランジスタ1411b, 1411cのゲート）に接続されている。トランジスタ1411aのソースは電源ラインV<sub>DD</sub>に接続され、トランジスタ1411dのソースは接地接続されている。トランジスタ1411aのゲートにはVクロックパルス2VCKの反転信号である/2VCKが入力され、トランジスタ1411dのゲートにはVクロックパルス2VCKが入力されるようになっている。

## 【0022】

インバータ1412は、CMOS構成のトランジスタ1412a, 1412bによって構成されており、その入力端（トランジスタ1412a, 1412bのゲート）は、クロックトインバータ1411の出力端（トランジスタ1411b, 1411cのドレイン）に接続されている。トランジスタ1412aのソースは電源ラインV<sub>DD</sub>に接続され、トランジスタ1412bのソースは接地接続されている。

## 【0023】

クロックトインバータ1413は、クロックトインバータ1411と同様の構成であり、2つのPMOS型のトランジスタ1413a, 1413bと、2つのNMOS型のトランジスタ1413c, 1413dとを含んで構成されている。このクロックトインバータ1413の入力端（CMOS構成をなすトランジスタ1413b, 1413cのゲート）は、インバータ1412の出力端（トランジスタ1412a, 1412bのドレイン）に接続される一方、出力端（トランジスタ1413b, 1413cのドレイン）はインバータ1412の入力端（トランジスタ1412a, 1412bのゲート）に接続されている。

## 【0024】

このような構成のパルス転送段141-1において、クロックトインバータ1411の出力端（トランジスタ1411b, 1411cのドレイン）からは、シフトレジスタパルスSRP1が出力され、次段のパルス転送段141-2に転送されると共に、デコーダ部142に入力されるようになっている。他のパルス転送段141-2～141-mについても同様の構成である。

## 【0025】

再び図3を参照して説明する。この図に示したように、デコーダ部142は、画素部11の各画素ラインa<sub>j</sub>ごとに設けられた NANDゲート142-j (j = 1 ~ M) を含んでいる。奇数番目の NANDゲート142-1, 142-3等の各一方の入力端には、図5(g)に示したようなデコードパルスVCK-Aが入力され、偶数番目の NANDゲート142-2, 142-4等の各一方の入力端には、図5(h)に示したようなデコードパルスVCK-Bが入力されている。ここで、デコードパルスVCK-Aは、Vクロックパルス2VCKの2分の1の周期を有し、デコードパルスVCK-BはデコードパルスVCK-Aを反転した波形を有する。

## 【0026】

デコーダ部142の NANDゲート142-(2k-1), 142-2kの各々他の入力端には、Vシフトレジスタ141のパルス転送段141-kからのシフトレジスタパルスSRPkが入力されるようになっている。ここで、k = 1 ~ mである。これらの NANDゲ

ート 142 - (2k - 1), 142 - 2k は、それぞれ、Vシフトレジスタ141からのシフトレジスタパルスSRPkをデコードパルスVCK-AまたはVCK-Bによってデコードして出力するようになっている。ここで、デコーダ部142が本発明における「個別駆動パルス生成手段」に対応する。

#### 【0027】

バッファ部143は、画素部11の各画素ラインajごとに設けられたバッファ143-j(j=1~M)を含んでいる。各バッファ143-jの入力端はデコーダ部142の各 NANDゲート142-jの出力端に接続され、出力端は画素ラインajの各画素を構成するTFT(図示せず)のゲートに接続されている。各バッファ143-jは、対応する NANDゲート142-jからの出力信号の論理を反転し、図5(i)~(n)に示したようなゲートパルスGPjを出力する。これらのゲートパルスGPjは、画素部11の対応する画素ラインajの各画素を構成するTFTトランジスタのゲート(図示せず)に供給され、各画素を駆動するようになっている。各バッファ143-jはまた、デコーダ部142やVシフトレジスタ141が、画素部11の対応する画素ラインajにおける配線容量の影響を受けないように、両者を隔離する機能をも有している。ここで、ゲートパルスGPjが本発明における「第2のパルス信号」に対応する。

10

#### 【0028】

次に、以上のような構成のカラー液晶表示装置の動作を説明する。

#### 【0029】

図3において、タイミング発生部30(図1)から出力されるVスタートパルス2VSTはVシフトレジスタ141のパルス転送段141-1に入力され、Vクロックパルス2VCKは、Vシフトレジスタ14の各パルス転送段141-1~141-mに供給される。これらの各パルス転送段141-1~141-mは、Vクロックパルス2VCKに従って順次パルス転送を行うと共に、図5(d)~(f)に示したようなシフトレジスタパルスSRP1~SRPmを順次出力する。

20

#### 【0030】

Vシフトレジスタ141の各パルス転送段141-1~141-mから出力されたシフトレジスタパルスSRP1~SRPmは、デコーダ部142におけるそれぞれ対応する NANDゲートの組に入力される。より具体的には、シフトレジスタパルスSRPk(k=1~m)は、対応する NANDゲート142-(2k-1), 142-2kに入力される。これらの NANDゲート142-(2k-1), 142-2kは、それぞれ、図5(g), (h)に示したようなデコードパルスVCK-A, VCK-BによってシフトレジスタパルスSRPkをデコードして出力する。NANDゲート142-j(j=1~M)の出力は、それぞれ、バッファ部143のバッファ143-jによってそれぞれ反転されて、図5(i)~(n)に示したようなゲートパルスGPjとして出力される。ゲートパルスGPjは、画素部11(図2)の対応する画素ラインajにおける各画素のTFTトランジスタのゲートに供給され、各トランジスタをオン(開)状態にする。

30

#### 【0031】

一方、タイミング発生部30(図1)から出力されるHスタートパルスHSTおよびHクロックパルスHCKは、Hシフトレジスタ13(図1)に供給される。Hシフトレジスタ13は、これらの信号HST, HCKに従って水平選択パルスを順次シフトしながら出力する。これらの水平選択パルスは、それぞれ、水平スイッチ部12の上記した各水平スイッチグループに順次入力され、各グループ内の水平スイッチを開状態にする。その結果、第1列から第N列までの各画素列が3列ずつ順次選択される。

40

#### 【0032】

バッファ部143からのゲートパルスGP1によって画素ラインa1が選択されている期間において、Hシフトレジスタ13からの水平選択パルスによって1列から第3列までの画素列が選択されると、信号ドライバ20から入力されるビデオ信号BS, RS, GSは、それぞれ、画素ラインa1の画素BD(1, 1)~GD(3, 1)に供給される。次に、第4列から第6列までの画素列が選択されることにより、ビデオ信号BS, RS, GS

50

はそれぞれ画素 B D ( 4 , 1 ) ~ G D ( 6 , 1 ) に供給される。以下同様に、画素ライン a 1 の画素が順次 3 個ずつ選択され、それぞれに対してビデオ信号 B S , R S , G S が同時に供給される。

#### 【 0 0 3 3 】

画素ライン a 1 の N 個の画素に対するビデオ信号の書き込みが終了すると、次に、ゲートパルス G P 2 によって画素ライン a 2 が選択され、ここでも画素ライン a 1 の場合と同様にして 3 個ずつの画素が選択されて同時にビデオ信号 B S , R S , G S が供給される。以下同様にして、1 画素ライン分のビデオ信号の供給が終了するたびにゲートパルス G P j によって次の画素ラインが選択される。これにより、1 フィールド分の処理が終了する。さらに、1 フィールド分の処理が終了すると、次のフィールドにおいても同様の処理が行われる。

#### 【 0 0 3 4 】

ここで、図 6 および図 7 を参照して、本実施の形態に対する比較例について説明する。

#### 【 0 0 3 5 】

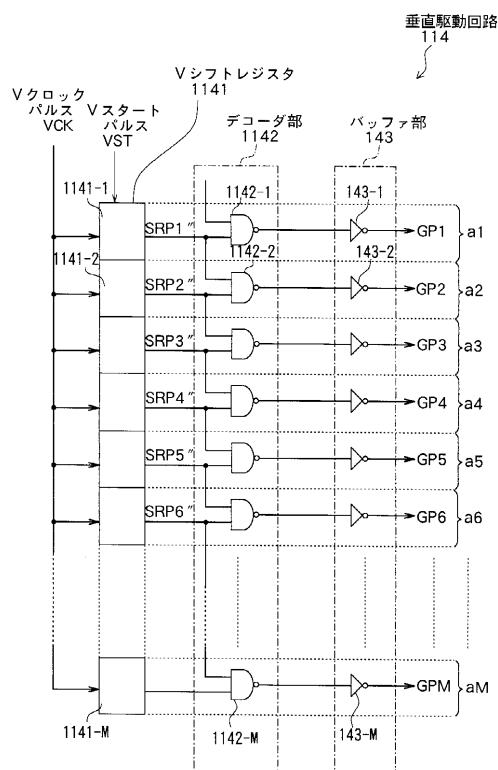

図 6 は本実施の形態における垂直駆動回路 1 4 に対する比較例としての垂直駆動回路 1 1 4 の概略構成を表し、図 7 は、この垂直駆動回路 1 1 4 における各種信号のタイミングを表すものである。なお、これらの図で本実施の形態（図 3 , 図 5 ）と同一構成部分には同一の符号を付す。図 6 に示したように、本比較例の垂直駆動回路 1 1 4 は、V シフトレジスタ 1 1 4 1 と、デコーダ部 1 1 4 2 と、バッファ部 1 4 3 とを含んで構成されている。V シフトレジスタ 1 1 4 1 は、上記実施の形態における V シフトレジスタ 1 4 1 と異なり、画素部 1 1 の各画素ライン a j に対応して設けられた合計 M ( = 2 m ) 個のパルス転送段 1 1 4 1 - j ( j = 1 ~ M ) から構成されている。ここで、各パルス転送段 1 1 4 1 - j は、上記実施の形態の図 4 に示した回路と同じ回路構成であり、2 つのクロックトインバータと、1 つのインバータとによって構成される。V シフトレジスタ 1 1 4 1 には、図 7 ( a ) に示したような V スタートパルス V S T と、図 7 ( b ) に示したような V クロックパルス V C K とが入力される。ここで、V スタートパルス V S T および V クロックパルス V C K は、それぞれ、上記実施の形態における V スタートパルス 2 V S T および V クロックパルス 2 V C K のそれぞれ 2 倍の周波数（2 分の 1 の周期）をもつパルス信号である。

#### 【 0 0 3 6 】

V シフトレジスタ 1 1 4 1 の各パルス転送段 1 1 4 1 - j は、V スタートパルス V S T および V クロックパルス V C K に従ってパルス転送を行い、図 7 ( c ) ~ ( h ) に示したようなシフトレジスタパルス S R P j ( この図では S P R 1 ~ S P R 6 のみを図示 ) を順次出力して、デコーダ部 1 1 4 2 における対応する NAND ゲート 1 1 4 2 - j に供給するようになっている。デコーダ部 1 1 4 2 の各 NAND ゲート 1 1 4 2 - j は、対応するパルス転送段 1 1 4 1 - j から供給されたシフトレジスタパルス S R P j を、前段のパルス転送段 1 1 4 1 - ( j - 1 ) からのシフトレジスタパルス S R P ( j - 1 ) によってデコードして出力する。バッファ部 1 4 3 の各バッファ 1 4 3 - j は、対応する NAND ゲート 1 1 4 2 - j の出力を反転して、図 7 ( i ) ~ ( n ) に示したようなゲートパルス G P j を出力し、対応する画素ライン a j に供給するようになっている。

#### 【 0 0 3 7 】

このように、本比較例の垂直駆動回路 1 1 4 においては、V シフトレジスタ 1 1 4 1 のパルス転送段 1 1 4 1 - j が画素部 1 1 の各画素ライン a j ごとに一つずつ設けられている。ここで、1 つのパルス転送段 1 1 4 1 - j を構成するには、図 4 に示したように、合計 10 個のトランジスタ素子が必要であり、各トランジスタ素子間の複雑な配線が必要であることを考慮すると、かなりの配置面積が必要となる。このため、画素部 1 1 の高精細化のために画素ピッチを狭くしようとした場合には、1 画素ライン a j の幅に対応する領域に 1 つのパルス転送段 1 1 4 1 - j を形成することが困難となる。例えば、V シフトレジスタ 1 1 4 1 の 1 つの転送段を図 4 のように構成する場合には、1 画素ライン分の幅領域に 10 個のトランジスタ素子を配置しなければならず、画素ピッチの狭小化に対応する

10

20

30

40

50

ことができない。また、仮に、製造技術の向上に伴うトランジスタ素子のサイズや配線幅の縮小化によって、1画素ライン  $a_j$  分の幅領域に1つのパルス転送段 1141-j を形成できたとしても、それを製造コストのアップを伴わずに実現することは困難であり、また、画素部 11 の画素ライン  $a_j$  の数 (=  $j$ ) を増加した場合には、それに比例して V シフトレジスタ 1141 の構成に必要な素子数が増加するため、垂直駆動回路 114 の消費電流が著しく増大することは必至である。さらに、V シフトレジスタ 1141 を動作させるための V スタートパルス VST や V クロックパルス VCK は、図 7 (a), (b) に示したように、周波数の高いパルス信号であることから、V シフトレジスタ 1141 の各パルス転送段を構成するトランジスタ素子は周波数特性がよいものでなければならず、この点でも構成上の難点がある。

10

#### 【0038】

これに対して、本実施の形態の垂直駆動回路 14 によれば、2つの画素ラインに対して1つのパルス転送段を対応付けると共に、各パルス転送段からの出力をデコーダ部 142 によりデコードして各画素ライン  $a_j$  用のゲートパルス GPj を作成するようにしたので、画素ラインの総数が同じであれば、V シフトレジスタ 141 の構成段数を上記比較例の2分の1とすることができます。したがって、V シフトレジスタ 141 の構成に必要な全素子数を約2分の1にすることが可能であり、消費電流を低減することができる。また、2画素ライン分の幅領域に1つのパルス転送段を形成すればよいことから、画素ピッチを相当狭くしたとしても、現状の製造技術レベルでも十分対応可能である。例えば、V シフトレジスタ 141 の1つの転送段を図 4 のように構成する場合には、2画素ライン分の幅領域に10個のトランジスタ素子を配置すればよく、1画素ライン当たりにすれば5個のトランジスタ素子を配置すればよいこととなるので、製造が容易である。さらに、V シフトレジスタ 141 を動作させるための V スタートパルス 2VST や V クロックパルス 2VCK は、図 5 (b), (c) に示したように、比較例で用いた V スタートパルス VST および V クロックパルス VCK ( 図 7 (a), (b) ) と比べて周波数の低いパルス信号であることから、V シフトレジスタ 141 の各パルス転送段を構成するトランジスタ素子は、周波数特性がさほどよいものである必要はなく、通常の特性の素子を使用可能である。

20

#### 【0039】

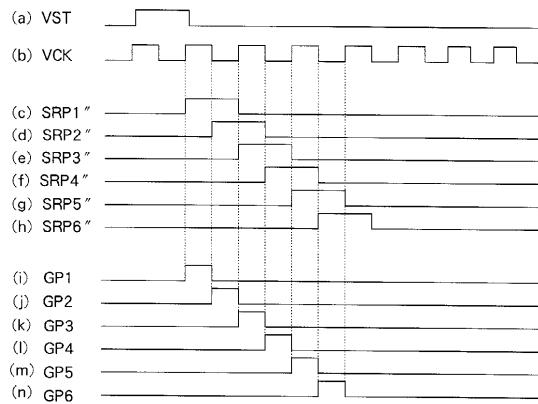

なお、本実施の形態では、図 3 に示したように、デコーダ部 142 で用いるデコードパルス VCK-A, VCK-B を、各 NAND ゲートごとに交互に A, B, A, B, ... という順序で割り当てて入力するようにしたが、このほか、図 8 および図 9 に示したように、上記のデコードパルス VCK-A, VCK-B の2倍のパルス幅 (2分の1の周波数) をもつデコードパルス 2VCK-A, 2VCK-B を用意して、これらをデコーダ部 142 の各 NAND ゲートに A, B, B, A, A, B, ... という順序で割り当てて入力するように変形してもよい。なお、図 8 は本実施の形態の変形例としての垂直駆動回路 14 の概略構成を表し、図 9 は図 8 の垂直駆動回路 14 の各種信号のタイミングを表すものである。これらの図で、上記の図 3 および図 5 に示した各構成部分と同一の構成部分には同一の符号を付し、説明を省略する。図 8 および図 9 のうち、デコードパルス 2VCK-A, 2VCK-B の波形、およびデコーダ部 142 の各 NAND ゲートに対するデコードパルス 2VCK-A, 2VCK-B の割り当て方法以外の部分の構成は図 3 および図 5 と同様である。

30

#### 【0040】

図 8 に示した変形例では、図 9 (g), (h) に示したように、デコードパルス 2VCK-A, 2VCK-B の周波数を上記の図 5 (g), (h) に示したデコードパルス VCK-A, VCK-B の2分の1にすることができる。また、図 5 の例では、例えばタイミング  $t_1, t_2$  において、シフトレジスタパルス SRP1 とデコードパルス VCK-A または VCK-B とが同じタイミングで立ち上がり、または立ち下がっているので、両者間にわずかなタイミングずれがあると、 NAND ゲートの出力にヒゲ状のスパイクノイズが発生する可能性がある。これに対して、図 8 に示した変形例では、図 9 (g), (h) に

40

50

示したように、シフトレジスタパルス S R P 1 とデコードパルス 2 V C K - A または 2 V C K - B との間で、立ち上がりおよび立ち下がりのタイミングは完全に異なっているので、上記のようなヒゲ状のスパイクノイズが発生するおそれは少ない。

【 0 0 4 1 】

[ 第 2 の実施の形態 ]

次に、本発明の第 2 の実施の形態を説明する。

【 0 0 4 2 】

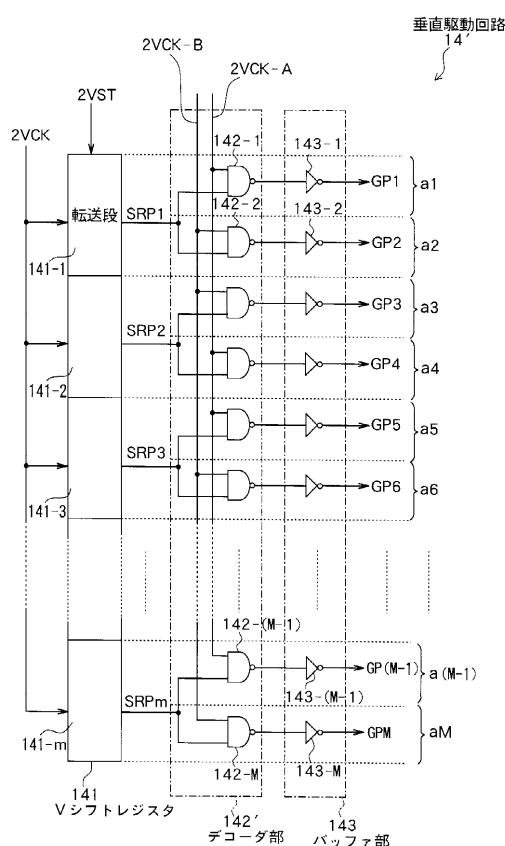

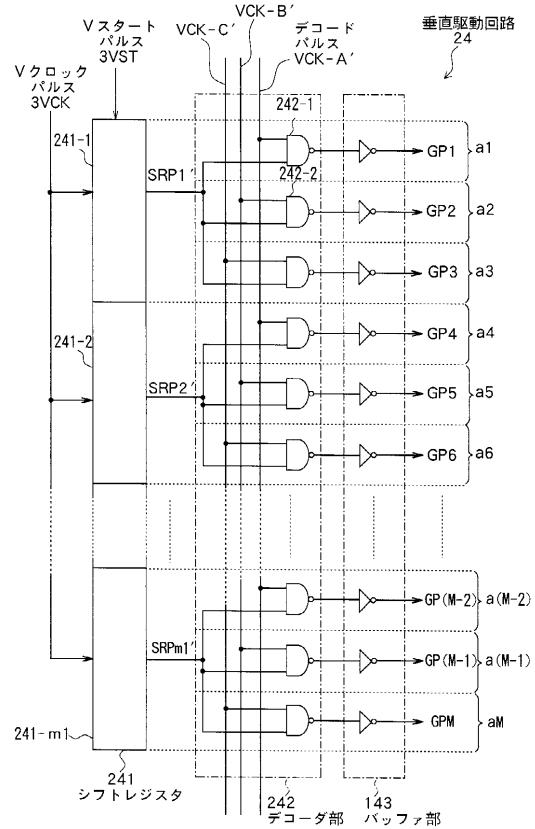

図 10 は本発明の第 2 の実施の形態に係るカラー液晶表示装置に適用される垂直駆動回路 24 の概略構成を表すものである。この垂直駆動回路 24 は、上記第 1 の実施の形態(図 3)における V シフトレジスタ 141 およびデコーダ部 142 に代えて、それぞれ、V シフトレジスタ 241 およびデコーダ部 242 を備えるようにしたものである。この V シフトレジスタ 241 は、m1 個のパルス転送段 241-1 ~ 241-m1 を含んで構成されている。各パルス転送段 241-p (ここで、p = 1 ~ m1) は、画素部 11 (図 2) の 3 つの画素ライン a (3p-2), a (3p-1), a (3p) に対して 1 つずつ設けられており、その内部構成は図 4 に示したものと同様である。ここで、m1 = M / 3 (= 自然数) である。

【 0 0 4 3 】

V シフトレジスタ 241 には、図 11 (b), (c) に示したように、上記比較例(図 7 (a), (b))における V スタートパルス V S T および V クロックパルス V C K のそれぞれ 3 倍の周期をもつ V スタートパルス 3 V S T および V クロックパルス 3 V C K がタイミング発生部 30 (図 1) から供給されるようになっている。ここで、V シフトレジスタ 241 が本発明における「パルス移動手段」に対応する。

【 0 0 4 4 】

デコーダ部 242 には、図 11 (g) ~ (i) に示したような互いに異なる位相をもつ 3 つのデコードパルス V C K - A , V C K - B , V C K - C が供給され、それぞれ、パルス転送段 241-p に対応する NAND ゲート 242-(3p-2), 242-(3p-1), 242-3p の各々一方の入力端に入力されるようになっている。これらの 3 個の NAND ゲート 242-(3p-2), 242-(3p-1), 242-3p の各々他の入力端には、V シフトレジスタ 241 のパルス転送段 241-p からシフトレジスタパルス S R P p が入力されるようになっている。デコーダ部 242 が本発明における「駆動パルス生成手段」に対応し、シフトレジスタパルス S R P p が本発明における「第 1 のパルス信号」に対応する。

【 0 0 4 5 】

次に、このような構成の垂直駆動回路 24 の動作を説明する。図 1 のタイミング配線部 30 から出力された V スタートパルス 3 V S T は V シフトレジスタ 241 のパルス転送段 241-1 に入力され、V クロックパルス 3 V C K は、V シフトレジスタ 24 の各パルス転送段 241-1 ~ 241-m1 に供給される。これらの各パルス転送段 241-1 ~ 241-m1 は、V クロックパルス 3 V C K に従って順次パルス転送を行うと共に、図 11 (d) ~ (f) に示したようなシフトレジスタパルス S R P 1 ~ S R P m1 を順次出力する。これらのシフトレジスタパルス S R P 1 ~ S R P m1 は、デコーダ部 242 におけるそれぞれ対応する 3 個の NAND ゲートの組に入力される。より具体的には、シフトレジスタパルス S R P p は 3 つの NAND ゲート 242-(3p-2), 242-(3p-1), 242-3p に入力される。但し、p = 1 ~ m1 である。NAND ゲート 242-(3p-2), 242-(3p-1), 242-3p は、デコードパルス V C K - A , V C K - B , V C K - C によってシフトレジスタパルス S R P p をそれぞれデコードして出力する。これらの各 NAND ゲートの出力は、それぞれ、バッファ部 143 のバッファ 143-j によってそれぞれ反転されて、図 11 (j) ~ (o) に示したようなゲートパルス G P j として出力される。ゲートパルス G P j は、画素部 11 (図 2) の対応する画素ライン a j における各画素の T F T トランジスタのゲートに供給され、各トランジスタをオン(開)状態にする。

【 0 0 4 6 】

10

20

30

40

50

このように、本実施の形態によれば、画素部 11 の 3 つの画素ラインに対して 1 つのパルス転送段 241 - p を設けるようにしたので、V シフトレジスタ 241 の構成に必要な全素子数を上記第 1 の実施の形態の場合よりもさらに低減することができ、消費電流をより一層低減することができる。また、3 画素ライン分の幅領域に 1 つのパルス転送段を形成すればよいことから、画素ピッチをさらに狭くしたとしても、現状の製造技術レベルで十分対応可能である。例えば、V シフトレジスタ 241 の 1 つの転送段を図 4 のように構成する場合には、3 画素ライン分の幅領域に 10 個のトランジスタ素子を配置すればよく、1 画素ライン当たりにすれば約 3 個のトランジスタ素子を配置すればよいことから、製造がさらに容易になる。さらに、V シフトレジスタ 241 を動作させるための V スタートパルス 3VST や V クロックパルス 3VCK は、図 11 (b), (c) に示したように、第 1 の実施の形態で用いる V スタートパルス 2VST および V クロックパルス 2VCK と比べてより周波数の低いパルス信号であることから、V シフトレジスタ 241 の各パルス転送段を構成するトランジスタ素子に要求される周波数特性は、より緩やかなものとなる。

#### 【0047】

##### [第 3 の実施の形態]

次に、本発明の第 3 の実施の形態を説明する。

#### 【0048】

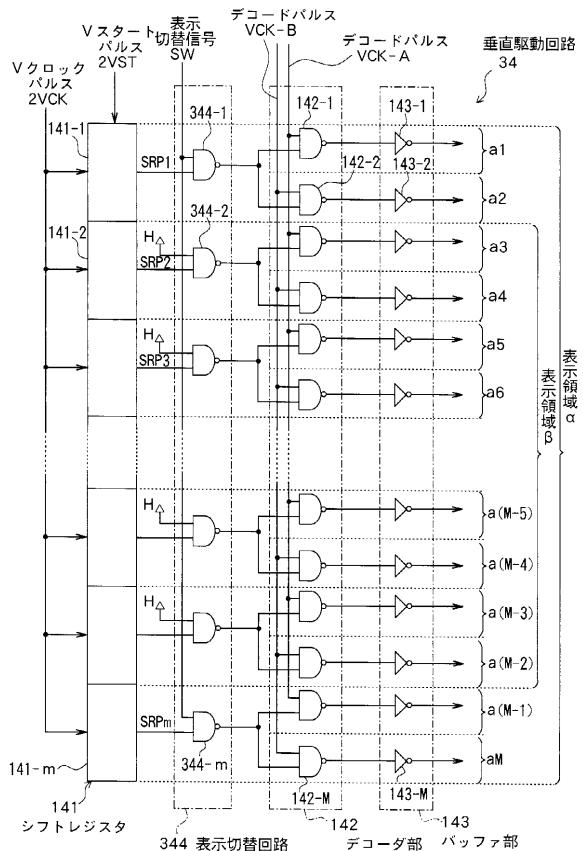

図 12 は本発明の第 3 の実施の形態に係るカラー液晶表示装置に適用される垂直駆動回路 34 の概略構成を表すものである。この垂直駆動回路 34 は、上記第 1 の実施の形態(図 3)で示した垂直駆動回路 14 における V シフトレジスタ 141 とデコーダ部 142 との間に、入力されるビデオ信号の種類(規格)に応じて画素部 11(図 2)の表示領域をまたはに切り替えることを可能とする表示切替回路 344 を設けたものである。ここで、表示領域 は、画素部 11 のすべての画素ライン  $a_1 \sim a_M$  を表示可能にしたときの表示領域であり、表示領域 は、画素部 11 の画素ラインのうち  $a_2 \sim a_{(M-1)}$  のみを表示可能にしたときの表示領域である。

#### 【0049】

図 12 に示したように、表示切替回路 344 は  $m$  個(但し、 $m = M / 2$ )の NAND ゲート 344 - 1 ~ 344 -  $m$  を含んでいる。各 NAND ゲート 344 -  $k$ (但し、 $k = 1 \sim m$ )は、V シフトレジスタ 141 の各パルス転送段 141 -  $k$  から出力されたシフトレジスタパルス S R P  $k$  を後段のデコーダ部 142 における対応する NAND ゲート 142 - (2  $k$  - 1), 142 - 2  $k$  に入力するか否かを制御するためのものである。NAND ゲート 344 -  $k$  の各々一方の入力端には、シフトレジスタパルス S R P  $k$  が入力されるようになっている。また、最上段の NAND ゲート 344 - 1 および最下段の NAND ゲート 344 -  $m$  における各々他の入力端には、“H”または“L”レベルのいずれかの値をとる表示切替信号 S W が入力されている。その他の NAND ゲート 344 - 2 ~ 344 - (  $m - 1$  )における各々他の入力端はすべて“H”レベルに固定されている。その他の構成は図 3 の場合と同様である。ここで、表示切替回路 344 が本発明における「切替手段」に対応する。

#### 【0050】

次に、以上のような構成の垂直駆動回路 34 の動作を説明する。

#### 【0051】

まず、表示領域 1 を表示可能にする場合には、表示切替回路 344 の NAND ゲート 344 - 1 および 344 -  $m$  に入力する表示切替信号 S W を“H”レベルにする。これにより、すべての NAND ゲート 344 - 1 ~ 344 -  $m$  がゲート開状態となり、V シフトレジスタ 141 からのすべてのシフトレジスタパルス S R P 1 ~ S R P  $m$  がそのままデコーダ部 142 に供給される。すなわち、この状態では、図 3 に示した回路状態と等しくなる。画素部 11 の全体である表示領域 1 がアクティブ状態となり、ここに画像が表示されることとなる。

#### 【0052】

一方、表示領域 2 を表示可能にする場合には、表示切替回路 344 の NAND ゲート 344 - 1 および 344 -  $m$  に入力する表示切替信号 S W を“L”レベルにする。これにより、

10

20

30

40

50

NANDゲート 344 - 2 ~ 344 - (m - 1) のみがゲート開状態となり、 NANDゲート 344 - 1 および 344 - m はゲート閉状態となる。このため、 V シフトレジスタ 141 からのシフトレジスタパルス S R P 1 および S R P m はデコーダ部 142 に供給されず、 シフトレジスタパルス S R P 2 ~ S R P (m - 1) のみがそのままデコーダ部 142 に供給される。これにより、 画素部 11 のうちの表示領域 のみがアクティブ状態となり、 ここに画像が表示される。このとき、 画素ライン a1 , a2 , a(M-1) , aM の部分は黒く表示される。

#### 【0053】

ここで、 本実施の形態の垂直駆動回路 34 に対する比較例を説明する。

#### 【0054】

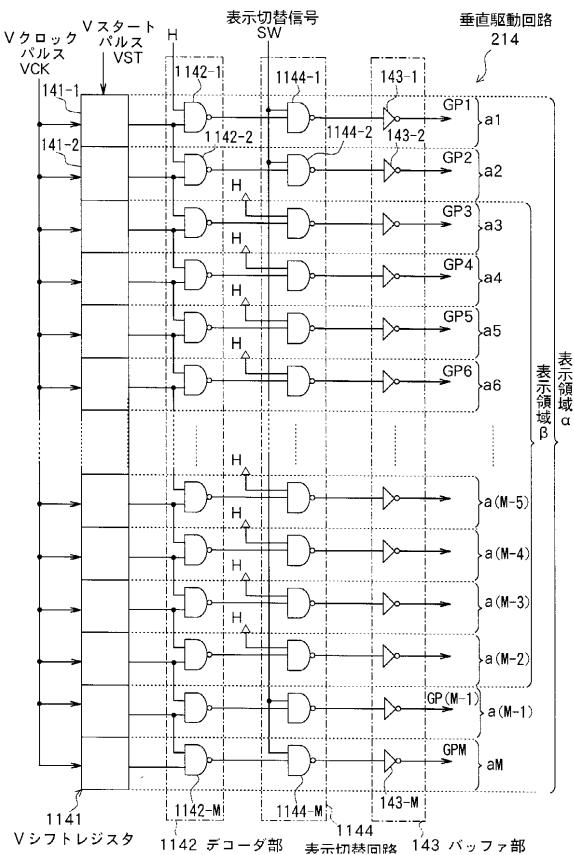

図 13 は本実施の形態に対する比較例としての垂直駆動回路 214 の概略構成を表すものである。この垂直駆動回路 214 は、 上記第 1 の実施の形態に対する比較例 ( 図 6 ) で示した垂直駆動回路 114 におけるデコーダ部 1142 とバッファ部 143 との間に、 入力されるビデオ信号の種類 ( 規格 ) に応じて画素部 11 ( 図 2 ) の表示領域を または に切り替えることを可能とする表示切替回路 1144 を設けたものである。ここで、 表示領域 は、 本実施の形態 ( 図 12 ) におけるものと同じである。表示切替回路 1144 は、 M 個の NANDゲート 1144 - 1 ~ 1144 - M から構成されている。これらの各 NANDゲート 1144 - j ( j = 1 ~ M ) は画素部 11 の各画素ライン a j に対応して設けられている。

#### 【0055】

各 NANDゲート 1144 - j は、 デコーダ部 1142 の各 NANDゲート 1142 - j の出力を後段のバッファ部 143 における対応するバッファ 143 - j に入力するか否かを制御するためのものである。 NANDゲート 1144 - j の各々一方の入力端には、 デコーダ部 1142 の各 NANDゲート 1142 - j の出力が入力されるようになっている。また、 最上段側の 2 つの NANDゲート 1144 - 1 , 1144 - 2 および最下段側の 2 つの NANDゲート 1144 - (M - 1) , 1144 - M における各々他の入力端には、 “H” または “L” レベルのいずれかの値をとる表示切替信号 SW が入力されるようになっている。 その他の NANDゲート 1144 - 3 ~ 1144 - (M - 2) における各々他の入力端はすべて “H” レベルに固定されている。 その他の構成は図 6 の場合と同様である。

#### 【0056】

このような構成の垂直駆動回路 214 において、 表示領域 を表示可能にするには、 表示切替信号 SW を “H” レベルにすることにより、 すべての NANDゲート 1144 - 1 ~ 1144 - M をゲート開状態にする。これにより、 デコーダ部 1142 のすべての NANDゲート 1142 - j の出力がそのままバッファ部 143 の対応するバッファ 143 - j に供給され、 表示領域 がアクティブ状態となる。一方、 表示領域 を表示可能にするには、 表示切替信号 SW を “L” レベルにすることにより、 最上段側の 2 つの NANDゲート 1144 - 1 , 1144 - 2 および最下段側の 2 つの NANDゲート 1144 - (M - 1) , 1144 - M のみをゲート閉状態にする。これにより、 これらの 4 つの NANDゲートの出力はバッファ部 143 に供給されず、 NANDゲート 1144 - 3 ~ 1144 - (M - 2) の出力のみがそのままデコーダ部 142 に供給される。これにより、 表示領域 のみがアクティブ状態となり、 画素ライン a1 , a2 , a(M-1) , aM の部分は黒く表示される。

#### 【0057】

このように、 本比較例では、 画素部 11 における各画素ライン a j ごとに表示切替用の NANDゲート 1144 - 1 ~ 1144 - M を設けて表示切替回路 1144 を構成しているので、 画素ピッチの狭小化に対応することが上記第 1 の実施の形態の場合 ( 図 3 ) よりもさらに困難になる。また、 表示切替回路 1144 の構成に必要なトランジスタ素子数が多いので、 消費電流が大きくなる。

#### 【0058】

これに対して、 本実施の形態の垂直駆動回路 34 ( 図 12 ) では、 2 つの画素ライン a(2k-1) , a(2k) の組に対して設けたパルス転送段 141 - k に対応して NANDゲート 114

10

20

30

40

50

4 - k を設けることで表示切替回路 344 を構成しているので、画素ピッチの狭小化に対応することが上記比較例（図13）の場合よりもさらに容易となる。また、表示切替回路 344 の構成に必要なトランジスタ素子数を削減できるので、上記比較例（図13）の場合よりも消費電流をさらに低減することができる。

#### 【0059】

なお、本実施の形態では、上記第1の実施の形態に示した垂直駆動回路 14 に表示切替回路 344 を設けて表示領域の切り替えを行う場合について説明したが、上記第2の実施の形態に示した垂直駆動回路 24（図10）に表示切替回路を設けて表示領域の切り替えを行うことも可能である。この場合には、図10の垂直駆動回路 24 において、Vシフトレジスタ 241 のパルス転送段 141 - p (p = 1 ~ m1) とデコーダ部 242 の対応する 10 3 個の NANDゲート 242 - (3p - 2), 242 - (3p - 1), 242 - 3p の組との間に 1 つの NANDゲートを設けるようにして表示切替回路を構成すればよい。

#### 【0060】

以上、いくつかの実施の形態を挙げて本発明を説明したが、本発明はこれらの実施の形態に限定されるものではなく、種々変形可能である。例えば、上記第2の実施の形態では、画素部 11 における 3 つの画素ライン a (3p-2), a (3p-1), a (3p) に対して 1 つのパルス転送段 241 - p を設けるようにして Vシフトレジスタ 241 を構成するようにしたが、4 つ以上の画素ラインに対して 1 つのパルス転送段を設けるようにしてもよい。

#### 【0061】

また、上記各実施の形態では、水平方向の駆動方式を 3 ドット同時サンプリングとしたが 20 、これに限らず、より多くの画素を同時駆動する多ドット同時サンプリングとしてもよく、あるいは 1 画素ずつ駆動するようにしてもよい。

#### 【0062】

また、本実施の形態ではカラー液晶表示装置について説明したが、本発明はこれに限定されるものではなく、白黒の液晶表示装置にも適用できる。さらに、液晶表示装置以外の表示装置、例えば P D (プラズマディスプレイ) 素子や E L (エレクトロ・ルミネンス) 素子、さらには、F E D (Field Emission Display) 素子等にも適用可能である。なお、この F E D とは、多数の微細な電子源を陰極としてアレイ上に配列すると共に、各陰極に高電圧を印加することにより各陰極から電子を引き出し、これらの電子を陽極に塗布した蛍光体に衝突させて発光させたものである。 30

#### 【0063】

#### 【発明の効果】

以上説明したように、請求項 1 もしくは請求項 2 記載の画素駆動回路、または請求項 3 もしくは請求項 4 記載の駆動回路一体型画素集積装置によれば、画素配列の 2 つの方向のうちの 1 の方向に沿って第 1 のパルス信号を複数画素分ずつ移動させながら順次出力するパルス移動手段を設けると共に、個別駆動パルス生成手段によって、第 1 のパルス信号を基に、2 つの方向のうちの他の方向に沿って配列された画素列を個別に駆動するためのより多くの第 2 のパルス信号を生成するようにしたので、パルス移動手段を構成する回路素子の数を削減することができる。このため、パルス移動手段を構成する回路の配置面積を縮小できると共に、消費電力の低減が可能になる。また、パルス移動手段は、複数の画素列に対応して 1 つの第 1 のパルス信号を出力すればよいので、このパルス移動手段を構成する回路素子に対する周波数特性の要求を緩和することができる。 40

また、パルス移動手段と個別駆動パルス生成手段との間に、パルス移動手段から個別駆動パルス生成手段に対して第 1 のパルス信号を供給するか否かを切替可能な切替手段を備えるように構成したので、従来のように個別駆動パルス生成手段と各画素列との間に切替手段を設けるように構成した場合と比べると、切替回路の構成素子数を削減することができ、回路サイズがよりコンパクトとなる。したがって、切替回路によって全画素のうちの一部を選択的に非駆動状態にして表示領域サイズを切り替え可能にする場合においても、従来に比べて消費電力を低減でき、また、画素ピッチの狭小化に対応することができるという効果がある。

## 【0064】

特に、請求項3または請求項4記載の駆動回路一体型画素集積装置によれば、パルス移動手段を構成する回路素子の数を削減して回路面積を縮小できることから、画素部とその駆動回路とを一体に構成する場合であっても、画素ピッチの狭小化に十分対応することができるという効果がある。

## 【0065】

また、請求項2記載の画素駆動回路または請求項4記載の駆動回路一体型画素集積装置によれば、切替手段が表示切替信号に応じて、他の方向に沿って配列された画素列のうちの一部の画素列が選択的に非駆動状態となるように第1のパルス信号を供給するか否かの切替を行うように構成したので、表示領域サイズを切り替えることが可能となる。

10

## 【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係るカラー液晶表示装置の概略構成を表すブロック図である。

【図2】図1における液晶パネルの概略構成を表す図である。

【図3】図1における垂直駆動回路の概略構成を表す回路図である。

【図4】図3におけるシフトレジスタの各転送段の構成を表す回路図である。

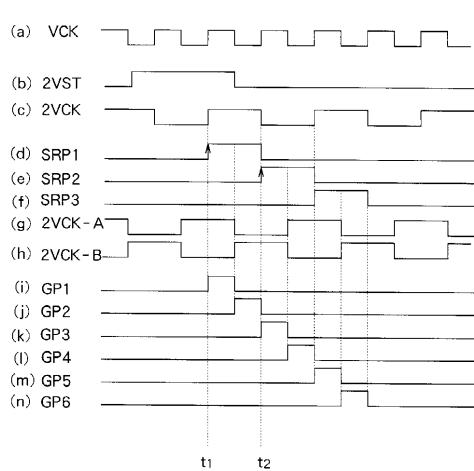

【図5】図3の垂直駆動回路の動作を説明するためのタイミング図である。

【図6】本発明の第1の実施の形態に対する比較例としての垂直駆動回路の概略構成を表す回路図である。

【図7】図6の垂直駆動回路の動作を説明するためのタイミング図である。

20

【図8】図3の垂直駆動回路に対する変形例を表す回路図である。

【図9】図8の垂直駆動回路の動作を説明するためのタイミング図である。

【図10】本発明の第2の実施の形態に係るカラー液晶表示装置に用いられる垂直駆動回路の概略構成を表すブロック図である。

【図11】図10の垂直駆動回路の動作を説明するためのタイミング図である。

【図12】本発明の第3の実施の形態に係るカラー液晶表示装置に用いられる垂直駆動回路の概略構成を表すブロック図である。

【図13】本発明の第3の実施の形態に対する比較例としての垂直駆動回路の概略構成を表す回路図である。

## 【符号の説明】

30

10...液晶パネル、11...画素部、12...水平スイッチ部、13...Hシフトレジスタ、14, 14, 24, 34...垂直駆動回路、141, 241...Vシフトレジスタ、141-1~141-m, 241-1~241-m...パルス転送段、142, 142, 242...デコーダ部、143...バッファ部、344...表示切替回路、a1~aM...画素ライン、B S, R S, G S...ビデオ信号、2 V S T, 3 V S T...Vスタートパルス、2 V C K, 3 V C K...Vクロックパルス、V C K - A, V C K - B, 2 V C K - A, 2 V C K - B, V C K - A, V C K - B, V C K - C...デコードパルス、S R P 1~S R P m, S R P 1~S R P m...シフトレジスタパルス、G P 1~G P M...ゲートパルス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/36 |         |

| H 0 4 N | 5/66 | B       |

| H 0 4 N | 5/66 | 1 0 2 B |

(56)参考文献 特開平08-122748 (JP, A)

特開平09-061788 (JP, A)

特開平09-325741 (JP, A)

特開平08-079663 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00-3/38

G02F 1/133 505-580