(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7622308号

(P7622308)

(45)発行日 令和7年1月28日(2025.1.28)

(24)登録日 令和7年1月20日(2025.1.20)

(51)国際特許分類

|                        |     |              |         |

|------------------------|-----|--------------|---------|

| H 01 L 21/60 (2006.01) | F I | H 01 L 21/92 | 6 0 2 G |

| H 01 L 23/50 (2006.01) |     | H 01 L 21/92 | 6 0 4 A |

|                        |     | H 01 L 21/92 | 6 0 4 S |

|                        |     | H 01 L 21/60 | 3 1 1 Q |

|                        |     | H 01 L 23/50 | R       |

請求項の数 25 (全18頁)

(21)出願番号 特願2020-519726(P2020-519726)

(86)(22)出願日 平成30年10月4日(2018.10.4)

(65)公表番号 特表2020-537342(P2020-537342)

A)

(43)公表日 令和2年12月17日(2020.12.17)

(86)国際出願番号 PCT/US2018/054392

(87)国際公開番号 WO2019/070995

(87)国際公開日 平成31年4月11日(2019.4.11)

審査請求日 令和3年9月28日(2021.9.28)

審判番号 不服2023-20298(P2023-20298/J

1)

審判請求日 令和5年11月30日(2023.11.30)

(31)優先権主張番号 62/568,330

(32)優先日 平成29年10月5日(2017.10.5)

(33)優先権主張国・地域又は機関

最終頁に続く

(73)特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 7 5 2 6 5

- 5 4 7 4 ダラス メイル ステイション

3 9 9 9 ピーオーボックス 6 5 5 4 7 4

(74)代理人 230129078

弁護士 佐藤 仁

(72)発明者 スリーニーバサン ケイ コドウリ

アメリカ合衆国 7 5 0 1 3 テキサス州

アレン, バーンサイド ドライブ 2 0

2 3

合議体

審判長 恩田 春香

審判官 緑川 隆

最終頁に続く

(54)【発明の名称】 半導体デバイスにおける成形された相互接続バンプ

## (57)【特許請求の範囲】

## 【請求項1】

半導体パッケージであって、

複数の第1のランディングサイトと複数の第2のランディングサイトとを含むリードフレームであって、前記第1のランディングサイトが前記第2のランディングサイトよりも大きい、前記リードフレームと、

直線状に配置される複数の第1のランディングサイトと直線状に配置される複数の第2のランディングサイトとを含む半導体ダイであって、前記第1のランディングサイトが前記第2のランディングサイトよりも大きい、前記半導体ダイと、

電力信号を伝送するように構成される複数の電力バンプであって、前記複数の電力バンプの各々が、

前記半導体ダイの第1のランディングサイトに接続される第1の端部であって、前記半導体ダイの第1のランディングサイトに対応する端部表面面積A1を有する、前記第1の端部と、

前記リードフレームの第1のランディングサイトに接続される反対の第2の端部であって、前記リードフレームの第1のランディングサイトに対応して前記端部表面面積A1よりも大きい端部表面面積A2を有する、前記第2の端部と、

を含む、前記複数の電力バンプと、

電気信号を伝送するように構成される複数の信号バンプであって、前記複数の信号バンプの各々が、

前記半導体ダイの第2のランディングサイトに接続される第1の端部であって、前記半導体ダイの第2のランディングサイトに対応する端部表面面積A3を有する、前記第1の端部と、

前記リードフレームの第2のランディングサイトに接続される反対の第2の端部であって、前記リードフレームの第2のランディングサイトに対応して前記端部表面面積A3よりも大きい端部表面面積A4を有する、前記第2の端部と、

を含む、前記複数の信号バンプと、

を含む、半導体パッケージ。

**【請求項2】**

請求項1に記載の半導体パッケージであって、

前記電力バンプの第2の端部の端部表面面積A2が、前記電力バンプの第1の端部の端部表面面積A1よりも少なくとも10パーセント大きい、半導体パッケージ。

**【請求項3】**

請求項1に記載の半導体パッケージであって、

前記電力バンプの第2の端部の端部表面面積A2が、前記電力バンプの第1の端部の端部表面面積A1の少なくとも2倍である、パッケージ。

**【請求項4】**

請求項1に記載の半導体パッケージであって、

前記複数の電力バンプの各々が切頭円錐として成形され、前記切頭円錐の大きな端部がA2を定義し、前記切頭円錐の狭い端部がA1を定義する、半導体パッケージ。

**【請求項5】**

請求項1に記載の半導体パッケージであって、

前記複数の電力バンプの各々に対し、前記第1の端部から前記第2の端部に向かう線に直交して得られる断面が長円形又は円形である、パッケージ。

**【請求項6】**

請求項1に記載の半導体パッケージであって、

前記リードフレームが金属製であり、前記複数の電力バンプと前記複数の信号バンプとが銅で構成される、半導体パッケージ。

**【請求項7】**

請求項1に記載の半導体パッケージであって、

前記複数の電力バンプと前記複数の信号バンプとの各々に関連するはんだ材料であって、前記バンプの第2の端部を前記パッケージに取り付けるために前記バンプの第2の端部と前記リードフレームとの間に配置される、前記はんだ材料を更に含む、半導体パッケージ。

**【請求項8】**

請求項1に記載の半導体パッケージであって、

前記リードフレームと前記半導体ダイと前記複数の電力バンプと前記複数の信号バンプとを少なくとも部分的に覆うモールド化合物を更に含む、半導体パッケージ。

**【請求項9】**

半導体パッケージであって、

第1のリードと第2のリードとを含むリードフレームであって、前記第1及び第2のリードが直線状であって並行に配置される、前記リードフレームと、

前記リードフレームに取り付けられる半導体ダイと、

電力信号を伝送するように構成される電力バンプと電気信号を伝送するように構成される信号バンプとを含む複数のバンプであって、前記電力バンプが前記半導体ダイと前記リードフレームの第1のリードとを電気的に接続し、前記信号バンプが前記半導体ダイと前記リードフレームの第2のリードとを電気的に接続し、前記バンプの各々が第1の端部から反対の第2の端部まで延在する長手方向長さを有する、前記複数のバンプと、

を含み、

前記第1の端部が前記半導体ダイに接続され、第2の端部が前記リードフレームに接続

10

20

30

40

50

され、

前記第1の端部が第2の端部の横方向幅W2より小さい長手方向長さに直交する横方向幅W1を有する、半導体パッケージ。

【請求項10】

請求項9に記載の半導体パッケージであって、

前記複数のバンプの各々が、前記第1の端部と前記第2の端部との間で先細りにされている、半導体パッケージ。

【請求項11】

請求項9に記載の半導体パッケージであって、

前記第1の端部が端部表面面積A1を有し、前記第2の端部が端部表面面積A2を有し、前記端部表面面積A1が前記端部表面面積A2の寸法の少なくとも半分である、半導体パッケージ。

10

【請求項12】

請求項9に記載の半導体パッケージであって、

前記第1の端部から前記第2の端部に向かう線に直交して得られる前記複数のバンプ断面の各々が長円形又は円形である、半導体パッケージ。

【請求項13】

請求項9に記載の半導体パッケージであって、

前記信号バンプが、前記電力バンプの平均横方向幅よりも小さい平均横方向幅を有する、半導体パッケージ。

20

【請求項14】

請求項13に記載の半導体パッケージであって、

前記複数のバンプの第2の端部と前記リードフレームとの間に配置されるはんだ材料と、

前記リードフレームの第1及び第2のリードと前記半導体ダイと前記複数のバンプとを少なくとも部分的に覆うモールド化合物と、

を更に含む、半導体パッケージ。

【請求項15】

請求項9に記載の半導体パッケージであって、

前記リードフレームが金属製である、半導体パッケージ。

【請求項16】

半導体パッケージにおけるリードフレームにダイを取り付けるために、前記ダイ上に複数の先細りにされたバンプを形成する方法であって、

30

ウェハ上にシード材料を堆積することと、

前記シード材料上にフォトレジストを堆積することと、

バンプサイトを備えるパターンに従って前記フォトレジストをマスクすることと、

中に複数の先細りにされたサイトを形成するために前記マスクされたフォトレジストを過剰露出させることであって、先細りにされたサイトの各々が、前記ウェハに最も近い第1の端部と、前記ウェハから最も遠い第2の端部とを有する、前記マスクされたフォトレジストを過剰露出させることと、

1つ又はそれ以上の金属を前記複数の先細りにされたサイトに配置することと、

前記複数の先細りにされたバンプを形成するために前記フォトレジストを除去することであって、前記複数の先細りにされたバンプの先細りにされたバンプの各々が、前記ウェハに最も近い前記第1の端部において第1の表面面積A1を有し、前記ウェハから最も遠い第2の端部において第2の表面面積A2を有し、前記先細りにされたバンプの第1の端部が前記ウェハに接し、前記第1の表面面積A1が前記第2の表面面積A2よりも小さい、前記フォトレジストを除去することと、

40

前記ウェハを複数のダイに個片化することと、

を含み、

前記複数の先細りにされたバンプが、電力信号を伝送するように構成される複数の電力バンプと、電気信号を伝送するように構成される複数の信号バンプとを含み、

50

前記複数の電力バンプが直線状に配置され、前記複数の信号バンプが直線状に配置され、前記複数の電力バンプと前記複数の信号バンプとが並行に配置される、方法。

**【請求項 17】**

請求項 16 に記載の方法であって、

前記第 2 の端部表面面積 A 2 が、前記第 1 の表面面積 A 1 よりも 10 パーセント大きい、方法。

**【請求項 18】**

請求項 16 に記載の方法であって、

前記第 2 の表面面積 A 2 が、前記第 1 の表面面積 A 1 の少なくとも 2 倍である、方法。

**【請求項 19】**

請求項 16 に記載の方法であって、

前記複数の先細りにされたサイトの各々が、前記リードフレームに面する前記ダイの表面に対して約 70 度又はそれより小さい側壁傾斜を備えて形成される、方法。

10

**【請求項 20】**

請求項 16 に記載の方法であって、

前記複数の先細りにされたバンプの各々が、曲線形状を有する横方向断面を有する、方法。

**【請求項 21】**

請求項 20 に記載の方法であって、

前記複数の先細りにされたバンプの各々が、円形又は長円形形状の横方向断面を有する方法。

20

**【請求項 22】**

半導体ダイをリードフレームに電気的に結合する方法であって、

前記半導体ダイ上に電力バンプと信号バンプとを含む複数の先細りにされたバンプを形成することであって、前記複数の先細りにされたバンプの各々が、前記半導体ダイに最も近い第 1 の端部において第 1 の端部表面面積 A 1 を有し、反対の第 2 の端部において第 2 の端部表面面積 A 2 を有するようにし、前記第 1 の端部表面面積 A 1 が前記第 2 の端部表面面積 A 2 より小さく、前記第 1 の端部が前記半導体ダイに取り付けられる、前記複数の先細りにされたバンプを形成することと、

前記電力バンプの第 2 の端部を前記リードフレームの第 1 のリードにはんだ付けし、前記信号バンプの第 2 の端部を前記リードフレームの第 2 のリードにはんだ付けすることであって、前記第 1 及び第 2 のリードが直線状であって並行に配置される、前記はんだ付けすることと、

30

を含み、

前記電力バンプが電力信号を伝送するように構成され、前記信号バンプが電気信号を伝送するように構成される、方法。

**【請求項 23】**

請求項 22 に記載の方法であって、

前記第 2 の端部表面面積 A 2 が、前記第 1 の端部表面面積 A 1 の少なくとも 2 倍である方法。

40

**【請求項 24】**

請求項 22 に記載の方法であって、

前記複数の先細りにされたバンプが、前記先細りにされたバンプの中心線に対して約 70 度又はそれより小さい側壁傾斜を有する、方法。

**【請求項 25】**

請求項 22 に記載の方法であって、

前記複数の先細りにされたバンプの各々が、前記先細りにされたバンプの中心線に直交する横方向断面において長円形形状を有する、方法。

**【発明の詳細な説明】**

**【技術分野】**

50

**【0001】**

本願は、概して半導体デバイスに関し、より詳細には半導体デバイスにおける成形された相互接続バンプに関する。

**【背景技術】****【0002】**

幾つかのタイプの半導体パッケージにおいて、半導体ダイが、複数の相互接続バンプ又はポストを介してリードフレームに直接的に取り付けられる。複数の相互接続バンプは、半導体ダイをリードフレームに電気的に接続する。複数の相互接続バンプは、信号バンプ及び電力バンプの両方を含み得る。信号バンプは概して、半導体ダイとリードフレームとの間の電気信号の送信を主に重要視し得る。電力バンプは概して、リードフレームと半導体ダイとの間で電力のバルクを送信することを主に重要視し得る。接続の密度が増加するにつれて、相互接続性はより難しくなってきている。

10

**【発明の概要】****【0003】**

一態様において、半導体パッケージが、リードフレームと、複数のバンプを介してリードフレームに取り付けられる半導体ダイとを含む。複数のバンプの各々は、半導体ダイに接続される第1の端部と、リードフレームに接続される反対の第2の端部とを含む。第1の端部は、端部表面面積A1を有する。第2の端部は、端部表面面積A2を有する。第1の端部の端部表面面積A1は、第2の端部の端部表面面積A2よりも小さい。

20

**【0004】**

一態様において、半導体パッケージが、リードフレーム、リードフレームに取り付けられる半導体ダイ、及び、半導体ダイとリードフレームとを電気的に接続する複数のバンプを含む。バンプは、第1の端部から、反対の第2の端部まで延在する長手方向長さを有する。第1の端部は半導体ダイに接続され、第2の端部はリードフレームに接続される。第1の端部は、第2の端部の横方向幅W2よりも小さい、長手方向長さに直交する横方向幅W1を有する。

**【0005】**

一態様に従って、半導体パッケージにおけるリードフレームにダイを取り付けるためにダイ上に複数の先細りにされたバンプを形成する方法が、ウェハ上にシード材料を堆積させること、シード材料上にフォトレジストを堆積させること、バンプサイトを有するパターンに従ってフォトレジストをマスクすること、及び、中に複数の先細りにされたサイトを形成するため、マスクされたフォトレジストを過剰露出させることを含む。先細りにされたサイトの各々は、ウェハに最も近い第1の端部と、ウェハから最も遠い第2の端部とを有する。この方法は更に、一つ又はそれ以上の金属を複数の先細りにされたサイトに配置すること、及び、フォトレジストを除去して複数の先細りにされたバンプを形成することを含む。複数の先細りにされたバンプの先細りにされたバンプの各々は、ウェハに最も近い第1の端部において第1の表面面積A1を有し、ウェハから最も遠い第2の端部において第2の表面面積A2を有する。先細りにされたバンプの第1の端部はウェハに接し、第1の表面面積A1は、第2の表面面積A2よりも小さい。

30

**【0006】**

一態様に従って、半導体ダイをリードフレームに電気的に結合する方法が、複数の先細りにされたバンプをダイ上に形成することを含み、それにより、複数の先細りにされたバンプの各々が、ダイに最も近い第1の端部における第1の端部表面面積A1と、反対の第2の端部における第2の端部表面面積A2とを有するようにする。第1の端部は、第2の端部表面面積A2未満の端部表面面積A1を有する。第1の端部はダイに取り付けられる。この方法は更に、複数の先細りにされたバンプの第2の端部をリードフレームにはんだ付けすることを含む。他の態様も本明細書に開示される。

40

**【図面の簡単な説明】****【0007】**

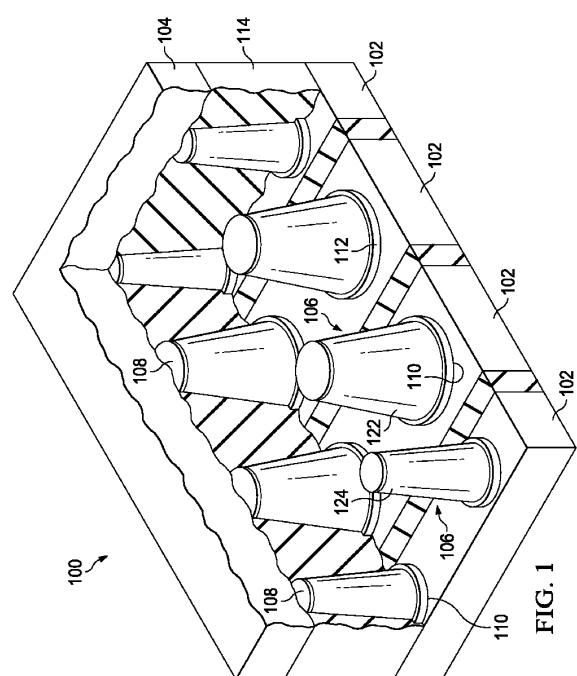

【図1】例示の半導体パッケージの一部の概略斜視図である。

50

【0008】

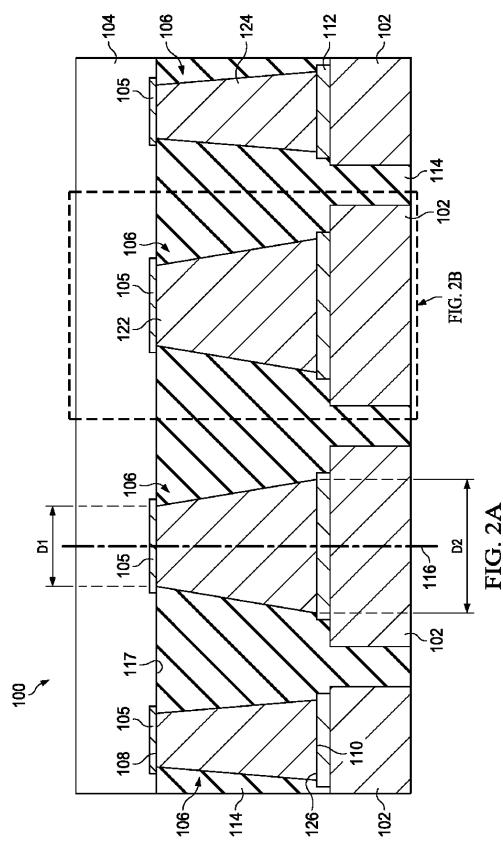

【図2A】図1の例示の半導体パッケージの概略正面図である。

【0009】

【図2B】図2Aの例示の半導体パッケージの一部の概略詳細図である。

【0010】

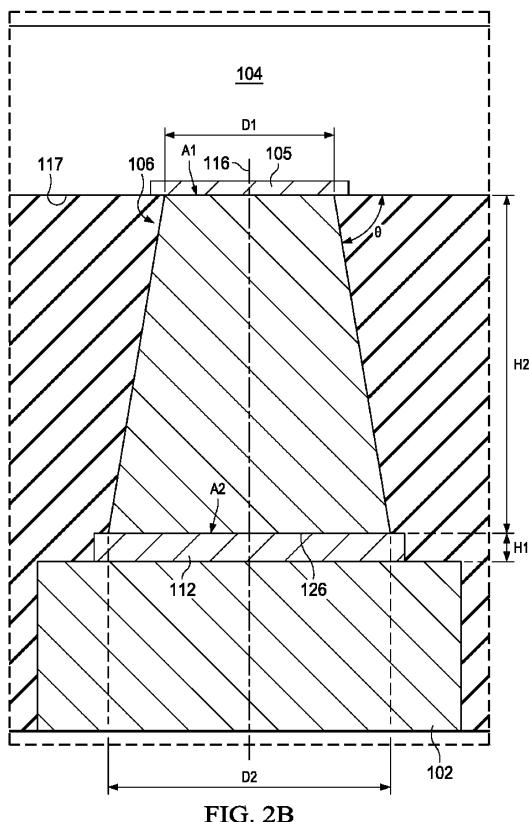

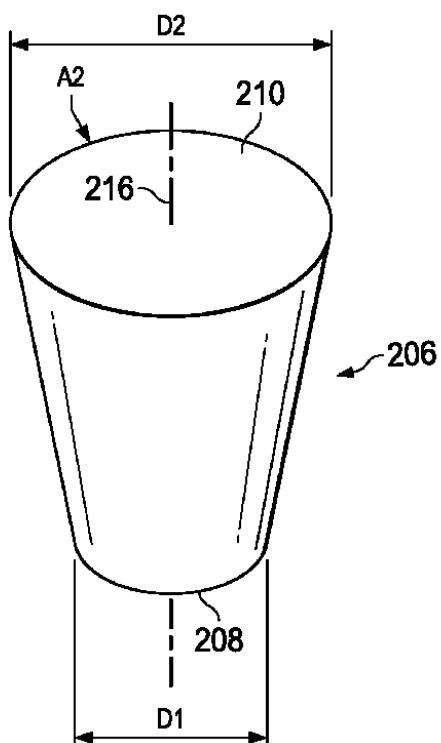

【図3A】例示的な形状の相互接続バンプの一端の概略図である。

【0011】

【図3B】図3Aの成形された相互接続バンプの概略斜視図である。

【0012】

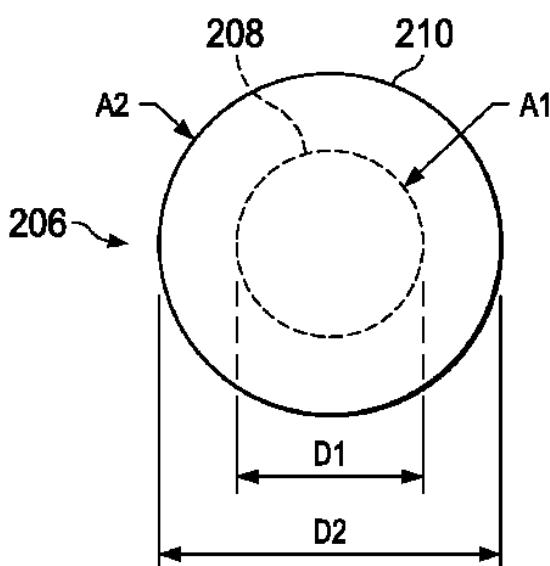

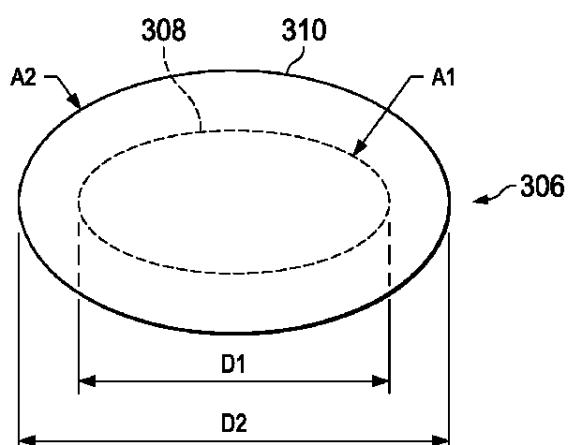

【図4】別の例示的な形状の相互接続バンプの概略図である。

10

【0013】

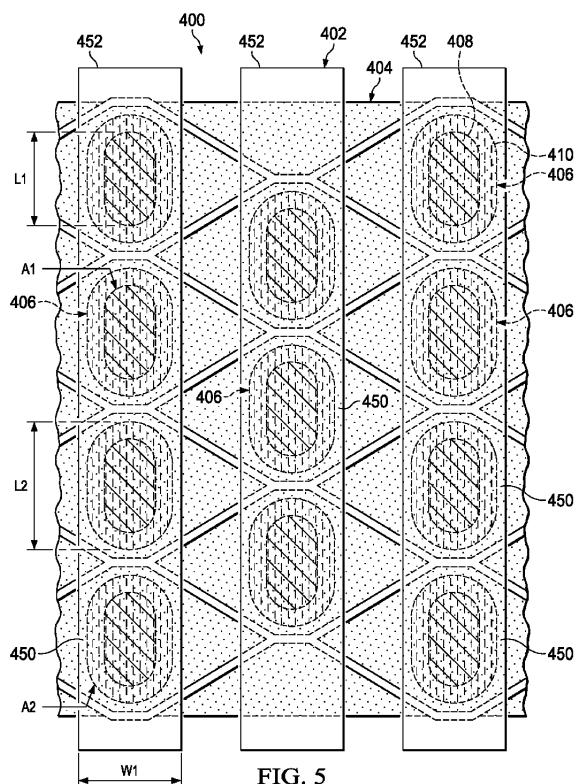

【図5】例示の半導体パッケージの一部の概略平面図である。

【0014】

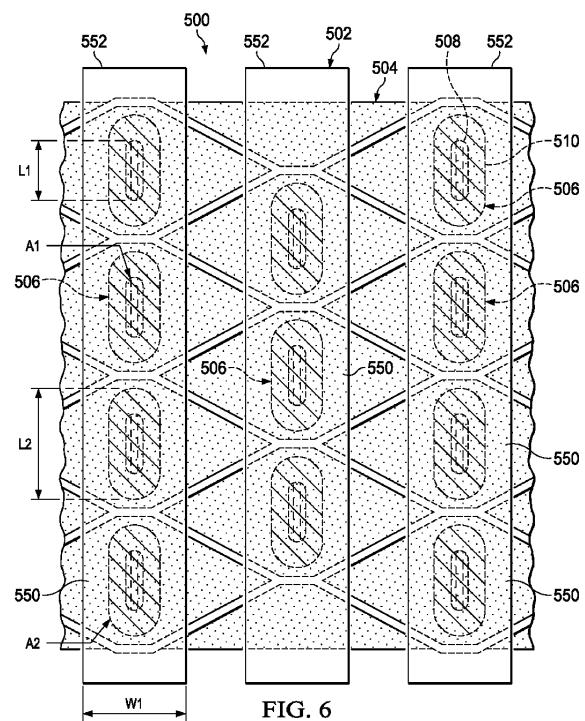

【図6】例示の半導体パッケージの一部の概略平面図である。

【0015】

【図7A】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

【図7B】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

【図7C】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

20

【図7D】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

【図7E】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

【図7F】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

【図7G】成形された相互接続バンプを半導体ウェハ上に形成するためのプロセス工程を示す、断面での概略図である。

【発明を実施するための形態】

30

【0016】

半導体パッケージには、半導体ダイが複数の相互接続バンプ（ポスト又はピラーと称されることもある）を介してリードフレームに直接的に取り付けられるように構成されるものがある。このタイプのパッケージングは、ワイヤボンディングを用いる他のタイプのリード（leaded）パッケージよりも改善された電気的及び熱的性能を提供し得る。また、半導体ダイをリードフレームに接続するワイヤボンドをなくすことにより、パッケージ寄生が低減され得る。

【0017】

しかしながら、半導体ダイは概して、リードフレームと比較して、相互接続バンプ又はバンプに接続するための利用可能な表面面積がより小さい。また、電子機器の普及と機能性の増加に伴い、半導体ダイの寸法を更に低減することが望ましい。その結果、半導体ダイが縮小するにつれて、相互接続バンプ接続のために利用可能な表面面積も減る。相互接続バンプのために半導体ダイ上で利用可能な表面面積は、状況によっては、それ以上無い制限要因である場合もある。

40

【0018】

通常、相互接続バンプは均一な円筒形状を有していた。例えば、相互接続バンプの直径は、相互接続バンプのダイ側とリードフレーム側との間で均一である。そのため、そのダイ接続側における相互接続バンプのコンタクト表面面積は、そのリードフレーム接続側におけるそのコンタクト表面面積と同じである。相互接続バンプの直径を小さくすると、半導体ダイだけでなくリードフレーム上の相互接続バンプのコンタクト表面面積も低減され

50

る。

【0019】

リードフレーム上の相互接続バンプのコンタクト表面面積の低減は、相互接続バンプとリードフレームとの間の接合において電力及び電流密度を増大させる傾向がある。電力及び電流密度が増大すると、相互接続バンプとリードフレームとの間の接合におけるエレクトロマイグレーションに起因して、より高い温度及び早期の欠陥となる可能性がある。相互接続バンプをリードフレームに取り付けるために用いられるはんだ材料は、相互接続バンプをリードフレームに取り付ける際に用いられるはんだ材料の特性に起因して、エレクトロマイグレーションの問題に更に寄与する可能性がある。

【0020】

例えばW C S P 及びQ F Nなどの、小型タイプのパッケージは、それらの小さな寸法に起因して、更にエレクトロマイグレーションが制限され得る。言い換えると、相互接続バンプとリードフレームとの間の接合における電力及び電流密度は、小型タイプのパッケージの寸法が小さいことに起因して、更に大きくなり得る。

【0021】

本明細書の相互接続バンプ及び方法は、上記の制約の少なくとも幾つかに対処する。一配置において、本明細書における相互接続バンプは、ダイ端部上のより狭い第1の端部（例えば、より小さい直径）と、リードフレームにおけるより広い（例えば、より大きな直径）とを有する。相互接続バンプは、ダイ側のバンプの寸法を低減し、はんだ又はリードフレーム側の面積を増大させる。

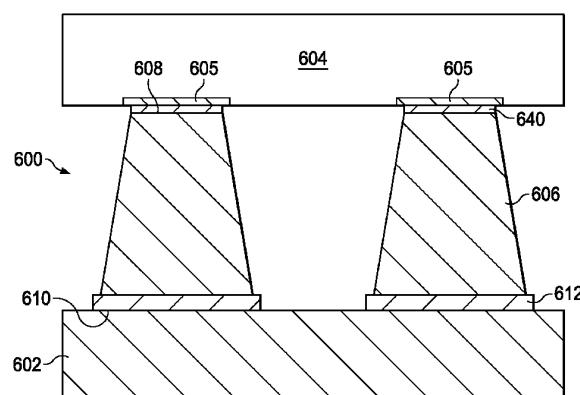

【0022】

主として図1～図2Bを参照すると、半導体パッケージ100が提示されている。半導体パッケージ100は、リードフレーム102、（個片化された、又は依然として半導体ウェハの一部である）半導体ダイ104、及び、半導体ダイ104をリードフレーム102に電気的に結合する複数の相互接続バンプ106又はバンプを含む。ダイ104及びモールディング化合物114の一部は、バンプ106をより良く示すために図1において取り除かれている。

【0023】

幾つかの態様において、リードフレーム102は金属で形成される。複数のバンプ106は、半導体ダイ104に接続される第1の端部108又はダイ端部と、リードフレーム102に接続される反対の第2の端部110又はリードフレーム端部とを含む。バンプ106は、複数のC O A (copper on anything) 要素105に一端において結合されている。

【0024】

他の何らかのバンプが存在してもよいが、複数のバンプ106は、複数のバンプ106の第2の端部110が複数のバンプ106の第1の端部108よりも大きくなるように、角度の付いた形状を有する。バンプ106は円筒の部材ではない。このように、第1の端部108における横方向断面又は端部は、第2の端部112における横方向断面又は端部よりも小さい。複数のバンプ106を、複数のバンプ106の第2の端部110が複数のバンプ106の第1の端部108よりも大きくなるように成形することによって、第1の端部108を半導体ダイ104上に適合させるために充分小さく保ちながら、第2の端部110が、リードフレーム102上で利用可能なより大きな端部表面面積を利用することができる。複数のバンプ106の第2の端部110の寸法を増加させることは、複数のバンプ106の第2の端部110とリードフレーム102との間に流れる電流及び電力密度を減少させるのに役立ち得る。複数のバンプ106の態様については、以下でより詳細に説明する。

【0025】

半導体パッケージ100は更に、複数のバンプ106とリードフレーム102との間に配置される、例えばS n A gなどのはんだ材料112を含む。はんだ材料112は、複数のバンプ106の第2の端部110をリードフレーム102に取り付けるために用いられ

10

20

30

40

50

る。幾つかの態様において、はんだ材料 112 は、錫銀 (SnAg) 合金で形成され得る。他のタイプのはんだを用いてもよい。幾つかの態様において、はんだ材料 112 は、約 20 ~ 30 μm の高さ H1 (図 2B) を有し得る。

#### 【0026】

複数のバンプ 106 の第 2 の端部 110 とはんだ材料 116 との間にはんだバンプインターフェース 126 が形成される。はんだバンプインターフェース 126 は、場合によっては、ボイド伝搬を含むエレクトロマイグレーションの問題を被る。電流密度の増大は、はんだバンプインターフェース 126 の破壊に寄与し得、これは信頼性の問題を起こし得、半導体ダイ 104 における幾つかのタイプの能動回路を複数のバンプ 106 の近隣に配置することを妨げ得る。複数のバンプ 106 の第 2 の端部 110 の寸法を増加させることによって、はんだバンプインターフェース 126 を流れる電流密度が減少され得、それによって、はんだバンプインターフェース 126 の寿命が増大する。同様に、複数のバンプ 106 の第 2 の端部 110 の寸法を増加させることは、電流交換の効率を増加させ得、これは、はんだバンプインターフェース 126 における熱出力の低下をもたらし得る。

#### 【0027】

幾つかの態様において、半導体パッケージ 100 は更に、半導体パッケージ 100 の構成要素を保護するためのモールディング化合物 114 (図 2A 及び図 2B) を含む。モールディング化合物 114 は、半導体パッケージ 100 に構造的支持を提供することができ、リードフレーム 102、半導体ダイ 104、複数のバンプ 106、又はそれらの任意の組み合わせの少なくとも一部を覆い得る。幾つかの態様において、モールディング化合物 114 は更に、例えば、複数のバンプ 106 の間など、半導体パッケージ 100 の構成要素の間のギャップを充填し得る。更に幾つかの態様において、モールディング化合物 114 は、エポキシ、ポリマー、又はその他の絶縁材料である。

#### 【0028】

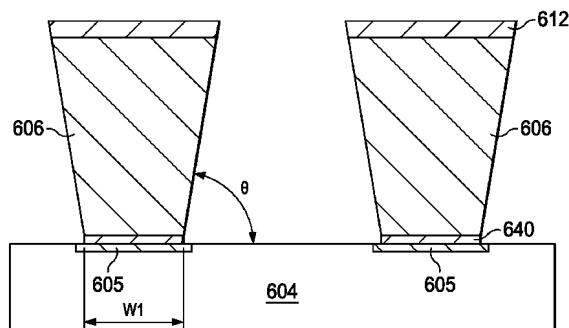

更に主として図 1 ~ 図 2B を参照すると、複数の相互接続バンプ 106 は、第 1 の端部上の半導体ダイ 104 と、長手方向軸 116 (図 2A 及び図 2B) 又は中心線に沿った第 2 の端部上のリードフレーム 102 との間に延在する。複数の相互接続バンプ 106 は、ピラー又はバンプとも称される。複数の相互接続バンプ 106 の各々は、長手方向軸 116 の方向の側壁上に或る角度を成す形状を有する。複数の相互接続バンプ 106 の各相互接続バンプ 106 の第 1 の端部 108 は、第 2 の端部 110 の幅又は直径 D2 より小さい幅又は直径 D1 を有する。各複数の相互接続バンプ 106 の第 1 の端部 108 はまた、複数の相互接続バンプ 106 の第 2 の端部 110 の端部表面面積 A2 より小さい端部表面面積 A1 を有する。言い換えれば、複数の相互接続バンプ 106 の第 1 の端部 108 は、複数の相互接続バンプ 106 の第 2 の端部 110 よりも小さい。一例において、A1 が A2 よりも少なくとも 10 パーセント小さい。一例において、A2 は A1 の少なくとも 2 倍である。

#### 【0029】

幾つかの態様において、複数の相互接続バンプ 106 の各々は、複数の相互接続バンプ 106 の各々が第 2 の端部 110 から第 1 の端部 108 に向かって寸法が減少するよう、第 2 の端部 110 から第 1 の端部 108 に先細りにされている。幾つかの態様において、第 2 の端部 110 の端部表面面積 A2 は、第 1 の端部 108 の端部表面面積 A1 の寸法の 1 倍から最大 3 倍大きくし得る。更に幾つかの態様において、第 2 の端部 110 の端部表面面積 A2 は、第 1 の端部 108 の端部表面面積 A1 の寸法の約 2 倍であり得る。第 2 の端部 110 の端部表面面積 A2 と第 1 の端部 108 の端部表面面積 A1 との間の比は、半導体ダイ 104 上の利用可能な表面面積及び相互接続バンプ接続のためのリードフレーム 102 に基づいて改変され得る。

#### 【0030】

図 1 ~ 図 2B は、複数の相互接続バンプ 106 の第 2 の端部 110 が、複数の相互接続バンプ 106 の第 1 の端部 108 より大きいことを示しているが、幾つかの例において、複数の相互接続バンプ 106 の第 2 の端部 110 が、複数の相互接続バンプ 106 の第 1

10

20

30

40

50

の端部 108 より小さいことが有益となり得る。したがって、幾つかの態様において、複数の相互接続バンプ 106 の第 2 の端部 110 の表面面積 A2 は、第 1 の端部 108 の表面面積 A1 の寸法の 1 倍より小さくし得る。更に幾つかの態様において、複数の相互接続バンプ 106 の第 2 の端部 110 の表面面積 A2 は、第 1 の端部 108 の表面面積 A1 の寸法の約 0.75 倍とし得る。

#### 【0031】

幾つかの態様において、複数の相互接続バンプ 106 は、長手方向軸 116 を横切るか又は長手方向軸 116 に直交する円形断面形状又は他の曲線形状を有して、長手方向軸 116 に沿った切頭円錐又は錐台形状を有する。更に幾つかの態様において、複数の相互接続バンプ 106 は、長手方向軸 116 を横切るか又は長手方向軸 116 の横方向の長円形断面形状を有して、長手方向軸 116 に沿った或る角度を成す形状を有する。複数の相互接続バンプ 106 は、第 2 の端部 110 の表面面積 A2 が第 1 の端部 108 の表面面積 A1 と異なっている限り、長手方向軸 116 に沿って幾つかの或る角度を成す形状をとることができる。

10

#### 【0032】

幾つかの態様において、複数の相互接続バンプ 106 は、半導体ダイ 104 の表面 117 に対して約 70 度又はそれより小さい傾斜 を有する側壁を有する。一配置において、勾配 は 45° ~ 90° である。複数の相互接続バンプ 106 は、高さ H2 (図 2B)、又は長手寸法を有する。幾つかの態様において、複数の相互接続バンプ 106 の高さ H2 は、約 35 ~ 75 μm である。更に幾つかの態様において、複数の相互接続バンプ 106 の高さ H2 は約 50 μm である。複数の相互接続バンプ 106 は導電性材料で形成される。幾つかの態様において、複数の相互接続バンプ 106 は、銅 (Cu) 又は銅合金で形成される。

20

#### 【0033】

角度 は、所望の端部表面面積関係を達成するように選択され得る。1 つの例示的な配置において、端部表面面積 A2 は、端部表面面積 A1 の 2 倍であることが望ましい。バンプは、横方向断面において円形であり、中心線 116 に沿って h の高さを有し、第 1 の端部において b の横方向幅又は直径を有し、第 2 の端部における直径が  $b + 2a$  によって与えられると仮定すると、角度 を見つけるために下記が用いられ得る。

30

$$\tan(90 - \theta) = a / h$$

$$\tan(\theta) = h / a$$

$$a = h / \tan(\theta)$$

再び、円形の断面を仮定すると、面積を倍にするため下記となる。

$$b + 2a = (2)^{1/2} \times b$$

$$b + 2(h / \tan(\theta)) = (2)^{1/2} \times b$$

$$h / \tan(\theta) = 1/2b((2)^{1/2} - 1) = 0.2071 \times b$$

$$\tan(\theta) = h / (0.2071 \times b)$$

$$= a \tan(h / 0.2071b)$$

したがって、 $h = 50$  ミクロン及び $b = 100$  ミクロンである場合、 $\theta$  は 67°、 $a = 20.7$  ミクロンとなる。

40

#### 【0034】

依然として主に図 1 ~ 図 2B を参照すると、幾つかの態様において、複数の相互接続バンプ 106 は、複数の電力バンプ 122 及び複数の信号バンプ 124 を含み得る。複数の電力バンプ 122 は、少なくとも半導体ダイ 104 とリードフレーム 102 との間の電力伝送の大部分を伝送するように構成される。複数の信号バンプ 124 は、半導体ダイ 104 とリードフレーム 102 との間で電気信号を送信するように構成される。幾つかの態様において、複数の電力バンプ 122 は、平均断面面積 (横方向断面) に関する複数の信号バンプ 124 よりも大きい。複数の電力バンプ 122 は、複数の電力バンプ 122 を介して交換される電流が複数の信号バンプ 124 を介して交換される電流よりも大きくなる傾向があるため、複数の信号バンプ 124 よりも大きくし得る。

50

## 【 0 0 3 5 】

幾つかの態様において、複数の電力バンプ 122 の少なくとも一部が、先細りにされるか、さもなければ、長手方向断面において或る角度を成す形状を有する。更に幾つかの態様において、複数の電力バンプ 122 の少なくとも幾つか及び複数の信号バンプ 124 の少なくとも幾つかが、先細りにされるか、さもなければ、或る角度を成す形状を有する。複数の信号バンプ 124 及び電力バンプ 122 は、前述のように形成される。

## 【 0 0 3 6 】

主として図 3 A 及び 3 B を参照すると、幾つかの態様に従った相互接続バンプ 206 が提示されている。相互接続バンプ 206 は、図 1 の複数の相互接続バンプ 106 のうちの 1 つであり得る。図 3 A は、相互接続バンプ 206 の概略端部（図 1 を参照した第 2 の端部）の図であり、相互接続バンプ 206 の第 1 の端部が隠れた線を介して示されている。図 3 B は、図 3 A の相互接続バンプ 206 の概略斜視図である。幾つかの態様において、相互接続バンプ 206 が、切頭円錐形状又は切頭円錐又は切頭円錐形状を有すると称される場合もある。相互接続バンプ 206 は、長手方向軸 216（又は中心線）を横切る円形断面形状、即ち横方向断面、を有するが、他の形状（楕円形、正方形、多角形など）も用いられ得る。幾つかの配置において、横方向断面は曲線状である。

10

## 【 0 0 3 7 】

相互接続バンプ 206 は、第 1 の端部 208 と、反対の第 2 の端部 210 とを有する。相互接続バンプ 206 の第 1 の端部 208 は、図 1 に示されている半導体ダイ 104 などの半導体ダイに取り付けるためのものである。相互接続バンプ 206 の第 2 の端部 210 は、図 1 に示すリードフレーム 102 などのリードフレーム又は他の導電性材料に取り付けるためのものである。相互接続バンプ 206 は、相互接続バンプ 206 が第 2 の端部 210 から第 1 の端部 208 に向かって寸法が減少するように、長手方向断面において最もよく見える先細りにされた形状を有する。図 3 B によく示されているように、相互接続バンプ 206 の第 1 の端部 208 は、相互接続バンプ 206 の第 2 の端部 210 の直径 D2 よりも小さい直径 D1 を有する。相互接続バンプ 206 の第 1 の端部 208 はまた、相互接続バンプ 206 の第 2 の端部 210 の第 2 の表面面積 A2 ( $\times (D2/2)^2$ ) よりも小さい第 1 の端部表面面積 A1 ( $\times (D1/2)^2$ ) を有する。相互接続バンプ 206 の第 1 の端部 208 及び第 2 の端部 210 はいずれも、1 つの配置において円形の断面形状を有する。

20

## 【 0 0 3 8 】

主として図 4 を参照すると、幾つかの態様に従った、相互接続バンプ 306 の第 2 の端部の概略図が示され、ここでは、相互接続バンプ 306 の第 1 の端部（より狭い端部）が、隠れた線を介して示される。相互接続バンプ 306 は、相互接続バンプ 306 がページ内へ延在する長手方向軸（軸 116、216 に類似）に対して横断方向又は直交方向である長円形断面形状を有する点で、図 3 A ~ 図 3 B の相互接続バンプ 206 とは異なる。相互接続バンプ 306 は、第 1 の端部 308 と、反対の第 2 の端部 310 とを有する。相互接続バンプ 306 の第 1 の端部 308 は、図 1 に示されている半導体ダイ 104 などの半導体ダイに取り付けるためのものである。相互接続バンプ 306 の第 2 の端部 310 は、図 1 に示すリードフレーム 102 などのリードフレームに取り付けるためのものである。

30

## 【 0 0 3 9 】

相互接続バンプ 306 は、相互接続バンプ 306 が第 2 の端部 310 から第 1 の端部 308 に向かって寸法が減少するように、その長手寸法に沿って先細りにされた形状を有する。相互接続バンプ 306 の第 1 の端部 308 は、相互接続バンプ 306 の第 2 の端部 310 の幅（横方向断面における長い寸法）よりも小さい幅（横方向断面における長い寸法） D1 を有する。相互接続バンプ 306 の第 1 の端部 308 はまた、相互接続バンプ 306 の第 2 の端部 310 の第 2 の表面面積 A2 よりも小さい第 1 の表面面積 A1 を有する。一例において、A1 は A2 の 10% より小さい。一配置において、A2 は A1 の少なくとも 2 倍である。図 4 は、長円形の横方向断面を示すが、例えば、曲線状、円形、多角形、正方形、円形、長円形、長方形、及び丸い角を有する多角形などの他の断面形状を用いて

40

50

もよいことを理解されたい。

【0040】

主として図5を参照すると、例示的な配置に従った半導体パッケージ400の一部の概略平面図が示されている。半導体パッケージ400は、複数の成形された或る角度を成す相互接続バンプ406を介して半導体ダイ404に接続されるリードフレーム402を含む。半導体パッケージ400は、本明細書に示される複数の成形された或る角度を成す相互接続バンプ406などの相互接続バンプが、半導体ダイ404及びリードフレーム402などの半導体パッケージ400内の構成要素の寸法又は配置に基づいて、どのように構成され得るかの例を提供する。半導体ダイ404は、例えば、250～100ナノメートルプロセスとすることができる。半導体ダイ404は、相互接続バンプ406への接続のためのランディングサイト450を有する。幾つかの態様において、半導体ダイ404上のランディングサイト450は、約25～400ミクロンの幅又は直径を有し得る。リードフレーム402は、例えば、約35～600ミクロンの断面幅W1を有するランディングサイト452又は要素を有し得る。

【0041】

相互接続バンプ406の第1の端部408が半導体ダイ404に接続され、相互接続バンプ406の第2の端部410がリードフレーム402に接続される。第1の端部408は、長さL1を有する表面面積A1を有し、第2の端部410は、表面面積A2及び長さL2を有する。相互接続バンプ406の第1の端部408の表面面積A1及び幅W1は、通常、少なくとも部分的に、半導体ダイ404上のランディングサイト450の寸法によって制限される。ランディングサイト450は、相互接続バンプ406の少なくとも一部を受けるためのダイ上の領域である。しかしながら、リードフレーム402上のランディングサイト452は、通常、半導体ダイ404上のランディングサイト450より大きく、したがって、より大きな相互接続バンプ又は相互接続バンプ406の一部を収容し得る。そのため、複数の相互接続バンプ406は、リードフレーム402に接続される第2の端部410の表面面積A2及び幅W2が、半導体ダイ404に接続される第1の端部408の表面面積A1及び幅W1より大きくなるように成形される。このようにして、複数の相互接続バンプ406は、リードフレーム402上の利用可能なより大きな表面面積を活用することができる。複数の成形された或る角度を成す相互接続バンプ406の形状、例えば、複数の相互接続バンプ406の第1の端部408及び第2の端部410の寸法は、半導体ダイ404上のランディングサイト450及びリードフレーム402上のランディングサイト452の利用可能な寸法に基づいて変更され得る。複数の成形された相互接続バンプ406は、半導体ダイ404に接続されるように構成された端部（第1の端部408）が、リードフレーム402に接続されるように構成された端部（第2の端部410）よりも小さな表面面積を有するように、角度を成すかその他の方式で不均一である。

【0042】

主として図6を参照すると、例示的な配置に従った半導体パッケージ500の一部の概略図が提示されている。半導体パッケージ500は、複数の成形された或る角度を成す相互接続バンプ506を介して半導体ダイ504に接続されるリードフレーム502を含む。半導体パッケージ500は、半導体ダイ504が図5に図示される半導体ダイ404よりも小さく、その結果、より小さなランディングサイト550を有することを除いて、図5に示された半導体パッケージ400に類似している。成形された或る角度を成す複数の相互接続バンプ506は少なくとも部分的に半導体ダイ504上のランディングサイト550の寸法に基づいて構成されている。半導体ダイ504は、例えば、100ナノメートル未満のプロセス生成ダイであり得る。幾つかの態様において、半導体ダイ504上のランディングサイト550は、約0.3×0.3mm～10×10mmの幅を有し得る。幾つかの態様において、リードフレーム502上のランディングサイト552は、図5のリードフレーム402上のランディングサイト452の幅W1に類似する又は幅W1と同じであり得る幅W1を有する。そのため、リードフレーム502上のランディングサイト552は、図5のリードフレーム402上のランディングサイト452と同じ寸法であり得

10

20

30

40

50

る。複数の成形された或る角度を成す相互接続バンプ 506 の形状、例えば、複数の相互接続バンプ 506 の第 1 の端部 508 (ダイ側) 及び第 2 の端部 510 (リードフレーム側) の寸法は、半導体ダイ 504 上のランディングサイト 550 及びリードフレーム 502 上のランディングサイト 552 の利用可能な寸法に基づいて改変され得る。

#### 【0043】

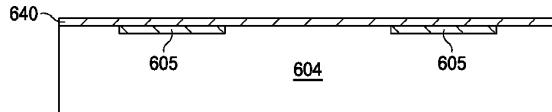

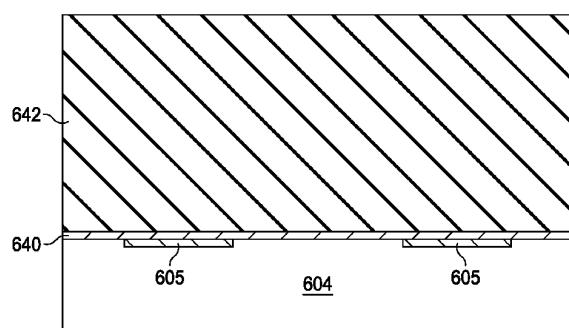

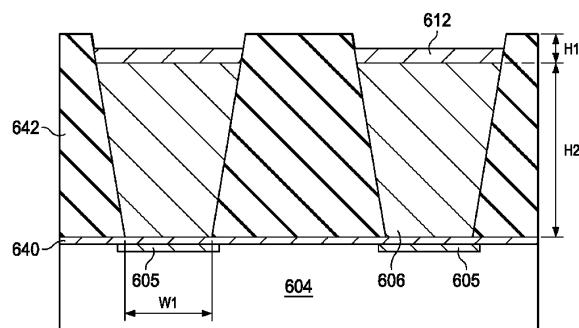

主として図 7A ~ 図 7G を参照すると、半導体パッケージ 600 (半導体パッケージ 100、400、500 にほとんどの点で類似) の一部を形成するためのプロセス工程を表す概略図が提示されている。まず図 7A ~ 図 7B を参照すると、シード層 640 (図 7B) が、適切な形成プロセスを介して、半導体ウェハ 604 上、又はシンギュレーション後にダイになるものの上に配置される。ウェハ 604 は、複数の COA (copper on anything) 要素 605 を有する。幾つかの態様において、シード層 640 は、化学気相成長 (CVD) 又はスパッタ堆積によって、半導体ダイ 604 又はウェハ上に配置され得る。配置によっては、シード層 640 は、チタン (Ti) 及びチタンタングステン (TiW) を含み得る。

#### 【0044】

主として図 7C を参照すると、COA 605 の上にあるシード層 640 上にフォトレジスト 642 が堆積される。フォトレジストパターンに従って、フォトレジスト 642 上にマスク (明示せず) が配置される。フォトレジストパターンは、相互接続バンプのためのサイトの位置を特定する。

#### 【0045】

図 5 及び図 6 を比較すると、バンプ 406、506 の先細りが、リードフレーム 402 を同じ寸法に保つが、その後、ウェハ / ダイ 504 上のより小さな面積を用いるために第 1 の側 (図 5) の端部表面面積を減少させるために用いられ得るか、又は、バンプ 406 は、端部表面面積をダイ / ウェハ (図 6) における第 1 の端部において同じに保つが、第 2 の端部における端部表面面積又はそれらの幾らかの組み合わせを拡大するために用いられ得ることを理解されたい。

#### 【0046】

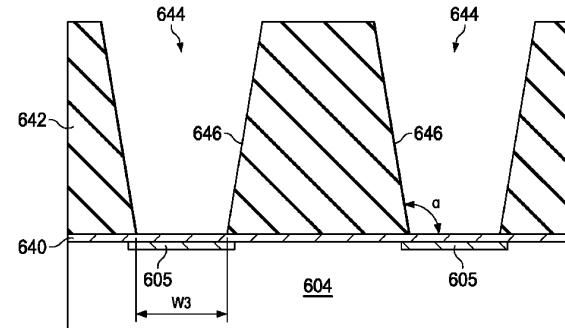

主として図 7D を参照すると、フォトレジスト 642 は、フォトレジストパターンに従ってフォトレジスト 642 内に複数の開口 644 を形成するために、光に曝される。複数の開口 644 は、シード層 640 までずっと延在する。複数の開口 644 の各々は、傾斜した側壁 646 によって画定される。幾つかの態様において、側壁 646 は、約 110 度又はそれ以上の角度 (図 2B では  $= 180 -$ ) 傾斜している。傾斜した側壁 646 は、フォトレジスト 642 を過剰露出させることによって達成され得る。幾つかの態様において、側壁 646 の角度 は、フォトレジスト 642 への光露光量に基づいて変化し得る。側壁 646 の角度 は、複数の相互接続バンプ 606 の所望の寸法又は形状に基づいて変更され得る。

#### 【0047】

複数の開口の各々は、シード層 640 に近接する開口 644 の最低 (図示の向きに対しても) 部分に沿った幅 W3 (図 7D) を有する。複数の開口 644 の幅 W3 は、複数の相互接続バンプ 606 の第 1 の端部 608 の幅 W1 (図 7E) に対応する。幾つかの態様において、複数の開口 644 の一部が、複数の開口 644 の他のものとは異なる寸法を有する。例えば、開口 644 の最低部分に沿った幅は、電力バンプ開口のための幅よりも小さい信号バンプ開口のための幅と異なり得る。

#### 【0048】

主として図 7E を参照すると、複数の開口 644 に金属が堆積される。金属は、銅及びはんだのプレートバンプとして堆積され得る。そして、フォトレジストを除去して、図 7G に示される段階となる。

#### 【0049】

主として図 7G を参照すると、複数の相互接続バンプ 606 は、複数の開口 644 の各々におけるウェハ上のシード層 640 上に形成される。複数の相互接続バンプ 606 は、

10

20

30

40

50

複数の開口 644 の最低部分に沿った傾斜され又は或る角度を成す側壁 646 及び幅 W3 (図 7D) によって少なくとも部分的に画定されるように、複数の開口 644 の形状をとる。

【0050】

複数の相互接続バンプ 606 は、めっきなどのプロセスによって形成され得る。複数の相互接続バンプ 606 を形成するために用いられる材料は、所望の高さまでめっきされ得る。一例において、複数のバンプ 606 の高さ H2 (図 7E) は、約 35 ~ 75  $\mu\text{m}$  である。幾つかの態様において、複数の相互接続バンプ 606 は銅で形成される。幾つかの態様において、フォトレジスト 142 が除去される前に、複数の相互接続バンプ 106 の第 2 の端部 110 上にはんだ材料 612 が配置される。幾つかの態様において、はんだ材料 112 の高さ H1 (図 7E) は約 20 ~ 30  $\mu\text{m}$  であり得る。

10

【0051】

複数の相互接続バンプ 606 が複数の開口 644 内に形成された後、フォトレジスト 642 は、アッシングなどの適切な除去プロセスによって取り除かれるか又は剥離される。また、フォトレジスト 642 を除去した後、複数の相互接続バンプ 606 の直下にないシード層 640 の部分は、エッチングなどの適切な除去プロセスによって除去され得る。

【0052】

主として図 7G を参照すると、次いで、はんだ材料 612 をリードフレーム 602 にはんだ付けすることによって、半導体ダイ 604 がリードフレーム 602 に取り付けられ得る。幾つかの態様において、フォトレジスト 642 が半導体ダイ 604 から除去された後、はんだ材料 612 が複数の相互接続バンプ 606 の第 2 の端部 610 上に配置される。半導体ダイ 604 をリードフレーム 602 に取り付けるプロセスは、半導体ダイ 604 を反転させることと称することができる。

20

【0053】

本明細書に記載されるような成形されたバンプを有することには、多くの考えられる利点がある。成形された又は非円筒のバンプは、ウェハノダイ側に一層小さなランディング面積を提供し、リードフレーム側に一層大きな面積を提供する。これにより、ウェハノダイ上でより多くの相互接続が可能になる一方で、リードフレーム上のより大きな接続が効率性を得ることも可能になり得る。最終的なファブプロセス工程 (「METTOP」) 後のダイの頂部上の任意選択のポリアミド (PI) 又は金属層 (通常は銅) を、バンプとウェハとの間で用いることもできる。はんだインタフェースは低減され得、電流定格が増大され得る。付加的なマスクは必要とされない。全体的なパッケージ寸法は低減され得る。これらは、考えられる利点の一部にすぎない。

30

【0054】

本発明の特許請求の範囲内で、説明した例示の実施例に改变が成され得、他の実施例が可能である。

40

50

【図面】

【図1】

【図2 A】

10

20

30

40

50

【図 2 B】

FIG. 2B

【図 3 A】

FIG. 3A

10

20

【図 3 B】

FIG. 3B

【図 4】

FIG. 4

30

40

50

【図5】

FIG. 5

【図6】

FIG. 6

10

20

30

【図7A】

FIG. 7A

【図7B】

FIG. 7B

40

50

【図 7 C】

FIG. 7C

【図 7 D】

FIG. 7D

10

【図 7 E】

FIG. 7E

【図 7 F】

FIG. 7F

20

【図 7 G】

FIG. 7G

30

40

50

---

フロントページの続き

米国(US)

(31)優先権主張番号 62/568,331

(32)優先日 平成29年10月5日(2017.10.5)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/568,333

(32)優先日 平成29年10月5日(2017.10.5)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 16/103,839

(32)優先日 平成30年8月14日(2018.8.14)

(33)優先権主張国・地域又は機関

米国(US)

審判官 棚田 一也

(56)参考文献 特開2014-179364 (JP, A)

特表2014-521935 (JP, A)

特開平10-178047 (JP, A)

特開2015-149459 (JP, A)

特開2017-152646 (JP, A)

米国特許出願公開第2013/0134568 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H01L 21/60

H01L 23/50