(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7510396号**

**(P7510396)**

(45)発行日 令和6年7月3日(2024.7.3)

(24)登録日 令和6年6月25日(2024.6.25)

(51)国際特許分類

H 0 1 L 27/146 (2006.01)

F I

H 0 1 L

27/146

A

請求項の数 14 (全23頁)

|          |                             |          |                                            |

|----------|-----------------------------|----------|--------------------------------------------|

| (21)出願番号 | 特願2021-132950(P2021-132950) | (73)特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22)出願日  | 令和3年8月17日(2021.8.17)        | (74)代理人  | 110003281<br>弁理士法人大塚国際特許事務所                |

| (65)公開番号 | 特開2023-27686(P2023-27686A)  | (72)発明者  | 白髪 大貴<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

| (43)公開日  | 令和5年3月2日(2023.3.2)          | (72)発明者  | 関根 寛<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内     |

| 審査請求日    | 令和5年6月16日(2023.6.16)        | (72)発明者  | 若嶋 駿一<br>東京都大田区下丸子3丁目30番2号<br>キヤノン株式会社内    |

|          |                             | (72)発明者  | 豊口 銀二郎                                     |

最終頁に続く

(54)【発明の名称】 光電変換装置、その製造方法及び機器

**(57)【特許請求の範囲】****【請求項 1】**

光電変換装置であって、

第1面と、前記第1面とは反対側の第2面と、前記第1面と前記第2面との間にある第1層と、前記第1層と前記第2面との間にある第2層と、を有する基板と、

前記基板に形成された複数の画素回路と、を備え、

前記複数の画素回路のそれぞれは、第1光電変換素子と、第2光電変換素子と、前記第1光電変換素子から信号電荷を転送するための第1転送ゲートと、前記第2光電変換素子から信号電荷を転送するための第2転送ゲートと、を有し、

前記第1光電変換素子は、

前記第1層に位置し、入射光に応じた信号電荷を生成するための第1不純物領域と、

前記第2層に位置し、前記第1不純物領域で生成された信号電荷を前記第1転送ゲートに向けて輸送するための第2不純物領域と、を有し、

前記第2光電変換素子は、

前記第1層に位置し、入射光に応じた信号電荷を生成するための第3不純物領域と、

前記第2層に位置し、前記第3不純物領域で生成された信号電荷を前記第2転送ゲートに向けて輸送するための第4不純物領域と、を有し、

前記第1層は、前記第1不純物領域と前記第3不純物領域との間に位置する第1分離領域をさらに有し、

前記第2層は、前記第2不純物領域と前記第4不純物領域との間に位置する第2分離領

10

20

域をさらに有し、

前記複数の画素回路のうちの少なくとも1つの画素において、

前記第1面に対する平面視において前記第1分離領域と前記第2分離領域とが互いに異なる方向に延在し、

前記第2不純物領域は、前記第1面に対する平面視において前記第1分離領域に重なる第1部分と、前記第1転送ゲートに隣接する第2部分と、前記第1部分に対して前記第2部分の反対側にある第3部分と、を含み、

前記第2不純物領域は、信号電荷にとって、前記第3部分から前記第2部分へ単調に低下する電位分布を有し、

前記第2不純物領域の前記第3部分では、前記第2不純物領域の前記第2部分よりも、信号電荷とは反対の導電型の不純物の濃度が高いことを特徴とする光電変換装置。

10

#### 【請求項2】

前記少なくとも1つの画素において、

前記第4不純物領域は、前記第1面に対する平面視において前記第1分離領域に重なる第4部分と、前記第2転送ゲートに隣接する第5部分と、前記第4部分に対して前記第5部分の反対側にある第6部分と、を含み、

前記第3不純物領域から前記第4不純物領域の前記第5部分へ信号電荷が輸送され、

前記第4不純物領域の前記第6部分では、前記第4不純物領域の前記第5部分よりも、前記反対の導電型の不純物の濃度が高いことを特徴とする請求項1に記載の光電変換装置。

20

#### 【請求項3】

前記第2不純物領域の前記第1部分では、前記第2不純物領域の前記第3部分よりも、信号電荷と同じ導電型の不純物の濃度が高いことを特徴とする請求項1又は2に記載の光電変換装置。

#### 【請求項4】

前記第2不純物領域の前記第2部分では、前記第2不純物領域の前記第3部分よりも、信号電荷と同じ導電型の不純物の濃度が高いことを特徴とする請求項1乃至3の何れか1項に記載の光電変換装置。

#### 【請求項5】

前記少なくとも1つの画素において、

前記第4不純物領域は、前記第1面に対する平面視において前記第1分離領域に重なる第4部分と、前記第2転送ゲートに隣接する第5部分と、前記第4部分に対して前記第5部分の反対側にある第6部分と、を含み、

前記第3不純物領域から前記第4不純物領域の前記第5部分へ信号電荷が輸送され、

前記第4不純物領域の前記第4部分又は前記第5部分では、前記第4不純物領域の前記第6部分よりも、前記同じ導電型の不純物の濃度が高いことを特徴とする請求項3又は4に記載の光電変換装置。

30

#### 【請求項6】

前記第1転送ゲート及び前記第2転送ゲートは、縦型構造を有することを特徴とする請求項1乃至5の何れか1項に記載の光電変換装置。

40

#### 【請求項7】

前記基板は、前記第1不純物領域の側方にディープトレンチ素子分離構造をさらに有することを特徴とする請求項1乃至6の何れか1項に記載の光電変換装置。

#### 【請求項8】

前記基板は、前記第2不純物領域と前記第3不純物領域との間に位置する第3分離領域をさらに有することを特徴とする請求項1乃至7の何れか1項に記載の光電変換装置。

#### 【請求項9】

前記複数の画素回路のうちの1つ以上の画素において、前記第1面に対する平面視において前記第1分離領域と前記第2分離領域とが同じ方向に延在することを特徴とする請求項1乃至8の何れか1項に記載の光電変換装置。

50

**【請求項 10】**

前記複数の画素回路のそれぞれにおいて、

前記第2不純物領域に対して前記第1転送ゲートが第1方向に配置され、

前記第4不純物領域に対して前記第2転送ゲートが前記第1方向に配置されている、ことを特徴とする請求項1乃至9の何れか1項に記載の光電変換装置。

**【請求項 11】**

請求項1乃至10の何れか1項に記載の光電変換装置と、

前記光電変換装置に対応した光学装置、

前記光電変換装置を制御する制御装置、

前記光電変換装置から出力された信号を処理する処理装置、

前記光電変換装置で得られた情報を表示する表示装置、

前記光電変換装置で得られた情報を記憶する記憶装置、及び

前記光電変換装置で得られた情報に基づいて動作する機械装置、の少なくともいずれかと、を備えることを特徴とする機器。

10

**【請求項 12】**

光電変換装置の製造方法であって、

第1レジストパターンを使用して、第1導電型の不純物を含む第1不純物領域を有する基板に、前記第1導電型とは反対の第2導電型の不純物を注入することによって、前記第1不純物領域の一部を第2不純物領域に置き換える工程と、

前記第1レジストパターンを使用して、前記第2不純物領域よりも浅い位置に前記第1導電型の不純物を注入する工程と、

前記基板に前記第2導電型の不純物を注入することによって、前記第1不純物領域の少なくとも一部を上下に分離する第3不純物領域を形成する工程と、

前記第2不純物領域よりも浅い位置に第4不純物領域を形成する工程と、を有し、

前記第1不純物領域のうち前記第3不純物領域よりも下にある部分は前記第2不純物領域によって分離され、

前記第1不純物領域のうち前記第3不純物領域よりも上にある部分は前記第4不純物領域によって分離され、

前記第4不純物領域は、前記基板の平面視において前記第2不純物領域に交差する方向に延在することを特徴とする製造方法。

20

30

**【請求項 13】**

前記第4不純物領域を形成する工程は、第2レジストパターンを使用して前記第1不純物領域に前記第1導電型の不純物を注入することを含み、前記第1不純物領域のうち、前記第3不純物領域よりも上にあり前記第2レジストパターンによって覆われた部分が前記第4不純物領域となることを特徴とする請求項12に記載の製造方法。

**【請求項 14】**

前記第3不純物領域を形成する工程は、前記第1不純物領域の一部を覆う第3レジストパターンを使用して前記第1不純物領域に前記第2導電型の不純物を注入することを含むことを特徴とする請求項12又は13に記載の製造方法。

40

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、光電変換装置、その製造方法及び機器に関する。

**【背景技術】****【0002】**

像面位相差オートフォーカス（AF）を可能にするために、1つの画素回路に2つの光電変換素子を有するイメージセンサが提案されている。特許文献1は、被写体のコントラストの方向に起因するAFの精度低下を抑制するために、2つの光電変換素子を、一部の画素回路では列方向に並べ、他の画素回路では行方向に並べる。さらに、光電変換素子以外の回路構成を複数の画素回路で同じにするために、2つの光電変換素子の不純物領域を

50

2層に分ける。一方の層に含まれる2つの不純物領域は、複数の画素回路で異なる方向に並んでいる。他方の層に含まれる2つの不純物領域は、複数の画素回路で同じ方向に並んでいる。後者の層に含まれる2つの不純物領域に対してゲート電極を配置することによって、複数の画素回路でゲート電極の位置を統一できる。

**【先行技術文献】**

**【特許文献】**

**【0003】**

**【文献】特開2020-141122号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0004】**

2つの光電変換素子の不純物領域を2層に分け、一方の層に含まれる2つの不純物領域を複数の画素回路で異なる方向に並べると、信号電荷の輸送経路に電位障壁が形成されてしまい、輸送効率が低下することがある。本発明の1つの側面は、光電変換素子における信号電荷の輸送効率を向上するための技術を提供することを目的とする。

**【課題を解決するための手段】**

**【0005】**

上記課題に鑑みて、光電変換装置であって、第1面と、前記第1面とは反対側の第2面と、前記第1面と前記第2面との間に有する基板と、前記基板に形成された複数の画素回路と、を備え、前記複数の画素回路のそれぞれは、第1光電変換素子と、第2光電変換素子と、前記第1光電変換素子から信号電荷を転送するための第1転送ゲートと、前記第2光電変換素子から信号電荷を転送するための第2転送ゲートと、を有し、前記第1光電変換素子は、前記第1層に位置し、入射光に応じた信号電荷を生成するための第1不純物領域と、前記第2層に位置し、前記第1不純物領域で生成された信号電荷を前記第1転送ゲートに向けて輸送するための第2不純物領域と、を有し、前記第2光電変換素子は、前記第1層に位置し、入射光に応じた信号電荷を生成するための第3不純物領域と、前記第2層に位置し、前記第3不純物領域で生成された信号電荷を前記第2転送ゲートに向けて輸送するための第4不純物領域と、を有し、前記第1層は、前記第1不純物領域と前記第3不純物領域との間に位置する第1分離領域をさらに有し、前記第2層は、前記第2不純物領域と前記第4不純物領域との間に位置する第2分離領域をさらに有し、前記複数の画素回路のうちの少なくとも1つの画素において、前記第1面に対する平面視において前記第1分離領域と前記第2分離領域とが互いに異なる方向に延在し、前記第2不純物領域は、前記第1面に対する平面視において前記第1分離領域に重なる第1部分と、前記第1転送ゲートに隣接する第2部分と、前記第1部分に対して前記第2部分の反対側にある第3部分と、を含み、前記第2不純物領域は、信号電荷にとって、前記第3部分から前記第2部分へ単調に低下する電位分布を有し、前記第2不純物領域の前記第3部分では、前記第2不純物領域の前記第2部分よりも、信号電荷とは反対の導電型の不純物の濃度が高いことを特徴とする光電変換装置が提供される。

**【発明の効果】**

**【0006】**

上記手段により、光電変換素子における信号電荷の輸送効率が向上する。

**【図面の簡単な説明】**

**【0007】**

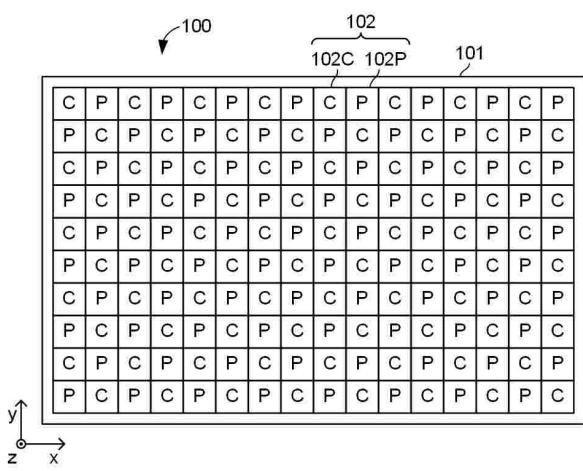

**【図1】第1実施形態に係る光電変換装置の構成例を説明する図。**

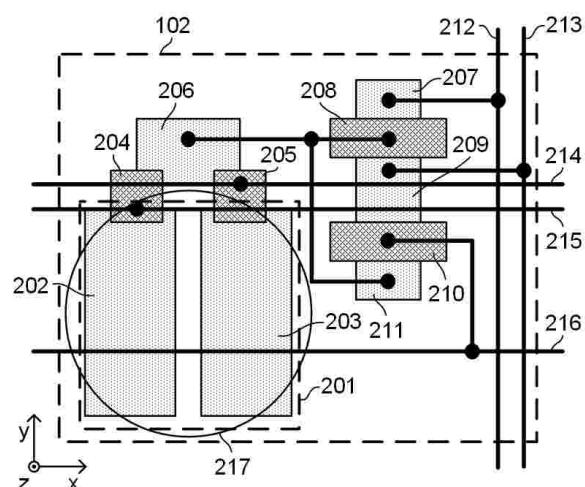

**【図2】第1実施形態に係る画素回路の構成例を説明する図。**

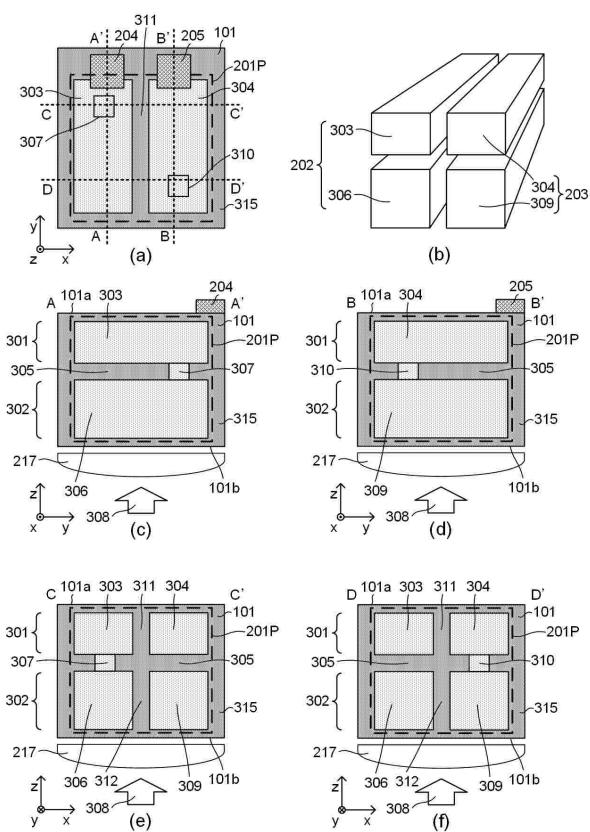

**【図3】第1実施形態に係る平行画素回路の構成例を説明する図。**

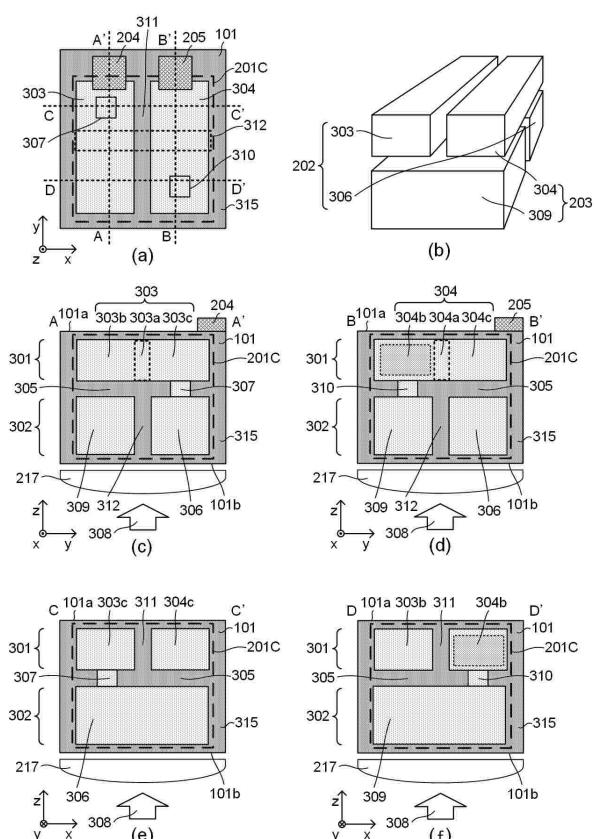

**【図4】第1実施形態に係る交差画素回路の構成例を説明する図。**

**【図5】第1実施形態に係る光電変換装置の製造方法例を説明する図。**

**【図6】第1実施形態に係る光電変換装置の製造方法例を説明する図。**

- 【図 7】第 1 実施形態に係る光電変換装置の電位分布例を説明する図。

- 【図 8】第 1 実施形態に係る光電変換装置の別の製造方法例を説明する図。

- 【図 9】第 2 実施形態に係る光電変換装置を説明する図。

- 【図 10】第 3 実施形態に係る光電変換装置を説明する図。

- 【図 11】第 4 実施形態に係る光電変換装置を説明する図。

- 【図 12】第 5 実施形態に係る光電変換装置を説明する図。

- 【図 13】その他の実施形態を説明する図。

【発明を実施するための形態】

【0008】

以下、添付図面を参照して実施形態を詳しく説明する。なお、以下の実施形態は特許請求の範囲に係る発明を限定するものではない。実施形態には複数の特徴が記載されているが、これらの複数の特徴の全てが発明に必須のものとは限らず、また、複数の特徴は任意に組み合わせられてもよい。さらに、添付図面においては、同一若しくは同様の構成に同一の参照番号を付し、重複した説明は省略する。

10

【0009】

<第 1 実施形態>

図 1～図 7 を参照して、第 1 実施形態に係る光電変換装置 100 について説明する。図 1 は、光電変換装置 100 の上面模式図を示す。光電変換装置 100 は、基板 101 と、基板 101 に形成された複数の画素回路 102 と、を有する。複数の画素回路 102 は、2 次元アレイ状に配置されている。これに代えて、複数の画素回路 102 は、1 次元状に配置されてもよい。

20

【0010】

複数の画素回路 102 は、平行画素回路 102P と、交差画素回路 102C と、の 2 種類に分類される。平行画素回路 102P とは、詳細を後述するように、2 つの光電変換素子を構成する 2 層の不純物領域が同じ方向に配置された画素回路 102 のことである。平行画素回路 102P は、図 1 で「P」の文字で表されている。交差画素回路 102C とは、詳細を後述するように、2 つの光電変換素子を構成する 2 層の不純物領域が交差する方向に配置された画素回路 102 のことである。交差画素回路 102C は、図 1 で「C」の文字で表されている。図 1 に示された例では、平行画素回路 102P と交差画素回路 102C とが交互に配置されている。これに代えて、平行画素回路 102P と交差画素回路 102C とは他のパターンで配置されてもよい。さらに、光電変換装置 100 は、交差画素回路 102C のみを有し、平行画素回路 102P を有しなくてもよい。

30

【0011】

図 2 を参照して、画素回路 102 の構成例について説明する。画素回路 102 についての説明は、平行画素回路 102P 及び交差画素回路 102C の両方に当てはまる。画素回路 102 は、2 つの光電変換素子 202、203 と、4 つのゲート電極 204、205、208、210 と、4 つの不純物領域 206、207、209、211 と、1 つのマイクロレンズ 217 と、を有する。2 つの光電変換素子 202、203 は、画素回路 102 の変換素子配置領域 201 に形成されている。2 つの光電変換素子 202、203 は、入射光に応じた信号電荷を個別に生成する。

40

【0012】

不純物領域 206 は、フローティングディフュージョンとして機能する。ゲート電極 204 は、光電変換素子 202 と不純物領域 206 とのそれぞれに隣接して配置されている。ゲート電極 204 は、光電変換素子 202 で生成された信号電荷を不純物領域 206 へ転送するための転送トランジスタの転送ゲートとして機能する。ゲート電極 204 へ駆動線 215 を通じて光電変換装置 100 の垂直走査回路（不図示）から制御信号が供給される。ゲート電極 205 は、光電変換素子 203 と不純物領域 206 とのそれぞれに隣接して配置されている。ゲート電極 205 は、光電変換素子 203 で生成された信号電荷を不純物領域 206 へ転送するための転送トランジスタの転送ゲートとして機能する。ゲート電極 205 へ、駆動線 214 を通じて光電変換装置 100 の垂直走査回路（不図示）から

50

制御信号が供給される。

【0013】

不純物領域206は、ゲート電極208と不純物領域211とのそれぞれに電気的に接続されている。不純物領域209へ、電源線213を通じて光電変換装置100の電源回路(不図示)から所定の電圧が供給される。ゲート電極210は、フローティングディフュージョン(不純物領域206)の電位をリセットするためのリセットトランジスタのゲートとして機能する。ゲート電極210へ、駆動線216を通じて光電変換装置100の垂直走査回路(不図示)から制御信号が供給される。

【0014】

不純物領域207は、信号線212に電気的に接続されている。ゲート電極208は、フローティングディフュージョン(不純物領域206)の電位に応じた信号を増幅して読み出すための増幅トランジスタのゲートとして機能する。したがって、2つの光電変換素子202、203のそれぞれで生成された信号電荷に応じた信号が、信号線212を通じて光電変換装置100の読み出し回路(不図示)に個別に読み出される。

10

【0015】

複数の画素回路102は、平行画素回路102Pであるか交差画素回路102Cであるかによらず、変換素子配置領域201を除いて、同一の構造を有する。具体的に、複数の画素回路102のゲート電極204は、光電変換素子202(具体的に、その不純物領域303)に対して同じ方向(図2に示す座標系ではy軸正の方向)に配置されている。同様に、ゲート電極205は、光電変換素子203(具体的に、その不純物領域304)に対して同じ方向(図2に示す座標系ではy軸正の方向)に配置されている。また、画素回路102内の導電パターンも平行画素回路102Pであるか交差画素回路102Cであるかによらず同じ構造を有する。このように画素回路102が変換素子配置領域201を除いて同一の構造を有することによって、例えばフローティングディフュージョンの容量の違いによる画素特性の差を抑制できる。

20

【0016】

図3を参照して、平行画素回路102Pの構造について詳細に説明する。平行画素回路102Cに含まれる変換素子配置領域201を変換素子配置領域201Pと表す。上述のように、本実施形態において、平行画素回路102Pと交差画素回路102Cとは、変換素子配置領域201の構造のみが異なる。そのため、以下では変換素子配置領域201Pの構造について詳細に説明する。

30

【0017】

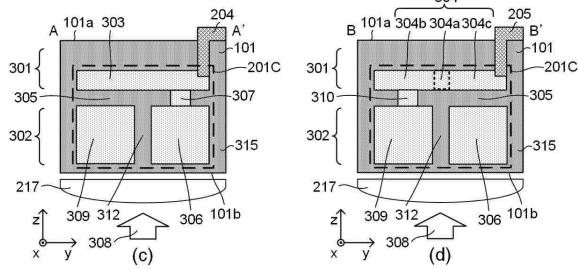

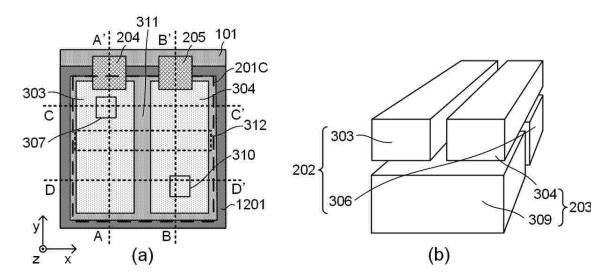

図3(a)は、変換素子配置領域201Pの上面図である。図3(b)は、平行画素回路102Pの4つの不純物領域303、304、306及び309の位置関係を説明するための透視図である。図3(c)は、図3(a)のAA'線における変換素子配置領域201Pの断面図である。図3(d)は、図3(a)のBB'線における変換素子配置領域201Pの断面図である。図3(e)は、図3(a)のCC'線における変換素子配置領域201Pの断面図である。図3(f)は、図3(a)のDD'線における変換素子配置領域201Pの断面図である。

40

【0018】

光電変換素子202及び203は、基板101に形成されている。基板101は、例えば半導体基板(シリコン基板など)である。基板101は、表面(おもてめん)101aと、表面101aとは反対側の裏面101bと、を有する。本実施形態では、光電変換装置100は、裏面照射型の光電変換装置である。基板101の裏面101bの側にマイクロレンズ217が形成され、基板101の表面101aの側に配線構造が形成されている。光電変換装置100への入射光308は、マイクロレンズ217を通った後に、裏面101bから光電変換素子202及び203へ入射する。そのため、裏面101bは入射面とも呼ばれる。

【0019】

光電変換素子202及び203は、基板101の2つの層301及び302にわたって

50

形成されている。層301及び302はいずれも、表面101aと裏面101bとの間に位置する。層302は、層301と裏面101bとの間に位置する。層301は、層302と表面101aとの間に位置する。層302は、層301よりも入射面（裏面101b）に近い。

#### 【0020】

光電変換素子202は、層301に位置する不純物領域303と、層302に位置する不純物領域306と、層301と層302との間に位置する不純物領域307と、を含む。不純物領域306は、入射光に応じた信号電荷を生成する。不純物領域306で生成された信号電荷は、不純物領域307を通じて不純物領域303に輸送され、そこに蓄積される。不純物領域303に蓄積された信号電荷は、ゲート電極204にオン電圧が供給されることによって、不純物領域206に転送される。このように、不純物領域303は、不純物領域306で生成された信号電荷をゲート電極204に向けて輸送する。

10

#### 【0021】

本実施形態では、信号電荷が電子である場合を扱う。そのため、不純物領域303及び306はいずれもN型の不純物領域である。信号電荷がホールである場合には、本書における各不純物領域の導電型が入れ替わる。

#### 【0022】

光電変換素子203は、層301に位置する不純物領域304と、層302に位置する不純物領域309と、層301と層302との間に位置する不純物領域310と、を含む。不純物領域309は、入射光に応じた信号電荷を生成する。不純物領域309で生成された信号電荷は、不純物領域310を通じて不純物領域304に輸送され、そこに蓄積される。不純物領域304に蓄積された信号電荷は、ゲート電極205にオン電圧が供給されることによって、不純物領域206に転送される。このように、不純物領域304は、不純物領域309で生成された信号電荷をゲート電極205に向けて輸送する。信号電荷が電子であるため、不純物領域304及び309はいずれもN型の不純物領域である。

20

#### 【0023】

不純物領域303と不純物領域304とは、層301に位置する不純物領域311によって互いに分離されている。不純物領域311は、不純物領域303と不純物領域304とを分離する分離領域として機能する。不純物領域311は、不純物領域303と不純物領域304との間に位置しており、表面101aに対する平面視においてy軸方向に延在している。表面101aと裏面101bとは略平行であるため、表面101aに対する平面視は、裏面101bに対する平面視でもある。不純物領域311は、P型の不純物領域であってもよいし、不純物領域303及び304よりも濃度が低いN型の不純物領域であってもよい。

30

#### 【0024】

不純物領域306と不純物領域309とは、層302に位置する不純物領域312によって互いに分離されている。不純物領域311は、不純物領域306と不純物領域309とを分離する分離領域として機能する。不純物領域312は、不純物領域306と不純物領域309との間に位置しており、表面101aに対する平面視においてy軸方向に延在している。不純物領域312は、P型の不純物領域である。このように、平行画素回路102Pでは、表面101aに対する平面視において、不純物領域311と不純物領域312とが同じ方向(y軸方向)に延在している。言い換えると、平行画素回路102Pでは、層301において2つの不純物領域303及び304が隣接する方向と、層302において2つの不純物領域306及び309が隣接する方向と、が同じ(どちらもx軸方向)である。

40

#### 【0025】

層301に位置する2つの不純物領域303及び304と、層302に位置する2つの不純物領域306及び309とは、不純物領域307及び310が配置された部分を除いて、不純物領域305によって互いに分離されている。不純物領域305は、層301と層302とを分離する分離領域として機能する。不純物領域305は、不純物領域30

50

3と不純物領域306との間と、不純物領域304と不純物領域309との間と、のそれに位置する。不純物領域305は、P型の不純物領域である。不純物領域307は、不純物領域306から不純物領域303への信号電荷の輸送が可能なような電位勾配を有する。この電位勾配は、単調に変化してもよい。不純物領域307は、N型の不純物領域であってもよいし、不純物領域305と比較して不純物濃度が低いP型の不純物領域であってもよい。不純物領域310についても、不純物領域307についての上述の説明が同様に当てはまる。

#### 【0026】

層301と層302との間に不純物領域305、307及び310が配置されていることによって、不純物領域306で生成された信号電荷は、不純物領域304には輸送されず、不純物領域303に輸送される。また、不純物領域309で生成された信号電荷は、不純物領域303には輸送されず、不純物領域304に輸送される。

10

#### 【0027】

変換素子配置領域201Pの側方には、不純物領域315が配置されている。不純物領域315は、隣接する2つの画素回路102の変換素子配置領域201を互いに分離する。不純物領域315は、P型の不純物領域である。

#### 【0028】

図4を参照して、交差画素回路102Cの構造について詳細に説明する。交差画素回路102Cに含まれる変換素子配置領域201を変換素子配置領域201Cと表す。上述のように、本実施形態において、交差画素回路102Cと交差画素回路102Cとは、変換素子配置領域201の構造のみが異なる。そのため、以下では変換素子配置領域201Cの構造について詳細に説明する。

20

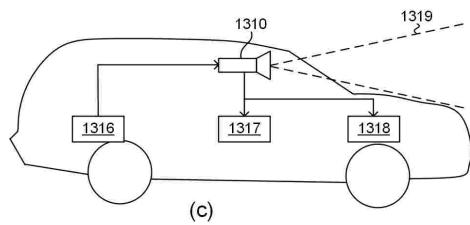

#### 【0029】

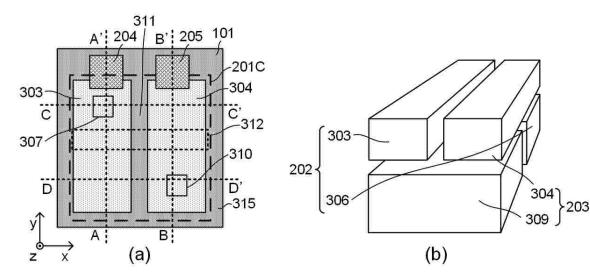

図4(a)は、変換素子配置領域201Cの上面図である。図4(b)は、交差画素回路102Cの4つの不純物領域303、304、306及び309の位置関係を説明するための透視図である。図4(c)は、図4(a)のAA'線における変換素子配置領域201Cの断面図である。図4(d)は、図4(a)のBB'線における変換素子配置領域201Cの断面図である。図4(e)は、図4(a)のCC'線における変換素子配置領域201Cの断面図である。図4(f)は、図4(a)のDD'線における変換素子配置領域201Cの断面図である。

30

#### 【0030】

変換素子配置領域201Cは、表面101aに対する平面視において不純物領域312がx軸方向に延在している点で変換素子配置領域201Pとは異なる。また、変換素子配置領域201Cでは、不純物領域304の部分313がP型不純物(例えは、ボロン。以下同様。)を含む。変換素子配置領域201Cは、その他の点において変換素子配置領域201Pと同様であってもよい。

#### 【0031】

交差画素回路102Cでは、表面101aに対する平面視において不純物領域311と不純物領域312とが互いに異なる方向に延在している。具体的に、表面101aに対する平面視において、不純物領域311はy軸方向に延在し、不純物領域312はx軸方向に延在している。言い換えると、交差画素回路102Cでは、層301において2つの不純物領域303及び304が隣接する方向と、層302において2つの不純物領域306及び309が隣接する方向と、が互いに異なる。図4の例では、不純物領域311と不純物領域312とが直交する方向に延在しているが、これらは他の角度で交差するように延在してもよい。

40

#### 【0032】

不純物領域305は、不純物領域303と不純物領域306との間と、不純物領域303と不純物領域309との間と、不純物領域303と不純物領域309との間と、不純物領域304と不純物領域309との間と、のそれぞれに位置する。

#### 【0033】

50

不純物領域 3 0 4 は、表面 1 0 1 a に対する平面視において不純物領域 3 1 2 に重なる部分 3 0 4 a と、ゲート電極 2 0 5 に隣接する部分 3 0 4 c と、部分 3 0 4 a に対して部分 3 0 4 c の反対側にある部分 3 0 4 b と、を有する。部分 3 0 4 b 及び 3 0 4 c は、部分 3 0 4 a を挟んで互いに反対側にある。部分 3 0 4 a よりも部分 3 0 4 b の方がゲート電極 2 0 5 から遠い位置にある。部分 3 0 4 a よりも部分 3 0 4 c の方がゲート電極 2 0 5 から近い位置にある。光電変換素子 2 0 3 では、不純物領域 3 0 4 の部分 3 0 4 b が不純物領域 3 1 0 に結合されている。そのため、不純物領域 3 0 9 で生成された信号電荷は、不純物領域 3 0 4 の部分 3 0 4 b に輸送され、その後、不純物領域 3 0 4 の部分 3 0 4 a 及び 3 0 4 c を通ってゲート電極 2 0 5 へ向けて輸送される。

#### 【 0 0 3 4 】

10

不純物領域 3 0 4 の部分 3 0 4 b では、不純物領域 3 0 4 の部分 3 0 4 c よりも、信号電荷とは反対の導電型（本実施形態では P 型）の不純物の濃度が高い。詳細を後述するように、このような濃度分布を有することによって、不純物領域 3 0 4 における信号電荷の輸送経路は、部分 3 0 4 b から部分 3 0 4 c へ信号電荷を輸送するように単調に変化する電位分布を有する。

#### 【 0 0 3 5 】

不純物領域 3 0 3 は、表面 1 0 1 a に対する平面視において不純物領域 3 1 2 に重なる部分 3 0 3 a と、ゲート電極 2 0 4 に隣接する部分 3 0 3 c と、部分 3 0 3 a に対して部分 3 0 3 c の反対側にある部分 3 0 3 b と、を有する。部分 3 0 3 b 及び 3 0 3 c は、部分 3 0 3 a を挟んで互いに反対側にある。部分 3 0 3 a よりも部分 3 0 3 b の方がゲート電極 2 0 4 から遠い位置にある。部分 3 0 3 a よりも部分 3 0 3 c の方がゲート電極 2 0 4 から近い位置にある。光電変換素子 2 0 2 では、不純物領域 3 0 3 の部分 3 0 3 c が不純物領域 3 0 7 に結合されている。そのため、不純物領域 3 0 6 で生成された信号電荷は、不純物領域 3 0 3 の部分 3 0 3 c に輸送され、その後、ゲート電極 2 0 4 へ向けて輸送される。

20

#### 【 0 0 3 6 】

上述のように、平行画素回路 1 0 2 P では、入射光に応じた信号電荷を生成する 2 つの不純物領域 3 0 6 及び 3 0 9 が x 軸方向に隣接している。一方、交差画素回路 1 0 2 C では、入射光に応じた信号電荷を生成する 2 つの不純物領域 3 0 6 及び 3 0 9 が y 軸方向に隣接している。そのため、光電変換装置 1 0 0 を用いて、2 つの異なる方向について、像面位相差 A F を実行できる。本実施形態では、不純物領域 3 0 6 及び 3 0 9 が複数の画素回路 1 0 2 で 2 つの異なる方向に隣接している。これに代えて、不純物領域 3 0 6 及び 3 0 9 が複数の画素回路 1 0 2 で 3 つ以上の異なる方向に隣接してもよい。

30

#### 【 0 0 3 7 】

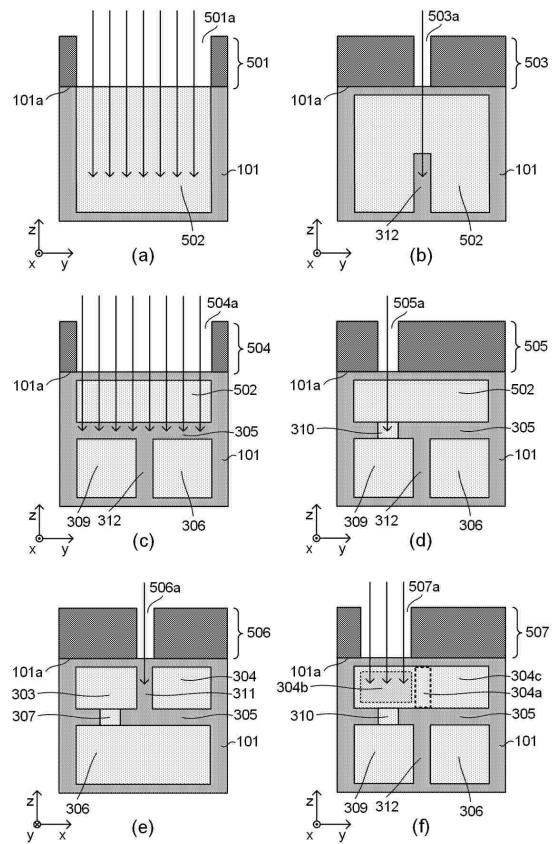

図 5 を参照して、光電変換装置 1 0 0 の製造方法について説明する。変換素子配置領域 2 0 1 以外の製造方法については既存の技術と同様であってもよいため、以下では変換素子配置領域 2 0 1 の製造方法を中心にして説明する。図 5 ( a ) ~ 図 5 ( d ) 及び図 5 ( f ) は、図 4 ( c ) の断面図に対応する位置における光電変換装置 1 0 0 の製造途中の基板 1 0 1 の断面図を示す。図 5 ( e ) は、図 4 ( d ) の断面図に対応する位置における光電変換装置 1 0 0 の製造途中の基板 1 0 1 の断面図を示す。

40

#### 【 0 0 3 8 】

図 5 ( a ) に示すように、基板 1 0 1 の表面 1 0 1 a の上にレジストパターン 5 0 1 を形成する。レジストパターン 5 0 1 には、画素回路 1 0 2 が形成される領域ごとに開口 5 0 1 a が形成されている。レジストパターン 5 0 1 は、変換素子配置領域 2 0 1 が形成される領域を開口 5 0 1 a から露出し、基板 1 0 1 の他の部分を覆う。レジストパターン 5 0 1 を使用して、開口 5 0 1 a を通じて N 型不純物（例えば、リン。以下同様。）を基板 1 0 1 に注入する。これによって、基板 1 0 1 に N 型の不純物領域 5 0 2 が形成される。この工程の前に、基板 1 0 1 のうち変換素子配置領域 2 0 1 が形成される領域及びその周囲は、P 型の半導体領域である。不純物領域 5 0 2 の一部が画素回路 1 0 2 の不純物領域 3 0 3 、 3 0 4 、 3 0 6 及び 3 0 9 となる。

50

### 【0039】

続いて、図5(b)に示すように、基板101の表面101aの上にレジストパターン503を形成する。レジストパターン503には、画素回路102が形成される領域ごとに開口503aが形成されている。レジストパターン503は、不純物領域312が形成される領域を開口503aから露出し、基板101の他の部分を覆う。表面101aに対する平面視において、平行画素回路102Pが形成される領域に形成された開口503aはy軸方向に延在し、交差画素回路102Cが形成される領域に形成された開口503aはx軸方向に延在する。レジストパターン503を使用して、開口503aを通じてP型不純物を基板101に注入する。これによって、不純物領域502の一部がP型の不純物領域312に置き換わる。不純物領域312は、光電変換装置100において、層302に位置する不純物領域306と不純物領域309とを分離する。そのため、この工程において、P型不純物は、基板101の深い位置(変換素子配置領域201の層302に対応する位置)に注入される。P型不純物は、基板101の裏面101bまで注入されてもよい。また、P型不純物は、多段注入されてもよい。

### 【0040】

続いて、図5(c)に示すように、基板101の表面101aの上にレジストパターン504を形成する。レジストパターン504には、画素回路102が形成される領域ごとに開口504aが形成されている。レジストパターン504は、不純物領域305が形成される領域を開口504aから露出し、基板101の他の部分を覆う。レジストパターン504を使用して、開口504aを通じてP型不純物を基板101に注入する。これによって、不純物領域502の一部がP型の不純物領域305に置き換わる。不純物領域305は、不純物領域502を上下に分離する。この工程において、P型不純物は、基板101の中位の位置に注入される。不純物領域502のうち不純物領域305より下にある部分は、不純物領域312によってすでに分離されている。そのため、不純物領域502のうち不純物領域305より下にある2つの部分が不純物領域306及び不純物領域309となる。不純物領域305を形成するためのP型不純物の濃度は、図5(b)の工程で不純物領域312を形成するためのP型不純物の濃度よりも高くてもよい。

### 【0041】

続いて、図5(d)に示すように、基板101の表面101aの上にレジストパターン505を形成する。レジストパターン505には、画素回路102が形成される領域ごとに2つの開口505aが形成されている。レジストパターン505は、不純物領域307及び310が形成される領域を開口505aから露出し、基板101の他の部分を覆う。レジストパターン505を使用して、開口505aを通じてN型不純物を基板101に注入する。これによって、不純物領域305の一部がN型の不純物領域307及び310に置き換わる。図5(d)の断面図では、不純物領域310が示され、不純物領域307が示されていない。

### 【0042】

続いて、図5(e)に示すように、基板101の表面101aの上にレジストパターン506を形成する。レジストパターン506には、画素回路102が形成される領域ごとに開口506aが形成されている。レジストパターン506は、不純物領域311が形成される領域を開口506aから露出し、基板101の他の部分を覆う。表面101aに対する平面視において、平行画素回路102Pが形成される領域に形成された開口503aと、交差画素回路102Cが形成される領域に形成された開口503aとのどちらもy軸方向に延在する。レジストパターン506を使用して、開口506aを通じてP型不純物を基板101に注入する。これによって、不純物領域502の一部がN型の不純物領域311に置き換わる。この工程によって、不純物領域502が不純物領域303と不純物領域304とに分離される。この工程において、P型不純物は、基板101の浅い位置(変換素子配置領域201の層301に対応する位置)に注入される。

### 【0043】

続いて、図5(f)に示すように、基板101の表面101aの上にレジストパターン

10

20

30

40

50

507を形成する。レジストパターン507には、画素回路102が形成される領域ごとに開口507aが形成される。レジストパターン507は、不純物領域304の一部（部分304bに対応する部分）を開口507aから露出し、基板101の他の部分を覆う。レジストパターン507を使用して、開口507aを通じてP型不純物を基板101に注入する。これによって、不純物領域304の部分304bにおけるP型不純物の濃度が上昇する。不純物領域304の部分304bに注入するP型不純物の濃度は、図5(b)の工程で不純物領域312を形成するためのP型不純物の濃度と同程度であってもよい。

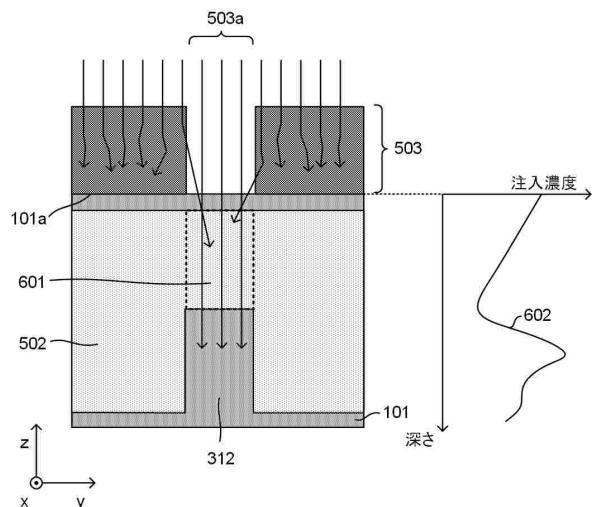

#### 【0044】

図6を参照して、図5(b)の工程の詳細について説明する。レジストパターン503の開口503aに向けて注入されたP型不純物は基板101の深い位置まで到達し、不純物領域312を形成する。一方、レジストパターン503に注入されたP型不純物は、理想的には基板101に到達しない。しかし、レジストパターン503のうち開口503aの近くに注入されたP型不純物の一部は、レジスト材料に衝突して転向し、開口503aの側面から飛び出し、基板101に到達する。このようなP型不純物はレジストパターン503でエネルギーを消費しているため、基板101の浅い位置（不純物領域312の上にある領域601）に注入される。図6の右側のグラフ602に示すように、領域601に注入されるP型不純物の濃度は、基板101の表面101aに近いほど高くなる。

10

#### 【0045】

図7を参照して、不純物領域312の形成時に基板101の深い位置にもP型不純物が注入されることによる影響と、その影響の軽減方法について説明する。図7(a)は、比較例に係る光電変換装置について説明する。比較例に係る光電変換装置は、図5(f)の工程を行わずに製造される。図7(a)は、図4(c)に対応する位置における光電変換装置の断面図を示す。図7(a)のグラフ702は、不純物領域304の位置701における電位分布を示す。電位は空乏時の電位であってもよい。位置701は、不純物領域304における信号電荷の輸送経路に含まれ、例えば基板101の深さ方向(z方向)における不純物領域304の中央であってもよい。

20

#### 【0046】

図6を参照して上述したように、不純物領域312を形成するためのP型不純物の注入時に、不純物領域304の部分304aにもP型不純物が注入されてしまう。このP型不純物のせいで、不純物領域304の電位分布は、グラフ702上の位置703に電位障壁を有する。この電位障壁に起因して、交差画素回路102Cの光電変換素子203では、不純物領域309からゲート電極205へ向かう信号電荷の輸送効率が低下する。一方、交差画素回路102Cの光電変換素子202では、不純物領域303のうちゲート電極204に近い部分303cに不純物領域306から信号電荷が輸送される。そのため、交差画素回路102Cの光電変換素子202は、不純物領域312の形成時に不純物領域303の部分303aに注入された影響を受けない。したがって、交差画素回路102Cの光電変換素子202と光電変換素子203との間で信号電荷の輸送効率に差が生じてしまう。また、平行画素回路102Pでは、表面101aに対する平面視において不純物領域303及び304が不純物領域312と重ならないため、このような信号電荷の輸送効率の低下は発生しない。

30

#### 【0047】

図7(b)は、本実施形態の光電変換装置100について説明する。図7(b)は、図4(c)に対応する位置における光電変換装置100の断面図を示す。図7(a)のグラフ704は、不純物領域304の位置701における電位分布を示す。電位は空乏時の電位であってもよい。位置701は、不純物領域304における信号電荷の輸送経路に含まれ、例えば基板101の深さ方向(z方向)における不純物領域304の中央であってもよい。

40

#### 【0048】

不純物領域304の部分304bへは、図5(f)の工程でP型不純物が注入されている。そのため、不純物領域304の部分304bでは、不純物領域304の部分304c

50

よりも、信号電荷とは反対の導電型（本実施形態ではP型）の不純物の濃度が高い。その結果、不純物領域304の電位分布は、グラフ704に示すように、不純物領域304における信号電荷の輸送経路は、部分304bから部分304cへ信号電荷を輸送するよう単調に変化する電位分布を有し、電位障壁を有しない。したがって、上述の比較例で発生する信号電荷の輸送効率の低下が抑制される。その結果、交差画素回路102Cの光電変換素子202と光電変換素子203との間の輸送効率のばらつきが低減し、さらに、平行画素回路102Pと交差画素回路102Cとの間の輸送効率のばらつきも低減する。

#### 【0049】

上述の実施形態では、交差画素回路102Cの光電変換素子203の不純物領域304の部分304bのみに図5(f)の工程でP型不純物を注入した。これに加えて、図5(f)の工程で、交差画素回路102Cの光電変換素子202の不純物領域303の部分303bにもP型不純物を注入してもよい。これにより、不純物領域303の部分303bでは、不純物領域303の部分303cよりも、信号電荷とは反対の導電型（本実施形態ではP型）の不純物の濃度が高くなる。光電変換素子202の不純物領域303と光電変換素子203の不純物領域304とを同様の不純物濃度の分布とすることによって、光電変換素子間の信号電荷の輸送特性（転送可能な電荷の最大量など）のばらつきが低減する。さらに、図5(f)の工程で、平行画素回路102Pの光電変換素子202及び203の不純物領域303及び304のうちゲート電極204及び205から遠くにある部分にもP型不純物を注入してもよい。これにより、2種類の画素回路間の信号電荷の輸送特性（転送可能な電荷の最大量など）のばらつきが低減する。

10

#### 【0050】

上述の実施形態において、不純物領域304のうち、表面101aに対する平面視において不純物領域310に重なる部分に電位ポケットが発生する場合がある。そこで、この電位ポケットを解消するために、この部分にP型不純物（例えば、ボロン）を注入してもよい。

20

#### 【0051】

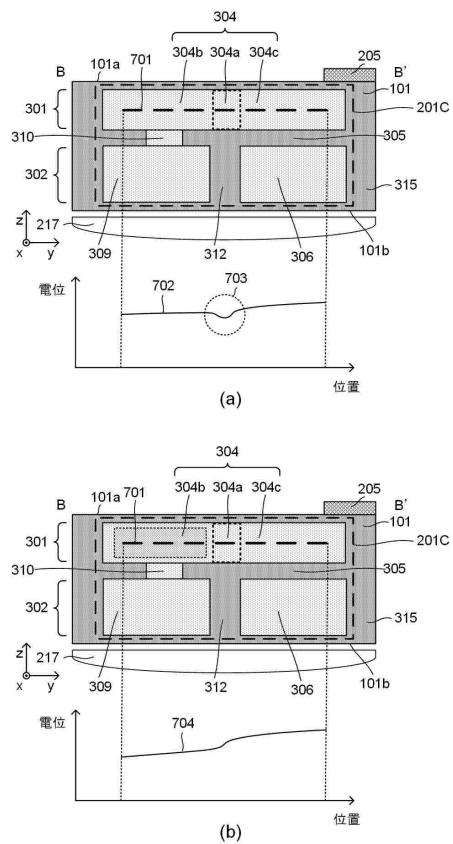

図8を参照して、光電変換装置100の別の製造方法について説明する。変換素子配置領域201以外の製造方法については既存の技術と同様であってもよいため、以下では変換素子配置領域201の製造方法を中心に説明する。図8(a)～図8(c)及び図8(e)は、図4(c)の断面図に対応する位置における光電変換装置100の製造途中の基板101の断面図を示す。図8(d)は、図4(d)の断面図に対応する位置における光電変換装置100の製造途中の基板101の断面図を示す。

30

#### 【0052】

図8(a)に示すように、基板101の表面101aの上にレジストパターン801を形成する。レジストパターン801には、画素回路102が形成される領域に対応して開口801aが形成されている。レジストパターン801は、変換素子配置領域201が形成される領域の周囲を開口801aから露出し、変換素子配置領域201が形成される領域を覆う。レジストパターン801を使用して、開口801aを通じてP型不純物を基板101に注入する。これによって、基板101にP型の不純物領域315が形成される。この工程の前に、基板101のうち変換素子配置領域201が形成される領域及びその周囲は、N型の半導体領域である。基板101のうちP型不純物が注入されなかった領域がN型の不純物領域502として残る。不純物領域502の一部が画素回路102の不純物領域303、304、306、307及び309となる。図示していないが、不純物領域315の形成の前に不純物領域502の下にP型の不純物領域が形成され、不純物領域315の形成の後に不純物領域502の上にP型の不純物領域が形成される。

40

#### 【0053】

続いて、図8(b)に示すように、上述の図5(b)の工程と同様にして、基板101の表面101aの上にレジストパターン503を形成し、レジストパターン503を使用して、開口503aを通じてP型不純物を基板101に注入する。これによって、不純物領域502の一部がP型の不純物領域312に置き換わる。

50

### 【0054】

続いて、図8(c)に示すように、基板101の表面101aの上にレジストパターン804を形成する。レジストパターン804には、画素回路102が形成される領域ごとに開口804aが形成されている。レジストパターン804は、不純物領域305が形成される領域を開口804aから露出し、基板101の他の部分(不純物領域310が形成される領域を含む。)を覆う。レジストパターン804を使用して、開口804aを通じてP型不純物を基板101に注入する。これによって、不純物領域502の一部がP型の不純物領域305に置き換わる。不純物領域305は、不純物領域502を上下に分離する。この工程において、P型不純物は、基板101の中位の位置に注入される。不純物領域502のうち不純物領域305より下にある部分は、不純物領域312によってすでに分離されている。そのため、不純物領域502のうち不純物領域305より下にある2つの部分が不純物領域306及び不純物領域309となる。また、不純物領域502のうち不純物領域305と同じ深さにある部分が不純物領域310となる。不純物領域305を形成するためのP型不純物の濃度は、図8(b)の工程で不純物領域312を形成するためのP型不純物の濃度よりも高くてよい。

### 【0055】

続いて、図8(d)に示すように、基板101の表面101aの上にレジストパターン805を形成する。レジストパターン805には、画素回路102が形成される領域ごとに2つの開口805aが形成されている。レジストパターン805は、不純物領域303及び304が形成される領域を開口805aから露出し、基板101の他の部分(不純物領域311が形成される領域を含む。)を覆う。レジストパターン805を使用して、開口805aを通じてN型不純物を基板101に注入する。これによって、不純物領域502の一部のN型不純物の濃度が高くなる。不純物領域502のうちN型不純物の濃度が高くなった部分が領域303及び304となり、領域303と領域304との間の部分(N型不純物が注入されなかった部分)が不純物領域311となる。この工程において、P型不純物は、基板101の浅い位置(変換素子配置領域201の層301に対応する位置)に注入される。図8(d)の工程にかえて又は加えて、上述の図5(e)の工程が行われてもよい。

### 【0056】

続いて、図8(e)に示すように、上述の図5(f)の工程と同様にして、基板101の表面101aの上にレジストパターン507を形成し、レジストパターン507を使用して、開口507aを通じてP型不純物を基板101に注入する。これによって、不純物領域304の部分304bにおけるP型不純物の濃度が上昇する。

### 【0057】

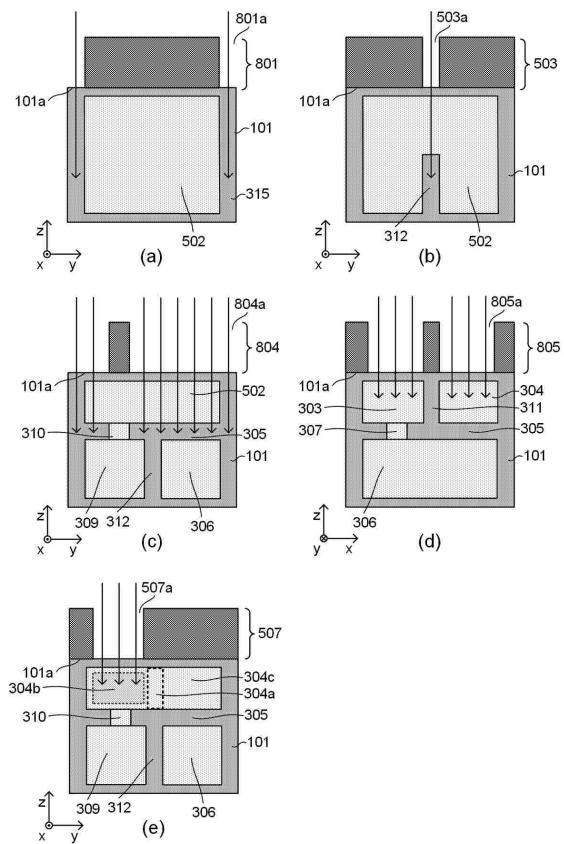

#### <第2実施形態>

図9を参照して、第2実施形態に係る光電変換装置100について説明する。以下では、第1実施形態との相違点を中心に説明する。説明が省略される部分は第1実施形態と同様であってもよい。本実施形態は、第1実施形態と組み合わされてもよい。

### 【0058】

図9(a)は、第1実施形態の図4(c)の位置における変換素子配置領域201Cの断面図を示す。図9(b)は、第1実施形態の図4(d)の位置における変換素子配置領域201Cの断面図を示す。本実施形態の不純物領域304の部分304a及び304cでは、不純物領域304の部分304bよりも、信号電荷と同じ導電型(本実施形態ではN型)の不純物の濃度が高い。このような濃度分布を有することによって、第1実施形態と同様に、不純物領域304における信号電荷の輸送経路は、部分304bから部分304cへ信号電荷を輸送するように単調に変化する電位分布を有する。したがって、本実施形態も、第1実施形態と同様の効果を奏する。

### 【0059】

図9(c)は、本実施形態に係る光電変換装置100の製造方法を説明する図である。図9(c)は、図4(c)の断面図に対応する位置における光電変換装置100の製造途

中の基板 101 の断面図を示す。本実施形態では、第1実施形態の図5(a)～図5(e)の工程を実行した後に、図9(c)で説明する工程を実行する。

#### 【0060】

図9(c)に示すように、基板101の表面101aの上にレジストパターン901を形成する。レジストパターン901には、画素回路102が形成される領域ごとに開口901aが形成される。レジストパターン901は、不純物領域304の一部(部分304a及び304cに対応する部分)を開口901aから露出し、基板101の他の部分を覆う。レジストパターン901を使用して、開口901aを通じてN型不純物を基板101に注入する。これによって、不純物領域304の部分304a及び304cにおけるN型不純物の濃度が上昇する。

10

#### 【0061】

上述の実施形態では、交差画素回路102Cの光電変換素子203の不純物領域304の部分304a及び304cのみに図9(c)の工程でN型不純物を注入した。これに加えて、図9(c)の工程で、交差画素回路102Cの光電変換素子202の不純物領域303の部分303a及び303cにもN型不純物を注入してもよい。これにより、不純物領域303の部分303a及び303cでは、不純物領域303の部分303bよりも、信号電荷と同じ導電型(本実施形態ではN型)の不純物の濃度が高くなる。光電変換素子202の不純物領域303と光電変換素子203の不純物領域304とを同様の不純物濃度の分布とすることによって、光電変換素子間の信号電荷の輸送特性(転送可能な電荷の最大量など)のばらつきが低減する。さらに、図9(c)の工程で、平行画素回路102Pの光電変換素子202及び203の不純物領域303及び304のうちゲート電極204及び205から遠くにある部分にもN型不純物を注入してもよい。これにより、2種類の画素回路間の信号電荷の輸送特性(転送可能な電荷の最大量など)のばらつきが低減する。

20

#### 【0062】

##### <第3実施形態>

図10を参照して、第3実施形態に係る光電変換装置100について説明する。以下では、第1実施形態との相違点を中心に説明する。説明が省略される部分は第1実施形態と同様であってもよい。本実施形態は、第1実施形態と組み合わされてもよい。

30

#### 【0063】

図10(a)は、第1実施形態の図4(c)の位置における変換素子配置領域201Cの断面図を示す。本実施形態の不純物領域304の部分304aでは、不純物領域304の部分304bよりも、信号電荷と同じ導電型(本実施形態ではN型)の不純物の濃度が高い。このような濃度分布を有することによって、第1実施形態と同様に、不純物領域304における信号電荷の輸送経路は、部分304bから部分304cへ信号電荷を輸送するように単調に変化する電位分布を有する。したがって、本実施形態も、第1実施形態と同様の効果を奏する。

#### 【0064】

図10(b)は、本実施形態に係る光電変換装置100の製造方法を説明する図である。図10(b)は、図4(c)の断面図に対応する位置における光電変換装置100の製造途中の基板101の断面図を示す。本実施形態では、第1実施形態の図5(a)及び図5(b)の工程を実行した後に、図10(b)で説明する工程を実行し、その後に図5(c)～図5(e)の工程を実行する。

40

#### 【0065】

図10(b)に示すように、図5(b)の工程で形成されたレジストパターン503を使用して、不純物領域312よりも浅い位置にある不純物領域502の部分1001にN型不純物を注入する。これによって、不純物領域502の部分1001のN型不純物の濃度が上昇する。不純物領域502の部分1001は、不純物領域304の部分304aに対応する部分を含む。

#### 【0066】

50

上述の実施形態では、図 5 ( b ) の工程と図 10 ( b ) の工程で共通のレジストパターン 503 を使用しているため、交差画素回路 102C の光電変換素子 202 の不純物領域 303 の部分 303a にも N 型不純物が注入される。これにより、不純物領域 303 の部分 303a 及び 303c では、不純物領域 303 の部分 303b よりも、信号電荷と同じ導電型（本実施形態では N 型）の不純物の濃度が高くなる。光電変換素子 202 の不純物領域 303 と光電変換素子 203 の不純物領域 304 とを同様の不純物濃度の分布とすることによって、光電変換素子間の信号電荷の輸送特性（転送可能な電荷の最大量など）のばらつきが低減する。さらに、平行画素回路 102P の光電変換素子 202 及び 203 の不純物領域 303 及び 304 のうちゲート電極 204 及び 205 から遠くにある部分にも N 型不純物が注入される。これにより、2 種類の画素回路間の信号電荷の輸送特性（転送可能な電荷の最大量など）のばらつきが低減する。

10

#### 【0067】

##### <第4実施形態>

図 11 を参照して、第4実施形態に係る光電変換装置 100 について説明する。以下では、第1実施形態との相違点を中心に説明する。説明が省略される部分は第1実施形態と同様であってもよい。本実施形態は、第1実施形態から第3実施形態のいずれと組み合わされてもよい。

#### 【0068】

図 11 ( a ) ~ 図 11 ( f ) は、第1実施形態の図 4 ( a ) ~ 図 4 ( f ) に対応する図面である。本実施形態は、ゲート電極 204 及びゲート電極が、縦型構造を有する点で第1実施形態とは異なる。ゲート電極 204 が縦型構造を有するとは、図 11 ( c ) に示すように、基板 101 に形成された開口にゲート電極 204 が入り込んだ構造を有することであってもよい。ゲート電極 204 は、不純物領域 303 に隣接する位置まで縦方向 ( z 軸負の方向 ) に延びる。ゲート電極 204 は、不純物領域 303 のどの位置に隣接してもよい。ゲート電極 204 についての上述の説明は、ゲート電極 205 についても同様に当てはまる。

20

#### 【0069】

図 6 の右側のグラフ 602 に示すように、注入される P 型不純物の濃度は、基板 101 の表面 101a に近いほど高くなる。ゲート電極 204 及びゲート電極が縦型構造を有するため、不純物領域 303 及び 304 を第1実施形態と比較して基板 101 の深い位置 ( 表面 101a から離れた位置 ) に形成できる。そのため、図 7 ( a ) で説明したような電位障壁が形成されることを抑制できる。その結果、不純物領域 304 における信号電荷の輸送経路は、部分 304b から部分 304c へ信号電荷を輸送するように単調に変化する電位分布を有する。

30

#### 【0070】

##### <第5実施形態>

図 12 を参照して、第5実施形態に係る光電変換装置 100 について説明する。以下では、第1実施形態との相違点を中心に説明する。説明が省略される部分は第1実施形態と同様であってもよい。本実施形態は、第1実施形態から第4実施形態のいずれと組み合わされてもよい。

40

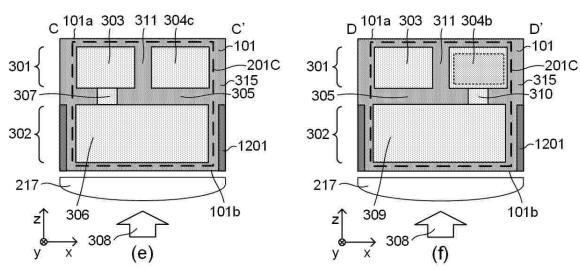

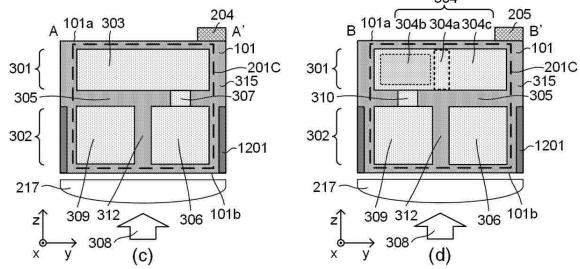

#### 【0071】

図 12 ( a ) ~ 図 12 ( f ) は、第1実施形態の図 4 ( a ) ~ 図 4 ( f ) に対応する図面である。本実施形態は、不純物領域 306 及び不純物領域 309 の側方にディープトレーンチ素子分離構造 1201 をさらに有する点で第1実施形態とは異なる。ディープトレーンチ素子分離構造 1201 は、平行画素回路 102P と交差画素回路 102C との両方に配置されてもよい。基板 101 の層 302 は、層 301 まで入射光が到達しないように、ある程度の厚さを有してもよい。基板 101 の層 302 が厚いと、斜めに入射した光によって画素間の混色が発生する恐れがある。特に、光電変換で生じた電子が、不純物領域 315 の電位障壁を超えて隣接画素へクロストークする恐れがある。本実施形態では、ディープトレーンチ素子分離構造 1201 によって、このような混色を抑制できる。ディープトレ

50

ンチ素子分離構造 1201 は、不純物領域 306 及び 309 と同程度の深さを有してもよい。また、ディープトレンチ素子分離構造 1201 は、基板 101 の裏面 101b まで到達してもよい。

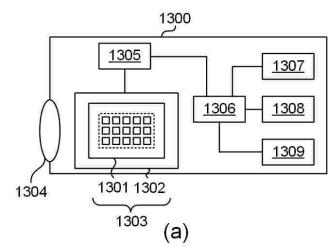

#### 【0072】

<その他の実施形態>

図 13(a) を参照しながら、半導体装置 1303 を備える機器 1300 に係る実施形態について詳細に説明する。半導体装置 1303 は、上述の何れの実施形態の光電変換装置であってもよい。半導体装置 1303 は、半導体デバイス 1301 と、半導体デバイス 1301 を収容するパッケージ 1302 とを含んでもよい。パッケージ 1302 は、半導体デバイス 1301 が固定された基体と、半導体デバイス 1301 に対向するガラスなどの蓋体と、を含んでもよい。パッケージ 1302 は、基体に設けられた端子と半導体デバイス 1301 に設けられた端子(ボンディングパッド)とを接続するボンディングワイヤやバンプなどの接合部材をさらに含んでもよい。

10

#### 【0073】

機器 1300 は、光学装置 1304、制御装置 1305、処理装置 1306、表示装置 1307、記憶装置 1308、および機械装置 1309 の少なくともいずれかを備えてもよい。光学装置 1304 は、例えばレンズやシャッター、ミラーである。制御装置 1305 は、半導体装置 1303 を制御する。制御装置 1305 は、例えば F P G A (Field Programmable Gate Array) や A S I C (Application Specific Integrated Circuit) などの半導体装置である。

20

#### 【0074】

処理装置 1306 は、半導体装置 1303 から出力された信号を処理する。処理装置 1306 は、A F E (アナログフロントエンド) あるいは D F E (デジタルフロントエンド) を構成するための、C P U (Central Processing Unit) や A S I C などの半導体装置である。表示装置 1307 は、半導体装置 1303 で得られた情報(画像)を表示する、E L (Electro-Luminescence) 表示装置や液晶表示装置である。記憶装置 1308 は、半導体装置 1303 で得られた情報(画像)を記憶する、磁気デバイスや半導体デバイスである。記憶装置 1308 は、S R A M (Static Random Access Memory) や D R A M (Dynamic Random Access Memory) などの揮発性メモリ、又はフラッシュメモリやハードディスクドライブなどの不揮発性メモリである。

30

#### 【0075】

機械装置 1309 は、モーターやエンジンなどの可動部又は推進部を有する。機器 1300 では、半導体装置 1303 から出力された信号を表示装置 1307 に表示したり、機器 1300 が備える通信装置(不図示)によって外部に送信したりする。そのために、機器 1300 は、半導体装置 1303 が有する記憶回路や演算回路とは別に、記憶装置 1308 や処理装置 1306 をさらに備えてもよい。機械装置 1309 は、半導体装置 1303 から出力され信号に基づいて制御されてもよい。

#### 【0076】

また、機器 1300 は、撮影機能を有する情報端末(例えばスマートフォンやウェアラブル端末)やカメラ(例えばレンズ交換式カメラ、コンパクトカメラ、ビデオカメラ、監視カメラ)などの電子機器に適する。カメラにおける機械装置 1309 は、ズーミングや合焦、シャッター動作のために光学装置 1304 の部品を駆動してもよい。これに代えて、カメラにおける機械装置 1309 は防振動作のために半導体装置 1303 を移動してもよい。

40

#### 【0077】

また、機器 1300 は、車両や船舶、飛行体などの輸送機器であり得る。輸送機器における機械装置 1309 は移動装置として用いられてもよい。輸送機器としての機器 1300 は、半導体装置 1303 を輸送するものや、撮影機能により運転(操縦)の補助および/または自動化を行うものであってもよい。運転(操縦)の補助および/または自動化のための処理装置 1306 は、半導体装置 1303 で得られた情報に基づいて移動装置とし

50

ての機械装置 1309 を操作するための処理を行ってもよい。これに代えて、機器 1300 は、内視鏡などの医療機器や、分析測距センサなどの計測機器、電子顕微鏡のような分析機器、複写機などの事務機器であってもよい。

#### 【0078】

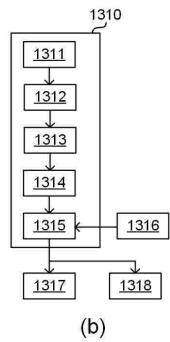

図 13 (b) 及び図 13 (c) を用いて、撮像システム及び移動体に係る実施形態について説明する。図 13 (b) は、車載カメラに関する撮像システム 1310 の一例を示したものである。撮像システム 1310 は、光電変換装置 1311 を有する。光電変換装置 1311 は、上述の実施形態の何れの光電変換装置であってもよい。撮像システム 1310 は、光電変換装置 1311 により取得された複数の画像データに対し、画像処理を行う処理装置である画像処理部 1312 を有する。また、撮像システム 1310 は、光電変換装置 1311 により取得された複数の画像データから視差（視差画像の位相差）の算出を行う処理装置である視差取得部 1313 を有する。さらに、撮像システム 1310 は、算出された視差に基づいて対象物までの距離を算出する処理装置である距離取得部 1314 と、算出された距離に基づいて衝突可能性があるか否かを判定する処理装置である衝突判定部 1315 と、を有する。ここで、視差取得部 1313 や距離取得部 1314 は、対象物までの距離情報等の情報を取得する情報取得手段の一例である。すなわち、距離情報とは、視差、デフォーカス量、対象物までの距離等に関する情報である。衝突判定部 1315 はこれらの距離情報のいずれかを用いて、衝突可能性を判定してもよい。上述した各種の処理装置は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールに基づいて演算を行う汎用のハードウェアによって実現されてもよい。また、処理装置は、FPGA、ASIC 等によって実現されてもよいし、これらの組合せによつて実現されてもよい。

10

20

30

#### 【0079】

撮像システム 1310 は、車両情報取得装置 1316 と接続されており、車速、ヨーレート、舵角などの車両情報を取得することができる。また、撮像システム 1310 は、衝突判定部 1315 での判定結果に基づいて、車両に対して制動力を発生させる制御信号を出力する制御装置である制御 ECU 1317 に接続されている。すなわち、制御 ECU 1317 は、距離情報に基づいて移動体を制御する移動体制御手段の一例である。また、撮像システム 1310 は、衝突判定部 1315 での判定結果に基づいて、ドライバーへ警報を発する警報装置 1318 にも接続されている。例えば、衝突判定部 1315 の判定結果として衝突可能性が高い場合に、制御 ECU 1317 はブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして衝突を回避、被害を軽減する車両制御を行う。警報装置 1318 は音等の警報を鳴らす、カーナビゲーションシステムなどの画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

#### 【0080】

本実施形態では、車両の周囲、例えば前方又は後方を撮像システム 1310 で撮像する。図 13 (c) に、車両前方（撮像範囲 1319）を撮像する場合の撮像システム 1310 を示した。車両情報取得装置 1316 は、撮像システム 1310 を動作させ撮像を実行させるように指示を送る。

30

40

#### 【0081】

以上の説明では、他の車両と衝突しないように制御する例を述べたが、他の車両に追従して自動運転する制御、車線からはみ出さないように自動運転する制御等にも適用可能である。更に、撮像システムは、自動車等の車両に限らず、例えば、船舶、航空機あるいは産業用ロボットなどの移動体（輸送機器）に適用することができる。移動体（輸送機器）における移動装置はエンジン、モーター、車輪、プロペラなどの各種の移動手段である。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

#### 【0082】

発明は上記実施形態に制限されるものではなく、発明の精神及び範囲から離脱することなく、様々な変更及び変形が可能である。従って、発明の範囲を公にするために請求項を

50

添付する。

【符号の説明】

【0 0 8 3】

1 0 0 光電変換装置、1 0 1 基板、2 0 2 光電変換素子 2 0 3 光電変換素子

10

20

30

40

50

## 【図面】

## 【図 1】

## 【図 2】

10

## 【図 3】

## 【図 4】

20

30

40

50

【図5】

【図6】

10

20

30

40

【図7】

【図8】

50

【図9】

【図10】

【図11】

【図12】

10

20

30

40

50

【図 1 3】

10

20

30

40

50

---

フロントページの続き

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 脇水 佳弘

(56)参考文献 特開2020-141122(JP,A)

韓国公開特許第10-2005-0040360(KR,A)

米国特許出願公開第2021/0210532(US,A1)

特開2019-009425(JP,A)

特開2006-191100(JP,A)

特開2021-090022(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H04N 25/70