(10) DE 10 2012 224 361 B4 2022.02.24

(12)

## Patentschrift

(21) Aktenzeichen: 10 2012 224 361.5

(51) Int Cl.: H03K 19/0185 (2006.01)

(22) Anmelddatag: 24.12.2012

H01L 27/12 (2006.01)

(43) Offenlegungstag: 27.06.2013

(45) Veröffentlichungstag

der Patenterteilung: 24.02.2022

Innerhalb von neun Monaten nach Veröffentlichung der Patenterteilung kann nach § 59 Patentgesetz gegen das Patent Einspruch erhoben werden. Der Einspruch ist schriftlich zu erklären und zu begründen. Innerhalb der Einspruchsfrist ist eine Einspruchsgebühr in Höhe von 200 Euro zu entrichten (§ 6 Patentkostengesetz in Verbindung mit der Anlage zu § 2 Abs. 1 Patentkostengesetz).

(30) Unionspriorität:

**2011-282510** 23.12.2011 JP

(72) Erfinder:

**Ohshima, Kazuaki, Atsugi-shi, Kanagawa-ken, JP**

(73) Patentinhaber:

**Semiconductor Energy Laboratory Co., Ltd.,

Atsugi-shi, Kanagawa-ken, JP**

(56) Ermittelter Stand der Technik:

US 2006 / 0 244 107 A1

EP 1 737 044 A1

(74) Vertreter:

**Grünecker Patent- und Rechtsanwälte PartG mbB,

80802 München, DE**

### (54) Bezeichnung: Pegelverschieberschaltung und integrierte Halbleiterschaltung

(57) Hauptanspruch: Pegelverschieberschaltung, die umfasst:

einen ersten Transistor (101, 410), der umfasst:

eine erste Gate-Elektrode (405);

eine zweite Gate-Elektrode (398);

eine Source-Elektrode (416a); und

einen Kanalbereich (408) zwischen der ersten Gate-Elektrode (405) und der zweiten Gate-Elektrode (398); und

eine Wechselrichterschaltung (102), die elektrisch mit dem ersten Transistor (101) verbunden ist, wobei die Wechselrichterschaltung (102) einen Eingangsanschluss (IN) und einen Ausgangsanschluss (OUT) aufweist,

wobei die erste Gate-Elektrode (405) und die Source-Elektrode (416a) konfiguriert sind, um mit einem ersten Leistungsversorgungspotenzial (V1) versorgt zu werden,

wobei die zweite Gate-Elektrode (398) konfiguriert ist, um mit einem zweiten Leistungsversorgungspotenzial (V2) versorgt zu werden,

wobei die Wechselrichterschaltung (102) konfiguriert ist, um mit einem dritten Leistungsversorgungspotenzial (V3) als ein Leistungsversorgungspotenzial versorgt zu werden,

wobei der Eingangsanschluss (IN) konfiguriert ist, um mit einem Eingangssignal versorgt zu werden,

wobei das dritte Leistungsversorgungspotenzial (V3) oder ein Potenzial, das durch Abziehen einer Menge an Veränderung einer Schwellenspannung des ersten Transistors (101, 410) von dem ersten Leistungsversorgungspotenzial (V1) erhalten wird, als eine Leistungsversorgungsspannung zu der Wechselrichterschaltung (102) zugeführt wird,

**Beschreibung**

## Hintergrund der Erfindung

## 1. Gebiet der Erfindung

**[0001]** Die vorliegende Erfindung bezieht sich auf einen Pegelverschieber, bei dem ein Transistor verwendet wird. Außerdem bezieht sich die Erfindung auf ein Ansteuerverfahren dafür.

## 2. Beschreibung des Standes der Technik

**[0002]** In den letzten Jahren werden zum Herstellen der elektronischen Geräte mit höheren Leistungen integrierte Halbleiterschaltungen wie z. B. LSI entwickelt, in dem eine Vielzahl von Funktionen aufweisende Schaltungen wie z. B. ein Hauptprozessor (central processing unit: CPU) und ein Speicher in einem Chip eingebaut sind. Man erwartet, dass die Leistungsversorgungsspannung für solche integrierten Schaltungen verringert wird, damit der Energieverbrauch reduziert wird. In dem Fall, in dem Signale zwischen den eine Vielzahl von Funktionen aufweisenden Schaltungen, deren Leistungsversorgungsspannungen voneinander unterschiedlich sind, gesendet und empfangen werden, ist es erforderlich, Pegel der Signale umzusetzen.

**[0003]** Hinsichtlich eines Verfahrens zum Umsetzen des Pegels offenbart das Patentdokument 1 eine Pegelverschieberschaltung, bei der ein Gate und ein Drain eines n-Kanal-MOS-Transistors gemeinsam mit einer Leistungsversorgungsspannung VDD verbunden sind und eine Source des n-Kanal-MOS-Transistors mit einem leistungsversorgungsseitigen Schaltungsanschluss einer CMOS-Wechselrichterschaltung verbunden ist. Bei der Pegelverschieberschaltung, die in dem Patentdokument 1 offenbart ist, wird die Schwellenspannung des n-Kanal-MOS-Transistors durch Verbinden einer p-Wanne, die einem Rückgate des n-Kanal-MOS-Transistors entspricht, mit GND gesteuert, wodurch ein Signal mit solch einer Wellenform ausgegeben wird, dass ein „H“-Pegel eines Ausgangspulses der Pegelverschieberschaltung niedriger als die Leistungsversorgungsspannung VDD um einen Wert ist, der nahe der Schwellenspannung des n-Kanal-MOS-Transistors ist.

[Referenz]

[Patentdokument]

**[0004]** [Patentdokument 1] Japanische Patentoffenlegungsschrift Nr. 2001-077684.

**[0005]** EP 1 737 044 A1 befasst sich mit einem amorphen Oxid und einem Dünnfilmtransistor. Ein amorphes Oxid gemäß dem Dokument ist dadurch

gekennzeichnet, dass die Elektronenträgerkonzentration weniger als  $10^{18}/\text{cm}^3$  beträgt. Wenn ein Feldeffektransistor eine Kanalschicht enthält, die aus einem amorphen Oxidfilm mit einer Ladungsträgerkonzentration von weniger als  $10^{18}/\text{cm}^3$ , einem Source-Anschluß, einem Drain-Anschluß und einem Gate-Anschluß besteht, die auf dem Gate-Isolierfilm angeordnet sind, kann der Strom zwischen dem Source- und dem Drain-Anschluß auf etwa  $10^{-7}$  A eingestellt werden, wenn eine Spannung von etwa 5 V an den Source- und den Drain-Anschluß ohne Anlegen einer Gate-Spannung angelegt wird.

**[0006]** US 2006 / 0 244 107 A1 bietet eine Halbleitervorrichtung, ein Herstellungsverfahren und eine elektronische Vorrichtung. Für den Fall, dass einer aus einer Vielzahl von offengelegten Dünnfilmtransistoren auf eine Flüssigkristall-Anzeigevorrichtung aufgebracht wird, kann die Schwellenspannung durch Steuerung der Dotierungsmenge entsprechend eingestellt werden. Daher kann jeder der Dünnfilmtransistoren als ein Transistor zur Ansteuerung eines Bildelements verwendet werden.

## Zusammenfassung der Erfindung

**[0007]** Jedoch ist es nicht leicht bei dem Verfahren, bei dem der Pegel durch die Steuerung der Schwellenspannung des mit dem Wechselrichter verbundenen Transistors umgesetzt wird, die Spannung eines Ausgangsanschlusses hochpräzise zu steuern. Das liegt daran, dass eine Schwankung der Schwellenspannung jedes Transistors die Spannung des Ausgangsanschlusses verändert.

**[0008]** Ferner ist dann, wenn die Signale zwischen den eine Vielzahl von Funktionen aufweisenden Schaltungen, deren Leistungsversorgungsspannungen voneinander unterschiedlich sind, unter Verwendung einer Vielzahl von solchen Pegelverschieberschaltungen übertragen werden, erforderlich, die Schwellenspannung jedes mit dem Wechselrichter verbundenen Transistors zu steuern, damit die Vielzahl von Pegelverschieberschaltungen unterschiedliche Spannungen ausgeben können.

**[0009]** Von diesem Standpunkt aus betrachtet, wird es bei der Pegelverschieberschaltung, die in dem Patentdokument 1 offenbart ist, als nötig angesehen, die Spannung eines Substrats zu verändern, damit die Schwellenspannung des Transistors verändert wird. Die Veränderung der Spannung des Substrats macht es jedoch schwierig, die Schwellenspannungen einer Vielzahl von Transistoren getrennt zu steuern, weil die Schwellenspannung eines Transistors in einer anderen Schaltung auch verändert wird. Außerdem wird eine weitere Schaltung erforderlich, um die Schwellenspannungen der Vielzahl von Transistoren getrennt zu steuern, was die Schaltung vergrößert.

**[0010]** Wenn eine Vielzahl von Pegelverschieberschaltungen unter Verwendung eines Siliziumwafers hergestellt werden, ist es erforderlich, die Länge L oder die Mengen an Kanaldotierung der Transistoren, die je mit dem Wechselrichter verbunden sind, zu variieren, um die Schwellenspannungen der Transistoren zu variieren. Dies kompliziert den Schaltungsaufbau.

**[0011]** Angesichts der oben angegebenen Probleme hat eine Ausführungsform der vorliegenden Erfindung eine Aufgabe, eine verkleinerte Pegelverschieberschaltung zur Verfügung zu stellen. Außerdem hat eine Ausführungsform der vorliegenden Erfindung eine Aufgabe, eine Pegelverschieberschaltung anzubieten, bei der Ausgangssignale mit unterschiedlichen Amplituden aus einer Vielzahl von Ausgangsanschlüssen ausgegeben werden können. Außerdem hat eine Ausführungsform der vorliegenden Erfindung eine Aufgabe, unter Verwendung der Pegelverschieberschaltung eine weiter verkleinerte integrierte Halbleiterschaltung mit reduziertem Energieverbrauch anzubieten.

Die Aufgabe wird gelöst durch eine Pegelverschieberschaltung nach den Ansprüchen 1, 2, 6, 7 und 11.

**[0012]** Eine Ausführungsform der vorliegenden Erfindung ist eine Pegelverschieberschaltung, die aufweist: einen ersten Eingangsanschluss, an den ein erstes Leistungsversorgungspotenzial angelegt wird, einen zweiten Eingangsanschluss, an den ein zweites Leistungsversorgungspotenzial angelegt wird, einen dritten Eingangsanschluss, an den ein drittes Leistungsversorgungspotenzial angelegt wird, einen vierten Eingangsanschluss, an den ein erstes Eingangssignal angelegt wird, einen ersten Ausgangsanschluss, aus dem ein Signal ausgegeben wird, einen n-Kanal ersten Transistor, und eine Wechselrichterschaltung, die einen p-Kanal zweiten Transistor und einen n-Kanal dritten Transistor aufweist.

**[0013]** Bei dem n-Kanal ersten Transistor ist ein Kanalbereich in einem Oxidhalbleiterfilm ausgebildet, und ein Paar von Gate-Elektroden, die dazwischen den Oxidhalbleiterfilm aufweisen, sind vorgesehen. Es ist zu bevorzugen, dass sich eine von dem Paar von Gate-Elektroden mit dem Oxidhalbleiterfilm mit einem dazwischen liegenden ersten Gate-Isolierfilm überlappt, und sich die andere von dem Paar von Gate-Elektroden mit dem Oxidhalbleiterfilm mit einem dazwischen liegenden zweiten Gate-Isolierfilm überlappt. Hier ist eine von dem Paar von Gate-Elektroden eine erste Gate-Elektrode des ersten Transistors. Ferner ist die andere von dem Paar von Gate-Elektroden eine zweite Gate-Elektrode (auch als ein Rückgate bezeichnet) des ersten Transistors. Die Schwellenspannung des ersten Transistors wird von dem Potenzialniveau der zweiten Gate-Elektrode, insbesondere von der Differenz zwi-

schen Potenzialen einer Source-Elektrode des ersten Transistors und der zweiten Gate-Elektrode, gesteuert. Die Menge an Veränderung der Schwellenspannung des ersten Transistors,  $\Delta V_{th}$ , kann von dem zweiten Leistungsversorgungspotenzial, das an die zweite Gate-Elektrode des ersten Transistors angelegt wird, gesteuert werden.

**[0014]** Zu beachten ist, dass in dieser Beschreibung und dergleichen die „Menge an Veränderung der Schwellenspannung“ eines Transistors eine Menge an Veränderung der Schwellenspannung vor und nach dem Anlegen eines Potenzials an die zweite Gate-Elektrode des Transistors bedeutet.

**[0015]** Bei jedem des p-Kanal zweiten Transistors und des n-Kanal dritten Transistors ist ein Kanalbereich in einem Halbleiterfilm aus Silizium oder dergleichen ausgebildet. Als der Halbleiterfilm kann ein einkristalliner Halbleiterfilm oder ein polykristalliner Halbleiterfilm aus Silizium, Siliziumkarbid oder dergleichen, oder ein Verbindungshalbleiterfilm aus Silizium-Germanium, Galliumarsenid, Indiumphosphid oder dergleichen verwendet werden.

**[0016]** Eine Gate-Elektrode des zweiten Transistors und eine Gate-Elektrode des dritten Transistors sind mit dem vierten Eingangsanschluss verbunden, und eine Drain-Elektrode des zweiten Transistors und eine Source-Elektrode des dritten Transistors sind mit dem ersten Ausgangsanschluss verbunden. Außerdem ist eine Drain-Elektrode des dritten Transistors mit dem dritten Eingangsanschluss verbunden.

**[0017]** Die Source-Elektrode und die erste Gate-Elektrode des ersten Transistors sind mit dem ersten Eingangsanschluss verbunden, die zweite Gate-Elektrode des ersten Transistors ist mit dem zweiten Eingangsanschluss verbunden, und die Drain-Elektrode des ersten Transistors ist mit der Source-Elektrode des zweiten Transistors verbunden.

**[0018]** Infolgedessen wird bei der Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung das dritte Leistungsversorgungspotenzial aus dem ersten Ausgangsanschluss der Wechselrichterschaltung ausgegeben, wenn das Eingangssignal von einem niedrigen Pegel auf einen hohen Pegel geändert wird. Außerdem wird dann, wenn das Eingangssignal von einem hohen Pegel auf einen niedrigen Pegel geändert wird, ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des ersten Transistors von dem ersten Leistungsversorgungspotenzial erhalten wird, aus dem ersten Ausgangsanschluss der Wechselrichterschaltung ausgegeben. Die Schwellenspannung des ersten Transistors kann von dem zweiten Leistungsversorgungspotenzial,

das an die zweite Gate-Elektrode des ersten Transistors angelegt wird, gesteuert werden.

**[0019]** Die Schwellenspannung des ersten Transistors, bei dem ein Oxidhalbleiterfilm verwendet wird, wird von dem an die zweite Gate-Elektrode des ersten Transistors angelegten Potenzial verändert, wodurch das Potenzial, das aus der Wechselrichterschaltung ausgegeben wird, leicht gesteuert werden kann.

**[0020]** Selbst wenn eine Vielzahl von Pegelverschieberschaltungen, die je die oben angegebene Struktur aufweisen, verwendet wird, kann in jeder der Pegelverschieberschaltungen die Schwellenspannung des Transistors, bei dem ein Oxidhalbleiterfilm verwendet wird, einzeln verändert werden. Dadurch können unterschiedliche Potenziale (oder Signale) aus der Vielzahl von Pegelverschieberschaltungen ausgegeben werden.

**[0021]** Eine Ausführungsform der vorliegenden Erfindung ist eine Pegelverschieberschaltung, die aufweist: einen ersten Eingangsanschluss, an den ein erstes Leistungsversorgungspotenzial angelegt wird; einen zweiten Eingangsanschluss, an den ein zweites Leistungsversorgungspotenzial angelegt wird; einen dritten Eingangsanschluss, an den ein drittes Leistungsversorgungspotenzial angelegt wird; einen vierten Eingangsanschluss, an den ein erstes Eingangssignal angelegt wird; einen ersten Ausgangsanschluss, aus dem ein erstes Ausgangssignal ausgegeben wird; einen ersten Transistor, an dessen Source-Elektrode und dessen erste Gate-Elektrode das erste Leistungsversorgungspotenzial angelegt wird und an dessen zweite Gate-Elektrode das zweite Leistungsversorgungspotenzial angelegt wird; und eine Wechselrichterschaltung, an die das erste Eingangssignal angelegt wird, zu der ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des ersten Transistors von dem ersten Leistungsversorgungspotenzial erhalten wird, oder das dritte Leistungsversorgungspotenzial als die Leistungsversorgungsspannung zugeführt wird, und aus der das erste Ausgangssignal ausgegeben wird. Ein Kanalbereich des ersten Transistors ist in einem Oxidhalbleiterfilm ausgebildet.

**[0022]** Ferner ist eine Ausführungsform der vorliegenden Erfindung eine Pegelverschieberschaltung, die aufweist: einen ersten Eingangsanschluss, an den ein erstes Leistungsversorgungspotenzial angelegt wird; einen zweiten Eingangsanschluss, an den ein zweites Leistungsversorgungspotenzial angelegt wird; einen dritten Eingangsanschluss, an den ein drittes Leistungsversorgungspotenzial angelegt wird; einen vierten Eingangsanschluss, an den ein erstes Eingangssignal angelegt wird; einen ersten Ausgangsanschluss, aus dem ein erstes Ausgangs-

signal ausgegeben wird; einen zweiten Ausgangsanschluss, aus dem ein zweites Ausgangssignal ausgegeben wird; einen ersten Transistor, an dessen Source-Elektrode und dessen erste Gate-Elektrode das erste Leistungsversorgungspotenzial angelegt wird und an dessen zweite Gate-Elektrode das zweite Leistungsversorgungspotenzial angelegt wird; eine erste Wechselrichterschaltung, an die das erste Eingangssignal angelegt wird, zu der ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des ersten Transistors von dem ersten Leistungsversorgungspotenzial erhalten wird, oder das dritte Leistungsversorgungspotenzial als die Leistungsversorgungsspannung zugeführt wird, und aus der das erste Ausgangssignal ausgegeben wird; und eine zweite Wechselrichterschaltung, in die das erste Ausgangssignal, das aus der ersten Wechselrichterschaltung ausgegeben wird, eingegeben wird, zu der das Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des ersten Transistors von dem ersten Leistungsversorgungspotenzial erhalten wird, oder das dritte Leistungsversorgungspotenzial als die Leistungsversorgungsspannung zugeführt wird, und aus der das zweite Ausgangssignal ausgegeben wird. Ein Kanalbereich des ersten Transistors ist in einem Oxidhalbleiterfilm ausgebildet.

**[0023]** Ferner ist eine Ausführungsform der vorliegenden Erfindung eine Pegelverschieberschaltung, die aufweist: einen ersten Eingangsanschluss, an den ein erstes Leistungsversorgungspotenzial angelegt wird; einen zweiten Eingangsanschluss, an den ein zweites Leistungsversorgungspotenzial angelegt wird; einen dritten Eingangsanschluss, an den ein drittes Leistungsversorgungspotenzial angelegt wird; einen vierten Eingangsanschluss, an den ein vierter Leistungsversorgungspotenzial angelegt wird; einen fünften Eingangsanschluss, an den ein erstes Eingangssignal angelegt wird; einen ersten Ausgangsanschluss, aus dem ein erstes Ausgangssignal ausgegeben wird; einen zweiten Ausgangsanschluss, aus dem ein zweites Ausgangssignal ausgegeben wird; einen ersten Transistor, an dessen Source-Elektrode und dessen erste Gate-Elektrode das erste Leistungsversorgungspotenzial angelegt wird und an dessen zweite Gate-Elektrode das zweite Leistungsversorgungspotenzial angelegt wird; einen zweiten Transistor, an dessen Source-Elektrode das dritte Leistungsversorgungspotenzial angelegt wird und an dessen zweite Gate-Elektrode das vierte Leistungsversorgungspotenzial angelegt wird; eine erste Wechselrichterschaltung, an die das erste Eingangssignal angelegt wird, zu der ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des ersten Transistors von dem ersten Leistungsversorgungspotenzial erhalten wird, oder ein Potenzial, das durch Addieren der Menge an Veränderung der Schwellenspannung des zweiten Transistors zu dem dritten Leistungsver-

sorgungspotenzial erhalten wird, als die Leistungsversorgungsspannung zugeführt wird, und aus der das erste Ausgangssignal ausgegeben wird; und eine zweite Wechselrichterschaltung, in die das erste Ausgangssignal, das aus der ersten Wechselrichterschaltung ausgegeben wird, eingegeben wird, zu der das Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des ersten Transistors von dem ersten Leistungsversorgungspotenzial erhalten wird, oder das Potenzial, das durch Addieren der Menge an Veränderung der Schwellenspannung des zweiten Transistors zu dem dritten Leistungsversorgungspotenzial erhalten wird, als die Leistungsversorgungsspannung zugeführt wird, und aus der das zweite Ausgangssignal ausgegeben wird. Ein Kanalbereich jedes des ersten Transistors und des zweiten Transistors ist in einem Oxidhalbleiterfilm ausgebildet.

**[0024]** Bei jeder der oben angegebenen Strukturen weist die zweite Wechselrichterschaltung einen p-Kanal dritten Transistor und einen n-Kanal vierten Transistor auf, und bei jedem des dritten Transistors und des vierten Transistors ist ein Kanalbereich in einem Siliziumfilm ausgebildet.

**[0025]** Bei jeder der oben angegebenen Strukturen weist die erste Wechselrichterschaltung einen p-Kanal fünften Transistor und einen n-Kanal sechsten Transistor auf, und bei jedem des fünften Transistors und des sechsten Transistors ist ein Kanalbereich in einem Siliziumfilm ausgebildet.

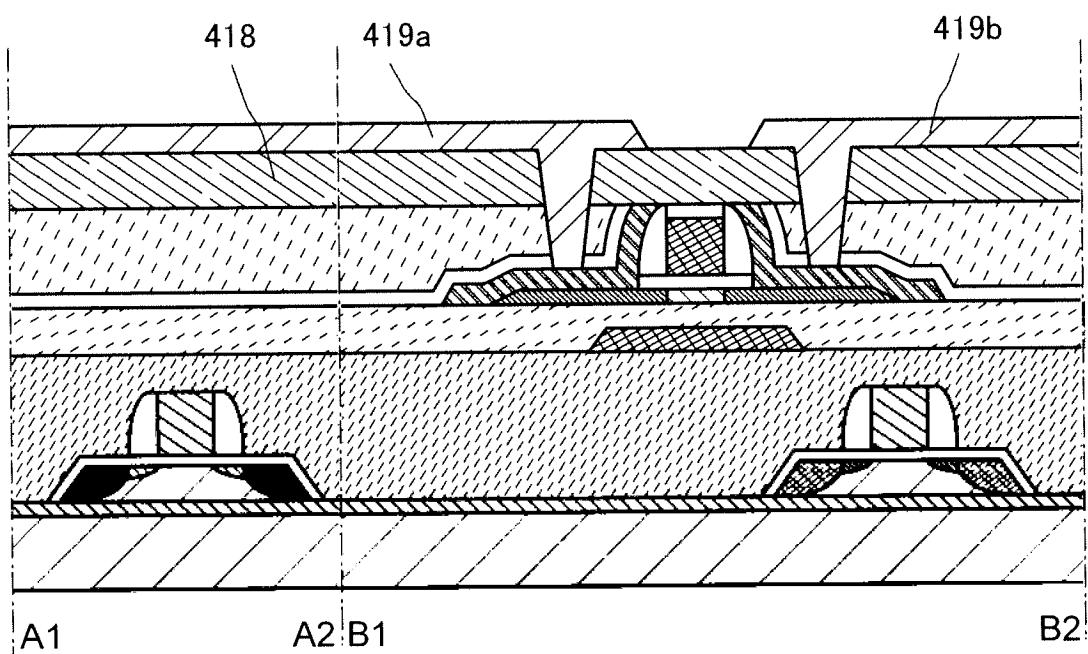

**[0026]** Außerdem kann eine integrierte Halbleiterorschaltung unter Verwendung einer Pegelverschieberschaltung, die eine der oben angegebenen Strukturen aufweist, und eines Speicherzellenarrays, das eine Vielzahl von Speicherzellen je mit einem siebten Transistor und einem Kondensator aufweist, gebildet werden. Ein Kanalbereich des siebten Transistors ist wie bei den ersten und zweiten Transistoren in einem Oxidhalbleiterfilm ausgebildet.

**[0027]** Entsprechend einer Ausführungsform der vorliegenden Erfindung kann eine verkleinerte Pegelverschieberschaltung zur Verfügung gestellt werden. Außerdem kann eine Pegelverschieberschaltung angeboten werden, bei der Ausgangssignale mit unterschiedlichen Amplituden aus einer Vielzahl von Ausgangsanschlüssen ausgegeben werden können. Ferner kann unter Verwendung der Pegelverschieberschaltung eine weiter verkleinerte integrierte Halbleiterorschaltung mit reduziertem Energieverbrauch angeboten werden.

#### Figurenliste

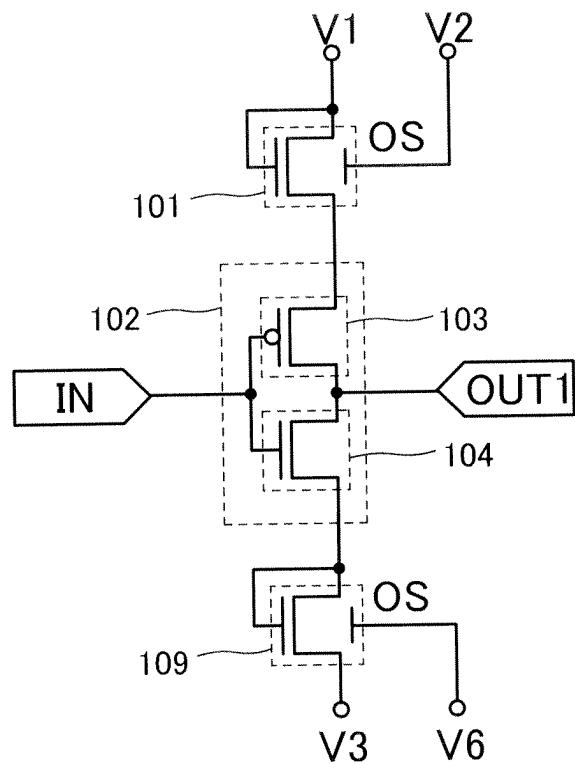

**Fig. 1A bis Fig. 1C** zeigen je eine Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung.

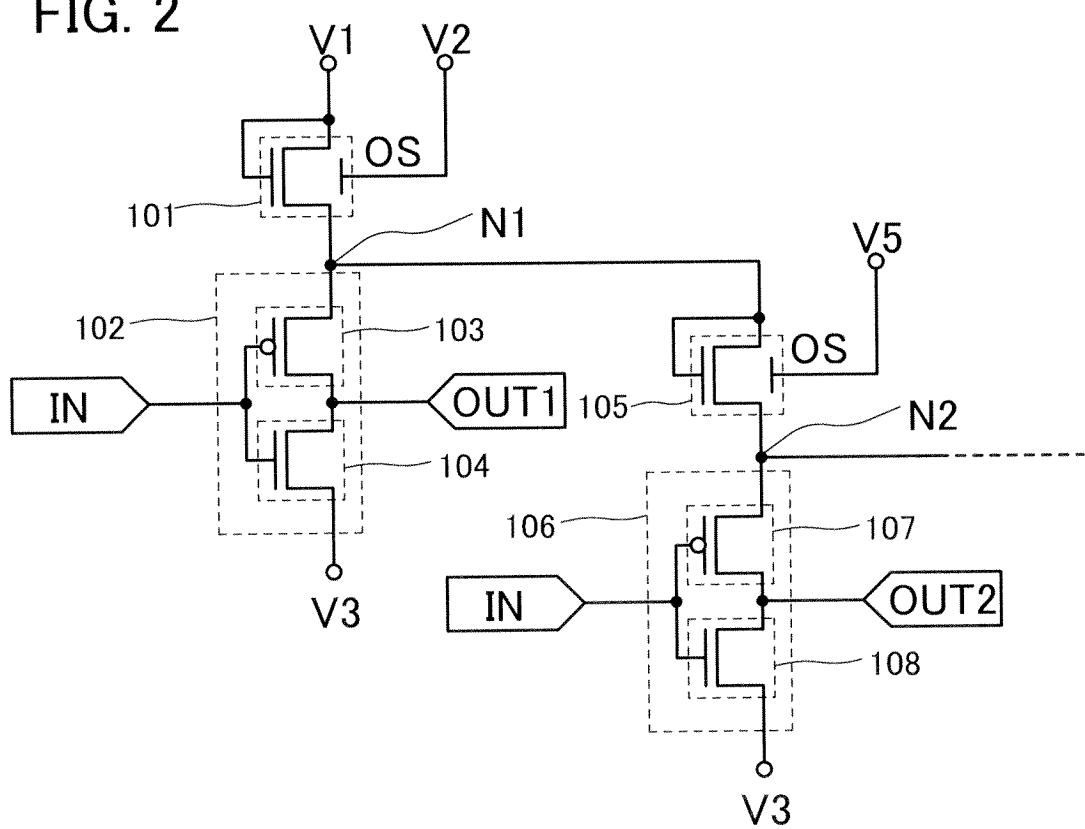

**Fig. 2** zeigt eine Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung.

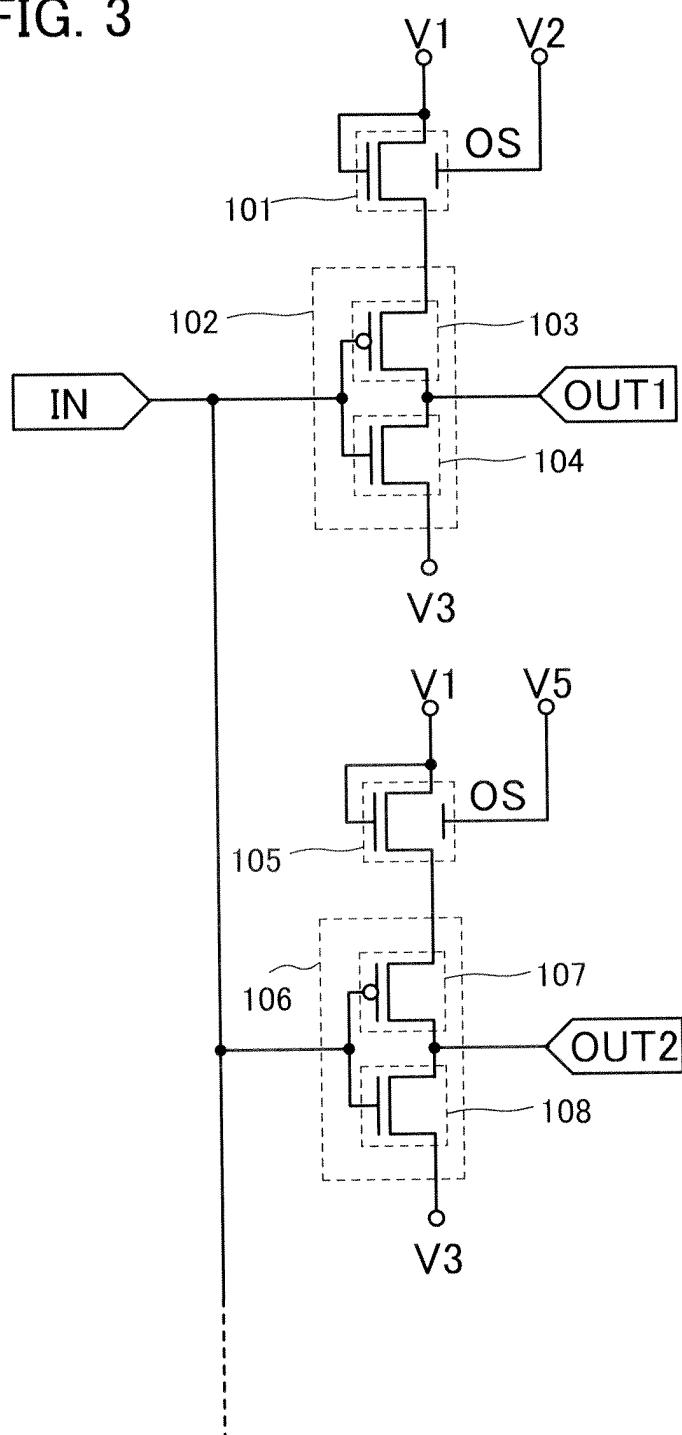

**Fig. 3** zeigt eine Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung.

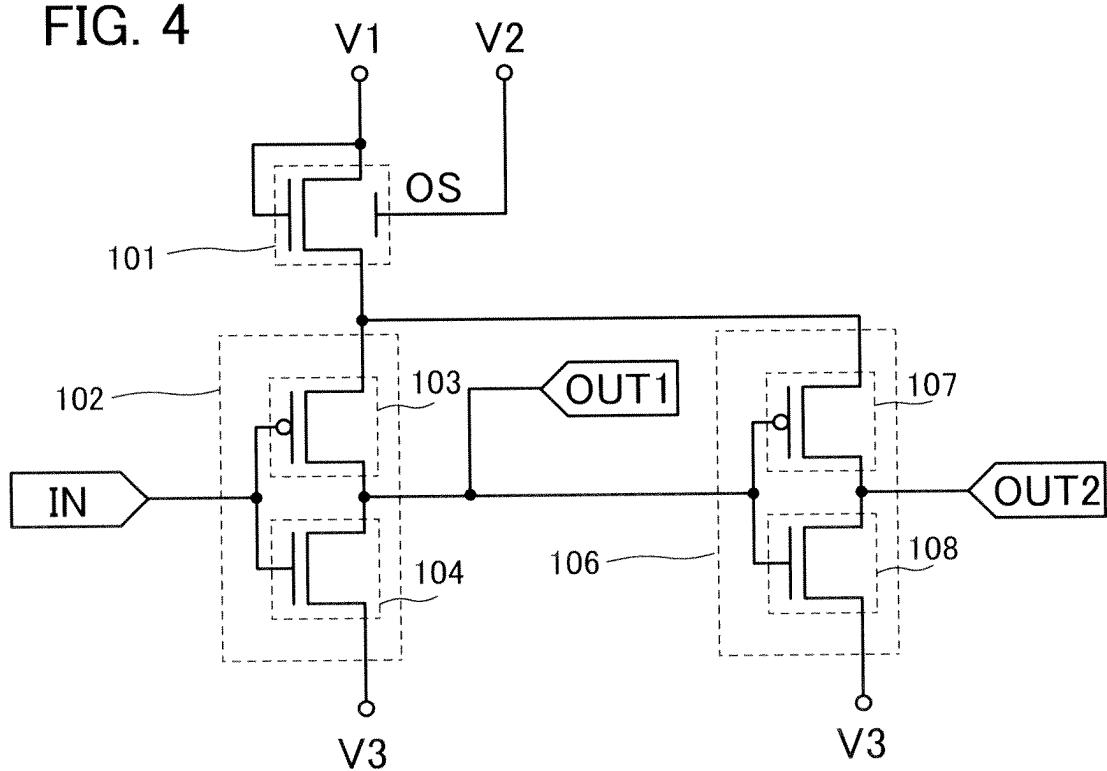

**Fig. 4** zeigt eine Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung.

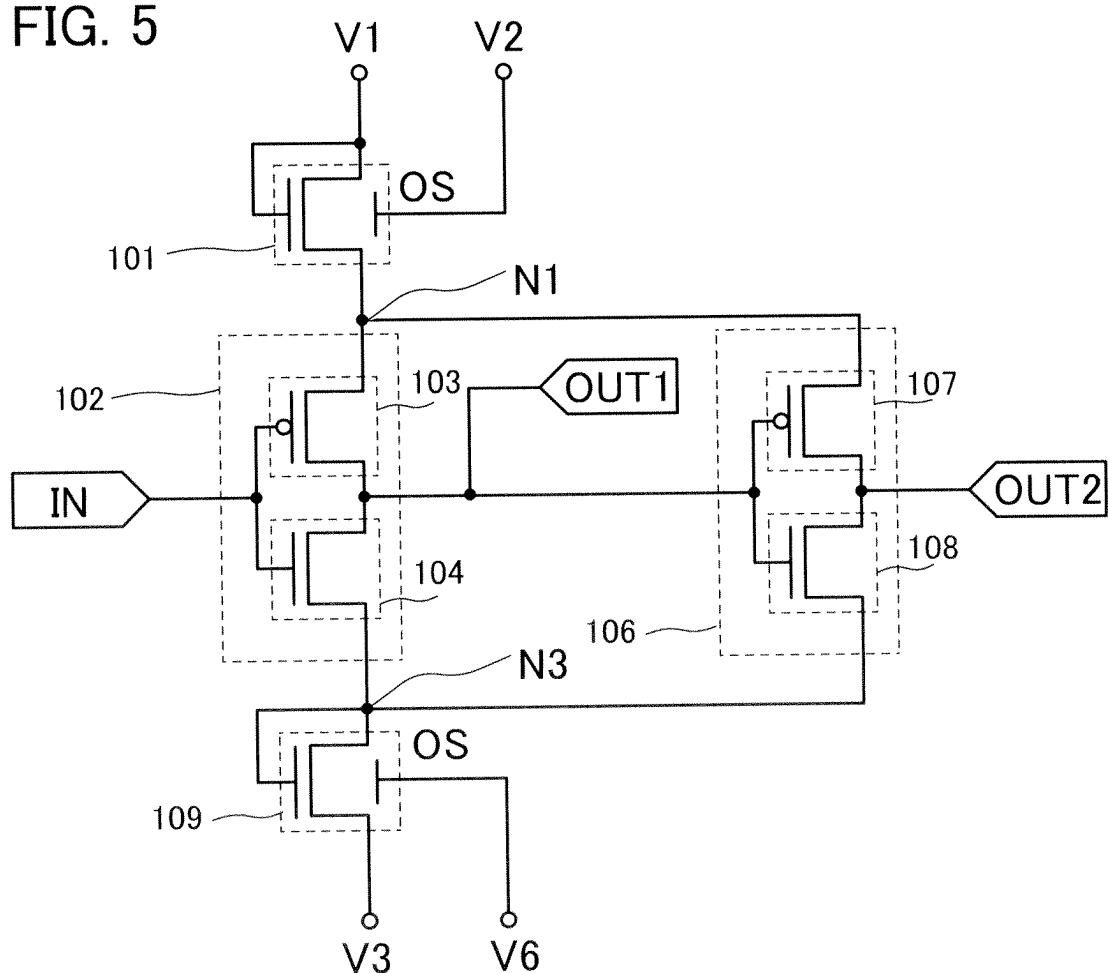

**Fig. 5** zeigt eine Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung.

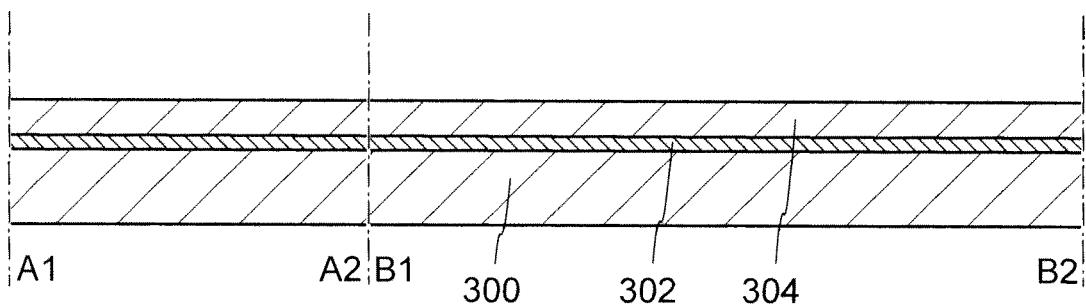

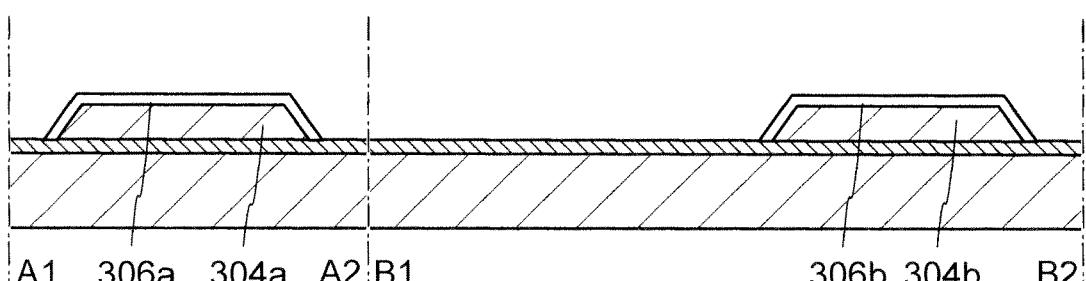

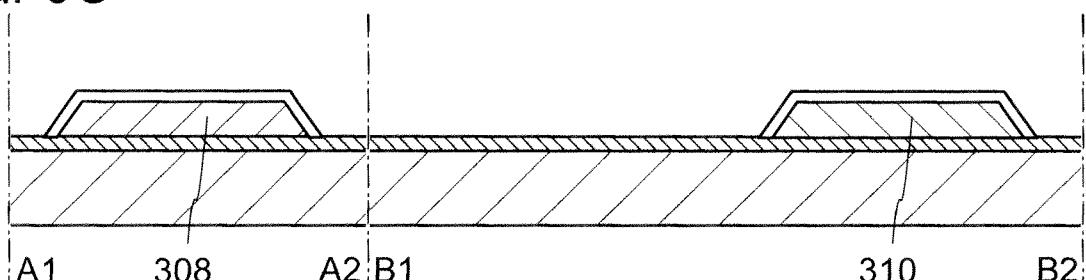

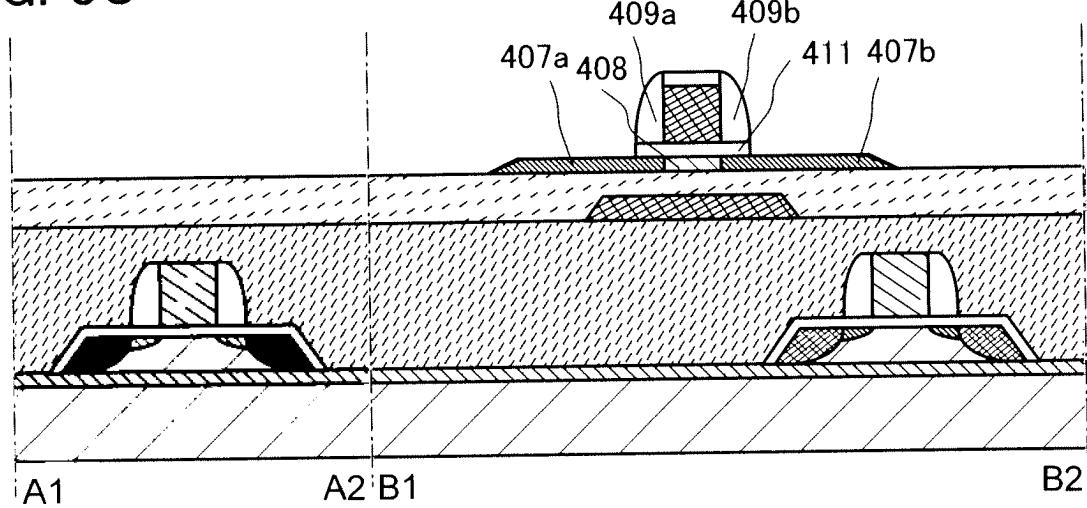

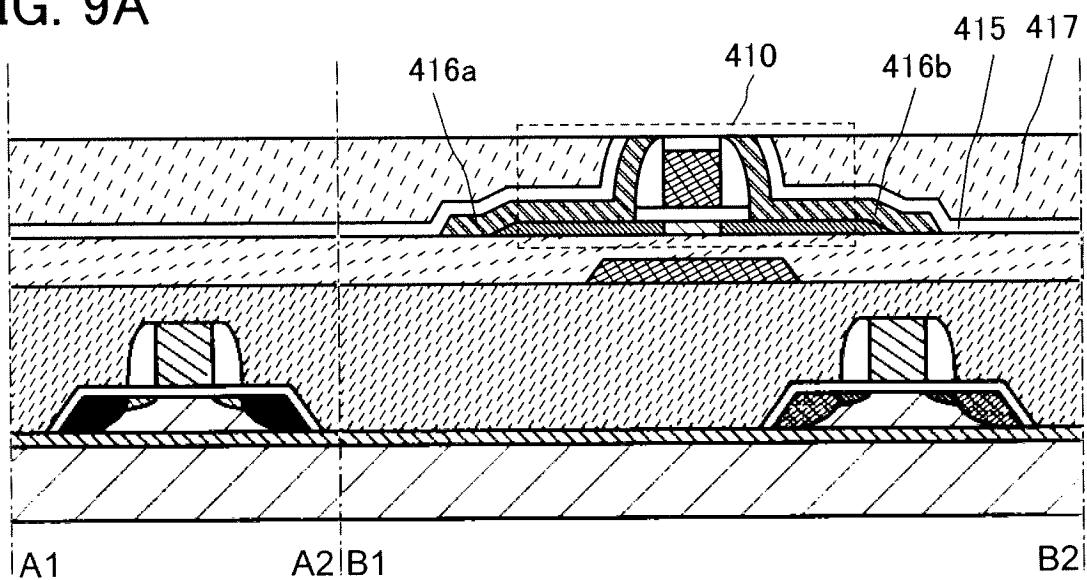

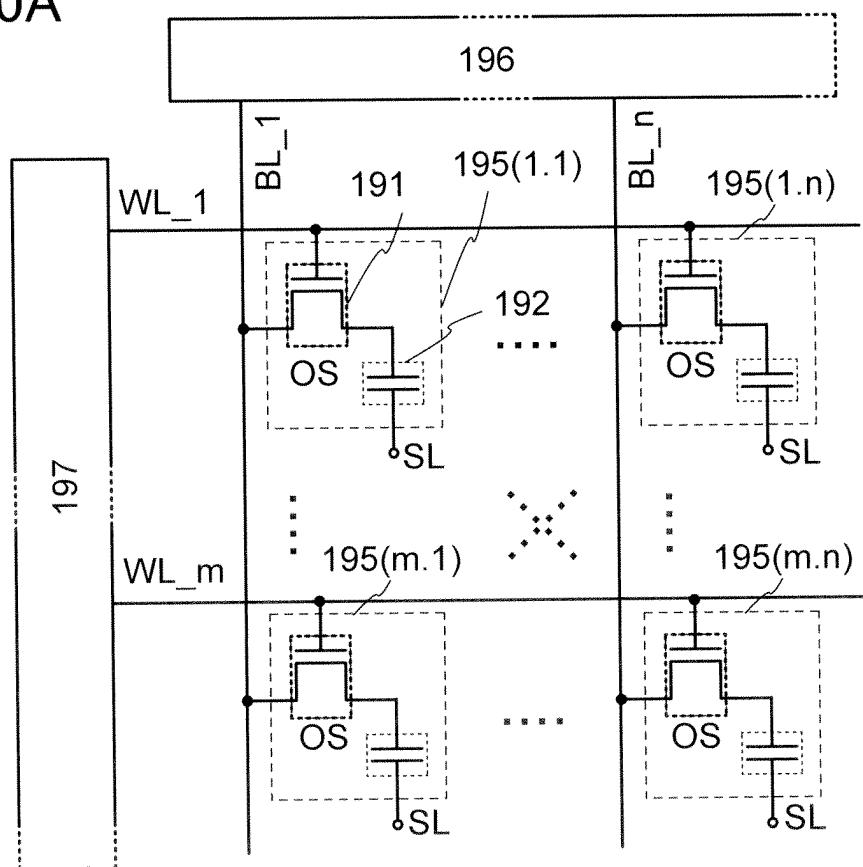

**Fig. 6A** bis **Fig. 6E** zeigen ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung.

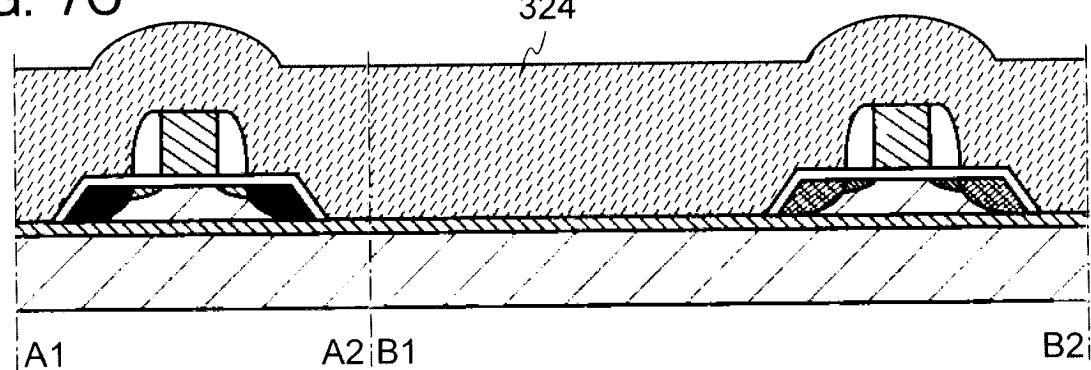

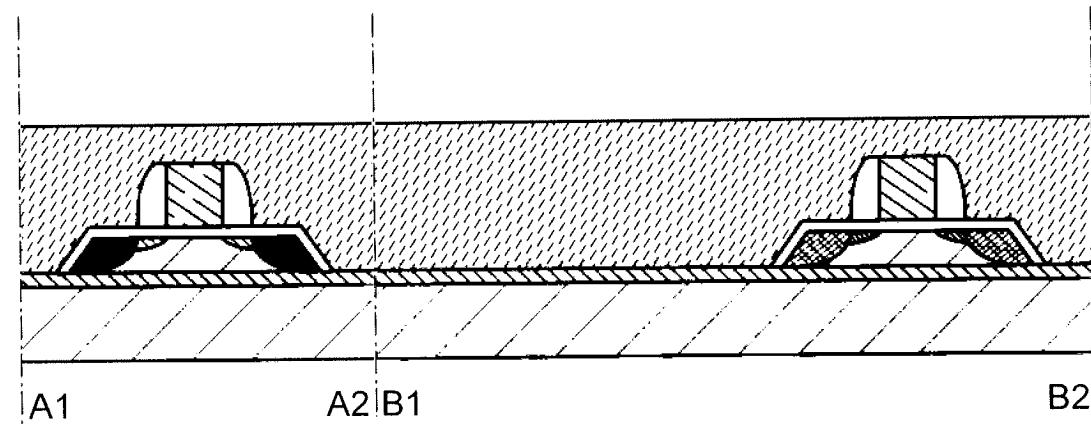

**Fig. 7A** bis **Fig. 7D** zeigen ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung.

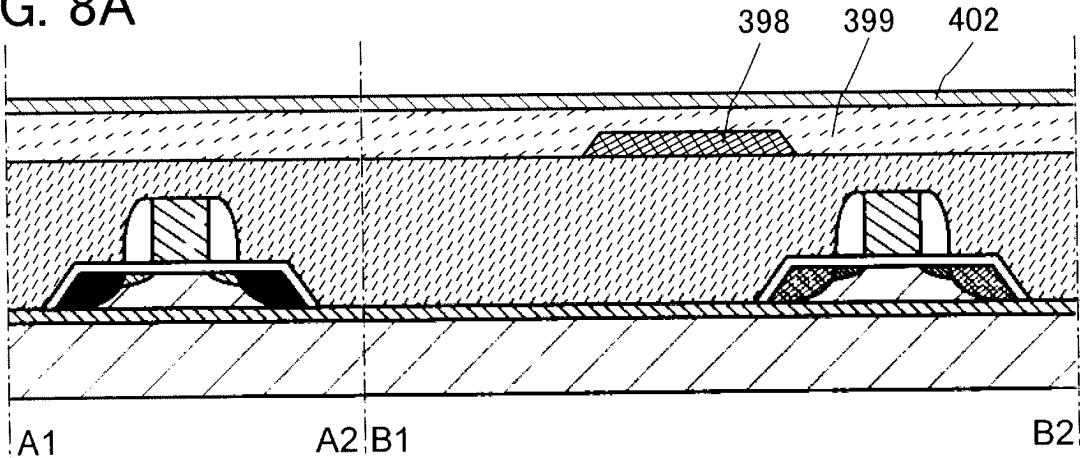

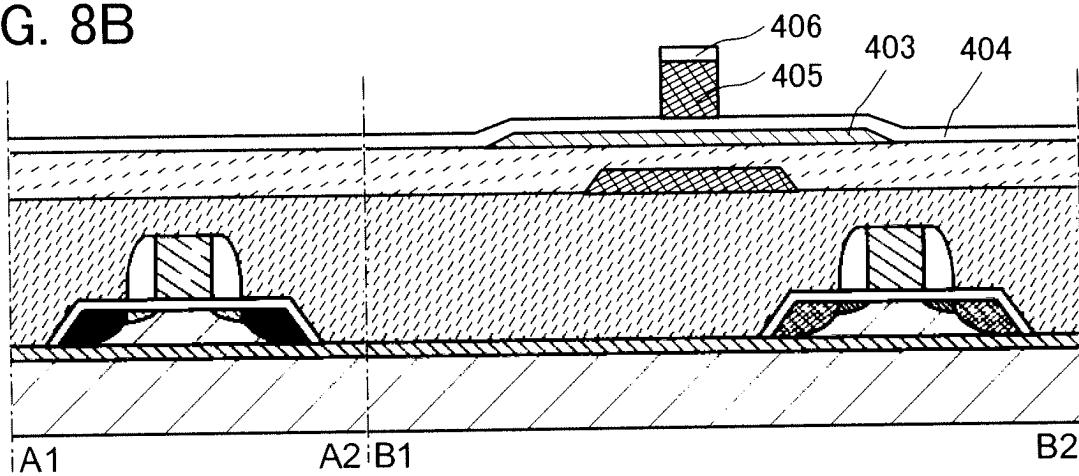

**Fig. 8A** bis **Fig. 8C** zeigen ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung.

**Fig. 9A** und **Fig. 9B** zeigen ein Beispiel für einen Herstellungsprozess einer Halbleitervorrichtung.

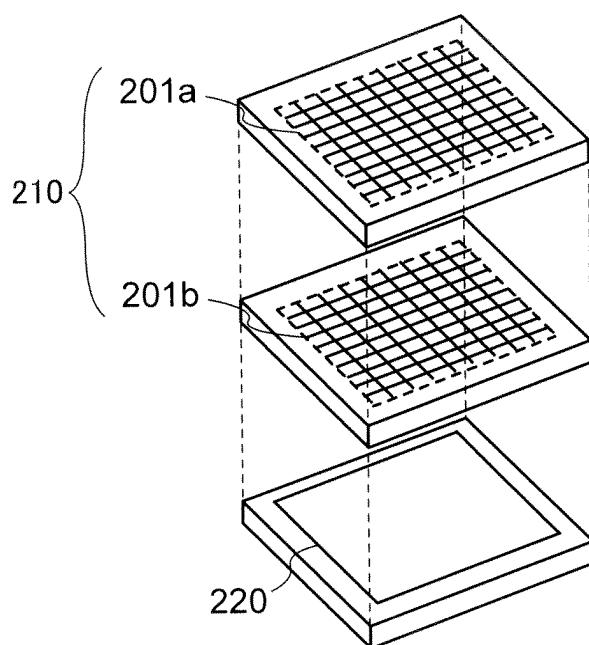

**Fig. 10A** und **Fig. 10B** sind ein Schema einer Schaltung bzw. eine perspektivische Ansicht, die eine Ausführungsform einer Halbleitervorrichtung zeigen.

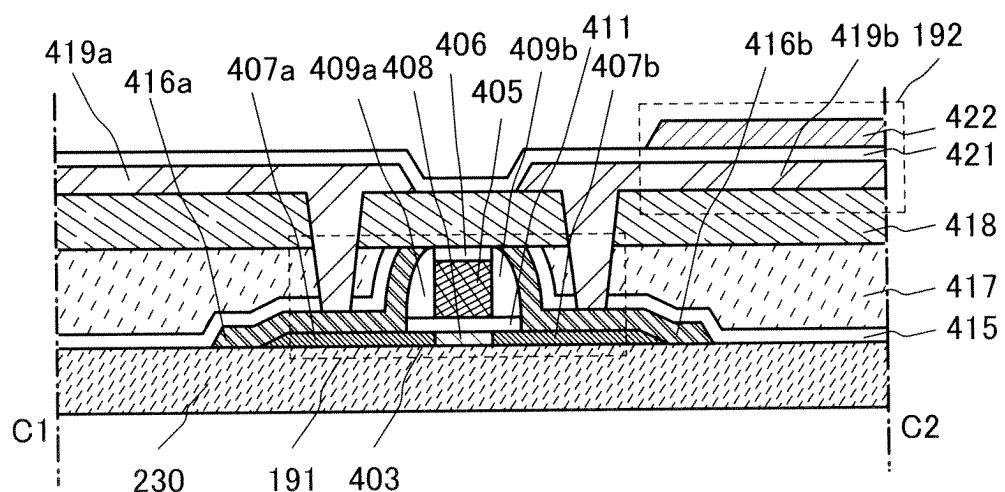

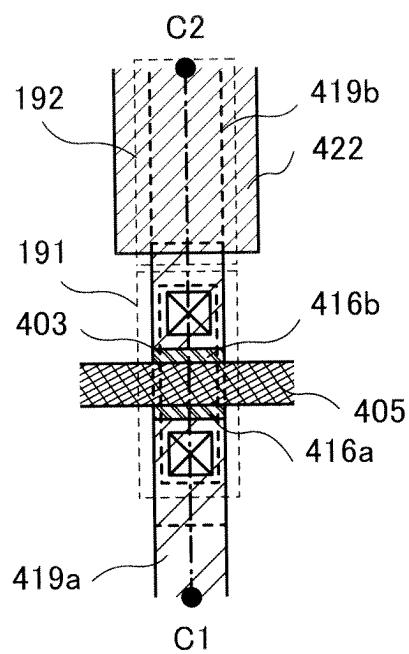

**Fig. 11A** und **Fig. 11B** sind eine Querschnittsansicht bzw. eine Draufsicht, die eine Ausführungsform einer Halbleitervorrichtung zeigen.

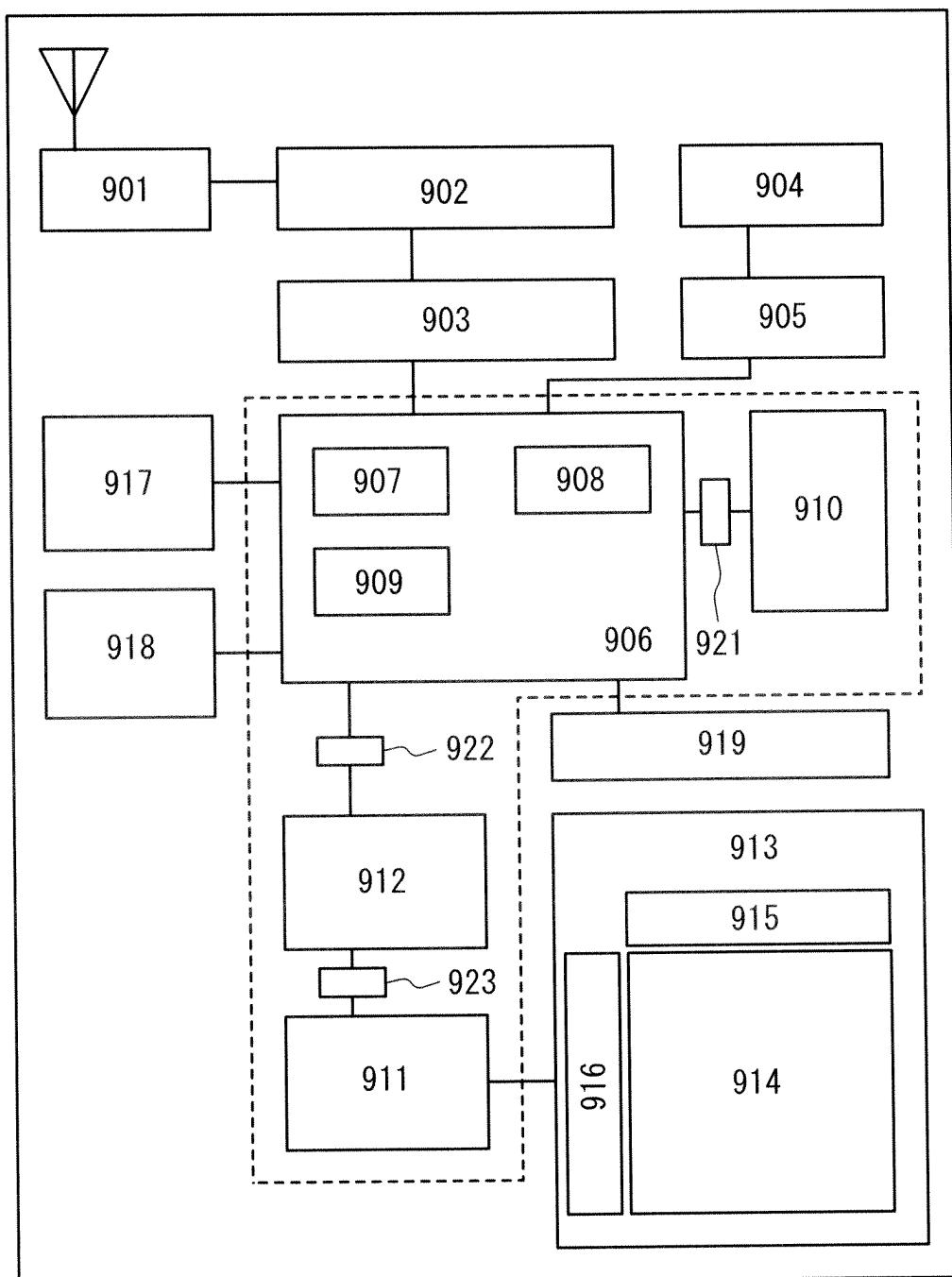

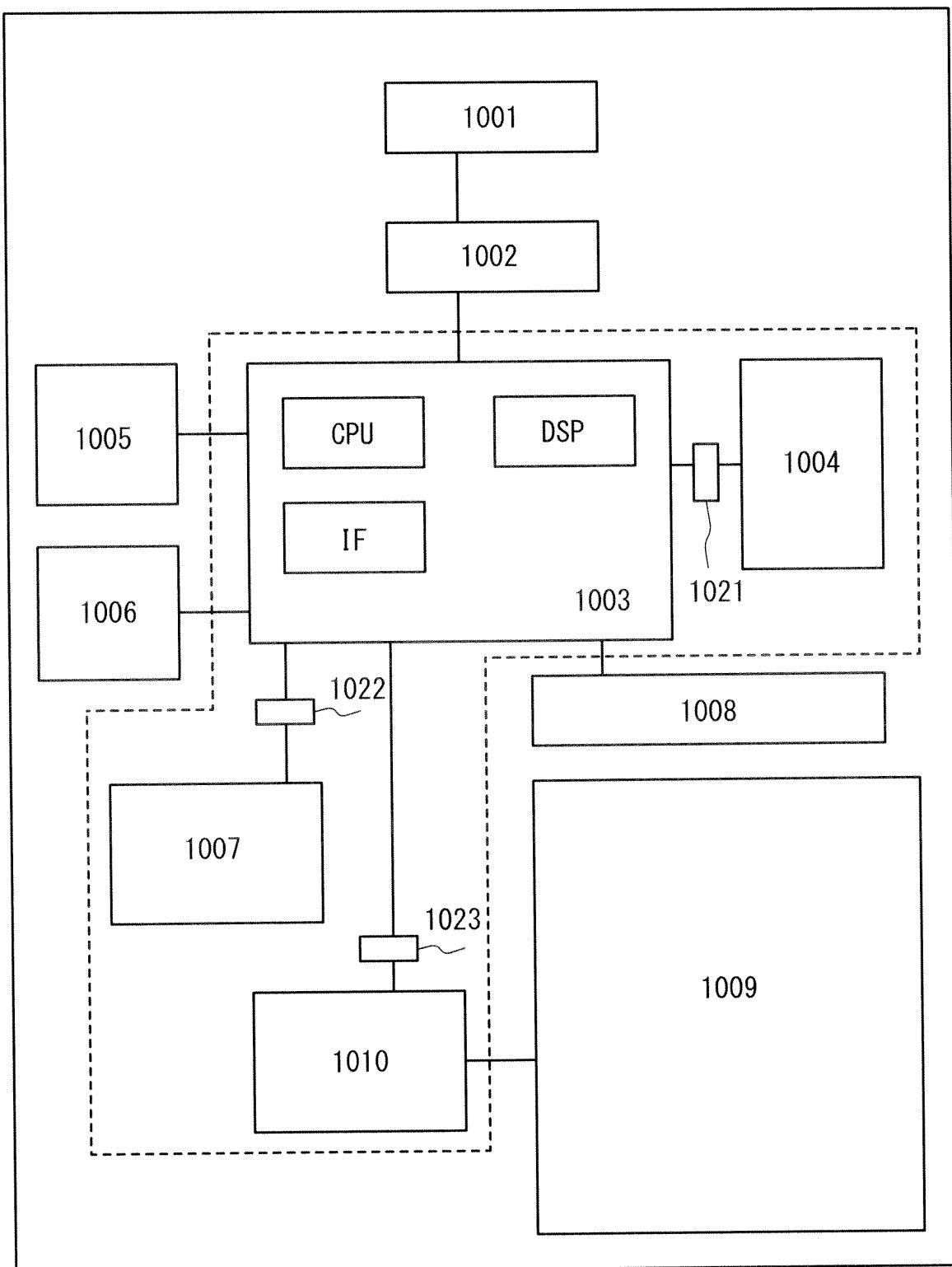

**Fig. 12** ist ein Blockdiagramm, das eine Ausführungsform einer Halbleitervorrichtung zeigt.

**Fig. 13** ist ein Blockdiagramm, das eine Ausführungsform einer Halbleitervorrichtung zeigt.

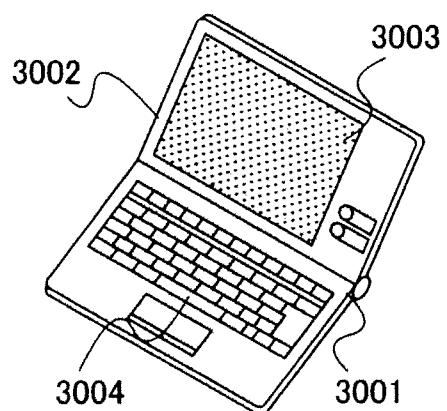

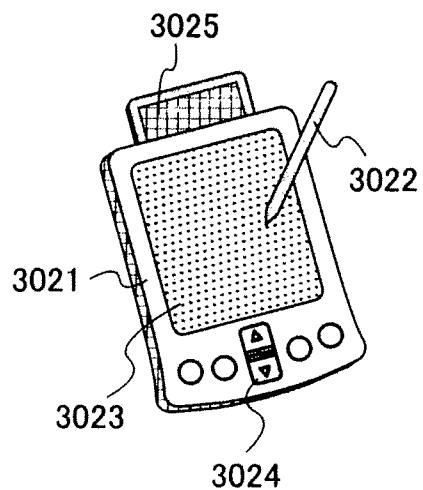

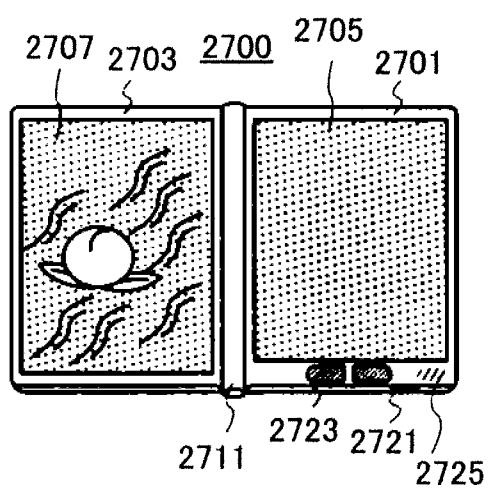

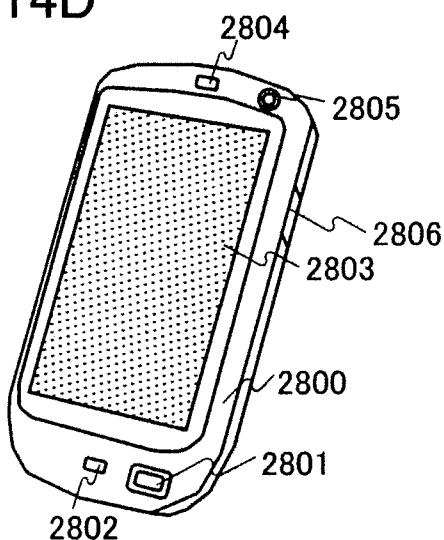

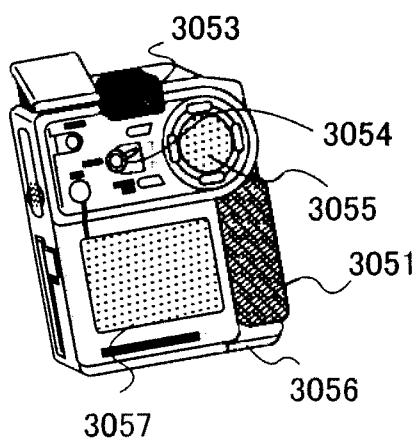

**Fig. 14A** bis **Fig. 14F** zeigen elektronische Geräte.

#### Detaillierte Beschreibung der Erfindung

**[0028]** Anhand der Zeichnungen werden Beispiele für die Ausführungsform der vorliegenden Erfindung ausführlich beschrieben. Bei den nachstehenden Strukturen werden gleiche Teile oder Teile mit ähnlichen Funktionen in unterschiedlichen Zeichnungen durch die gleichen Bezugszeichen benannt, und die Beschreibung derartiger Teile wird nicht notwendigerweise wiederholt.

**[0029]** Zu beachten ist, dass die Position, die Größe, der Bereich oder dergleichen jeder der in den Zeichnungen und dergleichen dargestellten Komponente in einigen Fällen zum leichten Verständnis nicht genau dargestellt ist. Somit sind die Ausführungsfor-

men der offenbarten Erfindung nicht notwendigerweise auf die Position, die Größe, den Bereich oder dergleichen, die in den Zeichnungen und dergleichen offenbart ist, beschränkt.

**[0030]** Zu beachten ist, dass in dieser Beschreibung und dergleichen Ordnungszahlen wie z. B. „erstes“, „zweites“ und „drittes“ verwendet werden, um eine Verwechslung zwischen Komponenten zu vermeiden, aber die Zahl nicht einschränken.

**[0031]** Zu beachten ist, dass in dieser Beschreibung und dergleichen „Spannung“ und „Potenzial“ in einigen Fällen die gleiche Bedeutung haben.

**[0032]** Die Funktionen einer „Source“ und eines „Drains“ können sich vertauschen, z. B. wenn ein Transistor mit entgegengesetzter Polarität verwendet wird oder wenn die Richtung des Stromflusses im Schaltungsbetrieb geändert wird. Somit können die Ausdrücke, „Source“ und „Drain“, in dieser Beschreibung vertauscht werden.

**[0033]** Zu beachten ist, dass der Ausdruck, „elektrisch verbunden“, in dieser Beschreibung und der gleichen den Fall enthält, in dem Komponenten über ein Objekt mit irgendeiner elektrischen Funktion miteinander verbunden sind. Solange zwischen den Komponenten, die über das Objekt mit irgendeiner elektrischen Funktion miteinander verbunden sind, elektrische Signale gesendet und empfangen werden können, gibt es hier keine bestimmte Beschränkung auf das Objekt.

### (Ausführungsform 1)

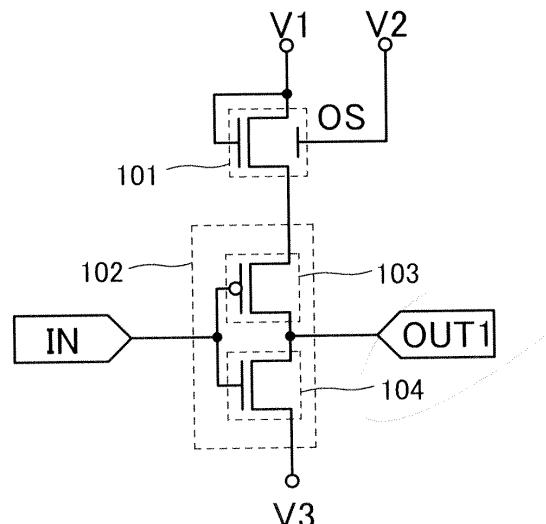

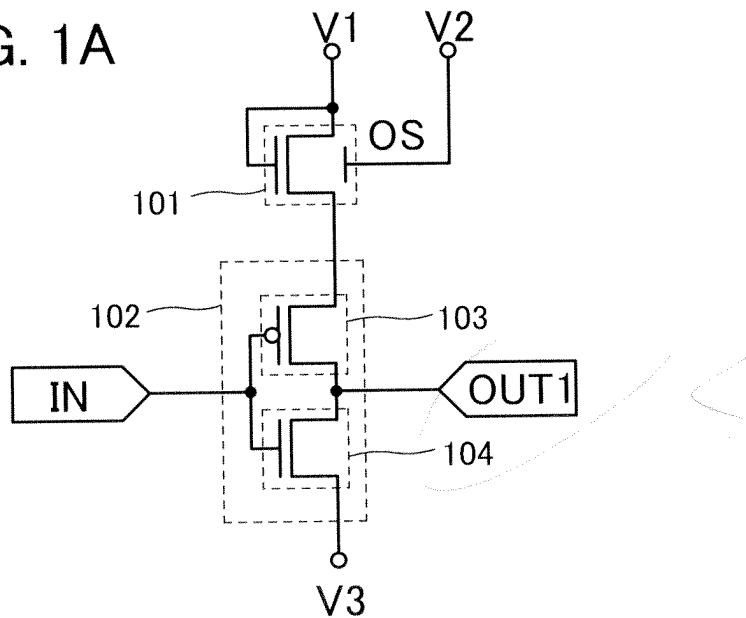

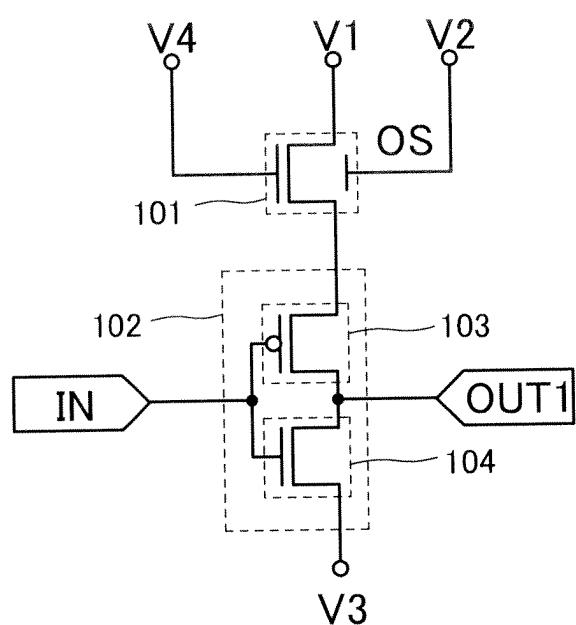

**[0034]** Bei dieser Ausführungsform wird anhand der **Fig. 1A bis Fig. 1C, Fig. 2, Fig. 3, Fig. 4** und **Fig. 5** eine Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung beschrieben. Zu beachten ist, dass in Schemas einer Schaltung neben einigen Transistoren „OS“ geschrieben ist, um anzugeben, dass diese Transistoren einen Oxidhalbleiter aufweisen.

## <Pegelverschieberschaltungsstruktur 1 >

**[0035] Fig. 1A** zeigt ein Beispiel für eine Struktur einer Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung. Die Pegelverschieberschaltung in **Fig. 1A** weist einen ersten Eingangsanschluss, an den ein erstes Leistungsversorgungspotenzial V1 angelegt wird, einen zweiten Eingangsanschluss, an den ein zweites Leistungsversorgungspotenzial V2 angelegt wird, einen dritten Eingangsanschluss, an den ein drittes Leistungsversorgungspotenzial V3 angelegt wird, einen vierten Eingangsanschluss, an den ein Eingangssignal IN angelegt wird, einen ersten Ausgangsanschluss, aus dem ein erstes Ausgangssignal OUT1 ausgege-

ben wird, einen n-Kanal Transistor 101 und eine Wechselrichterschaltung 102 auf. Die Wechselrichterschaltung 102 weist einen p-Kanal Transistor 103 und einen n-Kanal Transistor 104 auf.

**[0036]** Bei dem n-Kanal Transistor 101 ist ein Kanalbereich in einem Oxidhalbleiterfilm ausgebildet, und ein Paar von Gate-Elektroden, die dazwischen den Oxidhalbleiterfilm aufweisen, sind vorgesehen. Es ist zu bevorzugen, dass sich eine von dem Paar von Gate-Elektroden mit dem Oxidhalbleiterfilm mit einem dazwischen liegenden ersten Gate-Isolierfilm überlappt, und sich die andere von dem Paar von Gate-Elektroden mit dem Oxidhalbleiterfilm mit einem dazwischen liegenden zweiten Gate-Isolierfilm überlappt. Hier ist eine von dem Paar von Gate-Elektroden eine erste Gate-Elektrode des Transistors 101. Ferner ist die andere von dem Paar von Gate-Elektroden eine zweite Gate-Elektrode (auch als ein Rückgate bezeichnet) des Transistors 101. Die Schwellenspannung des Transistors 101 wird von dem Potenzialniveau der zweiten Gate-Elektrode, insbesondere von der Differenz zwischen Potenzialen einer Source-Elektrode des ersten Transistors 101 und der zweiten Gate-Elektrode, gesteuert. Die Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , kann von dem zweiten Leistungsversorgungspotenzial V2, das an die zweite Gate-Elektrode des Transistors 101 angelegt wird, gesteuert werden.

**[0037]** Bei jedem des p-Kanal Transistors 103 und des n-Kanal Transistors 104 ist ein Kanalbereich in einem Halbleiterfilm aus Silizium oder dergleichen ausgebildet. Als der Halbleiterfilm kann ein einkristalliner Halbleiterfilm oder ein polykristalliner Halbleiterfilm aus Silizium, Siliziumkarbid oder dergleichen, oder ein Verbindungshalbleiterfilm aus Silizium-Germanium, Galliumarsenid, Indiumphosphid oder dergleichen verwendet werden.

**[0038]** Eine Gate-Elektrode des Transistors 103 und eine Gate-Elektrode des Transistors 104 sind mit dem vierten Eingangsanschluss verbunden, und eine Drain-Elektrode des Transistors 103 und eine Source-Elektrode des Transistors 104 sind mit dem ersten Ausgangsanschluss verbunden. Außerdem ist eine Drain-Elektrode des Transistors 104 mit dem dritten Eingangsanschluss verbunden.

**[0039]** Die Source-Elektrode und die erste Gate-Elektrode des Transistors 101 sind mit dem ersten Eingangsanschluss verbunden, die zweite Gate-Elektrode des Transistors 101 ist mit dem zweiten Eingangsanschluss verbunden, und die Drain-Elektrode des Transistors 101 ist mit einer Source-Elektrode des Transistors 103 verbunden.

**[0040]** Der Transistor 101 kann unter Verwendung eines Oxidhalbleiterfilms ausgebildet werden und

daher über dem Transistor 103 und dem Transistor 104 gestapelt werden. Auf diese Weise können bei der Pegelverschieberschaltung Transistoren teilweise übereinander gestapelt werden, was zur Verkleinerung der Fläche der Pegelverschieberschaltung führt. Zu beachten ist, dass bei dieser Ausführungsform der Transistor, bei dem ein Oxidhalbleiterfilm verwendet wird, über dem Transistor, bei dem ein Halbleiterfilm aus Silizium oder dergleichen verwendet wird, gestapelt werden kann.

**[0041]** Als Nächstes wird eine Bedienung der Pegelverschieberschaltung in **Fig. 1A** beschrieben. In der unten angegeben Beschreibung ist das erste Leistungsversorgungspotenzial V1 VDD, das zweite Leistungsversorgungspotenzial V2 ist VSS, das dritte Leistungsversorgungspotenzial V3 ist GND (ein Erdpotenzial), das Eingangssignal IN auf einem niedrigen Pegel ist GND, das Eingangssignal IN auf einem hohen Pegel ist VDD, und die Menge an Veränderung der Schwellenspannung des Transistors 101 ist  $\Delta V_{th101}$ .

**[0042]** Bei der Pegelverschieberschaltung in **Fig. 1A** wird dann, wenn das Potenzial des Eingangssignals IN von einem niedrigen Pegel auf einen hohen Pegel geändert wird, das Ausgangssignal OUT1 auf einem niedrigen Pegel (das dritte Leistungsversorgungspotenzial V3) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben.

**[0043]** Außerdem wird dann, wenn das Potenzial des Eingangssignals IN von einem hohen Pegel auf einen niedrigen Pegel geändert wird, das Ausgangssignal OUT1 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben.

**[0044]** Auf diese Weise kann dann, wenn die Schwellenspannung des Transistors 101 von dem Potenzial, das an dessen zweite Gate-Elektrode angelegt wird, verändert wird, das Ausgangssignal OUT1 im Falle des Eingangssignals IN auf einem niedrigen Pegel leicht gesteuert werden.

**[0045]** Eine Pegelverschieberschaltung in **Fig. 1B** wird durch Verbinden der ersten Gate-Elektrode des Transistors 101 der Pegelverschieberschaltung in **Fig. 1A** mit einem fünften Eingangsanschluss, an den ein vierter Leistungsversorgungspotenzial V4 angelegt wird, erhalten. Zu beachten ist, dass beispielsweise das vierte Leistungsversorgungspotenzial V4 VDD sein kann.

**[0046]** Bei der Pegelverschieberschaltung in **Fig. 1A** ist die erste Gate-Elektrode des Transistors

101 mit dem ersten Eingangsanschluss verbunden und daher von dem ersten Leistungsversorgungspotenzial V1 gesteuert. Andererseits kann bei der Pegelverschieberschaltung in **Fig. 1B** die erste Gate-Elektrode des Transistors 101 von dem vierten Leistungsversorgungspotenzial gesteuert werden. Wenn die erste Gate-Elektrode und die zweite Gate-Elektrode des Transistors 101 getrennt gesteuert werden, kann das Ausgangssignal OUT1 im Falle des Eingangssignals IN auf einem niedrigen Pegel leicht gesteuert werden. Außerdem kann bei der Pegelverschieberschaltung in **Fig. 1B** der Transistor 101 durch Anlegen eines Potenzials auf einem hohen Pegel (wie z. B. VDD) oder eines Potenzials auf einem niedrigen Pegel (wie z. B. GND) an die erste Gate-Elektrode gesteuert werden, um eingeschaltet oder ausgeschaltet zu werden. Ferner kann der Aus-Strom des Transistors 101 sehr klein sein, da bei dem Transistor 101 ein Oxidhalbleiter verwendet wird. Deshalb kann dann, wenn der Transistor 101 im Falle des Eingangssignal IN auf einem hohen Pegel ausgeschaltet wird, Energieverbrauch der Pegelverschieberschaltung reduziert werden.

**[0047]** Eine Pegelverschieberschaltung in **Fig. 1C** weist zusätzlich zu den Bestandteilen der Pegelverschieberschaltung in **Fig. 1A** einen siebten Eingangsanschluss, an den ein sechstes Leistungsversorgungspotenzial V6 angelegt wird, und einen n-Kanal Transistor 109 auf.

**[0048]** Bei dem n-Kanal Transistor 109 ist ein Kanalbereich wie bei dem n-Kanal Transistor 101 in einem Oxidhalbleiterfilm ausgebildet, und ein Paar von Gate-Elektroden, die dazwischen den Oxidhalbleiterfilm aufweisen, sind vorgesehen. Hier ist eine von dem Paar von Gate-Elektroden eine erste Gate-Elektrode des Transistors 109. Ferner ist die andere von dem Paar von Gate-Elektroden eine zweite Gate-Elektrode (auch als ein Rückgate bezeichnet) des Transistors 109. Die Schwellenspannung des Transistors 109 wird von dem Potenzialniveau der zweiten Gate-Elektrode, insbesondere von der Differenz zwischen Potenzialen einer Source-Elektrode des Transistors 109 und der zweiten Gate-Elektrode gesteuert.

**[0049]** Die Source-Elektrode des Transistors 109 ist mit der Drain-Elektrode des Transistors 104 verbunden, die zweite Gate-Elektrode des Transistors 109 ist mit dem siebten Eingangsanschluss verbunden, und eine Drain-Elektrode des Transistors 109 ist mit dem dritten Eingangsanschluss verbunden.

**[0050]** Als Nächstes wird eine Bedienung der Pegelverschieberschaltung in **Fig. 1C** beschrieben. In der unten angegeben Beschreibung ist das erste Leistungsversorgungspotenzial V1 VDD, das zweite Leistungsversorgungspotenzial V2 ist VSS, das dritte Leistungsversorgungspotenzial V3 ist GND

(ein Erdpotenzial), das sechste Leistungsversorgungspotenzial V6 ist VDD, das Eingangssignal IN auf einem niedrigen Pegel ist GND, das Eingangssignal IN auf einem hohen Pegel ist VDD, die Menge an Veränderung der Schwellenspannung des Transistors 101 ist  $\Delta V_{th101}$ , und die Menge an Veränderung der Schwellenspannung des Transistors 109 ist  $\Delta V_{th109}$ .

**[0051]** Bei der Pegelverschieberschaltung in **Fig. 1C** wird dann, wenn das Potenzial des Eingangssignals IN von einem niedrigen Pegel auf einen hohen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem niedrigen Pegel (ein Potenzial, das durch Addieren der Menge an Veränderung der Schwellenspannung des Transistors 109,  $\Delta V_{th109}$ , zu dem dritten Leistungsversorgungspotenzial V3 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben.

**[0052]** Außerdem wird dann, wenn das Potenzial des Eingangssignals IN von einem hohen Pegel auf einen niedrigen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben.

**[0053]** Auf diese Weise wird bei der Pegelverschieberschaltung in **Fig. 1C** die Schwellenspannung des Transistors 101 von dem Potenzial, das an dessen zweite Gate-Elektrode angelegt wird, geändert, und die Schwellenspannung des Transistors 109 wird von dem Potenzial, das an dessen zweite Gate-Elektrode angelegt wird, geändert, wodurch ein Ausgangssignal mit kleinerer Amplitude als die der Ausgangssignale OUT1 der Pegelverschieberschaltungen in **Fig. 1A** und **Fig. 1B** (mit einem höheren Potenzial im Falle des Eingangssignals IN auf einem hohen Pegel) ausgegeben werden kann.

<Pegelverschieberschaltungsstruktur 2>

**[0054]** **Fig. 2** zeigt ein anderes Beispiel für eine Struktur einer Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung. Die Pegelverschieberschaltung in **Fig. 2** weist zusätzlich zu den Bestandteilen der Pegelverschieberschaltung in **Fig. 1A** einen sechsten Eingangsanschluss, an den ein fünftes Leistungsversorgungspotenzial V5 angelegt wird, einen zweiten Ausgangsanschluss, aus dem ein zweites Ausgangssignal OUT2 ausgegeben wird, einen n-Kanal Transistor 105 und eine Wechselrichterschaltung 106 auf. Die Wechselrichterschaltung 106 weist einen p-Kanal Transistor 107 und einen n-Kanal Transistor 108 auf.

**[0055]** Bei dem n-Kanal Transistor 105 ist ein Kanalbereich wie bei dem n-Kanal Transistor 101 in einem Oxidhalbleiterfilm ausgebildet, und ein Paar von Gate-Elektroden, die dazwischen den Oxidhalbleiterfilm aufweisen, sind vorgesehen. Hier ist eine von dem Paar von Gate-Elektroden eine erste Gate-Elektrode des Transistors 105. Ferner ist die andere von dem Paar von Gate-Elektroden eine zweite Gate-Elektrode (auch als ein Rückgate bezeichnet) des Transistors 105. Die Schwellenspannung des Transistors 105 wird von dem Potenzialniveau der zweiten Gate-Elektrode, insbesondere von der Differenz zwischen Potenzialen einer Source-Elektrode des Transistors 105 und der zweiten Gate-Elektrode, gesteuert. Die Menge an Veränderung der Schwellenspannung des Transistors 105,  $\Delta V_{th105}$ , kann von dem fünften Leistungsversorgungspotenzial V5, das an die zweite Gate-Elektrode des Transistors 105 angelegt wird, gesteuert werden.

**[0056]** Bei jedem des p-Kanal Transistors 107 und des n-Kanal Transistors 108 ist ein Kanalbereich in einem Halbleiterfilm aus Silizium oder dergleichen ausgebildet. Eine Gate-Elektrode des Transistors 107 und eine Gate-Elektrode des Transistors 108 sind mit dem ersten Eingangsanschluss verbunden, und eine Drain-Elektrode des Transistors 107 und eine Source-Elektrode des Transistors 108 sind mit dem zweiten Ausgangsanschluss verbunden. Außerdem ist eine Drain-Elektrode des Transistors 108 mit dem dritten Eingangsanschluss verbunden.

**[0057]** Die Source-Elektrode des Transistors 105 ist mit einem Knoten N1 verbunden, wo die Drain-Elektrode des Transistors 101 und die Source-Elektrode des Transistors 103 miteinander verbunden sind, die zweite Gate-Elektrode des Transistors 105 ist mit dem sechsten Eingangsanschluss verbunden, und die Drain-Elektrode des Transistors 105 ist mit einer Source-Elektrode des Transistors 107 verbunden.

**[0058]** Als Nächstes wird eine Bedienung der Pegelverschieberschaltung in **Fig. 2** beschrieben. In der unten angegebenen Beschreibung ist das erste Leistungsversorgungspotenzial V1 VDD, das zweite Leistungsversorgungspotenzial V2 ist VSS, das dritte Leistungsversorgungspotenzial V3 ist GND (ein Erdpotenzial), das fünfte Leistungsversorgungspotenzial V5 ist VDD, das Eingangssignal IN auf einem niedrigen Pegel ist GND, das Eingangssignal IN auf einem hohen Pegel ist VDD, die Menge an Veränderung der Schwellenspannung des Transistors 101 ist  $\Delta V_{th101}$ , und die Menge an Veränderung der Schwellenspannung des Transistors 105 ist  $\Delta V_{th105}$ .

**[0059]** Bei der Pegelverschieberschaltung in **Fig. 2** wird dann, wenn das Potenzial des Eingangssignals IN von einem niedrigen Pegel auf einen hohen Pegel geändert wird, das Signal auf einem niedrigen Pegel

(das dritte Leistungsversorgungspotenzial V3) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben, und das Signal auf einem niedrigen Pegel (das dritte Leistungsversorgungspotenzial V3) wird aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0060]** Außerdem wird dann, wenn das Potenzial des Eingangssignals IN von einem hohen Pegel auf einen niedrigen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben. Ferner wird das zweite Ausgangssignal OUT2 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 105,  $\Delta V_{th105}$ , von dem Potenzial erhalten wird, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0061]** Auf diese Weise wird die Schwellenspannung des Transistors 101 von dem zweiten Leistungsversorgungspotenzial V2, das an dessen zweite Gate-Elektrode angelegt wird, verändert, und die Schwellenspannung des Transistors 105 wird von dem fünften Leistungsversorgungspotenzial V5 verändert, wodurch aus dem zweiten Ausgangsanschluss ein Signal mit anderer Amplitude als der eines Signals aus dem ersten Ausgangsanschluss ausgegeben werden kann. Zu beachten ist, dass das Potenzial, das aus dem zweiten Ausgangsanschluss ausgegeben wird, niedriger als das Potenzial ist, das aus dem ersten Ausgangsanschluss ausgegeben wird.

**[0062]** Die Potenziale der ersten Gate-Elektrode und der zweiten Gate-Elektrode des Transistors 101 werden gesteuert, wodurch das erste Ausgangssignal OUT1 der Wechselrichterschaltung 102 im Falle des Eingangssignals auf einem niedrigen Pegel leicht gesteuert werden kann. Ferner kann durch Steuern der Potenziale der ersten Gate-Elektrode und der zweiten Gate-Elektrode des Transistors 105 unter Verwendung des Potenzials des Knotens N1, das durch Steuern der Potenziale der ersten Gate-Elektrode und der zweiten Gate-Elektrode des Transistors 101 erzeugt wird, das zweite Ausgangssignal OUT2 der Wechselrichterschaltung 106 im Falle des Eingangssignal IN auf einem niedrigen Pegel leicht gesteuert werden. Unter Verwendung der Pegelverschieberschaltungsstruktur 2 kann ein Potenzial, das bei der Pegelverschieberschaltungs-

struktur 1 nicht behandelt werden kann, als das zweite Ausgangssignal OUT2 der Wechselrichterschaltung 106 ausgegeben werden.

**[0063]** Bei der Pegelverschieberschaltung in **Fig. 2** werden unterschiedliche Signale aus den zwei Ausgangsanschlüssen ausgegeben, aber die Ausführungsformen der vorliegenden Erfindung sind nicht auf diese Struktur beschränkt; unterschiedliche Signale können aus drei oder mehr Ausgangsanschlüssen ausgegeben werden. Beispielsweise kann dann, wenn unterschiedliche Signale aus drei Ausgangsanschlüssen ausgegeben werden, eine Source-Elektrode eines Transistors, bei dem ein Kanalbereich in einem Oxidhalbleiterfilm ausgebildet ist, mit einem Knoten N2 in **Fig. 2** verbunden werden, und eine Drain-Elektrode des Transistors kann mit einer Wechselrichterschaltung verbunden werden. Durch Steuern eines Leistungsversorgungspotenzials, das an eine zweite Gate-Elektrode des Transistors angelegt wird, kann ein Ausgangssignal mit kleinerer Amplitude als die des zweiten Ausgangssignals (mit einem niedrigen Potenzial im Falle des Eingangssignals IN auf einem niedrigen Pegel) als ein drittes Ausgangssignal aus der Wechselrichterschaltung ausgegeben werden.

<Pegelverschieberschaltungsstruktur 3>

**[0064]** **Fig. 3** zeigt ein anderes Beispiel für eine Struktur einer Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung. Die Verbindung bei einer Pegelverschieberschaltung in **Fig. 3** ist anders als die Verbindung bei der Pegelverschieberschaltung in **Fig. 2**.

**[0065]** Während bei der Pegelverschieberschaltung in **Fig. 2** die Source-Elektrode des Transistors 105 mit dem Knoten N1 verbunden ist, ist bei der Pegelverschieberschaltung in **Fig. 3** die Source-Elektrode des Transistors 105 mit dem ersten Eingangsanschluss verbunden.

**[0066]** Als Nächstes wird eine Bedienung der Pegelverschieberschaltung in **Fig. 3** beschrieben. In der unten angegebenen Beschreibung ist das erste Leistungsversorgungspotenzial V1 VDD, das zweite Leistungsversorgungspotenzial V2 ist VSS, das dritte Leistungsversorgungspotenzial V3 ist GND (ein Erdpotenzial), das fünfte Leistungsversorgungspotenzial V5 ist VDD, das Eingangssignal IN auf einem niedrigen Pegel ist GND, das Eingangssignal IN auf einem hohen Pegel ist VDD, die Menge an Veränderung der Schwellenspannung des Transistors 101 ist  $\Delta V_{th101}$ , und die Menge an Veränderung der Schwellenspannung des Transistors 105 ist  $\Delta V_{th105}$ .

**[0067]** Bei der Pegelverschieberschaltung in **Fig. 3** wird dann, wenn das Potenzial des Eingangssignals

IN von einem niedrigen Pegel auf einen hohen Pegel geändert wird, das Signal auf einem niedrigen Pegel (das dritte Leistungsversorgungspotenzial V3 wie z. B. GND) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben, und das Signal auf einem niedrigen Pegel (das dritte Leistungsversorgungspotenzial V3 wie z. B. GND) wird aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0068]** Außerdem wird dann, wenn das Potenzial des Eingangssignals IN von einem hohen Pegel auf einen niedrigen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 wie z. B. VDD erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben. Ferner wird das zweite Ausgangssignal OUT2 auf einem niedrigen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 105,  $\Delta V_{th105}$ , von dem ersten Leistungsversorgungspotenzial V1 wie z. B. VDD erhalten wird) aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0069]** Der erste Ausgangsanschluss der Wechselrichterschaltung 102 und der zweite Ausgangsanschluss der Wechselrichterschaltung 106, in die das gleiche Eingangssignal IN eingegeben wird, können getrennt gesteuert werden, und somit können Signale mit unterschiedlichen Potenzialen auch durch die gleiche logische Bedienung ausgegeben werden. Die Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , kann von dem zweiten Leistungsversorgungspotenzial V2 gesteuert werden. Die Menge an Veränderung der Schwellenspannung des Transistors 105,  $\Delta V_{th105}$ , kann von dem fünften Leistungsversorgungspotenzial V5 gesteuert werden. Infolgedessen kann das zweite Ausgangssignal OUT2 ein Ausgangssignal mit größerer Amplitude als die des ersten Ausgangssignals OUT1 (mit einem höheren Potenzial im Falle des Eingangssignals IN auf einem niedrigen Pegel) sein oder ein Ausgangssignal mit kleinerer Amplitude als die des ersten Ausgangssignals OUT1 (mit einem niedrigen Potenzial im Falle des Eingangssignals IN auf einem niedrigen Pegel) sein.

**[0070]** Bei der Pegelverschieberschaltung in **Fig. 3** werden unterschiedliche Signale aus den zwei Ausgangsanschlüssen ausgegeben, aber die Ausführungsformen der vorliegenden Erfindung sind nicht auf diese Struktur beschränkt; unterschiedliche Signale können aus drei oder mehr Ausgangsanschlüssen ausgegeben werden. Beispielsweise kann dann, wenn unterschiedliche Signale aus drei Ausgangsanschlüssen ausgegeben werden, eine Wechselrich-

terschaltung mit dem vierten Eingangsanschluss in **Fig. 3** verbunden werden, und eine Drain-Elektrode eines Transistors, bei dem ein Kanalbereich in einem Oxidhalbleiterfilm ausgebildet ist, kann mit einer Source-Elektrode eines p-Kanal Transistors in der Wechselrichterschaltung verbunden werden. Durch Steuern des Leistungsversorgungspotenzials, das an eine zweite Gate-Elektrode des Transistors angelegt wird, kann ein Ausgangssignal, das anders als das erste Ausgangssignal und das zweite Ausgangssignal ist, aus einem dritten Ausgangsanschluss der Wechselrichterschaltung ausgegeben werden. Selbstverständlich können Ausgangssignale mit gleicher Amplitude (mit dem gleichen Potenzial im Falle des Eingangssignals IN auf einem niedrigen Pegel) aus den drei Ausgangsanschlüssen ausgegeben werden.

<Pegelverschieberschaltungsstruktur 4>

**[0071]** **Fig. 4** zeigt ein anderes Beispiel für eine Struktur einer Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung. Die Pegelverschieberschaltung in **Fig. 4** weist zusätzlich zu den Bestandteilen der Pegelverschieberschaltung in **Fig. 1A** einen zweiten Ausgangsanschluss, aus dem ein zweites Ausgangssignal OUT2 ausgegeben wird, und eine Wechselrichterschaltung 106 auf. Die Wechselrichterschaltung 106 weist einen p-Kanal Transistor 107 und einen n-Kanal Transistor 108 auf.

**[0072]** Bei jedem des p-Kanal Transistors 107 und des n-Kanal Transistors 108 ist ein Kanalbereich in einem Halbleiterfilm aus Silizium oder dergleichen ausgebildet. Eine Gate-Elektrode des Transistors 107 und eine Gate-Elektrode des Transistors 108 sind mit dem ersten Eingangsanschluss verbunden, und eine Drain-Elektrode des Transistors 107 und eine Source-Elektrode des Transistors 108 sind mit dem zweiten Ausgangsanschluss verbunden.

**[0073]** Als Nächstes wird eine Bedienung der Pegelverschieberschaltung in **Fig. 4** beschrieben. In der unten angegebenen Beschreibung ist das erste Leistungsversorgungspotenzial V1 VDD, das zweite Leistungsversorgungspotenzial V2 ist VSS, das dritte Leistungsversorgungspotenzial V3 ist GND (ein Erdpotenzial), das Eingangssignal IN auf einem niedrigen Pegel ist GND, das Eingangssignal IN auf einem hohen Pegel ist VDD, und die Menge an Veränderung der Schwellenspannung des Transistors 101 ist  $\Delta V_{th101}$ .

**[0074]** Bei der Pegelverschieberschaltung in **Fig. 4** wird dann, wenn das Potenzial des Eingangssignals IN von einem niedrigen Pegel auf einen hohen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem niedrigen Pegel (das dritte Leistungsversorgungspotenzial V3) aus dem ersten Ausgangsan-

schluss der Wechselrichterschaltung 102 ausgegeben. Weil dadurch das dritte Leistungsversorgungspotenzial V3 an die Gate-Elektrode des Transistors 107 und die Gate-Elektrode des Transistors 108 angelegt wird, wird das zweite Ausgangssignal OUT2 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0075]** Außerdem wird dann, wenn das Potenzial des Eingangssignals IN von einem hohen Pegel auf einen niedrigen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben. Weil dadurch das Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird, an die Gate-Elektrode des Transistors 107 und die Gate-Elektrode des Transistors 108 angelegt wird, wird das zweite Ausgangssignal OUT2 auf einem niedrigen Pegel (das dritte Leistungsversorgungspotenzial V3) aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0076]** Durch Steuern des Potenzials, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 (wie z. B. VDD) erhalten wird, kann das Potenzial im Falle des zweiten Ausgangssignals OUT2 der Wechselrichterschaltung 106 auf einem hohen Pegel leicht gesteuert werden.

#### <Pegelverschieberschaltungsstruktur 5>

**[0077]** Fig. 5 zeigt ein anderes Beispiel für eine Struktur einer Pegelverschieberschaltung nach einer Ausführungsform der vorliegenden Erfindung. Die Pegelverschieberschaltung in Fig. 5 weist zusätzlich zu den Bestandteilen der Pegelverschieberschaltung in Fig. 4 einen siebten Eingangsanschluss, an den ein sechste Leistungsversorgungspotenzial V6 angelegt wird, und einen n-Kanal Transistor 109 auf.

**[0078]** Bei dem n-Kanal Transistor 109 ist ein Kanalbereich wie bei dem n-Kanal Transistor 101 in einem Oxidhalbleiterfilm ausgebildet, und ein Paar von Gate-Elektroden, die dazwischen den Oxidhalbleiterfilm aufweisen, sind vorgesehen. Hier ist eine von dem Paar von Gate-Elektroden eine erste Gate-Elektrode des Transistors 109. Ferner ist die andere

von dem Paar von Gate-Elektroden eine zweite Gate-Elektrode (auch als ein Rückgate bezeichnet) des Transistors 109. Die Schwellenspannung des Transistors 109 wird von dem Potenzialniveau der zweiten Gate-Elektrode, insbesondere von der Differenz zwischen Potenzialen einer Source-Elektrode des Transistors 109 und der zweiten Gate-Elektrode, gesteuert.

**[0079]** Die Source-Elektrode des Transistors 109 ist mit der Drain-Elektrode des Transistors 104 verbunden, die zweite Gate-Elektrode des Transistors 109 ist mit dem siebten Eingangsanschluss verbunden, und die Drain-Elektrode des Transistors 109 ist mit dem dritten Eingangsanschluss verbunden.

**[0080]** Die Source-Elektrode des Transistors 107 ist mit dem Knoten N1 verbunden, und die Drain-Elektrode des Transistors 108 ist mit einem Knoten N3 verbunden, wo die Drain-Elektrode des Transistors 104 und die Source-Elektrode des Transistors 109 miteinander verbunden sind.

**[0081]** Als Nächstes wird eine Bedienung der Pegelverschieberschaltung in Fig. 5 beschrieben. In der unten angegebenen Beschreibung ist das erste Leistungsversorgungspotenzial V1 VDD, das zweite Leistungsversorgungspotenzial V2 ist VSS, das dritte Leistungsversorgungspotenzial V3 ist GND (ein Erdpotenzial), das sechste Leistungsversorgungspotenzial V6 ist VDD, das Eingangssignal IN auf einem niedrigen Pegel ist GND, das Eingangssignal IN auf einem hohen Pegel ist VDD, die Menge an Veränderung der Schwellenspannung des Transistors 101 ist  $\Delta V_{th101}$ , und die Menge an Veränderung der Schwellenspannung des Transistors 109 ist  $\Delta V_{th109}$ .

**[0082]** Bei der Pegelverschieberschaltung in Fig. 5 wird dann, wenn das Potenzial des Eingangssignals IN von einem niedrigen Pegel auf einen hohen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem niedrigen Pegel (ein Potenzial, das durch Addieren der Menge an Veränderung der Schwellenspannung des Transistors 109,  $\Delta V_{th109}$ , zu dem dritten Leistungsversorgungspotenzial V3 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben. Weil dadurch das Potenzial, das durch Addieren der Menge an Veränderung der Schwellenspannung des Transistors 109,  $\Delta V_{th109}$ , zu dem dritten Leistungsversorgungspotenzial V3 erhalten wird, an die Gate-Elektrode des Transistors 107 und die Gate-Elektrode des Transistors 108 angelegt wird, wird das zweite Ausgangssignal OUT2 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0083]** Außerdem wird dann, wenn das Potenzial des Eingangssignals IN von einem hohen Pegel auf einen niedrigen Pegel geändert wird, das erste Ausgangssignal OUT1 auf einem hohen Pegel (ein Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird) aus dem ersten Ausgangsanschluss der Wechselrichterschaltung 102 ausgegeben. Weil dadurch das Potenzial, das durch Abziehen der Menge an Veränderung der Schwellenspannung des Transistors 101,  $\Delta V_{th101}$ , von dem ersten Leistungsversorgungspotenzial V1 erhalten wird, an die Gate-Elektrode des Transistors 107 und die Gate-Elektrode des Transistors 108 angelegt wird, wird das zweite Ausgangssignal OUT2 auf einem niedrigen Pegel (ein Potenzial, das durch Addieren der Menge an Veränderung der Schwellenspannung des Transistors 109,  $\Delta V_{th109}$ , zu dem dritten Leistungsversorgungspotenzial V3 erhalten wird) aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 ausgegeben.

**[0084]** Die Source-Elektrode des Transistors 107 ist mit dem Knoten N1 verbunden, und die Drain-Elektrode des Transistors 108 ist mit dem Knoten N3 verbunden, wodurch das Potenzial aus dem zweiten Ausgangsanschluss der Wechselrichterschaltung 106 in beiden Fällen des Eingangssignals IN auf einem hohen Pegel und auf einem niedrigen Pegel leicht gesteuert werden kann.

**[0085]** Die bei dieser Ausführungsform beschriebenen Strukturen, Verfahren und dergleichen können, soweit erforderlich, mit jeder/jedem geeigneten der bei den anderen Ausführungsformen beschriebenen Strukturen, Verfahren und dergleichen kombiniert werden.

(Ausführungsform 2)

**[0086]** Bei dieser Ausführungsform wird ein Beispiel für ein Verfahren zum Herstellen der Pegelverschieberschaltung, die bei der Ausführungsform 1 beschrieben ist, anhand der **Fig. 6A bis Fig. 6E**, **Fig. 7A bis Fig. 7D**, **Fig. 8A bis Fig. 8C** und **Fig. 9A** und **Fig. 9B** beschrieben. Zuerst wird ein Verfahren zum Herstellen eines Transistors, der in einem Unterteil einer Pegelverschieberschaltung ausgebildet wird, erklärt, und danach wird ein Verfahren zum Herstellen eines Transistors, der in einem Oberteil der Pegelverschieberschaltung ausgebildet wird, erklärt.

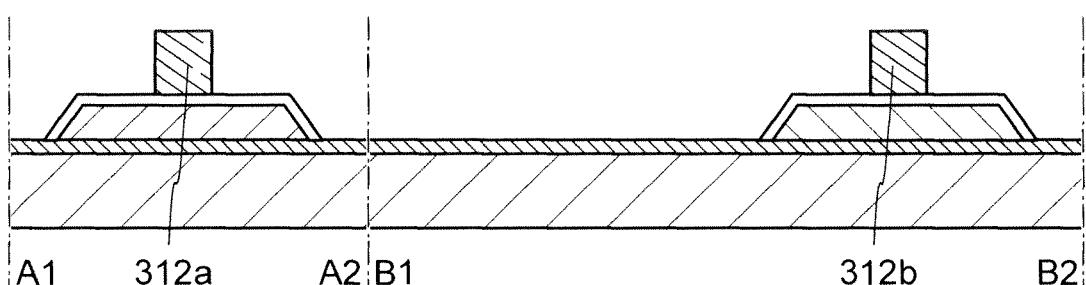

**[0087]** In jeder der Querschnittsansichten der **Fig. 6A bis Fig. 6E**, **Fig. 7A bis Fig. 7D**, **Fig. 8A bis Fig. 8C** und **Fig. 9A** und **Fig. 9B**, die einen Herstellungsprozess zeigen, zeigt ein Querschnitt A1-A2 einen Prozess zum Herstellen eines Transistors 330, und ein Querschnitt B1-B2 zeigt einen Prozess zum Herstel-

len eines Transistors 410 über einem Transistor 340. Zu beachten ist, dass der Transistor 410 bei dieser Ausführungsform dem Transistor 101 bei der Ausführungsform 1 entspricht, der Transistor 330 bei dieser Ausführungsform dem Transistor 103 bei der Ausführungsform 1 entspricht, und der Transistor 340 bei dieser Ausführungsform dem Transistor 104 bei der Ausführungsform 1 entspricht.

<Verfahren zum Herstellen eines Transistors in einem Unterteil>

**[0088]** Zuerst wird ein Substrat 300, über dem ein Halbleiterfilm 304 mit einem dazwischen liegenden Isolierfilm 302 ausgebildet ist, vorbereitet (siehe **Fig. 6A**).

**[0089]** Für das Substrat 300 kann beispielsweise ein einkristallines Halbleitersubstrat oder ein polykristallines Halbleitersubstrat aus Silizium, Siliziumkarbid oder dergleichen, oder ein Verbindungshalbleitersubstrat aus Silizium-Germanium, Galliumarsenid, Indiumphosphid oder dergleichen verwendet werden. Ferner kann auch jedes geeignete der verschiedenen Glassubstrate aus Aluminosilikatglas, Aluminoborosilikatglas, Bariumborosilikatglas und der gleichen, die in der Elektronikbranche verwendet werden, ein Quarzsubstrat, ein Keramiksubstrat, ein Saphirsubstrat oder dergleichen als das Substrat 300 verwendet werden.

**[0090]** Der Isolierfilm 302 weist eine einschichtige Struktur oder eine mehrschichtige Struktur auf, die eines oder mehrere von Siliziumoxid, Siliziumoxynitrid, Siliziumnitrid und dergleichen enthält. Als ein Verfahren zum Ausbilden des Isolierfilms 302 kann ein thermisches Oxidationsverfahren, ein CVD-Verfahren, ein Sputterverfahren oder dergleichen verwendet werden. Die Dicke des Isolierfilms 302 beträgt größer als oder gleich 1 nm und kleiner als oder gleich 100 nm, bevorzugt größer als oder gleich 10 nm und kleiner als oder gleich 50 nm.

**[0091]** Als der Halbleiterfilm 304 kann ein einkristalliner Halbleiterfilm oder ein polykristalliner Halbleiterfilm aus Silizium, Siliziumkarbid oder dergleichen, oder ein Verbindungshalbleiterfilm aus Silizium-Germanium, Galliumarsenid, Indiumphosphid oder dergleichen verwendet werden. Weil der Halbleiterfilm 304 kein Oxidhalbleitermaterial enthält, kann ein Material für den Halbleiterfilm 304 auch als ein Halbleitermaterial außer einem Oxidhalbleiter bezeichnet werden.

**[0092]** Es ist zu bevorzugen, einen einkristallinen Halbleiterfilm aus Silizium oder dergleichen für den Halbleiterfilm 304 zu verwenden, da die Transistoren 103 und 104 oder dergleichen mit hoher Geschwindigkeit betrieben werden können.

**[0093]** Ferner kann ein SOI- (silicon on insulator, Silizium auf einem Isolator) Substrat als das Substrat 300, über dem der Halbleiterfilm 304 mit dem dazwischen liegenden Isolierfilm 302 ausgebildet ist, verwendet werden. Zu beachten ist, dass der Ausdruck „SOI-Substrat“ allgemein ein Substrat bedeutet, bei dem eine Siliziumschicht über einer isolierenden Oberfläche vorgesehen ist. In dieser Beschreibung und dergleichen bedeutet der Ausdruck „SOI-Substrat“ ebenfalls ein Substrat, bei dem über einer isolierenden Oberfläche ein Halbleiterfilm aus einem anderen Material als Silizium vorgesehen ist. Das heißt, dass ein in dem „SOI-Substrat“ aufgewiesener Halbleiterfilm nicht auf eine Siliziumschicht beschränkt ist. Darüber hinaus kann das SOI-Substrat eine Struktur aufweisen, bei der ein Halbleiterfilm über einem isolierenden Substrat wie z. B. einem Glassubstrat mit einem dazwischen liegenden Isolierfilm ausgebildet ist. Bei dieser Ausführungsform wird der Fall beschrieben, in dem ein SOI-Substrat mit einer Struktur, bei der ein Siliziumfilm über einem einkristallinen Siliziumsubstrat mit einem dazwischen liegenden Siliziumoxidfilm ausgebildet ist, als das Substrat 300, über dem der Halbleiterfilm 304 mit dem dazwischen liegenden Isolierfilm 302 ausgebildet ist, verwendet wird.

**[0094]** Als Nächstes wird der Halbleiterfilm 304 in inseiförmige Halbleiterfilme bearbeitet, und somit werden Halbleiterfilme 304a und 304b ausgebildet (siehe **Fig. 6B**). Für die Bearbeitung wird vorzugsweise Trockenätzen verwendet, aber auch Nassätzen kann verwendet werden. Ein Ätzgas oder ein Ätzmittel kann je nach einem zu ätzenden Material geeignet ausgewählt werden.

**[0095]** Dann werden Gate-Isolierfilme 306a und 306b ausgebildet, um die Halbleiterfilme 304a und 304b zu bedecken (siehe **Fig. 6C**). Die Gate-Isolierfilme 306a und 306b können beispielsweise durch eine Wärmebehandlung (eine thermische Oxidationsbehandlung, eine thermische Nitrierungsbehandlung oder dergleichen), die an den Oberflächen der Halbleiterfilme 304a und 304b durchgeführt wird, ausgebildet werden. Anstelle einer Wärmebehandlung kann eine Behandlung durch hochdichtetes Plasma verwendet werden. Die Behandlung durch hochdichtetes Plasma kann z. B. unter Verwendung eines Mischgases, das eines/einen oder mehrere von Edelgasen wie z. B. He, Ar, Kr und Xe, Sauerstoff, Stickstoffoxid, Ammoniak, Stickstoff, Wasserstoff und dergleichen enthält, durchgeführt werden. Natürlich können die Gate-Isolierfilme durch ein CVD-Verfahren, ein Sputterverfahren oder dergleichen ausgebildet werden.

**[0096]** Für die Gate-Isolierfilme 306a und 306b kann ein Material wie z. B. Siliziumoxid, Siliziumoxydnitrid, Siliziumnitrid, Aluminiumoxid oder Tantaloxid verwendet werden. Alternativ kann für die Gate-Isolier-

filme 306a und 306b ein Material mit hoher Dielektrizitätskonstante (hohem k) wie z. B. Hafniumoxid, Yttriumoxid, Hafniumsilikat ( $\text{HfSi}_x\text{O}_y$  ( $x > 0$ ,  $y > 0$ )), Hafniumsilikat, zu dem Stickstoff zugesetzt worden ist ( $\text{HfSi}_x\text{O}_y\text{N}_z$  ( $x > 0$ ,  $y > 0$ ,  $z > 0$ )), oder Hafniumaluminat, zu dem Stickstoff zugesetzt worden ist ( $\text{HfAl}_x\text{O}_y\text{N}_z$  ( $x > 0$ ,  $y > 0$ ,  $z > 0$ )) verwendet werden. Die Gate-Isolierfilme 306a und 306b weisen eine einschichtige Struktur oder eine mehrschichtige Struktur auf, die eines oder mehrere der vorstehenden Materialien enthält. Die Dicke jedes der Gate-Isolierfilme 306a und 306b kann z. B. größer als oder gleich 1 nm und kleiner als oder gleich 100 nm, bevorzugt größer als oder gleich 10 nm und kleiner als oder gleich 50 nm betragen.

**[0097]** Wenn die Gate-Isolierfilme wie oben beschrieben dünn gemacht werden sind, wird ein Gate-Leckstrom wegen eines Tunneleffekts oder dergleichen zu einem Problem. Um das Problem des Gate-Leckstroms zu lösen, wird vorzugsweise für die Gate-Isolierfilme das vorstehende Material mit hohem k verwendet. Die Verwendung des Materials mit hohem k für die Gate-Isolierfilme ermöglicht die Dicke zu erhöhen, um den Gate-Leckstrom zu unterdrücken sowie die elektrischen Eigenschaften sicherzustellen. Zu beachten ist, dass eine mehrschichtige Struktur, die einen Film aus einem Material mit hohem k und einen Film aus einem von Siliziumoxid, Siliziumnitrid, Siliziumoxynitrid, Siliziumnitridoxid, Aluminiumoxid und dergleichen aufweist, ebenfalls verwendet werden kann.

**[0098]** Bei dieser Ausführungsform werden Siliziumoxidfilme durch eine thermische Oxidationsbehandlung ausgebildet, um die Gate-Isolierfilme 306a und 306b auszubilden.

**[0099]** Als Nächstes werden ein Störstellenelement, das n-Leitfähigkeit verleiht, und ein Störstellenelement, das p-Leitfähigkeit verleiht, durch die Gate-Isolierfilme 306a und 306b zu den Halbleiterfilmen 304a und 304b zugesetzt, damit die Schwellenspannungen der Transistoren gesteuert werden können (siehe **Fig. 6C**). In dem Fall, in dem Silizium für die Halbleiterfilme 304a und 304b verwendet wird, kann als ein Störstellenelement, das n-Leitfähigkeit verleiht, z. B. Phosphor, Arsen oder dergleichen verwendet werden. Ferner kann als ein Störstellenelement, das p-Leitfähigkeit verleiht, z. B. Bor, Aluminium, Gallium oder dergleichen verwendet werden. Bei dieser Ausführungsform wird Bor durch den Gate-Isolierfilm 306a zu dem Halbleiterfilm 304a zugesetzt, um ein Störstellengebiet 308 auszubilden, während Phosphor durch den Gate-Isolierfilm 306b zu dem Halbleiterfilm 304b zugesetzt wird, um ein Störstellengebiet 310 auszubilden.

**[0100]** Als Nächstes wird ein leitender Film zum Ausbilden der Gate-Elektroden (einschließlich einer

Leitung, die in derselben Schicht wie die Gate-Elektroden ausgebildet ist) über den Gate-Isolierfilmen 306a und 306b ausgebildet, und der leitende Film wird bearbeitet, um Gate-Elektroden 312a und 312b auszubilden (siehe **Fig. 6D**).

**[0101]** Für den leitenden Film zum Ausbilden der Gate-Elektroden 312a und 312b kann ein Metallmaterial wie z. B. Aluminium, Kupfer, Titan, Tantal oder Wolfram verwendet werden. Außerdem kann eine Schicht, die ein leitendes Material enthält, unter Verwendung eines Halbleitermaterials wie z. B. eines polykristallinen Siliziums ausgebildet werden. Auf ein Verfahren zum Ausbilden des leitenden Films gibt es keine besondere Beschränkung, und jedes geeignete der verschiedenen Verfahren wie z. B. ein Verdampfungsverfahren, ein CVD-Verfahren, ein Sputterverfahren und ein Rotationsbeschichtungsverfahren kann verwendet werden. Der leitende Film kann durch Ätzen unter Verwendung einer Fotolackmaske bearbeitet werden. Bei dieser Ausführungsform werden ein Tantalnitridfilm und ein Wolframfilm unter Verwendung eines Sputterverfahrens gestapelt und bearbeitet, so dass die Gate-Elektroden 312a und 312b ausgebildet werden.

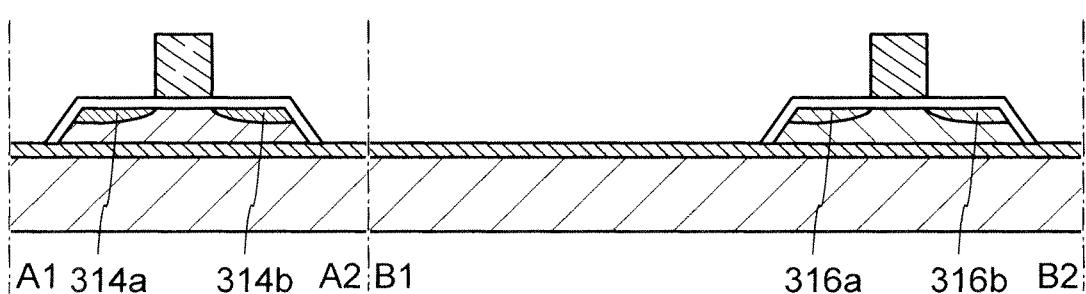

**[0102]** Als Nächstes werden ein Störstellenelement, das n-Leitfähigkeit verleiht, und ein Störstellenelement, das p-Leitfähigkeit verleiht, unter Verwendung der Gate-Elektroden 312a und 312b als Masken durch die Gate-Isolierfilme 306a und 306b zu den Halbleiterfilmen 304a und 304b zugesetzt (siehe **Fig. 6E**). Bei dieser Ausführungsform wird Phosphor durch den Gate-Isolierfilm 306a zu dem Halbleiterfilm 304a zugesetzt, um Störstellengebiete 314a und 314b auszubilden, während Bor durch den Gate-Isolierfilm 306b zu dem Halbleiterfilm 304b zugesetzt wird, um Störstellengebiete 316a und 316b auszubilden.

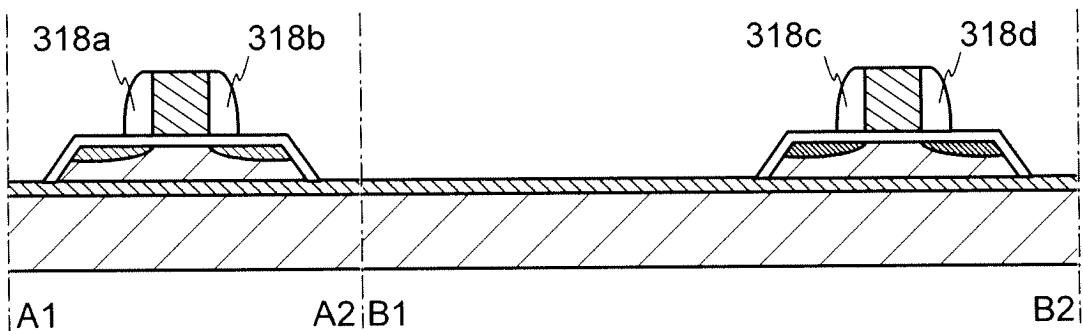

**[0103]** Als Nächstes werden Seitenwand-Isolierfilme 318a bis 318d je mit einer Seitenwand-Struktur an den Seitenflächen der Gate-Elektroden 312a und 312b ausgebildet (siehe **Fig. 7A**). Die Seitenwand-Isolierfilme 318a bis 318d können an den Seitenflächen der Gate-Elektroden 312a und 312b selbstausrichtend wie folgt ausgebildet werden: ein Isolierfilm, der die Gate-Elektroden 312a und 312b bedeckt, wird ausgebildet und dann durch anisotropes Ätzen mittels eines reaktiven Ionenätz- (reactive ion etching: RIE) Verfahrens bearbeitet. Es gibt keine besondere Beschränkung auf den Isolierfilm; beispielsweise kann ein Film aus Siliziumoxid, der einen untenliegenden Film gut bedeckt, durch eine Reaktion zwischen Tetraethylorthosilicat (TEOS), Silan oder dergleichen und Sauerstoff, Distickstoffmonoxid oder dergleichen ausgebildet werden. Außerdem kann ein Film aus Siliziumoxid, der durch ein Niedertemperaturoxidations- (low temperature oxidation: LTO) Verfahren ausgebildet wird, ver-

wendet werden. Der Isolierfilm kann durch ein thermisches CVD-Verfahren, ein Plasma-CVD-Verfahren, ein Normaldruck-CVD-Verfahren, ein Vorspannung-ECRCVD-Verfahren, ein Sputterverfahren oder dergleichen ausgebildet werden.

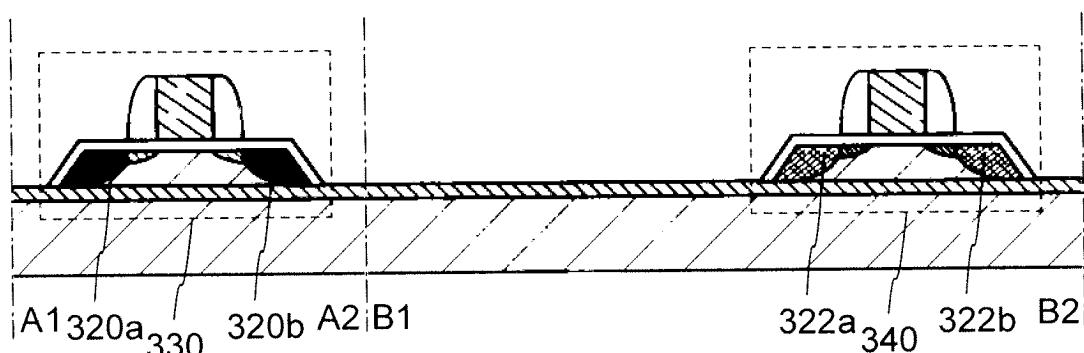

**[0104]** Als Nächstes werden ein Störstellenelement, das n-Leitfähigkeit verleiht, und ein Störstellenelement, das p-Leitfähigkeit verleiht, unter Verwendung der Gate-Elektroden 312a und 312b und der Seitenwand-Isolierfilme 318a bis 318d als Masken durch die Gate-Isolierfilme 306a und 306b zu den Halbleiterfilmen 304a und 304b zugesetzt (siehe **Fig. 7B**). Bei dieser Ausführungsform wird Phosphor durch den Gate-Isolierfilm 306a zu dem Halbleiterfilm 304a zugesetzt, um Störstellengebiete 320a und 320b auszubilden, während Bor durch den Gate-Isolierfilm 306b zu dem Halbleiterfilm 304b zugesetzt, um Störstellengebiete 322a und 322b auszubilden.

**[0105]** Durch die oben angegebenen Schritte können der n-Kanal Transistor 330 und der p-Kanal Transistor 340 unter Verwendung des Substrats 300, das ein Halbleitermaterial außer einem Oxidhalbleiter enthält, hergestellt werden (siehe **Fig. 7B**). Solche Transistoren sind zu einem Hochgeschwindigkeitsbetrieb fähig. Da ein Hochgeschwindigkeitsbetrieb erhältlich ist, werden solche Transistoren bevorzugt auf den Transistor 103 und den Transistor 104 angewendet.

**[0106]** Dann wird ein Isolierfilm 324 ausgebildet, um den Transistor 330 und den Transistor 340 zu bedecken (siehe **Fig. 7C**). Der Isolierfilm 324 kann unter Verwendung eines Materials ausgebildet werden, das ein anorganisches Isoliermaterial wie z. B. Siliziumoxid, Siliziumoxynitrid, Siliziumnitrid oder Aluminiumoxid enthält. Es ist zu bevorzugen, für den Isolierfilm 324 ein Material mit niedriger Dielektrizitätskonstante (niedrigem  $\kappa$ ) zu verwenden, weil die Kapazität wegen Überlappung der Elektroden oder Leitungen ausreichend verringert werden kann. Zu beachten ist, dass als der Isolierfilm 324 ein poröser Isolierfilm aus einem der vorstehenden Materialien verwendet werden kann. Der poröse Isolierfilm weist eine niedrigere Dielektrizitätskonstante als ein Isolierfilm mit hoher Dichte auf und ermöglicht somit, die Kapazität wegen Überlappung der Elektroden oder Leitungen weiter zu verringern. Alternativ kann der Isolierfilm 324 unter Verwendung eines organischen Isoliermaterials wie z. B. eines Polyimids oder eines Acryls ausgebildet werden. Bei dieser Ausführungsform wird der Fall beschrieben, in dem der Isolierfilm 324 unter Verwendung eines Siliziumoxynitrids ausgebildet wird.

**[0107]** Nachdem der Isolierfilm 324 ausgebildet worden ist, wird dann eine Wärmebehandlung zum Aktivieren der Störstellenelemente, die zu den Halbleiterfilmen 304a und 304b zugesetzt worden sind,

durchgeführt. Die Wärmebehandlung wird mittels eines Glühofens durchgeführt. Alternativ kann ein Laserglühverfahren (Laser-Annealing) oder ein schnelles thermisches Ausheilungs- (rapid thermal anneal: RTA) Verfahren verwendet werden. Die Wärmebehandlung wird 1 bis 4 Stunden lang in einer Stickstoffatmosphäre bei 400 °C bis 600 °C, typischerweise 450 °C bis 500 °C durchgeführt. Durch diese Wärmebehandlung werden die Störstellenelemente aktiviert, und Wasserstoff in dem Siliziumoxy-nitridfilm als dem Isolierfilm 324 wird entzogen, so dass Hydrieren der Halbleiterfilme 304a und 304b durchgeführt werden kann.

**[0108]** Zu beachten ist, dass vor oder nach jedem der obigen Schritte ferner ein Schritt zum Ausbilden einer Elektrode, einer Leitung, eines Halbleiterfilms, eines Isolierfilms oder dergleichen durchgeführt werden kann. Beispielsweise ist es zu bevorzugen, dass eine Elektrode, eine Leitung oder dergleichen zur Verbindung des Transistors in dem Unterteil mit dem Transistor in dem Oberteil ausgebildet wird. Außerdem kann eine hoch integrierte Halbleitervorrichtung verwirklicht werden, wenn die Leitung eine mehrschichtige Struktur, bei der ein Isolierfilm und eine leitende Schicht gestapelt sind, aufweist.

<Verfahren zum Herstellen eines Transistors in einem Oberteil>

**[0109]** Zuerst wird als eine Behandlung vor dem Herstellen des Transistors 410 eine Oberfläche des Isolierfilms 324 verflacht (siehe **Fig. 7D**). Zum Verflachen des Isolierfilms 324 kann zusätzlich zu einer Polierbehandlung wie z. B. chemisch-mechanischem Polieren (CMP) eine Ätzbehandlung, eine Plasmabehandlung oder dergleichen verwendet werden.

**[0110]** Die CMP-Behandlung ist ein Verfahren zum Verflachen einer Oberfläche eines zu bearbeitenden Objekts durch eine Kombination von chemischen und mechanischen Aktionen. Genauer ist die CMP-Behandlung ein Verfahren, in dem an einem Polierteller ein Poliertuch befestigt wird, wobei der Polierteller und ein zu bearbeitendes Objekt je gedreht oder geschwenkt werden, während zwischen dem zu bearbeitenden Objekt und dem Poliertuch ein Slurry (ein Poliermittel) zugeführt wird, und die Oberfläche des zu bearbeitenden Objekts durch eine chemische Reaktion zwischen dem Slurry und dem zu bearbeitenden Objekt und durch eine mechanische Polieraktion des Poliertuchs zu dem zu bearbeitenden Objekt poliert wird.

**[0111]** Ferner kann als die Plasmabehandlung beispielsweise ein umgekehrtes Sputtern durchgeführt werden, in dem ein Argongas eingesetzt wird und ein Plasma erzeugt wird. Das umgekehrte Sputtern ist ein Verfahren, in dem eine Spannung unter Verwendung einer HF-Leistungsquelle an eine Substrat-

seite in einer Argonatmosphäre angelegt wird, um in der Nähe des Substrats ein Plasma zu erzeugen und eine Oberfläche zu ändern. Zu beachten ist, dass anstelle einer Argonatmosphäre eine Stickstoffatmosphäre, eine Heliumatmosphäre, eine Sauerstoffatmosphäre oder dergleichen verwendet werden kann. Durch das umgekehrte Sputtern können Pulversubstanzen (auch als Partikel oder Staub bezeichnet) auf der Oberfläche des Isolierfilms 324 entfernt werden.

**[0112]** Als die Behandlung zum Verflachen können die Polierbehandlung, die Trockenätzbehandlung und die Plasmabehandlung je mehrmals oder in einer Kombination durchgeführt werden. In dem Fall, in dem die oben angegebenen Behandlungen kombiniert werden, ist die Reihenfolge der Schritte nicht besonders beschränkt und kann angemessen entsprechend der Rauheit der Oberfläche des Isolierfilms 324 bestimmt werden.

**[0113]** Durch Verflachen des Isolierfilms 324 kann die mittlere Rauheit ( $R_a$ ) der Oberfläche des Isolierfilms 324 kleiner als oder gleich 1 nm, bevorzugt kleiner als oder gleich 0,3 nm, stärker bevorzugt kleiner als oder gleich 0,1 nm sein. Zu beachten ist, dass  $R_a$  durch Ausdehnen der arithmetischen mittleren Rauheit, die von JIS B 0601: 2001 (ISO4287:1997) definiert ist, in die dritte Dimension erhalten ist, so dass die Rauheit auf eine krumme Oberfläche angewendet werden kann.  $R_a$  kann als „ein mittlerer Wert der absoluten Werte der Abweichungen von einer Bezugsoberfläche bis einer bestimmten Oberfläche“ dargestellt werden und wird durch die folgende Formel definiert.

$$R_a = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy \quad [\text{Formel 1}]$$

**[0114]** Die bestimmte Oberfläche ist eine Oberfläche, die ein Gegenstand der Rauheitsmessung ist, wobei sie ein viereckiges Gebiet ist, das von vier durch die Koordinaten  $(x_1, y_1, f(x_1, y_1))$ ,  $(x_1, y_2, f(x_1, y_2))$ ,  $(x_2, y_1, f(x_2, y_1))$  und  $(x_2, y_2, f(x_2, y_2))$  bezeichneten Punkten dargestellt ist. Die Fläche eines Rechtecks, das durch Projizieren der bestimmten Oberfläche auf eine x-y Fläche erhalten ist, ist  $S_0$ , und die Höhe der Bezugsoberfläche (die durchschnittliche Höhe der bestimmten Oberfläche) ist  $Z_0$ .  $R_a$  kann unter Verwendung eines Rasterkraftmikroskops (atomic force microscope: AFM) gemessen werden.

**[0115]** Als Nächstes wird ein leitender Film zum Ausbilden einer Gate-Elektrode (einschließlich einer Leitung, die in derselben Schicht wie die Gate-Elektrode ausgebildet ist) über dem verflachten Isolierfilm 324 ausgebildet und bearbeitet, um eine Gate-Elektrode 398 auszubilden. Zu beachten ist, dass die Gate-Elektrode 398 als eine zweite Gate-Elektrode dient.

**[0116]** Die Gate-Elektrode 398 kann unter Verwendung eines Metallmaterials wie z. B. Molybdäns, Titans, Tantals, Wolframs, Aluminiums, Kupfers, Chroms, Neodyms oder Scandiums oder eines Legierungsmaterials, das eines dieser Materialien als Hauptkomponente enthält, ausgebildet werden. Alternativ kann als die Gate-Elektrode 398 ein Halbleiterfilm wie z. B. ein polykristalliner Siliziumfilm, der mit einem Störstellenelement wie z. B. Phosphor dotiert ist, oder ein Silizidfilm wie z. B. ein Nickelsilizidfilm verwendet werden. Die Gate-Elektrode 398 wird als eine einschichtige Struktur oder eine mehrschichtige Struktur ausgebildet.

**[0117]** Außerdem kann die Gate-Elektrode 398 unter Verwendung eines leitenden Materials, wie z. B. eines Indiumzinnoxids, eines Indiumoxids, das ein Wolframoxid enthält, eines Indiumzinkoxids, das ein Wolframoxid enthält, eines Indiumoxids, das ein Titanoxid enthält, eines Indiumzinnoxids, das ein Titanoxid enthält, eines Indiumzinkoxids oder eines Indiumzinnoxids, zu dem ein Siliziumoxid zugesetzt worden ist, ausgebildet werden. Ferner kann die Gate-Elektrode 398 eine mehrschichtige Struktur, die das leitende Material und das Metallmaterial enthält, aufweisen.

**[0118]** Als Nächstes wird ein Isolierfilm 399 über dem Isolierfilm 324 und der Gate-Elektrode 398 ausgebildet. Der Isolierfilm 399 kann durch ein Plasma-CVD-Verfahren oder ein Sputterverfahren ausgebildet werden, um eine einschichtige Struktur oder eine mehrschichtige Struktur aufzuweisen, die einen/eines oder mehrere von einem Oxidisolierfilm aus Siliziumoxid, Siliziumoxynitrid, Aluminiumoxid, Aluminiumoxynitrid, Hafniumoxid, Galliumoxid oder dergleichen, einem Nitridisolierfilm aus Siliziumnitrid, Siliziumnitridoxid, Aluminiumnitrid, Aluminiumnitridoxid oder dergleichen, und einem Mischmaterial davon verwendet.

**[0119]** Es ist zu bevorzugen, dass in dem Isolierfilm 399 (einem Film, der mit einem nachher auszubildenden Oxidhalbleiterfilm 402 in Kontakt steht, in dem Fall der mehrschichtigen Struktur) die Menge an Sauerstoff zumindest größer als die der stöchiometrischen Zusammensetzung in dem Film (im Bulk) ist. Zum Beispiel erfüllt die Menge an Sauerstoff im Fall der Verwendung eines Siliziumoxidfilms als des Isolierfilms 399 bevorzugt  $\text{SiO}_{2+\alpha}$  ( $\alpha > 0$ ). Nach dem Ausbilden des Isolierfilms 399 wird Sauerstoff zu dem Isolierfilm 399 zugeführt, wodurch der Isolierfilm 399 Sauerstoff in einer großen Menge enthalten kann.