(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5461094号

(P5461094)

(45) 発行日 平成26年4月2日(2014.4.2)

(24) 登録日 平成26年1月24日(2014.1.24)

(51) Int.CI.

H01L 31/10 (2006.01)

F 1

H01L 31/10

G

請求項の数 4 (全 22 頁)

(21) 出願番号 特願2009-174907 (P2009-174907)

(22) 出願日 平成21年7月28日 (2009.7.28)

(65) 公開番号 特開2010-62537 (P2010-62537A)

(43) 公開日 平成22年3月18日 (2010.3.18)

審査請求日 平成24年5月22日 (2012.5.22)

(31) 優先権主張番号 特願2008-204965 (P2008-204965)

(32) 優先日 平成20年8月8日 (2008.8.8)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 天野 聖子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 山本 元彦

最終頁に続く

(54) 【発明の名称】光電変換装置、及び当該光電変換装置を具備する電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

光電流を生成することができる機能を有する光電変換素子と、

前記光電流の大きさに応じた周波数のランプ波形信号を出力することができる機能を有するランプ波形出力回路と、

前記ランプ波形信号と、第1の電位とを比較することができる機能を有する第1のコンパレータと、

前記ランプ波形信号と、第2の電位とを比較することができる機能を有する第2のコンパレータと、

前記第1のコンパレータの出力信号と、前記第2のコンパレータの出力信号とが入力されることで、前記光電流に応じて周波数が変化するクロック信号を生成することができる機能を有するフリップフロップ回路と、

前記第1のコンパレータの出力信号と、前記第2のコンパレータの出力信号との否定論理和を取ることができる機能を有するNOR回路と、

前記クロック信号のパルス数をカウントすることができる機能を有するカウンタ回路と、

前記カウンタ回路で前記パルス数をカウントする期間を生成することができる機能を有するパルス出力回路と、を有し、

前記パルス出力回路は、前記NOR回路の出力信号に応じて、前記パルス数をカウントする期間の生成を停止することができる機能を有するスイッチを有し、

前記パルス出力回路は、定電流回路と、第1乃至第3のトランジスタと、前記スイッチと、容量素子と、第3のコンパレータと、第1の電位を供給することができる機能を有する第1の配線と、第2の電位を供給することができる機能を有する第2の配線と、リセット信号を供給することができる機能を有する第3の配線と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、前記定電流回路と、前記第1のトランジスタのゲートと、前記第2のトランジスタのゲートと、に電気的に接続されており、

前記第1のトランジスタのソース又はドレインの他方は、前記第2のトランジスタのソース又はドレインの一方と、前記容量素子の第1の電極と、に電気的に接続されており、

前記第2のトランジスタのソース又はドレインの他方は、前記スイッチの一端と電気的に接続されており、

前記スイッチの他端は、前記容量素子の第2の電極と、前記第3のトランジスタのソース又はドレインの一方と、前記第3のコンパレータの第1の入力端子と、に電気的に接続されており、

前記第3のトランジスタのソース又はドレインの他方は、前記第2の配線と電気的に接続されており、

前記第3のトランジスタのゲートは、前記第3の配線と電気的に接続されており、

前記第3のコンパレータの第2の入力端子は、前記第1の配線と電気的に接続されていることを特徴とする光電変換装置。

#### 【請求項2】

請求項1において、

前記光電変換装置は、複数の增幅回路を有し、

前記複数の増幅回路を切り替えて動作させるための切り替え回路によって、増幅された前記光電流が前記ランプ波形出力回路に入力されることを特徴とする光電変換装置。

#### 【請求項3】

請求項2において、

前記複数の増幅回路は異なる増幅率を有することを特徴とする光電変換装置。

#### 【請求項4】

請求項1乃至3のいずれか一に記載の光電変換装置を具備することを特徴とする電子機器。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、光電変換装置に関する。また、当該光電変換装置を具備する電子機器に関する。

##### 【背景技術】

##### 【0002】

光を検知するための用途に用いられる光電変換装置は数多く知られており、例えば可視光センサ等が実用化されている。光電変換装置は、人間の生活環境に応じて照度調整や、オンまたはオフの制御などが必要な機器類に数多く用いられている。

##### 【0003】

表示装置では、表示装置の周囲の明るさを検出し、その表示輝度を調整することを行うものもある。光電変換装置により、周囲の照度を検出して適度な表示輝度を得ることによって、視認性を向上させ、表示装置の無駄な電力を減らすことができるからである。例えば、輝度調整用の光電変換装置を具備する表示装置としては、携帯電話、表示部付きコンピュータが挙げられる。

##### 【0004】

光電変換装置は、光のセンシング部分にフォトダイオードなどの光電変換素子を用い、光電変換素子に流れる電流量に基づいて照度を検出することができる。特許文献1には、フォトダイオードから流れる電流を、当該電流の大きさに応じて周波数が変化するランプ

10

20

30

40

50

波形の信号に変換し、デジタル信号として出力する構成について記載している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第6556155号

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の光電変換装置は、フォトダイオードを流れる入射光量に応じた電流の値が大きい場合、ランプ波形の周波数も大きくなる構成となる。ランプ波形の周波数が大きくなるに従って、ランプ波形を有する信号が、寄生容量及び／またはコンパレータの周波数特性などに伴う、回路遅延の影響を受けやすくなる。そのため、ランプ波形を有する信号は、周波数が高い（高周波数）ほど、回路遅延の影響をうけてしまい、照度に応じた出力信号のばらつきが大きくなるといった課題がある。10

【0007】

本発明の一態様は、寄生容量等に起因した回路遅延の影響を受けることなく、照度に応じた周波数のランプ波形を有する信号によりデジタル信号を出力することのできる光電変換装置を提供することである。

【課題を解決するための手段】

【0008】

本発明の一態様は、光電流を生成する光電変換素子と、光電流の大きさに応じた周波数のランプ波形信号を出力するランプ波形出力回路と、ランプ波形信号と、第1の電位とを比較する第1のコンパレータと、ランプ波形信号と、第2の電位とを比較する第2のコンパレータと、第1のコンパレータの出力信号と、第2のコンパレータの出力信号とが入力されることで、光電流に応じて周波数が変化するクロック信号を生成するフリップフロップ回路と、第1のコンパレータの出力信号と、第2のコンパレータの出力信号との否定論理和を取るための回路と、クロック信号のパルス数をカウントするカウンター回路と、カウンター回路でパルス数をカウントする期間を生成するためのパルス出力回路と、を有し、パルス出力回路は、否定論理和を取るための回路の出力信号に応じて、パルス数をカウントする期間の生成を停止するためのスイッチを有する光電変換装置である。30

【発明の効果】

【0009】

本発明の一態様により、寄生容量等に起因した回路遅延の影響を受けることなく、照度に応じた周波数のランプ波形を有する信号をデジタル信号に変換することのできる光電変換装置を提供することができる。

【図面の簡単な説明】

【0010】

【図1】実施の形態1を説明するための図。

【図2】実施の形態1を説明するための図。

【図3】実施の形態1を説明するための図。

【図4】実施の形態1を説明するための図。

【図5】実施の形態1を説明するための図。

【図6】実施の形態1を説明するための図。

【図7】実施の形態1を説明するための図。

【図8】実施の形態1を説明するための図。

【図9】実施の形態1を説明するための図。

【図10】実施の形態1を説明するための図。

【図11】実施の形態2を説明するための図。

【図12】実施の形態2を説明するための図。

【図13】実施の形態3を説明するための図。

10

20

30

40

50

【図14】実施の形態3を説明するための図。

【図15】実施の形態4を説明するための図。

【発明を実施するための形態】

【0011】

以下に、本発明の実施の形態を図面に基づいて説明する。但し、本発明は多くの異なる様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、実施の形態の記載内容に限定して解釈されるものではない。なお、実施の形態を説明するための全図において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

10

【0012】

(実施の形態1)

本実施の形態では、本発明の一態様の光電変換装置の構成及びその動作について説明する。

【0013】

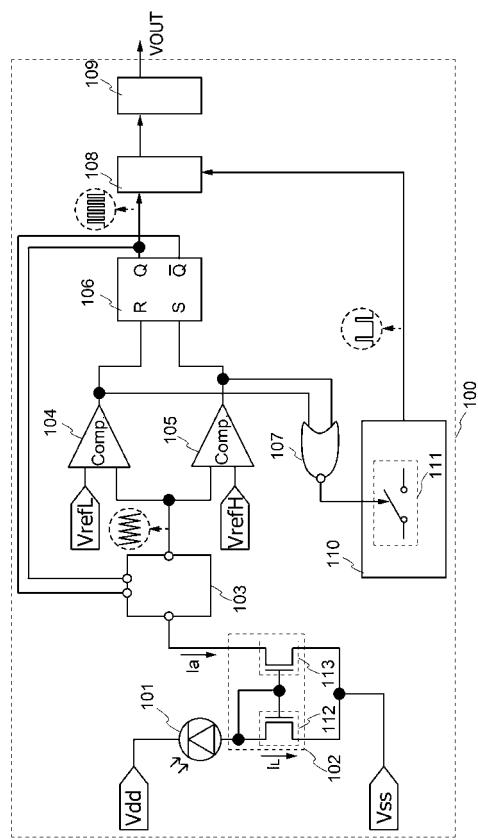

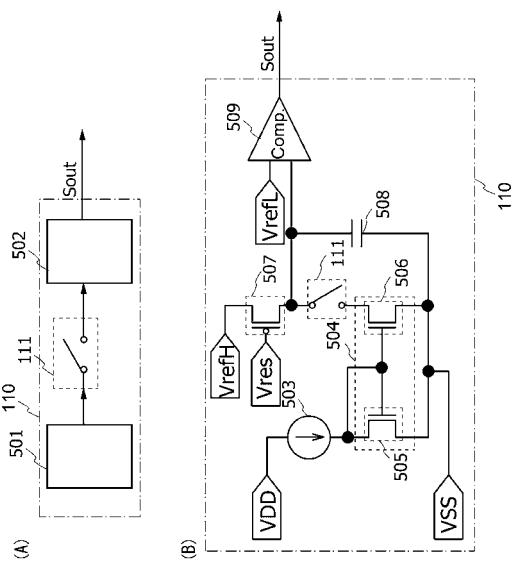

まず本発明の一態様の光電変換装置における回路図について説明する。図1に示す光電変換装置100は、光電変換素子101、增幅回路102、ランプ波形出力回路103、第1のコンパレータ104、第2のコンパレータ105、フリップフロップ回路106、NOR回路107(否定論理和回路ともいう)、カウンター回路108、ラッチ回路109、及びパルス出力回路110を有する。

20

【0014】

光電変換素子101は、一方の端子(n型半導体側)に高電源電位(Vdd)が供給され、他方の端子(p型半導体側)が増幅回路102に電気的に接続されることで、光電流I<sub>L</sub>を増幅回路102に供給するものである。増幅回路102は、光電変換素子101の光電流I<sub>L</sub>を電流I<sub>a</sub>に増幅するための回路である。また増幅回路102は低電源電位(Vss)が供給されている。ランプ波形出力回路103は、電流I<sub>a</sub>に応じて、周波数が変化するランプ波形の信号(以下、ランプ波形信号という)を出力する回路である。ランプ波形出力回路103の入力端子は増幅回路102に電気的に接続されており、ランプ波形出力回路103の出力端子は第1のコンパレータ104及び第2のコンパレータ105に電気的に接続されている。第1のコンパレータ104は、第1の電位VrefLとランプ波形信号の電位とを比較し、第1の電位VrefLが高い場合に高電位信号(以下、H信号ともいう)を出力する回路である。第2のコンパレータ105は、第2の電位VrefHとランプ波形信号の出力信号の電位とを比較し、第2の電位VrefHが低い場合にはH信号を出力するための回路である。フリップフロップ回路106は一例としてRSフリップフロップ回路を示しており、R端子に第1のコンパレータ104の出力信号が入力され、S端子に第2のコンパレータ105の出力信号が入力されている。NOR回路107は、第1のコンパレータ104及び第2のコンパレータ105の出力信号の否定論理和を取ることにより、出力信号の論理が決まる回路である。カウンター回路108とラッチ回路109とは、カウント値のビット数に応じたバスにより電気的に接続されている。カウンター回路108は、フリップフロップ回路106のQ端子からの出力信号(以下クロック信号という)のパルス数を所定の期間カウントするための回路である。ラッチ回路109はカウンター回路108でクロック信号のパルス数を所定の期間カウントして得られるカウント値をラッチし、光電変換装置の出力信号として出力する回路である。パルス出力回路110は上述のカウンター回路108でクロック信号のパルス数をカウントする期間の生成を行うための回路である。

30

【0015】

パルス出力回路110は、内部にスイッチ111を有する。スイッチ111は、NOR回路107からの出力信号に応じて間欠的な動作を行い、H信号であるときにオン状態となり、低電位信号(以下、L信号ともいう)であるときはオフ状態となる。また増幅回路102は、一例として、図1に示すようにカレントミラー回路で構成されており、第1のn

40

50

チャネル型トランジスタ 112 及び第 2 の n チャネル型トランジスタ 113 を有する。第 1 の n チャネル型トランジスタ 112 の第 1 端子は光電変換素子 101 の p 型半導体側に電気的に接続されている。第 1 の n チャネル型トランジスタ 112 及び第 2 の n チャネル型トランジスタ 113 のゲート端子は互いに電気的に接続されており、第 1 の n チャネル型トランジスタ 112 の第 1 端子は第 1 の n チャネル型トランジスタ 112 及び第 2 の n チャネル型トランジスタ 113 のゲート端子に電気的に接続されている。第 1 の n チャネル型トランジスタ 112 及び第 2 の n チャネル型トランジスタ 113 の第 2 端子は低電源電位 (Vss) が供給されている。

#### 【0016】

なお本明細書にて用いる第 1 、第 2 、第 3 、乃至第 N (N は自然数 ) という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

#### 【0017】

なお本明細書において、 A と B とが接続されている、とは、 A と B とが直接接続されているものの他、電気的に接続されているものを含むものとする。ここで、 A と B とが電気的に接続されているとは、 A と B との間に何らかの電気的作用を有する対象物が存在するとき、対象物を介して A と B とが概略同一ノードとなる場合を表すものとする。

#### 【0018】

具体的には、トランジスタをはじめとするスイッチング素子を介して A と B とが接続され、該スイッチング素子の導通によって、 A と B とが概略同電位となる場合や、抵抗素子を介して A と B とが接続され、該抵抗素子の両端に発生する電位差が、 A と B とを含む回路の動作に影響しない程度となっている場合など、回路動作を考えた場合、 A と B とが同一ノードとして捉えて差し支えない状態である場合を表す。

#### 【0019】

なお本明細書において、スイッチは、一方の端子と他方の端子との導通または非導通を制御できるものであればよく、特定のものに限定されない。スイッチとしては、電気的スイッチや機械的なスイッチなどがあり、一例として薄膜トランジスタを用いてアナログスイッチ等を構成すればよい。

#### 【0020】

なお、光電変換素子 101 は、 PIN フォトダイオードを用いればよい。また光電変換素子 101 として、 PIN フォトダイオードの代わりに、 PN フォトダイオードを用いても良い。

#### 【0021】

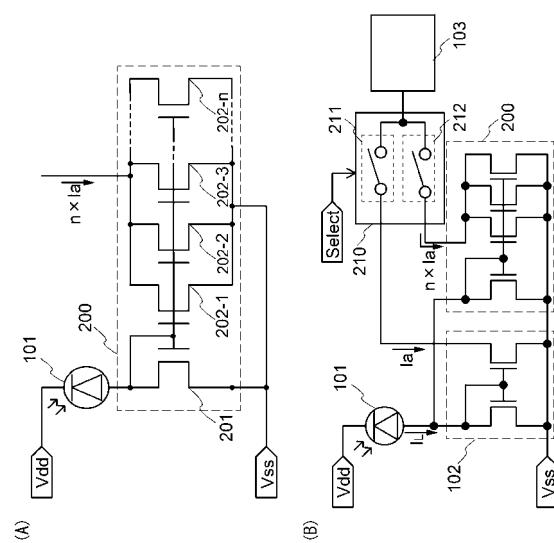

増幅回路 102 は、光電変換素子から出力される光電流  $I_L$  を、電流  $I_a$  の n 倍 (n は正の数 ) に増幅する回路であってもよい。一例として、増幅回路 102 は、図 2 (A) に示す増幅回路 200 のように、第 2 の n チャネル型トランジスタ 202 - 1 乃至 202 - n (n は 2 以上の自然数 ) を複数設けることにより、電流  $I_a$  を n 倍にして流すことができる。そのため、光電変換素子 101 に照射される入射光量が小さい場合であっても、第 2 の n チャネル型トランジスタ 202 - 1 乃至 202 - n の側に十分な電流を流すことができる。また第 2 の n チャネル型トランジスタ 201 のチャネル幅を長くする、またはチャネル長を短くすることでも、十分な電流を流すことができる。

#### 【0022】

また増幅回路 102 での光電流  $I_L$  の増幅率を照度に応じて切り替える構成としてもよい。図 2 (B) に照度に応じて光電流の増幅率を切り替える構成について示す。一例としては、光電変換素子 101 からの光電流  $I_L$  を増幅する回路を、増幅回路 102 と増幅回路 200 とし、選択信号 Select によって光電流  $I_L$  を増幅する回路を切り替える切り替え回路 210 を有する。切り替え回路 210 は、第 1 のスイッチ 211 及び第 2 のスイッチ 212 を有し、選択信号 Select によってランプ波形出力回路 103 に電気的に接続される増幅回路を切り替えるものである。なお、複数の異なる増幅率が得られる増幅回路を配し、切り替え回路 210 により切り替える構成とすることで照度に応じた光電流

10

20

30

40

50

$I_L$  の増幅率を最適化することができる。

【0023】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタは、ゲートと、ドレインと、ソースとを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことができる。ここで、ソースとドレインとは、トランジスタの構造や動作条件等によって変わるために、いずれがソースまたはドレインであるかを限定することが困難な場合もある。そこで、本実施の形態においては、ソース及びドレインとして機能する領域のそれぞれを、第1端子、第2端子と表記することもある。またゲートとして機能する端子については、ゲート端子と表記することもある。

10

【0024】

なお、nチャネル型トランジスタまたはpチャネル型トランジスタのようなトランジスタとして、様々な形態のトランジスタを用いることができる。例えば、非晶質シリコン、多結晶シリコン、微結晶（マイクロクリスタル、セミアモルファスとも言う）シリコンなどに代表される非単結晶半導体膜を有する薄膜トランジスタ（TFT）などを用いることができる。TFTを用いる場合、比較的に低温のプロセスで作製することができるため製造装置を大きくでき、大型基板上に製造できる。そのため、一度の製造工程で多くの取り数を得ることができ、低コストで製造することができる。さらに、比較的に低温のプロセスで作製するため、耐熱性の弱い基板を用いることができる。そのため、透光性を有する基板（例えば、絶縁表面を有するガラス基板）上にトランジスタを製造でき、透光性を有する基板上のトランジスタを用いて光の透過を利用した装置に用いることができる。

20

【0025】

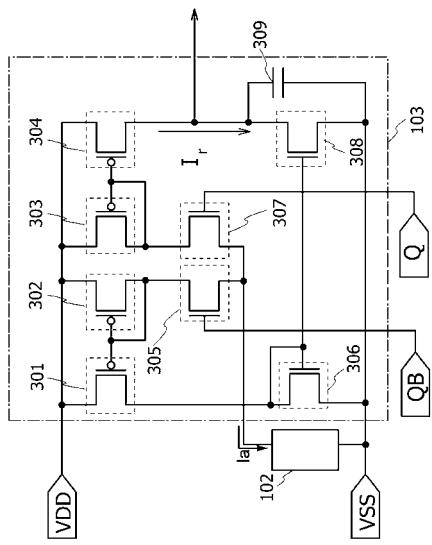

ランプ波形出力回路103は、図3に示すように接続されたpチャネル型トランジスタ301、pチャネル型トランジスタ302、pチャネル型トランジスタ303、pチャネル型トランジスタ304、nチャネル型トランジスタ305、nチャネル型トランジスタ306、nチャネル型トランジスタ307、nチャネル型トランジスタ308、および容量素子309で構成される。pチャネル型トランジスタ301及びpチャネル型トランジスタ302はカレントミラー回路を構成している。pチャネル型トランジスタ303及びpチャネル型トランジスタ304は、カレントミラー回路を構成している。またnチャネル型トランジスタ305のゲートには、反転クロック信号QBが入力される。またnチャネル型トランジスタ307のゲートには、クロック信号Qが入力される。nチャネル型トランジスタ306及びnチャネル型トランジスタ308は、カレントミラー回路を構成している。またnチャネル型トランジスタ305及びnチャネル型トランジスタ307のソース端子は増幅回路102に電気的に接続されており、増幅回路102の増幅率に応じた電流 $I_a$ が流れることとなる。図3に示すランプ波形出力回路103は、pチャネル型トランジスタ304またはnチャネル型トランジスタ308を流れる電流 $I_r$ により、容量素子309が充電と放電を繰り返す。そのため、ランプ波形出力回路103からランプ波形信号が第1のコンパレータ104及び第2のコンパレータ105に出力される。

30

【0026】

なお、ランプ波形出力回路103に入力されるクロック信号Q及び反転クロック信号QBは、フリップフロップ回路106のQ端子、QB端子より出力される信号である。

40

【0027】

また第1のコンパレータ104は、第1の電位 $V_{refL}$ とランプ波形信号の電位とを比較する。第1の電位 $V_{refL}$ が高い場合にH信号を出力するため、非反転入力端子に第1の電位 $V_{refL}$ が入力され、反転入力端子にランプ波形信号が入力されるようすればよい。また、第2のコンパレータ105は、第2の電位 $V_{refH}$ とランプ波形信号の電位とを比較する。第2の電位 $V_{refH}$ が低い場合にはH信号を出力するため、非反転入力端子にランプ波形信号が入力され、反転入力端子に第2の電位 $V_{refH}$ が入力されるようすればよい。

【0028】

50

フリップフロップ回路 106 は、図 1 で R S フリップフロップ回路である場合について示している。R 端子には、第 1 のコンパレータ 104 の出力信号が入力されている。S 端子には、第 2 のコンパレータ 105 の出力信号が入力されている。フリップフロップ回路 106 の Q 端子は、クロック信号が出力され、カウンター回路 108 及びランプ波形出力回路 103 に入力されている。フリップフロップ回路 106 の Q\_B 端子は、反転クロック信号が出力され、ランプ波形出力回路 103 に入力されている。

#### 【0029】

なおランプ波形出力回路 103 では、n チャネル型トランジスタ 305 と n チャネル型トランジスタ 307 とが、クロック信号及び反転クロック信号により交互にオンまたはオフすることで、p チャネル型トランジスタ 304 または n チャネル型トランジスタ 308 に電流  $I_r$  が流れる。電流  $I_r$  が流れることにより容量素子 309 が充電または放電をするため、容量素子 309 にはランプ波形の信号を出力する。ここで、ランプ波形出力回路 103 が output するランプ波形信号の周波数  $f$  は、電流  $I_r$  、および容量素子 309 の静電容量 C、第 1 の電位  $V_{refL}$  、第 2 の電位  $V_{refH}$  を用いて、下記で表される。式(1)より、電流  $I_r$  に応じて、周波数が変化する出力信号を得られることがわかる。

#### 【0030】

#### 【数 1】

$$f = \frac{Ir}{2C(V_{refH} - V_{refL})} \quad \cdots (1)$$

10

20

#### 【0031】

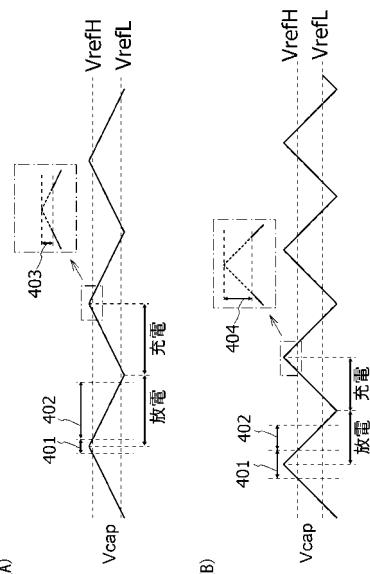

図 4 を用いて、図 3 で説明したランプ波形出力回路 103 より出力されるランプ波形信号について説明を行う。図 4 (A) に示すランプ波形は、光電変換素子に照射される光が小さい場合についてのランプ波形信号について示したものである。図 4 (B) に示すランプ波形は、光電変換素子に照射される光が大きい場合についてのランプ波形信号について示したものである。図 4 (A)、(B) に示すように、ランプ波形信号の電位 (図中、 $V_{cap}$  とする) は、第 1 の電位  $V_{refL}$  と、第 2 の電位  $V_{refH}$  の間 (バンドギャップリファレンスともいう) で充電または放電を繰り返す。そのため、上記式(1)で説明したように光電変換素子の照度が小さい場合と、大きい場合とで周波数が異なってくる。

30

#### 【0032】

高周波数の信号であればあるほど、配線抵抗、寄生容量等により、回路遅延が生じる。そのため図 4 (A)、(B) 中第 1 の期間 401 及び第 2 の期間 402 で見た場合、第 1 の期間 401 は、第 1 の電位  $V_{refL}$  と第 2 の電位  $V_{refH}$  の間に入らずに、充電と放電が切り替わる期間であり、第 2 の期間は、第 1 の電位  $V_{refL}$  と第 2 の電位  $V_{refH}$  の間で、充電または放電が行われる期間である。第 1 の期間 401 は、図 4 (A)、(B) 中の矢印 403、矢印 404 で示すように、周波数が高い程長くなり、後段のカウンター回路 108 での波数のカウントの際のばらつきの原因ともなる。

30

#### 【0033】

なお、カウンター回路 108 は、任意のビット数に応じたカウントを、パルス出力回路 110 からの出力に応じた期間に行う。カウント値は、フリップフロップ回路 106 の Q 端子から出力されるクロック信号のパルス数に応じてインクリメントする。なお、パルス出力回路 110 からの出力に応じた期間の終了とともに、カウンター回路 108 はカウント値のリセットを行い、再度カウンターでのカウントを行う。得られたカウント値は、ラッチ回路 109 に出力され、ラッチ回路 109 でラッチされたカウント値が光電変換装置からのデジタル値の出力信号  $V_{out}$  となる。

40

#### 【0034】

NOR 回路 107 は、第 1 のコンパレータ 104 の出力信号及び第 2 のコンパレータ 105 の出力信号の否定論理和を取ることにより、出力信号の論理が決まる回路である。

#### 【0035】

50

パルス出力回路 110 は、カウンター回路 108 でクロック信号のパルス数をカウントする期間の生成を行うための回路である。パルス出力回路 110 は、内部にスイッチ 111 を有する。スイッチ 111 は、NOR 回路 107 からの出力信号に応じて、交互にオンまたはオフするものである。一例としてスイッチ 111 は、NOR 回路 107 からの出力信号が H 信号であるときにオン状態となり、L 信号であるときはオフ状態となるスイッチを用いればよい。

#### 【0036】

スイッチ 111 を有するパルス出力回路 110 の具体的な構成について、図 5 (A)、(B) を用いて説明する。

#### 【0037】

図 5 (A) に示すパルス出力回路 110 は、発振回路 501、スイッチ 111、及びカウンター回路 502 を有する。発振回路 501 は、リングオシレータ、または水晶発振器等から出力される信号を分周して所望の周波数の信号を出力する回路である。またカウンター回路 502 は、スイッチ 111 を介して入力される発振回路 501 からの信号の波数をカウントしていく、所定のカウント値になった際にパルス Sout を出力するための回路である。

#### 【0038】

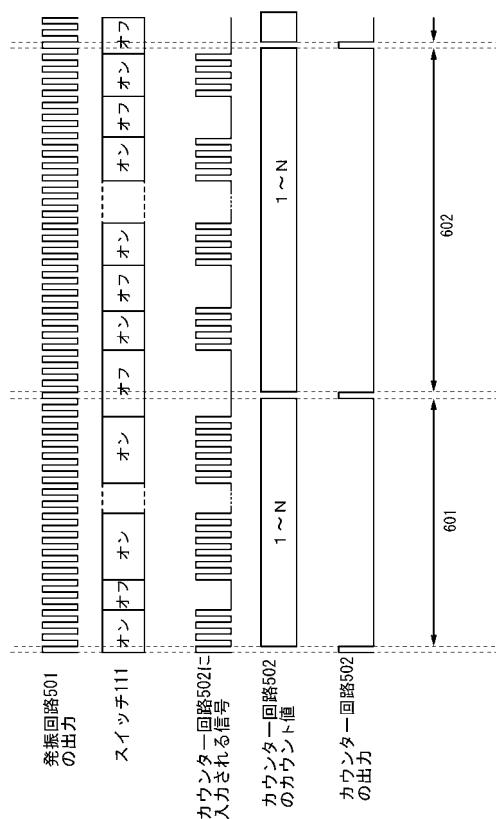

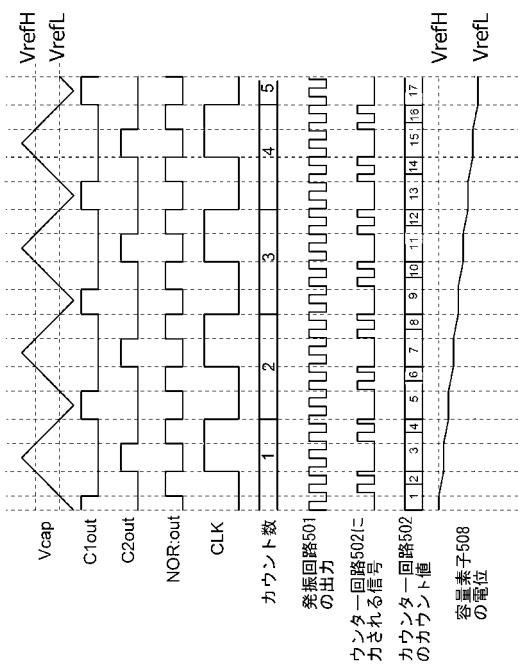

図 5 (A) に示すパルス出力回路 110 の動作についてタイミングチャートを使って図 6 で説明する。なお図 6において、期間 601 は、光電変換素子に照射される光が小さい場合について説明する期間である。また期間 602 は、光電変換素子に照射される光が大きい場合について説明する期間である。

#### 【0039】

図 6 に示すタイミングチャートでは、発振回路 501 の出力、スイッチ 111 のオンまたはオフ、カウンター回路 502 に入力される信号、カウンター回路 502 のカウント値、カウンター回路 502 の出力について示している。図 6 に示すように、発振回路 501 の出力は、一定の周波数の信号を出力する。スイッチ 111 は、NOR 回路 107 に入力される信号に応じて、オンまたはオフを繰り返す。図 6 の説明ではオンまたはオフを交互に繰り返す例について示している。カウンター回路 502 に入力される信号は、スイッチ 111 がオンしている期間にのみ発振回路 501 の出力と同じになる信号である。カウンター回路 502 のカウント値は 1 から N (N は任意の自然数) まで、カウンター回路 502 に入力される信号の波数に応じてカウンターをインクリメントする。カウンター回路 502 の出力は、カウンター回路 502 のカウント値が N までカウントした際にパルスを出し、パルス出力回路 110 のパルス Sout とするものである。

#### 【0040】

上記説明したように、期間 601 は光電変換素子に照射される光が小さい場合について説明する期間であり、期間 602 は光電変換素子に照射される光が大きい場合について説明する期間である。そのため、図 4 で説明したように、バンドギャップリファレンスからのずれが、期間 602 のほうが期間 601 より大きくなり、補正する期間が増えることとなる。図 6 に示すようにスイッチ 111 のオンまたはオフを制御することで、パルス出力回路 110 から出力される信号をランプ波形信号に応じて停止させ、ばらつきを制御することができる。

#### 【0041】

図 5 (B) に示すパルス出力回路 110 は、定電流回路 503、トランジスタ 505 及びトランジスタ 506 とで構成されるカレントミラー回路 504、スイッチ 111、トランジスタ 507、容量素子 508、コンパレータ 509 を有する。定電流回路 503 は、定電流を生成する回路である。また、トランジスタ 505 及びトランジスタ 506 とで構成されるカレントミラー回路 504 は、定電流回路 503 の定電流の大きさに応じて、容量素子 508 の放電を制御するための回路である。トランジスタ 507 は、第 2 の電位 VrefH により容量素子 508 を充電するためのタイミングを、リセット信号 Vreset で制御するための素子である。なお図 5 (B) においてトランジスタ 507 は、p チャネル型

10

20

30

40

50

トランジスタで示しているが、スイッチでもよい。容量素子 508 は充電または放電されることにより、コンパレータ 509 に電気的に接続されるノードの電位を得るためのものである。またコンパレータ 509 は、容量素子 508 が接続されたノードの電位と、第 1 の電位  $V_{refL}$  を比較し、第 1 の電位  $V_{refL}$  が高い場合に、H 信号を出力するための回路である。

#### 【0042】

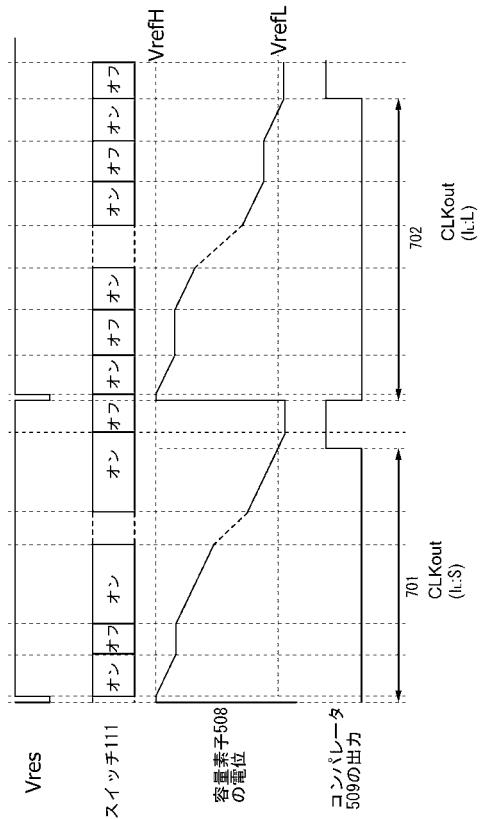

図 5 (B) に示すパルス出力回路 110 の動作を、図 7 のタイミングチャートを使って説明する。なお図 7において、期間 701 は、光電変換素子に照射される光が小さい場合について説明する期間である。また期間 702 は、光電変換素子に照射される光が大きい場合について説明する期間である。

10

#### 【0043】

図 7 に示すタイミングチャートでは、トランジスタ 507 のオンまたはオフを制御するリセット信号  $V_{res}$  の電位、スイッチ 111 のオンまたはオフ、容量素子 508 の電位、コンパレータ 509 の出力について示している。図 7 に示すように、リセット信号  $V_{res}$  がトランジスタ 507 をオンにする電位となると、容量素子 508 が第 2 の電位  $V_{refH}$  によって充電されるため、容量素子 508 が接続されたノードの電位が上昇する。スイッチ 111 は、NOR 回路 107 に入力される信号に応じて、オンまたはオフを繰り返す。図 7 の説明ではオンまたはオフを交互に繰り返す例について示している。第 2 の電位  $V_{refH}$  に充電された容量素子 508 が接続されたノードの電位は、スイッチ 111 がオンになる毎に放電がなされ、低下していく。スイッチ 111 がオフの場合には、容量素子 508 の放電が止まり、電位の変化はない。容量素子 508 が接続されたノードの電位が低下し第 1 の電位  $V_{refL}$  を下回ると、コンパレータ 509 の出力が反転することでパルスを出力し、パルス出力回路 110 のパルス  $S_{out}$  とするものである。

20

#### 【0044】

上記説明したように、期間 701 は光電変換素子に照射される光が小さい場合について説明する期間であり、期間 702 は光電変換素子に照射される光が大きい場合について説明する期間である。そのため、図 4 で説明したように、バンドギャップリファレンスからのずれが、期間 702 のほうが期間 701 より大きくなり、補正する期間が増えこととなる。図 7 に示すようにスイッチ 111 のオンまたはオフを制御することで、図 6 と同様に、パルス出力回路 110 から出力される信号を、ランプ波形信号に応じて停止させ、ばらつきを制御することができる。

30

#### 【0045】

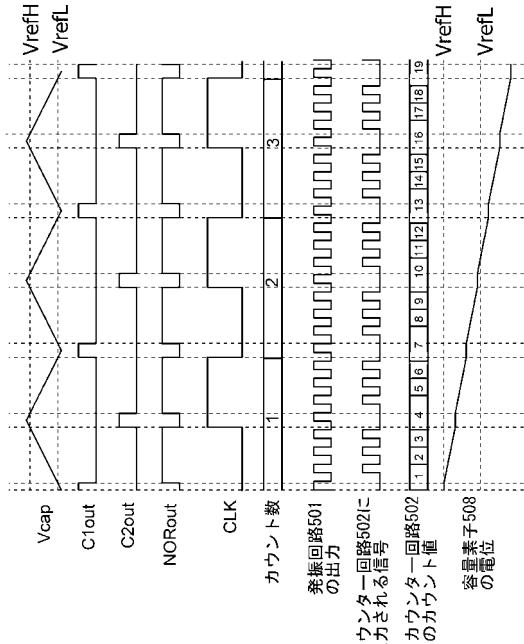

次に図 8、図 9 を用いて、上記図 1 乃至図 7 で説明した回路、及び各回路からの信号についてのタイミングチャートを示す。図 8、図 9 のタイミングチャートは、ランプ波形出力回路 103 より出力されるランプ波形信号の電位  $V_{cap}$ 、第 1 のコンパレータ 104 の出力信号  $C_{1out}$ 、第 2 のコンパレータ 105 の出力信号  $C_{2out}$ 、NOR 回路 107 の出力信号  $NOR_{out}$ 、フリップフロップ回路 106 の Q 端子の出力であるクロック信号  $C_{LK}$ 、カウンター回路 108 でのカウント数、発振回路 501 の出力、カウンター回路 502 に入力される信号、カウンター回路 502 のカウント値、及び容量素子 508 の電位について示している。

40

#### 【0046】

なお図 8 は、光電変換素子に照射される光が小さい場合について説明するものである。また図 9 は、光電変換素子に照射される光が大きい場合について説明するものである。

#### 【0047】

図 8、図 9 に示すタイミングチャートにおいて、ランプ波形信号の電位  $V_{cap}$  に応じて、第 1 のコンパレータ 104 の出力信号  $C_{1out}$  及び第 2 のコンパレータ 105 の出力信号  $C_{2out}$  が動作する。そして、NOR 回路 107 の出力信号  $NOR_{out}$  及びクロック信号が output されることとなる。カウンター回路 108 でのカウントは、パルス出力回路 110 からのパルスで制御される。パルス出力回路 110 は、NOR 回路 107 からの出力信号に応じてパルス出力回路 110 内のスイッチ 111 がオンまたはオフになるため

50

、図5( A )、( B )、図6、及び図7で説明したように、パルス出力回路110の出力を得ることができる。

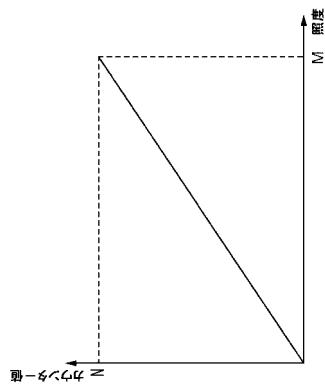

#### 【0048】

また図10に横軸に照度、縦軸にカウント値とした際の関係をグラフにして示す。図10に示すように、照度の増加に伴い、カウント値は増加する右上がりのグラフとなる。なお照度Mの上限としては、人間の視感度を考慮して、10万ルクス程度に設定することが好みしい。カウント値Nは、ビット数に応じて設定されるものである。

#### 【0049】

上記照度と出力電圧となるカウント値の関係が、照度の増加によって出力電圧も増加する右上がりのグラフだと、照度に応じて出力電圧が飽和する。そのため、上限の照度に応じた出力電圧を決めることで、照度の検出範囲を設定することができる。10

#### 【0050】

以上説明したように本実施の形態の光電変換装置の構成では、寄生容量等に起因した回路遅延の影響を受けることなく、照度に応じた周波数のランプ波形を有する信号をデジタル信号に変換することができる。

#### 【0051】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0052】

##### (実施の形態2)

20

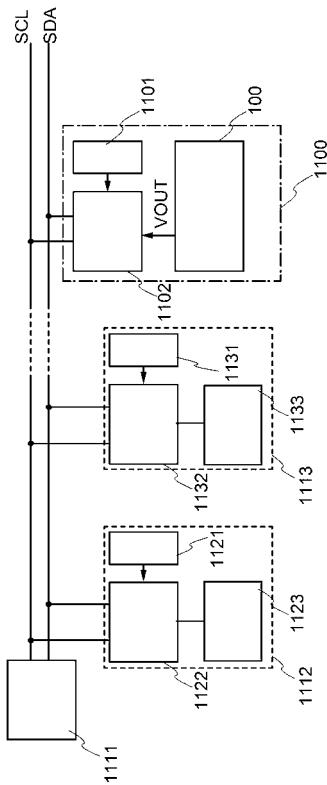

本実施の形態では、上記実施の形態で説明した光電変換装置に加え、デジタル信号が出力される外部の回路を加えたブロック図の構成について図11、図12を用いて説明する。

#### 【0053】

図11に示すデジタル出力型のフォトIC1100は、図1で示した光電変換装置100、アドレスメモリ1101、I2C(Inter Integrated circuit)インターフェース回路1102を有する。また、I2Cインターフェース回路1102は、他の装置とのデータ通信のためのシリアルデータライン(SDA)と、他の装置との間のデータ通信を制御及び同期化するためのシリアルクロックライン(SCL)と、からなるI2Cバスによって外部装置と電気的に接続されている。SDAとSClからなるI2Cバスは、各装置に設けられるアドレスメモリに割り振られた固有のアドレスによって、マイクロコンピュータ1111からの制御を行うためのバス規格である。なお他の装置が液晶表示装置である場合には、一例として、アドレスメモリ1121、I2Cインターフェース回路1122、ロジック部1123を有するディスプレイドライバー1112、アドレスメモリ1131、I2Cインターフェース回路1132、ロジック部1133を有するLEDドライバー1113がI2Cバスに電気的に接続される構成となる。他の装置がEL素子を具備する表示装置の場合には、バックライトであるLEDの制御を行うLEDドライバーは必ずしも必要ない。30

#### 【0054】

なお、光電変換装置100で変換されたデジタル信号は、I2Cインターフェース回路1102を介して、LEDドライバー1113等の他の外部装置に送られる。LEDドライバー1113は、フォトIC1100で得られた照度に関するデジタル信号に応じて、表示装置のバックライトであるLEDを制御するための信号を生成し、出力するものである。

40

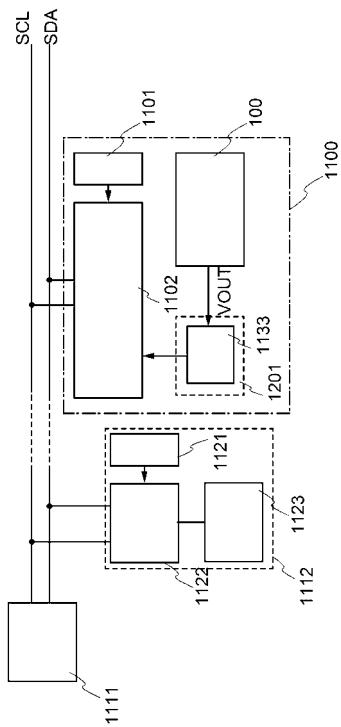

#### 【0055】

また図11に示したデジタル出力型のフォトIC1100について、別の構成を図12に示す。図12で示すフォトIC1100は、光電変換装置100に加え、アドレスメモリ1101、I2Cインターフェース回路1102、LEDドライバー1201を有する。また、I2Cインターフェース回路1102は、SDAと、SClと、からなるI2Cバスによってディスプレイドライバー1112と電気的に接続されている。図12に示す構成が、図11と異なる点はフォトIC1100の内部にロジック部1133を有するLE50

D ドライバー 1201 とする点にある。LED ドライバー 1201 をフォト I C 1100 の内部に設ける構成とすることにより、光電変換装置 100 で生成されたデジタル信号を直接 LED ドライバー 1201 で受け取り、I 2C インターフェース回路 1102 より出力することができるため、回路の共通化を図ることができるため、小型化及び高付加価値化を図ることができる。

#### 【 0056 】

なお図 11、図 12において、各回路のインターフェースは、一例として、デジタルシリアルインターフェースの一つである I 2C インターフェースを用いる構成について示した。なお I 2C バス以外に、ユニバーサルシリアルバス (Universal Serial Bus) 、シリアル周辺インターフェース (Serial Peripheral Interface) 等のバス規格を用いることが可能である。10

#### 【 0057 】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【 0058 】

##### ( 実施の形態 3 )

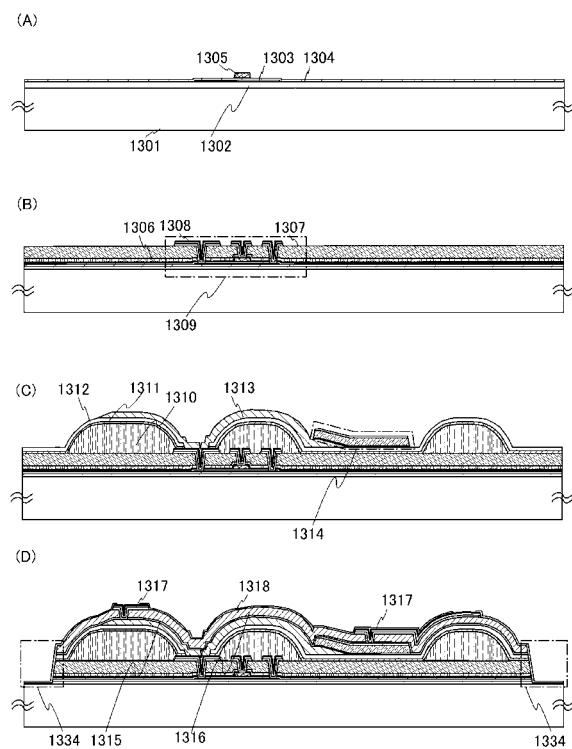

本実施の形態では、本発明の一態様の光電変換装置の作製方法について図 13、図 14 を用いて述べる。なお、本実施の形態では、光電変換装置の各回路を構成する素子である薄膜トランジスタ (TFT) と、光電変換素子である縦型接合タイプの PIN フォトダイオード (以下、フォトダイオードともいう) とを具備する光電変換装置の一例を示す。なお本発明の一態様の光電変換装置は、TFT 及び PIN フォトダイオードの他に、記憶素子、抵抗、ダイオード、容量、インダクタなども用いることがある。また、本発明の一態様の光電変換装置は、縦型接合タイプの PIN フォトダイオードの代わりに、縦型接合タイプの PN フォトダイオードを用いていても良い。20

#### 【 0059 】

まず、透光性を有する基板 1301 上にフォトダイオード及び薄膜トランジスタを形成する。ここでは基板 1301 として、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板等を用いることができる。基板上に形成するトランジスタとして、薄膜トランジスタを用いることにより、基板上に、フォトダイオードと薄膜トランジスタを同一工程で作製することができるため、光電変換装置の量産化がしやすいといった利点がある。30

#### 【 0060 】

次いで、プラズマ CVD 法で下地絶縁膜 1302 となる窒化酸化珪素膜 (膜厚 140 nm) 、酸化窒化珪素膜 (膜厚 100 nm) を順に積層して形成し、さらに大気にふれることなく、半導体膜例えば水素を含む非晶質珪素膜 (膜厚 50 nm) を積層形成する。なお、窒化酸化珪素膜は、ガラス基板からのアルカリ金属などの不純物拡散を防止するブロック層として機能する。

#### 【 0061 】

なお、酸化窒化珪素膜とは、その組成として、窒素よりも酸素の含有量が多い膜であって、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) 及び水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合に、濃度範囲として酸素が 50 ~ 70 原子%、窒素が 0.5 ~ 1.5 原子%、珪素が 2.5 ~ 3.5 原子%、水素が 0.1 ~ 1.0 原子% の範囲で含まれる膜をいう。また、窒化酸化珪素膜とは、その組成として、酸素よりも窒素の含有量が多い膜であって、RBS 及び HFS を用いて測定した場合に、濃度範囲として酸素が 5 ~ 30 原子%、窒素が 20 ~ 55 原子%、珪素が 2.5 ~ 3.5 原子%、水素が 1.0 ~ 2.5 原子% の範囲で含まれる膜をいう。但し、酸化窒化珪素または窒化酸化珪素を構成する原子の合計を 100 原子%としたとき、窒素、酸素、珪素及び水素の含有比率が上記の範囲内に含まれるものとする。40

#### 【 0062 】

10

20

30

40

50

次いで、上記非晶質珪素膜を公知の技術（固相成長法、レーザ結晶化方法、触媒金属を用いた結晶化方法など）により結晶化させて、結晶構造を有する半導体膜（結晶性半導体膜）、例えば多結晶珪素膜を形成する。

#### 【0063】

次いで、得られた結晶構造を有する半導体膜（例えば結晶性珪素膜）上に、第1のフォトマスクを用いてレジストからなるマスクを形成し、所望の形状にエッチング処理して島状に分離された半導体膜（本明細書では「島状半導体領域1303」という）を形成する。島状半導体領域を形成した後、レジストからなるマスクを除去する。

#### 【0064】

次いで、必要があればTFTのしきい値を制御するために微量な不純物元素（ホウ素またはリン）のドーピングを行う。ここでは、ジボラン（B<sub>2</sub>H<sub>6</sub>）を質量分離しないでプラズマ励起したイオンドープ法を用いる。10

#### 【0065】

次いで、ゲート絶縁膜1304となる珪素を主成分とする絶縁膜を形成する。ここでは、プラズマCVD法により30nmの厚さで酸化窒化珪素膜を形成する。

#### 【0066】

次いで、ゲート絶縁膜1304上に導電膜を形成した後、第2のフォトマスクを用いて、ゲート電極1305を形成する（図13（A）参照）。この導電膜として、例えば窒化タンタル及びタンゲステン（W）をそれぞれ30nm、170nm積層した膜を用いる。20

#### 【0067】

また、ゲート電極1305して、上記以外にもチタン（Ti）、タンゲステン（W）、タンタル（Ta）、モリブデン（Mo）、ネオジム（Nd）、コバルト（Co）、ジルコニア（Zr）、亜鉛（Zn）、ルテニウム（Ru）、ロジウム（Rh）、パラジウム（Pd）、オスミウム（Os）、イリジウム（Ir）、白金（Pt）、アルミニウム（Al）、金（Au）、銀（Ag）、銅（Cu）から選ばれた元素、または前記元素を主成分とする合金材料若しくは化合物材料からなる単層膜、或いは、これらの窒化物、例えば、窒化チタン、窒化タンゲステン、窒化タンタル、窒化モリブデンからなる単層膜を用いることができる。

#### 【0068】

次いで、島状半導体領域1303への一導電型を付与する不純物の導入を行って、TFTのソース領域またはドレイン領域の形成を行う。本実施の形態では一例として、nチャネル型TFTを形成するので、n型の不純物、例えばリン（P）、砒素（As）を島状半導体領域1303に導入する。pチャネル型TFTを形成する際には、p型の不純物を島状半導体領域1303に導入する。30

#### 【0069】

次いで、第1の層間絶縁膜として酸化窒化珪素膜（膜厚50nm：図示しない）、窒化酸化珪素膜1306（膜厚165nm）、酸化窒化珪素膜1307（膜厚600nm）を形成する。

#### 【0070】

次に、熱処理（300～550℃で1～12時間の熱処理、例えば窒素雰囲気中410℃で1時間）を行い、島状半導体膜を水素化する。この工程は酸化窒化珪素膜に含まれる水素により島状半導体膜のダンギリングボンドを終端させるために行うものである。40

#### 【0071】

次いで、第3のフォトマスクを用いてレジストからなるマスクを形成し、第1の層間絶縁膜及びゲート絶縁膜1304を選択的にエッチングしてコンタクトホールを形成する。そして、レジストからなるマスクを除去する。

#### 【0072】

次いで、スパッタ法で導電積層膜を成膜した後、第4のフォトマスクを用いてレジストからなるマスクを形成し、選択的に導電積層膜をエッチングして、第1の配線1308を形成する（図13（B）参照）。そして、レジストからなるマスクを除去する。なお、本実50

施の形態の導電膜は、膜厚100nmのTi膜と、膜厚100nmのAl膜と、膜厚50nmのTi膜との3層を積層したものとする。

#### 【0073】

以上の工程で、多結晶珪素膜を用いたトップゲート型TFT1309を作製することができる。

#### 【0074】

次いで、第1の層間絶縁膜及び第1の配線1308上に、第2の層間絶縁膜として有機樹脂1310（膜厚1.5μm）を形成する。有機樹脂1310は、ポリイミドを用い、他にもアクリル、ベンゾシクロブテン、ポリアミド、エポキシ等の、耐熱性を有する有機材料を用いることで形成すればよい。そして有機樹脂1310上に、第5のフォトマスクを用いてレジストからなるマスクを形成し、選択的にエッチングする。そして、レジストからなるマスクを除去する。10

#### 【0075】

次いで、有機樹脂1310上に、窒化珪素膜1311（膜厚100nm）、酸化珪素膜1312（膜厚200nm）を順に形成する。窒化珪素膜1311及び酸化珪素膜1312は、第6のフォトマスクを用いてレジストからなるマスクを形成し、選択的にエッチングする。そして、レジストからなるマスクを除去する。酸化珪素膜1312は、シランと酸素、TEOS（テトラエトキシシラン）と酸素等の組み合わせの混合ガスを用い、熱CVD、プラズマCVD、常圧CVD、バイアスECR CVD等の方法によって形成することができる。また、窒化珪素膜1311は、代表的には、シランとアンモニアの混合ガスを用い、プラズマCVDによって形成することができる。20

#### 【0076】

次いで、第2の層間絶縁膜上及び第1の配線1308上に、Ti膜からなる導電膜を成膜した後、第7のマスクを用いてレジストからなるマスクを形成し、選択的に導電膜をエッチングして、第2の配線1313を形成する。なお、第2の配線1313は、ハーフトーン露光技術等を用いて、その端部がテーパー形状になるようにエッチングする。

#### 【0077】

次いで、第2の層間絶縁膜上及び第2の配線1313上に、フォトダイオードで構成される光電変換素子1314を形成する（図13（C）参照）。ここでは、光電変換素子1314をP型の導電性を示す層（膜厚60nm）、I型の導電性を示す層（膜厚400nm）、およびN型の導電性（膜厚80nm）を示す層でなる3層構造の非晶質珪素膜で形成する。光電変換素子1314は、3層構造の非晶質珪素膜を形成し、第8のマスクを用いてレジストからなるマスクを形成し、選択的にエッチングする。そして、レジストからなるマスクを除去する。30

#### 【0078】

なお、1枚の基板1301上には、複数の光電変換装置が同じ工程を経ることにより、同時に作製される。そのため、複数の光電変換装置の大きさに応じて基板1301を分断する必要がある。分割した後の光電変換装置の側面を不純物が侵入することを防止するため、図13（D）に示すように、光電変換装置の側面となる領域1334（一点鎖線で示す部分）の下地絶縁膜1302の窒化酸化珪素膜上に形成される積層膜を除去する。この工程は、第9のマスクを用いてレジストからなるマスクを形成し、選択的にエッチング処理をすることにより行われる。そして、レジストからなるマスクを除去する。40

#### 【0079】

次に、下地絶縁膜1302の窒化酸化珪素膜、第2の層間絶縁膜の酸化珪素膜1312、第2の配線1313、及び光電変換素子1314上に、第3の層間絶縁膜として窒化珪素膜1315（膜厚100nm）、酸化珪素膜1316（膜厚400nm）を順に形成する。窒化珪素膜1315及び酸化珪素膜1316は、第10のフォトマスクを用いてレジストからなるマスクを形成し、選択的にエッチングする。そして、レジストからなるマスクを除去する。

#### 【0080】

10

20

30

40

50

次いで、第3の層間絶縁膜上、第2の配線1313上、及び光電変換素子1314上に、導電積層膜を成膜した後、第11のマスクを用いてレジストからなるマスクを形成し、選択的に導電積層膜をエッティングして、第3の配線1317を形成する。なお、本実施の形態の導電膜は、膜厚50nmのTi膜と、膜厚100nmのAl膜と、膜厚50nmのTi膜との3層を積層したものとする。

#### 【0081】

次いで、第3の層間絶縁膜の酸化珪素膜1316上、第3の配線1317上、及び光電変換装置の側面となる領域1334に、窒化珪素膜1318（膜厚100nm）を形成する（図13（D）参照）。窒化珪素膜1318は、第12のフォトマスクを用いてレジストからなるマスクを形成し、選択的にエッティングする。そして、レジストからなるマスクを除去する。

10

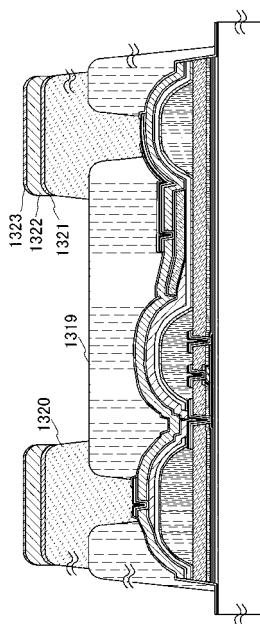

#### 【0082】

次いで、絶縁樹脂膜1319（膜厚25μm）を形成する。絶縁樹脂膜1319により、TFT1309を含む層の上面および側面が封止される。絶縁樹脂膜1319は、印刷法により、感光性のエポキシ・フェノール系樹脂膜を形成する。なお絶縁樹脂膜1319には、光電変換装置からの信号の入出力を行うための開口部が設けられている。

#### 【0083】

次に、絶縁樹脂膜1319上に、光電変換装置の端子電極を形成する。まず、1層目の導電膜1320として、ニッケル粒子を含む導電性ペーストを用いて、スクリーン印刷法により厚さ15μm程度に形成する。

20

#### 【0084】

導電性ペーストは、樹脂でなるバインダーに導電粒子、または導電の粉体が分散している材料である。このような導電性ペーストを固化することで、導電性樹脂膜が形成される。よって、1層目の導電膜1320は導電性樹脂膜で構成されているため、ハンダとの密着性に乏しい。そこで、端子電極とハンダとの密着性を高めるため、1層目の導電膜1320の上面にメタルマスクを用いたスパッタ法で、所定の形状の導電膜を形成する。一例としては、1層目の導電膜1320上に、チタン膜1321（膜厚150nm）、ニッケル膜1322（膜厚750nm）、金（Au）膜1323（膜厚50nm）を順次積層して形成する（図14参照）。

#### 【0085】

30

なお、光電変換装置は、基板1301を切断し、1つずつの光電変換装置に分割される。基板1301の切断は、ダイシング法、レーザカット法などを用いることができる。

#### 【0086】

以上の工程で、光電変換装置を作製することができる。

#### 【0087】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【0088】

##### （実施の形態4）

本発明の一態様の光電変換装置は、寄生容量等に起因した回路遅延の影響を受けることなく、照度に応じた周波数のランプ波形を有する信号によりデジタル信号を出力することのできるといった特徴を有している。よって、本発明の一態様の光電変換装置を具備する電子機器は、光電変換装置をその構成要素に追加することに伴って、電子機器での照度の検出を精度良く行うことができ、視認性の向上及び消費電力の低減を図ることができる。本発明の一態様の光電変換装置は、表示装置、ノート型パソコンコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様の光電変換装置を用いることができる電子機器として、携帯電話、携帯型ゲーム機または電子書籍、ビデオカメラ、デジタルスチルカメラなどのカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーシ

40

50

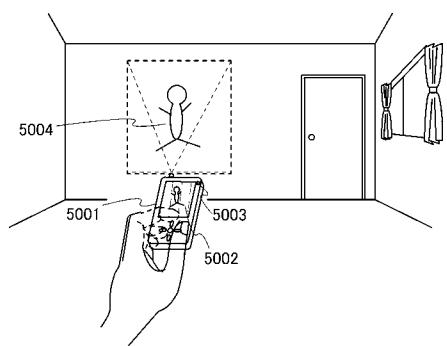

ヨンシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、などが挙げられる。これら電子機器の具体例を図15に示す。

#### 【0089】

図15(A)は表示装置であり、筐体5001、表示部5002、センサ部5003等を有する。本発明の一態様の光電変換装置は、センサ部5003に用いることができる。センサ部5003は外光の照度を検知する。表示装置は、検知した照度に合わせて、表示部5002の輝度のコントロールを行うことができる。照度に合わせて表示部5002の輝度をコントロールすることで、表示装置の消費電力を抑えることができる。

#### 【0090】

なお図15(A)に表示装置は、MEMS技術等により壁面等に画像5004を投影することもできる。画像5004の輝度もセンサ部5003でコントロールすることができ、表示装置の消費電力を抑えることができる。なお、液晶テレビ表示装置には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示装置が含まれる。

10

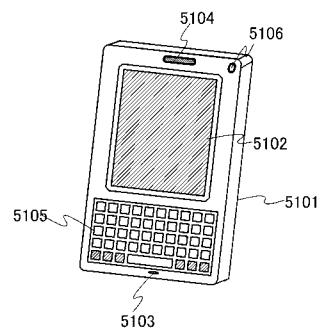

#### 【0091】

図15(B)は携帯電話であり、本体5101、表示部5102、音声入力部5103、音声出力部5104、操作キー5105、センサ部5106等を有する。センサ部5106は外光の強度を検知する。携帯電話は、検知した照度に合わせて、表示部5102または操作キー5105の輝度のコントロールを行うことができる。照度に合わせて表示部5102または操作キー5105の輝度のコントロールすることで、携帯電話の消費電力を抑えることができる。

20

#### 【0092】

なお、本実施の形態において、各々の図で述べた内容は、別の実施の形態で述べた内容に対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

#### 【符号の説明】

#### 【0093】

|     |              |    |

|-----|--------------|----|

| 100 | 光電変換装置       |    |

| 101 | 光電変換素子       |    |

| 102 | 增幅回路         |    |

| 103 | ランプ波形出力回路    | 30 |

| 104 | コンパレータ       |    |

| 105 | コンパレータ       |    |

| 106 | フリップフロップ回路   |    |

| 107 | NOR回路        |    |

| 108 | カウンター回路      |    |

| 109 | ラッチ回路        |    |

| 110 | パルス出力回路      |    |

| 111 | スイッチ         |    |

| 112 | nチャネル型トランジスタ |    |

| 113 | nチャネル型トランジスタ | 40 |

| 200 | 増幅回路         |    |

| 201 | nチャネル型トランジスタ |    |

| 202 | nチャネル型トランジスタ |    |

| 210 | 切り替え回路       |    |

| 211 | スイッチ         |    |

| 212 | スイッチ         |    |

| 301 | pチャネル型トランジスタ |    |

| 302 | pチャネル型トランジスタ |    |

| 303 | pチャネル型トランジスタ |    |

| 304 | pチャネル型トランジスタ | 50 |

|         |                  |    |

|---------|------------------|----|

| 3 0 5   | n チャネル型トランジスタ    |    |

| 3 0 6   | n チャネル型トランジスタ    |    |

| 3 0 7   | n チャネル型トランジスタ    |    |

| 3 0 8   | n チャネル型トランジスタ    |    |

| 3 0 9   | 容量素子             |    |

| 4 0 1   | 期間               |    |

| 4 0 2   | 期間               |    |

| 4 0 3   | 矢印               |    |

| 4 0 4   | 矢印               |    |

| 4 1 0   | 窒素雰囲気中           | 10 |

| 5 0 1   | 発振回路             |    |

| 5 0 2   | カウンター回路          |    |

| 5 0 3   | 定電流回路            |    |

| 5 0 4   | カレントミラー回路        |    |

| 5 0 5   | トランジスタ           |    |

| 5 0 6   | トランジスタ           |    |

| 5 0 7   | トランジスタ           |    |

| 5 0 8   | 容量素子             |    |

| 5 0 9   | コンパレータ           |    |

| 6 0 1   | 期間               | 20 |

| 6 0 2   | 期間               |    |

| 7 0 1   | 期間               |    |

| 7 0 2   | 期間               |    |

| 1 1 0 0 | フォトI C           |    |

| 1 1 0 1 | アドレスメモリ          |    |

| 1 1 0 2 | I 2 C インターフェース回路 |    |

| 1 1 1 1 | マイクロコンピュータ       |    |

| 1 1 1 2 | ディスプレイドライバー      |    |

| 1 1 1 3 | L E D ドライバー      |    |

| 1 1 2 1 | アドレスメモリ          | 30 |

| 1 1 2 2 | I 2 C インターフェース回路 |    |

| 1 1 2 3 | ロジック部            |    |

| 1 1 3 1 | アドレスメモリ          |    |

| 1 1 3 2 | I 2 C インターフェース回路 |    |

| 1 1 3 3 | ロジック部            |    |

| 1 2 0 1 | L E D ドライバー      |    |

| 1 3 0 1 | 基板               |    |

| 1 3 0 2 | 下地絶縁膜            |    |

| 1 3 0 3 | 島状半導体領域          |    |

| 1 3 0 4 | ゲート絶縁膜           | 40 |

| 1 3 0 5 | ゲート電極            |    |

| 1 3 0 6 | 窒化酸化珪素膜          |    |

| 1 3 0 7 | 酸化窒化珪素膜          |    |

| 1 3 0 8 | 配線               |    |

| 1 3 0 9 | T F T            |    |

| 1 3 1 0 | 有機樹脂             |    |

| 1 3 1 1 | 窒化珪素膜            |    |

| 1 3 1 2 | 酸化珪素膜            |    |

| 1 3 1 3 | 配線               |    |

| 1 3 1 4 | 光電変換素子           | 50 |

|         |          |

|---------|----------|

| 1 3 1 5 | 窒化珪素膜    |

| 1 3 1 6 | 酸化珪素膜    |

| 1 3 1 7 | 配線       |

| 1 3 1 8 | 窒化珪素膜    |

| 1 3 1 9 | 絶縁樹脂膜    |

| 1 3 2 0 | 導電膜      |

| 1 3 2 1 | チタン膜     |

| 1 3 2 2 | ニッケル膜    |

| 1 3 2 3 | 金 (Au) 膜 |

| 1 3 3 4 | 領域       |

| 5 0 0 1 | 筐体       |

| 5 0 0 2 | 表示部      |

| 5 0 0 3 | センサ部     |

| 5 0 0 4 | 画像       |

| 5 1 0 1 | 本体       |

| 5 1 0 2 | 表示部      |

| 5 1 0 3 | 音声入力部    |

| 5 1 0 4 | 音声出力部    |

| 5 1 0 5 | 操作キー     |

| 5 1 0 6 | センサ部     |

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

## 【図 1 5】

(A)

(B)

---

フロントページの続き

(56)参考文献 特開2004-325409(JP,A)

特開2006-133135(JP,A)

特開昭58-095423(JP,A)

特開平06-095218(JP,A)

特開2009-250842(JP,A)

実開昭64-015973(JP,U)

特公昭63-034968(JP,B1)

特公昭62-000614(JP,B1)

(58)調査した分野(Int.Cl., DB名)

H01L 31/10 - 31/119

H03M 1/00 - 1/88

G01J 1/00 - 1/60, 11/00