(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4846571号

(P4846571)

(45) 発行日 平成23年12月28日(2011.12.28)

(24) 登録日 平成23年10月21日(2011.10.21)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/20 (2006.01)G09G 3/36

G09G 3/20 621M

G09G 3/20 633P

G09G 3/20 631A

G09G 3/20 631H

請求項の数 16 (全 43 頁) 最終頁に続く

(21) 出願番号 特願2006-513274 (P2006-513274)

(86) (22) 出願日 平成16年4月23日 (2004.4.23)

(65) 公表番号 特表2006-524844 (P2006-524844A)

(43) 公表日 平成18年11月2日 (2006.11.2)

(86) 國際出願番号 PCT/US2004/012643

(87) 國際公開番号 WO2004/097506

(87) 國際公開日 平成16年11月11日 (2004.11.11)

審査請求日 平成19年4月18日 (2007.4.18)

(31) 優先権主張番号 60/465,364

(32) 優先日 平成15年4月24日 (2003.4.24)

(33) 優先権主張国 米国(US)

(73) 特許権者 593026188

ディスプレイテック、インコーポレイテッド

Displaytech, Incorporated

アメリカ合衆国 コロラド 80503-

7603, ロングモント, クローバー ベ

イシン ドライブ 2602

2200 Central Avenue

, Suite A, Boulder,

Colorado 80301, United States of America

(74) 代理人 100068755

弁理士 恩田 博宣

最終頁に続く

(54) 【発明の名称】微小表示装置システム及び画像を表示する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

異なった表示状態間を切換え可能な画素のアレイを有する、半導体基板上に存在する微小表示装置と、

該半導体基板に同じく存在し、第1のフォーマットでデジタル画像データを受信し、かつ、第2のフォーマットで前記微小表示装置の画素に前記デジタル画像データを供給し、前記第1のフォーマットは標準ビデオ信号である、デジタル・インターフェイス・デバイスと、

からなる画像データを表示するための微小表示装置システムであって、

前記第1のフォーマットは、第1の画素に対するRGBデータを含み、次に第2の画素に対するRGBデータが続き、そしてRGB画素データの行全体が供給されるまで順次継続し、その後にRGB画素データの別の行が同様に続き、

前記第2のフォーマットは、第1の色、第2の色、および、第3の色の順次フィールドを含み、

前記微小表示装置は表示される画像データを保存するためのメモリ・セルを備え、同メモリ・セルは前記画素アレイ全体に分散しており、

前記分散したメモリ・セルは、特定の画素と機能的に接続されるが、同特定の画素内に、または、同特定の画素に隣接して必ずしも所在するわけではなく、

前記微小表示装置は、複数の画素を支援する集中型タイミング回路を含み、同集中型タイミング回路は、前記複数の画素の各画素に対してランプ・カウンタ信号と所望の画素値

10

20

との間で比較を行い、これに基づき、各画素に対する独立した画素状態信号を各画素に送出する、

微小表示装置システム。

【請求項 2】

前記デジタル・インターフェイス・デバイスは、RGBデータを、輝度成分および少なくとも2つの色成分を有するデータ・フォーマットに変換する請求項1に記載の微小表示装置システム。

【請求項 3】

前記微小表示装置は、輝度成分および少なくとも2つの色成分を有する前記データ・フォーマットにおいて前記画像データを保存すべく該微小表示装置内に所在するメモリ・セルを含む請求項2に記載の微小表示装置システム。10

【請求項 4】

輝度データは各画素に対して保存され、色データは複数の画素のグループに対して保存される請求項3に記載の微小表示装置システム。

【請求項 5】

前記分配されたメモリ・セルは前記画素アレイとは共存されるが、該画素アレイ内の特定の画素とは物理的に接続されていない請求項1に記載の微小表示装置システム。

【請求項 6】

各画素は反射性画素電極を含み、同反射性画素電極は第1の平面内にあり、かつ、前記分配されたメモリ・セルは該第1の平面に平行な第2の平面内にあり、さらに、該反射性画素電極の少なくともいくつかの該第2の平面上への直角な投影は、別の反射性画素電極に対する画像情報を保存するメモリ・セルを覆う請求項5に記載の微小表示装置システム。20

【請求項 7】

照明装置、および、前記半導体基板に装着しているビームスプリッタ・アセンブリをさらに含む請求項1に記載の微小表示装置システム。

【請求項 8】

前記微小表示装置は各画素に対する画像データの2つの連続したフレームを保存するための二連メモリ・バッファを含む請求項1に記載の微小表示装置システム。

【請求項 9】

該微小表示装置は表示される画像データを保存するための、低電力SRAMのメモリ・セルを含む請求項1に記載の微小表示装置システム。30

【請求項 10】

該微小表示装置の各画素は画素電極を含み、該画素は、画素電圧源が、該微小表示装置の残り部分を駆動するために使用される論理電圧源により供給される電圧とは異なった大きさの電圧を、選択された画素電極に供給するために使用されることを可能にする回路、を含む請求項1に記載の微小表示装置システム。

【請求項 11】

特定の微小表示装置システムに固有の情報を保存し、それにより、該微小表示装置は該保存された情報を利用可能であり、かつ、該情報に基づき、該微小表示装置システムにより表示される画像の品質を向上する、該微小表示装置に接続された不揮発性メモリ、を含む請求項1に記載の微小表示装置システム。40

【請求項 12】

前記微小表示装置における該画素のアレイは行に配列され、該行の第1の部分は1つのグループ内にあり、該行の第2の部分は第2のグループ内にあり、さらに、該第1および該第2のグループの1つのグループの該画素は画像情報を使用して頂部行から底部行に更新される一方、該第1および該第2のグループの別のグループの該画素は画像情報を使用して底部行から頂部行に更新される、請求項1に記載の微小表示装置システム。

【請求項 13】

前記微小表示装置は表示される画像データを保存するためのメモリ・セルを含み、該メ50

モリ・セルは該微小表示装置全体を通じて分配され、該分配されたメモリ・セルは該画素アレイと同位置に存在するが、該画素アレイの特定の画素に物理的には接続されておらず、かつ、さらに、各画素は反射性画素電極を含み、該反射性画素電極は第1の平面内にあり、かつ、該分配されたメモリ・セルは該第1の平面に平行である第2の面内にあり、さらに、該反射性画素電極の少なくともいくつかの該第2の平面上への直角投影は、別の反射性画素電極に対する画像情報を保存しているメモリ・セルを覆っている、請求項1に記載の微小表示装置システム。

【請求項14】

各画素は内部に回路を有し、該回路は該画素に動作可能に接続され、該画素の内部の、かつ、該画素と動作可能に接続された該回路は複数のトランジスタを含み、該回路中には700未満のトランジスタが存在する請求項1に記載の微小表示装置システム。 10

【請求項15】

各画素は表示表面を有し、各画素は該画素の今後の表示状態に関する情報を含む該画素に動作可能に接続された少なくとも1つのメモリ・レジスタを有する微小表示装置と、

各画素および該画素に動作可能に接続された少なくとも1つのメモリ・レジスタにより占められた半導体基板上の表面積は1,000平方ミクロン未満である、請求項1に記載の微小表示装置システム。

【請求項16】

半導体基板上に存在するデジタル・インターフェイスにおいて、第1のフォーマットでデジタル画像データを受信する工程と、 20

前記半導体基板上に同じく存在する微小表示装置の画素に対し、第2のフォーマットで前記デジタル画像データを供給する工程と、

前記微小表示装置の画素のアレイにおける一部の画素を、異なった表示状態間で切換える工程と、

を含む、画像を表示する方法であって、

前記第1のフォーマットは、第1の画素に対するRGBデータを含み、次に第2の画素に対するRGBデータが続き、そしてRGB画素データの行全体が供給されるまで順次継続し、その後にRGB画素データの別の行が同様に続き、

前記第2のフォーマットは、第1の色、第2の色、および、第3の色の順次フィールドを含み、 30

前記微小表示装置は表示される画像データを保存するためのメモリ・セルを備え、同メモリ・セルは前記画素アレイ全体に分散しており、

前記分散したメモリ・セルは、特定の画素と機能的に接続されるが、同特定の画素内に、または、同特定の画素に隣接して必ずしも所在するわけではなく、

前記微小表示装置は、複数の画素を支援する集中型タイミング回路を含み、同集中型タイミング回路は、前記複数の画素の各画素に対してランプ・カウンタ信号と所望の画素値との間で比較を行い、これに基づき、各画素に対する独立した画素状態信号を各画素に送出する、

画像を表示する方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般に微小表示装置に関し、特には、一緒に設けられた集積化インターフェイス回路を有する微小表示装置システムに関する。

【背景技術】

【0002】

過去数年、微小表示装置は様々な民生用製品の応用例において陰極線管(CRT)に取って代わり始め、かつ、より新しい特定の製品の応用例においては好ましい近接視用表示装置となり始めている。これらの応用例はビデオ・カムコーダ、デジタル静止画カメラ、および、頭部搭載用表示装置の新興領域を含む。これらの微小表示装置は、レンズ系また 50

は何らかの光学的拡大装置を介してユーザにより閲覧され得る、シリコン集積回路の「背面」に形成された極小表示パネルを含む。多くの微小表示装置は、独立した光源により供給される光に対する空間光変調装置として機能することにより、完全カラー画像、単色画像、または、白黒画像を作り出す。空間光変調装置微小表示装置は強誘電性またはネマティック液晶材料などの液晶材料も使用でき、機械式微小鏡もしくは他の適当な光変調技術などの他の技術も利用できる。代替として、微小表示装置はエレクトロルミネセント熒光体または有機発光ダイオード（O L E D）などの発光体から作成された極小発光アレイを使用することにより、同装置自体の光を発光できる。液晶を利用した反射型空間光変調装置の場合、同装置は、特性上、透過型も反射型も可能である。液晶を利用した反射型空間光変調装置の場合、1つの好適な配列は反射型L C O S（シリコン上液晶）として知られている。透過性である液晶変調装置を備えた他の配列は、ポリシリコンまたは非晶質シリコンのいずれかの薄膜トランジスタ（T F T）から作成されるか、または、コパンコーポレーション社（K o p i n C o r p o r a t i o n）の微小表示装置製品により例示される如くのバルク・シリコン・ウェハの「リフト・オフ」された単結晶シリコンから作成された能動マトリクスの背面で形成される。10

#### 【0003】

様々な微小表示装置技術はそれらの技術の駆動電圧要件において大幅に異なる。例えば、エレクトロルミネセント（E L）熒光体表示装置は、画素を完全なオフ状態から完全なオン状態に切り換えるために約80Vの範囲にわたり変化する画素駆動を必要とする。E L微小表示装置は画素駆動装置としての二重拡散されたM O S（D M O S）高電圧トランジスタを使用して組み立てられた背面を使用して、そのような駆動電圧を達成している。ネマティックL C O S表示装置は一般に、5V程度に低い電圧さえ通常は必要としない。強誘電性液晶（F L C）を使用したL C O Sの場合、わずか3.3Vでの画素切換えを使用した微小表示装置製品が、出願人により現在商業的に生産されている。5Vおよび3.3VのL C O S微小表示装置はそれぞれ0.5μmおよび0.35μmの基本ルールを有する標準C M O Sロジック工程で組み立てられた背面を使用して作成されており、この標準C M O Sロジックは十分な画素駆動電圧を供給する。20

#### 【0004】

様々な微小表示装置技術は、それらの技術がどのようにして色を生成するか、においても異なる。それらの技術はフィールド順次方式で、または、三色の組み合わせを備えた画素を使用して3つの色フィールドを同時生成させて、色を生成できる。フィールド順次式カラーは1回に1つの色フィールドのカラー画像を表示することを意味する。例えば、赤フィールドを表示し、これに緑フィールドが続き、青フィールドが続き得る。もしこれらの独立した色フィールドが十分に大きな速度で連続されれば、人間の目／脳はそれらのフィールドを知覚された完全カラー画像に一緒に一体化する。30

#### 【0005】

微小表示装置についてのさらなる問題は濃度階調画像の生成である。微小表示装置背面を従来のシリコン集積回路（I C）として組み立てることは有利である。濃度階調を作成するには、各表示画素が多数の明るさレベルを表示できる必要がある。このことは、アナログ応答画素発光体またはアナログ回路付変調装置を駆動することにより達成できる。アナログ回路に対して特化したシリコン組み立て工程は知られているが、通常、標準デジタル工程より費用がかかる。さらに、アナログ回路の設計は、同様のデジタル回路の設計よりも困難であり、かつ、より大きな手間を必要とする。アナログ回路は、もし慎重に管理されなければ不要な画像擬似信号を生成し得る様々な雑音およびオフセット効果を受けやすい。したがって、純粋なデジタル回路を介して濃度階調を供給することが望ましい。40

#### 【0006】

微小表示装置に適したデジタル駆動を介して濃度階調を生成できるいくつかの技術が当技術分野では知られている。例えば、プラズマ表示装置、エレクトロルミネセント表示装置、発光ダイオード、テキサス・インスツルメンツ社デジタル微小鏡デバイス（T e x a s I n s t r u m e n t s D i g i t a l M i c r o m i r r o r D e v i c e

)、および、他の微小電子機械( M E M S )デバイスに見出されるものなどの高速応答発光体および変調装置、ならびに、強誘電性液晶( F L C )は、明暗動作周期の変化が明白な濃度諧調を生成するために使用される形で、2レベル駆動を使用して駆動できる。このような技術の1つの分類において、画像データは最大有意義ビット( M S B )面から最小有意義ビット( L S B )面の範囲を有する「ビット面」に一般的に分離され、ビット面内の画像データは表示装置上に書き込まれ、かつ、持続時間保持される。したがって、非常に単純な例示において、8ビット単色濃度諧調を表示する画素は1ビデオ・フレームの間に8回書き込まれ、かつ、同じ回数だけ状態を変化させる可能性がある。事実、このような濃度諧調技術は、特に動画の場合に、激しい視覚的擬似信号を生成することが知られている。このような擬似信号の1つの分類は動的偽輪郭形成として知られている。このような擬似信号の削減は、データ処理の増加および画素状態の変化の増加を伴って、上記に与えられた単純な例の複雑な変形を必要とする。さらに、高品質ビデオ画像に通常必要である256の濃度色相などの多数の濃度色相の生成は、画素発光体または変調装置が状態を変化可能でなければならない短いL S B周期をもたらす。3つの順次式カラー・フィールドは、各々が上述の256のレベルを備えた画像からなり、これらのフィールドからの60Hzカラー画像の生成は約22μsである1秒の1/(3×60×255)の短い周期内での切換えを必要とすることがある。強誘電性液晶変調装置などのいくつかのタイプの変調装置に対しては、応答時間をこのように速く維持することは困難であり、特に低温部分においては、ほとんどの表示装置が過度に動作することが予想されている。

## 【0007】

ビット面系の濃度諧調技術はネマティック液晶などのより緩慢に応答する表示材料と共にでも使用できる。この場合、画素は基本となる2レベル電気駆動のR M S(平均自乗根)値に対するアナログ応答を有する。この場合、液晶材料の緩慢な平均演算性は動的偽輪郭形成の発生を防止するが、別の分類の擬似信号が代わりに発生する。隣接した濃度値に駆動された近隣の画素は非常に異なった駆動波形を経験することがある。例えば、8ビット濃度諧調方式において、濃度値128(二進法で10000000)に駆動された画素はビデオ・フレームのほぼ前半に対して高く、かつ、残り部分に対しては低く駆動されることがある一方、濃度値127(二進法で01111111)に駆動された別の画素はビデオ・フレームのほぼ前半に対して低く、かつ、残り部分に対しては高く駆動されることがある。もしこれらの2つの画素が物理的に互いに隣接していれば、それらの画素が円滑に変化する明るさを持つ画像の一部である場合でそうであるように、強い横方向電場がこれら2つの画素間の境界に生成される。この横方向の、または、縁取りする電場はネマティック液晶において回位と呼ばれる欠陥をしばしば生成する。このような回位は、隣接液晶材料に対するしばしばはるかに暗く見える視覚的コントラストを有し、かつ、一旦形成されれば、それらの回位を生成した電気的駆動条件が除かれた時でも消えるのが緩慢である。したがって、ビット面型デジタル駆動を使用して駆動されたネマティック微小表示装置に対して生成された画像における明るさの変化は、画像内容が変更された時にさえ一時的に持続し得る不要な暗線で「装飾」される。

## 【0008】

ビット面型デジタル濃度諧調駆動の上記の短所の多くは、ビデオ・フレーム当たりの駆動遷移の数を低減する代案2状態駆動方式により克服可能である。例えば、パルス幅変調( P W M )駆動方式は、米国特許第5977940号明細書、同第6249269号明細書、同第6329974号明細書、および、同第6525709号明細書に例えれば教示されたように、既に使用されている。これらの例において、各画素は自身の駆動装置を有し、選択されたデジタル値にビデオ・フィールドの開始時に典型的に「リセット」され、かつ、繰りて、所望の濃度値に比例した時刻において別のデジタル値に1回(かつ、1回のみ)切り換える。しかし、上記に参照された一方、デジタル画素駆動を利用した以前の実施は、内部にアナログ電圧比較器を有する各画素を使用する、画素コンデンサに保存されたアナログ画像値と、全域アナログ・ランプ電圧との間の比較を行うために基礎となっているアナログ画素回路にすべてが依存している。画像値のアナログ保存は達成可能な

10

20

30

40

50

画素サイズを低減するために選択された。なぜなら、単一のコンデンサは8ビットの画像値を保存でき、8つのデジタル・メモリ・レジスタの機能を代替するからである。これらのアナログ実施は、ビット面型デジタル濃度階調に関して上述の画像擬似信号の問題を回避する一方、すべてがアナログ回路に対して既に説明された実践的な困難から被害を受ける。

【特許文献1】米国特許第5977940号明細書

【特許文献2】米国特許第6249269号明細書

【特許文献3】米国特許第6329974号明細書、

【特許文献4】米国特許第6525709号明細書

【非特許文献1】ケラー(Khehlah)、「A Low-Power High-Performance Current-Mode Multiport SRAM」、IEEE Transactions On VLSI Systems、第9巻第5号、590から598ページ(2001年10月) 10

【非特許文献2】ブラロック(Blalock)およびジャガー(Jaeger)、「A High-Speed Clamped Bit-Line Current-Mode Sense Amplifier」、IEEE Journal of Solid-State Circuits、第26巻第4号、(1991年4月)

【発明の開示】

【発明が解決しようとする課題】

【0009】

20

この背景に反し、かつ、従来技術に対する改善を所望して、本発明が開発された。

【課題を解決するための手段】

【0010】

本発明は画像データを表示するための微小表示装置システムに関する。システムは異なる表示状態に切換える可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在する。システムは同じく前記半導体基板上に存在するデジタル・インタフェイス・デバイスも含み、インタフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給し、第1のフォーマットは標準ビデオ信号である。

【0011】

30

微小表示装置は第1の色、第2の色、および、第3の色の各フィールドを順次表示することにより画像データを表示できる。第1のフォーマットは画素に対するRGBデータを含み得、第2の画素に対するRGBデータが続き、かつ、RGB画素データの行全体が供給されるまで順次に継続し、RGB画素データの別の行が続く。第2のフォーマットは第1の色、第2の色、および、第3の色の順次の各フィールドを含み得る。デジタル・インタフェイス・デバイスは、RGBデータを、輝度成分および少なくとも2つの色成分を有するデータ・フォーマットに変換可能である。微小表示装置は、輝度成分および少なくとも2つの色成分を有するデータ・フォーマットにおける画像データを保存するための内部に存在するメモリ・セルを含み得る。輝度データは各々の個別画素に対して保存され、色データは複数の画素のグループに対して保存されている。画素の各グループは4つの画素を含み得る。微小表示装置内の画素は複数の行および列に配列可能であり、4つの画素の各グループは特定の行に2つの隣接した画素を、および、隣接した1つの行に2つの隣接した画素を含み、そのため、画素の2つは1つの列にあり、画素の2つは1つの隣接した列にある。

【0012】

40

微小表示装置は表示される画像データを保存するためのメモリ・セルを含み得、メモリ・セルは微小表示装置全体を通じて分配されている。分配されたメモリ・セルは、必ずしも、いずれかの特定の画素の中に、または、同画素に隣接して所在可能ではない。分配されたメモリ・セルは画素アレイと同一位置に存在可能であるが、画素アレイ内の特定の画素に物理的に接続し得ない。各画素は反射性画素電極を含み得、反射性画素電極は第1の

50

面内に横たわり、かつ、分配されたメモリ・セルは第1の平面であり、かつ、同平面に平行である第2の面内に横たわり、かつ、さらに、反射性画素電極の少なくともいくつかの第2の平面上への正射影は、別の反射性画素電極に対する画像情報を保存しているメモリ・セルを覆っている。

【0013】

システムは、照明装置、および、半導体基板に装着された分光器をさらに含み得る。微小表示装置は各画素に対する画像データの2つの連続したフレームを保存するための二連メモリ・バッファを含み得る。

【0014】

本発明は画像データを表示するための微小表示装置システムにも関する。システムは異なる表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、デジタル・インターフェイス・デバイスも同じく前記半導体基板上に存在し、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給する。微小表示装置は表示される画像データを保存するためのメモリ・セルを含み、メモリ・セルは低電力S R A Mである。

10

【0015】

画像データは電圧モード感度増幅器を使用して低電力S R A Mから読み込み可能である。電圧モード感度増幅器は高速精密比較器を含み得る。

本発明は画像データを表示するための微小表示装置システムにも関し得る。システムは異なる表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、かつ、デジタル・インターフェイス・デバイスも同じく前記半導体基板上に存在し、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給する。微小表示装置の各画素は画素電極を含み、画素は、画素電圧源が、微小表示装置の選択された画素電極に、残り部分を駆動するために使用される論理電圧源により供給される電圧とは異なる大きさで電圧を供給するために使用されることを可能にするための回路も含む。

20

【0016】

画素電圧源は、論理電圧源より小さな、に等しい、または、より大きな大きさの電圧を供給するように制御され得る。画素電圧源は、1つまたは複数の環境条件を補償するために可変電圧を供給するように制御され得る。画素電圧源を変化させることにより補償される1つの環境条件は微小表示装置の温度とし得る。微小表示装置の温度は微小表示装置上で電子的に感知され得る。温度は1つまたは複数のダイオードにわたる電圧降下を感知することにより電子的に感知され得る。

30

【0017】

本発明は画像データを表示するための微小表示装置システムにも関し得る。システムは異なる表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、デジタル・インターフェイス・デバイスも同じく前記半導体基板上に存在し、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給し、不揮発性メモリは微小表示装置に接続され、その特定の微小表示装置システムに固有の情報を保存し、それにより、微小表示装置は保存された情報を利用可能であり、かつ、この情報に基づき、微小表示装置システムにより表示された画像の品質を向上できる。

40

【0018】

不揮発性メモリはE E P R O Mを含み得る。

本発明は画像データを表示するための微小表示装置システムにも関し得る。システムは異なる表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、デジタル・インターフェイス・デバイスも同じく前記半導体基板上に存在し、インターフェイス・デバイスは第1のフォーマットにおいて画像データを

50

受け入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給する。微小表示装置における画素のアレイは行に配列され、行の第1の部分は1つのグループ内にあり、行の第2の部分は第2のグループ内にあり、かつ、さらに、第1および第2のグループの1つのグループの画素は画像情報を使用して頂部行から底部行に更新される一方、第1および第2のグループの別のグループの画素は画像情報を使用して底部行から頂部行に更新される。

#### 【0019】

画素が画像情報を使用して頂部行から底部行に更新された第1および第2のグループの1つのグループは、連続する各フレームに関して第1と第2のグループの間で交番できる。

10

#### 【0020】

本発明は画像データを表示するための微小表示装置システムにも関し得る。システムは異なる表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、デジタル・インターフェイス・デバイスも同じく前記半導体基板上に存在し、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給する。微小表示装置は複数の画素を支援する集中型タイミング回路を含み得、同回路においては、複数の画素の各画素に対してランプ・カウンタ信号と所望の画素値の間で比較が行われ、かつ、これに基づき、各画素に対する独立した画素状態信号が各画素に送出される。

#### 【0021】

複数のセットの集中化タイミング回路が存在可能であり、画素の各N個の列に対して1つである。

20

本発明は画像データを表示するための微小表示装置システムにも関し得る。システムは異なる光変調状態間で切換え可能な画素のアレイを有する空間光変調装置を含み、空間光変調装置は半導体基板上に存在し、デジタル・インターフェイス・デバイスも同じく前記半導体基板上に存在し、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて空間光変調装置の画素に供給する。空間光変調装置は表示される画像データを保存するためのメモリ・セルを含み、メモリ・セルは空間光変調装置全体を通じて分配され、分配されたメモリ・セルは画素アレイと同位置に存在するが、画素アレイの特定の画素に物理的に接続し得ず、かつ、さらに、各画素は反射性画素電極を含み、反射性画素電極は第1の面内に横たわり、かつ、分配されたメモリ・セルは第1の平面であり、かつ、同平面に平行である第2の面内に横たわり、かつ、さらに、反射性画素電極の少なくともいくつかの第2の平面上への正射影は、別の反射性画素電極に対する画像情報を保存しているメモリ・セルを覆っている。

30

#### 【0022】

本発明は色および濃度階調を有する画像を生成する方法にも関する。方法は絵要素のアレイおよび一緒に集積化されたデータ保存要素のアレイを設ける工程と、各画素に対する何らかの数のビットを含む画像データを受信する工程と、その画素に対して受信されたビット数より小さい各画素に対する数のビットをデータ保存アレイに保存し、それにより、保存された画像を作成する工程と、その画素に対して保存されたビット数より大きいビット数を各画素に対して表示することにより、保存された画像を画素アレイ上に表示する工程とを含む。

40

#### 【0023】

保存された画像を表示する工程は、絵要素の同じアレイ上に異なるカラー・フィールドを順次に表示する工程を含み得る。方法は、複数の保存アレイを設ける工程と、各受信された画像をどの保存アレイが受信するかを選択する工程と、どの保存画像を表示するかを選択する工程とをさらに含み得る。保存されたデータのビットの一部は1つまたは複数の画素に対する情報を含み得る。輝度情報は各画素に対して保存可能であり、色情報は画素のグループに対して保存されている。

#### 【0024】

50

本発明は画像データを表示するための微小表示装置システムに関する。システムは異なった表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、各画素は内部に回路を有し、回路はその画素に動作可能に接続され、各画素の内部の、かつ、各画素と動作可能に接続された回路は複数のトランジスタを含み、この回路中には700未満のトランジスタがある。システムは同じく前記半導体基板上に存在するデジタル・インターフェイス・デバイスも含み、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給する。

#### 【0025】

この回路中には600未満のトランジスタが、この回路中には500未満のトランジスタが、この回路中には400未満のトランジスタが、この回路中には300未満のトランジスタが、この回路中には200未満のトランジスタが、この回路中には160未満のトランジスタが、この回路中には150未満のトランジスタが、この回路中には140未満のトランジスタが、または、この回路中には135未満のトランジスタが存在可能である。

10

#### 【0026】

本発明は画像データを表示するための微小表示装置システムにも関する。システムは異なった表示状態間で切換え可能な画素のアレイを有する微小表示装置を含み、微小表示装置は半導体基板上に存在し、各画素は表示表面を有し、各画素はその画素の今後の表示状態に関する情報を含むその画素に動作可能に接続された少なくとも1つのメモリ・レジスタを有する。システムは同じく前記半導体基板上に存在するデジタル・インターフェイス・デバイスも含み、インターフェイス・デバイスは第1のフォーマットにおいて画像データを受入れ、かつ、画像データを第2のフォーマットにおいて微小表示装置の画素に供給する。各画素およびその画素に動作可能に接続された少なくとも1つのメモリ・レジスタにより占められたシリコン基板上の表面積は1,000平方ミクロン未満である。

20

#### 【0027】

占められた表面積は700平方ミクロン未満、335平方ミクロン未満、305平方ミクロン未満、または、300平方ミクロン未満とし得る。各画素に動作可能に接続されたメモリ・レジスタの少なくともいくつかは画素内には物理的に所在し得ない。画素アレイは第1の平面内に横たわり得、メモリ・レジスタは全般に第1の平面に平行であり、かつ、同平面の下方にある第2の平面内に物理的に所在可能であり、画素アレイはメモリ・レジスタの大多数の上に横たわり得る。1つまたは複数のメモリ・レジスタに欠陥があることが一旦決定されれば、微小表示装置システムによる使用のために利用可能である予備のメモリ・レジスタが存在可能である。

30

#### 【発明を実施するための最良の形態】

#### 【0028】

ここで、本発明の様々な適切な特徴を示すうえで役立つ添付の図面が参照される。ここで本発明は空間光変調装置に基づく微小表示装置に主に関して説明されるが、画像表示システムへのデジタル・インターフェイス、画像圧縮、低電力S R A M、および、本発明の他の多くの特徴が必要／所望である他の用途にも本発明が適用可能とし得ることを明白に理解されたい。この点において、微小表示装置システムの以下の説明は例示および説明のみの目的に対して提示されている。さらに、説明は、本願明細書に開示された形態に本発明を限定することは意図されていない。その結果、以下の教示、ならびに、関連技術の技能および知識に相当する改変および修正は本発明の範囲内である。本願明細書に説明されている実施形態は、本発明を実施するうえで知られている最良の形態を説明すること、および、他の当業者が、本発明のそのような、または、他の実施形態において、ならびに、特定の応用例または用途により要求される様々な改変を伴って、本発明を利用することを可能にすることをさらに意図されている。

40

#### 【0029】

本発明の背景から理解され得るように、P W M濃度諧調をデジタル・アーキテクチャで

実施することは望ましい。このことが発明者によりどのようにして行われたかを説明する前に、デジタル PWM 技術の平易な実施が高度な画素の複雑さから損害を被る可能性がなぜ高いかを以下に先ず述べた。微小表示装置のデジタル実施の複雑さは画素当たりに必要な画像ビットの総数に依存し、その総数が、今度は、表示のガンマ特性に依存している。ガンマ ( ) は表示の明るさと入力画像値の間の指数法則関係の指数である。上述の「ピット面」型デジタル濃度諧調技術は画像データ値と表示の明るさの間の線形関係を生成し、かつ、したがって、ほとんどの PWM 方式がそうであるように  $= 1$  を有する。他方、典型的な CRT 表示装置は  $= 2$  を有し、このことは、人間の知覚の特性により良好に適合することが分かる。約 2 のガンマ値は、より精密に均等な知覚上の間隔を有する数値的に隣接した入力データ間の明るさの段階をもたらす一方、 $= 1$  に対しては、知覚される明るさの段階は濃度諧調の明るさの弱い端部において大きく、諧調の明るさの強い端部においては小さい。 $= 1$  に対する画像品質の不利益は色当たり約 2 ビットであることが一般に考えられており、すなわち、CRT 上での標準的 24 ビット画像に品質で等しい画像を表示するためには、 $= 1$  の表示装置上で 30 ビットが必要である。したがって、標準的な 8 ビット / 色の入力信号から直接に動作する  $= 1$  の表示装置は、所望の 1,670 万色パレットの代わりに、 $2^{18} = 262,144$  色のパレットを備えた CRT に知覚可能な品質でほとんど同等の色パレットを生成する。

## 【0030】

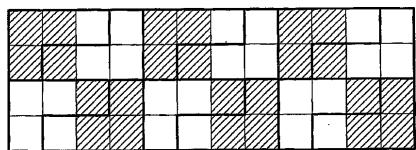

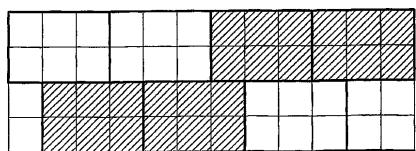

フィールド順次カラー画像を発生する微小表示装置の場合、現在の製品は、入来標準ビデオ画像データを微小表示装置に対する許容可能なフォーマットに変換するために、微小表示装置の上流の独立したインタフェイス・チップを典型的に含む。例えば、標準デジタル・ビデオ画像信号は第 1 の画素（絵要素）に対する赤のデータ、その同じ画素に対する緑のデータ、および、続いて、その同じ画素に対する青のデータを供給可能である。このことは、次のおよびその後の画素に対する赤、緑、および、青のデータ（RGB データ）が後に続く。これが、画像内の特定の線における画素の各々に対して継続され、画像内の次およびその後の後続の線が後に続く。データはフレームの表示に対して割当てられた時間全体を通じてほとんど均一な速度で典型的に送達されるが、各線の終端の短い水平空白間隔および各フレームの終端の短い垂直空白間隔を除く。例えば、C C I R 601 および C C I R 656 標準ビデオ信号において、水平空白は各線に割当てられた時間の約 17 % を占める（この時間は  $60 \mu s$  のオーダである）一方、垂直空白はフレーム時間の約 8 % を占める。時間の残り部分で、データは表示に対して送達される。他方、フィールド順次カラー表示装置は画像内の画素の各々に対する赤のデータを典型的に先ず必要とし、画像内の画素の各々に対する緑のデータが後に続き、画像内の画素の各々に対する青のデータが後に続く。最も単純な順次カラー表示照明方式において、表示全体が 1 回に单一の原色で照明される。この場合、与えられた原色に対するすべてのデータは照明が開始される前に画素に書き込まれなければならず、このことはデータ供給の問題をさらに深刻にし、照明作業係数を不当に低減することを回避するためにデータが短い時間間隔にわたり大きな速度で表示するために供給されることを必要とする。これらの理由のために、フィールド順次カラー微小表示装置システムは、1 つのフォーマットにおいてデータを受信し、かつ、異なったフォーマットにおいてデータを微小表示装置に供給するための追加の回路を必要とする。このフォーマット変換はかなりの量のバッファ・メモリ、表示された画像におけるすべての画素に対する赤、緑、および、青のデータのすべてを保存可能な少なくともメモリの実質的な部分を必ず必要とする。動画の場合、図 17 に示された「ティアリング（tearing）」擬似信号を防止するために、追加のバッファ・メモリが必要である。【M H 1】同図は順次カラー表示装置上の画像を示し、表示装置は新しい入来フレームで同時に更新されつつある単一のフレーム・バッファから再表示されている。描かれた物体は（この例では水平に）移動しつつあり、同物体はフレーム毎に自身の位置を変化させている。表示装置の再表示速度が更新速度とは異なる（すなわち、3 倍以上速い）ため、再表示と更新は完全には同期し得ず、したがって、現在のフレームおよびその前のフレームに対応する画像データの部分が表示装置の異なった領域に同時に出現することは不可避

10

20

30

40

50

である。表示された物体の位置の不整合が存在する水平線がこれらの領域を分離している。物体の詳細または質感はこれらの線に沿って「引き裂かれた」ように見える。この擬似信号は非常に鮮明であり、かつ、平均的な閲覧者には不愉快である。この擬似信号を回避することは、画像データを二重バッファすること、すなわち、前のフレームを保存および表示するために1つのバッファ・メモリを使用する一方、第2のバッファ・メモリが入来画像データで更新されることを必要とする。2つのバッファの役割は入来フレーム間で逆転される。

#### 【0031】

追加データの必要な再フォーマット化または再順列、および、当技術分野で実現されている画像バッファ回路を設ける1つの方法は、これらを微小表示装置から分離されている半導体チップ上に供給することである。この分離インターフェイス・チップ手法の短所は、微小表示装置システムが追加のチップ、例えば、データ・フォーマットの変換に対して1つの余分のチップ、および、画像をバッファするメモリに専用の別のチップを有する必要性によるコストの上昇である。さらなる短所は多チップ表示装置システムのサイズの増大である。最後に、オフ・チップでバッファすることはバッファ・チップと微小表示装置の間の高帯域通信をさらに必要とし、このことは電力消費量の増加を常にもたらす。

10

#### 【0032】

必要な回路およびバッファ・メモリに対する代案位置は、微小表示装置の背面自体上の恐らく画素アレイ内である。しかし、画像バッファを達成するための大量の背面部回路は実際の実施を妨害する。なぜなら、結果として得られる背面は非常に大きく、かつ、そのため、高価となる。もしフレーム・バッファが、単に、画素から分離されているが、それでも微小表示装置の背面上にあるメモリ・ブロックであったなら、背面の総面積に対する画素アレイの面積の比は不要に低減される。なぜなら、画素がメモリ・ブロック領域を覆うことは非現実的であるからである。代案として、微小表示装置の画素の回路構成は、与えられた画素に対する必要なバッファ・メモリがその画素と物理的に接続され、かつ、その画素の下にある回路の一部となるように設計可能である。このことは背面サイズ問題全体を解決しないが、分離されたメモリ・ブロックの能動領域比の好ましくない問題は確かに解決する。なぜなら、ここで画素はメモリ回路を覆っているからである。しかし、この恩恵は別の大きな問題の導入という犠牲を払うことになる。メモリ・レジスタのいずれかの故障は目視可能な画素の欠陥をもたらす。欠陥のあるレジスタのアドレス周辺を「マッピング」することにより生産高を向上させるために半導体メモリ技術において使用されている冗長技法は、そのような画素欠陥を補償するためには容易に使用し得ない。なぜなら、1つの場所の欠陥のある画素は異なった位置の機能中の画素により代替され得ないからである。

20

#### 【0033】

背面サイズの問題は埋め込みD R A M工程などの特殊C M O Sシリコン組立て工程により対処され得るが、それらの工程は組み立てるのにより高価である。さらに、D R A Mは、実質的な不要電力消費量を追加する一定した再表示を必要とする。

30

#### 【0034】

微小表示装置の背面内に所望の完全デジタル順次カラー・フォーマット変換の全体を設けるための従来技術の非現実性は1例により最も良く例示され得る。例示の目的に対して、色当たり8ビットの濃度調節を備えた順次完全カラーを表示可能な微小表示装置を考える。目視可能擬似信号を排除するため、および、大きなカラー・フィールド率を可能にするために、その画素内に所在するバッファ回路を備えた二重画像バッファを微小表示装置が利用することをさらに考える。任意の画素回路のレイアウト・サイズは、完全な設計を行わずに正確に決定し得ないが、同サイズの下方境界は、同画素回路のトランジスタが、標準的な6トランジスタS R A Mセル内のトランジスタと同じ密度で配置されていると仮定することにより見積り可能である。標準的S R A Mセルに対する設計規則およびレイアウトが高度に最適化されているとすれば、任意の画素回路が、より高い密度で配置可能となる可能性は非常に低い。出願人により行われた先進的C M O Sシリコン製造工場の調

40

50

査において、工場により提供された最適化 6 トランジスタ S R A M セルの面積が全般に  $130 f^2$  より大きかったことが見出され、ここで、 $f$  は C M O S 工程の基本原則（通常、指定された工程におけるポリシリコン線に対する最小実行可能半間隔）を示す。例えば、 $0.35 \mu m$  C M O S 工程において、6 トランジスタ S R A M セルは一般に約  $16 \mu m^2$  の面積を有した。式  $a = 130 f^2$  は、（中でも）米国半導体工業会（United States' Semiconductor Industry Association）により後援されている「International Technology Roadmap for Semiconductors 2002 Update」における将来の工程および今後数年に対して見積られた面積よりもわずかに大きな S R A M 面積の見積りを与える。

10

### 【0035】

順次カラー表示装置技術において知られているように、画素内でのバッファおよび画像データの再順列はシフト・レジスタを使用して便利に達成可能である。2つの静電ラッチ（各ラッチは交差結合型インバータの形態の4つのトランジスタをさらに含む）および2つの伝達ゲート（各伝達ゲートは2つのトランジスタを含む）を含む標準的 C M O S シフト・レジスタ・セルは、保存ビット当たり 12 個のトランジスタを必要とする。したがって、二重バッファする 24 ビットの画像情報は  $48 \times 12 = 576$  個のトランジスタを必要とする。もしこれらのトランジスタが高度に最適化された標準 S R A M セルの密度に適合する密度で配置可能であれば、それらのトランジスタは  $0.35 \mu m$  C M O S 工程において  $1,536 \mu m^2$  を占める。したがって、画像バッファに接続されたトランジスタのみが、四角形の微小表示装置画素の最小達成可能間隔を、この候補 C M O S 工程に対しては  $39.2 \mu m$  に制限する。ダウン・カウンタを使用することにより、保存されたデジタル画像値が画素持続時間信号（実際には、P W M 駆動信号）に変換可能であることは、順次カラー表示技術において知られている。カウンタの各段は、図 18 に示されたように、ゼロ状態を検出するための N A N D ゲートと共に、半加算器およびマスタ / スレーブ・フリップ・フロップを使用して、従来、実施可能である。半加算器は 8 トランジスタ X O R ゲートに加え、4 トランジスタ A N D ゲートを含み、マスタ段は交差結合型インバータとして配列された 4 つのトランジスタに加え、負荷トランジスタおよび割込み可能トランジスタを含み、スレーブ・トランジスタは同様のものから負荷トランジスタを除いたものである。N A N D ゲートは入力当たり 2 つのトランジスタを必要とする。したがって、カウンタはビット当たり 25 個のトランジスタを必要とし、これらのトランジスタは、8 ビット濃度調節に対しては、カウンタのゼロ段の使用されていない A N D ゲートの 4 つのトランジスタが破棄された後の 196 個のトランジスタに相当する。したがって、合計で、24 ビットカラー表示装置のこの二重バッファ P W M 実施は  $576 + 196 = 772$  個のトランジスタを必要とする。この見積りは画素選択などに必要な他のトランジスタを無視している。上述の  $0.35 \mu m$  C M O S 工程において、この 772 トランジスタ画素は  $2,050 \mu m^2$  より大きな面積を必要とし、このことは達成可能な四角形画素間隔を  $45 \mu m$  に制限する。この画素サイズの見積りは、現在の市販微小表示装置に見出される  $12 \mu m$  の周辺の範囲にある画素間隔と対照され得る。したがって、デジタル順次カラー・フォーマット変換の平易な実施は、市場で競争の激しいものより 10 倍を超えて大きな面積を持つ画素をもたらす。与えられた表示解像度に対して、大きな画素サイズは大きな背面ダイ・サイズをもたらし、このことは、このことに対応して、シリコン・ウェハ当たり少数の背面ダイ、および、低い背面ダイ生産高をもたらし、不要に高い背面ダイのコストを合わせて与える。

20

### 【0036】

1 つの画像に必要なビット数を削減するための技術が微小表示装置背面の複雑さおよびサイズを低減する可能性のあることは理解し得よう。例えば、J P E G 圧縮などの画像圧縮技術は画像を保存するために必要なメモリの量を低減するために使用可能である。しかし、これらの技術は複雑な数値処理論理を典型的に必要とし、同論理の追加サイズは必要なメモリのいかなる節約も相殺する。

30

40

50

## 【0037】

保存されなければならない画像データ・ビット数も、表示装置が示し得る色の数を制限する技術を介して、画素当たり全24ビットにおいて利用可能な全1,670万種の明度より小さな「パレット」に低減可能である。例えば、もし明度の数が65,536種の明度に制約されたなら、保存される必要のあるビット数は、結果的な背面の複雑さの低減を伴って、画素当たり24から画素当たり16に低減可能である。しかし画像のパレット化は画像自体の望ましくない画像擬似信号を、特に自然の風景の写真またはビデオに見出されるものなどの連続諧調画像に対して生成する。なぜなら、パレット化は色および明るさの円滑な変化を描写することを困難にするからである。この問題はPWM画素変調装置に対して大きく深刻化され、表示の明るさと入力画像値の間に線形関係を生成する。入力値パレットの16ビットへのさらなる低減は、 $= 2$  の表示装置上の  $2^{10} = 1024$  色に等価である  $= 1$  において表示されたパレットをもたらし、ほとんどいずれの応用例にも適さない。10

## 【0038】

## システムの要素

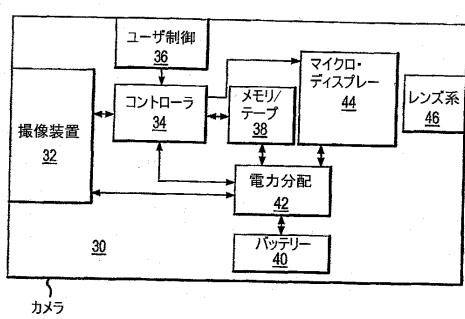

このことに留意して、ここで本発明が検討可能となる。本発明が採用可能である応用例の1つの実施例は図1に示された如くのカメラ30である。カメラ30はビデオ・カメラ、デジタル静止画カメラ、または、他のタイプのカメラとし得る。カメラ30はユーザが記録したいと所望可能な画像を表す電気信号を作成可能である画像取込みデバイス32を含み得る。電気信号は画像取込みデバイス32からカメラ30の機能を制御する制御装置34に送られる。カメラ30は、ユーザがカメラ30の動作のモードを選択するために使用可能なユーザ制御部36も含む。制御装置34は、メモリ/テープ部38などの保存デバイスに画像を表す電子信号を保存する能力を有する。ビデオ・カメラの場合、同部38は典型的にビデオ・テープとなり得る一方、デジタル静止画カメラの場合、同部38は典型的に何らかのタイプの電子的不揮発性メモリとなり得る。カメラ30は電力分配部42を介してカメラ30の各構成部分に電力を供給する電池40も含む。画像の保存された電子的表現は、レンズ系46または反射式拡大装置を介してユーザにより閲覧され得る微小表示装置44により視覚的画像に変換可能である。このことは、本発明の微小表示装置が利用され得る応用例の1つの実施例である一方、それは、例示のみの性質を持ち、かつ、本発明の範囲をいかなる形においても限定することは意図されていない。20

## 【0039】

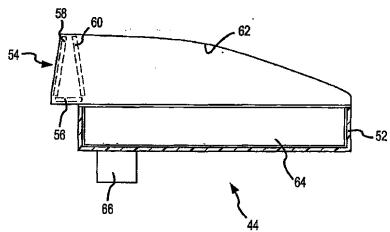

微小表示装置44は、同装置44の主要構成部分を示すために図2に示されている。微小表示装置44は照明装置筐体54が装着されているプラスチック製パッケージ筐体52を含む。照明装置筐体54は三色LED56およびLED56により照射された光を集光する反射器58を収容している。続いて、光は、不要な偏光の迷光を最小に抑えるため、および、均一な照明を作成するために前偏光器および拡散器60を通過する。拡散され、偏光された光は偏光分光器(PBS)62に向けて差向けられ、分光器62は1つの線形偏光の光を反射する一方、直交する線形偏光の光は拒絶する。反射光はパッケージ筐体52内に存在するシリコン(LCOS)表示パネル64上の液晶に向けて差向けられる。以下にさらに詳細に説明するように、表示パネルは、2つの異なった光変調状態の1つに電子的に制御可能である画素のアレイを含む。1つの光変調状態において、偏光された入来光は同じ偏光を持ってPBS62に向けて反射し戻される。もう1つの光変調状態において、光は、90度だけ回転された自身の線形偏光を持ってPBS62に向けて反射し戻される。理解され得るよう、PBS62は、自身の偏光が回転されなかった反射光を反射する一方、偏光が回転された光は、レンズ系46を介したユーザによる閲覧のためにPBS62を通過する。コネクタ66は屈曲ケーブルを介するなどしたカメラ30への電気的接続のためにパッケージ筐体52から下方に懸垂する。40

## 【0040】

表示パネル64の動作の上記の検討は本発明を限定することは意図されていない一方、他のタイプの空間光変調装置、例えば機械式極小鏡に依存する空間光変調装置なども本発50

明において利用可能である。同様に、自身の光を発する表示パネルも使用可能である。加えて、検討が2つの異なった直交する方向の線形に偏光された光に関与する一方、未偏光の光または異なったタイプの偏光が使用されているシステムにおいて本発明を利用することも可能である。液晶空間光変調装置の動作に関するさらなる詳細は、各々の内容を本願明細書に援用する米国特許第5748164号、同第5808800号、同第5977940号、同第6100945号、同第6507330号、同第6525709号、および、同第6633301号に見出され得る。

#### 【0041】

##### 表示パネルの詳細

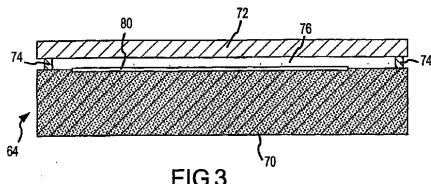

表示パネル64はさらに詳細に図3および4に示されている。図3に示すように、表示パネル64は、ガラス板72が接着剤封止74を介して固着されているシリコン背面70を含む。シリコン背面70とガラス板72の間に挟まれているのは、液晶材料層76である。異なった側面から見ると、ガラス72および背面70は、1つの側にガラスのわずかな張り出しが、および、向かい合う側にシリコンのわずかな張り出しが存在することを可能にするために、1つの方向においてわずかにずらされていることが明白になり得る。液晶材料76は強誘電性、ネマティック、または、他のタイプの液晶を含むが、これらに限定されないいくつかのタイプの液晶のいずれかを含み得る。この実施形態において、強誘電性液晶が利用されている。代案として、デジタル微小鏡、および、他の微小電子機械デバイス、プラズマ表示装置、エレクトロルミネセント表示装置、発光ダイオードなどの他のタイプの表示デバイスも表示パネルの一部として採用され得る。理解され得るように、これらの代案は、光源からの光を変調する空間光変調装置のいずれかとし得るか、または、独立した光源を必要としない光放射性デバイスとし得る。

#### 【0042】

シリコン背面70は、反射性画素電極のアレイ80が所在する自身の頂部表面上の領域を含む。理解され得るように、画像は、表示パネルの「能動領域」として知られている表示パネル64のこの領域に形成される。シリコン背面70は、表示パネル64の主要構成部分の例示の容易さのみのために、固体シリコン材料で形成されているように図3に示されている。現実では、以下にさらに詳細に検討されるように、複数の回路、導体などがシリコン背面70内に存在する。

#### 【0043】

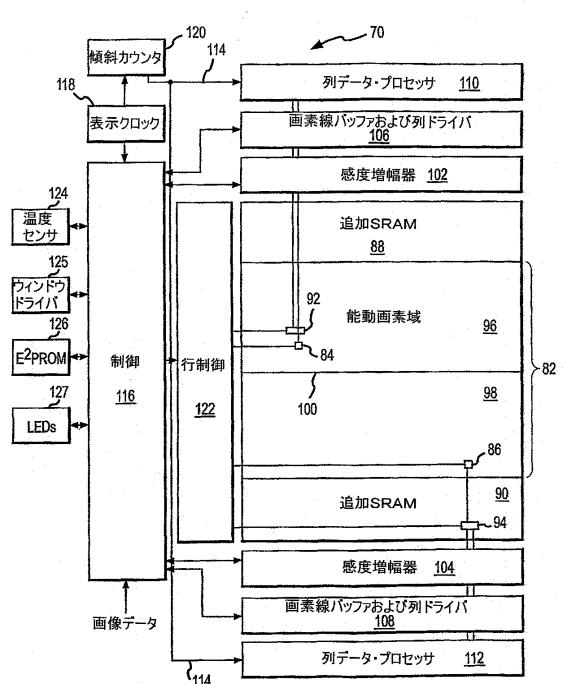

図5は、シリコン背面70の特定の重要な部分を、位置に關した形におけるよりも、むしろ機能上の形で、および、背面70とのインタフェイスを行う構成部分を表すことを意図されている。シリコン背面70は画素の複数の行および列を含む能動画素領域82を有する。2つの画素、第1の画素84および第2の画素86は能動画素領域82に示されている。反射性画素電極のアレイ80の下方にシリコン背面内に所在するのは、(以下にさらに詳細に検討される)回路であり、同回路の主要構成部分は、能動画素領域82の下の、かつ、メモリ・セルの追加領域88および90が示されている図5に見られるように垂直に能動画素領域82の境界を越えて任意で延長している複数のメモリ・セルである。本実施形態において、これらのメモリ・セルは従来の6トランジスタSRAMとして実施されているが、ダイナミック・レジスタを含む他のタイプのメモリ・レジスタも同様に使用可能である。メモリ・セルの2つの特定の領域、SRAMの第1の領域92およびSRAMの第2の領域94が図5に示されている。見られるように、SRAMの第1の領域92は第1の画素84と機能的に接続され、SRAMの第2の領域94は第2の画素86と機能的に接続されているが、SRAMの領域92および94は第1および第2の画素84および86の隣には所在していない。第2の主要な構成部分は、SRAMセルとしてデータを保存可能であり、ならびに、ブースト・セルに保存されているデータにより指令されたように画素電極に特定の電圧を駆動可能である複数のブースト回路である。

#### 【0044】

この実施形態において、能動画素領域82の上部半体96は能動画素領域82の上方に図5に示された1セットの回路と結合されている一方、能動画素領域82の下部半体98

10

20

30

40

50

は能動画素領域 8 2 の下方に図 5 に示された回路と接続されている。この場合、上部半体 9 6 および下部半体 9 8 は図 5 に示された分割線 1 0 0 に沿って分割されている。以下にさらに詳細に検討されるように、上部および下部半体 9 6 および 9 8 に接続された能動画素領域 8 2 の上方および下方の追加の回路はそれぞれ感度増幅器 1 0 2 および 1 0 4 の 1 対の列体、それぞれ画素ライン・バッファおよび列駆動装置 1 0 6 および 1 0 8 の 1 対の列体、ならびに、それぞれ列データ・プロセッサ ( C D P ) 1 1 0 および 1 1 2 の 1 対の列体である。列体 1 0 2 および 1 0 4 の感度増幅器は列体 1 1 0 および 1 1 2 の列データ・プロセッサによる使用のために S R A M メモリ・セルの内容を読み取る。列体 1 0 6 および 1 0 8 の画素ライン・バッファは S R A M への途中でデータを一時的に保存し、S R A M の列を駆動するための回路を含み、かつ、S R A M の特定の列のみを選択的に駆動するための機構を提供する。列体 1 1 0 および 1 1 2 の列データ・プロセッサは、画素アレイ 8 2 の画素電極が、表示された画像を作成するために、いつ、および、どのようにして駆動されるべきかを決定するために、S R A M から感度増幅器により読み戻されたデータを受信し、データを圧縮解除し、ランプ信号 1 1 4 と比較する。

10

#### 【 0 0 4 5 】

シリコン背面 7 0 内の制御部 1 1 6 は、様々なフォーマットのいずれかの 1 つにおいてカメラ 3 0 の制御装置 3 4 から到来可能な画像データなどの微小表示装置 4 4 に供給された画像データを受信する。制御部 1 1 6 は R G B 順次、 C C I R - 6 0 1 、および、 C C I R - 6 5 6 を含む少なくとも 3 つの異なった標準ビデオ・フォーマットで画像データを受け入れるように動作可能である。これらの標準フォーマットの各々において、三原色すべてに関連する画像データが、いかなる画像データも次の画素に対して伝送される前に、与えられた画素に対して伝送される。これらのビデオ・フォーマットの各々に対するタイミングは N T S C または P A L とし得、垂直周波数は 5 0 H z または 6 0 H z のいずれかとし得る。 R G B 順次データの解像度は 4 3 2 × 2 4 0 とし得る一方、 C C I R ビデオ・フォーマットに対する解像度は 7 2 0 × 2 4 2 または 7 2 0 × 2 8 8 のいずれかとし得る。本発明はいずれの特定のフォーマット、タイミング、垂直周波数、解像度、または、幾何学的形状にも限定されない。本発明は、表示装置が標準アナログ・ビデオ信号を受入れ、かつ、表示装置の残り部分にデジタル・データを供給することを可能にするために、入力データ経路中にアナログ / デジタル変換装置をさらに設け得る。制御部は、必要および適切となり得る場合に受信された画像に対するガンマ補正、ディザリング、および、縮尺調整を行うように動作可能である。例えば、もし以下により詳細に説明されるように列データ・プロセッサおよび S R A M アレイが = 1 を持つ P W M 濃度調節を生成するために共働したなら、かつ、受信された画像データが = 2 の表示装置を駆動するように設計された標準供給源から供給されたなら、制御部は、表示された時に閲覧者が正しいガンマ特性を知覚するように、入来するデジタル値を新しい値に変換可能である。本実施形態において、このことは入来 8 ビット / カラー・データを所望のガンマ補正を備えた 1 0 ビット / カラー・データに変換することにより達成される。本発明の 1 つの実施形態の 8 ビット / カラーの制限内でこのデータを表示するために、 1 0 ビット / カラー・データは、 1 0 ビット値を表示可能である精度の不足からもたらされるいかなるエラーの目視可能性も最小に抑えるために、制御ブロック 1 1 6 内で実行されるフロイド - スタインバーグ ( F l o y d - S t e i n b e r g ) エラー拡散アルゴリズムを使用して 8 ビット / カラー・データに変換される。加えて、制御ブロック 1 1 6 は、画素アレイのフォーマットに適合する 4 3 2 × 2 4 0 フォーマットへの双線形内挿を使用して ( 例えば、 7 2 0 × 2 4 2 または 7 2 0 × 2 8 8 のフォーマットを有することがある ) 入来画像データを水平に、および、垂直に縮尺調整可能である。

20

30

40

#### 【 0 0 4 6 】

制御部 1 1 6 は表示ブロック 1 1 8 からクロック信号を受信する。表示ブロックからのクロック信号は、上述のランプ信号 1 1 4 を供給するランプ・カウンタ 1 2 0 も駆動する。制御部 1 1 6 は、画素のどの行およびどの S R A M セルがアクセスされるかを選択する行制御論理 1 2 2 を制御する。制御部 1 1 6 は、そのいくつかが背面 7 0 から分離されて

50

所在することがある様々な周辺回路要素と通信もする。これらの要素は温度センサ 124、ウィンドウ駆動装置 125、画素電圧発生器、1つまたは複数の LED 駆動装置、1つまたは複数のデジタル／アナログ変換器 (D A C)、1つまたは複数のアナログ／デジタル変換器 (A D C)、EEPROM 126などの不揮発性メモリ、および、1セットの LED 127を含む。

#### 【0047】

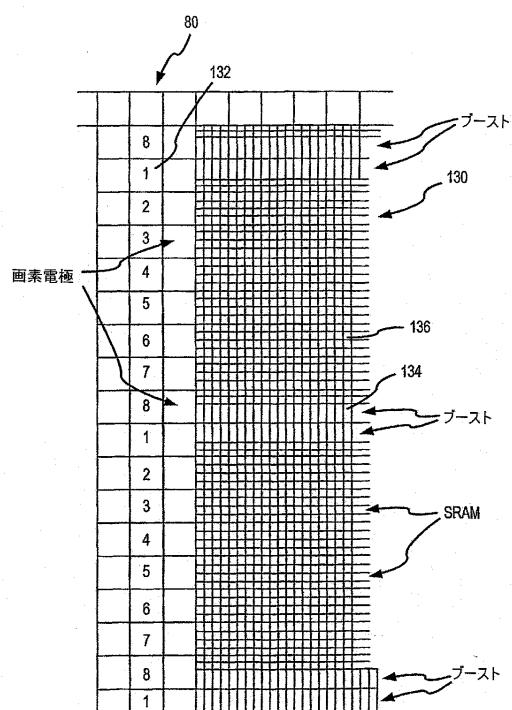

図 6 は S R A M メモリ・セルの層 130 内の画素電極 80 のアレイと、同アレイの下に横たわる画素駆動ブースト回路との間のサイズの関係を示している。理解され得るように、1つの次元において、画素アレイ 80 および下の層 130 は同じ幅である一方、別の次元において層 130 は画素アレイ 80 より大幅に高い。図 5 に示されたように、このことは、この特定の実施形態において利用されている追加の S R A M 88 および 90 による。

10

#### 【0048】

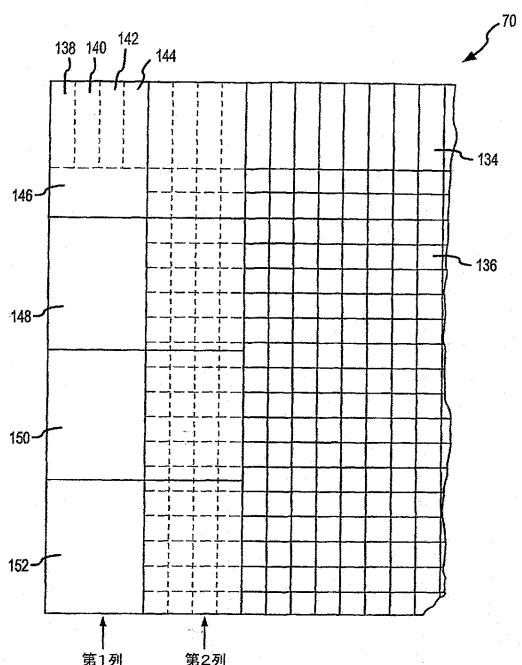

図 7 は画素アレイ 80 と層 130 の間の位置の関係を示している。例示の目的のため、画素アレイ 80 の一部は同アレイの下の層 130 の部分を露出させるために除去されている。この実施形態において、画素電極 132 の各々は図 7 に示されたように単一の列内の 8 つの隣接した画素電極のグループの 1 つである。画素アレイ 80 の下にある層 130 はブースト回路 134 の複数の行および複数の S R A M メモリ・セル 136 を含む。観察され得るように、ブースト回路 134 は隣接した行の各対に一緒にグループ分けされ、S R A M メモリ・セル 136 の約 30 個の行により分離されている。さらに、ブースト回路 134 は、この実施形態において、画素電極 132 の各々を基準として特定の位置に所在する一方、S R A M はブースト回路間の残りの面積を占めている。ブースト回路、および、データが最終的に表示される画素を基準とした S R A M セル内のデータの位置は根本的に任意である。これらの関係、または、その欠如は図 8 でより良く理解可能である。図 8 の左側では、4 つの電極 146、148、150、および、152 が第 1 の垂直列にあり、かつ、他の 4 つが第 2 の垂直列にある 8 つの画素電極は画素電極 146 の下に仮想線で示された複数のブースト回路 138、140、142、および、144 と共に観察され得る。追加のブースト回路および S R A M メモリ・セルは画素電極の第 2 の垂直列の下に仮想線で示されている。図 8 の右側には、シリコン背面 70 が、複数の画素ブースト回路 134 および S R A M メモリ・セル 136 を直接に露出させるために除去された画素電極と共に観察される。

20

#### 【0049】

この実施形態において、特定の行の 4 つの特定のブースト回路 138、140、142、および 144 のグループは特定の列の 4 つの特定の画素電極 146、148、150、および、152 と接続されている。ブースト回路が画素電極の幅の約 4 分の 1 となる空間を占めているため、4 つのブースト回路 138、140、142、および、144 は画素電極の単一の 1 つ 146 の下に横たわっている。この実施形態において、ブースト回路 138 は画素電極 146 と接続され、かつ、同電極を駆動し、ブースト回路 140 は画素電極 148 と接続され、かつ、同電極を駆動し、ブースト回路 142 は画素電極 150 と接続され、かつ、同電極を駆動し、ならびに、ブースト回路 144 は画素電極 152 と接続され、かつ、同電極を駆動する。理解され得るように、画素電極 146 の下方の残りの空間ならびに画素電極 148、150、および、152 の下方の空間のすべては複数の S R A M メモリ・セル 136 により占められている。しかし、画素電極 132 のこの特定のサイズ決定および使用されている特定の半導体組立て工程の場合、特定の画素電極 146、148、150、および、152 の下方の残りの空間はそれらの 4 つの画素電極に対するこの設計により必要とされるバッファされた保存に対しては十分ではない。この理由のために、画素アレイ 80 の垂直に上方および下方の追加の空間は、図 5 および 6 に示されたように層 130 内の追加の S R A M 88 および 90 に対して使用されている。

30

#### 【0050】

図 7 に戻って参照すると、ブースト回路 134 の各隣接した 2 つの列の底部行が 4 つの画素電極、すなわち、ブースト回路の底部行の頂部上に直接に所在するその同じ列内の画

40

50

素電極、および、同じ列内でブースト回路の下に横たわる3つの隣接した画素電極と接続され、かつ、同電極を駆動することが理解し得る。同様に、ブースト回路134の各対の上部列は4つの画素電極、すなわち、ブースト回路の上部行の頂部上に直接に所在するその同じ列内の画素電極、および、同じ列内で垂直に上方にある3つの隣接した画素電極と接続され、かつ、同電極を駆動する。

#### 【0051】

既に説明されたように、この実施形態においては、ブースト回路間の空間内の能動画素アレイの下に取付けられるよりも多くのS R A M保存装置が必要である。この理由のために、S R A Mは図6に示された能動画素アレイ80を越えて延長している。したがって、以下に続けて説明されている使用されているS R A Mが画素電極と同じ垂直分層内に存在しなければならないこと以外に、能動画素アレイの画素電極とその画素に対するデータが保存されているS R A M位置の間には特定の関係が存在しないことが理解され得る。

10

#### 【0052】

特定のS R A Mメモリ・セル136と特定の画素電極132の位置の間の特定の関係の欠如が、画素アレイ80内のどこの画素電極上にも表示される画像データに対するメモリ・バッファとして追加のS R A M領域88および90内にあるS R A Mメモリ・セルを微小表示装置44が使用することを可能にすることにより、この欠如が有利であることが理解され得る。加えて、特定のS R A Mメモリ・セル136またはS R A Mメモリ・セルの行が欠陥を持つと決定された場合、シリコン背面70のどこかに所在する予備のS R A Mメモリ・セルまたはS R A Mメモリ・セルの行はその特定の画素電極132に対するメモリ・バッファとして利用可能である。不調のセルまたは行のアドレス位置は微小表示装置に接続されたE E P R O M不揮発性メモリ内に外部ダイ試験の時点で保存可能であるか、または、微小表示装置が通電された時に始動する内蔵自己試験機能により決定可能であり、かつ、微小表示装置内の揮発性レジスタ内に保存可能である。制御ブロック116内の論理は不調のセルまたは行のアドレスを取り込んで解読することが可能であり、かつ、解釈可能であり、ならびに、適した予備のセルまたは行のアドレスに自動的に代用可能である。

20

#### 【0053】

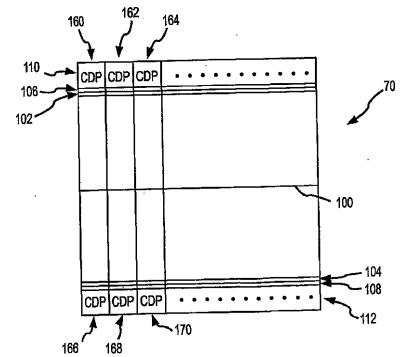

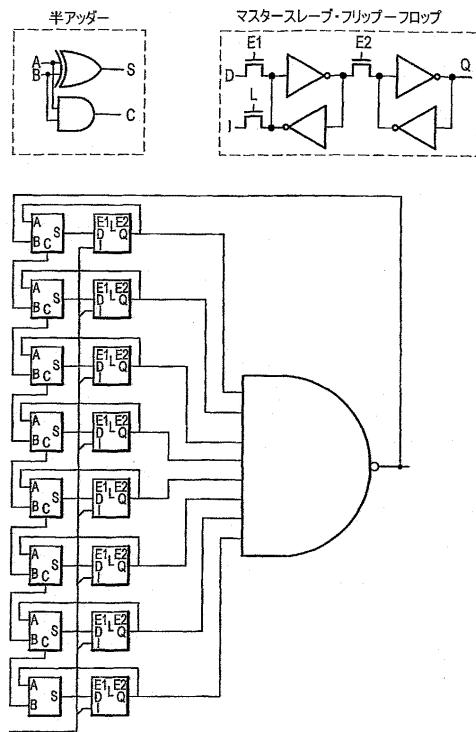

##### 列データ・プロセッサおよびその機能

シリコン背面70の各部分は図9に示されている。既に検討されたように、シリコン背面70は分割線100により上部半体および下部半体に分割されている。上部半体は感度増幅器の水平列体102、画素ライン・バッファおよび列駆動装置の水平列体106、ならびに、列データ・プロセッサ(C D P)の水平列体110を含む。さらに、シリコン背面のこの部分は垂直分層に分割され、それらの分層の3つ160、162、および、164が示されていることが観察され得る。各垂直分層は自身のC D Pおよび関連画素ライン・バッファ、ならびに、列体106からの列駆動装置ならびに列体102からの関連感度増幅器を有する。特定の分層のC D Pはその特定の分層内の画素電極の各々に対するデータ処理を行う。分割線100の別の側には、同様のC D P分層166、168、および、170が示されている。これらの分層166、168、および、170の各々は単一のC D Pおよび関連画素ライン・バッファならびに列体108からの列駆動装置および列体104からの関連感度増幅器を含む。

30

#### 【0054】

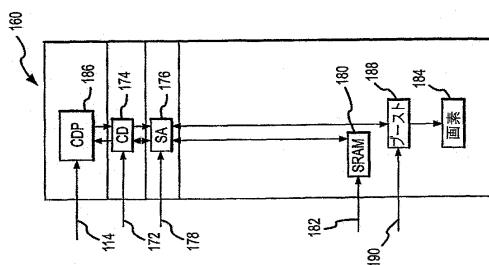

##### S R A Mの読み出しおよび書き込み

図10はC D P分層160の機能図を示す。制御部116からの符号化画像データ172は分層160内の列駆動装置174に供給される。列駆動装置174は(この書き込み動作に対する信号178を介して選択解除されている)感度増幅器176を通って複数のS R A Mメモリ・セル180にデータを送る。データが保存されている特定のS R A Mメモリ・セルは列制御部122からの特定の列駆動装置174および行可能信号182により決定される。その後、制御部116は、行制御部122に、画素電極のデータが保存されているS R A Mセルの列180に対して行可能信号182を駆動し、かつ、感度増幅器可

40

50

能信号 178 を活性化することにより感度増幅器 176 を可能にするように指令する。感度増幅器 176 は選択された S R A M セル 180 の内容を決定し、かつ、データを分層 160 の C D P 186 に送る [ J M D 2 ]。C D P 186 はデータを圧縮解除し、かつ、圧縮解除された値の選択された部分をランプ信号 114 と比較し、続いて、感度増幅器 176 を不能にすること、列駆動装置 174 を可能にすること、および、行制御部 122 に行可能信号 190 を駆動させることにより、その比較結果は一時的に保存され、かつ、その後、画素 184 に接続されたブースト回路 188 に書き込まれる。

#### 【 0 0 5 5 】

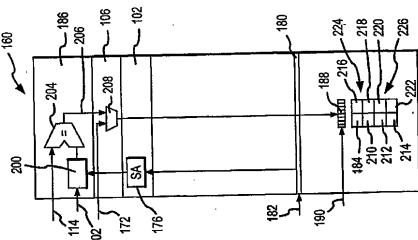

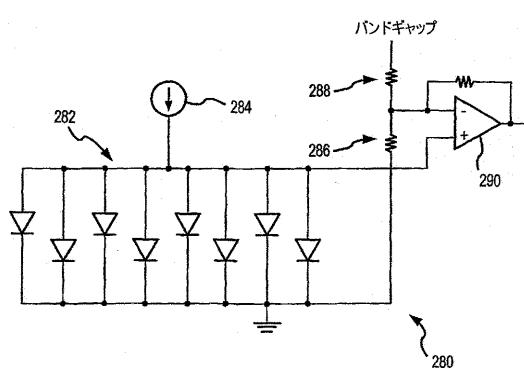

##### デジタル・パルス幅変調濃度階調

図 11 は、画素の状態をいつ変化させるかを決定するために、比較を行い、その比較の結果を使用する S R A M からデータを読み出す動作についてさらなる詳細を示す。この場合、S R A M メモリ・セルは、この C D P 分層 160 内の 48 個の異なったメモリ・セルを含み得るメモリ・セルの行全体として表されている。特定の行 180 は行可能信号 182 により選択される。S R A M メモリ 180 内の特定のメモリ・セルからのデータは感度増幅器 176 により読み出され、かつ、復号化ブロック 200 に供給される。このことは以下にさらに詳細に検討する。復号化ブロック 200 は制御部 116 から復号化信号 202 を受信する。復号化信号 202 は、保存されている符号化された画像データから復号化された結果のどの部分がデジタル比較器 204 の第 1 の入力に供給されるべきかを示す。比較器 204 は符号化された画像値のこの復号化された部分を（その第 2 の入力に供給された）デジタル・ランプ信号 114 と比較し、かつ、画素制御信号 206 を（図 12 に関連して以下に説明される論理を介して）、画素制御信号 206 または符号化された画像信号のいずれかの以下の保存場所への書き込みを可能にするように制御され得る多重化器 208 に供給する。この場合、画素制御信号 206 は、4 つの画素 184、210、212、および、214 の下の列内の 4 つのブースト回路のグループ内にある選択されたブースト回路 188 に設けられている（例示の容易さのために、ブースト回路は、この場合、画素の 1 つの下には示されていない）。ブースト回路 188 は、画素制御信号 206 が状態を制御することを意図されている画素電極 184 に接続され、かつ、電気的に連絡している。この実施形態において、各ブースト回路は画素の所望の状態に対する 1 ビット保存レジスタとして機能する。8 つのブースト回路はブースト回路 188 を含む行において示されていることが観察され得る。これらは 4 つのブースト回路の 2 つのグループに分けられ、4 つのブースト回路の下方に示された 4 つの画素 184、210、212、および、214 に対する意図された表示値を保存している同回路の最も左のグループ、および、4 つのブースト回路の下方に示された 4 つの画素 216、218、220、および、222 に対する意図された表示値を保存している同回路の最も左のグループを備えている。後の検討の容易さのために、画素 184、210、216、および、218 の  $2 \times 2$  のアレイが画素グループ 224 として図 11 に示されている一方、4 つの画素 212、214、220、および、222 の別のグループが画素グループ 226 として図 11 に示されている。

#### 【 0 0 5 6 】

この特定の実施形態において、画素アレイ 80 は 240 画素を垂直に、および、432 画素を水平に含む。分割線 100 はこの  $240 \times 432$  アレイを垂直に 120 画素および水平に 432 画素の 2 つのアレイに分割している。これらの 2 つのアレイの各々は、既に説明されたように、36 個の C D P 分層に垂直に分層されている。これらの C D P 分層の各々は垂直に 120 画素および水平に 12 画素の下位アレイを含む。これらの画素の下にはブースト回路の行があり、C D P 分層の各特定の行に 48 個のブースト回路を、または、画素の各列に対して 4 つのブースト回路を備える。ブースト回路の二重行の間には、S R A M メモリ・セルの約 30 個の行があり、各 C D P 分層の各行に 48 個のメモリ・セルがある。このことは、本発明の 1 つの実施形態に過ぎないものと意図されており、かつ、本願明細書において検討されたサイズまたは数のいずれも、本発明を限定することは意図されていない。

10

20

30

40

50

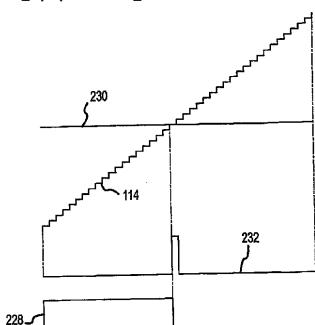

## 【0057】

図12はCDP分層160内の比較器204に入力された信号、画素制御信号206を作成するうえで役立つ比較器204の出力232、および、同様に、画素電極の状態を表す結果的な画素電気駆動信号228を示している。ランプ信号114は比較器への入力の1つである一方、他の入力は復号化された画素値230である。画素電気駆動信号228は、同じ時間縮尺上ですぐ下方に示されている。双方の比較器入力信号はデジタルであるが、それらの信号は、図の垂直方向が値を示す形でこの図中に模式的に示されている。ランプ・カウンタ120により出力されたランプ信号114は、二進値000000000(デジタル0)から二進値11111111(デジタル255)に進行する8ビット・カウンタの出力とし得る。交番二進符号などの単純な計数以外の方式も使用可能である。さらに、計数は減少する順ならびに増大する順で進行し得る。図から理解され得るように、ランプ信号114が開始すると、画素電気駆動信号228、画素制御信号206により信号指令されたように、例えば低状態から高状態に移行する。一旦ランプ信号114が復号化された画素値230と同じデジタル値に到達すれば、比較器出力232は高くなる。この出力は、列駆動装置174が行可能信号182により選択された画素に書き込むことを可能にし、それにより、画素制御信号206を供給する。この場合、画素制御信号206の値は、比較器204による等価性の検出に応じて画素電気駆動信号228が高状態から低状態に移行するように選択される。当然、画素電気駆動信号228が低状態を基準として高状態にある時間の長さは復号化された画素値230の規模の関数である。すなわち、複合化された画素値230の小さな規模に対して、画素電気駆動信号228の高状態は比較的短い一方、複合化された画素値230の比較的大きな規模に対して、画素電気駆動信号228は時間の実質的に大部分にわたり高状態にある。このように、微小表示装置44はパルス幅変調画素駆動を実施している。当然、PWMの感度は逆転可能である(すなわち、論理回路への単純な変更による復号化された画素値230の小さな規模に対する画素電気駆動信号228の比較的長い持続時間など)。列データ・プロセッサの機能は加算器、シフタなどの組合せ論理を介して達成される。

## 【0058】

表示装置の底部半体と表示装置の頂部半体とに対して、異なった順で各画素に対するブースト回路に書き込まれることは、画素制御信号206にとって好ましいとし得る。例えば、もし信号が同じ形で各半体に書き込まれ、各半体の頂部行から底部行に画像を更新したなら、2つの半体間の分割線100に近い画像の一部は、時間の実質的に大部分にわたり、新しい画像の部分の隣に古い画像の部分を有する。このことは目視可能な画像擬似信号を引き起こし得る。この擬似信号を回避するために、頂部半体を頂部行から底部行に更新する一方、底部半体を底部行から頂部行に更新することが可能である。このことは、外側から内側に更新するとも呼び得る。代案として、更新はまったく逆の形態、内側から外側に、または、頂部半体の底部行から頂部行に、および、底部半体の頂部行から底部行に行われ得る。別の代案は、データの1つのフレームの外側から内側に、次の後続フレームでは内側から外側に、かつ、この交番形態で繰り返すことである。これらの代案または目視可能擬似信号を排除するいずれかの他の代案に対するいかなる変形も許容可能である。

## 【0059】

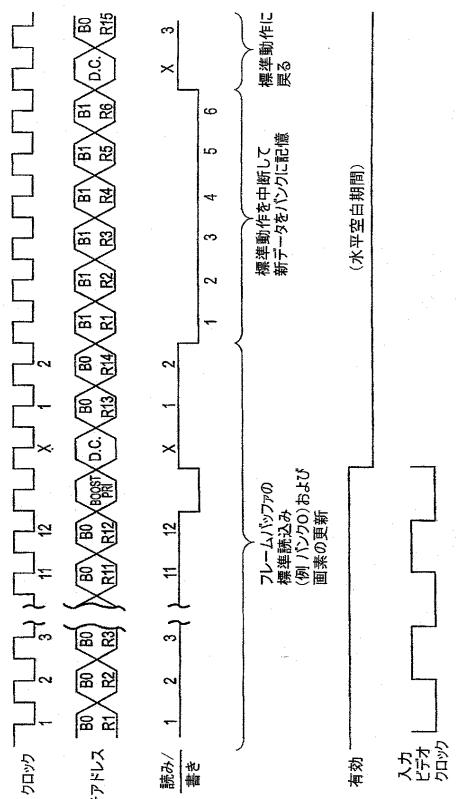

本願明細書に開示されている微小表示装置の重要な特徴は標準ビデオ信号を受入れ、かつ、同時に表示する機能である。この機能は、図19に関してここで説明されるように、列データ・プロセッサ110および112の作用に関連した画素ライン・バッファ106および108の前述の列体により達成される。図19は入力ビデオ信号の要素、すなわち、符号化された入力ビデオ・データおよびVALID信号と、CDPおよび画素ライン・バッファの濃度調節作用の要素、すなわち、表示クロック118、制御ブロック116から画素ライン・バッファ106および108に供給されるREAD信号、ならびに、感度增幅器102および104との間のタイミング関係、さらに、制御ブロック116により行制御部122に供給される行アドレスのシーケンスを示している。行制御部122により選択されたSRAMレジスタの行からデータを読み出すことが感度增幅器に対して所望

10

20

30

40

50

されている時、R E A D 信号は 1 つの状態（例えば、高状態）を有し、S R A M レジスタの選択された行に符号化された画像データを書き込むことが所望されている時、反対の状態（例えば、低状態）を有する。既に説明されたように、S R A M アレイは符号化された画像データの二重バッファを提供し、それにより、入来画像に対応するデータが 1 つのバッファに書き込まれ得る一方、前の画像に対応するデータは第 2 のバッファから損なわれることなく読み出され得る。図 19 の目的のため、1 つの画像バッファ内の行アドレスは B 0 R i と示され、ここで i は行番号を示す一方、もう 1 つのバッファ内の行アドレスは B 1 R i と示されている。画素ブースト回路レジスタに対応する行アドレスは P R i と示されている。図 19 の左側に示されている時刻において、V A L I D は高く、有効な画像データが供給されていることを示している。このデータが供給されている間、このデータは画素ライン・バッファ 106 および 108 内のレジスタに一時的に書き込まれる。この間、R E A D は高状態にあり、C D P は保存されている符号化された画像データを画素アレイ上の濃度階調表示のために処理している。図 19 に示された実施例において、符号化された画像データは同図の左側の行 B 0 R 1 で開始してバッファ列体 B 0 から読み出されている。12 クロック後、データは行 B 0 R 1 から B 0 R 12 まで読み出され、この時点の後、C D P は、ブースト・セル内のレジスタに画素制御信号 1206 を書き込むために、十分な比較結果を蓄積している。このことを達成するために、R E A D はこの点で低くなり、フレーム・バッファ・レジスタを読み出し、かつ、画素を更新するサイクルを完了する。同図に示されたように、V A L I D はこのサイクル中は低く進行し得、入来ビデオ・データのラインの終端に印を付ける。したがって、制御ブロック 116 は画素ライン・バッファが満杯であることを認識する。例えフレーム・バッファからの画像データの読み出しの次のサイクルが既に（この図に示された実施例ではライン B 0 R 13 および B 0 R 14 からの読み出しを）開始していても、バッファ満杯信号はサイクルに割り込みを引き起こし、R E A D は低く進行し、かつ、画素ライン・バッファに保存されているデータは別のフレーム・バッファ列体に（この実施例では行 B 1 R 1 から B 1 R 6 に）書き込まれる。この書き込みが完了した後、R E A D は高く進行し、かつ、ブースト・レジスタへの書き込みが最終的に後に続く読み出しの通常サイクルが継続する。このように、1 つのフレーム・バッファからのデータの読み出しに別のフレーム・バッファへのデータの時々の書き込みを挟み込むことにより、表示装置は標準ビデオ・データを同時に受け入れ得る一方、擬似信号のない画像を表示する。入来ビデオ・データの新しいラインが 60 μ s 毎などに開始し、かつ、この期間の水平空白部分が約 11 μ s を占め、かつ、画素ライン・バッファを空にするために必要な時間が（出願人により典型的に使用されている 60 M H z 表示クロックに対して）6 個の表示クロック周期または約 100 n s に等しいとすれば、入来データを書き込むための要件は比較的たまにしか発生せず、かつ、比較的広範な間隔内のどこかで発生させられ得、ならびに、濃度階調方式の最低限の擾乱のみを引き起こす。

#### 【 0 0 6 0 】

##### 画像の圧縮 / 圧縮解除

本発明の特徴の 1 つは、制御部 116 に供給される入来画像データがシリコン背面 70 全体を通じて分配された S R A M 画像バッファ内での保存の目的のために圧縮可能であり、かつ、画素による最終的な表示のために圧縮解除可能であることである。圧縮アルゴリズムのいくつかの異なったタイプのいずれもこのことを達成するために利用可能である。1 つの手法は、先ず、R G B データを各画素に対する赤、緑、および、青の値から従来の Y U V システムまたは同システムの変形に変換することである。Y U V システムは輝度成分 (Y) および 2 つの色差信号 (U および V) を含む。Y C B C R で示された 1 つの共通の版において、色差信号は大部分は赤 (C R) および青 (C B) の情報を保存し、ここで（緑のほとんども含む）輝度が差し引かれる。以下のマトリクス変換は R G B 信号から標準 Y C B C R 信号を生成する。

#### 【 0 0 6 1 】

## 【数1】

$$\begin{bmatrix} Y \\ C_B \\ C_R \end{bmatrix} = \begin{bmatrix} 16 \\ 128 \\ 128 \end{bmatrix} + \frac{1}{256} \begin{bmatrix} 65.738 & 129.057 & 25.064 \\ -37.945 & -74.494 & 112.439 \\ 112.439 & -94.154 & 18.285 \end{bmatrix} \cdot \begin{bmatrix} R \\ G \\ B \end{bmatrix} \quad (1)$$

この式において、R, G, および、Bは0から255までの値を取る(正負符号のない8ビットの数)。Yは16から235の範囲にわたり、C<sub>B</sub>およびC<sub>R</sub>は16から240の範囲にわたる。いくつかの実施において、YC<sub>B</sub>C<sub>R</sub>値は、同期のための特別な符号の挿入を可能にするため、および、ビデオ電子回路における処理の余裕を許容するために、8ビットの範囲(0から255)のサブセットに制限されている。

10

## 【0062】

(例えばCRTモニタ上で、画像を実際に閲覧するために必要とされる)RGB値を復元するために、この変換を逆転可能である。

## 【0063】

## 【数2】

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \frac{1}{256} \begin{bmatrix} 298.082 & 0 & 408.583 \\ 298.082 & -100.291 & -208.120 \\ 298.082 & 516.411 & 0 \end{bmatrix} \cdot \begin{bmatrix} Y-16 \\ C_B-128 \\ C_R-128 \end{bmatrix} \quad (2)$$

他の同様のシステムよりも、むしろYUVシステムを使用するための1つの動機は、人間の視覚システムが異なった波長の光に対して異なった応答を有することである。例えば微小な空間的詳細を区別する能力は、輝度がより一定であり、かつ、詳細の色が変化している画像に対するよりも、詳細に輝度のある画像に対する方が高い。空間解像力も、赤または緑に対するよりも、青に対する方が低い。本発明の圧縮アルゴリズムは色に基づく空間解像力のこの差を利用している。アルゴリズムはRGBデータをYUVシステムの変形に変換する。

30

## 【0064】

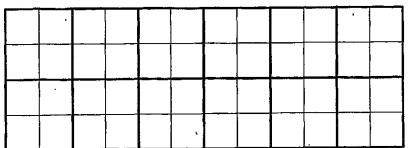

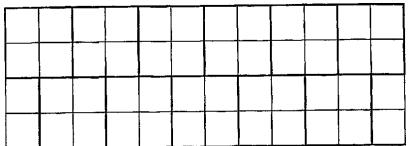

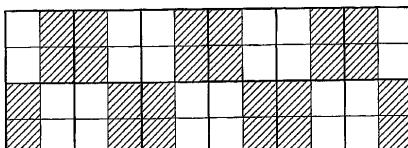

現行の標準サンプリング技術は(図20に示された)4:4:4、(図21に示された)4:2:2、および、(図22および23に示された)4:1:1などの用語により示されている。輝度情報を含む第1の成分、および、色差または他のタイプのいくつかの彩度情報を含む次の2つの成分を有するYUV型システムにおいて、用語4:2:2における3つの数字はこれらの成分の各々がサンプリングされる速度を表す。図20および21において、各四角形は各画素に対する独立した輝度サンプルを備えた独立した画素を表す。図20において、これらの四角形は各画素に対する独立したUおよびVの値を表す。図21において、太線の境界を持つ各長方形は、単一のU値および単一のV値と一緒に有する2つの隣接した画素を表す。したがって、4:2:2においてはY成分が色差成分と同じ頻度で2回サンプリングされ、4:1:1においてはY成分が(図22および23に示されたように、4つの画素を各々が含む太線の長方形により例示されたものと)同じ頻度で4回サンプリングされている。語句4:2:2はしばしば「放送用ビデオ」と呼ばれ、かつ、かなり高品質の画像圧縮フォーマットであると考えられている。最近の民生用デジタル・ビデオ・カムコーダはほとんど専ら4:1:1を使用している。この削減されたサンプリングは画像データの与えられた水平ライン内に通常発生する。したがって、720画素を含む走査線に対しては、図22に示されたように、4:1:1のサンプリング技術は720個の輝度(Y)サンプル、180個のC<sub>R</sub>サンプル、および、180個のC<sub>B</sub>サンプルを示唆する。これは4:1:1のNTSC版である。PALシステムは垂直の下位サンプリングも典型的に含む。例えば単一のC<sub>R</sub>サンプルを共有する4つの水平画素の代

40

50

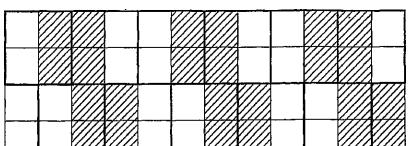

わりに、画素の  $2 \times 2$  領域は、図 2 3 に示されたように、単一の  $C_R$  サンプルを共有する。このことは、前の走査線を保存するために、ライン・バッファおよびデジタル・ビデオ・システムの追加を必要とするが、この追加はわずかにより満足できる画像を生成する。したがって、4 : 1 : 1 の P A L 版は、サンプリングの幾何学形状のこの差を強調するために、時々 4 : 2 : 0 と示されている。

#### 【0065】

本発明は各画素に対して 24 ビット R G B データ（赤、緑、および、青に対して各々 8 ビット）を受信し、かつ、同データを、画素当たり 12 ビットの平均値として保存可能な以下にさらに検討されるフォーマットに変換する。見られるように、画素は画素グループ 10 224 および 226 などの  $2 \times 2$  画素グループにグループ分けされ、そのため、各画素グループに対して、48 ビットのデータが各画像に対して保存される。二重バッファにより、データの 2 つの 48 ビット行が各画素グループに対して必要である。

#### 【0066】

さらに、制御部 116 により行われる符号化段における、および、復号化ブロック 20 0 などの C D P における復号化ブロックにより行われる復号化段におけるデータ処理を単純化するために、D E F と呼ばれる Y U V システムに関する新しい変形が作成されている。座標変換は、順方向変換に対して、

$$\begin{aligned} D_i &= (1/2) R_i + (1/2) G_i \\ E &= (-1/4) R_{ave} + (-1/4) G_{ave} + (1/2) B_{ave} \\ (3) \end{aligned} \quad 20$$

$$F = (1/2) R_{ave} + (-1/2) G_{ave}$$

となり、逆変換に対しては、

$$\begin{aligned} R_i &= D_i + F \\ G_i &= D_i - F \\ B_i &= D_i + 2E \end{aligned} \quad (4)$$

となる。ここで、下付  $i$  は単一の画素に対する値を示す一方、E および F は、いくつかの画素にわたり平均された  $R_{ave}$ 、 $G_{ave}$ 、および、 $B_{ave}$  の値に基づいている。

#### 【0067】

D、E、および、F は Y U V システムの変形であるこの新しい色空間を表すために任意に選択された 3 つの文字である。これらの文字は、R G B、Y U V、 $C_R$ 、および、 $C_B$  などの他の色空間方式に共通な文字の使用を回避することを求める以外に特に意味は有さない。座標変換が、上記の式 1 および 2 に示されたように、R G B と Y U V フォーマットの間で変換するために必要となる浮動小数点計算よりも、むしろ整数計算で行われることに注意されたい。D E F 色空間が、微小表示装置の内部の画像の保存の目的に対する仮の色空間としてのみ意図されているために、D、E、および、F が表すものの意味は、Y U V システムとは異なり、幾分か任意である。

#### 【0068】

画素当たり現に 12 ビットのフレーム・バッファを必要とする上記に説明されたサンプリングに対する代案として、画素当たり 10 ビットのフレーム・バッファを現に必要とするために 12 : 2 : 1 フォーマットでサンプリングすることも可能である。40

#### 【0069】

理解されるように、図 5 および 11 に戻って参照すると、制御部 116 に供給された画像データは 24 ビット R G B データとし得る一方、制御部 116 からライン・バッファならびに列駆動装置列体 106 および 108 に供給された符号化された画像データ 172 は（画素当たり 12 ビットの平均値に対して、4 つの画素に関連した画像内容を符号化する 48 ビットを備えた）D E F フォーマットになっている。続いて、この D E F フォーマットのデータは垂直分層内の S R A M メモリ・セル 180 内に保存され、後に、感度増幅器 176 により読み出され、かつ、上述の比較動作に先立ち、D E F データが R G B データに変換し戻される垂直分層の復号化ブロック 200 に供給される。

#### 【0070】

10

20

30

40

50

本発明において利用可能であるタイプのサンプリングに対しては多くの代案がある。この代案は、 $2 \times 2$  画素グループの各々がその下の $2 \times 2$  画素グループと整列されている（図 23）もの、または、第 1 の $2 \times 2$  画素グループの隣の隣接した 1 対の行内の $2 \times 2$  画素グループが 1 画素分だけ水平にずらされ得て（図 24）、そのため、 $2 \times 2$  画素グループが垂直には整列されていないものなどの 4 : 1 : 1 に等価の符号化に対する多くの変形も含み得る。（図 25 に示された）別の変形は、（太線の境界により示された）彩度成分の 1 つ（例えば、E または F 成分）に対する異なった $2 \times 2$  画素グループを定義するため、および、（斜線の不在または存在により示された）2 つの彩度成分のもう 1 つに対する異なった $2 \times 2$  画素グループを定義するためである。すなわち、E 成分に対する画素グループは F 成分に対する画素グループと 2 つの画素のみを共有している。そうでなければ、E 成分画素グループは互いに垂直に整列され、F 成分画素グループは互いに垂直に整列され得る。この変形に対するさらなる変形として、隣接した行の他の各対において水平に 1 つの画素分のずれが存在し得（図 26）、そのため、E 成分画素グループは垂直に整列されず、かつ、F 成分画素グループも垂直には整列されない。別の変形は、 $2 \times 2$  アレイではない 4 画素のグループを定義することである（図 27）。例えば、画素グループは、L 字型を達成するために、1 つの行上の 3 つの画素および隣接した行内の 1 つの画素からなり得る。次の隣接した画素グループは、同じく L 字型を達成し、かつ、2 つの L 字型を、2 画素の高さおよび 4 画素の幅である画素グループの組合せに一緒に嵌め合うために、隣接した行上の 3 つの画素および元の行上の 1 つの画素を有し得る。この配列は、例えば、彩度成分の双方に対して、または、本来の $2 \times 2$  配置構成を有する他の彩度成分を持つ 1 つだけに対して行われ得る。見られるように、彩度の組合せのほぼ終わりのない変形がある。これらの変形に対してはいくつかの方法があり、1 つは垂直方向に色差のサンプルの開始位置を互い違いにすることである。このことは、圧縮技術においてサンプルの垂直補正が多すぎれば、画像内に発生し得る垂直の縞模様の外観に対処することを意図されている。別の方法は 2 つの彩度サンプルを互いを基準として移動させることである。さらに別の方法はサンプリングの幾何学形状のタイプを変化させることである。同様に、人間の視覚システムは青い光に比較的感度が低いため、下位成分として青い光を有する E 成分は F 成分より低い速度でさえサンプリングされ得る。1 つの手法は、画素当たり平均 10 ビットを必要とする 12 : 2 : 1 サンプリング技術である。（図 28 に示された）この場合、各画素は自身の D 値を有する一方、 $3 \times 2$  画素グループは F 値を共有し、 $6 \times 2$  画素グループは E 値を共有する。

#### 【0071】

したがって、特定の垂直分層内の S R A M の各行が、 $2 \times 2$  の画素アレイまたは画素グループに対する（定義された D E F フォーマットにおける）符号化された輝度および彩度の情報を表す 48 ビットのデータを含むため、および、画素の行全体を同時に書き込むことが所望されている（実際に、画素の 4 つの行に相当する 1 つの行のブースト回路に書き込むことが所望されている）ため、12 個の異なった読み出し、画素の行の 4 つに所望の状態を復号化し、比較し、かつ、書き込むために必要な情報のすべてを得るために異なった 48 ビットの行の各々が必要となることが理解され得よう。比較が行われると、その比較の結果は 48 ビットのレジスタに徐々に保存されていく。このレジスタが（48 個の比較結果で）満杯となった後、蓄積された値は、单一の書き込み動作におけるブースト回路レジスタへの変更の書き込みを（特定の比較の結果が等しい場合に）可能にするために、または、（異なった特定の比較の結果が等しくない場合に）可能にしないために使用される。

#### 【0072】

微小表示装置 44 の電力節減の特徴は、レジスタ内のデータがブースト回路への書き込み可能として機能するし、したがって、0 または 1 の状態の 1 つにおけるビット・ラインへの変更を引き起こすのみであるということである。これにより、ビット・ラインが充電 / 放電される必要のある回数が削減される。

#### 【0073】

E および F が 127 と 128 の間の正負符号付きの数であり、D が 0 と 255 の間の正

10

20

30

40

50

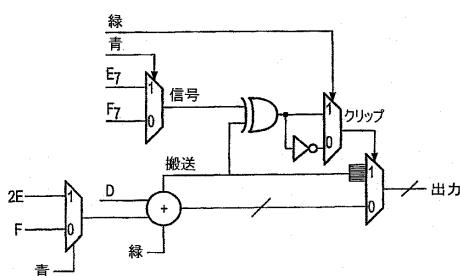

負符号のない数であるため、無効な R G B 値に（式 4 を介して）変換する有効な D E F 値を有することが可能である（例えば、R、G、または、B は 0 未満または 255 を超える値を有する）。変換された値を比較することにより従来の方法で 0 および 255 にクリッピングすること、および、もしこれらの値が許容範囲を超えた場合に行動を起こすことは可能であるが、シリコンの面積を消費しすぎる可能性が高い。図 13 は、D E F から R G B への変換により 0 から 255 の範囲の外でのいかなる値の発生も防止するために、各復号化ブロック 200 の一部として含まれた簡略化されたクリッピング回路を示す。式 4 から分かり得るように、D E F から R G B への変換は入力として D<sub>i</sub>、2 E、および、F を必要とする。復号化信号 202 は、例えば G R E E N および B L U E と呼ばれる 2 つのライン上で供給される。C D P が比較器に緑の復号化画像データを供給している時、G R E E N は活性化され、B L U E は不活性化されている。C D P が青の復号化画像データを供給している時、B L U E は活性化され、G R E E N は不活性化されている。C D P が赤の復号化画像データを供給している時、G R E E N および B L U E の双方が不活性化されている。G R E E N および B L U E の双方が同時に活性となることは回避される。第 1 の多重化器は B L U E の状態によって 2 E と F の間で選択し、多重化器の出力は加算器への第 1 の入力として供給される。信号 D は加算器への他の入力として供給され、加算器は自身の搬送入力において信号 G R E E N も受け入れる。加算器の出力は第 2 の多重化器に供給される。加算器の搬送出力は専用 O R ゲートに入力として供給される。専用 O R ゲートへの他の入力は E および F（各々の M S B）からの正負符号ビットを受信する第 3 の多重化器から供給される。第 3 の多重化器は B L U E 復号化信号により制御され、そのため、青が復号化される時に E の正負符号ビットが使用され、そうでなければ、F の正負符号ビットが使用される。したがって、加算器からの選択された正負符号ビットおよび搬送ビットは専用 O R ゲートへの入力であり、かつ、もし入力が異なっていれば、出力は論理 1 となり、もし入力が同じであれば、論理 0 となる。この出力およびその逆数は第 4 の多重化器への 2 つの入力として供給される。第 4 の多重化器は G R E E N 復号化信号により制御され、そのため、緑が復号化される時、専用 O R の逆転出力が使用され、そうでなければ、専用 O R の逆転出力が使用される。もし第 4 の多重化器の出力が論理 0 であれば、このことは、クリッピングが必要なく、加算器の 8 ビット出力が使用されることを意味する。しかし、もし出力が論理 1 であれば、このことは、クリッピングが必要であり、加算器の出力の代わりに搬送ビットが（当然、搬送ビットの同じ値の 8 ビットに拡張されて）選択されることを意味する。したがって、255（二進法で 11111111）または 0（二進法で 00000000）のいずれかが供給される。

#### 【0074】

本発明の 1 つの態様は、画素の表示を制御するための保存レジスタからの分配フレーム・バッファ内のデータ保存の論理的分離である。これらの 2 つの保存位置は論理的に分離される一方、共通の物理的アクセス機構（C D P、感度増幅器、列駆動装置、および、行制御部）はこの 2 つの保存領域に機能的に相互関連している。

#### 【0075】

##### 濃度諧調モード

本発明の微小表示装置は、この装置のフィールド順次カラーの性質により 120 個の赤の画像、120 個の緑の画像、および、120 個の青の画像を意味する毎秒 120 の完全カラー画像を供給可能である。このことは、同装置が毎秒 360 個の画像を表示することを根本的に意味し、それは、1 秒の 360 分の 1 毎または各 2.78 ミリ秒毎に新しい画像または少なくとも新しいカラー・フィールドを意味する。これらの 2.78 ミリ秒の間隔の各々の間、符号化されたデータが S R A M メモリ・セルから読み出され、復号化され、かつ、ランプ信号 114 と 255 回比較される。したがって、1 秒のこれらの 360 分の 1 の各々はランプ信号 114 の 255 のタイム・スロットに分割される。このことは、秒当たり  $360 \times 255$  個のタイム・スロットがあることを意味する。したがって、各タイム・スロットは最大で 10.9 ミリ秒の長さがある。これらのタイム・スロットの各々の間、新しいデータが各画素の保存レジスタに、このデジタル・パルス幅変調手法で各画

10

20

30

40

50

素の状態を変更するために書き込まれ得る。

【0076】

色当たり 512 個のデータ比較（表示される 256 個および DC バランスのための 256 個）を備えた 3 つの色の各々の 8 ビットを表示する 3X（入力フィールド周波数の 3 倍の）モードが説明された一方、微小表示装置 44 はいくつかの他の表示モードにも対応する。1 つは 3 つの色の各々の 7 ビットを表示する 6X モードである。このモードはフィールド当たりで色当たり 512 個のデータ比較を有する。もう 1 つは 6X8 ビット S p 1 i t M S B 7 - 4 モードである。2 つの表示ランプの各々で 6 ビットのみを表示することにより、このモードは、利用可能な最低電力アルゴリズムを備えた表示フィールド内に 8 ビット濃度譜調解像度を送達する。フィールド当たりで色当たり合計 192 個のデータ比較 10 に対して、第 1 のアルゴリズム・サイクルは 32 個のデータ比較を有し、第 2 のアルゴリズム・サイクルは 64 個のデータ比較を有する。もう 1 つは 6X8 ビット A d d L S B モードである。このモードは第 1 のアルゴリズム・サイクルの間は 7 ビット・モードで、かつ、第 2 のアルゴリズム・サイクルの間は 8 ビット・モードで運転する。L S B のオン・スイッチの場合の色値は L S B がオフの場合よりも後で循環する。このことは、L S B が第 2 の 7 ビット・ランプに追加された波形を生成する。このモードはフィールド当たりで色当たり 512 個のデータ比較を有する。

【0077】

S R A M

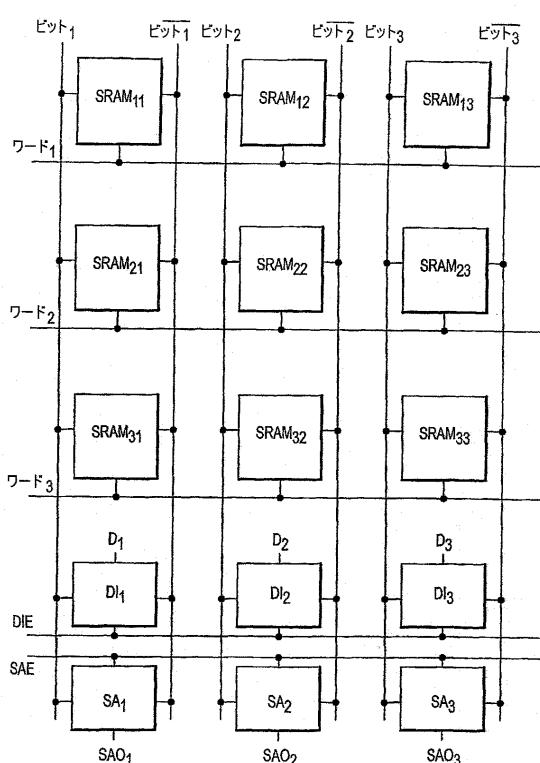

図 14 はシリコン背面 30 の層 130 内の S R A M メモリ・セルのアレイの一部を示す 20 。例示の容易さのために、S R A M メモリ・セルの 9 つのみが 3 つの行に示されており、各々は隣接した行内に対応するセルを備えた列内に配列されている。図 14 の S R A M メモリ・セルは、S R A M メモリ・セルに対する行の数である X および列の数である Y を使用して S R A M <sub>X Y</sub> とラベル付けされている。S R A M メモリ・セルの各列は、同列に接続された B I T 線の対 B I T <sub>Y</sub> および B I T <sub>Y Z</sub> を有し、ここで、Y は B I T 線に対する列の数である。S R A M メモリ・セルの各行はワード・ライン W o r d <sub>X</sub> を有し、ここで、X はワード線に対する行の数である。S R A M メモリ・セルの各列に接続されているのは、D I <sub>Y</sub> と示された单一の「データ・イン」回路であり、ここで Y は列の数であり、および、S A <sub>Y</sub> と示された感度増幅器であり、ここで、Y は列の数である。データ・イン回路 D I <sub>Y</sub> の行は各々がデータ・イン回路の行全体を可能にするために機能するデータ・イン可能信号（D I E）を受信する。各感度増幅器回路（S A <sub>Y</sub>）は感度増幅器の行全体を可能にする増幅器可能信号（S A E）を受信する。データ・イン D A <sub>Y</sub> および感度増幅器 S A <sub>Y</sub> も B I T <sub>Y</sub> および B I T <sub>Y Z</sub> 線に接続されている。なぜなら、これが、データがどのようにして S R A M メモリ・セルに書き込まれ、かつ、これから読み出されるかだからである。各データ・イン回路 D I <sub>Y</sub> は選択された S R A M メモリ・セルに書き込まれるデータを示す分離データ信号 D <sub>Y</sub> を受信する。各感度増幅器回路 S A <sub>Y</sub> は、選択された S R A M メモリ・セルから読み出された値を示す感度増幅器出力信号 S A O <sub>Y</sub> を供給する。 30

【0078】

例えば、その同じ特定の行内の別の S R A M メモリ・セルに関連なく、データがいずれかの個々の S R A M メモリ・セルに書き込み、または、それから読み出しえても、同時に S R A M メモリ・セルの行全体にデータを書き込むこと、および、同時に S R A M メモリ・セルの行全体からデータを読み出すことは最も典型的である。もし図 14 に示された第 2 の行にデータを書き込むことが所望されたとすれば、データ D <sub>Y</sub> は D I <sub>Y</sub> 回路の各々に供給され、データ・イン可能 D I E 信号は論理 1 に設定される。W o r d <sub>2</sub> ラインも同じく論理 1 に設定され、そのため、データ D <sub>Y</sub> はデータ・イン回路 D I <sub>Y</sub> により B I T <sub>Y</sub> および B I T <sub>Y Z</sub> 線上に置かれる。論理 1 になっている W o r d <sub>2</sub> ラインにより可能となっている S R A M メモリ・セルの第 2 の行は、以下にさらに説明されるように、B I T <sub>Y</sub> および B I T <sub>Y Z</sub> 線にアクセスし、かつ、同線内の値を保存する。続いて、W o r d <sub>2</sub> および D I E 信号は論理 0 に戻され得る。S R A M メモリ・セルの第 2 の行からデータを読み出すことが所望されると、W o r d <sub>2</sub> ラインは論理 1 に設定され、S R A M メモリ・セル 40

の第2の行S R A M<sub>2Y</sub>は感度増幅器回路S A<sub>Y</sub>により読み出されるB I T<sub>Y</sub>およびB I T<sub>YZ</sub>線に関する情報を供給する。一旦、感度増幅器可能信号S A Eが論理1に設定されれば、感度増幅器回路S A<sub>Y</sub>は活性化され、B I T<sub>Y</sub>およびB I T<sub>YZ</sub>線に関する情報を読み出し、かつ、S A O<sub>Y</sub>線において出力信号を供給する。

### 【0079】

#### 低電力の特徴

多くの微小表示装置応用例において、微小表示装置により消費される電力を最小に抑えることは重要である。本願明細書において開示されている微小表示装置は、微小表示装置の電力消費量全体へのS R A M動作の寄与を最小に抑えるためのいくつかの特徴を組み込んでおり、この寄与は、そうでなければ、非現実的に大きい。内容を本願明細書に援用するケラー(Khella h)、「A Low-Power High-Performance Current-Mode Multiport S R A M」、IEEE Transactions On VLSI Systems、第9巻第5号、590から598ページ(2001年10月)、ならびに、ブラロック(Bla lock)およびジャガー(Jaeger)、「A High-Speed Clamped Bit-Line Current-Mode Sense Amplifier」、IEEE Journal of Solid-State Circuits、第26巻第4号、(1991年4月)に例証されているように、電流モード動作を使用することによりS R A Mにより引き出される電力を最小に抑えることを求めるることは、メモリ技術において知られている。電流モード動作において、B I T<sub>Y</sub>およびB I T<sub>YZ</sub>線の双方はほぼ不变の電圧レベルに保持され、かつ、両線に(書込み中に)注入される、または、これらから(読み出し中に)検出される差分電流はメモリを動作させるために使用される。ビット線の電圧振動Vを小さく保つことにより、ビット線の容量Cを充電および放電することにより引き起こされるC V<sup>2</sup>の電力放散は小さく保たれる。本微小表示装置の構成においては、多くの読み出し動作が各書き込み動作に対して発生し、そのため、読み出し中の電力消費量は表示装置の電力消費量全体に対して実質的により重要となる。出願人は本微小表示装置の設計中に電流モードの教示を適用しようと試みたが、当技術分野において知られている電流モード感度増幅器が出願人の微小表示装置における使用に十分には適さないことを見出した。従来技術の電流モード感度増幅器はこの微小表示装置S R A Mの列間隔により必要とされたきつい間隔で配置することが困難であった。さらに、適切な感度増幅器の感度に対して必要とされたバイアス電流は出願人の微小表示装置のS R A Mアレイに対して感度増幅器の大きな電力放散をもたらした。したがって、電流モード動作の使用は本願における本微小表示装置の低電力の目的を凌駕した。

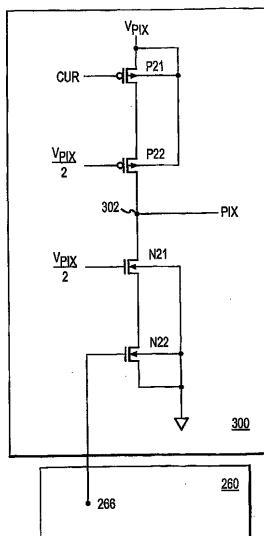

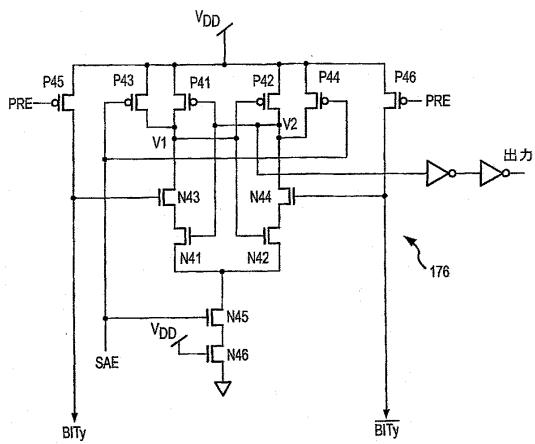

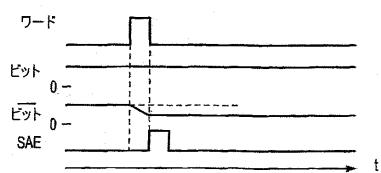

### 【0080】

本微小表示装置の新規な低電力設計およびS R A Mアレイの動作が図29aおよび29bに示されている。図29aは感度増幅器176に対する回路の概略を示す。感度増幅器176は精密電圧比較器として機能する。S R A Mビット線B I T<sub>Y</sub>およびB I T<sub>YZ</sub>は感度増幅器の入力をトランジスタN43およびN44のゲートに接続する。同じく図29bを参照すると、増幅器は以下のように動作する。読み出しに先立ち、感度増幅器可能信号S A Eは低く保持され、増幅器内のいかなる電流も遮断する一方、内部のノードV1およびV2を高くV<sub>DD</sub>に引き上げる。ビット線も信号P R Eの制御下でP45およびP46の作用により高くV<sub>DD</sub>に引き上げる。S R A Mの読み出しに先立ち、P R Eは高い状態に移り、ビット線を開放回路に移らせる。次に、W o r d線は、選択された行のS R A Mレジスタをビット線に接続するために高い状態のパルスが送られる。S R A Mセルの1つの側は既に高いが、別の側はビット線の1つを低く引き下げ始めている。(ここで示されている実施例におけるB I T<sub>YZ</sub>)。ワード線パルスはビット線の電圧振動を制限するために短く保たれている。典型的な動作において、W o r d線パルスの幅は4 n sとし得、この幅の間、ビット線は200 m Vのオーダに到達する。次に、感度増幅器は高く上がりつつある信号S A Eにより可能とされる。このことは内部ノードV1およびV2を解放し、かつ、N45およびN46を介して電流も流れさせる。(この実施例では200 m Vの才

10

20

30

40

50

ーダにある)小さな差分電圧がN43とN44のゲート間に出現したとすれば、V1およびV2の内部ノードの1つは他方より速く降下する。N42およびP42のゲートに対してV1の、および、N41およびP41のゲートに対してV2の交差結合により発生されたフィードバックは、ビット線間の小さな電圧差により決定された状態に、感度増幅器を迅速に固定させる。感度増幅器の出力は選択されたSRAMレジスタに本来保存されている状態を明らかにする。

#### 【0081】

感度増幅器176の重要な特徴は、同増幅器が非常に小さな電量消費量で電圧モードで動作すること、および、同増幅器が非常に小さな配置にしやすいことである。SRAMアレイの読み出し中の電力消費量は、ビット線上の発展した電圧振動を最小に抑え、それにより、 $CV^2$ 電力放散を低く保つように機能するWord線の短いパルス化された動作により最小に抑えられる。ビット線振動を200mVに制限することにより、 $CV^2$ 電力放散は、ビット線が $0.25\mu\text{m CMOS}$ 工程に対して典型的な $V_{DD} = 2.5\text{V}$ の仕切りまで終始振動されているモードで動作中の従来のSRAMに比較して150の係数で低減される。

#### 【0082】

電力消費量をさらに削減するために、本微小表示装置のSRAMアレイにおいては、他の技術が使用されている。分割線100に沿ってアレイを半分に切断することは、電力およびクロックの分配の節減に役立つ。書き込みサイクルの数を制限することは電力を節減する。

#### 【0083】

##### 画素ブースト回路

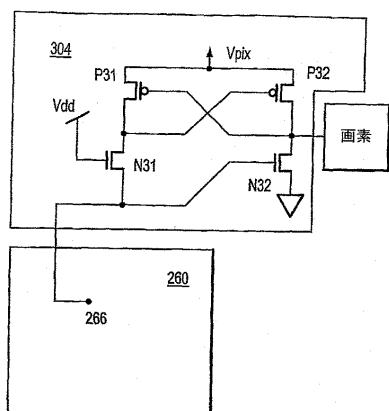

ブースト回路188についてのさらなる詳細は図15a、15b、および、15cに与えられている。ブースト回路は、図15aおよび15bに示されたようにカスコード配列における標準論理低電圧トランジスタから、または、より高電圧のI/Oトランジスタを使用することにより、かつ、図15cに示されたように構築され得る。

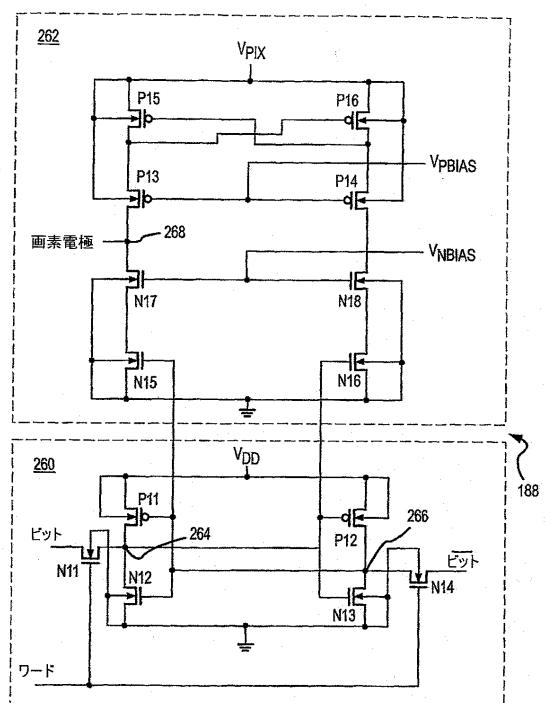

#### 【0084】

##### カスコード型ブースト回路

図15aに示されたブースト回路の実施形態は保存レジスタ部分260およびブースト部分262を含む。ブースト回路のトランジスタの各々はエンハンスマント・モードのデバイスである。同トランジスタは、ワード線により制御される1対のNチャンネル・アクセス・デバイスN11およびN14を含む。ワード線により論理1にオンとされると、これらのアクセス・デバイスN11およびN14は、保存レジスタ260の残りがそれぞれB<sub>IT</sub>およびB<sub>ITz</sub>線に接続されることを可能にする。保存レジスタ260の残りは、1つのインバータがP11およびN12を含み、第2のインバータがP12およびN13を含む1対のインバータを含む。ワード線が論理1に移行されると、B<sub>IT</sub>線の電圧はN12とP11の間に所在するノード264上に印加される。同様に、N14がオンとされ、B<sub>ITz</sub>線の電圧がN13とP12の間のノード266上に印加される。これらのノード264および266の各々が逆のインバータのゲート端末に接続されているため、この状態はアクセス・デバイスN11およびN14がオフとされた後でさえも維持される。P11およびP12のソース端末はV<sub>DD</sub>に接続されている。N11、N12、N13、および、N14の各々はアースに接続された自身のPウェル・シリコン基板を有する一方、P11およびP12はV<sub>DD</sub>に接続された自身のNウェルを有する。

#### 【0085】

N12およびP11のゲート端末はブースト部分262のN15のゲート端末にも接続されている。N13およびP12のゲート端末はブースト部分262のN16のゲート端末にも接続されている。したがって、N15はオフとされ、N16はオンとされる。N15およびN16のソース端末はアースに接続されている。N15およびN16のドレイン端末はそれぞれN17およびN18のソース端末に接続されている。N17およびN18のゲート端末は2.5ボルトの電圧で固定バイアス信号VNBIASに接続されている。

10

20

30

40

50

N17およびN18のドレイン端末はそれぞれP13およびP14のドレイン端末に接続されている。P13およびP14のゲート端末は可変電圧バイアス信号VPBIASに接続されている。P13のドレイン端末とN17のドレイン端末の間のノード268はその特定のブースト回路に対する画素電極に接続されている。P13およびP14のソース端末はそれぞれP15およびP16のドレイン端末にそれぞれ接続されている。P15およびP16のソース端末は一緒に、かつ、独立した電圧源VPIXに接続されている。P16のゲート端末はP15のドレイン端末に接続されている一方、P15のゲート端末はP16のドレイン端末に接続されている。N15、N16、N17、および、N18の各々はアースに接続された自身のPウェル・シリコン基板を有する一方、P13、P14、P15、および、P16はVPIXに接続された自身のNウェルを有する。

10

#### 【0086】

この実施例において、ゲートN15はオフとされ、かつ、ゲートN16はオンとされ、ならびに、 $V_{DD}$ が2.5ボルトの値であり、 $V_{P_{IX}}$ が4ボルトの値であることが仮定されている。VPBIASは可変であり、かつ、約0.5ボルトの最小値を持って $V_{P_{IX}}$ 未満の約2.5ボルトに制御可能である。VNBLASはグランドより約2.5ボルト高い電圧を有するように固定される。VNBIASは、N17およびN18に継続的に伝導させる一方、VPBIASはP13およびP14にも継続的に伝導させる。N16がオンであるため、N16とN18のドレイン・ソース接続ならびにN18とP14のドレイン-ドレイン接続にかかる電圧は約ゼロ・ボルトである。P14のゲートが $V_{P_{IX}}$ から2.5ボルトを差し引いた電圧であるため、このデバイスのソース電圧がゲート電圧より高い約0.45ボルトの閾値電圧未満であると、デバイスは伝導を停止する。したがって、この実施例に対するP14のソース電圧は(4V - 2.5V) + 0.45Vまたは約ゼロ・ボルトのP14のドレイン電圧より1.95高い。P14のソースはP15のゲートに接続されているため、P15は伝導する。なぜなら、2.05VのP15のソース・ゲート電圧は0.45Vの必要閾値電圧より十分高いからである。P15は伝導するため、P15のドレインおよびP16のゲートは約4Vとなり、このことはP16をオフとする。P13のゲートがVPBIASにあるためにP13が伝導するため、P13のドレインは4ボルトの $V_{P_{IX}}$ 電圧となる。このように、P15がオンであり、かつ、約 $V_{P_{IX}}$ の電圧がP13のドレイン端末に印加されると、可変VPBIASゲート電圧は、P13のゲート端末とソース端末の間の電圧が2.5ボルトであることを確実にする一方、ソース・ドレイン電圧は約0ボルトであり、かつ、いかなる状況でも2.5ボルトを超えることはない。このことは、高いソース・ゲート電圧が、ホット・キャリアまたは酸化物の破壊によりP13に過剰な応力をかけ、かつ、損傷を与えることを防止する。このようにP13がオンになると、続いて、画素電極に接続されたノード268での電圧が $V_{P_{IX}}$ にほぼ等しくなる。同時に、ゲートが2.5VにバイアスされたN17が、自身のソースが自身のゲート電圧2.5V - 0.45 = 2.05Vを下回る1つの閾値電圧に近づくに従い、伝導を停止する。このように、N17への高電圧損傷が防止される。なぜなら、2.05Vのソース・ゲート電圧および1.95Vのソース・ドレイン電圧が2.5Vデバイスにより十分に耐えられるからである。より高い画素電圧は、ソース・ゲートおよびソース・ドレインの全デバイス端末にかかる最大電圧を制限するために、隔離ウェルNチャンネルおよびPチャンネル・デバイスに、注意深く制御された対応するバイアス電圧を挿入することにより、同様の方法で制御可能である。温度および他の環境条件などの様々な影響を補償するために、 $V_{P_{IX}}$ がこの実施形態においては1.1と1.2ボルトの間の最小値および5ボルトの最大値における電圧から変化可能であることが理解され得る。 $V_{P_{IX}}$ が補償のこれらの理由に対して変化されるに従い、VPBIASも変化され、そのため、ブースト回路188内のゲートのいずれにも過剰応力はかけられない。

20

#### 【0087】

代案カスコード実施形態は図15bに示されている。図15aに示された回路におけるように、同実施形態は保存レジスタ部分260およびブースト部分300を含む。図15bの実施形態において、ブースト部分300は4つのトランジスタP21、P22、N2

30

40

50

1、および、N 2 2 のみを含む。N 2 2 のゲートは保存レジスタ部分 2 6 0 のトランジスタ N 1 2 (ノード 2 6 6 )のゲートに接続され、このノードは、レジスタに 0 が保存されているか、1 が保存されているかによって 0 V または  $V_{DD}$  になっている。N 2 1 および P 2 2 のゲートは双方とも、現在  $V_{P_{IX}}/2$  に設定されているバイアス電圧  $V_{PBIAS}$  に接続されている。P 2 1 のゲートは、P 2 1 に、P 2 2 に向かう小さな電流、例えば 8 nA を供給する電流源として機能させるように選択された独立したバイアス電圧  $CUR$  に接続されている。画素電極は P 2 2 と N 2 1 の間のノード 3 0 2 に接続されている。N 2 2 のゲートが低く、N 2 2 はオフとされ、かつ、N 2 1 または N 2 2 を介しては電流が流れていな時は、 $V_{PBIAS}$  は P 2 2 をオンに保ち、小さな電流はノード 3 0 2 および画素電極を  $V_{P_{IX}}$  に素早く充電する。N 2 2 のゲートが高い状態の時、N 2 2 はオンとされ、電流がアースに流れることを可能にする。N 2 1 のゲートにおける  $V_{PBIAS}$  は N 2 1 もオンに保ち、ノード 2 6 8 および画素電極がアースに放電することを可能にする。小さな電流はこの状態において継続して流れている。10

#### 【0088】

##### 高電圧トランジスタ・ブースト回路

図 15 a および 15 b に関して上記に説明されたカスコード・ブースト回路に対する代案として、ブースト回路は、I / O に対して頻繁に必要とされるより高い電圧レベルで動作するように設計された多くの低電圧 CMOS 工程において利用可能である如くのトランジスタを使用して実施可能であり、トランジスタは中核論理トランジスタより厚いゲート酸化膜を通常利用している。このようなブースト回路は図 15 c に示されている。同回路は保存レジスタ部分 2 6 0 およびブースト回路部分 3 0 4 を再び含む。図 15 c の実施形態において、ブースト部分 3 0 4 は、各々が全電圧  $V_{P_{IX}}$  に耐えるように設計された 4 つのトランジスタ N 3 1 、 N 3 2 、 P 3 1 、および、 P 3 2 から作成されている。この目的に対して有用なトランジスタは、中核論理  $V_{DD}$  値より高い電圧を必要とする I / O 機能を実行するために多くの低電圧 CMOS 工程において供給されるトランジスタを含む。このようなトランジスタは、典型的に、中核論理トランジスタに対して設けられたゲート酸化膜よりも厚いゲート酸化膜を使用して作成される。回路のブースト部分はレジスタ部分 2 6 0 の内部のノード 2 6 6 により再び駆動され、このノード 2 6 6 はレジスタに保存されたビットの値によって電圧ゼロまたは  $V_{DD}$  を有する。ノード 2 6 6 が低い状態の時、N 3 1 は自身のゲートに印加された  $V_{DD}$  によりオンとされ、N 3 1 と P 3 1 の間のノードは低い状態に引き下げられ、P 3 2 をオンとし、画素電極を高く  $V_{P_{IX}}$  に引き上げる。ノード 2 6 6 が高い状態の時、N 3 1 はオフとされるが、N 3 2 はオンとされ、画素電極を低くアースに引き下げる一方、P 3 2 をオフとする。20

#### 【0089】

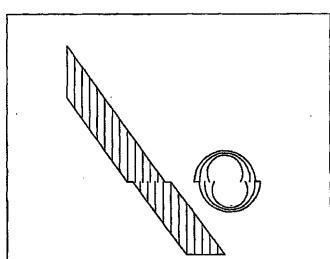

##### 温度センサ

本発明の微小表示装置 4 4 は、動作温度の結果としての微小表示装置 4 4 の性能の変化、および、それにより生成された画像への影響を補償するために使用可能である温度補償方式も含む。例えば、微小表示装置に使用されている液晶材料の応答は液晶材料の動作温度により異なり得る。この場合、温度に基づく液晶材料の異なった切換え速度を補償するために、液晶材料に対して異なった駆動電圧を使用することが望ましい。異なった駆動電圧を選択することにより、液晶の切換え速度を温度変化とは独立にすることが可能となり得る。上記に説明されたように、画素電極に対しては異なる駆動電圧を選択することが可能である。微小表示装置 4 4 における温度変化を感知するための回路 2 8 0 が図 16 に示されている。より詳細には、回路 2 8 0 はシリコン背面 7 0 内に所在しても、しなくてよい。回路 2 8 0 は従来のバンドギャップ参照回路に対する変形とし得る。バンドギャップ参照回路は、第 1 次に対して温度である電圧を供給し、独立に供給することを意図されている。この場合、回路 2 8 0 は定電流源 2 8 4 により駆動されている並列の 8 つのダイオードのグループ 2 8 2 を含む。ダイオードのグループ 2 8 2 にかかる定電流源 2 8 4 からの電流により展開された電圧は、増幅器 2 9 0 の正端末への入力として供給される。電圧は、抵抗 2 8 6 および 2 8 8 を含む電圧駆動装置にかかるバンドギャップ電圧によって304050

も展開される。抵抗 286 にかかる電圧は増幅器 290 の負端末への入力として供給される。フィードバック抵抗 292 は増幅器 290 の利得を決定する。ダイオードのグループ 282 にかかる電圧は、温度が摂氏 20 から 100 度に変化するに従い、約 0.7 ボルトから 0.4 ボルトに変化する。増幅器 290 からの出力は同じ温度範囲に対して 1.6 ボルトから 0.0 ボルトに変化する。同図には示されていない増幅器 290 および従来の下流回路は、電源から所望の電圧源 ( $V_{P_{IX}}$ ) を供給するために、電圧のこの変化を定量化し、電源を制御するために使用されている。この電圧はシリコン背面の動作温度に比例し、温度補償のために使用可能である。温度センサ電圧をデジタル化し、平均温度値を保存されている設定点と比較する制御部 116 に、この電圧は供給される。温度が、保存された設定点に到達すると、 $V_{P_{IX}}$  電圧は、温度の設定点に関連して保存されている電圧値に、多くのフレームにわたり徐々に調整される。画素電極に印加された信号のタイミングも同様に変化し得る。他の環境条件を感知すること、および、駆動信号または照明の電圧またはタイミングを変化させることにより、同条件を補償することが可能である。

#### 【0090】

##### 表示装置の動作

上記に説明された微小表示装置の様々な特徴は、以下に説明されるように、電力消費量が低減されて、広範な動作温度範囲にわたり、より優れた表示画面品質を生成する。

#### 【0091】

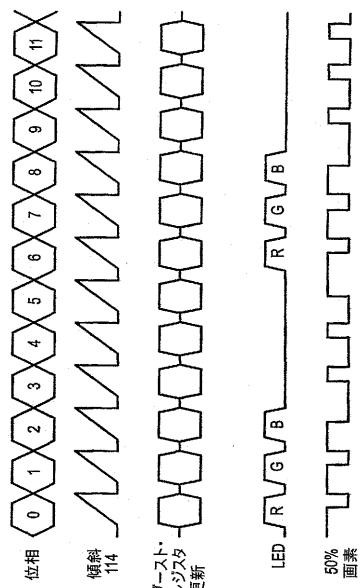

##### 順次カラー・モードおよびDCバランス

望ましい技術で知られているように、順次カラー表示装置において柔軟性を提供するために、および、液晶駆動信号のDCバランスに対処するために、本発明の微小表示装置はビデオ入力データの各フレームに関連したフレーム時間をいくつかの位相、例えば図30に示された如くの 12 の相に分割する。各位相の間、以下の表に掲げられた変数は独立に制御可能である。

#### 【0092】

##### 【表1】

| VAR. # | 変数      | 値                                                                                              |

|--------|---------|------------------------------------------------------------------------------------------------|

| 0      | 発光      | 0=LED off; 1=LED on                                                                            |

| 1,2    | 相カラー    | 00=Red, 01=Green, 10=Blue                                                                      |

| 3      | 画素オン    | 0=pixel switches to 0, 1=pixel switches to 1                                                   |

| 4      | 充満Dir   | 0=Fill outside to in, 1=Fill inside to out                                                     |

| 5      | 空白Wr    | 0=Disable pixel write during blanking; 1=enable pixel write during blanking                    |

| 6      | 空白WrDir | 0=Write pixel to 0 during blanking; 1=Write pixel to 1 during blanking (if BlankWr is enabled) |

図30の例において、変数は、例えば表示装置のEEPROM126の適切なレジスタにおける一覧表化されたシーケンスを保存することにより、以下の表に示された値を取るようにプログラムされている。

#### 【0093】

【表2】

| 相  | 変数 |   |   |   |   |   |   |

|----|----|---|---|---|---|---|---|

|    | 0  | 1 | 2 | 3 | 4 | 5 | 6 |

| 0  | 1  | 0 | 0 | 0 | 0 | 0 | x |

| 1  | 1  | 0 | 1 | 0 | 0 | 1 | 1 |

| 2  | 1  | 1 | 0 | 0 | 0 | 1 | 1 |

| 3  | 0  | 0 | 0 | 1 | 0 | 0 | x |

| 4  | 0  | 0 | 1 | 1 | 0 | 1 | 0 |

| 5  | 0  | 1 | 0 | 1 | 0 | 1 | 0 |

| 6  | 1  | 0 | 0 | 0 | 0 | 0 | x |

| 7  | 1  | 0 | 1 | 0 | 0 | 1 | 1 |

| 8  | 1  | 1 | 0 | 0 | 0 | 1 | 1 |

| 9  | 0  | 0 | 0 | 1 | 0 | 0 | x |

| 10 | 0  | 0 | 1 | 1 | 0 | 1 | 0 |

| 11 | 0  | 1 | 0 | 1 | 0 | 1 | 0 |

図30はランプ信号114、画素ブースト・レジスタが更新される間隔、画素アレイがLEDにより照射された赤、緑、または、青の光により照明されている期間、および、その画素が50%中立な濃度値を表示するように指令されている例示的画素電極の電圧を示す。60Hzの入力ビデオに対して、各位相は1.389msの持続時間を有する。

## 【0094】

位相ゼロの間、CDP比較器は復号化された画像データの赤部分に対して機能する。プランギング期間と呼ばれるこの位相の開始における期間にわたり、アレイ内のすべての画素はオンに駆動される。プランギング期間は400μsの持続時間を典型的に有し得る。プランギング期間の終了において、ランプおよび復号化画像データ比較が開始される。ランプの開始のすぐ後の時点で、赤LEDがオンとされる。ランプの途中で、50%の輝度を表示しているこの例示的画素に対して、比較器は、画素画像値とランプ値の等しさを検出し、CDPは画素にオフに閉鎖するように指令する。ランプの終了において、LEDはオフとされ、すべての画素は次の位相の開始に対して再び準備して、再びオンに駆動される。位相1は位相0がしたように進行するが、活性化されるのが緑LEDである一方、復号化画像データの緑部分が比較器の入力に印加されることを今度は除く。青LEDおよび青データを使用して、位相2が位相1に続く。位相1の終了において、プランギング信号は必要ない。なぜなら、この実施例では、位相1は「逆転した」形で機能するDCバランス化位相(次に説明される位相3)が後に続く。この理由のために、すべての画素の最終的状態および位相2の終了は、いかなるさらなる明白な作用もなしに、位相3を開始するために既に必要なものである。位相3の間、表示装置は、復号化画像データの赤部分を比較器の入力に再び印加するが、このDCバランス位相の間、LEDはオフに保たれ、かつ、画素は自身の電極が低い状態で開始し、画素をオフの状態にし、かつ、画素は全体を通じて途中でオンに切り換わる(すなわち、比較器の作用の感度が逆転される)。緑および青のデータに対する追加のDCバランス位相は位相4および5の間に続く。位相6において、赤、緑、青の表示サイクルが再び開始される。このように、各色は1.389msの色当たりの持続時間にわたり、フレームの間に2回表示される。さらに、与えられた画素に対する画像データ値に関係なく、画素の駆動電極はフレーム時間の半分を高い状態で、かつ、フレーム時間の半分を低い状態で費やし、内容を本願明細書に援用する米国特許第6525709号明細書に教示されているように、固着している画面を排除するためにDCバランスの取れた駆動信号を供給する。赤のデータが表示される期間をRにより、および、対応するDCバランス期間を(特定の色のより低い状態の場合の版) rにより示すことなどにより、本発明の表示装置は図30に示されたようにRGBrgbRGBrgbの順で、または、RrgbRGBrgbの順で、または、さらなる実施例に対して、gbrrRBGgbrrRBGのように、または、他の多くの順列でデータを表示するようにプログラム可能である。

## 【0095】

## ガンマ変化

既に説明されたように、一定した照明およびランプ・クロック周波数を持つ単純な PWM 方式は  $= 1$  の表示特性を生成する一方、 $= 2$  は限られた濃度ビット深さの知覚的に優れた利用をもたらす。本発明の表示装置は、いくつかの方法で所望のガンマ特性を提供可能である。最初の方法では、LED の輝度がランプ信号 114 を使用して一斉に上下する。このことは、画像データ値に対して表示輝度の 2 次の変化をもたらす。LED の輝度は、瞬時の電流値に伴うスペクトルの変化を回避するために、好ましくは PWM 方式により制御される。

## 【0096】

10

第 2 の方法において、LED の輝度はランプの間は一定に保持されるが、ランプ・カウントを駆動するクロックの周波数は「チャーブされ」ており、そのため、ランプ値間の間隔は、暗い画素値に対応するランプの部分に対して比較的短く、明るい画素値に対応するランプの部分に対しては比較的長い。LED ランピングまたはクロック・チャーピングの方法のいずれかにおいて、LED の明るさ、または、クロック周波数がどのようにしてランプ・カウントと共に変化されるかの適切な選択により、様々なガンマ特性が得られ得る。

## 【0097】

## 白点の調整

20

LED の輝度を変化させるための能力は別の重要な長所を有する。設けられた如くの RGB の LED 三連構造体は、様々な色の相対的な明るさのかなりの変化を有し、知覚された白色の変化をもたらす。このことは、参照駆動条件下の様々な LED の相対輝度を測定すること、および、特定の表示装置の EEPROM に保存可能である効率係数として、これらの測定の結果を提供することにより製造の時点で補正可能である。続いて、動作中に、制御ブロック 116 の作用下で、様々な LED に供給された相対駆動強度は、それらの強度の変化を正確に補償するように調整可能であり、一貫した所望の白点をもたらす。

## 【0098】

## 温度補償

例えば採用され得る強誘電性液晶 (FLC) 変調装置の特性が所望の温度範囲にわたり劇的に変化してさえも、広い範囲の動作温度にわたり高品質画像を表示する微小表示装置を有することが所望されている。例えば、FLC の切換え速度は FLC の温度が低下されるに従い典型的に低下する。この緩慢な切換えは表示コントラスト比の劣化を引き起こし得る。本発明の微小表示装置はこれらの、および、類似の影響を補償するための方策を提供する。

30

## 【0099】

## LED のタイミング

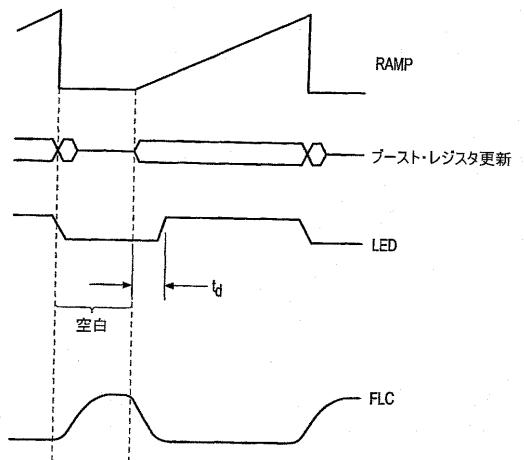

第 1 の補償方法は図 31 に示されているように、LED 照明のタイミングの温度変化に関与している。この図は、図 30 に対して選択された変数の同じ例示的選択肢に対する 1 つの表示位相の一部を示す。分かり得るように、ランプはブランкиング期間の後に開始するが、LED 照明の立ち上がりは時間  $t_D$  だけ遅延されている。本発明の表示装置は、制御ブロック 116 の作用を介して、温度センサ 280 により感知された温度に従った遅延持続時間の変化に対処する。例えば、もし表示装置の温度が低下される間、LED の遅延が一定に保たれたなら、画素 FLC の光学的応答の降下するエッジは、同図に示されたように、画素画像値がゼロとなっている時でさえ、かなり遅くなった時点で発生する。このことは、画素により反射される不要な量の光をもたらし、達成可能なコントラスト比を劣化させる。FLC 応答のこの遅延は、ランプの開始を基準とした LED 照明の遅延を増大させることにより、本発明により補償可能である。予想される様々な温度での所望の LED 遅延時間に対する値は EEPROM 126 [MH5] に保存可能であり、本発明の表示装置と共に使用可能である様々な FLC 材料の特性を同表示装置がプログラム可能に補償することをさらに可能にする。

40

50

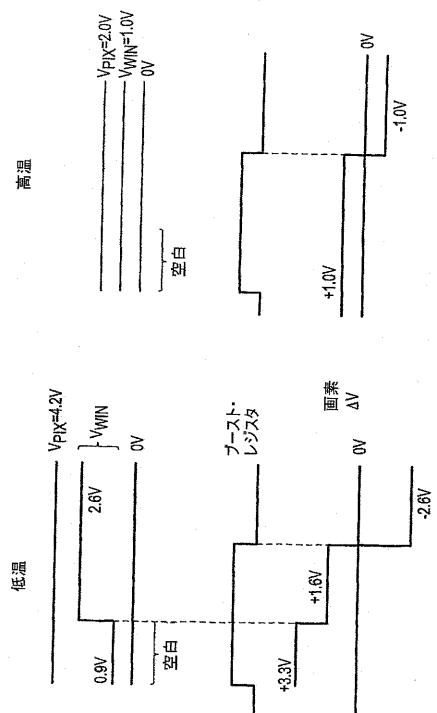

## 【0100】

## 画素駆動電圧

表示装置の様々な特性を補償するための別な方法は、典型的な低温および高温での動作に対する位相の一部の間に画素にかかる電圧  $V$  の波形の例を示す図32を参照して説明されている。低温で、FLCは比較的緩慢に切り換わり、FLCの速度を上昇させるためにより高い駆動電圧が所望される。逆に、高温では、FLCが比較的速く切り換わり、より低い駆動電圧が最適となる。ブースト・セルに関して既に説明されたように、電圧  $V_{P_{IX}}$  は  $V_{DD}$  より低い電圧から  $V_{DD}$  より高い電圧の範囲を通じて変化可能である。同図に示されたように、低温動作に対しては  $V_{P_{IX}} = 4.2V$  が選択可能である。同様に、ガラス・ウインドウ上の共通電極に印加された電圧  $V_{W_{IN}}$  は変化可能であり、かつ、位相内で様々な値を介して段階的にし得る。図32はブランкиング中に  $0.9V$  に設定された電圧  $V_{W_{IN}}$  および  $2.6V$  への設定を示す。画素電極はブースト・セル・レジスタの状態によって  $0V$  または  $V_{W_{IN}}$  に駆動される。結果として得られる液晶にかかる電圧  $V$  は、所望の初期状態が迅速に得られることを確実にするために、ブランкиングの間、 $+3.3V$  の高い値を有するとして示されている。続いて、濃度スケール変調が発生する位相の一部の間に、画素  $V$  は既に得られているオン状態を保持するために  $+1.6V$  に下降される。比較器が、示された画素に対する等しさを検出し、かつ、同画素のブースト・レジスタの状態を変更すると、画素電極電圧は  $0V$  に下降し、変調装置にわたり印加された比較的高い  $V = -2.6V$  をもたらす。対照的に、高温では、電圧  $V_{P_{IX}}$  はより低い  $2.0V$  に設定され得、 $V_{W_{IN}}$  は  $1.0V$  に設定され得、一定に保持される。この場合、画素にかかる  $V$  はブランкиングの間に  $+1.0V$  で開始され、その画素のブースト・セル・レジスタが変化されるまで、そのレベルに留まり、そのレベルで  $V$  は  $-1.0V$  に変化する [MH6]。 10

## 【0101】

## 低電力動作

さらなる電力節減に対処する少なくとも2つの他のモードがある。先ず、電力は微小表示装置に印加されて保たれ得るが、同装置に送られたいかなる新しい画像データも受信せず、または、いかなる画像も表示し続けないことが可能である。これに続くある時点で、画像の表示を再開するために指令が与えられ得、フレーム・バッファを構成するSRAMメモリ・セルに保存されている画像は、微小表示装置に送信されている新しい画像データがなくても表示可能である。このことは、微小表示装置が内部に所在するデバイスにおける電力節減を、または、通信リンクの受信端に所在している微小表示装置の場合に、そのデバイスに画像データを以前送信していたデバイスにおける電力節減を可能にもたらすことが理解可能であろう。このことは微小表示装置自体による幾つかの電力節減ももたらす。なぜなら、クロックまたはデータの読み出しありは書き込みがない一方、画像が表示されなかつたからである。第2の電力節減モードは、新しい画像データを受信せずにデータを表示し続ける表示装置を含み得る。このことは、例えば、カメラが、微小表示装置に同じ画像データを送信し続ける必要を無くし得る一方、以前に取り込まれた画像がオペレータによる検討のために表示されているデジタル静止画カメラの応用例に発生し得る。このモードの電力節減は主にカメラにおけるが、微小表示装置はここでも幾つかの電力節減を有する。なぜなら、新しいデータはガンマ補正、縮尺調整、符号化、および、フレーム・バッファへの書き込みを有する必要がないからである。 20

## 【0102】

## 長所のまとめ

上記に説明された微小表示装置回路および濃度調節方式は従来技術に対する実質的な長所を有する。画像フィールド当たり限られた数の画素駆動遷移を持つパルス幅変調駆動は完全にデジタルで実施される。JPEGまたは正準4:1:1 YUVさえなどにより洗練された圧縮アルゴリズムに必要な回路の複雑さを必要とせずに、「DEF」画像圧縮は画素当たりに保存される必要なビット数を低減する。さらに、PWMを実施するために必要なデジタル比較器は、各画素において実施されるよりも、むしろ多くの画素間で共有され 40

る。これらの方法において、表示装置の複雑さは最小に抑えられる。本発明によれば、表示装置内の画素数が増大されるに従い、画素当たり（だが、画素ではなく）追加される必要のあるトランジスタの数は、144、すなわち、フレーム当たり12ビットの二重バッファ画像保存装置を含む画素当たり24個の6トランジスタS R A Mレジスタに、画素ブースト・セルに対する14個のトランジスタを加え、合計158個に等しくなる。D E F方式の代案変形は画素当たりに必要なビット数を12から10にまで低く低減し、画素当たりの複雑さを $120 + 14 = 134$ 個のトランジスタにさらに低減する。本発明の背景において上記に説明されたように、画像圧縮なしのデジタルP W Mアーキテクチャの平易な実施は、もし24ビットの色が所望されれば、画素当たり772個のトランジスタという表示装置の複雑さをもたらす。したがって、本発明による微小表示装置は他の全デジタルP W M実施に比較して実質的に低減された複雑さを有する。より詳細には、本発明は、700未満、600未満、500未満、400未満、300未満、200未満、160未満、150未満、140未満、135未満の限界の追加トランジスタの数値のみを必要とする改善された設計を含む。本発明のより単純な画素はより小さな達成可能な画素サイズに、かつ、したがって、低減されたダイ・サイズ、より高いシリコン利用率、および、低減された背面組立て費用に直接変換される。平易な24ビット・デジタルP W M実施と比較して、本発明の微小表示装置は、各画素に伴う約5倍少ないトランジスタを有し、2.25倍より微細な達成可能な画素間隔をもたらす。

#### 【0103】

これらの長所は比較例により例示可能である。出願人は0.25 $\mu$ m C M O S工程における $432 \times 240$ のアレイの画素として本発明による微小表示装置を実施した。この例示的実施において、画素は12.0 $\mu$ mの幅および16.2 $\mu$ mの高さを有し、5.184mmの幅および3.888mmの高さの活性領域82を与える。この例示的実施において、活性領域82の高さに、追加のS R A M領域88および90を加えると5.896mmであり、この長さは冗長さを提供するためのS R A Mレジスタの少数の予備行を含んだ。この実施における各S R A Mレジスタは $2.74 \mu m \times 3.60 \mu m$ のセルを占有した。したがって、画素に伴う面積は $(5184 \mu m \times 5896 \mu m) (432 \times 240) = 295 \mu m^2$  / 画素であった。この面積は、画素が772個のトランジスタを必要とする上記に説明された従来技術による微小表示装置における画素当たりの面積に比較され得る。もしこの画素が同じ0.25 $\mu$ m C M O S工程で実施され、上記に与えた見積りにより、各6トランジスタに対して面積 $130 (0.25 \mu m)^2$ のセルを必要とする典型的なS R A Mと同じ密度で実施されたなら、各画素は、この低電圧(2.5V)C M O S工程における画素ブースト・セルを供給するために必要となる追加のトランジスタを数えなければ、1,045 $\mu m^2$ の面積を必要とする。

#### 【0104】

この例示的実施において、分層が表示装置の6画素列の幅のある上部半体片または下部半体片のいずれかとなるという事実が一旦考慮されれば、本微小表示装置のC D Pは分層当たり8,846個のトランジスタを必要とし、この数は列当たり約2,950個のトランジスタに達する。したがって、C D Pを追加することは画素当たり約2,950 / 240 = 12トランジスタを追加する。出願人の例示的実施において、各C D Pは約350 $\mu$ mの高さを有した。もし双方のC D Pの700 $\mu$ mの高さが5.896mmのアレイ高さに追加されれば、6.6mmの全高を作り出すために、画素当たりのアレイ総面積は330 $\mu m^2$ に増大され、それでも従来技術タイプの二重バッファ・デジタル濃度諧調表示装置に必要な1,045 $\mu m^2$ に対して非常に大幅な面積節減となる。

#### 【0105】

本発明の上記の説明は例示および説明の目的のために提示された。さらに、説明は本発明を本願明細書に開示された形態に限定することは意図されていない。その結果、上記の教示に相当する変形および修正、ならびに、関連技術の技能および知識は本発明の範囲内である。本願明細書で上記に説明された実施形態は、本発明の実現の知られている最良の形態を説明すること、ならびに、他の当業者が、このような、または、他の実施形態にお

10

20

30

40

50

いて、および、本発明の特定の応用例または使用により必要とされる様々な変形を使用して本発明を利用するすることを可能にすることをさらに意図されている。添付の特許請求の範囲が、従来技術により許容される程度まで代案実施形態を含むと解釈されることが意図されている。

【図面の簡単な説明】

【0106】

【図1】本発明の微小表示装置が内部に採用可能であるカメラのブロック図。

【図2】本発明の微小表示装置のL C O S部を明らかにするために切開されたプラスチック・パッケージの一部を示す本発明の微小表示装置の側面図。

【図3】図2のL C O S部の断面図。

10

【図4】図2のL C O S部のシリコン背面の上面図。

【図5】図4のシリコン背面の一部のブロック図。

【図6】画素アレイと、ブースト回路およびS R A Mメモリ・セルの層との間のサイズの関係を示すシリコン背面の一部の斜視図。

【図7】本発明のシリコン背面の一部の機能図。

【図8】本発明のシリコン背面の一部の拡大機能図。

【図9】C D P片を示す本発明のシリコン背面の一部の機能図。

【図10】本発明のシリコン背面の単一のC D P片の機能図。

【図11】本発明のシリコン背面の単一のC D P片のより詳細な機能図。

【図12】本発明の微小表示装置の比較器への入力信号およびC D P片における結果的に得られた画素電気駆動信号を示す図。

20

【図13】座標系間での変換において一方、D E FからR G Bカラー空間への復号化において利用される本発明の回路の論理図。

【図14】S R A Mメモリ・アレイならびに同アレイのデータ・イン回路および感度増幅器回路への接続の一部の簡略図。

【図15a】本発明の微小表示装置の各画素と接続されている接続済みS R A Mメモリ・セルに対するブースト回路の概略図。

【図15b】本発明の微小表示装置の各画素と接続されている接続済みS R A Mメモリ・セルに対するブースト回路の概略図。

【図15c】本発明の微小表示装置の各画素と接続されている接続済みS R A Mメモリ・セルに対するブースト回路の概略図。

30

【図16】本発明の電圧源により供給される電圧を調節するため、ならびに、本発明の微小表示装置の動作温度を示す電圧信号を発生させるために使用されている回路の概略図。

【図17】動画のいくつかの表示において目視可能となるティアリング(t e a r i n g)として知られている視覚的擬似信号の図。

【図18】デジタル・ハードウェアにおいてP W M濃度諧調を実施するための論理の一部の図。

【図19】本発明における読み出し動作および書き込み動作の挟み込みを示すタイミング図。

【図20】画像データに対するサンプリング技術の図。

【図21】圧縮画像データに対するサンプリング技術を示す図。

40

【図22】圧縮画像データに対するサンプリング技術を示す図。

【図23】圧縮画像データに対する本発明の第1のサンプリング技術を示す図。

【図24】圧縮画像データに対する本発明の第2のサンプリング技術を示す図。

【図25】圧縮画像データに対する本発明の第3のサンプリング技術を示す図。

【図26】圧縮画像データに対する本発明の第4のサンプリング技術を示す図。

【図27】圧縮画像データに対する本発明の第5のサンプリング技術を示す図。

【図28】圧縮画像データに対する本発明の第6のサンプリング技術を示す図。

【図29a】本発明のS R A M回路に対する感度増幅器に対する概略図。

【図29b】本発明のS R A M回路に対する感度増幅器に対するタイミング図。

【図30】本発明の順次カラー動作の様々な段階を示すタイミング図。

50

【図1】本発明によるLED照明のタイミングの温度変化を示すタイミング図。

【図2】本発明による低温動作および高温動作に対する表示特性の変化を示すタイミング図。

【図1】

【図2】

FIG.2

【図3】

FIG.3

【図4】

FIG.4

【図5】

【図6】

FIG.6

【図7】

【図8】

【図9】

FIG.9

【図10】

【図11】

FIG.11

【図12】

FIG.12

【図13】

【図14】

【図15a】

【図15b】

FIG.15b

【図15c】

【図17】

FIG.17

【図16】

【図18】

【図19】

【図20】

FIG.20

【図21】

FIG.21

【図22】

FIG.22

【図23】

FIG.23

【図24】

FIG.24

【図25】

FIG.25

【図26】

FIG.26

【図27】

FIG.27

【図28】

FIG.28

【図29 a】

【図29 b】

【図30】

【図31】

【図 3 2】

## フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 5 0 Z |

| G 0 9 G | 3/20 | 6 3 1 K |

| G 0 9 G | 3/20 | 6 4 1 A |

| G 0 9 G | 3/20 | 6 8 0 G |

| G 0 9 G | 3/20 | 6 2 2 L |

(74)代理人 100105957

弁理士 恩田 誠

(72)発明者 ダラス、ジェームズ エム.

アメリカ合衆国 8 0 0 2 7 コロラド州 スーペリア イートン サークル 6 9 8

(72)発明者 ピッカリー ザ サード、アール アール.

アメリカ合衆国 8 9 0 1 2 ネバダ州 ヘンダーソン イーグル ウォッч ドライブ 2 0 9

3

(72)発明者 マルツベンダー、レイナー エム.

アメリカ合衆国 8 0 5 0 4 コロラド州 ニウォト ホーガン コート 4 4 5 8

(72)発明者 ラーセン、ペア ハロルド

アメリカ合衆国 8 0 3 0 3 コロラド州 ボルダー ペンシルバニア アベニュー 5 5 7 5

ナンバーシー

(72)発明者 ホーレンベック、デイビッド

アメリカ合衆国 8 0 5 3 0 コロラド州 フレデリック ウエスト ウェットランズ ドライブ

5 5 4 7

(72)発明者 イー、マイケル ウェイン

アメリカ合衆国 8 0 0 2 0 コロラド州 ブルームフィールド ボルダー ポイント 1 3 7 1

3 ナンバー 1 0 1

審査官 鳥居 祐樹

(56)参考文献 特開2 0 0 1 - 3 3 1 1 4 2 (JP, A)

特開平0 7 - 0 9 2 9 3 5 (JP, A)

特開2 0 0 2 - 1 4 9 1 3 4 (JP, A)

特開2 0 0 0 - 0 7 8 6 1 0 (JP, A)

特開平1 1 - 0 6 5 4 8 9 (JP, A)

特開2 0 0 0 - 3 1 6 1 7 0 (JP, A)

特開2 0 0 0 - 3 1 0 7 6 7 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G09G 3/00 - 3/38

G09G 5/00 - 5/40

G02F 1/13

G02F 1/137- 1/141