(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6572095号

(P6572095)

(45) 発行日 令和1年9月4日 (2019.9.4)

(24) 登録日 令和1年8月16日 (2019.8.16)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G09G 3/20 (2006.01)

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

G09G 3/20

請求項の数 8 (全 20 頁) 最終頁に続く

(21) 出願番号

特願2015-212091 (P2015-212091)

(22) 出願日

平成27年10月28日 (2015.10.28)

(65) 公開番号

特開2017-83654 (P2017-83654A)

(43) 公開日

平成29年5月18日 (2017.5.18)

審査請求日

平成30年10月23日 (2018.10.23)

(73) 特許権者 502356528

株式会社ジャパンディスプレイ

東京都港区西新橋三丁目7番1号

(74) 代理人 110001737

特許業務法人スズエ国際特許事務所

(72) 発明者 島 武弘

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

(72) 発明者 仲尾 貴之

東京都港区西新橋三丁目7番1号 株式会

社ジャパンディスプレイ内

審査官 斎藤 厚志

最終頁に続く

(54) 【発明の名称】 表示装置

(57) 【特許請求の範囲】

## 【請求項 1】

複数の画素が配置された表示領域を有する一対の基板と、

前記一対の基板の間に封入された液晶層と、

前記複数の画素のそれぞれに配置された画素電極と、

前記画素電極と対向し、前記画素電極との間で前記液晶層を駆動する電位差を発生させる共通電極と、

画像データに応じたデジタル信号が供給される信号線と、

前記信号線に前記デジタル信号を供給する第1駆動回路と、

前記共通電極に交流の共通信号を供給する第2駆動回路と、

前記表示領域において、前記複数の画素のそれぞれに配置されたメモリと、

画像の表示信号が供給される第1駆動線と、

画像の非表示信号が供給される第2駆動線と、

記憶期間において、前記信号線に供給された前記デジタル信号を前記メモリに記憶させる記憶制御回路と、

表示期間において、前記第1駆動線に供給される前記表示信号及び前記第2駆動線に供給される前記非表示信号のうち、前記メモリに記憶された前記デジタル信号に対応する一方を選択的に前記画素電極に供給する選択制御回路と、を備え、

前記表示期間において、前記第2駆動回路は、前記表示領域に配置された前記複数の画素の前記画素電極と前記共通電極の電位の極性を1フレーム期間毎に周期的に反転させ、

前記 1 フレーム期間の開始に同期して前記表示期間から前記記憶期間へ移行する際、前記第 2 駆動回路は、前記表示期間の前記共通信号の電位を前記記憶期間においても維持する、表示装置。

【請求項 2】

複数の画素が配置された表示領域を有する一対の基板と、

前記一対の基板の間に封入された液晶層と、

前記複数の画素のそれぞれに配置された画素電極と、

前記画素電極と対向し、前記画素電極との間で前記液晶層を駆動する電位差を発生させる共通電極と、

画像データに応じたデジタル信号が供給される信号線と、

10

前記信号線に前記デジタル信号を供給する第 1 駆動回路と、

前記共通電極に交流の共通信号を供給する第 2 駆動回路と、

前記表示領域において、前記複数の画素のそれぞれに配置されたメモリと、

画像の表示信号が供給される第 1 駆動線と、

画像の非表示信号が供給される第 2 駆動線と、

記憶期間において、前記信号線に供給された前記デジタル信号を前記メモリに記憶させる記憶制御回路と、

表示期間において、前記第 1 駆動線に供給される表示信号及び前記第 2 駆動線に供給される非表示信号のうち、前記メモリに記憶された前記デジタル信号に対応する一方を選択的に前記画素電極に供給する選択制御回路と、

20

前記表示期間から前記記憶期間への移行の可否を判定する制御装置と、を備え、

前記表示信号は、第 1 電位と第 2 電位とを含み、

前記記憶期間において前記メモリに記憶される前記デジタル信号の電位が第 3 電位であり、

前記制御装置は、

前記第 1 電位と前記第 2 電位のうち前記第 3 電位との電位差が小さい方の電位が、前記記憶期間の開始直前の前記画素電極の電位である場合に、前記記憶期間において前記第 3 電位を前記メモリに記憶させる動作を行い、

前記第 1 電位と前記第 2 電位のうち前記第 3 電位との電位差が大きい方の電位が、前記記憶期間の開始直前の前記画素電極の電位である場合に、前記記憶期間において前記第 3 電位を前記メモリに記憶させる動作を行わず、前記表示期間を継続させる、表示装置。

30

【請求項 3】

前記選択制御回路は、

前記第 1 駆動線及び前記第 2 駆動線のうち前記メモリに記憶された前記デジタル信号に對応する一方と接続される選択信号線と、

前記選択信号線と前記画素電極とを電気的に接続又は遮断するスイッチング素子と、を備え、

前記記憶期間において、前記スイッチング素子は、前記選択信号線と前記画素電極とを電気的に遮断する、

請求項 1 又は 2 に記載の表示装置。

40

【請求項 4】

前記表示期間から前記記憶期間への移行の際、前記スイッチング素子が前記選択信号線と前記画素電極とを電気的に遮断する前に、前記第 2 駆動回路は、前記共通信号の電位を既定量だけ低下させる、請求項 3 に記載の表示装置。

【請求項 5】

前記表示期間において、前記画素電極と前記共通電極との間の電位の極性が周期的に反転される、請求項 1 乃至 4 のうちいずれか 1 項に記載の表示装置。

【請求項 6】

前記信号線は、隣り合う前記画素の間を通って延び、

前記一対の基板の少なくとも一方は、光を遮光する遮光層を備え、

50

前記遮光層は、前記表示領域において、隣り合う前記画素の間にある前記信号線と重畠しない、請求項 1 乃至 5 のうちいずれか 1 項に記載の表示装置。

【請求項 7】

前記一対の基板は、第 1 基板と、第 2 基板とを含み、

前記画素電極は、前記第 1 基板に配置され、

前記第 1 基板は、前記第 2 基板に入射して前記液晶層を通り前記第 1 基板に到達した光を前記第 2 基板の方向へ反射する反射層を備え、

前記反射層が反射した光により画像を表示する、請求項 1 乃至 6 のうちいずれか 1 項に記載の表示装置。

【請求項 8】

10

デジタルモードとアナログモードとを有し、

前記第 1 駆動線と前記信号線とは同じ配線であり、

前記デジタルモードにおいては、前記記憶期間及び前記表示期間の動作が実行され、

前記アナログモードにおいては、前記第 1 駆動線に画像の階調に応じた信号が供給される、請求項 1 乃至 7 のうちいずれか 1 項に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、表示装置に関する。

【背景技術】

20

【0002】

表示領域において画素ごとにメモリが配置された液晶表示装置などの表示装置が知られている。この種の表示装置においては、表示させる画像に応じたデジタルデータを各メモリに書き込む記憶期間と、各画素の駆動電位を各メモリに記憶されたデジタルデータに対応する電位に設定することにより表示領域に画像を表示させる表示期間とが交互に繰り返される。このように、メモリに記憶されたデジタルデータに基づいて画素を駆動する方式は、例えば、デジタルモード或いはデジタル駆動方式などと呼ばれる。

【0003】

また、デジタルモードの機能に加え、各画素の駆動電位を多階調に変化させるアナログモード（或いはアナログ駆動方式）の機能を備えた表示装置も提案されている。（例えば特許文献 1 参照）

30

【先行技術文献】

【特許文献】

【0004】

【特許文献 1】特開 2008-256762 号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

記憶期間及び表示期間の動作をそれぞれ実現するために、各画素には種々の回路やスイッチング素子が設けられる。これらスイッチング素子がオンオフされることで、例えば記憶期間においては画素電極などの要素が電気的にフロー・ティングとなる。フロー・ティングとなった要素の電位は、他の要素の電位変動の影響を受けて変化する。これに起因して、画素において不所望な電界が生じ、画像の輝度変化などを招き得る。

40

【0006】

本開示の一態様における目的は、デジタルモードを採用した表示装置において、表示品位を高めることである。

【課題を解決するための手段】

【0007】

一実施形態に係る表示装置は、複数の画素が配置された表示領域を有する一対の基板と、上記一対の基板の間に封入された液晶層と、上記複数の画素のそれぞれに配置された画

50

素電極と、上記画素電極と対向し、上記画素電極との間で上記液晶層を駆動する電位差を発生させる共通電極と、画像データに応じたデジタル信号が供給される信号線と、上記信号線に上記デジタル信号を供給する第1駆動回路と、上記共通電極に交流の共通信号を供給する第2駆動回路と、上記表示領域において上記複数の画素のそれぞれに配置されたメモリと、画像の表示信号が供給される第1駆動線と、画像の非表示信号が供給される第2駆動線と、記憶期間において上記信号線に供給された上記デジタル信号を上記メモリに記憶させる記憶制御回路と、表示期間において上記第1駆動線に供給される上記表示信号及び上記第2駆動線に供給される上記非表示信号のうち上記メモリに記憶された上記デジタル信号に対応する一方を選択的に上記画素電極に供給する選択制御回路と、を備える。この表示装置において、上記第2駆動回路は、上記表示期間において上記表示領域に配置された上記複数の画素の上記画素電極と上記共通電極の電位の極性を1フレーム期間毎に周期的に反転させ、上記1フレーム期間の開始に同期して上記表示期間から上記記憶期間へ移行する際、上記第2駆動回路は、上記表示期間の上記共通信号の電位を上記記憶期間においても維持する。

10

## 【図面の簡単な説明】

## 【0008】

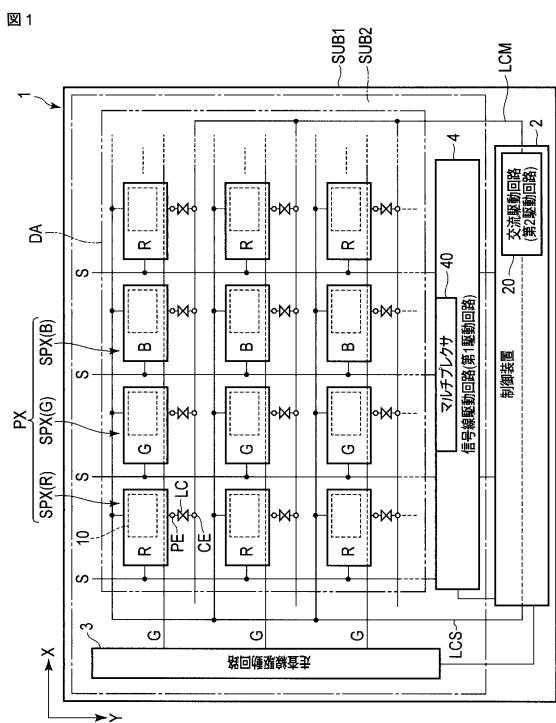

【図1】図1は、表示装置の各実施形態に共通する構成を示す平面図である。

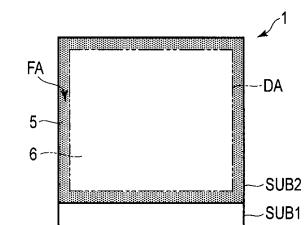

【図2】図2は、上記表示装置が備える第1基板及び第2基板の概略的な平面図である。

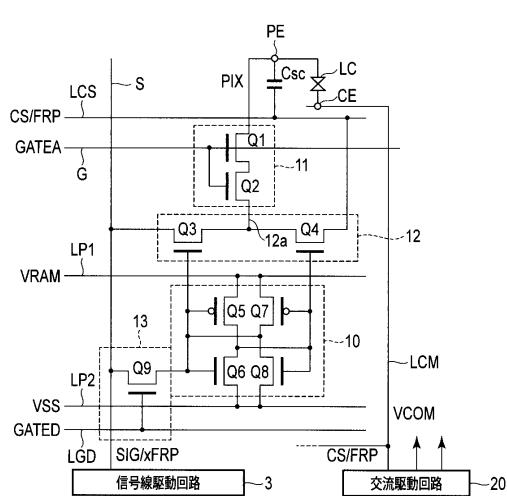

【図3】図3は、上記表示装置が備える副画素の等価回路の一例を示す図である。

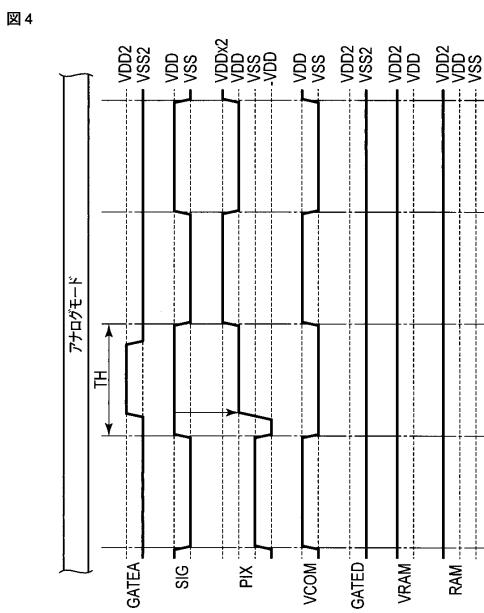

【図4】図4は、上記表示装置のアナログモードにおける動作の一例を示すタイミングチャートである。

20

【図5】図5は、上記表示装置の記憶期間における動作の一例を示すタイミングチャートである。

【図6】図6は、上記表示装置の表示期間における動作の一例を示すタイミングチャートである。

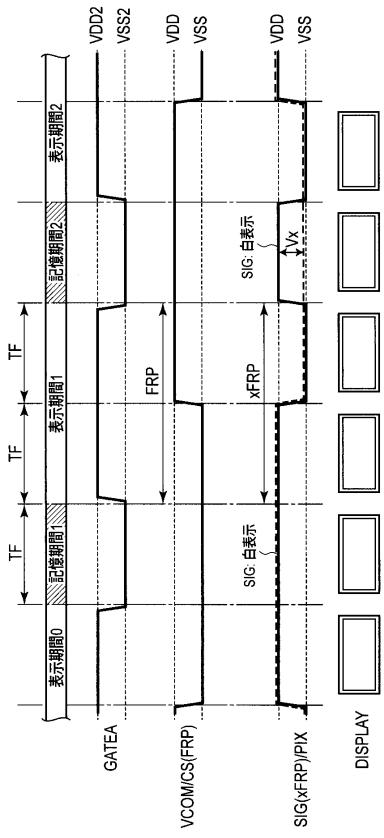

【図7】図7は、デジタルモードにおいて生じ得る問題点の一例を説明するためのタイミングチャートである。

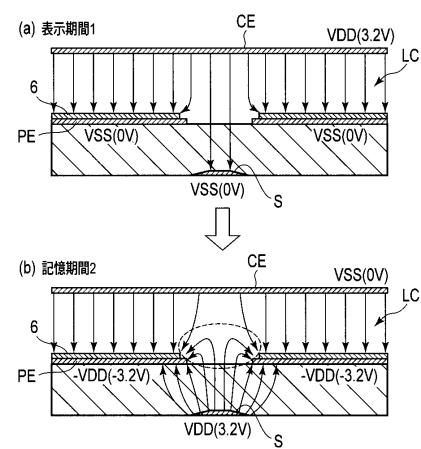

【図8】図8は、図7のタイミングチャートの表示期間及び記憶期間において副画素に発生する電界の様子を示す断面図である。

【図9】図9は、図7のタイミングチャートの他の表示期間及び記憶期間において副画素に発生する電界の様子を示す断面図である。

30

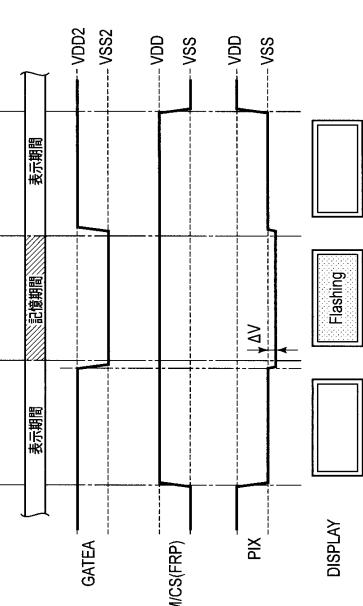

【図10】図10は、第1実施形態に係る表示装置の動作の一例を示すタイミングチャートである。

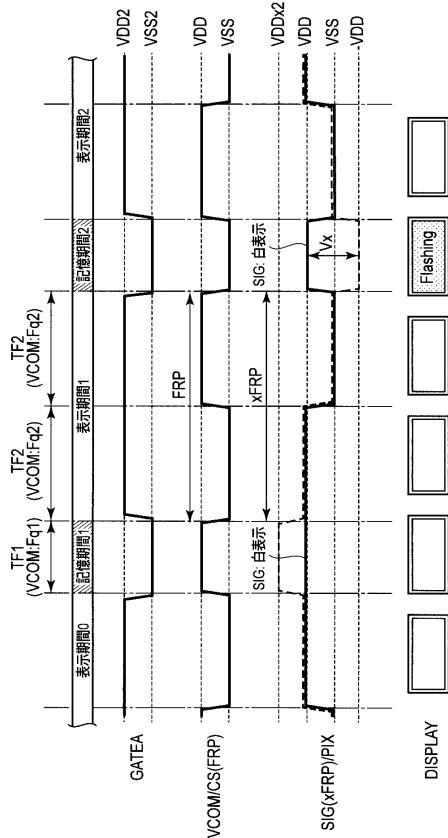

【図11】図11は、第2実施形態に係る表示装置の動作の一例を示すタイミングチャートである。

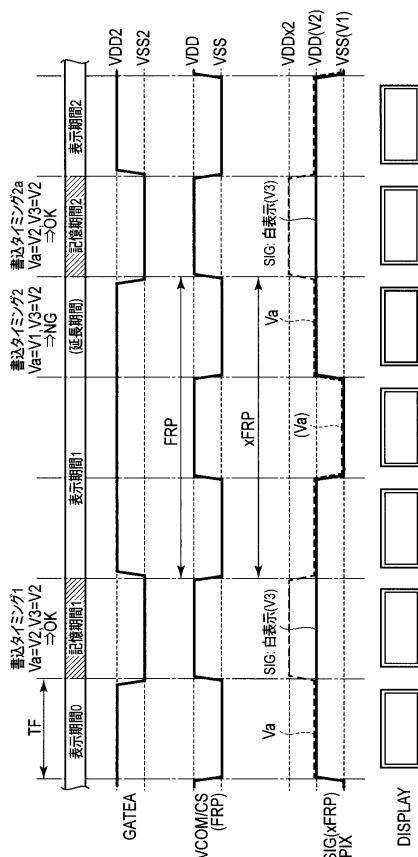

【図12】図12は、第3実施形態に係る表示装置の動作の一例を示すタイミングチャートである。

【図13】図13は、デジタルモードにおいて生じ得る他の問題点を説明するためのタイミングチャートである。

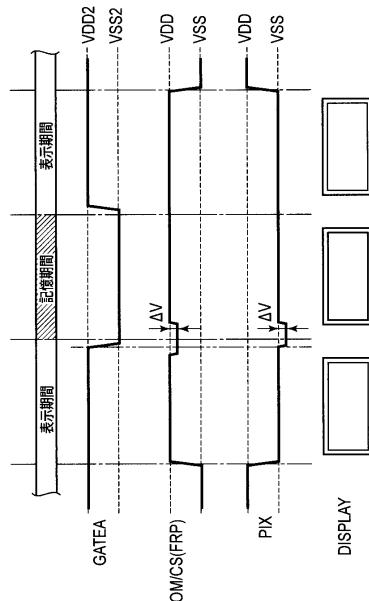

【図14】図14は、第4実施形態に係る表示装置の動作の一例を示すタイミングチャートである。

40

## 【発明を実施するための形態】

## 【0009】

いくつかの実施形態につき、図面を参照しながら説明する。

なお、開示はあくまで一例に過ぎず、当業者において、発明の主旨を保っての適宜変更について容易に想到し得るものについては、当然に本発明の範囲に含有される。また、図面は、説明をより明確にするため、実際の態様に比べて模式的に表される場合があるが、あくまで一例であって、本発明の解釈を限定するものではない。各図において、連続して配置される同一又は類似の要素については符号を省略することがある。また、本明細書と各図において、既出の図に関して前述したものと同一又は類似した機能を発揮する構成要

50

素には同一の参照符号を付し、重複する詳細な説明を省略することができる。

【0010】

各実施形態においては、表示装置の一例として、多諧調の表示信号により画素を駆動するアナログモードの機能と上述のデジタルモードの機能とを備えた反射型の液晶表示装置を開示する。ただし、各実施形態は、他種の表示装置に対する、各実施形態にて開示される個々の技術的思想の適用を妨げるものではない。他種の表示装置としては、有機エレクトロルミネッセンス表示装置などの自発光型の表示装置、或いは電気泳動素子等を有する電子ペーパ型の表示装置などが想定される。

【0011】

先ず、図1乃至図5を用いて、各実施形態に共通する表示装置の構成及び動作について述べる。

10

図1は、表示装置1の概略構成の一例を示す平面図である。表示装置1は、第1基板SUB1と、第2基板SUB2と、液晶層LCとを備えている。第1基板SUB1及び第2基板SUB2は、互いに対向した状態で貼り合わされている。液晶層LCは、第1基板SUB1及び第2基板SUB2の間に封入されている。

【0012】

表示装置1は、表示領域DAを有している。表示領域DAは、第1基板SUB1上の画素PXがマトリクス状に配列した領域に相当する。具体的には、表示領域DAには、多数の画素PXが第1方向X及び第2方向Yに沿ってマトリクス状に配列されている。第1方向X及び第2方向Yは、例えば互いに直交する。画素PXは、赤色(R)、緑色(G)、青色(B)の副画素SPXを含む。本開示においては、副画素SPXを単に“画素”と呼ぶこともある。

20

【0013】

図1の例においては、1つの画素PXに含まれる副画素SPXが第1方向Xに並んでいる。但し、画素PXのレイアウトは図1の例に限定されない。例えば、画素PXは、白色(W)などの他の色の副画素SPXをさらに含んでも良い。また、1つの画素PXに含まれる副画素SPXのうちの少なくとも一部が第2方向Yに並んでも良い。

【0014】

表示装置1は、複数の走査線Gと、複数の信号線Sと、制御装置2と、走査線駆動回路3と、信号線駆動回路4(第1駆動回路)とをさらに備えている。各走査線G及び各信号線Sは、第1基板SUB1に形成されている。走査線駆動回路3及び信号線駆動回路4は、例えばその少なくとも一部が第1基板SUB1に形成され、制御装置2に接続されている。各走査線Gは、第1方向Xに沿って走査線駆動回路3から表示領域DAに延出し、第2方向Yに並んでいる。各信号線Sは、第2方向Yに沿って信号線駆動回路4から表示領域DAに延出し、第1方向Xに並んでいる。平面視において、各信号線Sは、第1方向Xに隣り合う副画素SPXの間を通っている。

30

【0015】

制御装置2は、例えば第1基板SUB1に実装された集積回路であり、外部から入力される画像データに基づき画像表示に必要な各種の信号を出力する信号供給源として機能する。なお、制御装置2は、第1基板SUB1や第2基板SUB2に実装されずに、フレキシブル配線基板などを介してこれら基板に接続されても良い。走査線駆動回路3は、各走査線Gに対して走査信号を順次に供給する。信号線駆動回路4は、マルチプレクサ40を備えている。例えば、マルチプレクサ40は、信号の出力先をRGBの各副画素SPXに接続された3本の信号線Sの間で切り替えるスイッチング素子群である。

40

【0016】

副画素SPXの各々は、メモリ10と、画素電極PEとを備えている。メモリ10は、主にデジタルモードにおいて、信号線Sを介して供給されるデジタル信号を記憶する。画素電極PEは、第2基板SUB2に形成された共通電極CEと対向している。共通電極CEは、第1基板SUB1に形成されても良い。画素電極PE及び共通電極CEは、例えばインジウム・ティン・オキサイド(ITO)などの透明導電材料で形成することができる

50

。共通電極 C E は、複数の副画素 S P X に亘って形成されており、共通電極線 L C M を介して制御装置 2 が備える交流駆動回路 2 0 ( 第 2 駆動回路 ) に接続されている。交流駆動回路 2 0 には、補助容量線 L C S も接続されている。補助容量線 L C S は、表示領域 D A に延出し、各副画素 S P X の回路に接続されている。

#### 【 0 0 1 7 】

表示装置 1 は、各副画素 S P X に対向するカラーフィルタを備えている。これらのカラーフィルタは、対向する副画素 S P X の表示色に対応する色を有しており、例えば第 2 基板 S U B 2 に形成されている。

図 2 は、第 1 基板 S U B 1 及び第 2 基板 S U B 2 の概略的な平面図である。表示領域 D A の周囲には、周辺領域 F A が形成されている。周辺領域 F A は、第 1 基板 S U B 1 と第 2 基板 S U B 2 とが平面視で重畠する領域のうち、表示領域 D A を除いた領域に相当する。表示装置 1 は、周辺領域 F A の概ね全域と重畠する遮光層 5 を備えている。遮光層 5 は、例えば第 2 基板 S U B 2 に配置されている。遮光層 5 を設けることで、周辺領域 F A からの光漏れや、周辺領域 F A に形成された回路及び配線による光の反射を防ぐことができる。

#### 【 0 0 1 8 】

表示領域 D A には、外光を反射する反射層 6 が配置されている。反射層 6 は、例えば金属材料で形成することができる。表示装置 1 は、反射層 6 により反射された光を利用して画像を表示する。反射層 6 は、例えば後述の図 8 及び図 9 に示すように、画素電極 P E の一面に接して第 1 基板 S U B 1 に形成される。表示装置 1 は、第 2 基板 S U B 2 の第 1 基板 S U B 1 と対向しない面に配置されたフロントライトをさらに備えても良い。また、表示装置 1 は、第 1 基板 S U B 1 の第 2 基板 S U B 2 と対向しない面に配置されたバックライトをさらに備えても良い。例えばフロントライト及びバックライトとしては、表示領域 D A に対向する導光板と、この導光板の端部に沿って配置された複数の発光ダイオードとを備える面光源装置を用いることができる。さらに、表示装置 1 は、反射層 6 を備えずにバックライトを備えたものであっても良い。

#### 【 0 0 1 9 】

例えば、遮光層 5 は、表示領域 D A には配置されていない。すなわち、遮光層 5 は、表示領域 D A において、隣り合う副画素 S P X の間にある信号線 S と重畠しない。これにより、各画素 P X の開口率を高め、高輝度の画像表示が可能となる。なお、遮光層 5 は、表示領域 D A の一部と重畠しても良い。この場合においては、例えば、走査線 G と重畠するように遮光層 5 を形成しても良い。

#### 【 0 0 2 0 】

図 3 は、副画素 S P X の等価回路の一例を示す図である。各副画素 S P X の各々には、上記画素電極 P E と、上記メモリ 1 0 と、ゲート回路 1 1 と、選択制御回路 1 2 と、記憶制御回路 1 3 とが配置されている。

ゲート回路 1 1 は、走査線 G が制御端に接続されるとともに出力端が画素電極 P E に接続されたスイッチング素子 Q 1 , Q 2 を備えている。スイッチング素子 Q 1 , Q 2 は、例えばダブルゲート型の薄膜トランジスタである。走査線 G には、スイッチング素子 Q 1 , Q 2 をオンするための走査信号 G A T E A が供給される。

#### 【 0 0 2 1 】

選択制御回路 1 2 は、入力端が信号線 S に接続されたスイッチング素子 Q 3 と、入力端が補助容量線 L C S に接続されたスイッチング素子 Q 4 とを備えている。信号線 S には、信号線駆動回路 4 から表示信号 S I G 又は第 1 駆動信号 X F R P が供給される。補助容量線 L C S には、交流駆動回路 2 0 から補助容量信号 C S 又は第 2 駆動信号 F R P が供給される。補助容量線 L C S と画素電極 P E との電位差により、液晶層 L C を駆動するための補助容量 C S C が形成される。さらに、選択制御回路 1 2 は、スイッチング素子 Q 3 , Q 4 の出力端とスイッチング素子 Q 2 の入力端とを接続する選択信号線 1 2 a を備えている。スイッチング素子 Q 1 , Q 2 がオンされている間、選択信号線 1 2 a と画素電極 P E とが電気的に接続される。一方で、スイッチング素子 Q 1 , Q 2 がオフされている間、選択

10

20

30

40

50

信号線 12a と画素電極 P E とが電気的に遮断される。

【0022】

図3においては、交流駆動回路20から延出した配線が補助容量線LCS及び共通電極線LCMに分岐している。すなわち、この例では、補助容量線LCSに供給される補助容量信号CS又は第2駆動信号FRPと、共通電極線LCMに供給される共通信号VCOMとが同電位である。

【0023】

メモリ10は、スイッチング素子Q5～Q8を備えている。スイッチング素子Q5, Q7の入力端には、電源電圧VRAMを供給する第1電源線LPIが接続されている。スイッチング素子Q6, Q8の入力端には、電圧VSSが供給される第2電源線LP2が接続されている。例えば、スイッチング素子Q5, Q7はPMOSトランジスタであり、スイッチング素子Q6, Q8はNMOSトランジスタである。スイッチング素子Q5, Q6は出力端がスイッチング素子Q4の制御端に接続されたCMOS型の第1インバータを構成し、スイッチング素子Q7, Q8は出力端がスイッチング素子Q3の制御端に接続されたCMOS型の第2インバータを構成する。これら第1, 第2インバータは、逆方向に並列接続されており、スイッチング素子Q3, Q4のいずれか一方を選択的にオンする。

【0024】

記憶制御回路13は、メモリ10にデジタル信号を記憶させる回路であって、スイッチング素子Q9を備えている。スイッチング素子Q9の入力端は信号線Sに接続され、出力端はスイッチング素子Q5, Q6の制御端に接続されている。スイッチング素子Q9の制御端には、デジタル走査線LGDが接続されている。デジタル走査線LGDには、走査信号GATEDが供給される。

【0025】

スイッチング素子Q1～Q9は、例えればいずれも薄膜トランジスタであって、第1基板SUB1に形成されている。補助容量線LCS、走査線G、第1電源線LPI、第2電源線LP2、デジタル走査線LGDも第1基板SUB1に形成されており、第1方向Xに並ぶ複数の副画素SPXに接続されている。第1電源線LPI、第2電源線LP2、デジタル走査線LGDの信号は、例えば制御装置2から供給される。

【0026】

以上のような構成の表示装置1は、アナログモード及びデジタルモードの双方で各副画素SPXを駆動することができる。アナログモードは、信号線Sに供給される表示信号に基づき各副画素SPXの輝度を多諧調に制御する方式である。デジタルモードは、メモリ10が記憶するデジタルデータに基づき副画素SPXの輝度を単純にオンオフのモノクロで制御する方式である。以下の説明では、表示装置1がノーマリブラックモードの表示装置であって、デジタルモードにおいてメモリ10がHレベル(高電位レベル)に設定されているときに副画素SPXがオン(白表示)され、メモリ10がLレベル(低電位レベル)に設定されているときに副画素SPXがオフ(黒表示)される場合を想定する。

【0027】

以下、アナログモード及びデジタルモードにおける表示装置1の基本的な動作を説明する。

(アナログモード)

アナログモードにおいては、走査線Gに走査パルスが順次供給されるとともに、走査パルスが供給された走査線Gに対応する各副画素SPXの画像データに応じた多諧調の表示信号が各信号線Sに順次供給される。これにより、第1方向Xに並ぶ一群の副画素SPX(以下、一水平ラインと呼ぶ)ごとに、画像データに応じた電位が順次書き込まれていく。

【0028】

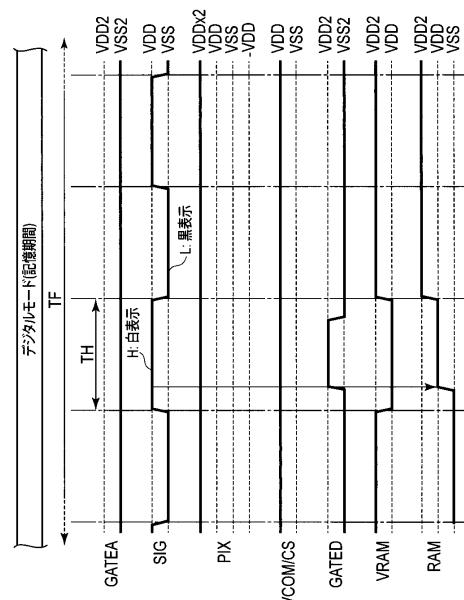

図4は、表示装置1のアナログモードにおける動作の一例を示すタイミングチャートである。このタイミングチャートにおいては、図3に示した1つの副画素SPXに着目して、走査線Gに供給される走査信号GATEA、信号線Sに供給される表示信号SIG、画

10

20

30

40

50

素電極 P E の画素電位 P I X 、共通電極 C E に供給される共通信号 V C O M 、デジタル走査線 L G D に供給される走査信号 G A T E D 、第 1 電源線 L P 1 に供給される電源電圧 V R A M 、メモリ 1 0 に記憶されるメモリ電位 R A M の変化を示している。以下の説明においては、一水平ラインに対して画素電位 P I X を書き込むための期間を、水平期間 T H と定義する。

#### 【 0 0 2 9 】

アナログモードにおいては、メモリ 1 0 が H レベルに設定されている。H レベルを設定するための動作は、後述の図 5 の動作と同様である。メモリ 1 0 が H レベルに設定され、電源電圧 V R A M が電圧 V D D から副画素 S P X の駆動電圧である電圧 V D D 2 に立ち上げられたとき、メモリ 1 0 からスイッチング素子 Q 3 に電圧 V D D 2 が供給される。これにより、スイッチング素子 Q 3 がオンされる。一方で、スイッチング素子 Q 4 はオフされる。

10

#### 【 0 0 3 0 】

走査線 G の走査信号 G A T E A が電圧 V S S 2 から電圧 V D D 2 に立ち上げられると（走査パルスが入力されると）、スイッチング素子 Q 1 , Q 2 がオンし、画素電極 P E が信号線 S に接続される。このとき、図中に矢印で示したように、画素電位 P I X が信号線 S に供給された多階調の表示信号 S I G のレベルに設定される。走査信号 G A T E A が電圧 V S S 2 に立ち下がった後は、画素電極 P E がフローディングとなり、補助容量 C s c により画素電極 P E と共通電極 C E との間の電位差が維持される。したがって、この副画素 S P X は、書き込まれた画素電位 P I X に応じた階調の色を、次に画素電位 P I X が書き換えるまで表示する。

20

#### 【 0 0 3 1 】

図 4 の例では、一水平ラインごとに画素電極 P E 及び共通電極 C E の間の電位の極性を反転させるライン反転制御を用いたケースを示している。したがって、共通信号 V C O M の電位は、水平期間 T H ごとに電圧 V S S , V D D の間で変化している。

#### 【 0 0 3 2 】

##### （デジタルモード）

デジタルモードにおいては、信号線 S に供給されたデジタル信号をメモリ 1 0 に記憶させる記憶期間と、第 1 駆動信号 x F R P 及び第 2 駆動信号 F R P のうちメモリ 1 0 に記憶されたデジタル信号（H レベル又は L レベル）に対応する一方を選択的に画素電極 P E に供給する表示期間とが繰り返される。

30

#### 【 0 0 3 3 】

記憶期間においては、デジタル走査線 L G D に走査パルスが順次供給されるとともに、走査パルスが供給されたデジタル走査線 L G D に対応する一水平ラインのデジタルの表示信号が各信号線 S に順次供給される。これにより、一水平ラインごとに、画像データに応じたデジタル信号がメモリ 1 0 に順次書き込まれていく。

#### 【 0 0 3 4 】

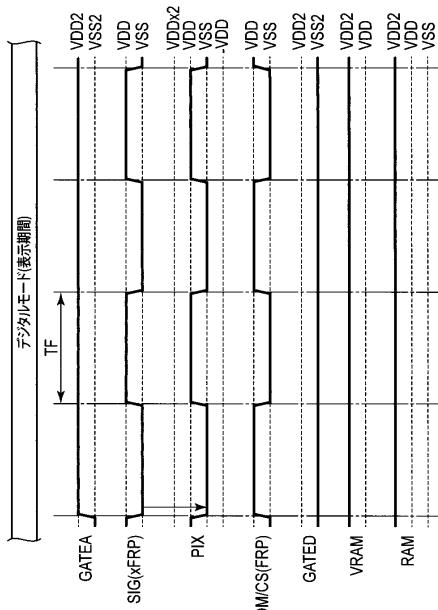

図 5 は、表示装置 1 の記憶期間における動作の一例を示すタイミングチャートである。このタイミングチャートにおいては、図 4 の場合と同じく 1 つの副画素 S P X に着目している。記憶期間においては、走査線 G の走査信号 G A T E A が電圧 V S S 2 に設定される。したがって、画素電極 P E はフローディングとなる。

40

#### 【 0 0 3 5 】

メモリ 1 0 への書き込みを実施する水平期間 T H において、信号線 S の表示信号 S I G は、メモリ 1 0 に書き込むべき電位に設定される。ここでは、H レベルである電圧 V D D が白表示に対応し、L レベルである電圧 V S S が黒表示に対応するものとする。第 1 電源線 L P 1 の電源電圧 V R A M は、記憶期間においてメモリ 1 0 の電位と同電位にするため、電圧 V D D 2 から電圧 V D D に立ち下げられる。その後、デジタル走査線 L G D の走査信号 G A T E D が電圧 V S S 2 から電圧 V D D 2 に立ち上げられると（走査パルスが入力されると）、スイッチング素子 Q 9 がオンし、メモリ 1 0 が信号線 S に接続される。このとき、図中に矢印で示したように、信号線 S に供給された表示信号 S I G のレベルがメモリ 1 0 の電位に合わせられる。

50

リ 1 0 に書き込まれる。図 5 においては、H レベルがメモリ 1 0 に書き込まれる場合を例示している。

【 0 0 3 6 】

その後、走査信号 G A T E D を電圧 V S S 2 に立ち下げることでスイッチング素子 Q 9 がオフされ、電源電圧 V R A M がスイッチング素子 Q 3 , Q 4 をオンにする電圧である V D D 2 に立ち上げられる。この際、メモリ 1 0 の電圧も V D D から V D D 2 に立ち上げられる。これにより、メモリ 1 0 は第 1 電源線 L P 1 とスイッチング素子 Q 3 を接続し、電源電圧 V R A M によりスイッチング素子 Q 3 をオンにする。一方で、メモリ 1 0 は電源線 L P 2 とスイッチング素子 Q 4 を接続し、電圧 V S S によりスイッチング素子 Q 4 をオフにする。スイッチング素子 Q 3 がオンになったことで、画素電極 P E に信号線 S の電位が供給される。

【 0 0 3 7 】

仮に、メモリ 1 0 に供給される電位が黒表示に相当する L レベルであれば、メモリ 1 0 は第 2 電源線 L P 2 とスイッチング素子 Q 3 を接続し、電圧 V S S によりスイッチング素子 Q 3 をオフにする。一方で、メモリ 1 0 は電源線 L P 1 とスイッチング素子 Q 4 を接続し、電源電圧 V R A M によりスイッチング素子 Q 4 をオンにする。スイッチング素子 Q 4 がオンになったことで、画素電極 P E と補助容量線 L C S が接続され共通信号と同電位の信号が供給される。つまり、メモリ 1 0 は、記憶した電圧によって、スイッチング素子 Q 3 , Q 4 のいずれかを排他的にオンにし、信号線 S 及び補助容量線 L C S のいずれか一方を画素電極 P E の接続先として選択する。

【 0 0 3 8 】

図 6 は、表示装置 1 の表示期間における動作の一例を示すタイミングチャートである。このタイミングチャートにおいては、図 5 の場合と同じく 1 つの副画素 S P X に着目している。なお、図 5 及び図 6 の例では、画素電極 P E 及び共通電極 C E の間の電位の極性を、表示領域 D A に配置された全ての副画素 S P X でフレーム期間 T F ごとに周期的に反転させるフレーム反転制御を用いたケースを示している。1 フレームを構成する各水平ラインのメモリ 1 0 の書き換えは、例えば 1 つのフレーム期間 T F の間に実行される。すなわち、図 5 に示した一連の水平期間 T H は、1 つのフレーム期間 T F に含まれるものであって、共通信号 V C O M 及び補助容量信号 C S が一定である。一方で、図 6 に示すように、表示期間は複数のフレーム期間 T F で構成されており、フレーム期間 T F ごとに共通信号 V C O M 及び補助容量信号 C S の電位が電圧 V S S , V D D の間で変化している。

【 0 0 3 9 】

表示期間において、フレーム期間 T F ごとに変化する補助容量信号 C S は、交流の第 2 駆動信号 F R P に相当する。また、表示期間においては、信号線 S に第 1 駆動信号 x F R P が供給される。第 1 駆動信号 x F R P は、第 2 駆動信号 F R P と逆相の交流信号であり、フレーム期間 T F ごとに電圧 V D D , V S S の間で変化する。

【 0 0 4 0 】

表示期間においては、走査線 G の走査信号 G A T E A が電圧 V S S 2 から電圧 V D D 2 に立ち上げられる。したがって、メモリ 1 0 によりスイッチング素子 Q 3 がオンされている場合には信号線 S が画素電極 P E に接続され、メモリ 1 0 によりスイッチング素子 Q 4 がオンされている場合には補助容量線 L C S が画素電極 P E に接続される。図 6 においては、信号線 S が画素電極 P E に接続されたことにより、画素電位 P I X が第 1 駆動信号 x F R P に設定される場合を例示している。この場合には、画素電極 P E と共通電極 C E との間に電圧 V D D - 電圧 V S S の電位差が生じ、副画素 S P X が白表示となる。一方で、補助容量線 L C S が画素電極 P E に接続された場合には、画素電極 P E と共通電極 C E との間に電位差が生じず、副画素 S P X が黒表示となる。

【 0 0 4 1 】

以上の説明から判るように、信号線 S は、メモリ 1 0 に記憶させるデジタルデータが供給される信号線としての機能と、画像の表示信号である第 1 駆動信号 x F R P が供給される第 1 駆動線としての機能とを兼ねている。また、補助容量線 L C S は、補助容量信号 C

10

20

30

40

50

Sを供給する信号線としての機能と、画像の非表示信号である第2駆動信号F R Pが供給される第2駆動線としての機能とを兼ねている。これにより、表示領域D Aにおける配線の数が減るので、副画素S P Xを高精細化したり、開口率を高めたりすることが可能となる。

#### 【0042】

記憶期間においては、スイッチング素子Q 1, Q 2がオフされるので、画素電極P Eがフローティングとなる。これに伴い生じ得る問題点の一つにつき、図7乃至図9を用いて説明する。

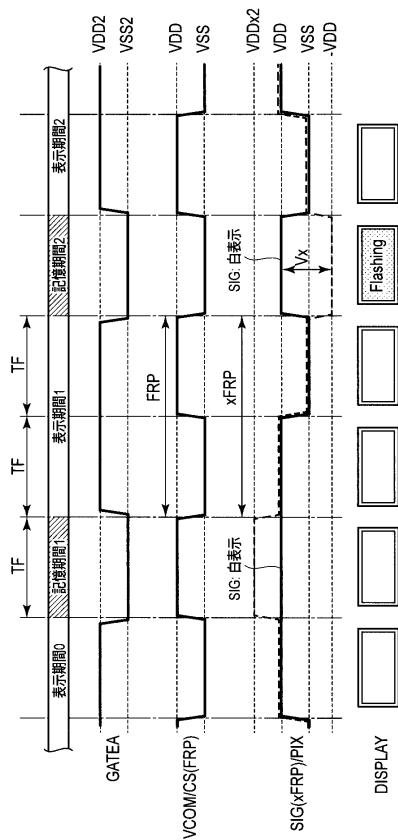

図7は、時系列に繰り返される記憶期間及び表示期間における走査信号G A T E A、共通信号V C O M、補助容量信号C S ( F R P )、表示信号S I G ( x F R P )、画素電位P I Xの変化を示すタイミングチャートである。この例においては、表示領域D Aの全ての副画素S P Xを連続的に白表示とする場合を想定している。なお、ここでは記憶期間が1つのフレーム期間T Fで構成され、表示期間が2つのフレーム期間T Fで構成されている。但し、記憶期間及び表示期間は、より多くのフレーム期間T Fで構成されても良い。

#### 【0043】

図中左側の記憶期間1においては、メモリ10の電位をHレベルに設定すべく、電圧V D Dの表示信号S I G(実線)が供給される。記憶期間1においては走査信号G A T E Aが電圧V S S 2に立ち下げられており、画素電極P Eがフローティングである。そのため、画素電位P I X(破線)は、共通信号V C O Mの電位上昇に引き寄せられて上昇する。つまり、画素電位P I Xは、直前の表示期間0における画素電位P I Xと共通信号V C O Mとの電位差が維持されるように電圧V D D × 2に上昇する。電圧V D D × 2は、電圧V D D, V S Sの差分の約2倍の電圧である。

#### 【0044】

記憶期間1に続く表示期間1においては、信号線Sに交流の第1駆動信号x F R Pが供給される。表示期間1に続く記憶期間2においては、メモリ10のHレベルの設定を継続すべく、再び電圧V D Dの表示信号S I Gが供給される。記憶期間2において画素電極P Eがフローティングであるため、画素電位P I Xは、共通信号V C O Mの電位の下降に引き寄せられて下降する。つまり、直前の表示期間1における画素電位P I Xと共通信号V C O Mとの電位差が維持されるように電圧-V D Dに下降する。電圧-V D Dは、およそ電圧V D D, V S Sの差分に相当する分だけ電圧V S Sより低い電圧である。このように、記憶期間2においては、信号線Sと画素電極P Eとの間に大きな電位差V xが生じる。

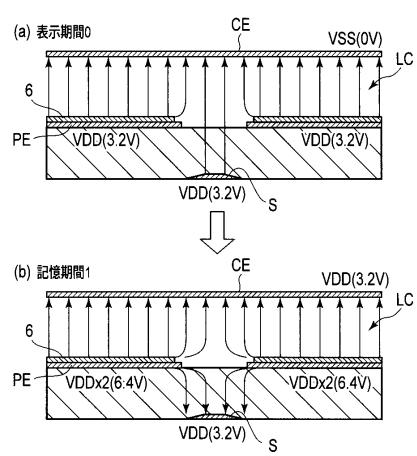

#### 【0045】

図8は、(a)記憶期間1の直前の表示期間0、及び、(b)記憶期間1において、副画素S P Xに発生する電界の様子を示す断面図である。この図の例では、反射層6が画素電極P Eの液晶層L C側の面に形成されている。反射層6は、第2基板S U B 2に入射して液晶層L Cを通り第1基板S U B 1に到達した光を、第2基板S U B 2の方向へ反射する。図8(a)においては、画素電極P Eが電圧V D Dであり、共通電極C Eが電圧V S Sである。したがって、画素電極P Eから共通電極C Eに向かう電界が発生する。また、信号線Sが電圧V D Dであるために、信号線Sから共通電極C Eに向かう電界も発生する。

#### 【0046】

一方で、図8(b)においては、画素電極P Eが電圧V D D × 2であり、共通電極C E及び信号線Sが電圧V D Dである。したがって、画素電極P Eから共通電極C Eに向かう電界と、画素電極P Eから信号線Sに向かう電界とが発生する。

例えば、電圧V S Sを0V、電圧V D Dを3.2Vとすると、電圧V D D × 2は約6.4Vとなる。この場合、図8(a)(b)で発生する各電界は、いずれも3.2Vの電位差に起因したものとなる。

#### 【0047】

図9は、(a)記憶期間2の直前の表示期間1、及び、(b)記憶期間2において、副画素S P Xに発生する電界の様子を示す断面図である。図9(a)においては、画素電極

10

20

30

40

50

P E 及び信号線 S が電圧 V S S であり、共通電極 C E が電圧 V D D である。したがって、共通電極 C E から画素電極 P E 及び信号線 S に向かう電界が発生する。

【 0 0 4 8 】

一方で、図 9 ( b )においては、画素電極 P E が電圧 - V D D であり、共通電極 C E が電圧 V S S であり、信号線 S が電圧 V D D である。この場合、共通電極 C E から画素電極 P E に向かう電界と、信号線 S から画素電極 P E に向かう電界とが主に発生する。

【 0 0 4 9 】

例えば、電圧 V S S を 0 V 、電圧 V D D を 3.2 V とすると、電圧 - V D D は約 - 3.2 V となる。この場合、図 9 ( a ) ( b )において画素電極 P E と共通電極 C E との間に発生する電界は、3.2 V の電位差に起因したものとなる。また、図 9 ( b )において画素電極 P E と信号線 S との間に発生する電界は、6.4 V の電位差 V x に起因した強い電界となる。この強い電界は、図 9 ( b )において破線で囲った領域のように、画素電極 P E と共通電極 C E との間の縦電界に影響し、液晶層 L C の配向制御能が低下するので、副画素 S P X の輝度低下などの不具合が生じ得る。

10

【 0 0 5 0 】

図 7 の下方に、画像が表示された表示領域 D A ( D I S P L A Y )を模式的に示している。全ての副画素 S P X を連続的に白表示とする場合を想定しているため、基本的には表示領域 D A の全てが連続して白表示である。しかしながら、記憶期間 2 においては、電位差 V x に起因した輝度低下により、表示領域 D A の画像が他の期間に比べて暗くなるフラッシング現象が生じる。このようなフラッシング現象は、表示品位の低下を招く一因となる。

20

【 0 0 5 1 】

なお、ここでは白表示の場合について例示したが、黒表示の場合でも同様に、記憶期間において画素電極 P E と信号線 S との間に大きな電位差 V x が形成されて、フラッシング現象が生じ得る。

以下、フラッシング現象による表示品位の低下を抑制するための実施形態を開示する。

【 0 0 5 2 】

( 第 1 実施形態 )

第 1 実施形態においては、表示期間から記憶期間への移行の際、表示期間の共通信号 V C O M 及び補助容量信号 C S ( F R P ) の電位を記憶期間においても維持することにより、フラッシング現象を抑制する。以下、本実施形態の詳細を説明する。

30

【 0 0 5 3 】

図 10 は、第 1 実施形態に係る表示装置 1 の動作の一例を示すタイミングチャートである。この図においては、図 7 の場合と同じく、副画素 S P X が白表示となる場合を想定して、時系列の表示期間 0 、記憶期間 1 、表示期間 1 、記憶期間 2 、表示期間 2 における各信号の電位を示している。

【 0 0 5 4 】

記憶期間 1 の直前、すなわち表示期間 0 の後半のフレーム期間 T F において、共通信号 V C O M 及び補助容量信号 C S の電圧は V S S である。この場合において、交流駆動回路 2 0 は、記憶期間 1 においても共通信号 V C O M 及び補助容量信号 C S の電圧を V S S で維持する。すなわち、交流駆動回路 2 0 は、記憶期間 1 において交流出力を停止する。記憶期間 1 に続く表示期間 1 において、交流駆動回路 2 0 は、交流出力を再開する。これにより、共通信号 V C O M 及び補助容量信号 C S は、フレーム期間 T F ごとに電圧 V S S 、 V D D の間で変位する交流信号 ( F R P ) となる。

40

【 0 0 5 5 】

記憶期間 2 の直前、すなわち表示期間 1 の後半のフレーム期間 T F において、共通信号 V C O M 及び補助容量信号 C S の電圧は V D D である。この場合にも、交流駆動回路 2 0 は、交流出力を停止して記憶期間 2 における共通信号 V C O M 及び補助容量信号 C S の電圧を V D D で維持し、記憶期間 2 に続く表示期間 2 において交流出力を再開する。

50

## 【0056】

図10において、表示信号S I G ( × F R P )の波形は図7と同じであるが、画素電位P I Xの波形は異なる。すなわち、記憶期間1においては、共通信号V C O Mが電圧V S Sであるために画素電位P I Xは電圧V D Dとなる。また、記憶期間2においては共通信号V C O Mの電圧がV D Dであるために画素電位P I Xが電圧V S Sとなる。

## 【0057】

図7の例においては、記憶期間2において画素電極P Eと信号線Sとの電位差V xが電圧V D D, V S Sの差分以上に大きくなつたが、図10の例においては電位差V xが電圧V D D, V S Sの差分にとどまる。したがつて、本実施形態によれば、フラッシング現象が抑制され、表示品位の低下を防止することができる。

10

## 【0058】

なお、ここでは白表示の場合を例にとって説明したが、黒表示の場合でも同様にフラッシング現象を抑制することができる。なお、本実施形態では、記憶期間1及び記憶期間2の両方において共通信号V C O Mの交流出力を停止しているが、一部の記憶期間だけ交流出力を停止させても良い。

## 【0059】

本実施形態では、交流駆動回路20の出力を制御することでフラッシング現象を抑制しており、新たな配線や素子を用いていない。したがつて、副画素S P Xの精細度の低下や、回路パターンの密度増加による製造歩留りの悪化などのデメリットが発生しない。

以上説明した他にも、本実施形態からは種々の好適な効果を得ることができる。

20

## 【0060】

## (第2実施形態)

第2実施形態においては、記憶期間を短くすることにより、フラッシング現象を人の目で捉えにくくする。以下、本実施形態の詳細を説明する。

図11は、第2実施形態に係る表示装置1の動作の一例を示すタイミングチャートである。この図においては、図7の場合と同じく、副画素S P Xが白表示となる場合を想定して、時系列の表示期間0、記憶期間1、表示期間1、記憶期間2、表示期間2における各信号の電位を示している。

## 【0061】

各表示期間及び各記憶期間における信号の波形は、図7と同様である。但し、図11においては、記憶期間を構成するフレーム期間がT F 1であり、表示期間を構成する各フレーム期間がいずれもT F 2である。フレーム期間T F 1は、フレーム期間T F 2よりも短い(T F 1 < T F 2)。

30

## 【0062】

記憶期間において交流駆動回路20が outputする共通信号V C O M及び補助容量信号C Sの周波数は、第1周波数F q 1 ( h z )である。一方で、表示期間において交流駆動回路20が outputする共通信号V C O M及び補助容量信号C S ( F R P )の周波数は、第2周波数F q 2 ( h z )である。フレーム期間T F 1がフレーム期間T F 2よりも短いので、第1周波数F q 1は第2周波数F q 2よりも高くなる(F q 1 > F q 2)。なお、この周波数は、図10の通り、ある特定の値から極大値又は極小値を経由し、その特定の値に戻る波形の個数を基準としている。

40

## 【0063】

図11の例においては、図7の場合と同様に、記憶期間2において画素電極P Eと共に電極C Eの電位差V xが大きくなり、フラッシング現象が生じ得る。しかしながら、第1周波数F q 1が第2周波数F q 2に比べて高いために、記憶期間2において輝度が低下する期間が相対的に短くなり、フラッシング現象が目立たなくなる。

## 【0064】

例えば、第1周波数F q 1を第2周波数F q 2の1.5倍以上とすれば、フラッシング現象による表示品位の低下を好適に防止することができる。第1周波数F q 1を第2周波数F q 2の2倍以上とすれば、表示品位の低下を防止する一層高い効果を得ることができ

50

る。なお、メモリ 10 に安定して電位を記憶させるため、第 1 周波数  $F_{q1}$  は第 2 周波数  $F_{q2}$  の 5 倍以下であることが好ましい。

#### 【0065】

他の観点から言えば、第 1 周波数  $F_{q1}$  を 90 Hz 以上とすればフラッシング現象が人の目で捉えにくくなり、表示品位の低下を好適に防止することができる。さらに、第 1 周波数  $F_{q1}$  を 120 Hz 以上とすればフラッシング現象が殆ど視認されないので、一層好ましい。なお、第 2 周波数  $F_{q2}$  は、例えば 60 Hz 程度に定めることができる。なお、メモリ 10 に安定して電位を記憶させるため、第 1 周波数  $F_{q1}$  は 300 Hz 以下であることが好ましい。

#### 【0066】

なお、ここでは白表示の場合を例にとって説明したが、黒表示の場合でも同様にフラッシング現象を抑制することができる。

本実施形態では、第 1 実施形態と同じく、交流駆動回路 20 の出力を制御することでフラッシング現象を抑制しており、新たな配線や素子を用いていない。したがって、副画素 SPX の精細度の低下や、回路パターンの密度増加による製造歩留りの悪化などのデメリットが発生しない。

以上説明した他にも、本実施形態からは種々の好適な効果を得ることができる。

#### 【0067】

##### (第 3 実施形態)

第 3 実施形態においては、画素電位 PIX が所定の条件を満たす場合に表示期間から記憶期間への移行を可能とすることで、フラッシング現象の発生を防止する。以下、本実施形態の詳細を説明する。

図 12 は、第 3 実施形態に係る表示装置 1 の動作の一例を示すタイミングチャートである。この図においては、図 7 の場合と同じく、副画素 SPX が白表示となる場合を想定して、時系列の表示期間 0、記憶期間 1、表示期間 1、記憶期間 2、表示期間 2 における各信号の電位を示している。

#### 【0068】

本実施形態では、表示期間から記憶期間へ移行する際に、制御装置 2 がこの移行の可否を判定する。この判定には、電位  $V_a$ 、第 1 電位  $V_1$ 、第 2 電位  $V_2$ 、第 3 電位  $V_3$  が用いられる。電位  $V_a$  は、記憶期間の開始直前の画素電位 PIX である。第 1 電位  $V_1$  は第 1 駆動信号  $\times$  F R P の L レベルの電圧  $V_{SS}$  であり、第 2 電位  $V_2$  は第 1 駆動信号  $\times$  F R P の H レベルの電圧  $V_{DD}$  である。第 3 電位  $V_3$  は、記憶期間においてメモリ 10 に記憶される表示信号 S I G の電位である。

#### 【0069】

具体的には、制御装置 2 は、“電位  $V_a$  が第 1 電位  $V_1$  と第 2 電位  $V_2$  のうち第 3 電位  $V_3$  との電位差が小さい方の電位である”との実行条件が成立する場合に、記憶期間への移行が可であると判定する。この場合、記憶期間に移行して、第 3 電位  $V_3$  をメモリ 10 に記憶させる動作が行われる。一方で、制御装置 2 は、上記実行条件が成立しない場合に、記憶期間への移行が不可であると判定する。この場合、本来であれば記憶期間へ移行すべき書き込みタイミングが到来しても記憶期間に移行せずに、表示期間を所定のフレーム期間 T F ( 例えは 1 つのフレーム期間 T F ) だけ延長する。そして、記憶期間への移行が可であるか再び判定し、可であれば記憶期間へ移行する。

#### 【0070】

図 12 を参照して具体例を示す。まず、記憶期間 1 においてメモリ 10 に記憶させる第 3 電位  $V_3$  は、白電位である  $V_{DD}$  である。この場合、第 1 電位  $V_1$  ( $V_{SS}$ ) と第 2 電位  $V_2$  ( $V_{DD}$ ) のうち第 3 電位  $V_3$  との電位差が小さい電位は、第 3 電位  $V_3$  との電位差が無い第 2 電位  $V_2$  となる。記憶期間 1 を実行すべき書き込みタイミング 1 の直前の表示期間 0 において、電位  $V_a$  は第 2 電位  $V_2$  である。よって、上記実行条件が成立し、記憶期間への移行が可である。したがって、この書き込みタイミング 1 で記憶期間 1 の動作が実行される。

## 【0071】

一方で、記憶期間2を実行すべき書込タイミング2の直前の表示期間1において、電位V<sub>a</sub>（図中では括弧を付している）は第1電位V<sub>1</sub>である。さらに、記憶期間2においてメモリ10に記憶させる第3電位V<sub>3</sub>はV<sub>DD</sub>である。この場合には上記実行条件が成立しないため、記憶期間への移行が不可である。したがって、書込タイミング2では記憶期間2の動作が実行されず、表示期間1が1つのフレーム期間T<sub>F</sub>だけ延長される。

## 【0072】

続いて、延長後に記憶期間2の動作を実行すべき書込タイミング2aの直前の表示期間1（図7の例では延長期間）において、電位V<sub>a</sub>は第2電位V<sub>2</sub>である。この場合には上記実行条件が成立するため、記憶期間への移行が可である。したがって、この書込タイミング2aで記憶期間2の動作が実行される。10

## 【0073】

なお、図12の例では実行条件が成立しない場合に1つのフレーム期間T<sub>F</sub>だけ表示期間1が延長される場合を示したが、より多くのフレーム期間T<sub>F</sub>に亘って表示期間1が延長されても良い。

## 【0074】

また、ここでは表示領域D<sub>A</sub>に含まれる全ての副画素S<sub>PX</sub>が白表示となる場合を想定したが、全ての副画素S<sub>PX</sub>が黒表示となる場合や、白表示の副画素S<sub>PX</sub>と黒表示の副画素S<sub>PX</sub>とが混在する場合にも同様の制御を適用できる。白表示の副画素S<sub>PX</sub>と黒表示の副画素S<sub>PX</sub>とが混在する場合、1つの書込タイミングにおいて電位V<sub>a</sub>と第3電位V<sub>3</sub>とが異なる副画素S<sub>PX</sub>が混在することになる。この場合においては、例えば、全ての副画素S<sub>PX</sub>のうち上記実行条件が成立する副画素S<sub>PX</sub>の数が所定の閾値以上である場合に表示期間を延長して、記憶期間を後にずらしても良い。また、黒表示の副画素S<sub>PX</sub>におけるフラッシング現象は白表示の場合に比べて表示品位に与える影響が小さいことから、白表示の副画素S<sub>PX</sub>の全てについて実行条件が成立する場合、或いは、白表示の副画素S<sub>PX</sub>のうち上記実行条件が成立する副画素S<sub>PX</sub>の数が所定の閾値以上である場合に表示期間を延長して、記憶期間を後にずらしても良い。20

## 【0075】

本実施形態によれば、記憶期間における表示信号S<sub>IG</sub>の電位と、この記憶期間の直前の画素電位P<sub>IX</sub>とが近い値（図12の例では同じ値）となる。したがって、記憶期間においてフローティングとなった画素電極P<sub>E</sub>の電位が共通電極C<sub>E</sub>の電位に応じて変動しても、図7に示したような大きな電位差V<sub>x</sub>が生じることはない。これにより、フラッシング現象を抑制することができる。30

以上説明した他にも、本実施形態からは種々の好適な効果を得ることができる。

## 【0076】

## (第4実施形態)

第1乃至第3実施形態においては、図7乃至図9にて説明した問題点を解消するための方法を開示した。ここで、デジタルモードにおいて生じ得る他の問題点につき、図13のタイミングチャートを用いて説明する。

表示期間から記憶期間へ移行する際に、走査信号GATEAが電圧V<sub>SS2</sub>に立ち下り、スイッチング素子Q<sub>1</sub>、Q<sub>2</sub>がオフされる。これにより、選択信号線12aと画素電極P<sub>E</sub>とが電気的に遮断されて、画素電極P<sub>E</sub>がフローティングとなる。走査信号GATEAが立ち下がる際には、画素電極P<sub>E</sub>と走査線Gとの容量結合により、画素電位P<sub>IX</sub>も所定の電位Vだけ低下し得る。この場合、記憶期間において副画素S<sub>PX</sub>の輝度変化が生じ、表示品位が低下する。40

## 【0077】

このような輝度変化を抑制するために、本実施形態では、スイッチング素子Q<sub>1</sub>、Q<sub>2</sub>が選択信号線12aと画素電極P<sub>E</sub>とを遮断する前に、共通信号V<sub>COM</sub>及び補助容量信号C<sub>S</sub>の電位を既定量だけ低下させる。以下、この動作の具体例を示す。

図14は、第4実施形態に係る表示装置1の動作の一例を示すタイミングチャートである50

る。このタイミングチャートは、第1実施形態に係る動作に本実施形態を適用した例である。交流駆動回路20は、表示期間から記憶期間へ移行するにあたり、走査信号GATEAが立ち下がるタイミングよりも僅かに早いタイミングで、共通信号VCOM及び補助容量信号CSの電位を既定量（図の例ではV）だけ低下させる。

【0078】

走査信号GATEAが立ち下がる際には、走査線Gと画素電極PEとの容量結合により、画素電位PIXが電位Vだけ低下する。走査信号GATEAが立ち下がった後に、交流駆動回路20は、共通信号VCOM及び補助容量信号CSの電位を既定量（V）だけ上昇させる。このとき、画素電極PEはフローティングであるので、画素電位PIXは共通信号VCOMの電位上昇に引き寄せられ、ともに既定量（V）だけ上昇する。

10

【0079】

以上の動作によれば、表示期間における画素電極PEと共通電極CEとの間の電位差が、この表示期間の直後の記憶期間においても維持される。したがって、走査線Gと画素電極PEとの容量結合に起因した輝度変化を防止することができる。

なお、図14の例では上記既定量が電位Vである場合を示したが、上記既定量はVと完全に一致する必要はない。例えば、上記既定量がVより小さい値であっても、記憶期間における輝度変化の低減に寄与し得る。

また、交流駆動回路20は、記憶期間の全てに亘って共通信号VCOMを上記既定量だけ低下させ続けても良い。

【0080】

20

また、図14の例では、第1実施形態に係る動作に本実施形態を適用した場合を例示したが、第2実施形態や第3実施形態に係る動作に本実施形態を適用することもできる。

以上、本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【0081】

30

例えば、各実施形態にて開示した構成は、適宜に組み合わせることができる。

また、各実施形態ではアナログモード及びデジタルモードの機能を備える表示装置を開示したが、各実施形態における表示装置の動作はデジタルモードの機能のみを備える表示装置に適用することもできる。

【符号の説明】

【0082】

1...表示装置、2...制御装置、4...信号線駆動回路、10...メモリ、11...ゲート回路、12...選択制御回路、12a...選択信号線、13...記憶制御回路、20...交流駆動回路、LCS...補助容量線、PE...画素電極、CE...共通電極、LC...液晶層、G...走査線、S...信号線、LP1...第1電源線、LP2...第2電源線、LGD...デジタル走査線、LCM...共通電極線、Q1~Q9...スイッチング素子、Csc...補助容量。

40

【図1】

【図2】

【図3】

【 図 4 】

【 図 5 】

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図 10】

図 10

【図 11】

図 11

【図 12】

図 12

【図 13】

図 13

【図14】

図14

---

フロントページの続き

(51)Int.CI. F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 2 4 B |

| G 0 9 G | 3/20 | 6 2 1 K |

| G 0 9 G | 3/20 | 6 2 4 D |

(56)参考文献 特開2008-256762 (JP, A)

特開2011-215635 (JP, A)

特開2014-071372 (JP, A)

国際公開第2011/077825 (WO, A1)

特開2013-025311 (JP, A)

国際公開第2011/033813 (WO, A1)

特開2008-058937 (JP, A)

韓国公開特許第10-2013-0100498 (KR, A)

特開2013-025069 (JP, A)

(58)調査した分野(Int.CI., DB名)

|         |         |

|---------|---------|

| G 0 9 G | 3 / 3 6 |

| G 0 9 G | 3 / 2 0 |