# (10) **DE 10 2007 037 798 A1** 2009.02.26

(12)

# Offenlegungsschrift

(21) Aktenzeichen: 10 2007 037 798.5

(22) Anmeldetag: **10.08.2007** (43) Offenlegungstag: **26.02.2009**

(30) Unionspriorität:

11/830,614 30.07.2007 US

(71) Anmelder:

Qimonda Flash GmbH, 01099 Dresden, DE

(74) Vertreter:

Schoppe, Zimmermann, Stöckeler & Zinkler, 82049 Pullach

(72) Erfinder:

Pilla, Camillo, 82008 Unterhaching, DE

(51) Int Cl.8: **H01L 25/16** (2006.01)

(56) Für die Beurteilung der Patentfähigkeit in Betracht gezogene Druckschriften:

US2005/02 66 614 A1 US2005/01 70 600 A1 US2002/01 95 697 A1

Die folgenden Angaben sind den vom Anmelder eingereichten Unterlagen entnommen

Prüfungsantrag gemäß § 44 PatG ist gestellt.

(54) Bezeichnung: Anordnung von Halbleiterchips mit integrierter Schaltung und Verfahren zum Fertigen derselben

(57) Zusammenfassung: Eine Anordnung von Halbleiterchips mit intergrierter Schaltung weist einen ersten Halbleiterchip, der eine erste elektrische Kopplungsstelle aufweist, und einen zweiten Halbleiterchip, der eine zweite elektrische Kopplungsstelle aufweist, wobei der zweite Halbleiterchip auf den ersten Halbleiterchip gestapelt ist, derart, dass die erste elektrische Kopplungsstelle zumindest teilweise freiliegt, wobei die erste elektrische Kopplungsstelle direkt elektrisch verbunden sind, und einen dritten Halbleiterchip auf, der über dem ersten Halbleiterchip und dem zweiten Halbleiterchip angeordnet ist, derart, dass eine Ausnehmung gebildet ist, wobei eine der ersten elektrischen Kopplungstellen in der Ausnehmung angeordnet ist.

## **Beschreibung**

**[0001]** Ausführungsbeispiele der Erfindung beziehen sich auf eine Anordnung von Halbleiterchips mit integrierter Schaltung und auf ein Verfahren zum Fertigen derselben.

**[0002]** Es ist die Aufgabe der vorliegenden Erfindung, eine Anordnung von Halbleiterchips mit integrierter Schaltung, eine Vorrichtung und ein Verfahren zum Fertigen einer Anordnung von Halbleiterchips mit integrierter Schaltung mit verbesserten Charakteristika zu schaffen.

**[0003]** Diese Aufgabe wird durch eine Anordnung gemäß Anspruch 1 und Anspruch 16, eine Vorrichtung gemäß Anspruch 17 und ein Verfahren gemäß Anspruch 18 gelöst.

**[0004]** Bevorzugte Ausführungsbeispiele der vorliegenden Erfindung werden nachfolgend Bezug nehmend auf die beiliegenden Zeichnungen näher erläutert. Es zeigen:

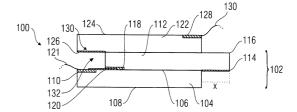

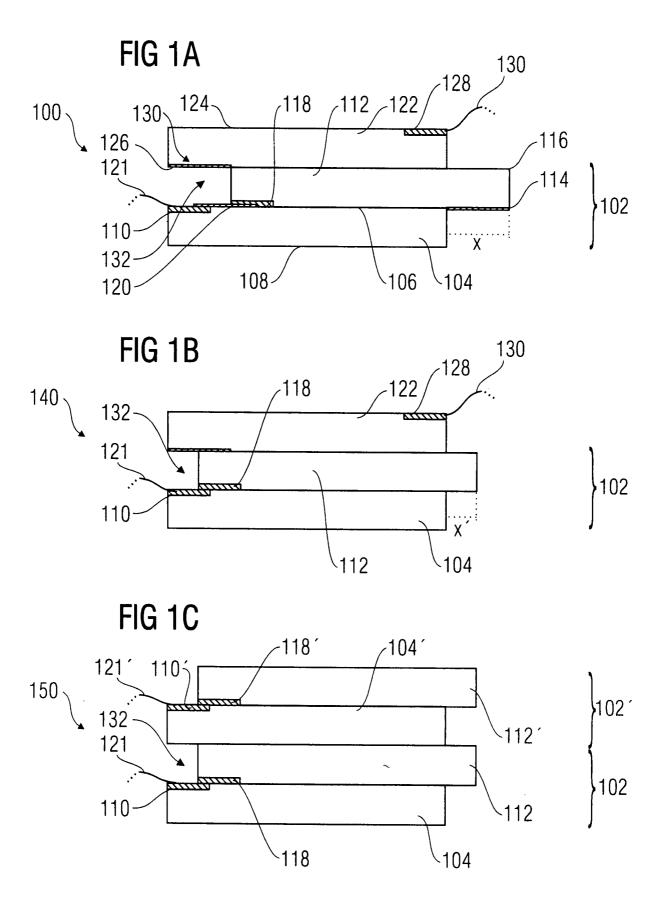

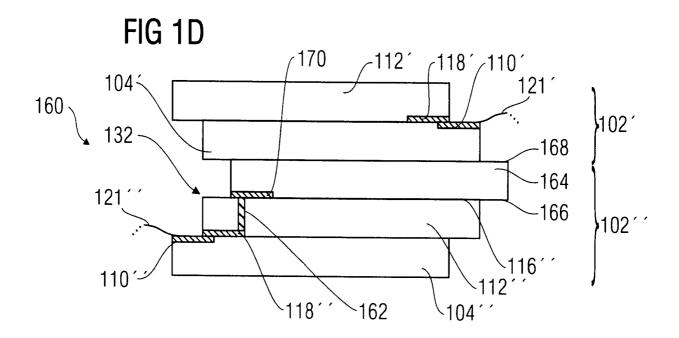

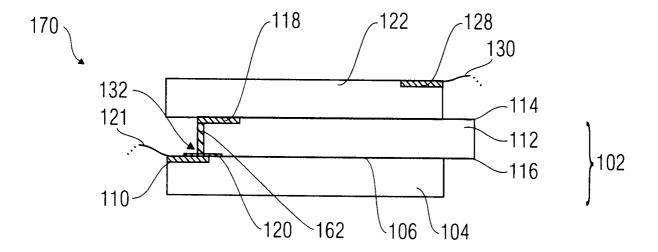

**[0005] Fig.** 1(A) bis (E) seitliche Querschnittsansichten von Anordnungen von Halbleiterchips mit integrierter Schaltung gemäß Ausführungsbeispielen;

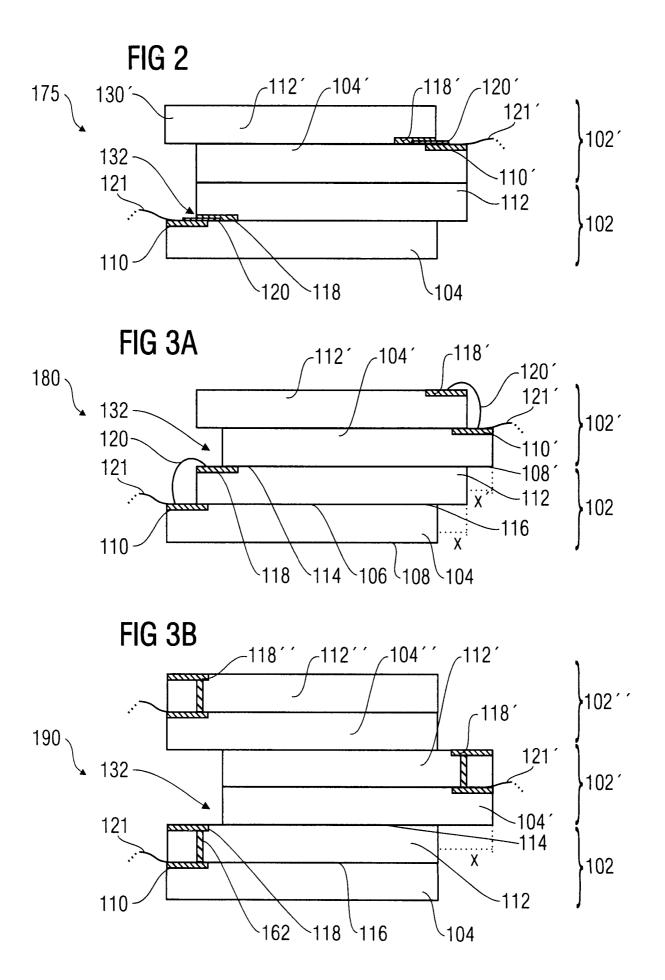

**[0006]** Fig. 2 eine seitliche Querschnittsansicht einer Anordnung von Halbleiterchips mit integrierter Schaltung gemäß einem weiteren Ausführungsbeispiel;

**[0007] Fig.** 3(A) und (B) seitliche Querschnittsansichten von Anordnungen von Halbleiterchips mit integrierter Schaltung gemäß noch einem anderen Ausführungsbeispiel;

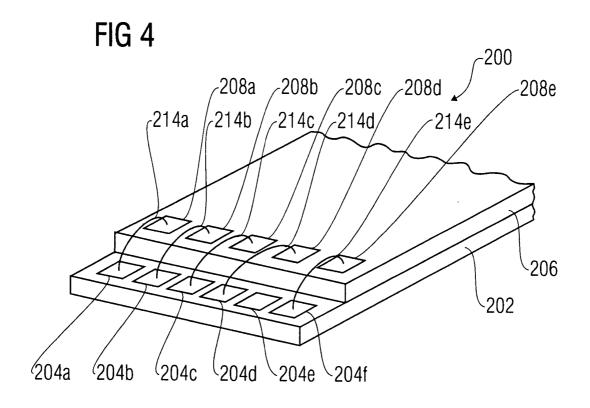

**[0008]** Fig. 4 eine perspektivische Ansicht eines Beispiels eines Stapels (Unteranordnung) von Halbleiterchips mit integrierter Schaltung, die bei der in Fig. 3(A) beschriebenen Anordnung verwendet werden;

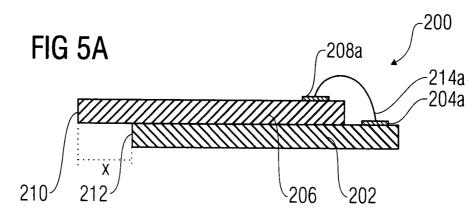

**[0009]** Fig. 5(A) eine seitliche Querschnittsansicht des Stapels von Halbleiterchips mit integrierter Schaltung von Fig. 4;

**[0010] Fig.** 5(B) eine seitliche Querschnittsansicht eines Halbleiterchips mit einer Filmanbringung;

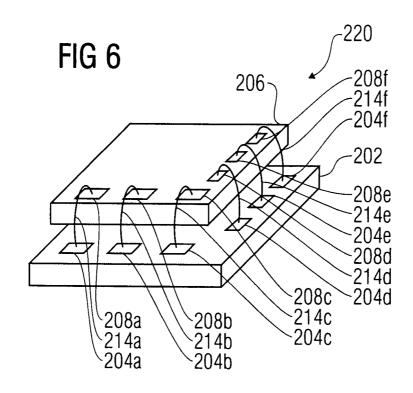

**[0011]** Fig. 6 eine perspektivische Ansicht eines anderen Beispiels eines Stapels von Halbleiterchips mit integrierter Schaltung;

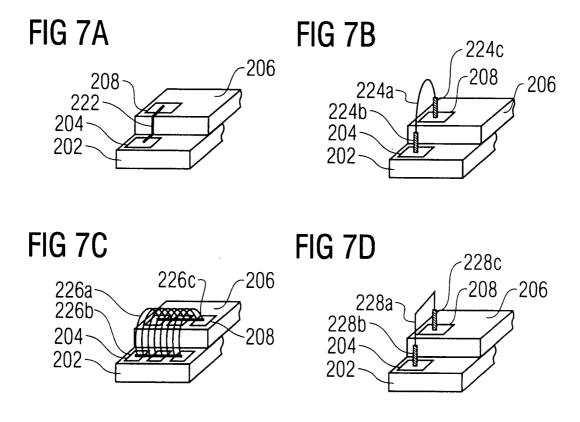

**[0012] Fig.** 7(A) bis (D) Beispiele von leitfähigen Elementen zum Verbinden elektrischer Kopplungsstellen (z. B. Kontaktanschlussflächen) von zwei oder mehr Halbleiterchips;

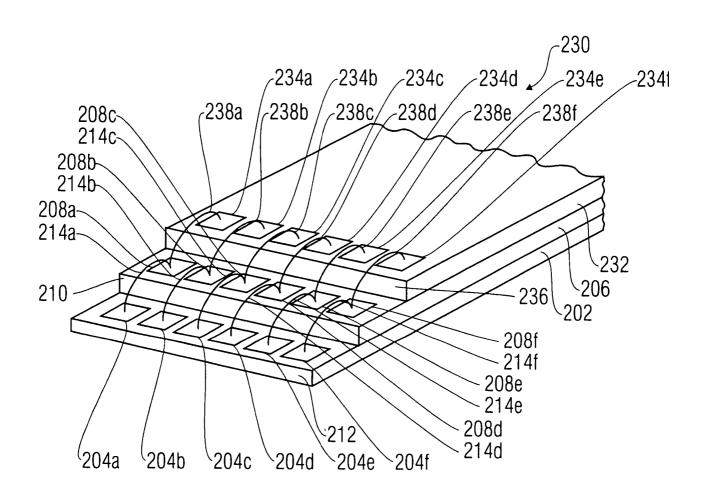

**[0013]** Fig. 8 eine perspektivische Ansicht noch eines anderen Beispiels eines Stapels von Halbleiterchips mit integrierter Schaltung;

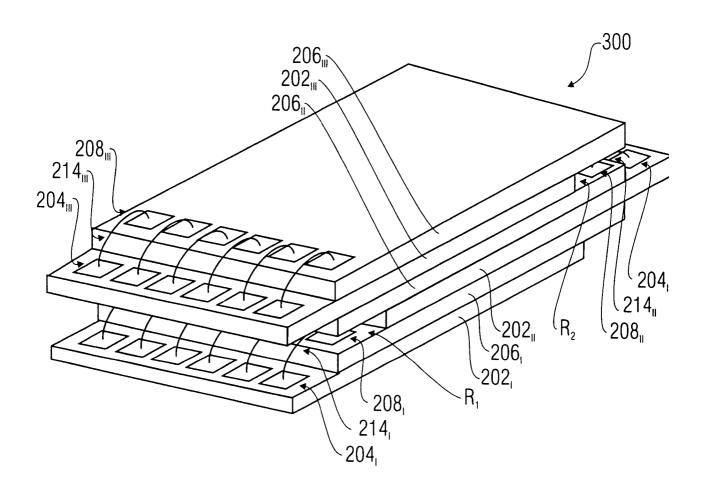

**[0014]** Fig. 9 eine schematische perspektivische Ansicht einer Anordnung von Halbleiterchips mit integrierter Schaltung gemäß noch einem anderen Ausführungsbeispiel;

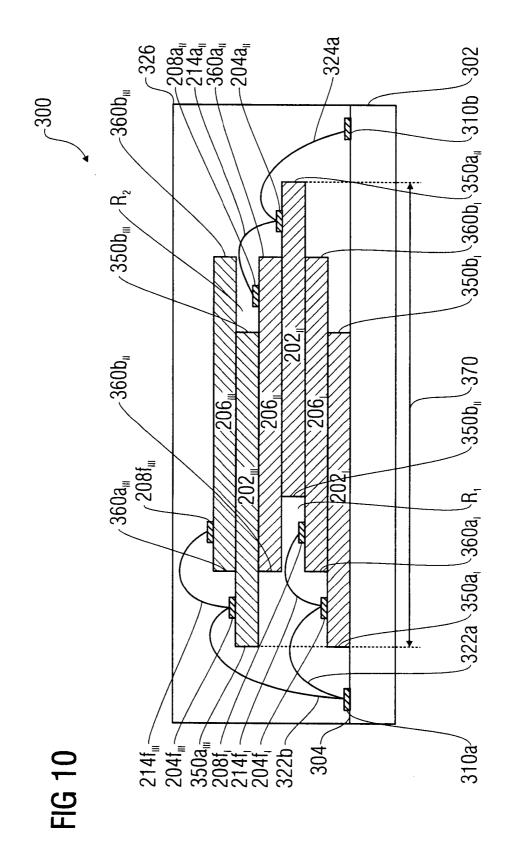

**[0015]** Fig. 10 eine seitliche Querschnittsansicht eines Mehrchipgehäuses bzw. Mehrchipbausteins, bei dem die Anordnung von Halbleiterchips mit integrierter Schaltung von Fig. 9 an einem Träger angeordnet ist:

[0016] Fig. 11 eine seitliche Querschnittsansicht eines anderen Mehrchipbausteins, der eine Anordnung von Halbleiterchips mit integrierter Schaltung gemäß einem anderen Ausführungsbeispiel der Erfindung aufweist, die an einem Träger angeordnet ist; und

**[0017] Fig.** 12(A) bis 12(B) ein Flussdiagramm, das ein Ausführungsbeispiel zum Herstellen eines Mehrchipbausteins darstellt, wie es in <u>Fig. 10</u> beschrieben ist.

**[0018]** Auf dem Gebiet integrierter Schaltungen kann es einen Bedarf danach geben, die Halbleiterchipdichte innerhalb eines einzigen Bausteins zu erhöhen, während bestehende Standards hinsichtlich Bausteinabmessungen und Bausteinstandfläche beibehalten werden.

[0019] Anordnungen von Halbleiterchips mit integrierter Schaltung gemäß Ausführungsbeispielen werden unten beschrieben. Die Anordnung kann einen ersten Halbleiterchip, der eine erste elektrische Kopplungsstelle aufweist, und einen zweiten Halbleiterchip, der eine zweite elektrische Kopplungsstelle aufweist, wobei der zweite Halbleiterchip auf den ersten Halbleiterchip gestapelt ist, derart, dass die erste elektrische Kopplungsstelle zumindest teilweise freiliegt, wobei die erste elektrische Kopplungsstelle und die zweite elektrische Kopplungsstelle direkt elektrisch verbunden sind, und einen dritten Halbleiterchip aufweist, der über dem ersten Halbleiterchip und dem zweiten Halbleiterchip angeordnet ist, derart, dass eine Ausnehmung gebildet ist, wobei eine der ersten elektrischen Kopplungsstellen in der Ausnehmung angeordnet ist. In der folgenden Beschreibung der Ausführungsbeispiele werden der erste Halbleiterchip und der zweite Halbleiterchip, der an den ersten Halbleiterchip gestapelt ist, eventuell als ein Stapel bezeichnet, der den ersten Halbleiterchip und den zweiten Halbleiterchip aufweist.

[0020] Ausführungsbeispiele stapeln Halbleiterchips in einem Baustein, d. h. stellen eine Mehrzahl von Halbleiterchips oder Chips in einem einzigen Baustein bereit. Um die Menge an Siliziumhalbleiter-

chipfläche zu erhöhen, die innerhalb eines einzigen Bausteins gehäust sein kann, können Halbleiterchips oder Chips, die eine spezifische Funktionalität aufweisen, gestapelt werden, d. h. eine Mehrzahl von Chips kann aufeinander angeordnet sein. Ein Halbleiterchipstapeln ist ein Prozess eines Befestigens mehrerer Halbleiterchips oder Chips aufeinander innerhalb eines einzigen Bausteins. Neben einem Einsparen von Fläche an dem Substrat kann ein Halbleiterchipstapeln ferner in einer besseren elektrischen Leistungsfähigkeit des Bauelements bzw. der Vorrichtung auf Grund der kürzeren Führung bzw. des kürzeren Routings von Verbindungen zwischen Schaltungen resultieren, was zu einer besseren Signalgüte führen kann. Derartige Mehrchipbausteine (auch als Mehrchipmodule bezeichnet) können als ein einziger Chip fungieren. Der Halbleiterchip kann aus irgendeinem Halbleitermaterial hergestellt sein, wie beispielsweise Silizium (Si), Galliumarsenid (GaAs), Siliziumcarbid (SiC) oder Indiumphosphid (InP). Der Halbleiterchip eines derartigen Mehrchipbausteins kann die gleichen Funktionalitäten oder unterschiedliche Funktionalitäten aufweisen, z. B. kann ein Halbleiterchip eine Mikrosteuerung sein und kann ein anderer Halbleiterchip ein Flash-Speicher, ein dynamischer Direktzugriffsspeicher (DRAM; DRAM = Dynamic Random Access Memory), ein statischer Direktzugriffsspeicher (SRAM; SRAM = Static Random Access Memory) oder ein Chip mit einer anderen Funktionalität sein. Diese Art eines Bildens eines Mikrochips mit einer bestimmten Funktionalität kann kostengünstiger als eine monolithische Integration innerhalb eines (einzigen) Halbleiterchips sein.

**[0021] Fig.** 1(A) bis (E) zeigen Querschnittsansichten von Anordnungen von Halbleiterchips mit integrierter Schaltung gemäß Ausführungsbeispielen.

[0022] Fig. 1(A) zeigt eine Anordnung 100 von Halbleiterchips mit integrierter Schaltung, die einen Stapel 102 aufweist. Der Stapel weist einen ersten Halbleiterchip 104 auf, der eine erste Oberfläche 106 (in Fig. 1(A) eine obere Oberfläche) und eine zweite Oberfläche **108** (in **Fig.** 1(A) eine untere Oberfläche) gegenüber der ersten Oberfläche 106 aufweist. An der ersten Oberfläche 106 ist eine erste elektrische Kopplungsstelle 110 vorgesehen, beispielsweise eine Kontaktanschlussfläche. Der Stapel 102 weist einen zweiten Halbleiterchip 112 auf, der eine erste Oberfläche **114** (in **Fig.** 1(A) eine untere Oberfläche) und eine zweite Oberfläche 116 (in Fig. 1(A) eine obere Oberfläche) aufweist. An der ersten Oberfläche 114 des zweiten Halbleiterchips 112 ist eine zweite elektrische Kopplungsstelle 118 gebildet, beispielsweise eine Kontaktanschlussfläche. Der Stapel 102 weist ferner ein leitfähiges Element 120 auf, das bei dem in Fig. 1(A) gezeigten Ausführungsbeispiel für eine direkte elektrische Verbindung der ersten elektrischen Kopplungsstelle 110 des ersten Halbleiterchips 104 und der zweiten elektrischen Kopplungsstelle 118 des zweiten Halbleiterchips 112 vorgesehen ist. Wie es aus Fig. 1(A) ersichtlich ist, sind die zwei Halbleiterchips 104 und 112 des Stapels 102 auf eine "Flip-Chip"-Weise angeordnet, d. h. die zwei Halbleiterchips 104 und 112 sind in einer derartigen Weise aufeinander gestapelt, dass die jeweiligen ersten Oberflächen 106 bzw. 114 derselben einander zugewandt sind und sich tatsächlich in Kontakt miteinander befinden. Der erste Halbleiterchip 104 und der zweite Halbleiterchip 112 sind in einer derartigen Weise aufeinander gestapelt, dass dieselben mit einem Versatz x voneinander angeordnet sind. Dadurch ist die erste elektrische Kopplungsstelle 110 des ersten Halbleiterchips 104 freiliegend, um eine externe Verbindung beispielsweise mit einem Träger oder dergleichen zu ermöglichen. Die externe Verbindung kann beispielsweise durch einen Bonddraht **121** vorgesehen sein, wie es in **Fig.** 1(A) gezeigt ist.

[0023] Auf den Stapel 102 ist ein weiterer Halbleiterchip 122 angeordnet. Der weitere Halbleiterchip 122 weist eine erste Oberfläche 124 (in Fig. 1(A) eine obere Oberfläche) und eine zweite Oberfläche 126 (in Fig. 1(A) eine untere Oberfläche) auf. Eine weitere elektrische Kopplungsstelle 128 ist an der ersten Oberfläche 124 des weiteren Halbleiterchips 122 angeordnet. Der weitere Halbleiterchip 122 ist auf den oberen Halbleiterchip in dem Stapel 102 gestapelt, d. h. ist auf den zweiten Halbleiterchip 112 gestapelt, in einer derartigen Weise, dass die zweite Oberfläche 116 des zweiten Halbleiterchips 112 und die zweite Oberfläche 126 des weiteren Halbleiterchips 122 sich in Kontakt miteinander befinden. Der weitere Halbleiterchip 122 kann ferner mit dem Träger, der die Anordnung 100 trägt, beispielsweise über einen weiteren Bonddraht 130 verbunden sein.

[0024] Bei dem in Fig. 1(A) gezeigten Ausführungsbeispiel ist der weitere Halbleiterchip 122 an dem Stapel 102 angeordnet, derart, dass die elektrische Kopplungsstelle 128 des weiteren Halbleiterchips 122 und die elektrische Kopplungsstelle 110 des ersten Halbleiterchips 104 an unterschiedlichen Seiten der Anordnung 100 angeordnet sind, z. B. an gegenüberliegenden Seiten der Anordnung 100. Der weitere Halbleiterchip 122 ist auf den Stapel 102 in einer derartigen Weise gestapelt, dass der erste Halbleiterchip 104 und der weitere Halbleiterchip 122 im Wesentlichen mit Bezug aufeinander ausgerichtet sind, so dass ein Abschnitt 130 des weiteren Halbleiterchips 122 sich oberhalb der und über die freiliegende elektrische Kopplungsstelle 110 des ersten Halbleiterchips 104 erstreckt, wodurch eine Ausnehmung 132 definiert ist, in der die erste elektrische Kopplungsstelle 110 angeordnet ist. Die Ausnehmung 132 ist beispielsweise ebenfalls ausreichend, um den Bonddraht 121 aufzunehmen, der vor einem Stapeln des weiteren Halbleiterchips 122 auf den Stapel 102 an der elektrischen Kopplungsstelle 110 angebracht werden kann. Der vertikale Abstand, der im Wesentlichen durch die Dicke des zweiten Halbleiterchips 112 definiert ist, ist ausreichend, um den weiteren Halbleiterchip 122 an dem zweiten Halbleiterchip 112 ohne jegliche Konflikte hinsichtlich des Bonddrahts 121 bereitzustellen.

[0025] Fig. 1(B) zeigt ein anderes Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung. Verglichen mit Fig. 1(A) besteht der Unterschied zwischen den Anordnungen darin, dass bei dem Stapel 102 der erste Chip 104 und der zweite Chip 112 auf unterschiedliche Weise elektrisch verbunden sind. Wie es zu sehen ist, ist das leitfähige Element 120, das bei Fig. 1(A) verwendet wird, weggelassen und ist der zweite Halbleiterchip 112 auf den ersten Halbleiterchip 104 in einer derartigen Weise befestigt, dass die elektrischen Kopplungsstellen 110 und 118 verbunden sind. Dies liefert eine direkte elektrische Verbindung zwischen der elektrischen Kopplungsstelle 110 und der elektrischen Kopplungsstelle 118 ohne den Bedarf eines Bereitstellens eines zusätzlichen leitfähigen Elements 120.

[0026] Fig. 1(C) beschreibt ein weiteres Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung. In Fig. 1(C) ist die Anordnung 150 durch ein Stapeln von zwei Stapeln 102 und 102' übereinander gebildet. Der zweite Stapel 102' ist in der gleichen Weise wie der Stapel 102 gebildet und ist auf dem oberen Halbleiterchip 112 (dem zweiten Halbleiterchip des Stapels 102) befestigt, derart, dass der erste Halbleiterchip 104' des oberen Stapels 102' sich in direktem Kontakt mit dem zweiten Halbleiterchip 112 des unteren Stapels 102 befindet. Bei dem in Fig. 1(C) gezeigten Ausführungsbeispiel sind die elektrischen Kopplungsstellen 110 und 110' an den gleichen Seiten der Anordnung 150 angeordnet. Alternativ können die elektrischen Kopplungsstellen 110 und 110' an gegenüberliegenden Seiten der Anordnung 150 vorgesehen sein, wie es in Fig. 1(A) und 1(B) gezeigt ist.

[0027] Fig. 1(D) zeigt ein anderes Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung. Die Anordnung 160 weist einen modifizierten Stapel 102" auf. Der Stapel 102" weist einen ersten Halbleiterchip 104" und einen zweiten Halbleiterchip 112" auf, die durch ein Überlappen der elektrischen Kopplungsstellen 110" und 118" elektrisch verbunden sind. Der zweite Halbleiterchip 112" weist ferner eine Durchkontaktierung 162 auf, die sich durch den Halbleiterchip 112" hindurch zu der zweiten Oberfläche 116" erstreckt. Der Stapel 102" weist einen dritten Halbleiterchip 164 auf, der eine erste Oberfläche 166 (in Fig. 1(D) eine untere Oberfläche) und eine zweite Oberfläche 168 (in Fig. 1(A) eine obere Oberfläche) aufweist. An der ersten Oberfläche 166 ist eine elektrische Kopplungsstelle 170 vorgesehen. Der dritte Halbleiterchip 164 ist auf den zweiten Halbleiterchip 112" in der "Flip-Chip"-Weise befestigt, d. h. die erste Oberfläche 166, die die elektrische Kopplungsstelle 170 aufweist, ist an der zweiten Oberfläche 116" des zweiten Halbleiterchips 112" befestigt. Die Befestigung ist derart, dass die elektrische Kopplungsstelle 170 des dritten Halbleiterchips 164 sich in einem elektrischen Kontakt mit der Durchkontaktierung 162 des zweiten Halbleiterchips 112" befindet.

[0028] Auf den Stapel 102" ist ein weiterer Stapel 102', der bereits hinsichtlich Fig. 1(C) beschrieben wurde, in einer derartigen Weise befestigt, dass sich der erste Halbleiterchip 104' des oberen Stapels 102' in Kontakt mit dem dritten Halbleiterchip 164 befindet und ferner mit dem ersten Halbleiterchip 104" in dem unteren Stapel 102" zum Definieren der Ausnehmung 132 ausgerichtet ist, in der die elektrische Kopplungsstelle 110" des ersten Halbleiterchips 104" angeordnet ist.

[0029] Fig. 1(E) beschreibt noch ein anderes Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung. Die Anordnung 170 ist ähnlich der in Fig. 1(A) gezeigten Anordnung, außer einer Modifikation des zweiten Halbleiterchips 112 in dem Stapel 102 und der Modifikation der Anordnung des zweiten Halbleiterchips 112 an dem ersten Halbleiterchip 104. In einer ähnlichen Weise wie in Fig. 1(D) ist der zweite Halbleiterchip 112 mit einer Durchkontaktierung 162 versehen, die sich von der elektrischen Kopplungsstelle 118 zu der zweiten Oberfläche 116 (in Fig. 1(E) eine untere Oberfläche) des zweiten Halbleiterchips 112 erstreckt. Anders als in Fig. 1(A) wird keine "Flip-Chip"-Befestigung verwendet, sondern sind die Halbleiterchips 104 und 112 aufeinander in einer derartigen Weise gestapelt, dass die zweite Oberfläche 116 des zweiten Halbleiterchips 112 sich in Kontakt mit der ersten Oberfläche **106** (in **Fig.** 1(E) eine obere Oberfläche) des ersten Halbleiterchips 104 befindet. Der Stapel 102 weist ferner das leitfähige Element 120, beispielsweise einen Leiter, auf, das sich von der ersten Kopplungsstelle 110 aus erstreckt. Das leitfähige Element 120 ist angeordnet, derart, dass auf ein Befestigen des zweiten Halbleiterchips 112 auf dem ersten Halbleiterchip 104 hin die Durchkontaktierung 162 das leitfähige Element 102 kontaktiert, wodurch ein direkter Kontakt zwischen den zwei elektrischen Kopplungsstellen 118 und 110 geliefert wird.

[0030] Fig. 2 zeigt ein anderes Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung. Die Anordnung 175 weist einen ersten Stapel 102 auf, der dem Stapel 102 entspricht, der oben mit Bezug auf Fig. 1(A) beschrieben ist. Ferner ist ein zweiter Stapel 102' vorgesehen, der die gleiche Konfiguration wie der erste Stapel 102 aufweist. Die zwei Stapel 102 und 102' sind aufeinander in einer derartigen Weise gestapelt, dass die jeweiligen

Kopplungsstellen 110 und 110' an gegenüberliegenden Seiten der Anordnung 175 vorgesehen sind. Zusätzlich ist der erste Halbleiterchip 104' an dem zweiten Halbleiterchip 112 befestigt und anders als bei den Ausführungsbeispielen, die mit Bezug auf Fig. 1 beschrieben sind, ist der Halbleiterchip 104' mit dem zweiten Halbleiterchip 112 in dem ersten oder unteren Stapel 102 ausgerichtet. Der obere Stapel 102' ist in einer derartigen Weise befestigt, dass der zweite Halbleiterchip 112' des oberen Stapels 102' mit dem ersten Halbleiterchip 104 in dem unteren Stapel 102 ausgerichtet ist. Ein Abschnitt 130' des zweiten Halbleiterchips 112' erstreckt sich über der elektrischen Kopplungsstelle 110 des ersten Halbleiterchips 104 des unteren Stapels 102, so dass die Ausnehmung 132, die die Kopplungsstelle 110 und den Bonddraht 121 aufnimmt, gebildet ist. Anders als bei den im Hinblick auf Fig. 1 beschriebenen Ausführungsbeispielen ist bei dem im Hinblick auf Fig. 2 beschriebenen Ausführungsbeispiel eine Mehrzahl von weiteren Halbleiterchips 104' und 112' zum Definieren der Ausnehmung 132 an dem oberen Halbleiterchip 112 in dem Stapel 102 befestigt.

**[0031]** Weitere Ausführungsbeispiele, die eine derartige Konfiguration verwenden, werden im Folgenden im Hinblick auf **Fig.** 3, <u>Fig. 9</u>, <u>Fig. 10</u> und <u>Fig. 11</u> beschrieben.

[0032] Fig. 3(A) zeigt ein Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung, bei dem die Anordnung 180 den Stapel 102 aufweist, der den ersten und den zweiten Halbleiterchip 104 und 112 aufweist, wobei die jeweiligen Halbleiterchips eine ähnliche Konfiguration aufweisen, wie es im Hinblick auf Fig. 1(A) bis (C) und Fig. 2 beschrieben ist. Anders als bei den Ausführungsbeispielen, die im Hinblick auf Fig. 1(A) bis 1(C) und Fig. 2 beschrieben sind, wurde jedoch keine "Flip-Chip"-Befestigung des zweiten Halbleiterchips 112 an dem ersten Halbleiterchip 104 zum Stapeln der zwei Halbleiterchips aufeinander verwendet. Wie es aus Fig. 3(A) zu sehen ist, ist anstelle dessen der zweite Halbleiterchip 112 an dem ersten Halbleiterchip 104 mit dem Versatz x in einer derartigen Weise befestigt, dass sich die zweite Oberfläche 116 des zweiten Halbleiterchips 112 (in Fig. 3(A) eine untere Oberfläche) in Kontakt mit der ersten Oberfläche 106 (in Fig. 3(A) eine untere Oberfläche) des ersten Halbleiterchips **104** befindet. Bei dem in Fig. 3(A) gezeigten Ausführungsbeispiel kann ein Bonddraht 120 als das leitfähige Element zum Liefern einer direkten elektrischen Verbindung zwischen der elektrischen Kopplungsstelle 110 des ersten Halbleiterchips 104 und der elektrischen Kopplungsstelle 118 des zweiten Halbleiterchips 112 verwendet werden.

[0033] Auf den oberen Halbleiterchip des Stapels 102, d. h. auf den zweiten Halbleiterchip 112, ist eine Mehrzahl weiterer Halbleiterchips 104' und 112' be-

festigt, wobei die Mehrzahl weiterer Halbleiterchips in der Form eines weiteren Stapels 102' vorgesehen sein kann. Bei dem in Fig. 3(A) gezeigten Ausführungsbeispiel weist der weitere Stapel 102' die gleiche Konfiguration wie der untere Stapel 102 auf. Wie es zu sehen ist, ist der obere Stapel 102' auf den unteren Stapel 102 in einer derartigen Weise befestigt, dass die zweite Oberfläche 108' des ersten Halbleiterchips 104' des oberen Stapels 102' an der ersten Oberfläche 114 (in Fig. 3(A) eine obere Oberfläche) des zweiten Halbleiterchips 112 in dem unteren Stapel 102 befestigt ist. Ferner ist der erste Halbleiterchip 104' an dem zweiten Halbleiterchip 112 in einer derartigen Weise befestigt, dass die elektrische Kopplungsstelle 118 des zweiten Halbleiterchips 112 in dem unteren Stapel 102 freiliegt. Der erste Halbleiterchip 104' des oberen Stapels 102' ist an dem zweiten Halbleiterchip 112 des unteren Stapels 102 mit einem Versatz x' befestigt, der der gleiche wie der Versatz x bei dem ersten Stapel 102 sein kann. Alternativ kann der Versatz x' größer oder kleiner als der Versatz x in dem ersten Stapel 102 sein. Bei dem in Fig. 3(A) gezeigten Ausführungsbeispiel sind der Versatz x und der Versatz x' ausgewählt, um im Wesentlichen gleich zu sein, so dass durch ein Befestigen des oberen Stapels 102 der zweite Halbleiterchip 112' in dem zweiten Stapel im Wesentlichen mit dem zweiten Halbleiterchip 112 in dem ersten Stapel 102 ausgerichtet sein wird. Durch den überlappenden Bereich 130 ist die Ausnehmung 132 definiert, die den Bonddraht 120 und die elektrische Kopplungsstelle 118 des zweiten Halbleiterchips 112 des ersten Stapels aufnimmt. Wie es aus Fig. 3(A) zu sehen ist, sind die Kopplungsstellen 110, 118 und die Kopplungsstellen 110' und 118' an unterschiedlichen Seiten des Stapels 180 angeordnet und können an gegenüberliegenden Seiten desselben vorgesehen

[0034] Fig. 3(B) zeigt ein anderes Ausführungsbeispiel einer Anordnung von Halbleiterchips mit integrierter Schaltung. Die Anordnung 190 weist einen ersten Stapel 102 auf, der den ersten Halbleiterchip 104 und den zweiten Halbleiterchip 112 aufweist. Die Halbleiterchips weisen eine Konfiguration ähnlich den Halbleiterchips auf, die im Hinblick auf Fig. 3(A) beschrieben sind, mit der Ausnahme, dass der zweite Halbleiterchip 112 eine Durchkontaktierung 162 aufweist, die für eine elektrische Verbindung der elektrischen Kopplungsstelle 118 mit der zweiten Oberfläche des zweiten Halbleiterchips 112 sorgt. Wie es zu sehen ist, sind die Halbleiterchips 104 und 112 aufeinander in einer derartigen Weise gestapelt, dass dieselben mit Bezug aufeinander ausgerichtet sind und eine elektrische Verbindung zwischen den Kopplungsstellen 110 und 118 durch die Durchkontaktierung 162 vorgesehen ist. Bei diesem Ausführungsbeispiel ist der Bonddraht 121 zum Liefern einer externen Verbindung mit der elektrischen Kopplungsstelle 118 des zweiten Halbleiterchips 112 in dem Stapel **102** verbunden. Alternativ können die Halbleiterchips **104** und **112** mit einem Versatz angeordnet sein, solange das untere Ende der Durchkontaktierung oder des Durchgangslochs **162** sich in Kontakt mit der Kopplungsstelle **110** an dem ersten Halbleiterchip **104** befindet.

[0035] Die Anordnung 190 weist zwei weitere Stapel 102' und 102" auf, die an dem ersten Stapel 102 befestigt sind. Die Konfiguration der zusätzlichen Stapel ist im Wesentlichen die gleiche wie diese des Stapels 102. Der Stapel 102' ist an dem Stapel 102 in einer derartigen Weise befestigt, dass der erste Halbleiterchip 104' des Stapels 102' auf die erste Oberfläche 114 des zweiten Halbleiterchips 112 des Stapels 102 befestigt ist. Die Befestigung ist derart, dass der erste Stapel **102** und der zweite Stapel **102'** aneinander mit einem Versatz x befestigt sind, wodurch die elektrische Kopplungsstelle 118 des zweiten Halbleiterchips 112 in dem ersten Stapel 102 zumindest teilweise freigelegt wird. Auf ähnliche Weise ist ein weiterer Stapel 102" an dem zweiten Stapel 102' befestigt, erneut mit einem Versatz, wobei die elektrische Kopplungsstelle 118' des zweiten Halbleiterchips 112' in dem zweiten Stapel 102' zumindest teilweise freiliegt. Der Versatz zwischen dem zweiten und dem dritten Stapel 102' und 102" kann der gleiche wie der Versatz x oder von demselben unterschiedlich sein. Das Befestigen des zweiten Stapels 102" in der eben erwähnten Weise bildet die Ausnehmung 132, in der die elektrische Kopplungsstelle 118 des zweiten Halbleiterchips 112 in dem ersten Stapel 102 aufgenommen ist. Bei dem in Fig. 3(B) gezeigten Ausführungsbeispiel sind der erste Stapel 102 und der zweite Stapel 102" miteinander ausgerichtet. Die jeweiligen externen Kopplungsstellen 118 und 118" sind an der gleichen Seite der Anordnung 190 vorgesehen, wohingegen die elektrische Kopplungsstelle 118' des zweiten Stapels 102' an einer unterschiedlichen Seite des Stapels 190 angeordnet ist.

[0036] Beispiele für die obigen Stapel 102, die zumindest den ersten Halbleiterchip und den zweiten Halbleiterchip aufweisen, werden im Folgenden beschrieben, wobei ein derartiger Stapel als eine "Unteranordnung" bzw. Teilanordnung bezeichnet wird, die zum Herstellen der Anordnung von integrierten Schaltungsvorrichtungen gemäß Ausführungsbeispielen verwendet wird. Eine derartige Unteranordnung ist durch ein Anwenden eines ersten Halbleiterchipanbringungsschritts, um den zweiten Halbleiterchip an dem ersten Halbleiterchip bereitzustellen, und eines ersten Halbleiterchipbondschrittes gebildet, um einen Bonddraht zwischen den Kontaktanschlussflächen der zwei Halbleiterchips bereitzustellen. Dies kann einen Durchlauf durch eine Halbleiterchipbonderausrüstung und einen Durchlauf durch eine Drahtbonderausrüstung erfordern. Somit kann das Drahtbonden von Halbleiterchip an Halbleiterchip vorgenommen werden, ohne zusätzliche Schritte zu dem Prozess hinzuzufügen. Ausführungsbeispiele können zwei oder mehr dieser Unteranordnungen zu der Anordnung von integrierten Schaltungen (auch als Mehrchipbauelement bzw. Mehrchipvorrichtung bezeichnet) zusammenfügen, die oben und im Folgenden in Fig. 9 bis Fig. 11 beschrieben ist. Falls N die Anzahl der Halbleiterchips ist, beträgt die Anzahl von benötigten Operationen bei der Herstellung eventuell lediglich (N/4) + 1, wobei eine Operation durch ein Halbleiterchipanbringen und ein Drahtbonden definiert ist. Zusätzlich ist die Drahtbestückung bzw. Drahtpopulation auf der Platinenebene, d. h. die Anzahl von Drahtverbindungen mit den Halbleiterchips der Mehrchipvorrichtung, die von einer einzigen Anschlussfläche ausgehen, auf N/2 Drähte oder Verbindungen reduziert.

[0037] Fig. 4 zeigt eine perspektivische Ansicht eines Stapels von Halbleiterchips (eine Unteranordnung) 200, der einen ersten Halbleiterchip 202, der eine Mehrzahl von ersten Kontaktanschlussflächen 204a bis 204f aufweist, die an einem Rand bzw. einer Peripherie des ersten Halbleiterchips 202 angeordnet sind, und einen zweiten Halbleiterchip 206 aufweist, der eine Mehrzahl von zweiten Kontaktanschlussflächen 208a bis 208e aufweist, die an dem Rand des zweiten Halbleiterchips 206 angeordnet sind. Der zweite Halbleiterchip **206** ist an dem ersten Halbleiterchip 202 mit einem Versatz angeordnet, so dass die ersten Kontaktanschlussflächen 204a bis 204f des ersten Halbleiterchips 202 freiliegen. Eine Mehrzahl von Bonddrähten 214a bis 214e ist zum Verbinden der ersten Kontaktanschlussflächen 204a. 204b, 204c, 204d und 204f mit den zweiten Kontaktanschlussflächen 208a, 208b, 208c, 208d und 208e vorgesehen. Die ersten Kontaktanschlussflächen 204a bis 204e und die zweiten Kontaktanschlussflächen 208a bis 208e können mit einer internen Schaltung im Inneren des jeweiligen Halbleiterchips 204, 206 verbunden sein, während die Kontaktanschlussfläche 204f an dem ersten Halbleiterchip 202 eine Dummy-Anschlussfläche sein kann, die keine Verbindung mit der internen Schaltung des ersten Halbleiterchips 202 aufweist. Die Dummy-Anschlussfläche 204f kann verwendet werden, um ein Signal lediglich zu dem zweiten Halbleiterchip 206 zu liefern, ohne dasselbe an den ersten Halbleiterchip 202 anzulegen. Ein Beispiel eines derartigen Signals kann ein Chipauswahlsignal (CE) sein, wie dasselbe bei Speichervorrichtungen verwendet wird, das vorgesehen ist, um lediglich einen erwünschten Speicherhalbleiterchip für einen Betrieb zu aktivieren, ohne andere Halbleiterchips zu aktivieren.

[0038] Fig. 5(A) zeigt eine seitliche Querschnittsansicht der Unteranordnung von Fig. 4. Wie es zu sehen ist, erstreckt sich ein Ende 210 des zweiten Halbleiterchips 206 über das Ende 212 des ersten Halbleiterchips 202 um eine Strecke x hinaus. Fig. 5(B) zeigt einen Halbleiterchip 202 mit einem Chipanbrin-

gungsfilm 203 an dem unteren Ende des Halbleiterchips 202, der als ein Grundelement zum Bilden der oben beschriebenen Unteranordnung verwendet werden kann. Ein möglicher Ansatz kann darin bestehen, den Halbleiterchipanbringungsfilm 203 auf den gesamten Wafer aufzubringen. Nach einer Vereinzelung der Halbleiterchips weisen alle der einzelnen Halbleiterchips eine Oberfläche auf, an dem das Halbleiterchipanbringungsmaterial aufgebracht ist. Zu dieser Zeit ist es möglich, die erste Halbleiterchipanbringung vorzunehmen. Nach dieser ersten Halbleiterchipanbringung werden zwei Halbleiterchips gestapelt und drahtgebondet, was die Unteranordnung ergibt.

[0039] Fig. 6 zeigt eine perspektivische Ansicht einer anderen Unteranordnung 220. In Fig. 6 sind Elemente, die bereits in Fig. 4 beschrieben wurden, mit den gleichen Bezugszeichen bezeichnet. Verglichen mit der Unteranordnung von Fig. 4 sind die Kontaktanschlussflächen 204 und 208 an unterschiedlichen Teilen des Rands des jeweiligen Halbleiterchips angeordnet. Zusätzlich sind alle Anschlussflächen mit der jeweiligen internen Schaltung verbunden, d. h. es ist keine Dummy-Anschlussfläche vorgesehen.

[0040] Die Halbleiterchips 202 und 206 können die gleichen integrierten Schaltungen aufweisen oder können unterschiedliche integrierte Schaltungen aufweisen. Die integrierte Schaltung kann aus einer Logikschaltung, einer Speicherschaltung und/oder einer Signalverarbeitungsschaltung ausgewählt sein. Die Speicherschaltung kann beispielsweise ein SRAM-Speicher, ein Flash-Speicher, ein DRAM, ein Phasenänderung-RAM (PCRAM; PCRAM = Phase Change RAM), ein RAM (Random Access Memory = Direktzugriffsspeicher), ein ROM (Read-Only Memory = Nur-Lese-Speicher), ein EEPROM (Electronically Erasable Programmable ROM = elektronisch löschbarer programmierbarer ROM) sein. Jede der Kontaktanschlussflächen kann ein elektrisches Signal weiterleiten, z. B. Befehls-, Adress- oder Datensignale.

**[0041]** Der erste Halbleiterchip und der zweite Halbleiterchip können die gleiche Form oder unterschiedliche Formen aufweisen, wobei die Form beispielsweise eine quadratische Form, eine rechteckige Form, eine dreieckige Form, eine polygonale Form, eine kreisförmige Form/oder eine elliptische Form sein kann.

[0042] Es können andere leitfähige Elemente als ein Bonddraht verwendet werden, z. B. ein Leiter 222 (siehe Fig. 7(A)), ein Kabel 224a mit jeweiligen Verbindern 224b, 224c für eine Verbindung mit jeweiligen Leitern, die die Anschlussflächen 204, 208 (siehe Fig. 7(B)) bilden, ein Bandkabel 226a, das Verbinder 226b, 226c aufweist, die eine Mehrzahl von Anschlussflächen 204, 208 überspannen, die jeweilige

Verbinder (siehe **Fig.** 7(D)) aufweisen, eine Drahtwickelverbindung, die einen Draht **228a** aufweist, der um jeweilige Stäbe **228b**, **228c** gewickelt ist, die an den Anschlussflächen **204**, **208** (siehe **Fig.** 7(D)) gebildet sind, oder Kombinationen derselben. Es können auch beschichtete Drähte verwendet werden.

[0043] Fig. 8 zeigt eine perspektivische Ansicht von noch einem anderen Beispiel einer Unteranordnung 230. Elemente, die bereits in Fig. 4 beschrieben wurden, sind mit den gleichen Bezugszeichen bezeichnet. Verglichen mit der Unteranordnung von Fig. 4 weist diese Unteranordnung 203 einen dritten Halbleiterchip 232 auf, der eine Mehrzahl von dritten Kontaktanschlussflächen 234a bis 234f aufweist, die an dem Rand des dritten Halbleiterchips 232 angeordnet sind. Der dritte Halbleiterchip 232 ist an dem zweiten Halbleiterchip 206 angeordnet, derart, dass die zweiten Kontaktanschlussflächen 208a bis 208f des zweiten Halbleiterchips 206 freiliegen. Es ist eine Mehrzahl von Bonddrähten 238a bis 238e zum Verbinden der zweiten Kontaktanschlussflächen 208a bis 208f mit den dritten Kontaktanschlussflächen 234a bis 234f vorgesehen. In Fig. 8 ist keine Dummy-Anschlussfläche vorgesehen.

[0044] Im Folgenden werden weitere Ausführungsbeispiele beschrieben, bei denen die oben beschriebenen Unteranordnungen zu der Anordnung von Halbleiterchips mit integrierter Schaltung (auch als eine Mehrchipvorrichtung bzw. ein Mehrchipbauelement bezeichnet) zusammengefügt sein können.

[0045] Fig. 9 zeigt eine schematische perspektivische Ansicht einer Anordnung von Halbleiterchips mit integrierter Schaltung (Mehrchipvorrichtung) 300 gemäß einem Ausführungsbeispiel. Die Mehrchipvorrichtung 300 weist Unteranordnungen auf, wie es in Fig. 4 detailliert beschrieben ist, aber ohne eine Dummy-Anschlussfläche. Eine erste Unteranordnung I und eine zweite Unteranordnung II sind gestapelt, derart, dass die Kontaktanschlussflächen 208, des zweiten Halbleiterchips 206, der ersten Unteranordnung I freiliegen. Ferner erstreckt sich der zweite Halbleiterchip 206, der zweiten Unteranordnung II über die Kontaktanschlussflächen 208, des zweiten Halbleiterchips 206, der ersten Unteranordnung I, wodurch eine erste Ausnehmung R1 (ähnlich der Ausnehmung 132 in Fig. 3(A)) gebildet ist, der die Kontaktanschlussflächen 208, aufnimmt, die an die Kontaktanschlussflächen 204, gebondet sind. Eine weitere Unteranordnung III ist auf die zweite Unteranordnung II in der gleichen Weise gestapelt, wie die zweite Unteranordnung II auf die erste Unteranordnung I gestapelt ist. Auf ähnliche Weise nimmt eine zweite Ausnehmung R<sub>2</sub> die Kontaktanschlussflächen 208<sub>II</sub> auf, die an die Kontaktanschlussflächen 204<sub>II</sub> gebondet sind.

[0046] Fig. 10 zeigt eine seitliche Querschnittsan-

sicht der Mehrchipvorrichtung 300 von Fig. 9, die an einem Träger 302 angeordnet ist, an dem Trägerkontaktanschlussflächen 310a und 310b vorgesehen sind. Bonddrähte 322a und 322b verbinden die Trägeranschlussfläche 310a mit der Kontaktanschlussfläche 204f, des ersten Halbleiterchips 202, der ersten Unteranordnung I und mit der Kontaktanschlussfläche 204f<sub>III</sub> des ersten Halbleiterchips 202<sub>III</sub> der dritten Unteranordnung III. Ein Bonddraht 324a verbindet die Trägeranschlussfläche 310b mit der Kontaktanschlussfläche 204a, des ersten Halbleiterchips 202, der zweiten Unteranordnung II. Die Unteranordnungen I, II, III sind gestapelt, derart, dass die Kontaktanschlussflächen 208<sub>I</sub>, 208<sub>II</sub>, 208<sub>III</sub> der jeweiligen zweiten Halbleiterchips 206, 206, 206, der Unteranordnungen I, II, III freiliegen, und derart, dass die Ausnehmungen R<sub>1</sub> und R<sub>2</sub> gebildet sind. Die ersten Halbleiterchips 202, und 202, und die zweiten Halbleiterchips 206, und 206, der ersten und der dritten Unteranordnung I und III sind im Wesentlichen miteinander ausgerichtet (siehe die Begrenzungen, die durch Bezugszeichen 350a, 360a, 360a, 350b, 350b<sub>III</sub>, 360b<sub>I</sub> und 360b<sub>III</sub> angegeben sind). Ferner sind die zweiten Halbleiterchips 206, und 206, der ersten und der dritten Unteranordnung I und III im Wesentlichen mit dem zweiten Halbleiterchip 206, der zweiten Unteranordnung II ausgerichtet (siehe die Begrenzungen, die durch Bezugszeichen 360a,  $360a_{II}$ ,  $360a_{III}$  und  $360b_{II}$  angegeben sind). Um die Ausnehmungen R<sub>1</sub>, R<sub>2</sub> zu erhalten, sind die Unteranordnungen gestaffelt gestapelt. Dies kann ferner die Standfläche 370 reduzieren. An der oberen Oberfläche 304 des Trägers 302 kann ein Gehäuse 326 angeordnet sein, das den Stapel, die Mehrzahl von Trägerkontakten 310a und 310b und die Mehrzahl von Bonddrähten 322a bis 322d und 324a bis 324b einschließt, um einen Mehrchipbaustein zu bilden. Das Gehäuse kann aus einer Metall- oder Kunststoffumhüllung gebildet sein, kann ein Harz sein, das die Elemente einkapselt, oder kann ein geformtes Gehäuse sein.

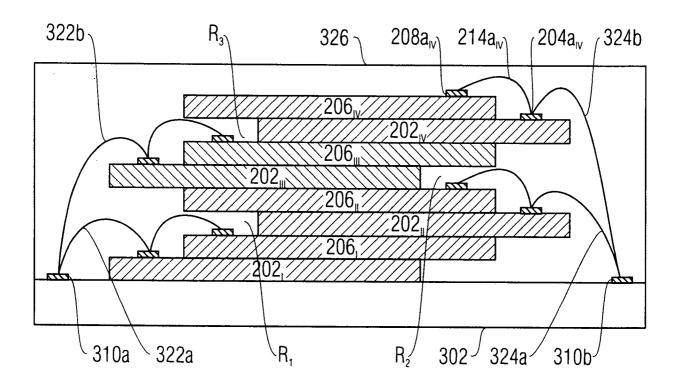

[0047] Fig. 11 zeigt eine seitliche Querschnittsansicht eines Mehrchipbausteins, der eine Mehrchipvorrichtung bzw. ein Mehrchipbauelement ähnlich diesem aufweist, das in Fig. 10 gezeigt ist, mit der Ausnahme, dass eine vierte Unteranordnung IV auf die dritte Unteranordnung III gestapelt ist, deren Kontaktanschlussfläche 204a $_{\rm IV}$  über einen Bonddraht 324b mit der Trägeranschlussfläche 310b verbunden ist. Die vierte Unteranordnung IV ist auf die dritte Unteranordnung III in einer Weise gestapelt, wie die zweite Unteranordnung II auf die erste Unteranordnung I gestapelt ist. Dadurch ist eine dritte Ausnehmung R $_{\rm 3}$  zum Aufnehmen der Kontaktanschlussflächen 204 $_{\rm III}$  gebildet, die an die Kontaktanschlussflächen 204 $_{\rm III}$  gebondet sind.

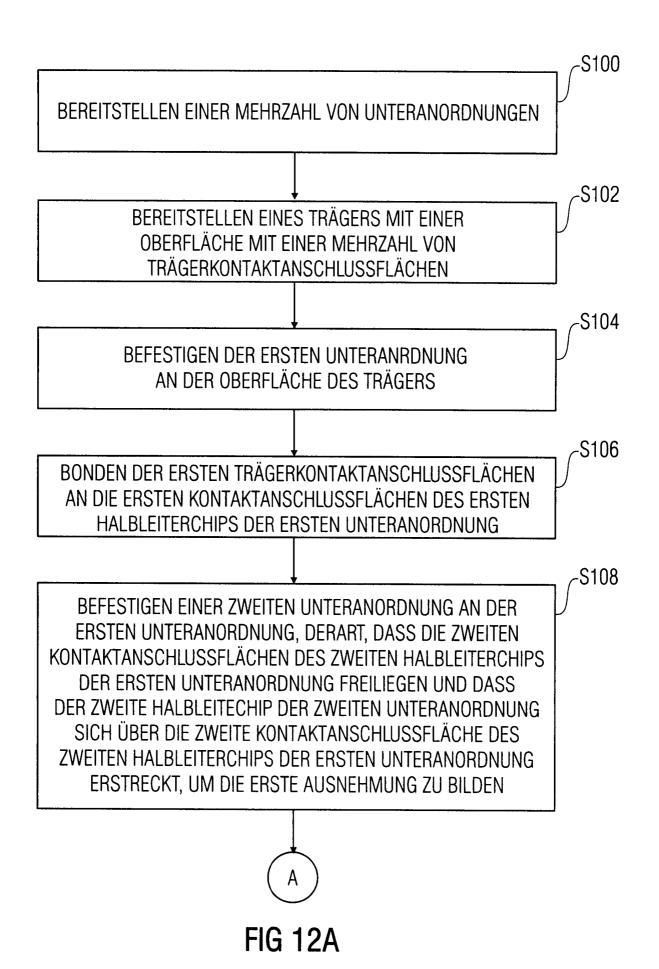

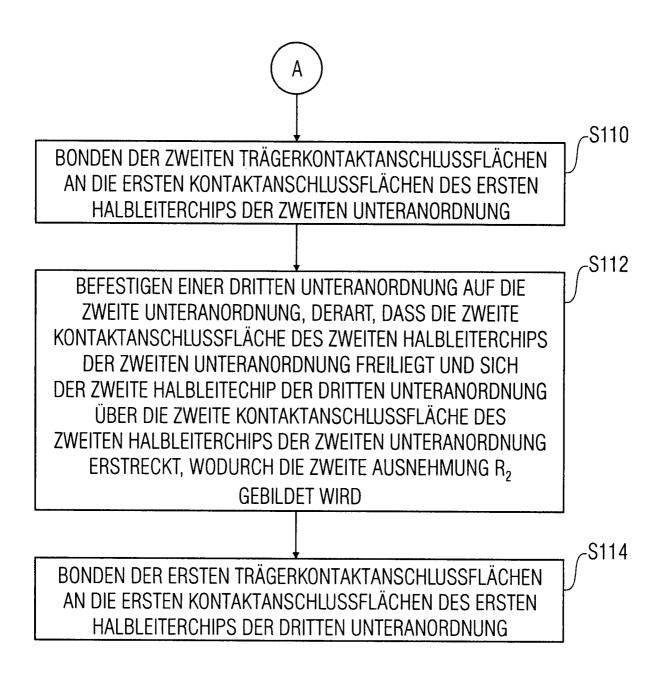

**[0048] Fig.** 12 zeigt ein Flussdiagramm, das ein Ausführungsbeispiel zum Herstellen eines Mehrchip-

bausteins darstellt, wie derselbe in <u>Fig. 9</u> beschrieben ist. Unteranordnungen, die in <u>Fig. 4</u> oder <u>Fig. 6</u> beschrieben sind, können (mit oder ohne Dummy-Anschlussfläche(n)) verwendet werden.

[0049] Bei einem Schritt S100 wird eine Mehrzahl von Unteranordnungen I, II, III bereitgestellt. Bei einem Schritt S102 wird ein Träger 302 mit einer Oberfläche, die die Mehrzahl von Trägerkontaktanschlussflächen 310a, 310b aufweist, bereitgestellt. An der Oberfläche des Trägers 302 wird die erste Unteranordnung I bei einem Schritt S104 befestigt. Dann werden die ersten Trägerkontaktanschlussflächen 310a elektrisch mit den ersten Kontaktanschlussflächen 204, des ersten Halbleiterchips 202, der ersten Unteranordnung I durch Bonddrähte verbunden (siehe Schritt S106). Auf diese Struktur wird eine zweite Unteranordnung II durch ein Befestigen derselben bei einem Schritt S108 auf die erste Unteranordnung I gestapelt. Die zweite Unteranordnung II wird befestigt, derart, dass die zweiten Kontaktanschlussflächen 208, des zweiten Halbleiterchips 206, der ersten Unteranordnung I freiliegen und dass der zweite Halbleiterchip 206, der zweiten Unteranordnung II sich über die zweite Kontaktanschlussfläche 204, des zweiten Halbleiterchips 208, der ersten Unteranordnung I erstreckt, um die Ausnehmung R₁ zu bilden. Die zweiten Trägerkontaktanschlussflächen 310b werden, wie es bei einem Schritt S110 gezeigt ist, elektrisch mit den ersten Kontaktanschlussflächen 204, des ersten Halbleiterchips 202, der zweiten Unteranordnung II durch Bonddrähte verbunden.

[0050] Eine dritte Unteranordnung III wird bei einem Schritt S112 auf die zweite Unteranordnung II gestapelt. Die dritte Unteranordnung III wird befestigt, derart, dass die zweite Kontaktanschlussfläche  $208_{II}$  des zweiten Halbleiterchips  $206_{II}$  der zweiten Unteranordnung II freiliegt und der zweite Halbleiterchip  $206_{III}$  der dritten Unteranordnung III sich über die zweite Kontaktanschlussfläche  $208_{II}$  des zweiten Halbleiterchips  $206_{II}$  der zweiten Unteranordnung II erstreckt, wodurch die zweite Ausnehmung  $R_2$  gebildet wird. Bei einem Schritt S114 werden die ersten Trägerkontaktanschlussflächen 310a und die ersten Kontaktanschlussflächen  $204_{III}$  des ersten Halbleiterchips  $202_{III}$  der dritten Unteranordnung III elektrisch durch Bonddrähte verbunden.

[0051] Während Ausführungsbeispiele der Erfindung beschrieben wurden, bei denen alle Kontaktanschlussflächen elektrisch verbunden waren, ist zu beachten, dass die Erfindung nicht auf eine derartige Anordnung beschränkt ist. Anstelle dessen sind eventuell abhängig von den Halbleiterchips (und den internen Schaltungen derselben) nicht alle Anschlussflächen verbunden. Ferner ist die Anzahl von Halbleiterchips, die bei den beschriebenen Unteranordnungen und Mehrchipvorrichtungen gestapelt sein sollen, nicht auf die gezeigte Anzahl beschränkt.

Es kann vielmehr irgendeine gewünschte Anzahl von Halbleiterchips gestapelt werden, um eine Unteranordnung zu bilden. Gleichermaßen ist die Anzahl von Unteranordnungen, die bei der beschriebenen Mehrchipvorrichtung gestapelt werden sollen, nicht auf die gezeigte Anzahl begrenzt. Vielmehr kann irgendeine erwünschte Anzahl von Unteranordnungen gestapelt werden. Ausführungsbeispiele der Erfindung können Mehrchipvorrichtungen liefern, die 8, 16 oder mehr Halbleiterchips aufweisen.

**[0052]** Ausführungsbeispiele der Erfindung betreffen ein System, das eine oder mehrere der Mehrchipvorrichtungen aufweist. Bei einem derartigen System kann es sich um ein Logiksystem, ein Speichersystem, ein Signalverarbeitungssystem und Kombinationen derselben handeln.

**[0053]** Der Träger in der Mehrchipvorrichtung kann eine Schaltungsplatine, eine gedruckte Schaltungsplatine, ein Halbleitersubstrat oder dergleichen sein.

[0054] Bei der obigen Beschreibung von Ausführungsbeispielen der Anordnungen von Halbleiterchips mit integrierter Schaltung wurde der weitere Halbleiterchip/wurden die weiteren Halbleiterchips als an dem oberen Halbleiterchip in einem Stapel von Halbleiterchips angeordnet beschrieben, der durch den ersten Halbleiterchip und den zweiten Halbleiterchip gebildet ist. Im Allgemeinen kann der weitere Halbleiterchip/können die weiteren Halbleiterchips über dem ersten Halbleiterchip und dem zweiten Halbleiterchip angeordnet sein, wobei sich eine oder mehrere zusätzliche Schichten, z. B. eine oder mehrere Abstandhalterschichten aus einem isolierenden Material zwischen denselben befindet bzw. befinden. Ferner wurden Ausführungsbeispiele beschrieben, bei denen ein Halbleiterchip an einem Träger befestigt war. Im Allgemeinen kann der Halbleiterchip über dem Träger mit einer oder mehreren zusätzlichen Schichten, z. B. einer oder mehreren Abstandhalterschichten aus einem isolierenden Material zwischen dem Träger und dem Halbleiterchip befestigt sein.

#### Patentansprüche

1. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) von Halbleiterchips mit integrierter Schaltung, die folgende Merkmale aufweist: einen ersten Halbleiterchip (104; 202), der eine erste elektrische Kopplungsstelle (110; 204) aufweist, und einen zweiten Halbleiterchip (112; 206), der eine zweite elektrische Kopplungsstelle (118; 208) aufweist, wobei der zweite Halbleiterchip (112; 206) auf den ersten Halbleiterchip (104; 202) gestapelt ist, derart, dass die erste elektrische Kopplungsstelle (110; 204) zumindest teilweise freiliegt, wobei die erste elektrische Kopplungsstelle (110; 204) und die zweite elektrische Kopplungsstelle (118; 208) direkt elektrisch verbunden sind; und

einen dritten Halbleiterchip (164; 232), der über dem ersten Halbleiterchip (104; 202) und dem zweiten Halbleiterchip (112; 206) angeordnet ist, derart, dass eine Ausnehmung (132;  $R_1$ ,  $R_2$ ,  $R_3$ ) gebildet ist, wobei eine der ersten elektrischen Kopplungsstellen (110; 204) in der Ausnehmung (132;  $R_1$ ,  $R_2$ ,  $R_3$ ) angeordnet ist

- 2. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 1, die einen Stapel (102) aufweist, der den ersten Halbleiterchip (104; 202) und den zweiten Halbleiterchip (112; 206) aufweist, wobei der dritte Halbleiterchip (164; 232) auf einem oberen Halbleiterchip in dem Stapel (102) angeordnet ist, derart, dass die Ausnehmung (132;  $R_1$ ,  $R_2$ ,  $R_3$ ) gebildet ist, und wobei die erste elektrische Kopplungsstelle (110; 204) in der Ausnehmung (132;  $R_1$ ,  $R_2$ ,  $R_3$ ) angeordnet ist.

- 3. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 1 oder 2, die einen Stapel (102), der den ersten Halbleiterchip (104; 202) und den zweiten Halbleiterchip (112; 206) aufweist, und eine Mehrzahl von weiteren Halbleiterchip des Stapels (102) angeordnet sind, derart, dass die Ausnehmung (132; R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub>) gebildet ist.

- 4. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß einem der Ansprüche 1 bis 3, bei der der erste Halbleiterchip (104; 202) eine erste Oberfläche (106) und eine zweite Oberfläche (108) aufweist, wobei die erste elektrische Kopplungsstelle (110; 204) an der ersten Oberfläche (106) des ersten Halbleiterchips (104; 202) angeordnet ist, wobei der zweite Halbleiterchip (112; 206) eine erste Oberfläche (114) und eine zweite Oberfläche (116) aufweist, wobei die zweite elektrische Kopplungsstelle (118; 208) an der ersten Oberfläche (114) des zweiten Halbleiterchips (112; 206) angeordnet ist, und wobei der zweite Halbleiterchip (112; 206) auf den ersten Halbleiterchip (104; 202) gestapelt ist, derart, dass die erste Oberfläche (106) des ersten Halbleiterchips (104; 202) und die erste Oberfläche (114) des zweiten Halbleiterchips (112; 206) einander zugewandt sind.

- 5. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 4, die ein leitfähiges Element (120) aufweist, das die erste elektrische Kopplungsstelle (110; 204) und die zweite elektrische Kopplungsstelle (118; 208) direkt verbindet, wobei das leitfähige Element (120) einen Leiter aufweist, der sich von der ersten elektrischen Kopplungsstelle (110; 204) aus erstreckt.

- 6. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 4 oder 5, bei der der zweite Halbleiterchip (112; 206) auf den ersten Halbleiterchip (104; 202) gestapelt ist, derart,

dass die erste elektrische Kopplungsstelle (110; 204) und die zweite elektrische Kopplungsstelle (118; 208) teilweise überlappen.

7. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß einem der Ansprüche 2 bis 6, bei der der dritte Halbleiterchip (164; 232) eine dritte elektrische Kopplungsstelle (170; 234) aufweist, und wobei die Anordnung ferner folgendes Merkmal aufweist:

einen vierten Halbleiterchip, der elektrisch mit dem dritten Halbleiterchip (164; 232) verbunden ist und eine vierte elektrische Kopplungsstelle aufweist, wobei der vierte Halbleiterchip auf den dritten Halbleiterchip (164; 232) gestapelt ist, derart, dass die dritte elektrische Kopplungsstelle (170; 234) oder die vierte elektrische Kopplungsstelle zumindest teilweise freiliegt.

- 8. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 7, bei der die erste (110; 204) und die zweite (118; 208) elektrische Kopplungsstelle sowie die dritte (170; 234) und die vierte elektrische Kopplungsstelle an der gleichen Seite oder an unterschiedlichen Seiten der Anordnung angeordnet sind.

- 9. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß einem der Ansprüche 2 bis 8, bei der der Stapel (102) zumindest einen weiteren Halbleiterchip aufweist.

- 10. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß einem der Ansprüche 1 bis 9, die eine Mehrzahl von ersten elektrischen Kopplungsstellen und eine Mehrzahl von zweiten elektrischen Kopplungsstellen aufweist.

- 11. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß einem der Ansprüche 1 bis 10, bei der der erste Halbleiterchip (104; 202) eine erste Oberfläche (106) und eine zweite Oberfläche (108) aufweist, wobei die erste elektrische Kopplungsstelle (110; 204) an der ersten Oberfläche (106) des ersten Halbleiterchips (104; 202) angeordnet ist, wobei der zweite Halbleiterchip (112; 206) eine erste Oberfläche (114) und eine zweite Oberfläche (116) aufweist, wobei die zweite elektrische Kopplungsstelle (118; 208) an der ersten Oberfläche (114) des zweiten Halbleiterchips (112; 206) angeordnet ist, und wobei der zweite Halbleiterchip (112; 206) auf den ersten Halbleiterchip (104; 202) gestapelt ist, derart, dass die erste Oberfläche (106) des ersten Halbleiterchips (104; 202) und die zweite Oberfläche (116) des zweiten Halbleiterchips (112; **206**) einander zugewandt sind.

- 12. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 11, die ein leitfähiges Element (120) aufweist, das die erste elek-

trische Kopplungsstelle (110; 204) und die zweite elektrische Kopplungsstelle (118; 208) direkt verbindet, wobei das leitfähige Element (120) aus der Gruppe ausgewählt ist, die einen Bonddraht, einen Leiter, ein Bandkabel, ein Kabel, das Verbinder aufweist, eine Drahtwickelverbindung und ein Durchgangsloch, das sich durch einen Halbleiterchip hindurch erstreckt, aufweist.

13. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß einem der Ansprüche 3 bis 12, bei der die Mehrzahl von weiteren Halbleiterchips folgende Merkmale aufweist:

einen dritten Halbleiterchip (164; 232), der an dem oberen Halbleiterchip in dem Stapel (102) angeordnet ist und eine dritte elektrische Kopplungsstelle (170; 234) aufweist; und

einen vierten Halbleiterchip, der elektrisch mit dem dritten Halbleiterchip (164; 232) verbunden ist und eine vierte elektrische Kopplungsstelle aufweist, wobei der vierte Halbleiterchip auf den dritten Halbleiterchip (164; 232) gestapelt ist, derart, dass die dritte elektrische Kopplungsstelle (170; 234) oder die vierte elektrische Kopplungsstelle zumindest teilweise freiliegt.

wobei die erste (110; 204) und die zweite (118; 208) elektrische Kopplungsstelle sowie die dritte (170; 234) und die vierte elektrische Kopplungsstelle an unterschiedlichen Seiten der Anordnung angeordnet sind.

14. Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; 300) gemäß Anspruch 13, bei der die Mehrzahl von weiteren Halbleiterchips ferner folgende Merkmale aufweist:

einen fünften Halbleiterchip, der an dem vierten Halbleiterchip angeordnet ist und eine fünfte elektrische Kopplungsstelle aufweist; und

einen sechsten Halbleiterchip, der elektrisch mit dem fünften Halbleiterchip verbunden ist und eine sechste elektrische Kopplungsstelle aufweist, wobei der sechste Halbleiterchip auf den fünften Halbleiterchip gestapelt ist, derart, dass die fünfte elektrische Kopplungsstelle oder die sechste elektrische Kopplungsstelle zumindest teilweise freiliegt,

wobei der fünfte Halbleiterchip und der sechste Halbleiterchip gestapelt sind, derart, dass eine weitere Ausnehmung gebildet ist, in der die dritte elektrische Kopplungsstelle (170; 234) oder die vierte elektrische Kopplungsstelle angeordnet ist, und

wobei die erste (110; 204) und die zweite (118; 208) elektrische Kopplungsstelle sowie die dritte (170; 234) und die vierte elektrische Kopplungsstelle an unterschiedlichen Seiten der Anordnung angeordnet sind, und wobei die erste (110; 204) und die zweite (118; 208) elektrische Kopplungsstelle sowie die fünfte und die sechste elektrische Kopplungsstelle an der gleichen Seite der Anordnung angeordnet sind.

15. Anordnung (100; 150; 160; 170; 175; 180;

**190**; **200**; **220**; **230**; **300**) gemäß einem der Ansprüche 3 bis 14, bei der der Stapel (**102**) zumindest einen weiteren Halbleiterchip aufweist.

16. Anordnung von Halbleiterchips mit integrierter Schaltung, die folgende Merkmale aufweist: einen Träger, der eine erste Mehrzahl von Trägerkopplungsstellen und eine zweite Mehrzahl von Trägerkopplungsstellen aufweist;

einen ersten Halbleiterchip, der eine erste Oberfläche, eine zweite Oberfläche und eine Mehrzahl von elektrischen Kopplungsstellen aufweist, die an dem Rand der ersten Oberfläche angeordnet sind, wobei der erste Halbleiterchip über dem Träger angeordnet ist:

eine erste Mehrzahl von Bonddrähten, die die erste Mehrzahl von elektrischen Kopplungsstellen mit der ersten Mehrzahl von Trägerkopplungsstellen direkt verbindet:

einen zweiten Halbleiterchip, der eine erste Oberfläche, eine zweite Oberfläche und eine zweite Mehrzahl von elektrischen Kopplungsstellen aufweist, die an dem Rand der ersten Oberfläche angeordnet sind, wobei der zweite Halbleiterchip auf den ersten Halbleiterchip gestapelt ist, derart, dass die Mehrzahl von ersten elektrischen Kopplungsstellen freiliegt;

eine zweite Mehrzahl von Bonddrähten, die die erste Mehrzahl von elektrischen Kopplungsstellen mit der zweiten Mehrzahl von elektrischen Kopplungsstellen direkt verbindet;

einen dritten Halbleiterchip, der eine erste Oberfläche, eine zweite Oberfläche und eine dritte Mehrzahl von elektrischen Kopplungsstellen aufweist, die an dem Rand der ersten Oberfläche angeordnet sind, wobei der dritte Halbleiterchip über dem zweiten Halbleiterchip angeordnet ist;

eine dritte Mehrzahl von Bonddrähten, die die dritte Mehrzahl von elektrischen Kopplungsstellen mit der zweiten Mehrzahl von Trägerkopplungsstellen direkt verbindet:

einen vierten Halbleiterchip, der eine erste Oberfläche, eine zweite Oberfläche und eine vierte Mehrzahl von elektrischen Kopplungsstellen aufweist, die an dem Rand der ersten Oberfläche angeordnet sind, wobei der vierte Halbleiterchip auf den dritten Halbleiterchip gestapelt ist, derart, dass die Mehrzahl von dritten elektrischen Kopplungsstellen freiliegt; und eine vierte Mehrzahl von Bonddrähten, die die dritte Mehrzahl von elektrischen Kopplungsstellen mit der vierten Mehrzahl von elektrischen Kopplungsstellen direkt verbindet,

wobei der dritte Halbleiterchip und der vierte Halbleiterchip angeordnet sind, derart, dass eine Ausnehmung gebildet ist, in der die Mehrzahl von zweiten elektrischen Kopplungsstellen angeordnet ist.

17. Vorrichtung, die folgende Merkmale aufweist: einen ersten Halbleiterchip (104; 202) mit integrierter Schaltung, der eine erste Einrichtung (110; 204) zum elektrischen Koppeln der integrierten Schaltung des

ersten Halbleiterchips (104; 202) aufweist, und einen zweiten Halbleiterchip (112; 206), der eine zweite Einrichtung (118; 208) zum elektrischen Koppeln der integrierten Schaltung des zweiten Halbleiterchips (112; 206) aufweist, wobei der zweite Halbleiterchip (112; 206) mit integrierter Schaltung auf den ersten Halbleiterchip (104; 202) mit integrierter Schaltung gestapelt ist, derart, dass eine der Einrichtungen zum elektrischen Koppeln zumindest teilweise freiliegt, wobei die erste Einrichtung (110; 204) zum elektrischen Koppeln und die zweite Einrichtung (118; 208) zum elektrischen Koppeln direkt elektrisch verbunden sind; und

einen oder mehrere weitere Halbleiterchips mit integrierter Schaltung, die über dem ersten Halbleiterchip (104; 202) und dem zweiten Halbleiterchip (112; 206) angeordnet sind, derart, dass eine Ausnehmung (132;  $R_1$ ,  $R_2$ ,  $R_3$ ) gebildet ist, wobei eine der Einrichtungen zum elektrischen Koppeln in der Ausnehmung (132;  $R_1$ ,  $R_2$ ,  $R_3$ ) angeordnet ist.

18. Verfahren zum Fertigen einer Anordnung (100; 150; 160; 170; 175; 180; 190; 200; 220; 230; **300**) von Halbleiterchips mit integrierter Schaltung, die eine Mehrzahl von Halbleiterchips mit integrierter Schaltung aufweist, wobei die Mehrzahl von Halbleiterchips mit integrierter Schaltung einen ersten Halbleiterchip (104; 202), der eine erste elektrische Kopplungsstelle (110; 204) aufweist, und einen zweiten Halbleiterchip (112; 206) aufweist, der eine zweite elektrische Kopplungsstelle (118; 208) aufweist, wobei der zweite Halbleiterchip (112; 206) auf den ersten Halbleiterchip (104; 202) gestapelt ist, derart, dass die erste elektrische Kopplungsstelle (110; 204) zumindest teilweise freiliegt, wobei die erste elektrische Kopplungsstelle (110; 204) und die zweite elektrische Kopplungsstelle (118; 208) direkt elektrisch verbunden sind, wobei das Verfahren folgende Schritte aufweist:

Befestigen der Mehrzahl von Halbleiterchips mit integrierter Schaltung an einem Träger;

elektrisches Verbinden einer der elektrischen Kopplungsstellen der Mehrzahl von Halbleiterchips mit integrierter Schaltung mit einer ersten Trägerkopplungsstelle;

Befestigen eines weiteren Halbleiterchips mit integrierter Schaltung an der Mehrzahl von Halbleiterchips mit integrierter Schaltung, derart, dass eine Ausnehmung ( $\mathbf{132}$ ;  $R_1$ ,  $R_2$ ,  $R_3$ ) gebildet ist, in der eine der elektrischen Kopplungsstellen der Mehrzahl von Halbleiterchips mit integrierter Schaltung angeordnet ist; und

elektrisches Verbinden der elektrischen Kopplungsstellen des weiteren Halbleiterchips mit integrierter Schaltung mit einer zweiten Trägerkopplungsstelle.

19. Verfahren gemäß Anspruch 18, bei der die Mehrzahl von Halbleiterchips mit integrierter Schaltung vor dem Befestigen derselben als ein Stapel gefertigt wird, wobei das Verfahren folgende Schritte

## DE 10 2007 037 798 A1 2009.02.26

## aufweist:

Befestigen eines ersten Halbleiterchips (104; 202), der eine erste elektrische Kopplungsstelle (110; 204) aufweist, an einem zweiten Halbleiterchip (112; 206), der eine zweite elektrische Kopplungsstelle (118; 208) aufweist, derart, dass eine der elektrischen Kopplungsstellen zumindest teilweise freiliegt; und elektrisches Verbinden der ersten elektrischen Kopplungsstelle (110; 204) und der zweiten elektrischen Kopplungsstelle (118; 208).

Es folgen 11 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG 1E

FIG 8

FIG 9

**FIG 11**

**FIG 12B**