(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-293596

(P2005-293596A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.CI.<sup>7</sup>

G06F 12/06

G06F 13/36

F 1

G06F 12/06

G06F 13/36

550C

310D

テーマコード(参考)

5B060

5B061

審査請求 未請求 請求項の数 17 O L (全 14 頁)

(21) 出願番号 特願2005-106228 (P2005-106228)

(22) 出願日 平成17年4月1日 (2005.4.1)

(31) 優先権主張番号 10/815961

(32) 優先日 平成16年4月2日 (2004.4.2)

(33) 優先権主張国 米国(US)

(71) 出願人 594154428

エイアールエム リミテッド

イギリス国 シービー1 9エヌジェイ

ケンブリッジ、チェリー ヒントン、フル

バーン ロード 110

(74) 代理人 100066692

弁理士 浅村皓

(74) 代理人 100072040

弁理士 浅村肇

(74) 代理人 100094673

弁理士 林鉢三

(74) 代理人 100091339

弁理士 清水邦明

(54) 【発明の名称】データ要求のアービトレーション

## (57) 【要約】

【課題】データ要求のアービトレーションを提供すること。

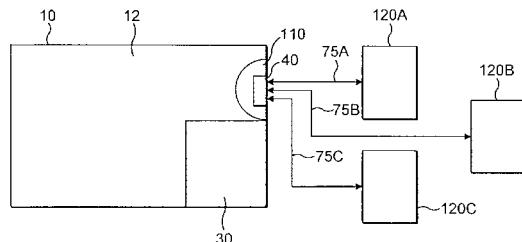

【解決手段】データ・プロセッサ・コア10は、外部データ・ソースと、メモリ120とメモリ・アクセス・インターフェイス部分30と、データ処理部分12と、該バスが該コア10と該メモリ120との間にデータ通信を提供する、該メモリ120が部分120A、120Bを含み、該バス75A、75Bの夫々が該部分120A、120Bの夫々にデータ・アクセスを提供するポート40と、該ポート40に関連するアービトレーション・ロジック110とを含む。該ロジックが、該インターフェイスから受信された該メモリの一部にあるデータのアクセスを要求するアクセス要求を、該メモリのバスのうちの一方に経路設定し、該データ処理部分から受信された該メモリの別の一部にあるデータのアクセスを要求する別のアクセス要求を、該バスのもう一方に経路設定し、該アクセス要求の経路設定が同じクロック・サイクル中に実行される。

【選択図】図5

**【特許請求の範囲】****【請求項 1】**

外部データ・ソースとデータ・プロセッサ・コアに関連付けられている少なくとも1つのメモリとの間でデータ転送操作を実行するように動作可能なメモリ・アクセス・インターフェイス部分と、

データ処理操作を実行するように動作可能なデータ処理部分と、

前記プロセッサ・コアから少なくとも2つのバスにデータを転送するように動作可能な読み取り／書き込みポートであって、前記少なくとも2つのバスが前記プロセッサ・コアと前記少なくとも1つのメモリとの間にデータ通信を提供するように動作可能であり、前記少なくとも1つのメモリが少なくとも2つの部分を含み、前記少なくとも2つのバスのそれぞれが前記少なくとも2つの部分のそれぞれにデータ・アクセスを提供するように動作可能である読み取り／書き込みポートと、

前記読み取り／書き込みポートに関連付けられているアービトレイション・ロジックとを含み、前記アービトレイション・ロジックが、前記メモリ・アクセス・インターフェイスから受信された前記少なくとも1つのメモリの一部にあるデータのアクセスを要求するデータ・アクセス要求を、前記少なくとも1つのメモリの前記一部にアクセスを提供する前記少なくとも2つのバスのうちの一方に経路設定し、前記データ処理部分から受信された前記少なくとも1つのメモリの別の一部にあるデータのアクセスを要求する別のデータ・アクセス要求を、前記少なくとも1つのメモリの前記別の一部にアクセスを提供する前記少なくとも2つのバスのうちのもう一方に経路設定するように動作可能であり、前記データ・アクセス要求の前記経路設定が同じクロック・サイクル中に実行される

データ・プロセッサ・コア。

**【請求項 2】**

前記アービトレイション・ロジックが、前記データ・アクセス要求に関連付けられている前記少なくとも1つのメモリ内のアドレス位置に基づいて前記データ・アクセス要求を経路設定する前記少なくとも2つのバスのうちの一方を選択するように動作可能である請求項1に記載のデータ・プロセッサ・コア。

**【請求項 3】**

前記メモリの前記少なくとも2つの部分が、命令を格納するように動作可能である命令部分、及びデータ項目を格納するように動作可能である少なくとも1つのデータ部分を含み、前記アービトレイション・ロジックは、転送すべきデータが命令であるとき、前記命令部分へのアクセスを提供する前記少なくとも2つのバスのうちの第1のものに前記アクセス要求を経路設定し、転送すべきデータがデータ項目であるとき、前記少なくとも1つのデータ部分へのアクセスを提供する前記少なくとも2つのバスのうちの第2のものに前記データ・アクセス要求を経路設定するように動作可能である請求項2に記載のデータ・プロセッサ・コア。

**【請求項 4】**

前記少なくとも1つのデータ部分が、偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分を含み、前記読み取り／書き込みポートが、前記命令部分へのアクセスを提供する第1のバス、前記奇数データ部分へのアクセスを提供する第2のバス、及び前記偶数データ部分へのアクセスを提供する第3のバスの3つのバスを介して前記プロセッサ・コアと前記少なくとも1つのメモリとの間にデータを転送するように動作可能であり、前記アービトレイション・ロジックが、転送すべきデータが命令であるときは前記第1のバスに、転送すべきデータが奇数アドレスに関連付けられているデータ項目であるときは前記第2のバスに、転送すべきデータが偶数アドレスに関連付けられているデータ項目であるときは前記第3のバスにデータ・アクセス要求を経路設定するように動作可能である請求項3に記載のデータ・プロセッサ・コア。

**【請求項 5】**

前記アービトレイション・ロジックが、前記少なくとも1つのメモリの一部にあるデータ

10

20

30

40

50

タへのアクセスを要求する、前記メモリ・アクセス・インターフェイス部分からのデータ・アクセス要求、及び前記データ処理部分からのデータ・アクセス要求の両方のデータ・アクセス要求の受信に応答して、前記処理部分からの前記要求を前記少なくとも2つのバスのうちの前記一方に経路設定する前に、前記メモリ・アクセス・インターフェイス部分からの前記データ・アクセス要求を、前記少なくとも1つのメモリの前記一部にデータ・アクセスを提供する前記少なくとも2つのバスのうちの前記一方に経路設定するように動作可能である請求項1に記載のデータ・プロセッサ・コア。

#### 【請求項6】

前記アービトレイション・ロジックが前記少なくとも1つのメモリの少なくとも1つのビジー部分から待機要求を検出するように動作可能であり、前記アービトレイション・ロジックが、前記待機要求が検出されなくなるまで、任意のデータ・アクセス要求を前記ビジー部分に経路設定しないように動作可能である請求項1に記載のデータ・プロセッサ・コア。

#### 【請求項7】

請求項1によるデータ・プロセッサ・コアと、

少なくとも2つの部分に分割される少なくとも1つのメモリと、

前記少なくとも1つのメモリの前記少なくとも2つの部分のそれぞれの部分へのデータ・アクセスをそれぞれ可能にする少なくとも2つのバスと

を含むデータ処理装置。

#### 【請求項8】

前記少なくとも1つのメモリが、命令を格納するように動作可能な命令部分、並びに偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分の3つの部分に分割され、前記データ処理装置が3つのバスを含み、前記読み取り／書き込みポートが前記3つのバスを介して前記プロセッサ・コアと前記少なくとも1つのメモリとの間でデータを転送するように動作可能であり、第1のバスが前記命令部分へのアクセスを提供し、第2のバスが前記奇数データ部分へのアクセスを提供し、第3のバスが前記偶数部分へのアクセスを提供する請求項7に記載のデータ処理装置。

#### 【請求項9】

前記少なくとも1つのメモリが密結合メモリである請求項7に記載のデータ処理装置。

#### 【請求項10】

外部データ・ソースとデータ・プロセッサ・コアに関連付けられている少なくとも1つのメモリとの間にデータを転送する方法であって、前記データ・プロセッサ・コアが、前記外部データ・ソースと前記データ・プロセッサ・コアに関連付けられている前記少なくとも1つのメモリとの間のデータ転送操作を実行するように動作可能であるメモリ・アクセス・インターフェイス部分、及びデータ処理操作を実行するように動作可能であるデータ処理部分を含み、前記方法が

前記メモリ・アクセス・インターフェイス部分から受信された前記少なくとも1つのメモリの一部にあるデータのアクセスを要求するデータ・アクセス要求、及び前記データ処理部分から受信された前記少なくとも1つのメモリの別の部分にあるデータへのアクセスを要求するデータ・アクセス要求に応答して、前記メモリ・アクセス・インターフェイス部分から受信された前記データ・アクセス要求を少なくとも2つのバスのうちの一方に経路設定するステップであって、前記少なくとも2つのバスのうちの前記一方が前記少なくとも1つのメモリの前記一部へのアクセスを提供するステップと、前記データ処理部分から受信された前記データ・アクセス要求を前記少なくとも2つのバスのうちのもう一方のバスに経路設定するステップであって、前記別のバスが前記少なくとも1つのメモリの前記別の部分へのアクセスを提供するステップとを含み、前記データ・アクセス要求の前記経路設定が同じクロック・サイクル中に実行される方法。

#### 【請求項11】

10

20

30

40

50

データ・アクセス要求をそれぞれのデータ・バスに経路設定する前記ステップが、前記データ・アクセス要求に関連付けられている前記少なくとも1つのメモリ内のアドレス位置に基づいて行われる請求項10に記載の方法。

【請求項12】

前記メモリの前記少なくとも2つの部分が、命令を格納するように動作可能である命令部分、及びデータ項目を格納するように動作可能である少なくとも1つのデータ部分を含み、前記データ・アクセス要求を経路設定する前記ステップが、転送すべきデータが命令であるとき、前記命令部分へのアクセスを提供する前記少なくとも2つのバスのうちの一方にデータ・アクセス要求を経路設定し、転送すべきデータがデータ項目であるとき、前記少なくとも1つのデータ部分へのアクセスを提供する前記少なくとも2つのバスのうちのもう一方に前記データ・アクセス要求を経路設定するように動作可能である請求項10に記載の方法。

10

【請求項13】

前記少なくとも1つのデータ部分が、偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分を含み、前記経路設定するステップが、前記命令部分へのアクセスを提供する第1のバス、前記奇数データ部分へのアクセスを提供する第2のバス、及び前記偶数データ部分へのアクセスを提供する第3のバスの3つのバスのうちの1つにデータ・アクセスを経路設定するように動作可能であり、前記経路設定するステップが、転送すべきデータが命令であるときは前記第1のバスに、転送すべきデータが奇数アドレスに関連付けられているデータ項目であるときは前記第2のバスに、転送すべきデータが偶数アドレスに関連付けられているデータ項目であるときは前記第3のバスにデータ・アクセス要求を経路設定するように動作可能である請求項12に記載の方法。

20

【請求項14】

前記経路設定するステップが、前記少なくとも2つのバスのうちの一方によってアクセスされる前記少なくとも1つのメモリの一部にあるデータへのアクセスを要求する、前記メモリ・アクセス・インターフェイス部分からのデータ・アクセス要求、及び前記データ処理部分からのデータ・アクセス要求の両方のデータ・アクセス要求の受信に応答して、前記処理部分からの前記要求を前記少なくとも2つのバスのうちの前記一方に経路設定する前に、前記メモリ・アクセス・インターフェイス部分からの前記データ・アクセス要求を前記少なくとも2つのバスのうちの前記一方に経路設定する請求項10に記載の方法。

30

【請求項15】

前記経路設定するステップが、前記少なくとも1つのメモリの少なくとも1つのビジー部分から待機要求を検出し、前記待機要求の検出に応答して、前記待機要求が検出されなくなるまで、前記ビジー部分にデータ・アクセス要求を経路設定しない請求項10に記載の方法。

40

【請求項16】

前記少なくとも1つのメモリが、命令を格納するように動作可能な命令部分、並びに偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分の3つの部分に分割され、前記経路設定するステップが、前記データ・アクセス要求に関連付けられている前記データのアドレスに基づいて、受信したデータ・アクセス要求を3つのバスのうちの1つに経路設定し、第1のバスが前記命令部分へのアクセスを提供し、第2のバスが前記奇数データ部分へのアクセスを提供し、第3のバスが前記偶数データ部分へのアクセスを提供する請求項10に記載の方法。

50

【請求項17】

請求項10から16までのいずれか一項による方法の諸ステップを実行するようにデータ・プロセッサを制御するよう動作可能であるアービトレイション・ロジック。

【発明の詳細な説明】

【技術分野】

50

**【 0 0 0 1 】**

本発明はデータ処理システムの分野に関する。より詳細には、本発明はデータ転送要求の分野に関する。

**【 背景技術 】****【 0 0 0 2 】**

データ処理システムでは、あるメモリから別のメモリに、又は外部データ・ソースとデータ・プロセッサに関連付けられているメモリとの間でデータを転送することがしばしば必要である。例えば、コードを、起動時にフラッシュなどの低速メモリに格納し、使用前にプロセッサに関連付けられているより速い命令メモリ(*instruction memory*)に転送することが望ましい場合がある。一般にこうした転送は、データが読み取られるフラッシュ・メモリ内の位置、及びデータ項目が書き込まれるコア内のレジスタを指定するロード命令、並びにコア内のレジスタ、及びより速い命令メモリ内の宛先位置を指定するストア命令により、データ・プロセッサ・コアを介して行われる。こうした転送は、かなり遅く、各データ項目にいくつかの命令がかかるので、命令の点で高くつく。

10

**【 発明の開示 】****【 発明が解決しようとする課題 】****【 0 0 0 3 】**

データ転送が相対的に遅く命令の点で高くつく問題は、データ・ロギングなど、常にプロセッサを介して大量のデータをメモリに転送することが必要となり得るアプリケーションにおいて特に重大となる場合がある。

20

**【 課題を解決するための手段 】****【 0 0 0 4 】**

一態様から見ると、本発明は、外部データ・ソースとデータ・プロセッサ・コアに関連付けられている少なくとも1つのメモリとの間でデータ転送操作を実行するように動作可能なメモリ・アクセス・インターフェイス部分と、データ処理操作を実行するように動作可能なデータ処理部分と、前記プロセッサ・コアから少なくとも2つのバスにデータを転送するように動作可能な読み取り／書き込みポートであって、前記少なくとも2つのバスが前記プロセッサ・コアと前記少なくとも1つのメモリとの間にデータ通信を提供するように動作可能であり、前記少なくとも1つのメモリが少なくとも2つの部分を含み、前記少なくとも2つのバスのそれぞれが前記少なくとも2つの部分のそれぞれにデータ・アクセスを提供するように動作可能である読み取り／書き込みポートと、前記読み取り／書き込みポートに関連付けられているアービトリレーション・ロジックとを含み、前記アービトリレーション・ロジックが、前記メモリ・アクセス・インターフェイスから受信された前記少なくとも1つのメモリの一部にあるデータのアクセスを要求するデータ・アクセス要求を、前記少なくとも1つのメモリの前記一部にアクセスを提供する前記少なくとも2つのバスのうちの一方に経路設定し、前記データ処理部分から受信された前記少なくとも1つのメモリの別の一部にあるデータのアクセスを要求する別のデータ・アクセス要求を、前記少なくとも1つのメモリの前記別の一部にアクセスを提供する前記少なくとも2つのバスのうちのもう一方に経路設定するように動作可能であり、前記データ・アクセス要求の前記経路設定が同じクロック・サイクル中に実行される、データ・プロセッサ・コアを提供する。

30

**【 0 0 0 5 】**

本発明は、一部の状況で、データを特定のメモリに、又は特定のメモリから迅速に転送することができることが特に重要であることを認識している。本発明は、メモリ・アクセス・インターフェイスを提供することによってこの問題に対処する。コアをいくつかの部分に分割することにはいくつかの利点があり、1つは、データを読み取り、それをコアのレジスタに格納し、次いでメモリに書き込むのに必要な命令が不要であるため、データが標準プロセッサ・コアを介して転送された場合より速く転送され得ることである。しかし、コアのメモリ・アクセス・インターフェイス部分を処理部分とともに提供することに関連する問題は、両方の部分が関連のメモリに格納されているデータに同時にアクセスしよ

40

50

うとする可能性があることである。この問題は、データ・ロギングなど、すぐに処理する必要のない大量のデータがコアを介してメモリに転送されるアプリケーションにおいて特に重大となる場合がある。

#### 【0006】

この問題は、プロセッサ・コアと関連のメモリとの間にデータ通信を提供するように動作可能な少なくとも2つのバスを提供することによって対処され、関連のメモリは少なくとも2つの部分に分割され、バスがそれぞれの部分にデータ・アクセスを提供する。アービトレイション・ロジックは、バス及び読み取り／書き込みポートと関連して提供され、メモリの特定の部分にあるデータへのアクセスを要求するデータ・アクセス要求を適切なバスに経路設定するように動作可能である。複数のバスの提供によって、同じクロック・サイクルでコアのメモリ・アクセス・インターフェイス及びデータ処理部分から受信されるメモリの異なる部分へのデータ・アクセス要求をそれぞれのバスに沿って並行して処理できるようになる。これによって、コアの2つの部分が単一のバスを介して1つのメモリにアクセスしようと試みているときに起こり得る問題の一部が軽減される。

#### 【0007】

好ましい実施例では、アービトレイション・ロジックは、前記データ・アクセス要求に関連付けられている前記少なくとも1つのメモリ内のアドレス位置に基づいて前記データ・アクセス要求を経路設定する前記少なくとも2つのバスのうちの一方を選択するように動作可能である。

#### 【0008】

データに関連付けられているアドレスは、データが格納されているメモリの部分の指示を提供し、したがってどのバスを使用するかを決定するためにアービトレイション・ロジックによって使用することができる有用なインジケータである。

#### 【0009】

好ましい実施例では、前記メモリの前記少なくとも2つの部分は、命令を格納するように動作可能である命令部分、及びデータ項目を格納するように動作可能である少なくとも1つのデータ部分を含み、前記アービトレイション・ロジックは、転送すべきデータが命令であるとき、前記命令部分へのアクセスを提供する前記少なくとも2つのバスのうちの第1のものに前記アクセス要求を経路設定し、転送すべきデータがデータ項目であるとき、前記少なくとも1つのデータ部分へのアクセスを提供する前記少なくとも2つのバスのうちの第2のものに前記データ・アクセス要求を経路設定するように動作可能である。

#### 【0010】

メモリを命令部分及びデータ部分に分割することは、メモリを分割する実際の方法である。

#### 【0011】

好ましくは、前記少なくとも1つのデータ部分は、偶数アドレスを有するデータを格納するように動作可能な偶数データ部分、及び奇数アドレスを有するデータを格納するように動作可能な奇数データ部分の2つのデータ部分を含み、前記読み取り／書き込みポートは、前記命令部分へのアクセスを提供する第1のバス、前記奇数データ部分へのアクセスを提供する第2のバス、及び前記偶数データ部分へのアクセスを提供する第3のバスの3つのバスを介して前記プロセッサ・コアと前記少なくとも1つのメモリとの間にデータを転送するように動作可能であり、前記アービトレイション・ロジックは、転送すべきデータが命令であるときは前記第1のバスに、転送すべきデータが奇数アドレスに関連付けられているデータ項目であるときは前記第2のバスに、転送すべきデータが偶数アドレスに関連付けられているデータ項目であるときは前記第3のバスにデータ・アクセス要求を経路設定するように動作可能である。

#### 【0012】

データ部分を奇数アドレス部分及び偶数アドレス部分に分割することによって、同時に格納された大量のデータ項目にアクセスするデータ・アクセス要求は、交互のデータ・バスを使用する。これは、プロセッサ・コアの部分のうちの1つがデータ・バスのうちの1

つを長時間独占する可能性がほとんどなく、それによってプロセッサ・コアの他方の部分によるメモリの対応する部分へのアクセスが防止されることを意味する。

#### 【0013】

好みしい実施例では、前記アービトレイション・ロジックは、前記少なくとも1つのメモリの一部にあるデータへのアクセスを要求する、前記メモリ・アクセス・インターフェイス部分からのデータ・アクセス要求、及び前記データ処理部分からのデータ・アクセス要求の両方のデータ・アクセス要求の前記受信に応答して、前記処理部分からの前記要求を前記少なくとも2つのバスのうちの前記一方に経路設定する前に、前記メモリ・アクセス・インターフェイス部分からの前記データ・アクセス要求を、前記少なくとも1つのメモリの前記一部にデータ・アクセスを提供する前記少なくとも2つのバスのうちの一方に経路設定するように動作可能である。10

#### 【0014】

アービトレイション・ロジックは、同じプロセッサ・クロック・サイクル中に両方の部分からのデータ・アクセス要求が受信されたときにメモリ・アクセス・インターフェイスに優先権を与えるように動作可能である。これは、メモリ・アクセス・インターフェイスは、メモリへの高速アクセスを提供するためにプロセッサ・コアに設けられているからであり、したがって、それに優先権を与えることは理解できる。特に重要なコードがコアの処理部分によって実行されている場合、コアの処理部分が長時間にわたってメモリへのアクセスを拒否されることによってコアの動作に重大な影響を及ぼす可能性があり、複数のバスの提供は、それを防ぐのを助ける。20

#### 【0015】

有利には、前記アービトレイション・ロジックは、前記少なくとも1つのメモリの少なくとも1つのビジー部分から待機要求を検出するように動作可能であり、前記アービトレイション・ロジックは、前記待機要求が検出されなくなるまで、任意のデータ・アクセス要求を前記ビジー部分に経路設定しないように動作可能である。

#### 【0016】

一部の実施例では、メモリは、プロセッサ・クロックほど速く動作しない場合がある。こうした場合、アービトレイション・ロジックが理解できる待機信号を使用できることが非常に便利である。これによって、プロセッサが対応できるよりも速くデータ・アクセス要求がメモリに、又はメモリから送信されるのを防ぐ。30

#### 【0017】

本発明の第2の態様は、本発明の第1の態様によるデータ処理コア、少なくとも2つの部分に分割される少なくとも1つのメモリ、及び前記少なくとも1つのメモリの前記少なくとも2つの部分のそれぞれの部分へのデータ・アクセスをそれぞれ可能にする少なくとも2つのバスを含むデータ処理装置を提供する。

#### 【0018】

有利には、前記少なくとも1つのメモリは厳重に制御されたメモリである。

#### 【0019】

本発明の実施例によって異なる種類のメモリを使用することはできるが、本発明は、特に厳重に制御されたメモリの扱いによく対応している。40

#### 【0020】

本発明の第3の態様は、外部データ・ソースとデータ・プロセッサ・コアに関連付けられている少なくとも1つのメモリとの間にデータを転送する方法を提供し、前記データ・プロセッサ・コアは、前記外部データ・ソースと前記データ・プロセッサ・コアに関連付けられている前記少なくとも1つのメモリとの間のデータ転送操作を実行するように動作可能であるメモリ・アクセス・インターフェイス部分、及びデータ処理操作を実行するように動作可能であるデータ処理部分を含み、前記方法は、前記メモリ・アクセス・インターフェイス部分から受信された前記少なくとも1つのメモリの一部にあるデータのアクセスを要求するデータ・アクセス要求、及び前記データ処理部分から受信された前記少なくとも1つのメモリの別の部分にあるデータへのアクセスを要求するデータ・アクセス要求50

に応答して、前記メモリ・アクセス・インターフェイス部分から受信された前記データ・アクセス要求を少なくとも2つのバスのうちの一方に経路設定するステップであって、前記少なくとも2つのバスのうちの前記一方が前記少なくとも1つのメモリの前記一部へのアクセスを提供するステップと、前記データ処理部分から受信された前記データ・アクセス要求を前記少なくとも2つのバスのうちのもう一方のバスに経路設定するステップであって、前記もう一方のバスが前記少なくとも1つのメモリの前記別の部分へのアクセスを提供するステップとを含み、前記データ・アクセス要求の前記経路設定は、同じクロック・サイクル中に実行される。

#### 【0021】

本発明の第4の態様は、本発明の第3の態様による方法の諸ステップを実行するようにデータ・プロセッサを制御するよう動作可能であるアービトレイション・ロジックを提供する。 10

#### 【0022】

本発明の上記及び他の目的、特徴、及び利点は、以下の実施例の詳細な説明を添付の図面とともに併せ読むことによって明らかになる。

#### 【実施例】

#### 【0023】

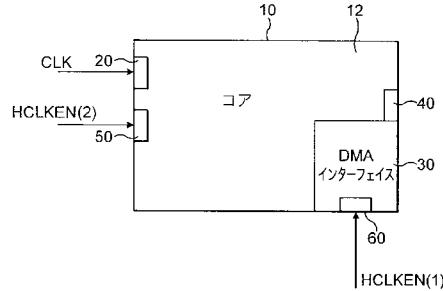

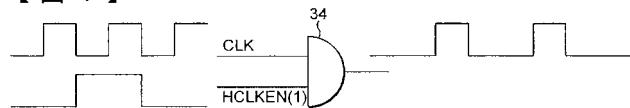

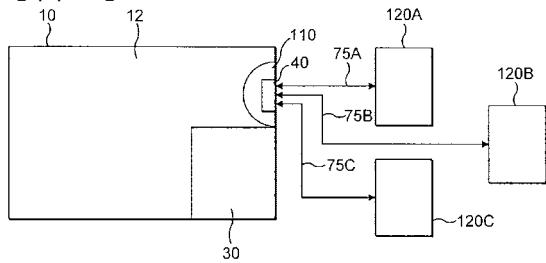

図1は、複数の部分に分割されたプロセッサ・コア10を示しており、一方の部分12が標準データ処理部分、他方の部分が直接メモリ・インターフェイス(direct memory interface)DMA30である。プロセッサ・コア10は、プロセッサ・クロック信号(processor clocking signal)CLKを受信するクロック信号入力20、及びバスを介してコアに関連付けられているメモリに接続されるように動作可能である少なくとも1つの読み取り/書き込みポート40を有する。コアは、クロック・イネーブル信号HCLKEN(1)を受信するメモリ・アクセス・イネーブル信号入力60、及びクロック・イネーブル信号HCLKEN(2)を受信するプロセッサ・イネーブル入力50のさらに2つの入力も有し得る。一部の実施例では、プロセッサ・イネーブル信号HCLKEN(2)は、外部信号として受信されるのではなく、コア内のロジックを処理することによって生成される(図3参照)。コアの処理部分12は、HCLKEN(2)信号があらかじめ定められた値を有しているとき、つまりこの実施例では1であるとき、プロセッサ・クロック信号CLKによってクロック制御される。HCLKEN(2)信号が0のとき、処理部分は、プロセッサ・クロック信号CLKを受信せず、したがって非アクティブである。 20 30

#### 【0024】

また、コアの直接メモリ・インターフェイス部分30も、プロセッサ・クロック信号CLKによってクロック制御される。メモリ・アクセス・イネーブル信号HCLKEN(1)があらかじめ定められた値、つまりこの実施例では1を有しているとき、直接メモリ・インターフェイス部分は、単にこのCLK信号を受信するだけである。HCLKEN(1)がゼロの場合、メモリ・アクセス・インターフェイス30は、プロセッサ・クロック信号CLKを受信せず、したがって非アクティブである。 40

#### 【0025】

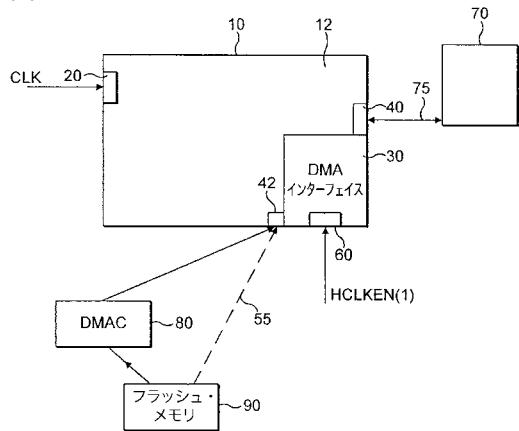

図2は、本発明の一実施例によるデータ処理装置を示しており、このデータ処理装置は、図1に示すようなデータ・プロセッサ・コア10、命令メモリ70、直接メモリ・アクセス・コントローラ(DMAC)80、及びフラッシュ・メモリ90を有する。プロセッサ・コアは、データ・バス75によって命令メモリ70に接続されている。命令メモリ70は、密結合メモリであり、したがってメモリとコアとの間のデータ転送は常に、予測できるある時間がかかる。

#### 【0026】

D MAC80は、DMAインターフェイス30を介して、外部データ・ソース、この場合はフラッシュ・メモリ90と、コアに関連付けられているメモリ、この場合は命令メモリ70との間のデータの転送を制御する。この実施例では、外部データ・ソースは、プロ

セッサに関連付けられているフラッシュ・メモリであるが、本発明の実施例は、他の任意の外部データ・ソースと、プロセッサに関連付けられているメモリとの間でデータを転送することができる。示した実施例では、データは、DMAインターフェイス30を介してフラッシュ・メモリ90と命令メモリ70との間で転送される。これは、処理部分12がアクティブである間、又はスリープ状態である間、すなわちHCKLEN(2)が1又は0の間にを行うことができる。DMACは、転送されるデータに制御信号を追加する。制御信号は、メモリ70内のデータが格納されている（格納される）場所のアドレスを示し、1つの信号は、データ転送が読み取りであるか書き込みであるかを示す。

#### 【0027】

フラッシュ・メモリ又は他の外部データ・ソースがAMBAバスを介してプロセッサ・コアに接続される一部の実施例では、データを、AMBAバス55を介して直接DMAインターフェイスに送信することができ、DMAC80は必要ない。これは、バスがDMAインターフェイスによって理解されるプロトコルを有しているときに可能であり、したがって、必要なアドレス及び制御信号は、転送されるデータにすでに関連付けられており、DMACによるこれらの信号の追加は必要ない。

#### 【0028】

DMAインターフェイス30は、プロセッサ・クロック信号CLKによってクロック制御され、各クロック・サイクルで、データ項目及びその対応するアドレスがDMAインターフェイスに入力される。次いでこれらは、レジスタに格納され、次のクロック・サイクルで、読み取り／書き込みポート40を介してデータ・バス75に沿って命令メモリ70に出力される。

#### 【0029】

図2のデータ処理装置の動作の一例は起動時である。この実施例では、データ・プロセッサの起動コードは、フラッシュ・メモリ90に格納される。フラッシュ・メモリはかなり遅いメモリであり、したがってこのコードは、実行前により速い命令メモリ70に転送される。起動が行われる前、プロセッサ・コアは非アクティブであり、起動要求の受信後に、DMAC80は、フラッシュ・メモリ90から起動コードを読み取り、入力42を介してデータをDMAインターフェイスに渡す。この時点で、メモリ・アクセス・イネーブル信号HCKLEN(1)は1に設定され、したがってDMAインターフェイスは、DMACから渡されたデータ項目を読み取り、DMAインターフェイスはプロセッサ・クロックによってクロック制御される。このデータはDMAインターフェイス30を通過し、次いで読み取り／書き込みポート40、及びプロセッサ・コアのデータ・バス75を介して命令メモリ70に出力される。この実施例では、コアはスリープ状態（コアのデータ処理部分へのクロック制御はオフにされ、割り込み待ちモード（wait-for-interrupt mode）になっている）であり、したがってDMAインターフェイス30は、コア自体からのデータ転送との任意の潜在的な衝突無しにコアをメモリに接続するデータ・バスを使用することができる。

#### 【0030】

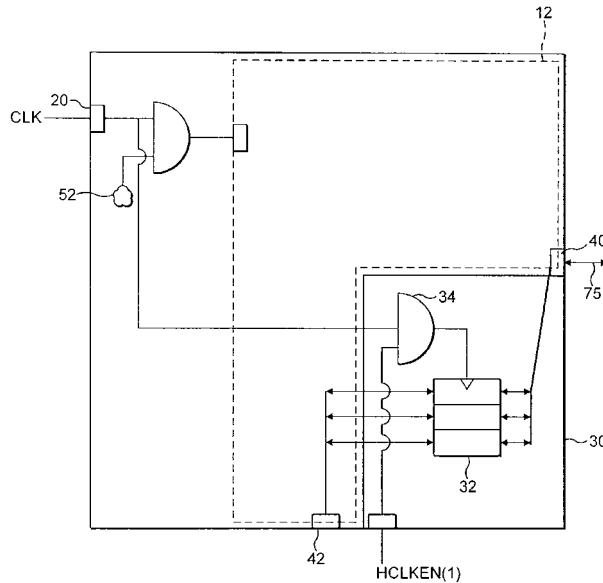

図3は、図1に示したものに似たプロセッサ・コアを示しており、この実施例では、プロセッサ・イネーブル信号は、外部信号としてコアに入力されるのではなく、処理ロジック52によって生成される。この処理ロジックは、コアのシステム・コントローラの状態の監視に応答して処理イネーブル信号を生成する。処理イネーブル信号及びプロセッサ・クロック信号は、ANDゲートを通過し、ANDゲートの出力は、プロセッサ・コアの処理部分12をクロック制御するために使用される。したがって、処理イネーブル信号が1の場合、プロセッサ・クロック信号CLKは、処理部分12によって受信され、処理イネーブル信号がゼロの場合、クロック信号は受信されず、したがってコアの処理部分は非アクティブ又はスリープ状態である。スリープ・モードでは、コアは、外部ピンでの割り込み要求又はデバッグ要求についてサンプリングを行い、これらのうちのいずれかを受信すると、プロセッサ・イネーブル信号が処理ロジック52によって生成され、割り込み待ちモード（すなわちスリープ・モード）を終了すべきであることをプロセッサ・コアに示す

10

20

30

40

50

。

### 【0031】

また、図3は、図1のコア10の直接メモリ・アクセス・インターフェイス部分30をより詳しく示している。DMAインターフェイス30は、いくつかのレジスタ32を含み、それぞれ、外部データ・ソースから転送され、入力24を介してコアに入力されるデータ、又はメモリから転送され、バス75を介して読み取り／書き込みポート40に入力されるデータを保持するように動作可能である。このデータは、レジスタ32で保持され、次いで外部データ・ソース又はメモリに転送される。直接メモリ・アクセス・インターフェイス30は、プロセッサ・クロックとメモリ・インターフェイス・イネーブル信号HCLKEN(1)との論理積演算を行うように動作可能であるANDゲート34も含む。レジスタへの格納を含むデータ転送の処理は、ANDゲート34から出力された信号を介してクロック制御される。ANDゲート34は、プロセッサ・クロック信号CLKを一方の入力として、またメモリ・アクセス・インターフェイス・イネーブル信号HCLKEN(1)を他方の入力として受信する。したがって、メモリ・アクセス・インターフェイス・イネーブル信号が実行可能であるとき、すなわち1のとき、プロセッサ・クロックは、ANDゲート34の出力に存在し、したがって直接メモリ・アクセス・インターフェイスは、クロック制御され、アクティブであり、レジスタ32は、データを受信し、転送することができる。HCLKEN(1)が0のとき、クロック信号は受信されず、メモリ・アクセス・インターフェイス30は非アクティブである。転送されたデータは、データ項目、データ項目に関連付けられているアドレス、及びデータがそのアドレスから読み取られるか、そこに書き込まれるかを表す制御信号を含む。これらは一般に、AMBAプロトコルに従って並行してレジスタ32に転送される。

10

20

### 【0032】

図4は、2つのクロック信号を受信する直接メモリ・アクセス・インターフェイスのANDゲート34を示している。明らかなように、この実施例では、クロック・イネーブル信号は、定常信号(steady signal)ではなく、むしろクロック信号自体である。これによってANDゲート34は、その出力にプロセッサ・クロックに対して異なる周波数のクロック信号を生成することになる。メモリ・アクセス・インターフェイス30によって実行されるデータ転送をクロック制御するのがこの信号である。これは、プロセッサ・クロックのクロック速度で動作することができない低速メモリからデータが転送されているときに有利である。このようにより遅いクロックを提供する能力は、低速メモリに関連付けられている潜在的な問題を軽減するのに効率的で簡単な方法であり、これによって実際に、より遅いメモリに適した速度でデータ転送を行うことができるようになる。

30

### 【0033】

データ処理コアの別の処理部分と同じ時にアクティブであり得るメモリ・アクセス・インターフェイス30を有する1つの潜在的な問題は、これらはいずれも、同じときに読み取り／書き込みポート40を介してデータ・アクセスを要求する場合があることである。図5は、これを扱う方法を示している。この実施例では、読み取り／書き込みポート40に関連付けられているアビトリレーション・ロジック110が提供され、アビトリレーション・ロジックは、2つのデータ・アクセス要求が同じクロック・サイクルで受信されたときに、最初にどのデータ・アクセス要求が処理されるかを制御する。直接メモリ・インターフェイス30は、高速データ転送を提供するために設けられているため、アビトリレーション110は、処理部分12から受信された要求より常にDMAデータ・アクセス要求に高い優先順位を与えるように設定される。これに関する1つの潜在的な問題は、大きいデータ転送要求が外部データ・ソースから受信された場合、バス75はしばらくの間DMAインターフェイス30によって独占される可能性があり、したがって、バス75に沿ってメモリにアクセスする必要がある重要なコードを実行する必要がある処理部分12が長時間の停止を被ることである。この問題は、いくつかの実施例では、読み取り／書き込みポート40を複数のデータ・バスに取り付けることによって対

40

50

処されている。図5は、読み取り／書き込みポート40が3つのバス、75A、75B、及び75Cに接続されているところを示している。

#### 【0034】

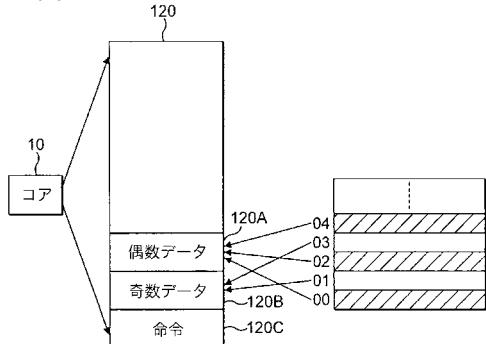

この実施例では、密結合メモリ120(図6参照)が3つの部分に分割される。部分120aは、偶数アドレスを有するデータを格納するように動作可能であり、部分120bは、奇数アドレスを有するデータを格納するように動作可能であり、部分120cは、命令を格納するように動作可能である。データ・バス75aは、読み取り／書き込みポート40をメモリ120aの偶数データ部分に接続し、バス75bは、読み取り／書き込みポートをメモリ120bの奇数データ部分に接続し、バス75cは、読み取り／書き込みポートをメモリ120cの命令部分に接続する。このように、密結合メモリ120への可能な経路が3つあり、これらは、同じクロック・サイクル中に並行して使用することができる。これによって、すべての場合に、直接メモリ・アクセス・インターフェイス30からのデータ・アクセス要求に優先順位が与えられたとき、データ・プロセッサ・コア10の処理部分12に起り得るデータの長時間の停止状態の問題が軽減される。10

#### 【0035】

アービトレーション・ロジック110は、どの要求に優先順位が与えられるかを制御し、また適切なバスへのデータ・アクセス要求の経路設定も制御する。これを行うには、データに関連付けられているアドレスを監視し、次いでこのアドレスを含むメモリ120の部分にアクセスするよう動作可能なバスにデータを置く。メモリ120cの命令部分は一般に命令を格納するために使用されるが、命令がそれに関連付けられているデータを有している場合、データ項目を命令とともに配置することができることに留意されたい。データの経路設定は、転送されているデータの種類の検出によるのではなく、データに関連付けられているアドレスを使用して行われる。20

#### 【0036】

信号の経路設定を制御すること、及びDMAインターフェイス30からのデータ・アクセス要求に優先順位を与えることに加えて、コードから出力され、プロセッサ・クロックCLKでクロック制御されているデータ・アクセス要求について行けないほど遅すぎるメモリのときは、アービトレーション・ロジック110を使用して、メモリの部分から出力される待機信号を検出することもできる。この場合、アービトレーション・ロジック110は、待機信号が検出されなくなるまで、他の任意のデータ・アクセス要求を処理しない。30

#### 【0037】

図6は、プロセッサ・コア10に関連付けられている密結合メモリ120をより詳しく示している。明らかなように、メモリはいくつかの部分に分割されており、偶数アドレスが部分120aにマップされ、奇数アドレスが部分120bにマップされる。この実施例では、メモリを語境界でインターリープ動作させる。命令は部分120cに格納される。このように偶数アドレス及び奇数アドレスを使用したデータのマッピングは、隣接するアドレスを有するいくつかのデータ項目が、交互のバス120a及び120bを使用して連続してアクセスされることを意味する。これは、メモリの特定の部分へのバスのうちの1つが大量のシリアル・データ・アクセス要求によって独占されている確率が低く、したがってコアの処理部分に対してデータの長時間の停止状態が起こる可能性が低いことを意味する。40

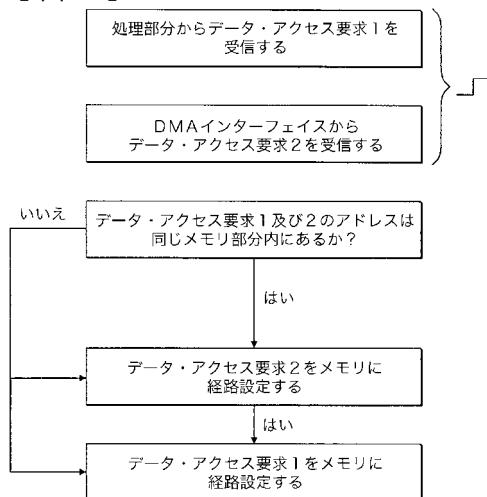

#### 【0038】

図7は、アービトレーション・ロジック110が同じクロック・サイクルで受信された処理部分12及びDMAインターフェイスからのデータ・アクセス要求をどのように扱うかを概略的に示しているフロー図である。明らかなように、アービトレーション・ロジックは、これらの要求がメモリの同じ部分のアドレスにアクセスしているかどうかを確認し、そうでない場合、それらはそれぞれのバスに沿って並行して経路設定される。それらが同じメモリ部分のアドレスを含んでいる場合、DMAインターフェイスからのデータ・アクセス要求2が最初に経路設定され、次のクロック・サイクルで、処理部分からのデータ50

・アクセス要求 1 が経路設定される。

【0039】

本発明の実施例について、添付の図面を参照して本明細書で詳しく説明してきたが、本発明は、こうした正確な実施例に限定されるものではなく、添付の特許請求の範囲によって定義された本発明の範囲及び意図から逸脱することなく、当業者によって様々な変更及び修正をそれに加えることができることを理解されたい。例えば、本発明の範囲から逸脱することなく頭記の従属クレームの特徴を独立クレームの特徴と様々に組み合わせることができる。

【図面の簡単な説明】

【0040】

10

【図1】一実施例によるプロセッサ・コアを示す概略図である。

【図2】一実施例によるデータ処理装置を示す概略図である。

【図3】プロセッサ・コアをより詳しく示す概略図である。

【図4】クロック及びクロック・イネーブル信号を結合するように動作可能であるロジックの一例を示す図である。

【図5】一実施例による、プロセッサ・コア、メモリ、及びその2つをリンクするバスを示す概略図である。

【図6】一実施例による関連のメモリを示す図である。

【図7】データ・アクセス要求の経路設定に関する諸ステップを示すフロー図である。

20

【符号の説明】

【0041】

20

10 プロセッサ・コア

12 一方の部分

20 クロック信号入力

30 直接メモリ・インターフェイス

32 レジスタ

34 A N D ゲート

40 読み取り／書き込みポート

42 入力

50 プロセッサ・イネーブル入力

30

55 A M B A バス

60 アクセス・イネーブル信号入力

70 命令メモリ

75 A データ・バス

75 B データ・バス

75 C データ・バス

80 直接メモリ・アクセス・コントローラ ( D M A C )

90 フラッシュ・メモリ

110 アービトレーション・ロジック

120 密結合メモリ

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 タン バ トラン

アメリカ合衆国、テキサス、ラウンド ロック、カーギル ドライブ 4015

(72)発明者 ジェラルド リチャード ウィリアムス ザ サード

アメリカ合衆国、テキサス、サンセット バレー、カーレイ メスキート コーブ 3

(72)発明者 ディヴィッド テレンス マセニー

アメリカ合衆国、テキサス、オースティン、バックトーン ドライブ 10706

(72)発明者 ディヴィッド ウォルター フリン

イギリス国、ケンブリッジ、トップクリフ ウェイ 1

F ターム(参考) 5B060 AB09 AB11 CA03 CA17 CD04 MB02

5B061 GG01 RR07

【要約の続き】