(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3998373号

(P3998373)

(45) 発行日 平成19年10月24日(2007.10.24)

(24) 登録日 平成19年8月17日(2007.8.17)

(51) Int.C1.

F 1

|                     |                  |            |      |

|---------------------|------------------|------------|------|

| <b>HO1L 21/768</b>  | <b>(2006.01)</b> | HO1L 21/90 | A    |

| <b>HO1L 21/28</b>   | <b>(2006.01)</b> | HO1L 21/28 | L    |

| <b>HO1L 21/8242</b> | <b>(2006.01)</b> | HO1L 27/10 | 621C |

| <b>HO1L 27/108</b>  | <b>(2006.01)</b> | HO1L 27/10 | 621Z |

請求項の数 11 (全 36 頁)

(21) 出願番号

特願平11-187450

(22) 出願日

平成11年7月1日(1999.7.1)

(65) 公開番号

特開2001-15712(P2001-15712A)

(43) 公開日

平成13年1月19日(2001.1.19)

審査請求日

平成15年11月5日(2003.11.5)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 古川 亮一

東京都青梅市新町六丁目16番地の3 株

式会社日立製作所 デバイス開発センタ内

須向 一行

東京都青梅市新町六丁目16番地の3 株

式会社日立製作所 デバイス開発センタ内

(72) 発明者 平沼 雅幸

東京都小平市上水本町五丁目20番1号

株式会社日立製作所 半導体グループ内

最終頁に続く

(54) 【発明の名称】半導体集積回路装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

以下の工程を含む半導体集積回路装置の製造方法；

(a) 半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜に溝またはスルーホールを形成して前記第1導電膜を露出する工程。

(b) 前記溝またはスルーホールの内部および前記第1絶縁膜の上部に、前記溝またはスルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(c) 前記第2導電膜をフォトトレジスト膜で覆った後、前記フォトトレジスト膜に露光光を照射することによって、少なくとも前記溝またはスルーホールの外部の前記フォトトレジスト膜および前記溝またはスルーホールに埋め込まれた上部のフォトトレジスト膜を露光する工程、

(d) 前記フォトトレジスト膜の露光部を除去し、前記溝またはスルーホールの内部に前記フォトトレジスト膜の未露光部を残す工程、

(e) 前記未露光部のフォトトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝またはスルーホールの内部に前記第2導電膜を残す工程、

(f) 前記溝またはスルーホールの内部の前記フォトトレジスト膜を除去し、前記溝またはスルーホールの内部に露出した前記第2導電膜の表面に第3導電膜を選択成長させることによって、前記溝またはスルーホールの内部に前記第3導電膜を埋め込む工程。

## 【請求項2】

10

20

請求項 1 記載の半導体集積回路装置の製造方法において、前記第 2 導電膜は窒化チタンまたはタンゲステンからなることを特徴とする半導体集積回路装置の製造方法。

**【請求項 3】**

請求項 1 記載の半導体集積回路装置の製造方法において、前記第 3 導電膜はタンゲステンまたはアルミニウム合金からなることを特徴とする半導体集積回路装置の製造方法。

**【請求項 4】**

請求項 1 記載の半導体集積回路装置の製造方法において、前記 (f) 工程の後、

(g) 前記第 1 絶縁膜の上部に第 4 導電膜を形成し、前記溝またはスルーホールの内部の前記第 3 導電膜を介して前記第 4 導電膜と前記第 1 導電膜とを電気的に接続する工程、

をさらに含むことを特徴とする半導体集積回路装置の製造方法。 10

**【請求項 5】**

以下の工程を含む半導体集積回路装置の製造方法；

(a) 半導体基板の主面上に第 1 導電膜を形成し、前記第 1 導電膜の上部に第 1 絶縁膜を形成した後、前記第 1 絶縁膜に溝またはスルーホールを形成して前記第 1 導電膜を露出する工程、

(b) 前記溝またはスルーホールの内部および前記第 1 絶縁膜の上部に、前記溝またはスルーホールを通じて前記第 1 導電膜に電気的に接続される第 2 導電膜を形成する工程、

(c) 前記第 2 導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、少なくとも前記溝またはスルーホールの外部の前記フォトレジスト膜および前記溝またはスルーホールに埋め込まれた上部のフォトレジスト膜を露光する工程、 20

(d) 前記フォトレジスト膜の露光部を除去し、前記溝またはスルーホールの内部に前記フォトレジスト膜の未露光部を残す工程、

(e) 前記未露光部のフォトレジスト膜で覆われていない領域の前記第 2 導電膜を除去することによって、前記溝またはスルーホールの内部に前記第 2 導電膜を残す工程、

(f) 前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部および前記第 1 絶縁膜の上部に第 5 導電膜を形成する工程、

(g) 前記第 5 導電膜の表面上に第 6 導電膜を選択成長させた後、前記溝またはスルーホールの外部の前記第 6 導電膜および前記第 5 導電膜を除去し、前記溝またはスルーホールの内部に前記第 6 導電膜および前記第 5 導電膜を残す工程。 30

**【請求項 6】**

請求項 5 記載の半導体集積回路装置の製造方法において、前記第 2 導電膜は窒化チタンまたは窒化タンタルからなることを特徴とする半導体集積回路装置の製造方法。

**【請求項 7】**

請求項 5 記載の半導体集積回路装置の製造方法において、前記第 5 導電膜および前記第 6 導電膜は銅からなることを特徴とする半導体集積回路装置の製造方法。

**【請求項 8】**

請求項 5 記載の半導体集積回路装置の製造方法において、前記第 6 導電膜および前記第 5 導電膜の除去は、化学機械研磨法によって行うことを特徴とする半導体集積回路装置の製造方法。 40

**【請求項 9】**

以下の工程を含む半導体集積回路装置の製造方法；

(a) 半導体基板の主面上に第 1 導電膜を形成し、前記第 1 導電膜の上部に第 1 絶縁膜を形成した後、前記第 1 絶縁膜および前記第 1 導電膜をパターニングすることによって、その上部が前記第 1 絶縁膜で覆われた前記第 1 導電膜からなるゲート電極を形成する工程、

(b) 前記ゲート電極の両側の前記半導体基板に半導体領域を形成する工程、

(c) 前記ゲート電極が形成された前記半導体基板上に第 2 絶縁膜を形成した後、前記第 2 絶縁膜の上部に、前記第 1 絶縁膜および前記第 2 絶縁膜とはエッティングの選択比が異なる第 3 絶縁膜を形成する工程、

(d) 第 1 フォトレジスト膜をマスクにして前記第 3 絶縁膜をエッティングすることにより 50

、前記半導体領域の上部の前記第2絶縁膜に達する第1溝および前記ゲート電極の上部の前記第2絶縁膜に達する第2溝を形成する工程、

(e) 前記第1フォトレジスト膜を除去した後、前記第1、第2溝の内部および前記第3絶縁膜の上部に第2フォトレジスト膜を形成する工程、

(f) 前記第2フォトレジスト膜に露光光を照射することによって、前記第2溝の内部および前記第3絶縁膜の上部の前記第2フォトレジスト膜を露光した後、前記第2フォトレジスト膜の露光部を除去することによって、前記第1溝の内部に前記第2フォトレジスト膜の未露光部を残す工程、

(g) 前記第1溝の内部の前記未露光部の第2フォトレジスト膜をマスクにしたエッチングで前記第2溝の底部の前記第2絶縁膜およびその下部の前記第1絶縁膜の一部をエッチングする工程、10

(h) 前記未露光部の第2フォトレジスト膜を除去した後、前記第1溝の下部の前記第2絶縁膜および前記第2溝の下部の前記第1絶縁膜をエッチングすることによって、前記半導体領域の上部に第1コンタクトホールを形成し、前記ゲート電極の上部に第2コンタクトホールを形成する工程。

#### 【請求項10】

請求項9記載の半導体集積回路装置の製造方法において、前記第1絶縁膜および前記第2絶縁膜は窒化シリコンからなり、前記第3絶縁膜は酸化シリコン膜からなることを特徴とする半導体集積回路装置の製造方法。

#### 【請求項11】20

請求項9記載の半導体集積回路装置の製造方法において、前記(h)工程の後、(i)前記第1、第2コンタクトホールの内部および前記第3絶縁膜の上部に第2導電膜を形成する工程、

(j) 前記第2導電膜をパターニングすることによって、前記第1コンタクトホールを通じて前記半導体領域に電気的に接続される第1配線および前記第2コンタクトホールを通じて前記ゲート電極に電気的に接続される第2配線を形成する工程、をさらに含むことを特徴とする半導体集積回路装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】30

本発明は、半導体集積回路装置の製造技術に関し、特に、絶縁膜に形成した溝またはスルーホールの内部に導電層を形成するプロセスに適用して有効な技術に関する。

##### 【0002】

##### 【従来の技術】

D R A M (Dynamic Random Access Memory) のメモリセルは、半導体基板の主面上にマトリクス状に配置された複数のワード線と複数のビット線との交点に配置され、1個のメモリセル選択用M I S F E T (Metal Insulator Semiconductor Field Effect Transistor) とこれに直列に接続された1個の情報蓄積用容量素子(キャパシタ)とで構成されている。

##### 【0003】40

上記メモリセル選択用M I S F E Tは、周囲を素子分離領域で囲まれた活性領域に形成され、主としてゲート酸化膜、ワード線と一緒に構成されたゲート電極およびソース、ドレインを構成する一対の半導体領域で構成されている。ビット線は、メモリセル選択用M I S F E Tの上部に配置され、その延在方向に隣接する2個のメモリセル選択用M I S F E Tによって共有されるソース、ドレインの一方と電気的に接続されている。情報蓄積用容量素子は、同じくメモリセル選択用M I S F E Tの上部に配置され、上記ソース、ドレインの他方と電気的に接続されている。

##### 【0004】

特開平7-7084号公報は、メモリセル選択用M I S F E Tの上部に情報蓄積用容量素子を配置するスタッケド・キャパシタ(Stacked Capacitor)構造のD R A Mを開示してい

る。この公報に記載されたDRAMは、メモリセルの微細化に伴う情報蓄積用容量素子の蓄積電荷量の減少を補うために、ビット線の上部に配置した情報蓄積用容量素子の下部電極（蓄積電極）を円筒状に加工することによってその表面積を増やし、その上部に容量絶縁膜と上部電極（プレート電極）とを形成している。

#### 【0005】

また、特開平11-17144号公報は、上記した円筒状の下部電極の内側底部に絶縁膜からなる補強部材を形成することによって、下部電極の機械的強度を向上させ、製造工程の途中で円筒状の下部電極が倒れたりする不良を防止している。特開平5-129550号公報の[0025]～[0028]および図5(a)～図5(c)には、溝の内部および外部のホトレジストを塗布後に露光量を制御して全面露光して溝内部にホトレジストを残して溝の上部を加工する開示がある。特開平7-66284号公報の[0015]～[0016]および図1(c)、(d)、(e)には、SOIの酸化膜分離溝の形成において分離溝内を含むホトレジストを塗布後全面露光して溝内部のみにホトレジストを残してマスク材のエッチング除去時に埋め込み酸化膜のエッチングを防止して、その後ホトレジストを除去後溝内部に絶縁膜を埋め込む開示がある。特開平8-335634号公報の[0012]および図1(e)、(f)には、デュアルダマシン配線の形成においてコントラクトホール内に有機膜を埋め込んだ状態で配線溝を形成するために絶縁膜をエッチングしたのち有機膜を除去してデュアルダマシン配線溝を形成する開示がある。

#### 【0006】

##### 【発明が解決しようとする課題】

本発明者は、ビット線の上部に堆積した厚い酸化シリコン膜に溝を形成し、この溝の内部に情報蓄積用容量素子の下部電極（蓄積電極）を形成する技術を開発している。

#### 【0007】

上記情報蓄積用容量素子を形成するには、一例としてビット線の上部に厚い酸化シリコン膜を形成した後、フォトトレジスト膜をマスクにしたドライエッチングで上記酸化シリコン膜に溝を形成する。次に、溝の内部および酸化シリコン膜の上部に多結晶シリコン膜を堆積した後、溝の内部の多結晶シリコン膜をSOG(Spin On Glass)などの塗布膜で保護し、酸化シリコン膜の上部の多結晶シリコン膜をドライエッチングで除去することによって、溝の内部に情報蓄積用容量素子の下部電極として使用される多結晶シリコン膜を形成する。

#### 【0008】

次に、溝の内部の多結晶シリコン膜を覆っているSOG膜を除去する。SOG膜の除去は、酸化シリコン膜とSOG膜とのエッチング選択比の差を利用したドライエッチングまたはウェットエッチングによって行う。

#### 【0009】

次に、多結晶シリコン膜の上部に酸化タンタル( $Ta_2O_5$ )膜などの誘電体膜を堆積した後、酸化タンタル膜の上部に窒化チタンなどの導電膜を堆積することによって、多結晶シリコン膜で構成された下部電極、酸化タンタル膜で構成された容量絶縁膜および窒化チタンなどの導電膜で構成された上部電極からなる情報蓄積用容量素子を形成する。

#### 【0010】

上記情報蓄積用容量素子は、酸化シリコン膜に形成した溝の内部に下部電極を形成するので、従来の円筒状の下部電極のように、製造工程の途中で下部電極が倒れたりする不具合が生じないという利点がある。その反面、上記情報蓄積用容量素子の下部電極は、円筒の内壁および外壁を蓄積電荷量確保のための有効領域として利用する従来の下部電極に比べて表面積が少ないので、蓄積電荷量を確保するためには、下部電極が形成される溝を深くしたり、下部電極の表面に凹凸を形成したりすることによって表面積を増やす工夫が必要となる。

#### 【0011】

しかし、酸化シリコン膜とSOG膜とのエッチング選択比の差を利用してSOG膜を選択的に除去する前記下部電極の製造方法は、酸化シリコン膜とSOG膜とのエッチング選択

10

20

30

40

50

比が十分に大きくないために、溝の内部の多結晶シリコン膜を覆っているSOG膜をエッチングで除去する際、溝の外部の酸化シリコン膜もある程度エッチングされてその上面が下方に後退してしまう。特に、多結晶シリコン膜の表面に凹凸を形成したような場合は、凹凸の隙間に残ったSOG膜を除去するためのオーバーエッチングが必要となるため、上記した酸化シリコン膜の後退量が大きくなる。

#### 【0012】

上記のような酸化シリコン膜の後退が生じると、溝の内部に形成された多結晶シリコン膜の上端部が溝の開孔端よりも上方に突き出てしまうために、情報蓄積用容量素子の表面の平坦性が低下したり、多結晶シリコン膜の上端部に電界が集中して情報蓄積用容量素子のリーク電流が増加したりするといった不具合を引き起こす。

10

#### 【0013】

本発明の目的は、絶縁膜に形成された溝の内部に下部電極を形成する情報蓄積用容量素子を備えたDRAMの製造歩留まりを向上させる技術を提供することにある。

#### 【0014】

本発明の他の目的は、絶縁膜に形成した溝またはスルーホールの内部に導電層を形成する技術を提供することにある。

#### 【0015】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

#### 【0016】

20

#### 【課題を解決するための手段】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、次のとおりである。

#### 【0017】

(1) 本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

#### 【0018】

(a) 半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜に溝またはスルーホールを形成する工程、

(b) 前記溝またはスルーホールの内部および前記第1絶縁膜の上部に、前記溝またはスルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

30

(c) 前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、少なくとも前記溝またはスルーホールの外部の前記フォトレジスト膜を露光する工程、

(d) 前記フォトレジスト膜の露光部を除去し、前記溝またはスルーホールの内部に前記フォトレジスト膜の未露光部を残す工程、

(e) 前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝またはスルーホールの内部に前記第2導電膜を残す工程。

#### 【0019】

(2) 本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程における前記第2導電膜の除去を、前記フォトレジスト膜をマスクにしたエッチングによって行う。

40

#### 【0020】

(3) 本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程における前記第2導電膜の除去を化学機械研磨法によって行う。

#### 【0021】

(4) 本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(d)工程における前記フォトレジスト膜の除去を、前記フォトレジスト膜を現像することによって行う。

#### 【0022】

(5) 本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程

50

の後、

(f) 前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部に露出した前記第2導電膜の表面に第3導電膜を選択成長させることによって、前記溝またはスルーホールの内部に前記第3導電膜を埋め込む工程をさらに含む。

【0023】

(6) 本発明の半導体集積回路装置の製造方法は、前記(5)において、前記第2導電膜が窒化チタンまたはタンゲステンからなる。

【0024】

(7) 本発明の半導体集積回路装置の製造方法は、前記(5)において、前記第3導電膜がタンゲステンまたはアルミニウム合金からなる。 10

【0025】

(8) 本発明の半導体集積回路装置の製造方法は、前記(5)において、前記(f)工程の後、

(h) 前記第1絶縁膜の上部に第4導電膜を形成し、前記溝またはスルーホールの内部の前記第3導電膜を介して前記第4導電膜と前記第1導電膜とを電気的に接続する工程をさらに含む。

【0026】

(9) 本発明の半導体集積回路装置の製造方法は、前記(1)において、前記(e)工程の後、 20

(f) 前記溝またはスルーホールの内部の前記フォトレジスト膜を除去し、前記溝またはスルーホールの内部および前記第1絶縁膜の上部に第5導電膜を形成する工程、

(g) 前記第5導電膜の表面に第6導電膜を選択成長させた後、前記溝またはスルーホールの外部の前記第6導電膜および前記第5導電膜を除去し、前記溝またはスルーホールの内部に前記第6導電膜および前記第5導電膜を残す工程をさらに含む。

【0027】

(10) 本発明の半導体集積回路装置の製造方法は、前記(9)において、前記第2導電膜が窒化チタンまたは窒化タンタルからなる。

【0028】

(11) 本発明の半導体集積回路装置の製造方法は、前記(9)において、前記第5導電膜および前記第6導電膜が銅からなる。 30

【0029】

(12) 本発明の半導体集積回路装置の製造方法は、前記(9)において、前記第6導電膜および前記第5導電膜の除去を、化学機械研磨法によって行う。

【0030】

(13) 本発明の半導体集積回路装置の製造方法は、半導体基板の主面に形成されたメモリセル選択用MISFETおよび前記メモリセル選択用MISFETの上部に形成された情報蓄積用容量素子によって構成されるメモリセルを備えた半導体集積回路装置の製造方法であって、以下の工程を含む。

【0031】

(a) 半導体基板の主面にメモリセル選択用MISFETを形成し、前記メモリセル選択用MISFETの上部に第1絶縁膜を形成した後、前記第1絶縁膜に形成したスルーホールの内部に、前記メモリセル選択用MISFETのソース、ドレインの一方に電気的に接続される第1導電膜を形成する工程、 40

(b) 前記第1絶縁膜の上部に第2絶縁膜を形成した後、前記第2絶縁膜に溝を形成する工程、

(c) 前記溝の内部および前記第2絶縁膜の上部に、前記溝を通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

(d) 前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、 50

(e) 前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(f) 前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝の内部に前記第2導電膜を残す工程、

(g) 前記溝の内部の前記フォトレジスト膜を除去した後、前記溝の内部および前記第2絶縁膜の上部に第3絶縁膜を形成し、前記第3絶縁膜の上部に第3導電膜を形成することによって、前記第2導電膜からなる第1電極、前記第3絶縁膜からなる容量絶縁膜および前記第3導電膜からなる第2電極によって構成される情報蓄積用容量素子を形成する工程。

**【0032】**

10

(14) 本発明の半導体集積回路装置の製造方法は、半導体基板の主面に形成されたメモリセル選択用MISFETおよび前記メモリセル選択用MISFETの上部に形成された情報蓄積用容量素子によって構成されるメモリセルを備えた半導体集積回路装置の製造方法であって、以下の工程を含む。

**【0033】**

(a) 半導体基板の主面にメモリセル選択用MISFETを形成し、前記メモリセル選択用MISFETの上部に第1絶縁膜を形成した後、前記第1絶縁膜に形成したスルーホールの内部に、前記メモリセル選択用MISFETのソース、ドレインの一方電気的に接続される第1導電膜を形成する工程、

(b) 前記第1絶縁膜の上部に第2絶縁膜を形成した後、前記第2絶縁膜に溝を形成する工程、

20

(c) 前記溝の内部および前記第2絶縁膜の上部に、前記溝を通じて前記第1導電膜に電気的に接続されるアモルファスシリコンからなる第2導電膜を形成する工程、

(d) 前記第2導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、

(e) 前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(f) 前記フォトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝の内部に前記第2導電膜を残す工程、

(g) 前記溝の内部の前記フォトレジスト膜を除去した後、前記溝の内部に露出した前記第2導電膜の表面に凹凸を形成する工程、

30

(h) 前記第2導電膜を熱処理することによって多結晶化する工程、

(i) 前記溝の内部および前記第2絶縁膜の上部に第3絶縁膜を形成し、前記第3絶縁膜の上部に第3導電膜を形成することによって、前記第2導電膜からなる第1電極、前記第3絶縁膜からなる容量絶縁膜および前記第3導電膜からなる第2電極によって構成される情報蓄積用容量素子を形成する工程。

**【0034】**

(15) 本発明の半導体集積回路装置の製造方法は、半導体基板の主面に形成されたメモリセル選択用MISFETおよび前記メモリセル選択用MISFETの上部に形成された情報蓄積用容量素子によって構成されるメモリセルを備えた半導体集積回路装置の製造方法であって、以下の工程を含む。

40

**【0035】**

(a) 半導体基板の主面にメモリセル選択用MISFETを形成し、前記メモリセル選択用MISFETの上部に第1絶縁膜を形成した後、前記第1絶縁膜に形成したスルーホールの内部に、前記メモリセル選択用MISFETのソース、ドレインの一方電気的に接続される第1導電膜を形成する工程、

(b) 前記第1絶縁膜の上部に第2絶縁膜を形成した後、前記第2絶縁膜に溝を形成する工程、

(c) 前記溝の内部および前記第2絶縁膜の上部に、前記溝を通じて前記第1導電膜に電気的に接続されるアモルファスシリコンからなる第2導電膜を形成する工程、

50

- (d) 前記第2導電膜の表面に凹凸を形成する工程、

- (e) 前記第2導電膜を熱処理することによって多結晶化する工程、

- (f) 前記第2導電膜をフォトトレジスト膜で覆った後、前記フォトトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトトレジスト膜を露光する工程、

- (g) 前記フォトトレジスト膜の露光部を除去し、前記溝の内部に前記フォトトレジスト膜の未露光部を残す工程、

- (h) 前記フォトトレジスト膜で覆われていない領域の前記第2導電膜を除去することによって、前記溝の内部に前記第2導電膜を残す工程、

- (i) 前記溝の内部の前記フォトトレジスト膜を除去した後、前記溝の内部および前記第2絶縁膜の上部に第3絶縁膜を形成し、前記第3絶縁膜の上部に第3導電膜を形成することによって、前記第2導電膜からなる第1電極、前記第3絶縁膜からなる容量絶縁膜および前記第3導電膜からなる第2電極によって構成される情報蓄積用容量素子を形成する工程。

**【0036】**

(16) 本発明の半導体集積回路装置の製造方法は、前記(14)または(15)において、前記フォトトレジスト膜で覆われていない領域の前記第2導電膜の除去を、前記フォトトレジスト膜をマスクにしたエッチングによって行う。

**【0037】**

(17) 本発明の半導体集積回路装置の製造方法は、前記(14)、(15)または(16)において、前記第2導電膜の表面の前記凹凸を、前記アモルファスシリコンの表面にシリコン粒を成長させることによって形成する。

**【0038】**

(18) 本発明の半導体集積回路装置の製造方法は、前記(1)～(17)のいずれか一項において、前記フォトトレジスト膜で覆われていない領域の前記第2導電膜を除去する際、前記溝の内部の前記第2導電膜の上端部を、前記溝の開孔端よりも下方に後退させる。

**【0039】**

(19) 本発明の半導体集積回路装置の製造方法は、前記(18)において、前記第2導電膜の上端部の後退量が、前記第2導電膜の表面に形成された前記凹凸の径とほぼ等しい。

**【0040】**

(20) 本発明の半導体集積回路装置の製造方法は、前記(13)～(19)のいずれか一項において、前記第2絶縁膜が酸化シリコン膜である。

**【0041】**

(21) 本発明の半導体集積回路装置の製造方法は、前記(13)～(20)のいずれか一項において、前記第3絶縁膜が高誘電率膜または強誘電体膜である。

**【0042】**

(22) 本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

**【0043】**

(a) 半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜にスルーホールを形成する工程、

(b) 前記スルーホールの内部および前記第1絶縁膜の上部にフォトトレジスト膜を形成した後、前記スルーホールの内部の前記フォトトレジスト膜の一部および配線溝形成領域の前記フォトトレジスト膜を選択的に露光する工程、

(c) 前記フォトトレジスト膜の露光部を除去し、前記第1絶縁膜の上部の一部および前記スルーホールの内部の一部に前記フォトトレジスト膜の未露光部を残す工程、

(d) 前記フォトトレジスト膜をマスクにして前記第1絶縁膜をエッチングすることにより、前記第1絶縁膜に配線溝を形成する工程、

(e) 前記フォトトレジスト膜を除去した後、前記第1絶縁膜の上部、前記配線溝の内部および前記スルーホールの内部に、前記スルーホールを通じて前記第1導電膜に電気的に接続される第2導電膜を形成する工程、

10

30

40

50

(f) 前記第1絶縁膜の上部の前記第2導電膜を化学機械研磨法で除去することによって、前記配線溝の内部および前記スルーホールの内部に前記第2導電膜からなる埋込み配線を形成する工程。

【0044】

(23) 本発明の半導体集積回路装置の製造方法は、前記(22)において、前記第2導電膜が銅からなる。

【0045】

(24) 本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0046】

(a) 半導体基板の主面上に第1導電膜を形成し、前記第1導電膜の上部に第1絶縁膜を形成した後、前記第1絶縁膜および前記第1導電膜をパターニングすることによって、その上部が前記第1絶縁膜で覆われた前記第1導電膜からなるゲート電極を形成する工程、

10

(b) 前記ゲート電極の両側の前記半導体基板に半導体領域を形成する工程、

(c) 前記ゲート電極が形成された前記半導体基板上に第2絶縁膜を形成した後、前記第2絶縁膜の上部に、前記第1絶縁膜および前記第2絶縁膜とはエッチングの選択比が異なる第3絶縁膜を形成する工程、

(d) 第1フォトレジスト膜をマスクにして前記第3絶縁膜をエッチングすることにより、前記半導体領域の上部の前記第2絶縁膜に達する第1溝および前記ゲート電極の上部の前記第2絶縁膜に達する第2溝を形成する工程、

(e) 前記第1フォトレジスト膜を除去した後、前記第1、第2溝の内部および前記第3絶縁膜の上部に第2フォトレジスト膜を形成する工程、

20

(f) 前記第2フォトレジスト膜に露光光を照射することによって、前記第2溝の内部および前記第3絶縁膜の上部の前記第2フォトレジスト膜を露光した後、前記第2フォトレジスト膜の露光部を除去することによって、前記第1溝の内部に前記第2フォトレジスト膜の未露光部を残す工程、

(g) 前記第1溝の内部の前記第2フォトレジスト膜をマスクにしたエッチングで前記第2溝の底部の前記第2絶縁膜およびその下部の前記第1絶縁膜の一部をエッチングする工程、

(h) 前記第2フォトレジスト膜を除去した後、前記第1溝の下部の前記第2絶縁膜および前記第2溝の下部の前記第1絶縁膜をエッチングすることによって、前記半導体領域の上部に第1コンタクトホールを形成し、前記ゲート電極の上部に第2コンタクトホールを形成する工程。

30

【0047】

(25) 本発明の半導体集積回路装置の製造方法は、前記(25)において、前記第1絶縁膜および前記第2絶縁膜が窒化シリコンからなり、前記第3絶縁膜が酸化シリコン膜からなる。

【0048】

(26) 本発明の半導体集積回路装置の製造方法は、前記(24)において、前記(h)工程の後、

(i) 前記第1、第2コンタクトホールの内部および前記第3絶縁膜の上部に第2導電膜を形成する工程、

40

(j) 前記第2導電膜をパターニングすることによって、前記第1コンタクトホールを通じて前記半導体領域に電気的に接続される第1配線および前記第2コンタクトホールを通じて前記ゲート電極に電気的に接続される第2配線を形成する工程をさらに含む。

【0049】

(27) 本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0050】

(a) 半導体基板の主面上に形成した第1絶縁膜に溝を形成した後、前記溝の内部および前記第1絶縁膜の上部にシリコン層を形成する工程、

(b) 前記溝の内部の前記シリコン層の上部に選択的に第2絶縁膜を形成し、前記溝の外

50

部の前記シリコン層を選択的に除去する工程、

(c) 前記溝の内部の前記第2絶縁膜を除去した後、前記シリコン層に凹凸を形成する工程、

(d) 前記凹凸が形成された前記シリコン層の上部に誘電体膜を形成し、前記誘電体膜の上部に導電膜を形成する工程。

【0051】

(28) 本発明の半導体集積回路装置の製造方法は、前記(27)において、前記シリコン層がアモルファスシリコンからなる。

【0052】

(29) 本発明の半導体集積回路装置の製造方法は、前記(27)において、前記第1絶縁膜が酸化シリコンからなり、前記第2絶縁膜がフォトレジストからなる。 10

【0053】

(30) 本発明の半導体集積回路装置の製造方法は、前記(27)において、前記シリコン層の前記凹凸を、前記シリコン層の表面にシリコン粒を成長させることによって形成する。

【0054】

(31) 本発明の半導体集積回路装置の製造方法は、前記(29)において、前記(b)工程が、

(b-1) 前記溝の内部および前記第1絶縁膜の上部にフォトレジスト膜を形成した後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を選択的に露光する工程、 20

(b-2) 前記フォトレジスト膜の露光部を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

(b-3) 前記フォトレジスト膜をマスクにしたエッチングで前記溝の外部の前記シリコン層を除去する工程を含む。

【0055】

(32) 本発明の半導体集積回路装置の製造方法は、(27)～(31)のいずれか一項において、前記凹凸が形成された前記シリコン層が容量素子の第1電極を構成し、前記誘電体膜が前記容量素子の容量絶縁膜を構成し、前記導電膜が前記容量素子の第2電極を構成する。 30

【0056】

(33) 本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0057】

(a) 半導体基板の主面上に形成した第1絶縁膜に溝を形成した後、前記溝の内部および前記第1絶縁膜の上部に導電層を形成する工程、

(b) 前記導電層の上部にフォトレジスト膜を形成した後、前記フォトレジスト膜に露光光を照射することによって、前記第1絶縁膜の上部の前記フォトレジスト膜を完全に露光し、前記溝の内部の前記フォトレジスト膜の一部を露光する工程、

(c) 前記フォトレジスト膜を現像することによって、完全に露光された領域の前記フォトレジスト膜を除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、 40

(d) 前記フォトレジスト膜で覆われていない領域の前記導電層を選択的に除去する工程。

【0058】

(34) 本発明の半導体集積回路装置の製造方法は、前記(33)において、前記導電層の選択的な除去を、前記フォトレジスト膜をマスクにしたエッチングによって行う。

【0059】

(35) 本発明の半導体集積回路装置の製造方法は、以下の工程を含む。

【0060】

(a) 半導体基板の主面上に酸化シリコン膜を形成した後、前記酸化シリコン膜に溝を形成する工程、

( b ) 前記溝の内部および前記酸化シリコン膜の上部に第1導電膜を形成する工程、

( c ) 前記第1導電膜をフォトレジスト膜で覆った後、前記フォトレジスト膜に露光光を照射することによって、前記溝の外部の前記フォトレジスト膜を露光する工程、

( d ) 前記フォトレジスト膜の露光部を現像により除去し、前記溝の内部に前記フォトレジスト膜の未露光部を残す工程、

( e ) 前記フォトレジスト膜をマスクにしたエッチングで前記酸化シリコン膜の上部の前記第1導電膜を除去する工程、

( f ) 前記溝の内部の前記フォトレジスト膜を除去することによって、前記溝の内部に前記第1導電膜を選択的に形成する工程。

## 【0061】

10

(36) 本発明の半導体集積回路装置の製造方法は、前記(35)において、前記(f)工程における前記フォトレジスト膜の除去を、アッシングによって行う。

## 【0062】

## 【発明の実施の形態】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において同一機能を有するものは同一の符号を付し、その繰り返しの説明は省略する。

## 【0063】

## (実施の形態1)

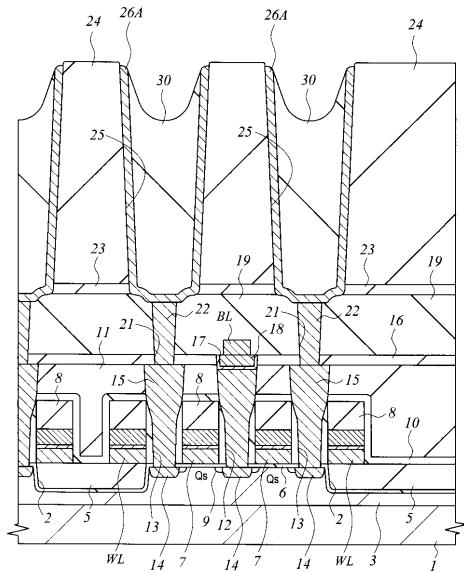

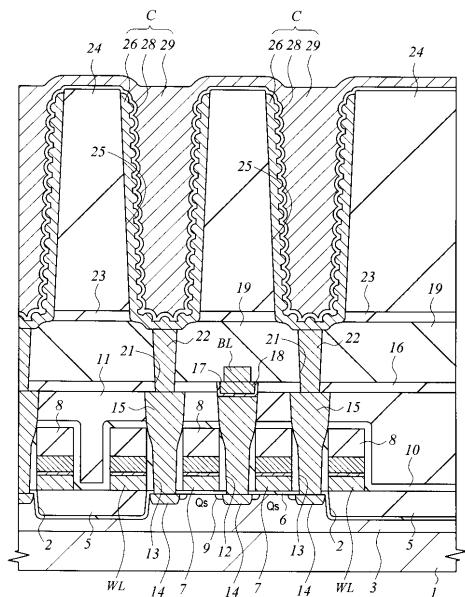

本発明の実施形態1であるDRAM(Dynamic Random Access Memory)の製造方法を図1～図21を用いて工程順に説明する。

20

## 【0064】

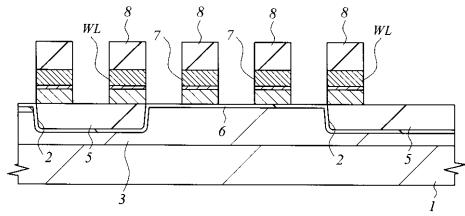

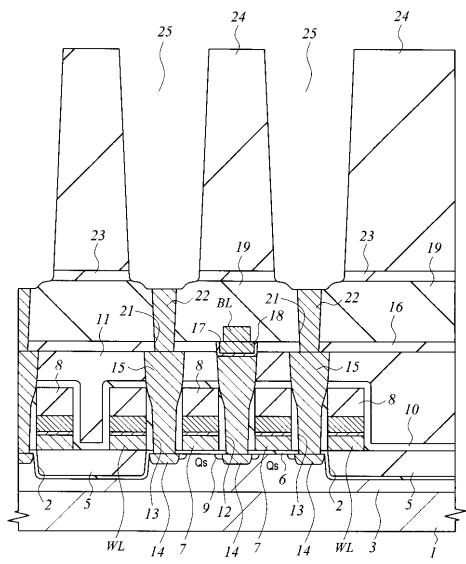

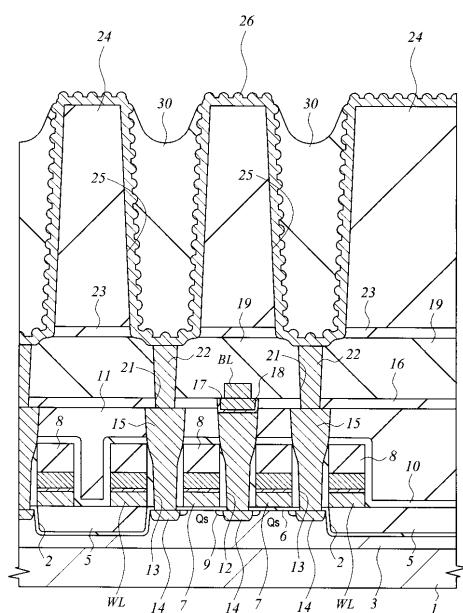

まず、図1に示すように、例えばp型の単結晶シリコンからなる半導体基板(以下、単に基板という)1の主面に素子分離溝2を形成した後、基板1にp型不純物(ホウ素(B))をイオン注入してp型ウエル3を形成する。素子分離溝2を形成するには、例えば基板1の素子分離領域をエッチングして溝を形成した後、溝の内部および基板1上にCVD(Chemical Vapor Deposition)法で酸化シリコン膜5を堆積し、続いて溝の外部の酸化シリコン膜5を化学機械研磨(Chemical Mechanical Polishing; CMP)法で除去して溝の内部のみに酸化シリコン膜5を残す。

## 【0065】

30

次に、基板1をスチーム酸化してp型ウエル3の表面にゲート酸化膜6を形成した後、ゲート酸化膜6上にゲート電極7(ワード線WL)を形成する。ゲート電極7(ワード線WL)を形成するには、例えば基板1上にリン(P)などのn型不純物をドープした多結晶シリコン膜をCVD法で堆積し、続いてその上部にスパッタリング法で窒化タンゲステン(WN)膜およびタンゲステン(W)膜を堆積し、さらにその上部にCVD法で窒化シリコン膜8を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでこれらの膜をパターニングする。

## 【0066】

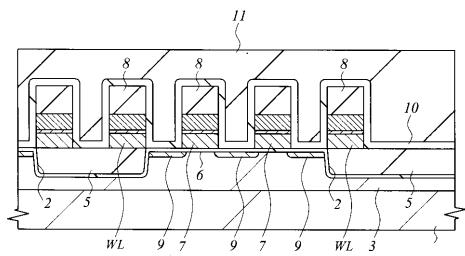

次に、図2に示すように、ゲート電極7の両側のp型ウエル3にリン(P)などのn型不純物をイオン注入してn<sup>-</sup>型半導体領域9を形成し、続いてゲート電極7(ワード線WL)の上部にCVD法で窒化シリコン膜10および酸化シリコン膜11を堆積した後、酸化シリコン膜11の表面を化学機械研磨法で平坦化する。

40

## 【0067】

次に、図3に示すように、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜11および窒化シリコン膜10をドライエッチングすることにより、n<sup>-</sup>型半導体領域9の上部にコンタクトホール12、13を形成する。酸化シリコン膜11のエッチングは、窒化シリコン膜10に対する酸化シリコン膜11のエッチング選択比が十分に大きくなる条件で行い、下層の窒化シリコン膜10が除去されないようにする。また、窒化シリコン膜10のエッチングは、基板1に対する窒化シリコン膜10のエッチング選択比が十分に大きくなる条件で行い、基板1が深く削れないようにする。さらに、窒化シリコン膜10

50

のエッチングは、窒化シリコン膜10を異方的にエッチングする条件で行い、ゲート電極7（ワード線WL）の側壁に窒化シリコン膜10を残す。これにより、コンタクトホール12、13がゲート電極7（ワード線WL）に対して自己整合（セルフアライン）で形成されるので、コンタクトホール12、13とゲート電極7（ワード線WL）との合わせ余裕が不要となり、DRAMのメモリセルサイズを縮小することができる。

#### 【0068】

次に、コンタクトホール12、13を通じてp型ウエル3にリンまたはヒ素(As)などのn型不純物をイオン打ち込みすることによって、n<sup>+</sup>型半導体領域14（ソース、ドレイン）を形成する。ここまで工程で、ゲート酸化膜6、ゲート電極7およびn<sup>+</sup>型半導体領域14（ソース、ドレイン）を有するnチャネル型のメモリセル選択用MISFET 10 Qsが形成される。

#### 【0069】

次に、コンタクトホール12、13の内部にプラグ15を形成する。プラグ15を形成するには、例えばコンタクトホール12、13の内部および酸化シリコン膜11の上部にリンなどのn型不純物をドープした低抵抗多結晶シリコン膜をCVD法で堆積した後、酸化シリコン膜11の上部の多結晶シリコン膜をドライエッチング（または化学機械研磨法）で除去し、多結晶シリコン膜をコンタクトホール12、13の内部のみに残す。

#### 【0070】

次に、図4に示すように、酸化シリコン膜11の上部にCVD法で酸化シリコン膜16を堆積し、続いてフォトレジスト膜（図示せず）をマスクにしたドライエッチングでコンタクトホール12の上部の酸化シリコン膜16にスルーホール17を形成した後、スルーホール17の内部にプラグ18を形成し、さらにプラグ18の上部にピット線BLを形成する。

#### 【0071】

プラグ18を形成するには、例えばスルーホール17の内部および酸化シリコン膜16の上部にスパッタリング法で窒化チタン膜およびタンゲステン膜を堆積した後、酸化シリコン膜16の上部の窒化チタン膜およびタンゲステン膜を化学機械研磨法で除去し、これらの膜をスルーホール17の内部のみに残す。また、ピット線BLを形成するには、例えば酸化シリコン膜16の上部にスパッタリング法でタンゲステン膜を堆積した後、フォトレジスト膜（図示せず）をマスクにしたドライエッチングでタンゲステン膜をパターニングする。ピット線BLは、スルーホール17内のプラグ18およびコンタクトホール12内のプラグ15を介してメモリセル選択用MISFETQsのソース、ドレインの一方（n<sup>+</sup>型半導体領域14）と電気的に接続される。

#### 【0072】

次に、酸化シリコン膜16の上部にCVD法で酸化シリコン膜19を堆積し、続いてフォトレジスト膜（図示せず）をマスクにしたドライエッチングでコンタクトホール13の上部の酸化シリコン膜19、16にスルーホール21を形成した後、スルーホール21の内部にプラグ22を形成する。プラグ22を形成するには、例えばスルーホール21の内部および酸化シリコン膜19の上部にリンなどのn型不純物をドープした低抵抗多結晶シリコン膜をCVD法で堆積した後、酸化シリコン膜19の上部の多結晶シリコン膜をドライエッチング（または化学機械研磨法）で除去し、多結晶シリコン膜をスルーホール21の内部のみに残す。

#### 【0073】

次に、図5に示すように、酸化シリコン膜19の上部にCVD法で窒化シリコン膜23を堆積し、続いて窒化シリコン膜23の上部にCVD法で酸化シリコン膜24を堆積した後、フォトレジスト膜（図示せず）をマスクにして酸化シリコン膜24および窒化シリコン膜23をドライエッチングすることにより、スルーホール21の上部に溝25を形成する。後述する情報蓄積用容量素子Cの下部電極は、この溝25の内壁に沿って形成されるので、下部電極の表面積を大きくして蓄積電荷量を増やすためには、酸化シリコン膜24を厚い膜厚（例えば1μm以上）で堆積する必要がある。

## 【0074】

酸化シリコン膜24のエッティングは、窒化シリコン膜23に対する酸化シリコン膜24のエッティング選択比が大きくなる条件で行い、下層の窒化シリコン膜23が除去されないようにする。また、窒化シリコン膜23のエッティングは、酸化シリコン膜19に対する窒化シリコン膜23のエッティング選択比が大きくなる条件で行い、下層の酸化シリコン膜19が深く削れないようにする。このように、厚い膜厚の酸化シリコン膜24の下層にエッティングストップとなる窒化シリコン膜23を設けることにより、酸化シリコン膜24をエッティングして溝25を形成する際に下層の酸化シリコン膜19が過剰にエッティングされる不具合が防止されるので、深い溝25を高い寸法精度で形成することができる。

## 【0075】

10

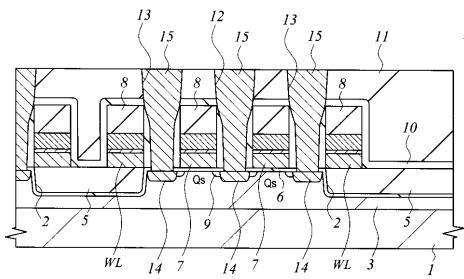

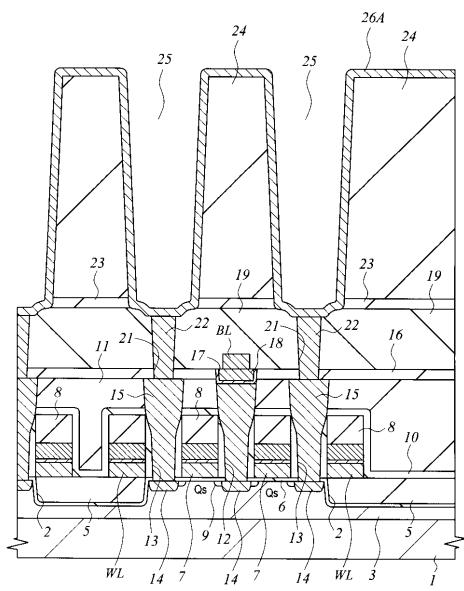

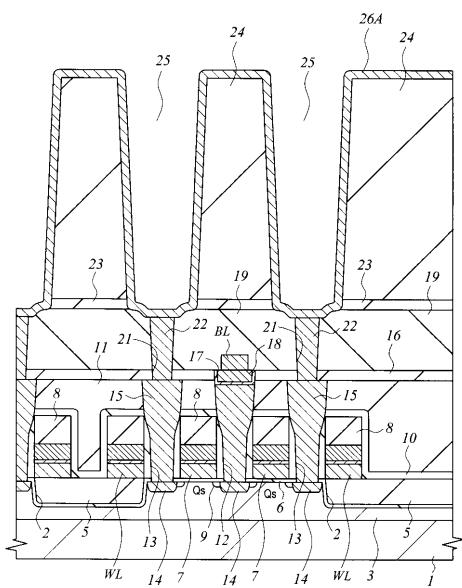

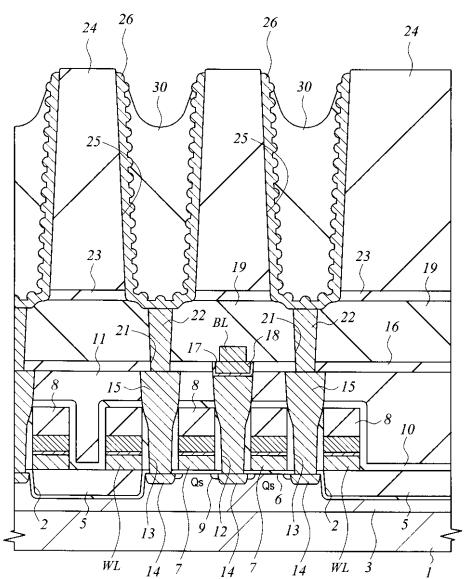

次に、図6に示すように、溝25の内部および酸化シリコン膜24の上部にリンなどのn型不純物をドープしたアモルファスシリコン膜26AをCVD法で堆積する。アモルファスシリコン膜26Aは、溝25の内壁に沿って堆積される程度の薄い膜厚（例えば50～60nm程度）で形成する。

## 【0076】

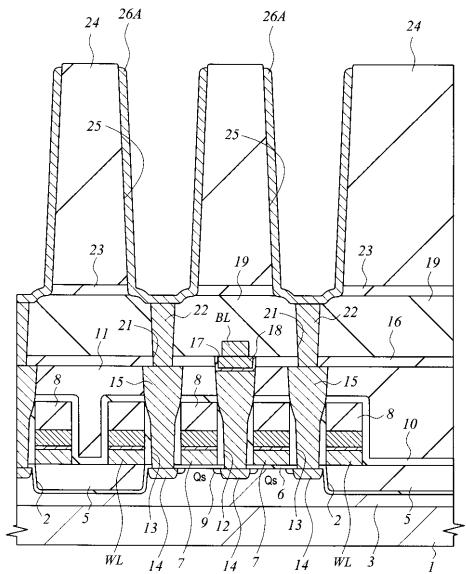

次に、図7に示すように、アモルファスシリコン膜26Aの上部にフォトレジスト膜30をスピンドル塗布する。フォトレジスト膜30は、露光部が現像液に可溶となるポジ型フォトレジスト（例えばノボラック樹脂系フォトレジスト）を使用する。

## 【0077】

20

次に、図8に示すように、フォトレジスト膜30の全面に露光光を照射する。このとき、溝25の外部や溝25の開孔端近傍のフォトレジスト膜30は露光されるが、深い溝25の内部のフォトレジスト膜2は露光量が不足するために露光されない。

## 【0078】

次に、図9に示すように、アルカリ水溶液などを使ってフォトレジスト膜30を現像する。このとき、露光部である溝25の外部や溝25の開孔端近傍のフォトレジスト膜30は現像液に可溶となるために除去されるが、未露光部である溝25の内部のフォトレジスト膜30は除去されない。この結果、溝25の外部の酸化シリコン膜24上にはアモルファスシリコン膜26Aが露出するが、溝25の内部のアモルファスシリコン膜26Aは、溝25の開孔端近傍を除き、フォトレジスト膜30で覆われたままとなる。

## 【0079】

30

次に、図10に示すように、フォトレジスト膜30で覆われていない領域、すなわち溝25の外部および溝25の開孔端近傍のアモルファスシリコン膜26Aをドライエッティングで除去する。アモルファスシリコン膜26Aのエッティングは、フォトレジスト膜30に対するアモルファスシリコン膜26Aのエッティング選択比が十分に大きくなる条件で行い、溝25の内部のフォトレジスト膜30で覆われたアモルファスシリコン膜26Aが露出して削られないようにする。

## 【0080】

また、このエッティングは、アモルファスシリコン膜26Aを異方的にエッティングする条件で行い、溝25の開孔端近傍においてアモルファスシリコン膜26の上端部を溝25の開孔端よりも僅かに下方に後退させることが望ましい。これにより、溝25の内部に形成される下部電極の先端部（上端部）に電界が集中し難くなるため、情報蓄積用容量素子のリード電流を低減することができる。なお、アモルファスシリコン膜26の後退量は、次の工程でアモルファスシリコン膜26Aの表面に成長させるシリコン粒の直径とほぼ同程度（約50nm）とするのがよい。後退量が少なすぎるとアモルファスシリコン膜26の上端部に成長したシリコン粒が溝25の開孔端よりも上方に突出するために、そこに電界が集中し易くなる。他方、後退量が多すぎると下部電極の表面積が小さくなるので、蓄積電荷量が減少する。

## 【0081】

次に、図11に示すように、溝25の内部に残ったフォトレジスト膜30を除去する。フォトレジスト膜30の除去は、例えばオゾンを熱分解したときに発生する酸素ラジカルに

40

50

よってフォトレジストを酸化分解するオゾンアッシング法を用いて行う。このアッシングは、酸素ラジカルが多量、かつ長時間にわたって発生する条件で行い、深い溝25の内部のアモルファスシリコン膜26Åを覆っているフォトレジスト膜30を完全に分解・除去する。

#### 【0082】

このように、本実施の形態では、溝25の外部のアモルファスシリコン膜26Åをドライエッチングで除去する際、溝25の内部のアモルファスシリコン膜26Åをフォトレジスト膜30で保護し、その後、不要となったフォトレジスト膜30をアッシングで除去する。この方法によれば、フォトレジスト膜30に対するアモルファスシリコン膜26Åのエッチング選択比が大きいため、溝25の外部のアモルファスシリコン膜26Åをドライエッチングで除去する際、溝25の内部のアモルファスシリコン膜26Åの削れを最小限に抑えることができる。また、溝25の内部のフォトレジスト膜30の除去をアッシングで行うことにより、溝25の外部の酸化シリコン膜24の削れを最小限に抑えることもできる。

10

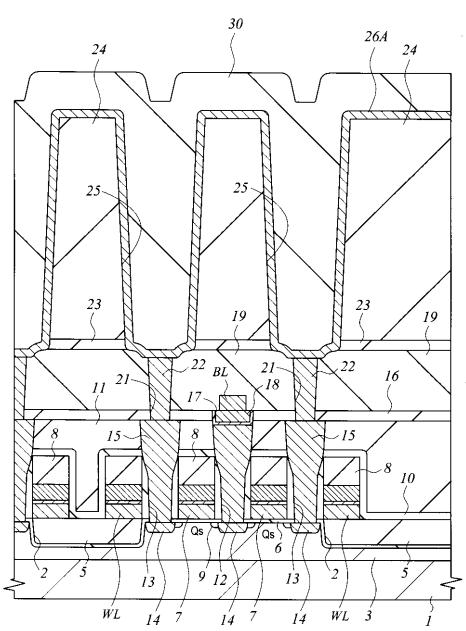

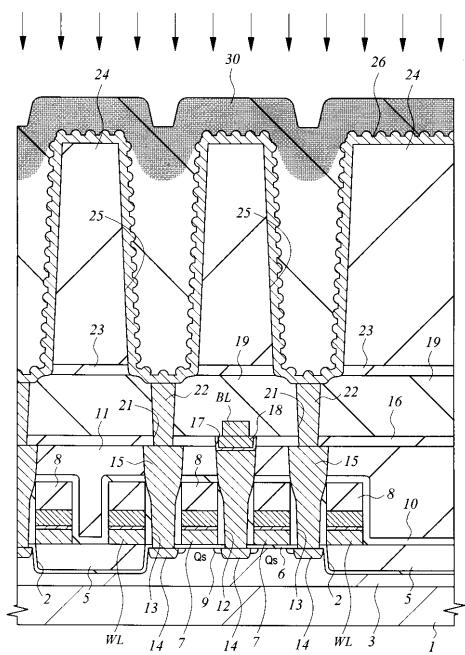

#### 【0083】

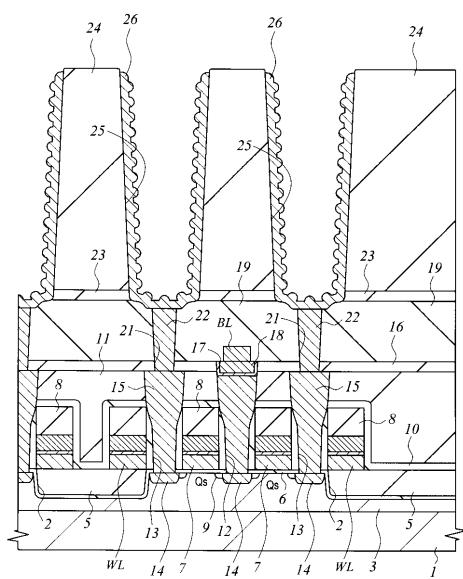

次に、図12に示すように、溝25の内部のアモルファスシリコン膜26Åを加工して表面が粗面化された多結晶シリコン膜26を形成する。多結晶シリコン膜26を形成するには、例えばフッ酸系の洗浄液を使ってアモルファスシリコン膜26Åの表面を清浄化し、続いて減圧雰囲気中、アモルファスシリコン膜26Åにモノシラン(SiH<sub>4</sub>)またはジシラン(Si<sub>2</sub>H<sub>6</sub>)を供給してその表面に平均粒径50nm程度のシリコン粒を成長させた後、基板1を熱処理してアモルファスシリコン膜26Åを多結晶化する。表面が粗面化された多結晶シリコン膜26はその表面積が大きいので、情報蓄積用容量素子の蓄積電荷量を増やすことができる。

20

#### 【0084】

また、本実施の形態では、溝25の内部のアモルファスシリコン膜26Åを保護するフォトレジスト膜30をアッシングで除去した後、アモルファスシリコン膜26Åの表面を粗面化するので、溝25の内部のフォトレジスト膜30を容易に除去することができる。これに対し、アモルファスシリコン膜26Åの表面を粗面化してからその表面を保護膜で覆い、溝25の外部のアモルファスシリコン膜26Åをエッチングで除去した後に保護膜を除去する方法では、アモルファスシリコン膜26Åの表面の細かい凹凸の隙間に保護膜が残り易い。

30

#### 【0085】

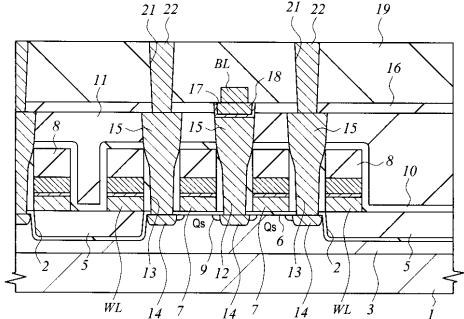

次に、図13に示すように、溝25の外部の酸化シリコン膜24の上部および溝25の内部の多結晶シリコン膜26の上部に高誘電率膜の一層である酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)膜28を堆積する。酸化タンタル膜28は、例えばペンタエトキシタンタルと酸素とをソースガスに用いた熱CVD法で形成し、その膜厚は20nm程度とする。また、酸化タンタル膜28の成膜に先立って多結晶シリコン膜26を窒化処理し、その表面に薄い窒化シリコン膜を形成することによって、酸化タンタル膜28のリーク電流を低減してもよい。その後、約800°Cの酸素雰囲気中で酸化タンタル膜28を改質・結晶化することにより、高誘電率でリーク電流の少ない良質の酸化タンタル膜28が得られる。

40

#### 【0086】

次に、図14に示すように、酸化タンタル膜28の上部にCVD法とスパッタリング法とを併用して窒化チタン(TiN)膜29を堆積することにより、多結晶シリコン膜26からなる下部電極、酸化タンタル膜28からなる容量絶縁膜および窒化チタン膜29からなる上部電極によって構成される情報蓄積用容量素子Cを形成する。情報蓄積用容量素子Cの下部電極(多結晶シリコン膜26)は、スルーホール21内のプラグ22およびコンタクトホール13内のプラグ15を介してメモリセル選択用MISFETQsのソース、ドレインの他方(n<sup>+</sup>型半導体領域14)と電気的に接続される。ここまで工程により、メモリセル選択用MISFETQsと、これに直列に接続された情報蓄積用容量素子Cによって構成されるDRAMのメモリセルが完成する。

50

## 【0087】

その後、情報蓄積用容量素子Cの上部に2層程度のアルミニウム(A1)配線を形成し、さらにその上部に酸化シリコン膜と窒化シリコン膜との積層膜などによって構成されるパッシベーション膜を形成するが、その図示および説明は省略する。

## 【0088】

なお、本実施の形態では、酸化シリコン膜24に形成した溝25の内部に多結晶シリコン膜26からなる下部電極を形成したが、下部電極材料は多結晶シリコンに限定されるものではない。また、容量絶縁膜材料や上部電極材料も酸化タンタルや窒化チタンに限定されるものではない。下部電極や上部電極は、例えばタンゲステン膜、白金、ルテニウム、イリジウムなどで構成することもできる。また、容量絶縁膜は、例えばBST、STO、BaTiO<sub>3</sub>(チタン酸バリウム)、PbTiO<sub>3</sub>(チタン酸鉛)、PZT(PbZr<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>)、PLT(PbLa<sub>x</sub>Ti<sub>1-x</sub>O<sub>3</sub>)、PLZTなどの金属酸化物からなる高誘電率膜や強誘電体膜などで構成することもできる。10

## 【0089】

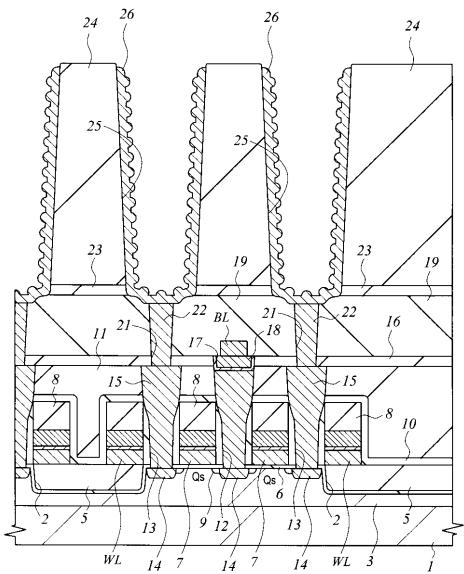

## (実施の形態2)

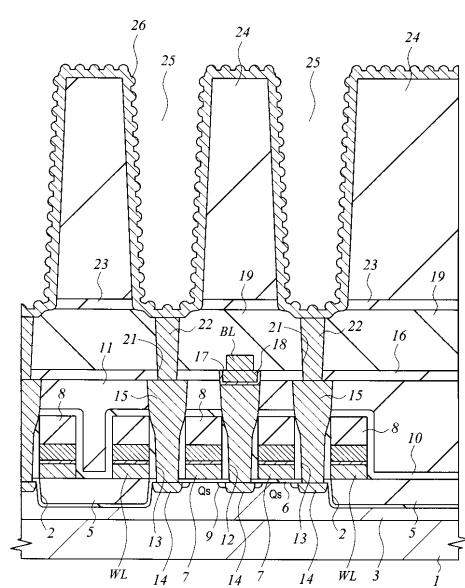

前記情報蓄積用容量素子Cの下部電極(多結晶シリコン膜26)は、次のような方法で形成することもできる。

## 【0090】

まず、図15に示すように、ビット線BLを覆う酸化シリコン膜19の上方に窒化シリコン膜23と厚い膜厚の酸化シリコン膜24とを堆積し、続いて酸化シリコン膜24および窒化シリコン膜23に深い溝25を形成した後、溝25の内部および酸化シリコン膜24の上部にアモルファスシリコン膜26Aを堆積する。ここまででは、前記実施の形態1の図1～図6に示す工程と同じである。20

## 【0091】

次に、図16に示すように、アモルファスシリコン膜26Aの表面にシリコン粒を成長させた後、基板1を熱処理してアモルファスシリコン膜26Aを多結晶化することにより、溝25の内部および酸化シリコン膜24の上部に表面が粗面化された多結晶シリコン膜26を形成する。アモルファスシリコン膜26Aの粗面化処理は、前記実施の形態1と同じ方法で行う。

## 【0092】

次に、図17に示すように、多結晶シリコン膜26の上部にポジ型のフォトレジスト膜30をスピンドル塗布し、続いてフォトレジスト膜30の全面に露光光を照射した後、図18に示すように、フォトレジスト膜30を現像して露光部を除去することにより、溝25の内部に未露光のフォトレジスト膜30を残す。30

## 【0093】

次に、図19に示すように、フォトレジスト膜30で覆われていない溝25の外部および溝25の開孔端近傍の多結晶シリコン膜26をドライエッティングで除去する。多結晶シリコン膜26のエッティングは、前記実施の形態1で行ったアモルファスシリコン膜26Aのエッティングと同様、フォトレジスト膜30に対する多結晶シリコン膜26のエッティング選択比が十分に大きくなる条件で行い、溝25の内部のフォトレジスト膜30で覆われたアモルファスシリコン膜26Aが露出して削られないようにする。また、このエッティングは、多結晶シリコン膜26を異方的にエッティングする条件で行い、溝25の開孔端近傍においてアモルファスシリコン膜26の上端部を溝25の開孔端よりも僅かに下方に後退させることが望ましい。40

## 【0094】

なお、表面に粗面化処理が施された多結晶シリコン膜26をエッティングする場合は、膜の表面形状に沿ってエッティングが進行するために、溝25の外部の酸化シリコン膜24の上部に多結晶シリコン膜26のエッティング残りが生じ易い。このエッティング残りは、隣接する溝25の間で下部電極同士が短絡する原因となるため、上記多結晶シリコン膜26をエッティングする際は、この点に配慮したエッティング条件を選定する必要がある。50

**【0095】**

次に、図20に示すように、前述したオゾンアッシング法などを用いて溝25の内部に残ったフォトレジスト膜30を除去し、多結晶シリコン膜26を露出させる。このとき、多結晶シリコン膜26の表面に形成されたシリコン粒の隙間などにフォトレジスト膜30のアッシング残りが生じると、情報蓄積用容量素子Cの蓄積電荷量の減少を引き起こす。従って、溝25の内部のフォトレジスト膜30を除去する際は、この点に配慮したアッシング条件を選定する必要がある。

**【0096】**

その後、図21に示すように、溝25の外部の酸化シリコン膜24の上部および溝25の内部の多結晶シリコン膜26の上部に酸化タンタル膜28を堆積し、続いて酸化タンタル膜28を改質・結晶化するための熱処理を行った後、酸化タンタル膜28の上部に窒化チタン膜29を堆積することにより、多結晶シリコン膜26からなる下部電極、酸化タンタル膜28からなる容量絶縁膜および窒化チタン膜29からなる上部電極によって構成される情報蓄積用容量素子Cを形成する。酸化タンタル膜28および窒化チタン膜29は、前記実施の形態1と同様の方法で形成する。

10

**【0097】**

このように、本実施の形態では、溝25の外部の多結晶シリコン膜26をドライエッチングで除去する際、溝25の内部の多結晶シリコン膜26をフォトレジスト膜30で保護し、その後、不要となったフォトレジスト膜30をアッシングで除去する。この方法によれば、フォトレジスト膜30に対する多結晶シリコン膜26のエッチング選択比が大きいため、溝25の外部のアモルファスシリコン膜26をドライエッチングで除去する際、溝25の内部の多結晶シリコン膜26の削れを最小限に抑えることができる。また、溝25の内部のフォトレジスト膜30の除去をアッシングで行うことにより、溝25の外部の酸化シリコン膜24の削れを最小限に抑えることもできる。

20

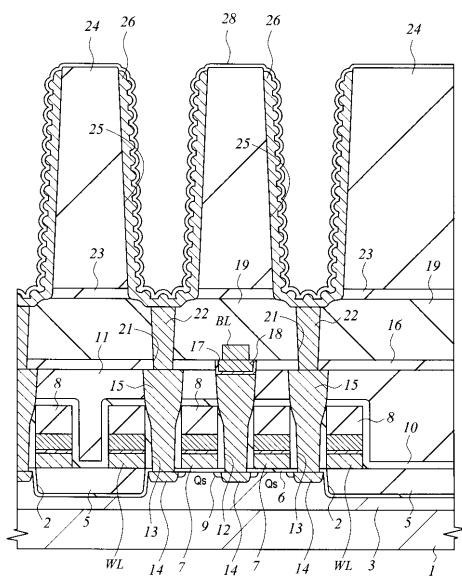

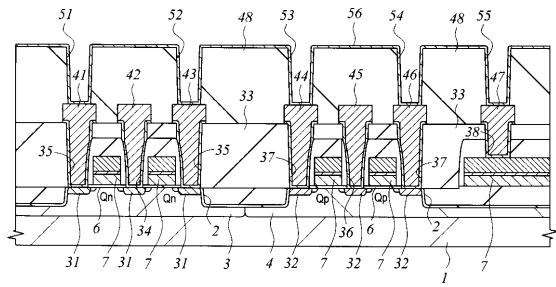

**【0098】****(実施の形態3)**

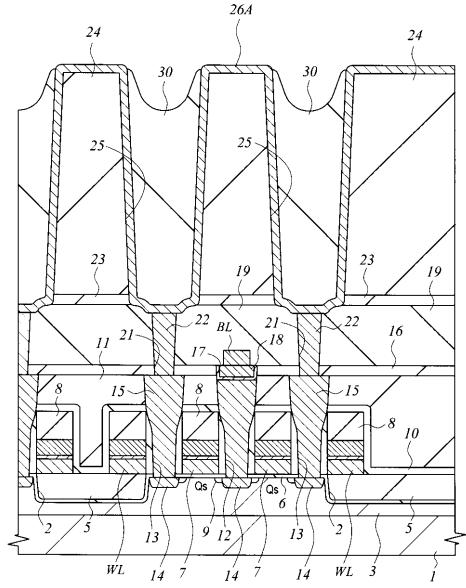

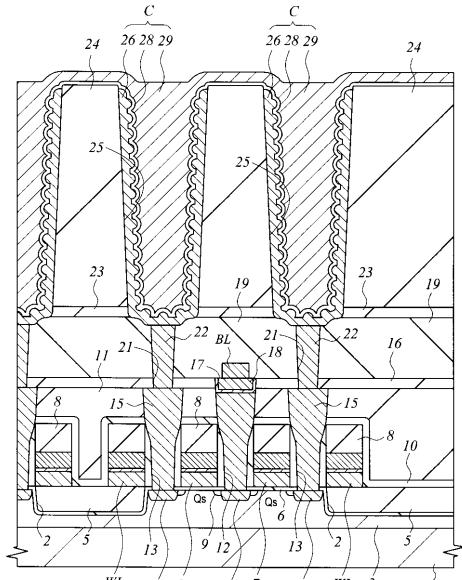

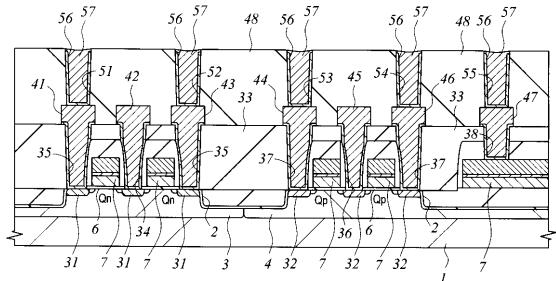

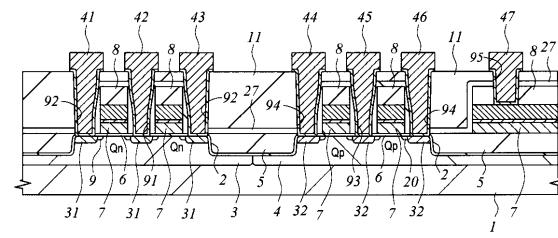

本発明の実施形態3であるプラグの形成方法を図22～図33を用いて工程順に説明する。

**【0099】**

まず、図22に示すように、例えばp型の単結晶シリコンからなる基板1の主面に素子分離溝2を形成した後、基板1の一部にp型不純物(ホウ素)をイオン注入してp型ウエル3を形成し、他の一部にn型不純物(リンまたはヒ素)をイオン注入してn型ウエル4を形成する。

30

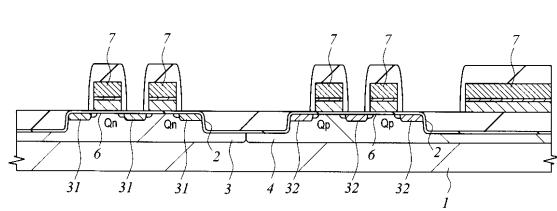

**【0100】**

次に、周知のCMOSプロセスに従ってp型ウエル3にnチャネル型MISFETQnを形成し、n型ウエル4にpチャネル型MISFETQpを形成する。nチャネル型MISFETQnは、主としてゲート酸化膜6、ゲート電極7およびn<sup>+</sup>型半導体領域(ソース、ドレイン)31で構成され、pチャネル型MISFETQpは、主としてゲート酸化膜6、ゲート電極7およびp<sup>+</sup>型半導体領域(ソース、ドレイン)32で構成される。

**【0101】**

40

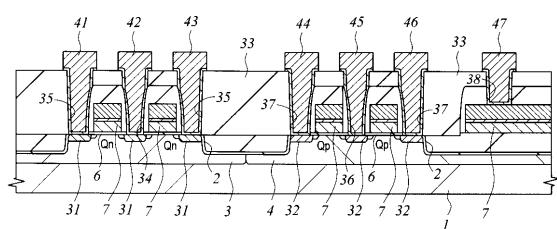

次に、図23に示すように、nチャネル型MISFETQnおよびpチャネル型MISFETQpの上部にCVD法で酸化シリコン膜33を堆積し、続いて酸化シリコン膜33の表面を化学機械研磨法で平坦化した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜33をドライエッチングすることにより、n<sup>+</sup>型半導体領域(ソース、ドレイン)31の上部にコンタクトホール34、35を形成し、p<sup>+</sup>型半導体領域(ソース、ドレイン)32の上部にコンタクトホール36、37を形成する。またこのとき同時に、ゲート電極7の上部にコンタクトホール38を形成する。

**【0102】**

次に、酸化シリコン膜33の上部に第1層目の配線41～47を形成する。配線41～47を形成するには、例えはコンタクトホール34～38の内部および酸化シリコン膜33

50

の上部にスパッタリング法またはCVD法で窒化チタン膜を堆積し、続いて窒化チタン膜の上部にCVD法でタングステン膜を堆積した後、フォトレジスト膜をマスクにしたドライエッティングでタングステン膜および窒化チタン膜をパターニングする。

#### 【0103】

上記コンタクトホール34～38の内部にはプラグを形成してもよい。この場合は、まず、コンタクトホール34～38の内部および酸化シリコン膜33の上部にスパッタリング法またはCVD法で窒化チタン膜を堆積し、続いて窒化チタン膜の上部にCVD法でタングステン膜を堆積した後、化学機械研磨法で酸化シリコン膜33の上部のタングステン膜および窒化チタン膜を除去することによって、コンタクトホール34～38の内部にプラグを形成する。次に、酸化シリコン膜33の上部にスパッタリング法でタングステン膜を堆積し、フォトレジスト膜をマスクにしたドライエッティングでタングステン膜をパターニングすることによって、第1層目の配線41～47を形成する。

10

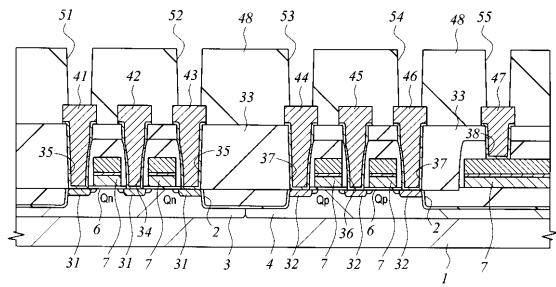

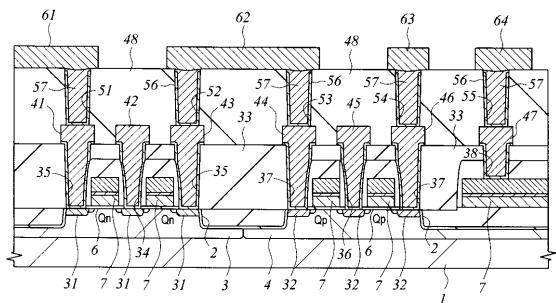

#### 【0104】

次に、図24に示すように、酸化シリコン膜33の上部にCVD法で酸化シリコン膜48を堆積し、続いて酸化シリコン膜48の表面を化学機械研磨法で平坦化した後、フォトレジスト膜(図示せず)をマスクにして酸化シリコン膜48をドライエッティングすることにより、第1層目の配線41、43、44、46、47の上部にスルーホール51～55を形成する。

#### 【0105】

次に、図25に示すように、スルーホール51～55の内部および酸化シリコン膜48の上部にバリアメタル膜56を形成する。このバリアメタル膜56は、次の工程でスルーホール51～55の内部に形成されるプラグと酸化シリコン膜48との接着力を向上させるための接着層であり、例えばスパッタリング法またはCVD法で堆積した窒化チタン膜からなる。

20

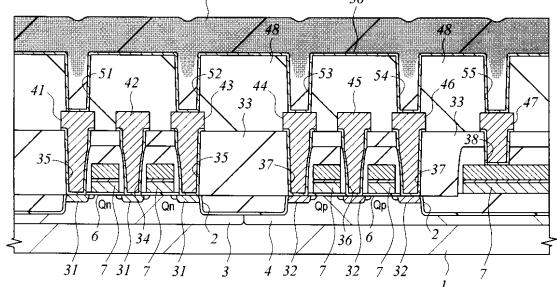

#### 【0106】

次に、図26に示すように、バリアメタル膜56の上部にポジ型のフォトレジスト膜40をスピニ塗布した後、図27に示すように、フォトレジスト膜40の全面に露光光を照射する。このとき、スルーホール51～55の外部やスルーホール51～55の開孔端近傍のフォトレジスト膜40は露光されるが、スルーホール51～55の内部のフォトレジスト膜40は露光量が不足するので露光されない。

30

#### 【0107】

次に、図28に示すように、フォトレジスト膜40を現像して露光部を除去し、スルーホール51～55の内部に未露光のフォトレジスト膜40を残した後、図29に示すように、スルーホール51～55の外部のバリアメタル膜56をドライエッティングで除去する。このとき、スルーホール51～55の内部のバリアメタル膜56は、その表面がフォトレジスト膜40で覆われているので、除去されずに残る。バリアメタル膜56のエッティングは、フォトレジスト膜40に対するバリアメタル膜56のエッティング選択比が十分に大きくなる条件で行い、スルーホール51～55の内部のフォトレジスト膜40で覆われたバリアメタル膜56が露出して削られないようにする。

#### 【0108】

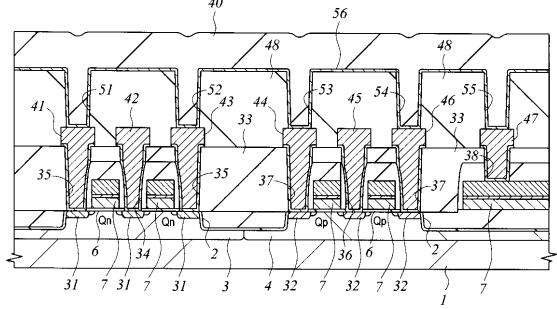

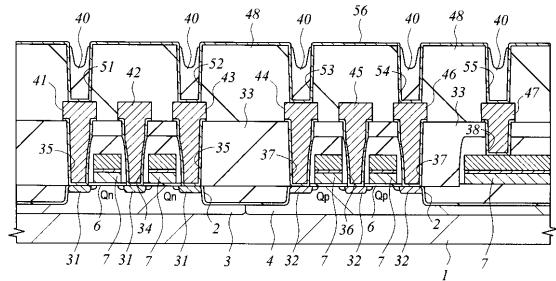

次に、図30に示すように、スルーホール51～55の内部に残ったフォトレジスト膜40をオゾンアッシング法などを用いて除去した後、図31に示すように、スルーホール51～55の内部に露出したバリアメタル膜56の表面に選択CVD法などを用いてタングステン膜57を成長させる。このタングステン膜57は、前記第1層目の配線41、43、44、46、47と次の工程で酸化シリコン膜48の上部に形成される第2層目の配線とを電気的に接続するプラグ材料として使用される。

40

#### 【0109】

次に、図32に示すように、スルーホール51～55の外部に露出したタングステン膜57をドライエッティング(または化学機械研磨法で研磨)してその表面の高さを酸化シリコン膜48の表面の高さとほぼ同じにした後、図33に示すように、酸化シリコン膜48の

50

上部に第2層目の配線61～64を形成する。配線61～64を形成するには、例えば酸化シリコン膜48の上部にスパッタリング法でタンゲステン膜を堆積した後、フォトレジスト膜をマスクにしたドライエッチングでタンゲステン膜をパターニングする。

【0110】

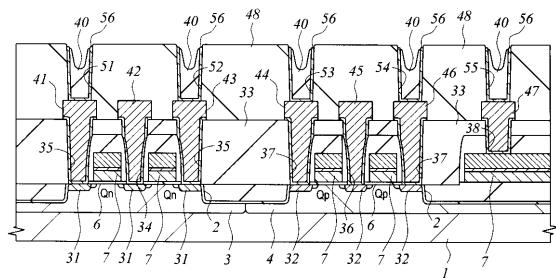

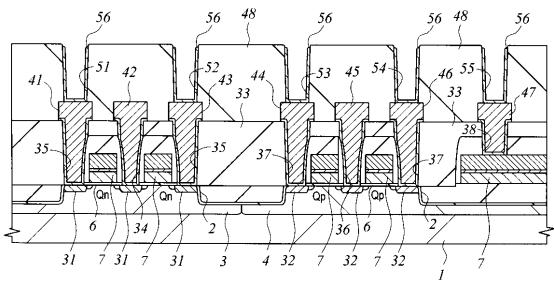

(実施の形態4)

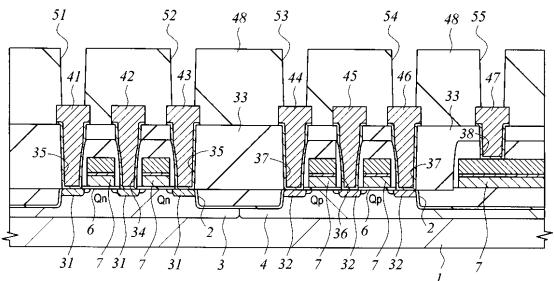

本発明の実施形態4であるプラグの形成方法を図34～図39を用いて工程順に説明する。

【0111】

まず、図34に示すように、前記実施の形態3と同様の方法でnチャネル型MISFET Qnおよびpチャネル型MISFET Qpの上部に第1層目の配線41～47を形成し、

続いて第1層目の配線41～47の上部に堆積した酸化シリコン膜48をドライエッチングしてスルーホール51～55を形成する。

10

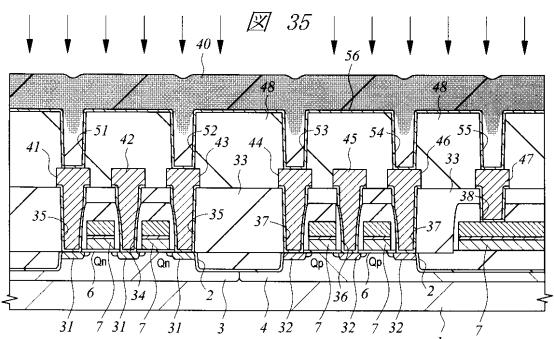

【0112】

次に、図35に示すように、スルーホール51～55の内部および酸化シリコン膜48の上部に接着層となるバリアメタル膜56を形成した後、バリアメタル膜56の上部にスピニ塗布したポジ型のフォトレジスト膜40を全面露光する。このとき、酸化シリコン膜48の上部およびスルーホール51～55の上部のフォトレジスト膜40は露光されるが、露光量が不足するスルーホール51～55の内部のフォトレジスト膜40は露光されない。

。

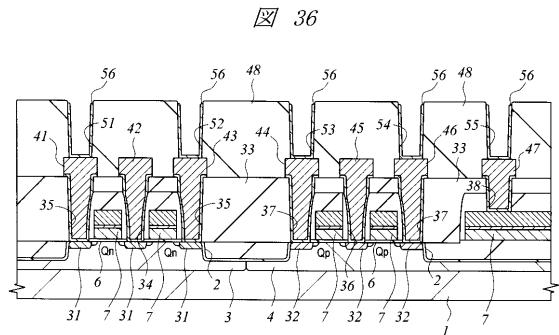

【0113】

次に、フォトレジスト膜40を現像して露光部を除去し、スルーホール51～55の内部に未露光のフォトレジスト膜40を残した後、図36に示すように、フォトレジスト膜40で覆われていない酸化シリコン膜48の上部のバリアメタル膜56をドライエッチングで除去し、さらにスルーホール51～55の内部に残ったフォトレジスト膜40をオゾンアッシング法などを用いて除去する。

20

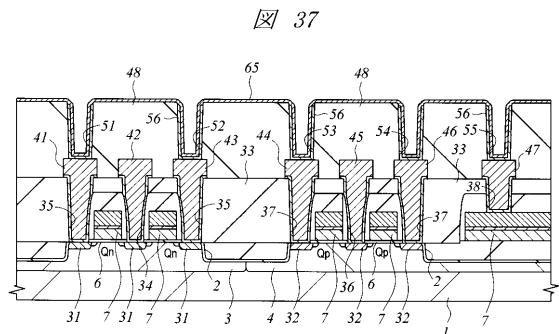

【0114】

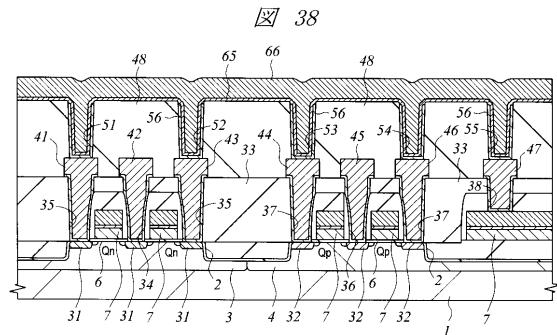

次に、図37に示すように、スルーホール51～55の内部および酸化シリコン膜48の上部にシード層65を形成する。このシード層65は、次の工程でスルーホール51～55の内部に形成されるプラグの下地層となるもので、例えばスパッタリング法で堆積した銅(Cu)膜からなる。

30

【0115】

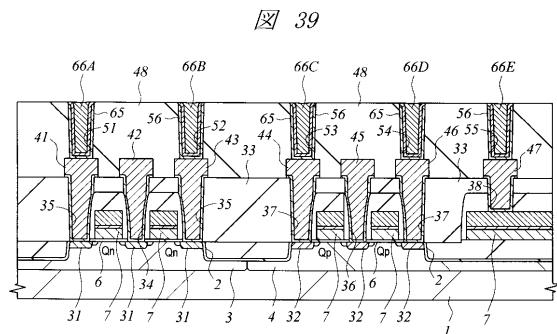

次に、図38に示すように、シード層65の表面に無電解メッキ法または蒸着法を用いて銅膜66を堆積した後、図39に示すように、スルーホール51～55の外部の銅膜66およびシード層65を化学機械研磨法で除去することにより、スルーホール51～55の内部に銅膜66およびシード層65からなるプラグ66A～66Eを形成する。

【0116】

一般に、銅は酸化シリコン膜中に拡散し易いという性質や、酸化シリコン膜に対する接着力が弱いという性質がある。そのため、酸化シリコン膜に形成した溝やスルーホールの内部に銅のプラグや配線を形成する場合は、銅膜と酸化シリコン膜との間に銅の拡散を抑制し、かつ酸化シリコンに対する接着力が大きい窒化チタン膜などのバリアメタル膜を設ける必要がある。

40

【0117】

このような理由から、化学機械研磨法を使った銅プラグや銅配線の形成工程では、溝やスルーホールの外部の酸化シリコン膜上に形成された銅膜や銅のシード層を研磨・除去した後、さらにその下層の銅とは材質が異なるバリアメタル膜を研磨・除去しなければならないので、化学機械研磨工程が煩雑になる。

【0118】

これに対し、上記した本実施の形態の銅プラグ形成方法によれば、化学機械研磨工程に先立ってスルーホール51～55の外部のバリアメタル膜56をドライエッチングで除去し、その後、銅膜66およびこれと同じ材質からなるシード層65を研磨・除去するので、

50

化学機械研磨工程が簡略になる。なお、銅の拡散を防ぐバリアメタル膜は、窒化チタン膜の他、窒化タンタル（TaN）膜、窒化タンゲステン（WN）膜などで構成することもできる。

【0119】

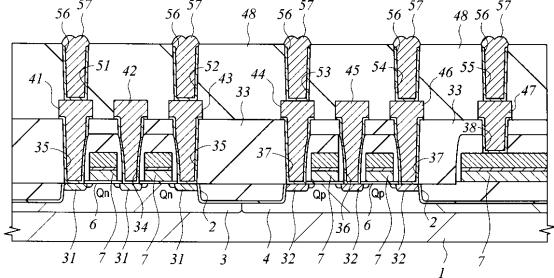

（実施の形態5）

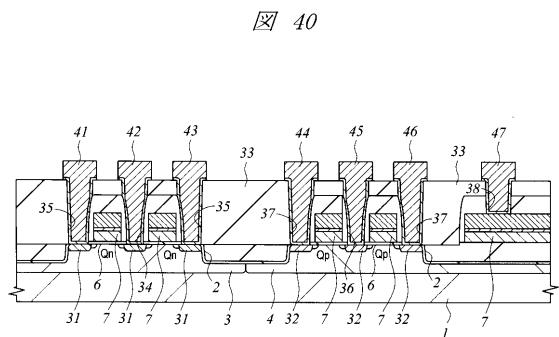

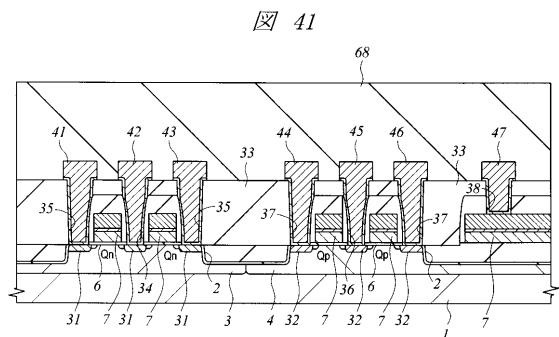

本発明の実施形態5であるデュアルダマシン方式を用いた埋込み銅配線の形成方法を図40～図49を用いて工程順に説明する。

【0120】

まず、図40に示すように、前記実施の形態3、4と同様の方法でnチャネル型MISFETQnおよびpチャネル型MISFETTpを形成し、続いてそれらの上部に第1層目の配線41～47を形成した後、図41に示すように、第1層目の配線41～47の上部にCVD法で酸化シリコン膜68を堆積する。10

【0121】

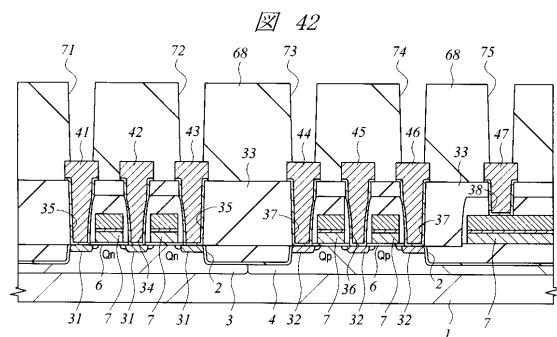

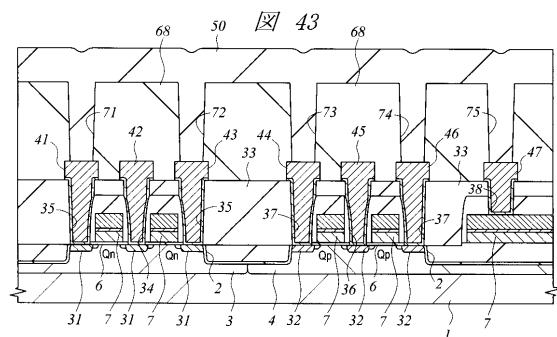

次に、図42に示すように、フォトレジスト膜（図示せず）をマスクにしたドライエッティングで配線41、43、44、46、47の上部の酸化シリコン膜68にスルーホール71～75を形成した後、図43に示すように、スルーホール71～75の内部および酸化シリコン膜68の上部にポジ型のフォトレジスト膜50をスピンドル塗布する。

【0122】

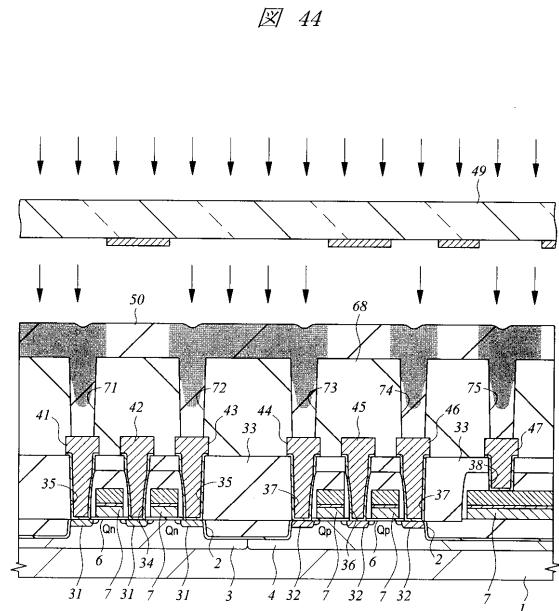

次に、図44に示すように、フォトマスク49を通して配線形成領域のフォトレジスト膜50に選択的に露光光を照射する。このとき、スルーホール71～75の内部のフォトレジスト膜50は、スルーホール71～75の途中までは露光されるが、途中よりも下方は露光量が不足するために露光されない。20

【0123】

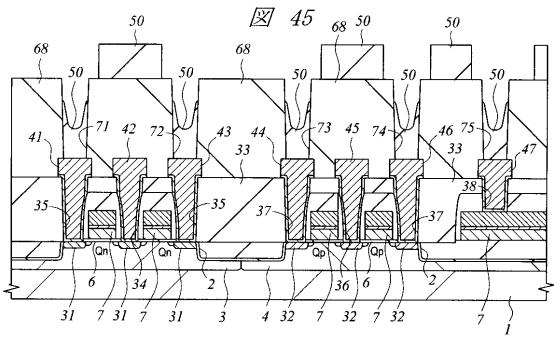

次に、図45に示すように、フォトレジスト膜50を現像して露光部を除去し、未露光のフォトレジスト膜50を残す。このとき、スルーホール71～75の内部は、途中よりも上のフォトレジスト膜50のみが除去されるので、途中よりも下方にフォトレジスト膜50が残った状態となる。

【0124】

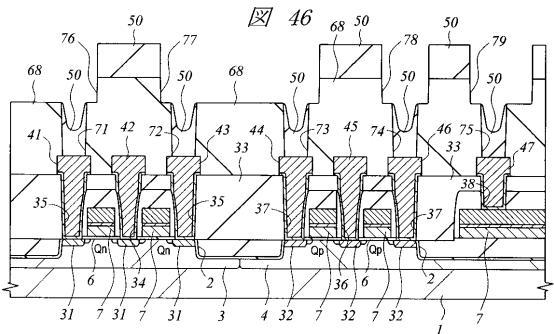

次に、図46に示すように、フォトレジスト膜50をマスクにして配線形成領域の酸化シリコン膜68をドライエッティングすることによって、配線溝76～79を形成する。酸化シリコン膜68のエッティングは、フォトレジスト膜50に対する比べて酸化シリコン膜68のエッティング選択比が十分に大きくなる条件で行い、スルーホール71～75の内部のフォトレジスト膜50が配線溝76～79の底部に露出した時点でエッティングを停止する。30

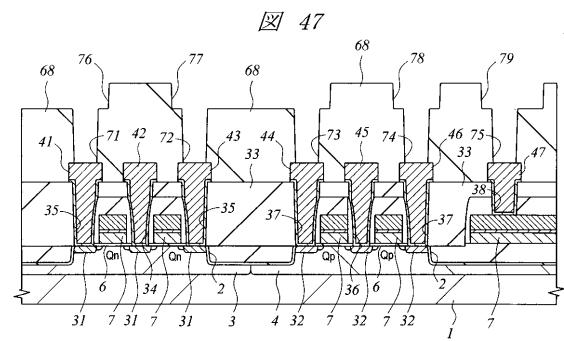

【0125】

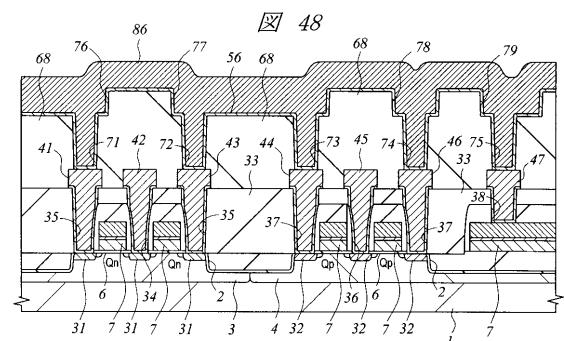

次に、図47に示すように、スルーホール71～75の内部に残ったフォトレジスト膜50をオゾンアッシング法などを用いて除去した後、図48に示すように、配線溝76～79およびその下部のスルーホール71～75の内部に接着層となるバリアメタル膜56を形成した後、バリアメタル膜56の上部に銅膜86を堆積する。バリアメタル膜56は、例えばCVD法で堆積した窒化チタン膜からなる。また、銅膜86は、スパッタリング法などを用いて堆積する。40

【0126】

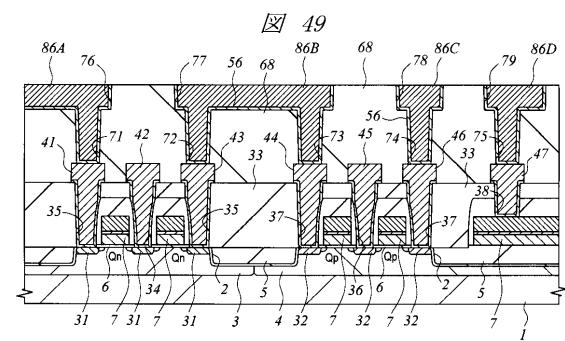

次に、図49に示すように、配線溝76～79の外部の銅膜86およびバリアメタル膜56を化学機械研磨法で除去することによって、配線溝76～79の内部およびその下部のスルーホール71～75の内部に埋込み銅配線86A～86Dを形成する。

【0127】

通常、配線溝およびその下部のスルーホールに同時に埋込み配線を形成するデュアルダマシン・プロセスでは、酸化シリコン膜に配線溝とスルーホールとを形成する際、配線溝とスルーホールとの境界部にエッティングストップとなる絶縁膜（例えば窒化シリコン膜）を形成することによって配線溝の深さを規定する。すなわち、第1酸化シリコン膜の上部に50

窒化シリコン膜を挟んで第2酸化シリコン膜を堆積し、続いて第2酸化シリコン膜、窒化シリコン膜および第1酸化シリコン膜をドライエッチングしてスルーホールを形成した後、窒化シリコン膜をエッチングストップにしてその上部の第2酸化シリコン膜をドライエッチングする。これにより、第2酸化シリコン膜に配線溝が形成され、その下部の窒化シリコン膜および第1酸化シリコン膜にスルーホールが残る。しかし、このようなデュアルダマシン・プロセスは、1層の埋込み配線を形成するのに3層の絶縁膜（第1酸化シリコン膜、窒化シリコン膜および第2酸化シリコン膜）を必要とするので、工程が増加するという問題がある。また、酸化シリコン膜よりも誘電率が高い窒化シリコン膜を含んだ絶縁膜に埋込み銅配線を形成すると、その寄生容量が増加するという問題もある。

## 【0128】

10

これに対し、スルーホール71～75の内部に埋め込んだフォトトレジスト膜50をエッチングストップにして配線溝76～79を形成する本実施の形態によれば、一層の酸化シリコン膜68にスルーホール71～75および配線溝76～79を形成するので、デュアルダマシン・プロセスの工程を短縮することができる。また、誘電率が高い絶縁膜（窒化シリコン膜）をエッチングストップに使用しないので、埋込み銅配線86A～86Eの寄生容量を低減することもできる。

## 【0129】

## (実施の形態6)

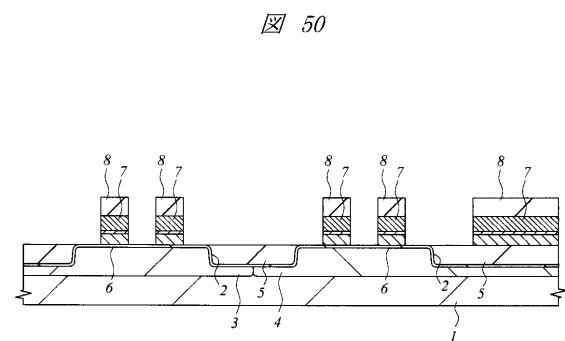

本発明の実施形態6であるセルフアライン・コンタクトホールの形成方法を図50～図58を用いて工程順に説明する。

20

## 【0130】

まず、図50に示すように、基板1の正面に酸化シリコン膜5を埋め込んだ素子分離2、p型ウエル3およびn型ウエル4を形成し、続いてp型ウエル3およびn型ウエル4の表面にゲート酸化膜6を形成した後、ゲート酸化膜6の上部にゲート電極7を形成する。ゲート電極7を形成するには、例えば基板1上にリンなどのn型不純物をドープした多結晶シリコン膜をCVD法で堆積し、続いてその上部にスピッタリング法で窒化タンゲステン膜およびタンゲステン膜を堆積し、さらにその上部にCVD法で窒化シリコン膜8を堆積した後、フォトトレジスト膜をマスクにしたドライエッチングでこれらの膜をパターニングする。ゲート電極7の上部の窒化シリコン膜8は、後述するコンタクトホールをゲート電極7に対して自己整合（セルフアライン）で形成するために必要な絶縁膜である。

30

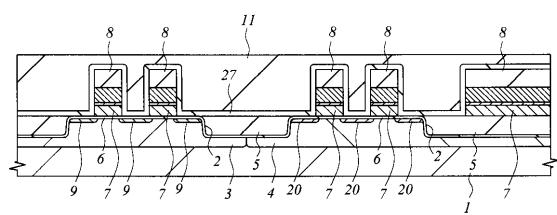

## 【0131】

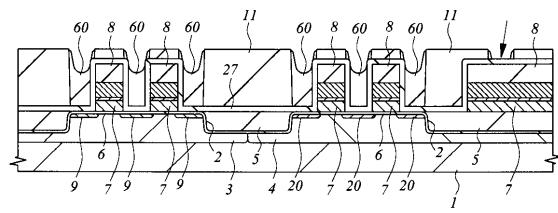

次に、図51に示すように、p型ウエル3にリンなどのn型不純物をイオン注入してn<sup>-</sup>型半導体領域9を形成し、n型ウエル4にp型不純物（ホウ素）をイオン注入してp<sup>-</sup>型半導体領域20を形成した後、ゲート電極7の上部にCVD法で窒化シリコン膜27および酸化シリコン膜11を堆積し、続いて酸化シリコン膜11の表面を化学機械研磨法で平坦化する。窒化シリコン膜27は、後述するコンタクトホールを素子分離溝2に対して自己整合で形成するために必要な絶縁膜である。

## 【0132】

コンタクトホールをゲート電極7および素子分離溝2に対してそれぞれ自己整合で形成する場合は、上記のようにゲート電極7の上部に窒化シリコン膜8を形成し、さらに素子分離溝2の上部に窒化シリコン膜27を形成する。そのため、ここまで工程で拡散層（n<sup>-</sup>型半導体領域9、p<sup>-</sup>型半導体領域20）および素子分離溝2は1層の窒化シリコン膜27で覆われ、ゲート電極7は2層の窒化シリコン膜8、27で覆われる。

40

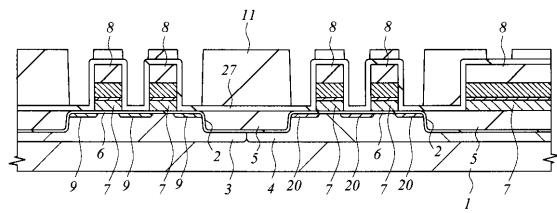

## 【0133】

次に、図52に示すように、フォトトレジスト膜（図示せず）をマスクにして拡散層（n<sup>-</sup>型半導体領域9、p<sup>-</sup>型半導体領域20）の上部の酸化シリコン膜11をドライエッチングする。またこのとき同時に、ゲート電極7の上部の酸化シリコン膜11をドライエッチングする。酸化シリコン膜11のエッチングは、窒化シリコン膜27に対する酸化シリコン膜11のエッチング選択比が大きくなる条件で行い、下層の窒化シリコン膜27が除去されないようにする。

50

## 【0134】

窒化シリコン膜27をエッティングストップにしてその上部の酸化シリコン膜11をドライエッティングすると、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部には1層の窒化シリコン膜27が残り、ゲート電極7の上部には2層の窒化シリコン膜8、27が残る。そのため、次の工程で拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部の1層の窒化シリコン膜27をドライエッティングしてそれらの上部にコンタクトホールを形成する際、同時にゲート電極7の上部の2層の窒化シリコン膜8、27をドライエッティングしてその上部にコンタクトホールを形成しようとすると、基板1および素子分離溝2内の酸化シリコン膜5が深く削れてしまい、リーク電流の増加といった素子特性の劣化を引き起こす。従って、基板1や酸化シリコン膜5の過剰な削れを防ぐためには、ゲート電極7の上部の窒化シリコン膜8、27のエッティングと、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部の窒化シリコン膜27のエッティングとを別工程で行う必要があり、フォトマスクが2枚必要となる。

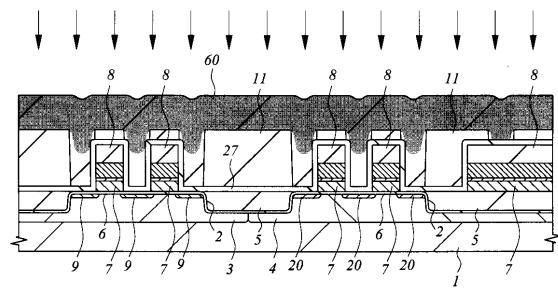

## 【0135】

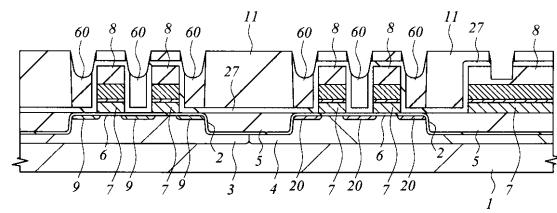

そこで本実施の形態では、窒化シリコン膜27をエッティングストップにしてその上部の酸化シリコン膜11をドライエッティングした後、図53に示すように、酸化シリコン膜11の上部にポジ型のフォトレジスト膜60をスピンドル塗布し、続いてフォトレジスト膜60の全面に露光光を照射する。このとき、ゲート電極7の上方のフォトレジスト膜60は、その膜厚が薄いために露光されるが、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上方のフォトレジスト膜60は、その膜厚が厚いために途中までしか露光されない。

## 【0136】

次に、図54に示すように、フォトレジスト膜60を現像して露光部を除去する。このとき、ゲート電極7の上部(図の矢印で示す箇所)は、フォトレジスト膜60が除去されて窒化シリコン膜27が露出するが、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部は、未露光のフォトレジスト膜60が残るので窒化シリコン膜27は露出しない。

## 【0137】

次に、図55に示すように、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部のフォトレジスト膜60をマスクにしてゲート電極7の上部の窒化シリコン膜27、8をドライエッティングする。このエッティングは、酸化シリコン膜11に対する窒化シリコン膜27、8のエッティング選択比が十分に大きくなる条件で行い、ゲート電極7を覆う窒化シリコン膜8の膜厚が拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)を覆う窒化シリコン膜27の膜厚とほぼ同じになった時点でエッティングを停止する。

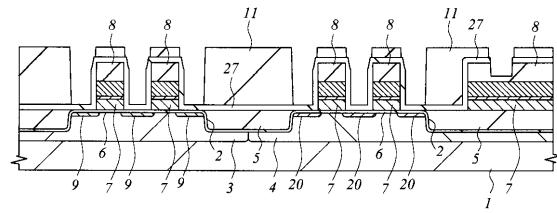

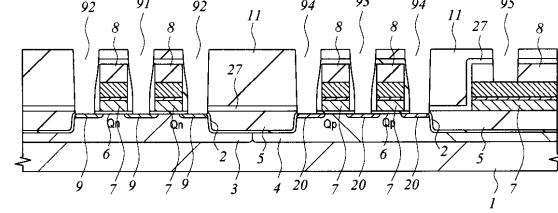

## 【0138】

次に、図56に示すように、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部に残ったフォトレジスト膜60をオゾンアッシング法で除去した後、図57に示すように、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)を覆う窒化シリコン膜27とゲート電極7を覆う窒化シリコン膜8とをドライエッティングで除去することにより、 $n^-$ 型半導体領域9の上部にコンタクトホール91、92を形成し、 $p^-$ 型半導体領域20の上部にコンタクトホール93、94を形成し、ゲート電極7の上部にコンタクトホール95を形成する。窒化シリコン膜8、27のエッティングは、それらを異方的にエッティングする条件で行い、ゲート電極7の側壁に窒化シリコン膜27を残すようとする。

## 【0139】

上記した窒化シリコン膜8、27のエッティングは、拡散層( $n^-$ 型半導体領域9、 $p^-$ 型半導体領域20)の上部の窒化シリコン膜27とゲート電極7の上部の窒化シリコン膜8とをほぼ同じ膜厚にしてから行うため、それらを同時にエッティングしても素子分離溝2内の酸化シリコン膜5や基板1が深く削られることはない。

## 【0140】

このように、本実施形態6によれば、コンタクトホール91～94をゲート電極7および素子分離溝2に対して自己整合で形成する際、ゲート電極7の上部のコンタクトホール9

10

20

30

40

50

5を同時に形成することができるので、コンタクトホール91～95を形成するためのフォトマスクが1枚で済む。

#### 【0141】

次に、図58に示すように、コンタクトホール91、92を通じてp型ウエル3にn型不純物（リンまたはヒ素）をイオン注入してn<sup>+</sup>型半導体領域（ソース、ドレイン）31を形成することにより、nチャネル型MISFETQnを形成する。また、コンタクトホール93、94を通じてn型ウエル4にp型不純物（ホウ素）をイオン注入してp<sup>+</sup>型半導体領域（ソース、ドレイン）32を形成することにより、pチャネル型MISFETTpを形成する。その後、前記実施の形態3～5と同様の方法で酸化シリコン膜11の上部に第1層目の配線41～47を形成する。

10

#### 【0142】

以上、本発明者によってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

#### 【0143】

##### 【発明の効果】

本願によって開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下の通りである。

#### 【0144】

(1) 本発明によれば、絶縁膜に形成された溝の内部に下部電極を形成する情報蓄積用容量素子を備えたDRAMの信頼性、製造歩留まりを向上させることができる。

20

#### 【0145】

(2) 本発明によれば、絶縁膜に形成した溝またはスルーホールの内部に歩留まりよく導電層を形成することができる。

#### 【0146】

(3) 本発明によれば、絶縁膜に形成した溝またはスルーホールの内部に少ない工程で導電層を形成することができる。

##### 【図面の簡単な説明】

【図1】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

30

【図2】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図3】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図4】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図5】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図6】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

40

【図7】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図8】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図9】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図10】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図11】本発明の実施の形態1である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

50

【図37】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図38】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図39】本発明の実施の形態4である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図40】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図41】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。 10

【図42】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図43】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図44】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。 20

【図45】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図46】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。 20

【図47】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図48】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図49】本発明の実施の形態5である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図50】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。 30

【図51】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図52】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。 30

【図53】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図54】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図55】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。 40

【図56】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図57】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

【図58】本発明の実施の形態6である半導体集積回路装置の製造方法を示す半導体基板の要部断面図である。

#### 【符号の説明】

- 1 半導体基板

- 2 素子分離溝

- 3 p型ウエル

- 4 n型ウエル

- 5 酸化シリコン膜

10

20

30

40

50

|             |                    |    |

|-------------|--------------------|----|

| 6           | ゲート酸化膜             |    |

| 7           | ゲート電極              |    |

| 8           | 窒化シリコン膜            |    |

| 9           | n⁻型半導体領域           |    |

| 10          | 窒化シリコン膜            |    |

| 11          | 酸化シリコン膜            |    |

| 12、13       | コンタクトホール           |    |

| 14          | n⁺型半導体領域           | 10 |

| 15          | プラグ                |    |

| 16          | 酸化シリコン膜            |    |

| 17          | スルーホール             |    |

| 18          | プラグ                |    |

| 19          | 酸化シリコン膜            |    |

| 20          | p⁻型半導体領域           |    |

| 21          | スルーホール             |    |

| 22          | プラグ                |    |

| 23          | 窒化シリコン膜            |    |

| 24          | 酸化シリコン膜            |    |

| 25          | 溝                  |    |

| 26 A        | アモルファスシリコン膜        | 20 |

| 26          | 多結晶シリコン膜           |    |

| 27          | 窒化シリコン膜            |    |

| 28          | 酸化タンタル膜            |    |

| 29          | 窒化チタン膜             |    |

| 30          | フォトレジスト膜           |    |

| 31          | n⁺型半導体領域（ソース、ドレイン） |    |

| 32          | p⁺型半導体領域（ソース、ドレイン） |    |

| 33          | 酸化シリコン膜            |    |

| 34 ~ 38     | コンタクトホール           |    |

| 40          | フォトレジスト膜           | 30 |

| 41 ~ 47     | 配線                 |    |

| 48          | 酸化シリコン膜            |    |

| 49          | フォトマスク             |    |

| 50          | フォトレジスト膜           |    |

| 51 ~ 55     | スルーホール             |    |

| 56          | バリアメタル膜            |    |

| 57          | タンクステン膜            |    |

| 60          | フォトレジスト膜           |    |

| 61 ~ 64     | 配線                 |    |

| 65          | シード層               | 40 |

| 66          | 銅膜                 |    |

| 66 A ~ 66 E | プラグ                |    |

| 68          | 酸化シリコン膜            |    |

| 71 ~ 75     | スルーホール             |    |

| 76 ~ 79     | 配線溝                |    |

| 86          | 銅膜                 |    |

| 86 A ~ 86 D | 埋込み銅配線             |    |

| 91 ~ 95     | コンタクトホール           |    |

| B L         | ビット線               |    |

| C           | 情報蓄積用容量素子          | 50 |

Qn nチャネル型MISFET

Qp pチャネ尔型MISFET

Qs メモリセル選択用MISFET

WL ワード線

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

【図6】

図6

【図7】

図7

【図8】

図8

【 図 9 】

【 図 1 0 】

【 図 1 1 】

【図12】

【図13】

図13

【図14】

図14

【図15】

図15

【図16】

図16

【図17】

図17

【図18】

図18

【図19】

図19

【図20】

図20

【 図 2 1 】

【 図 2 2 】

【 図 2 3 】

【図24】

【図26】

【図25】

【 図 27 】

【 図 2 8 】

【図29】

【図32】

【図33】

【図30】

【 図 3 1 】

【図34】

【図35】

【 図 3 6 】

【図37】

【図40】

【図41】

【 図 3 8 】

【図39】

【図42】

【図43】

【図44】

【図45】

【図46】

【図47】

【図49】

【図48】

【図50】

【図 5 1】

図 51

【図 5 2】

図 52

【図 5 3】

図 53

【図 5 4】

図 54

【図 5 5】

図 55

【図 5 6】

図 56

【図 5 7】

図 57

【図 5 8】

図 58

---

フロントページの続き

(72)発明者 斎藤 康一

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 山本 裕彦

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 吉田 正義

東京都小平市上水本町五丁目20番1号 株式会社日立製作所 半導体グループ内

(72)発明者 石坂 正行

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

(72)発明者 下田 真岐

東京都小平市上水本町5丁目22番1号 株式会社日立超エル・エス・アイ・システムズ内

審査官 長谷山 健

(56)参考文献 特開2000-307078(JP,A)

特開2000-323677(JP,A)

特開2000-058647(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/768

H01L 21/28

H01L 21/8242

H01L 27/108