(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년01월26일

(11) 등록번호 10-1700008

(24) 등록일자 2017년01월19일

- (51) 국제특허분류(Int. Cl.)

H03F 1/32 (2006.01) H03F 3/24 (2006.01)

- (21) 출원번호 10-2014-0027230

(22) 출원일자 2014년03월07일

심사청구일자 2014년03월07일

(65) 공개번호 10-2014-0113378

(43) 공개일자 2014년09월24일

(30) 우선권주장

13/803,797 2013년03월14일 미국(US)

- (56) 선행기술조사문헌

JP2005217714 A\*

US06998909 B1\*

\*는 심사관에 의하여 인용된 문헌

전체 청구항 수 : 총 20 항

심사관 : 성경아

(54) 발명의 명칭 베이스밴드 디지털 전치 왜곡 아키텍처

**(57) 요약**

증폭기는 전치 왜곡 신호를 생성하기 위해 입력 신호를 수신하는 전치 왜곡기, 전치 증폭된 신호를 생성하기 위해 전치 왜곡 신호를 수신하는 제 1 변환기, 전치 증폭된 신호 및 입력 신호에 기초하여 출력 신호를 생성하기 위해 전치 증폭된 신호를 수신하는 전력 증폭기, 및 피드백 신호를 생성하기 위해 출력 신호를 샘플링하는 제 2 변환기를 포함할 수 있다. 전치 왜곡기는 동위상 입력 신호에 대한 전치 왜곡 신호 성분 및 직교 입력 신호에 대한 전치 왜곡 신호 성분을 개별적으로 그리고 독립적으로 생성한다.

**대표도**

## 명세서

### 청구범위

#### 청구항 1

증폭기로서,

입력 신호를 수신하는 전치 왜곡기;

전치 증폭된 신호를 생성하기 위해 상기 전치 왜곡기의 출력을 수신하는 제 1 변환기;

상기 전치 증폭된 신호에 기초하여 출력 신호를 생성하기 위해 상기 전치 증폭된 신호를 수신하는 전력 증폭기;

및

피드백 신호를 생성하기 위해 상기 출력 신호를 샘플링하는 제 2 변환기를 포함하며;

상기 전치 왜곡기는 상기 입력 신호 및 상기 피드백 신호의 동위상 성분에 기초하여, 상기 입력 신호의 동위상 성분에 상응하는 상기 전치 왜곡 신호의 제 1 성분을 도입하고,

상기 전치 왜곡기는 상기 입력 신호 및 상기 피드백 신호의 직교 성분에 기초하여, 상기 입력 신호의 직교 성분에 상응하는 상기 전치 왜곡 신호의 제 2 성분을 도입하고,

상기 전치 왜곡기는, 상기 동위상 성분에 대한 제1 계수(coefficient) 세트와 상기 직교 성분에 대한 제2 계수 세트를 포함하는 개별적이고 독립적인 두 계수 세트들을 계산함으로써, 그리고 상기 제1 계수 세트를 상기 동위상 성분에 그리고 상기 제2 계수 세트를 상기 직교 성분에 개별적으로 그리고 독립적으로 적용함으로써, 상기 동위상 성분 및 상기 직교 성분 내의 비선형성을 보상하고, 상기 제1 계수 세트와 상기 제2 계수 세트는 서로 상이한 것인 증폭기.

#### 청구항 2

청구항 1에 있어서, 상기 제 1 변환기는 디지털-아날로그 변환기를 포함하고, 상기 제 2 변환기는 아날로그-디지털 변환기를 포함하는 증폭기.

#### 청구항 3

청구항 1에 있어서, 상기 전치 왜곡기는 제 1 필터 및 제 2 필터를 포함하는 증폭기.

#### 청구항 4

청구항 3에 있어서, 상기 제 1 필터는 상기 전치 왜곡 신호의 제 1 성분을 생성하기 위해 상기 입력 신호 및 상기 피드백 신호의 동위상 성분을 수신하는 증폭기.

#### 청구항 5

청구항 3에 있어서, 상기 제 2 필터는 상기 전치 왜곡 신호의 제 2 성분을 생성하기 위해 상기 입력 신호 및 상기 피드백 신호의 직교 성분을 수신하는 증폭기.

#### 청구항 6

청구항 3에 있어서, 상기 전치 왜곡기는 제 1 복조기, 제 2 복조기, 및 변조기를 더 포함하는 증폭기.

#### 청구항 7

청구항 6에 있어서, 상기 제 1 복조기는 상기 입력 신호를 상기 입력 신호의 동위상 성분 및 직교 성분으로 분할하고,

상기 제 2 복조기는 상기 피드백 신호를 상기 피드백 신호의 동위상 성분 및 직교 성분으로 분할하며,

상기 변조기는 전치 왜곡 신호를 생성하기 위해 상기 전치 왜곡 신호의 제 1 성분 및 제 2 성분을 결합하는 증

폭기.

### 청구항 8

전력 증폭기 내의 비선형성을 보상하는 방법으로서,

제 1 변환기에 의해, 전치 왜곡 신호에 기초하여 전치 증폭된 신호를 생성하는 단계;

전력 증폭기에 의해, 상기 전치 증폭된 신호 및 입력 신호에 기초하여 출력 신호를 생성하는 단계;

피드백 신호를 생성하기 위해, 제 2 변환기에 의해, 상기 출력 신호를 샘플링하는 단계; 및

전치 왜곡기에 의해, 상기 입력 신호에 기초하여 상기 전치 왜곡 신호를 생성하는 단계를 포함하며;

상기 전치 왜곡기는 상기 입력 신호 및 상기 피드백 신호의 동위상 성분에 기초하여, 상기 입력 신호의 동위상 성분에 상응하는 상기 전치 왜곡 신호의 제 1 성분을 도입하고,

상기 전치 왜곡기는 상기 입력 신호 및 상기 피드백 신호의 직교 성분에 기초하여, 상기 입력 신호의 직교 성분에 상응하는 상기 전치 왜곡 신호의 제 2 성분을 도입하고,

상기 동위상 성분 및 상기 직교 성분 내의 비선형성을 보상하기 위하여,

상기 동위상 성분에 대한 제1 계수(coefficient) 세트와 상기 직교 성분에 대한 제2 계수 세트를 포함하는 개별적이고 독립적인 두 계수 세트들을 계산하고; 및

상기 전치 왜곡기에 의해 개별적으로 그리고 독립적으로, 상기 제1 계수 세트를 상기 동위상 성분에 적용하고, 상기 제2 계수 세트를 상기 직교 성분에 적용하며, 상기 제1 계수 세트 및 상기 제2 계수 세트는 서로 상이한 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

### 청구항 9

청구항 8에 있어서, 상기 제 1 변환기는 디지털-아날로그 변환기를 포함하고, 상기 제 2 변환기는 아날로그-디지털 변환기를 포함하는 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

### 청구항 10

청구항 8에 있어서, 상기 전치 왜곡기는 제 1 필터 및 제 2 필터를 포함하는 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

### 청구항 11

청구항 10에 있어서, 상기 제 1 필터는 상기 전치 왜곡 신호의 제 1 성분을 생성하기 위해 상기 입력 신호 및 상기 피드백 신호의 동위상 성분을 수신하는 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

### 청구항 12

청구항 10에 있어서, 상기 제 2 필터는 상기 전치 왜곡 신호의 제 2 성분을 생성하기 위해 상기 입력 신호 및 상기 피드백 신호의 직교 성분을 수신하는 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

### 청구항 13

청구항 10에 있어서, 상기 전치 왜곡기는 제 1 복조기, 제 2 복조기, 및 변조기를 더 포함하는 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

### 청구항 14

청구항 13에 있어서, 상기 제 1 복조기는 상기 입력 신호를 상기 입력 신호의 동위상 성분 및 직교 성분으로 분할하고,

상기 제 2 복조기는 상기 피드백 신호를 상기 피드백 신호의 동위상 성분 및 직교 성분으로 분할하며,

상기 변조기는 전치 왜곡 신호를 생성하기 위해 상기 전치 왜곡 신호의 제 1 성분 및 제 2 성분을 결합하는 것인, 전력 증폭기 내의 비선형성을 보상하는 방법.

**청구항 15**

제 1 변환기에 의해, 전치 왜곡 신호에 기초하여 전치 증폭된 신호를 생성하는 단계;

전력 증폭기에 의해, 상기 전치 증폭된 신호 및 입력 신호에 기초하여 출력 신호를 생성하는 단계;

피드백 신호를 생성하기 위해, 제 2 변환기에 의해, 상기 출력 신호를 샘플링하는 단계; 및

전치 왜곡기에 의해, 상기 입력 신호에 기초하여 상기 전치 왜곡 신호를 생성하는 단계를 수행하도록 프로세서에 의해 실행가능한 컴퓨터 코드(computer code)를 포함하는 비일시적 컴퓨터 판독가능 매체로서;

상기 전치 왜곡기는 상기 입력 신호 및 상기 피드백 신호의 동위상 성분에 기초하여, 상기 입력 신호의 동위상 성분에 상응하는 상기 전치 왜곡 신호의 제 1 성분을 도입하고,

상기 전치 왜곡기는 상기 입력 신호 및 상기 피드백 신호의 직교 성분에 기초하여, 상기 입력 신호의 직교 성분에 상응하는 상기 전치 왜곡 신호의 제 2 성분을 도입하고,

상기 동위상 성분 및 상기 직교 성분 내의 비선형성을 보상하기 위하여,

상기 동위상 성분에 대한 제1 계수(coefficient) 세트와 상기 직교 성분에 대한 제2 계수 세트를 포함하는 개별적이고 독립적인 두 계수 세트들을 계산하고; 및

상기 전치 왜곡기에 의해 개별적으로 그리고 독립적으로, 상기 제1 계수 세트를 상기 동위상 성분에 적용하고, 상기 제2 계수 세트를 상기 직교 성분에 적용하며, 상기 제1 계수 세트 및 상기 제2 계수 세트는 서로 상이한 것인, 비일시적 컴퓨터 판독가능 매체.

**청구항 16**

청구항 15에 있어서, 상기 제 1 변환기는 디지털-아날로그 변환기를 포함하고, 상기 제 2 변환기는 아날로그-디지털 변환기를 포함하는 비일시적 컴퓨터 판독가능 매체.

**청구항 17**

청구항 15에 있어서, 상기 전치 왜곡기는 제 1 필터 및 제 2 필터를 포함하는 비일시적 컴퓨터 판독가능 매체.

**청구항 18**

청구항 17에 있어서, 상기 제 1 필터는 상기 전치 왜곡 신호의 제 1 성분을 생성하기 위해 상기 입력 신호 및 상기 피드백 신호의 동위상 성분을 수신하는 비일시적 컴퓨터 판독가능 매체.

**청구항 19**

청구항 17에 있어서, 상기 제 2 필터는 상기 전치 왜곡 신호의 제 2 성분을 생성하기 위해 상기 입력 신호 및 상기 피드백 신호의 직교 성분을 수신하는 비일시적 컴퓨터 판독가능 매체.

**청구항 20**

청구항 17에 있어서, 상기 전치 왜곡기는 제 1 복조기, 제 2 복조기, 및 변조기를 더 포함하는 비일시적 컴퓨터 판독가능 매체.

**발명의 설명****배경기술**

[0001] PA(Power amplifiers)는 무선 통신에 대한 브로드캐스트 장비와 같은 다양한 응용들에서 사용될 수 있다. 브로드캐스트 장비는 BTS(base transceiver station) 또는 UE(user equipment) 또는 LTE, WiMax, WiFi, CDMA, GSM, EDGE, 및 UMTS 표준들에서와 같은 무선 이동 통신 시설에 사용되는 다른 송수신기 장비에 포함될 수 있다.

[0002] 입력 신호들을 전력 증폭하는 전력 증폭기들은 입력 신호들의 선형 증폭인 출력 신호들을 이상적으로 생성할 수 있다. 그러나, 응용들 내의 전력 증폭기들은 전력 증폭기들 내의 비선형 특성들, 또는 비선형들로 인한 왜곡들을 가질 것이다. 출력 신호들에서 그러한 왜곡들을 감소시키기 위해, 전력 증폭기들 내의 비선형성들은 보상될

필요가 있을 수 있다.

[0003] 예를 들어, BTS 내의 전형적인 전력 증폭기는 BTS의 비용 및 전력 요구의 중요한 부분, 예를 들어 전체 전력 요구의 30% 및 비용의 30%를 나타낼 수 있다. 전형적인 전력 증폭기는 비선형성의 하나 이상의 구역을 가질 수 있고, 전형적인 전력 증폭기의 비선형 작용은 전력 공급, 온도, 개인 설정 등과 같은 다양한 요소들에 의해 영향을 받을 수 있다. 전력 증폭기 내의 비선형성은 무선 송신기 또는 수신기의 성능을 정량화하기 위해 사용되는 EVM(error vector magnitude)을 저하시키고, 왜곡들로 인한 신호 대역폭의 확산인 스펙트럼 재성장을 증가시킬 수 있다. 전형적으로, 출력 근처의 백엔드 구성요소들 내의 비선형성들, 즉 무선 주파수(RF) 왜곡들만이 보상을 위해 고려된다. 그러나, 비선형성들, 즉 베이스밴드 비선형 왜곡들은 프런트엔드 근처에 발생할 수도 있다. 프런트엔드 회로 경로들에서, 동위상 신호 경로 내의 비선형성은 직교 위상 신호 경로 내의 비선형성과 상이할 수 있다.

[0004] 따라서, 베이스밴드 비선형성을 보상하는 개선된 전력 증폭기들에 대한 요구가 있다.

### 도면의 간단한 설명

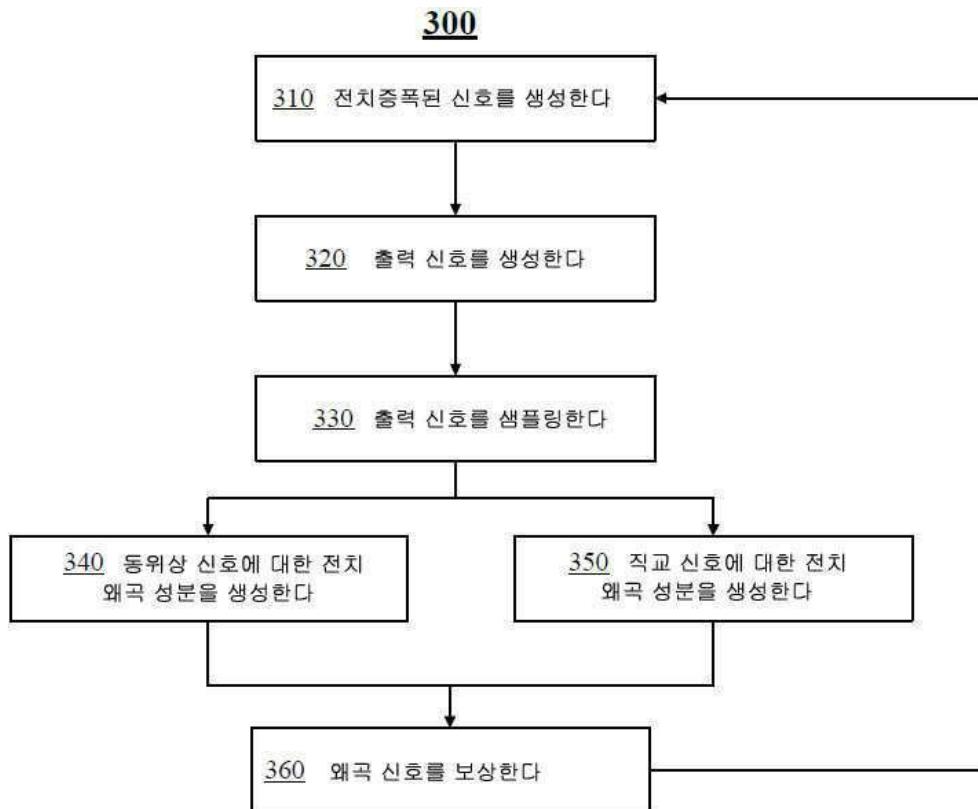

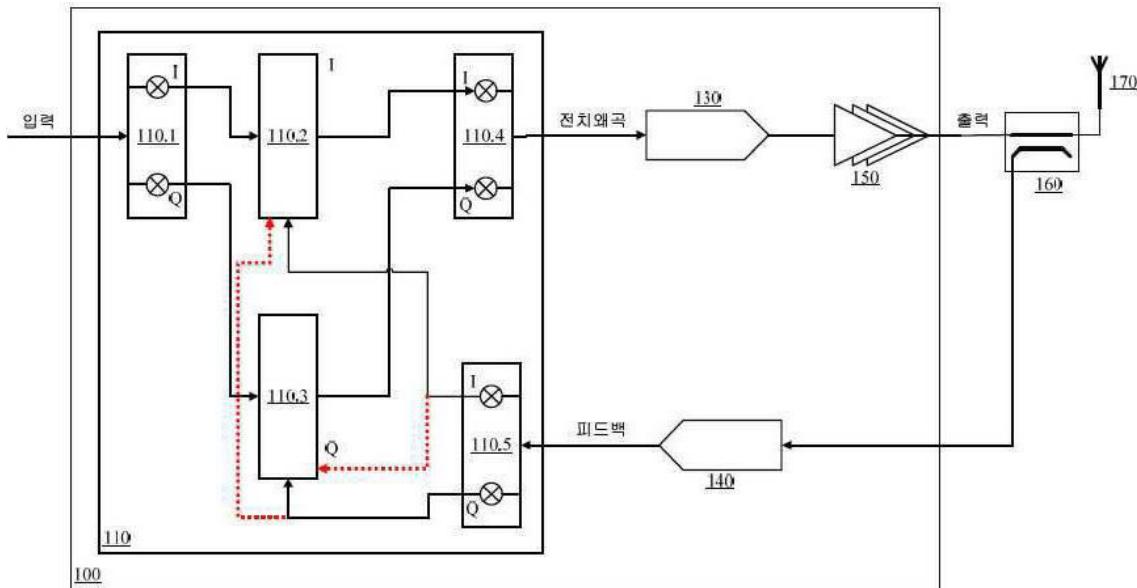

[0005] 도 1은 본 개시의 일 실시예에 따른 증폭기의 간략한 블록도를 예시한다.

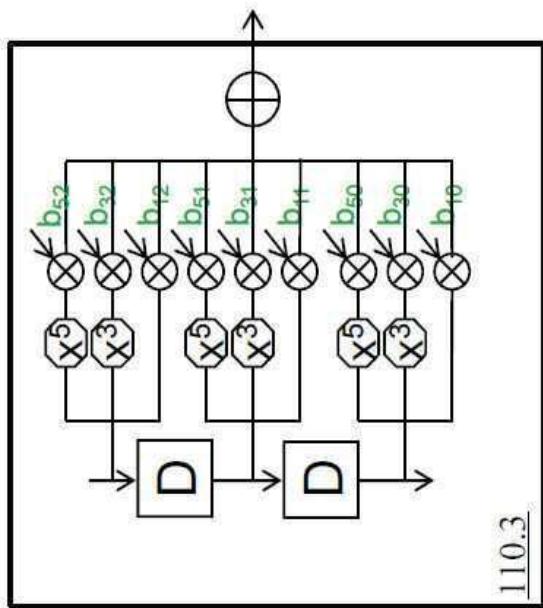

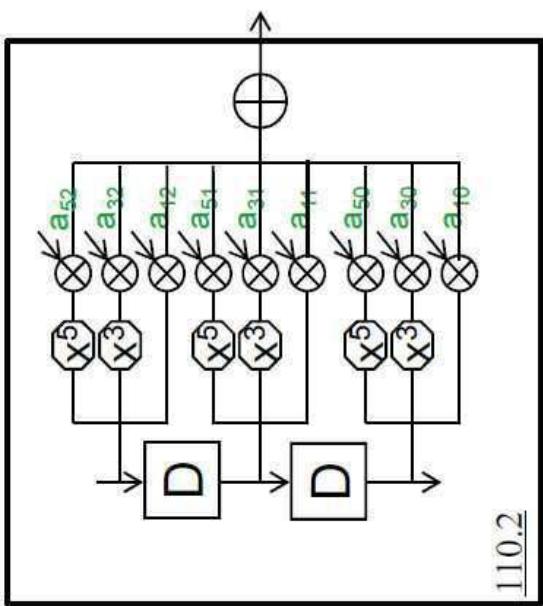

도 2는 본 개시의 일 실시예에 따른 예시적 전치 왜곡기 내의 예시적 필터들을 예시한다.

도 3은 본 개시의 일 실시예에 따른 예시적 방법을 예시한다.

### 발명을 실시하기 위한 구체적인 내용

[0006] 본 개시의 예시적 실시예에 따르면, 증폭기는 전치 왜곡 신호를 생성하기 위해 입력 신호를 수신하는 전치 왜곡기, 전치 증폭된 신호를 생성하기 위해 전치 왜곡 신호를 수신하는 제 1 변환기, 전치 증폭된 신호 및 입력 신호에 기초하여 출력 신호를 생성하기 위해 전치 증폭된 신호를 수신하는 전력 증폭기, 및 피드백 신호를 생성하기 위해 출력 신호를 샘플링하는 제 2 변환기를 포함할 수 있다. 전치 왜곡기는 동위상 입력 신호에 대한 전치 왜곡 신호 성분 및 직교 입력 신호에 대한 전치 왜곡 신호 성분을 개별적으로 및 독립적으로 생성할 수 있다.

[0007] 따라서, 입력 신호는 동위상 및 직교 위상 부분들로 분리될 수 있고, 알고리즘들은 2개의 분리 및 독립 복소수 계수 세트를 계산하기 위해 사용될 수 있으며, 계수들은 프런트엔드 근처의 입력 신호의 동위상 신호 경로 및 직교 신호 경로에 개별적으로 그리고 독립적으로 적용될 수 있다. I 및 Q 경로들에 대한 2개의 계수 세트는 상이할 수 있고, 따라서 I 및 Q 경로들을 독립적으로 보상함으로써 베이스밴드 타입 비선형성들을 정정할 때 더 양호한 성능을 달성할 수 있다.

[0008] 도 1은 본 개시의 일 실시예에 따른 증폭기(100)의 간략한 블록도를 예시한다. 증폭기(100)는 전치 왜곡 신호를 생성하기 위해 입력 신호를 수신하는 전치 왜곡기(110), 전치 증폭된 신호를 생성하기 위해 전치 왜곡 신호를 수신하는 제 1 변환기(130), 전치 증폭된 신호 및 입력 신호에 기초하여 출력 신호를 생성하기 위해 전치 증폭된 신호를 수신하는 전력 증폭기(150), 및 피드백 신호를 생성하기 위해 출력 신호를 샘플링하는 제 2 변환기(140)를 포함할 수 있다.

[0009] 전치 왜곡기(110)는 동위상 입력 신호에 대한 전치 왜곡 신호 성분 및 직교 입력 신호에 대한 전치 왜곡 신호 성분을 개별적으로 또는 독립적으로 생성할 수 있다.

[0010] 출력 신호는 안테나(170)를 통해 송신될 수 있다. 제 2 변환기(140)는 커플링(160)을 통해 출력 신호를 수신할 수 있다. 제 1 변환기(130)와 전력 증폭기(150) 사이에, 부가 구성요소들, 예를 들어 신호를 송신 경로에서 베이스밴드 / 중간 주파수(IF)로부터 무선 주파수(RF)로 변환하는 변조기들이 있을 수 있다. 제 2 변환기(130)와 커플링(160) 사이에, 부가 구성요소들, 예를 들어 신호를 수신 / 피드백 경로에서 RF로부터 IF / 베이스밴드로 변환하는 변조기들이 있을 수 있다. 부가 구성요소들은 슈퍼헤테로다인 또는 제로-IF 송수신기들을 포함할 수 있다.

[0011] 본 개시의 실시예에 따르면, 전치 왜곡기(110)는 제 1 필터(110.2) 및 제 2 필터(110.3)를 포함할 수 있고, 각각의 필터는 전치 왜곡 신호의 성분을 생성하기 위해 입력 신호의 성분을 개별적으로 또는 독립적으로 변환할 수 있다. 제 1 필터(110.2)는 입력 신호의 동위상 성분을 수신할 수 있고, 전치 왜곡 신호의 제 1 성분을 생성할 수 있다. 제 2 필터(110.3)는 입력 신호의 직교 성분을 수신할 수 있고, 전치 왜곡 신호의 제 2 성분을 생성할 수 있다. 전치 왜곡 신호의 제 1 및 제 2 성분은 각각 복소수 신호일 수 있다.

- [0012] 제 1 및 제 2 필터들(110.2 및 110.3)은 LUT(lookup tables)를 갖는 스토리지들을 포함할 수 있다. 제 1 및 제 2 필터들(110.2 및 110.3)은 다항식 기반 필터들을 포함할 수 있으며, 이는 비선형 왜곡들에 대한 보상을 포함하는 다중 차수들의 다항식 방정식에 기초하여 입력 신호를 왜곡할 수 있다. 다항식 기반 필터는 상당한 부가 수정들 없이 PA의 메모리 효과들에 효과적으로 보상하는 것이 가능할 수 있다. 통신 응용들에 사용되는 전치 왜곡기에 대한 다항식 기반 필터는 5차 다항식 방정식으로 충분한 보상을 달성할 수 있다. 그러나, 다른 수의 차수들이 가능하다.

- [0013] 전치 왜곡기(110)는 제 1 복조기(110.1) 및 제 2 복조기(110.5)를 포함할 수 있다. 제 1 복조기(110.1)는 입력 신호를 그것의 동위상 성분 및 그것의 직교 성분으로 복조하고 분할할 수 있다. 제 1 복조기(110.1)는 입력 신호의 동위상 성분을 전치 왜곡 처리를 위한 제 1 필터(110.2)로 송신할 수 있다. 제 1 복조기(110.1)는 입력 신호의 직교 성분을 전치 왜곡 처리를 위한 제 2 필터(110.3)로 송신할 수 있다. 제 2 복조기(110.5)는 피드백 신호를 그것의 동위상 성분 및 그것의 직교 성분으로 복조하고 분할할 수 있다. 제 2 복조기(110.5)는 피드백 신호의 동위상 성분을 전치 왜곡 처리를 위한 제 1 필터(110.2)로 송신할 수 있고, 피드백 신호의 직교 성분을 전치 왜곡 처리를 위한 제 2 필터(110.3)로 송신할 수 있다. 대안적으로, 제 2 복조기(110.5)는 피드백 신호의 임의의 또는 모든 성분들을 전치 왜곡 처리를 위한 제 1 필터(110.2)로 송신할 수 있고, 피드백 신호의 임의의 또는 모든 성분들을 전치 왜곡 처리를 위한 제 2 필터(110.3)로 송신할 수 있다.

- [0014] 대안적으로, 제 2 복조기(110.5)는 제 2 변환기(140) 이전에 아날로그 도메인에 있고 피드백 경로에 배치될 수 있다. 예를 들어, 피드백 경로는 제로-IF(intermediate frequency) 수신기 구성일 수 있으며, 이는 아날로그 직교 복조기로부터 수신되는 변조된 출력을 샘플링하기 위해 2개의 ADC(analog-to-digital converter)를 포함할 수 있다.

- [0015] 전치 왜곡기(110)는 전치 왜곡 신호의 제 1 성분 및 제 2 성분을 수신하고, 전치 왜곡 신호를 생성하기 위해 그들을 조합할 수 있는 변조기(110.4)를 포함할 수 있다.

- [0016] 제 1 필터(110.2) 및 제 2 필터(110.3)는 전력 증폭기(100)에서 비선형성들, 예를 들어 베이스밴드 비선형성들, RF 비선형성들 등을 보상하도록 전치 왜곡 신호의 제 1 성분 및 제 2 성분을 생성하기 위해 입력 신호를 변환하도록 각각 조정되고 제어될 수 있다.

- [0017] 제 1 필터(110.2) 및 제 2 필터(110.3)는 제 1 필터(110.2) 및 제 2 필터(110.3)의 설정들 또는 파라미터들을 조정하기 위해 적응 필터 알고리즘들을 포함할 수 있다. 적응 필터 알고리즘들은 LMS(least mean square), LS(least square), RLS(recursive least square), LQE(linear quadratic estimation, 칼만 필터), 또는 베이지안 추정 알고리즘을 포함할 수 있다.

- [0018] 부가적으로, 제 1 필터(110.2) 및 제 2 필터(110.3)는 증폭기(100)의 성능을 계속적으로 교정하고 향상시키기 위해 피드백 신호 또는 에러 신호(뿐만 아니라 PA의 성능 레벨 및 환경 조건들과 같은 다른 정보)를 계속적으로 기록하고 감시하는 학습 알고리즘을 포함할 수 있다. 제 1 필터(110.2) 및 제 2 필터(110.3)는 입력 신호에 대한 피드백 신호의 시간 지연을 보상하기 위해 시간 지연 알고리즘을 포함할 수 있다.

- [0019] 제 1 필터(110.2) 및 제 2 필터(110.3)는 각각 트렁케이티드(truncated) 이산 시간 볼테라 급수 방정식과 같은 비선형성에 대한 다항식 방정식에 따라 모델링되는 신호 변환을 수행할 수 있다.

- [0020] 도 2는 본 개시의 일 실시예에 따른 예시적 전치 왜곡기 내의 예시적 필터들(110.2 및 110.3)을 예시한다. 도 2에 도시된 바와 같이, 제 1 필터(110.2) 및 제 2 필터(110.3)는 각각 5차 트렁케이티드 이산 시간 볼테라 급수 방정식에 따라 모델링되는, 전치 왜곡 신호의 제 1 및 제 2 성분들을 생성하기 위한 다항식 아키텍처를 포함할 수 있다. 제 1 필터(110.2) 및 제 2 필터(110.3)는 비선형성들의 그것들의 각각의 모델들에 대한 그것들 자체의 분리 및 독립 계수 세트를 각각 포함할 수 있다. 제 1 필터(110.2)는 계수들( $a_{10}, a_{30}, a_{50}, a_{11}, a_{31}, a_{51}, a_{12}, a_{32}$ , 및  $a_{52}$ )을 포함할 수 있고, 제 2 필터(110.3)는 계수들( $b_{10}, b_{30}, b_{50}, b_{11}, b_{31}, b_{51}, b_{12}, b_{32}$ , 및  $b_{52}$ )을 포함할 수 있다. 계수들( $a_{10}, a_{30}, a_{50}, a_{11}, a_{31}, a_{51}, a_{12}, a_{32}$ , 및  $a_{52}$ , 및  $b_{10}, b_{30}, b_{50}, b_{11}, b_{31}, b_{51}, b_{12}, b_{32}$ , 및  $b_{52}$ ) 등은 각각 복소수일 수 있다(예를 들어:  $a_{10} = a_{10} + i \cdot a_{q10}$ ).

- [0021] 제 1 필터(110.2) 및 제 2 필터(110.3)가 비선형성들의 그것들의 각각의 모델들에 대한 그것들 자체의 분리 및 독립 계수 세트를 각각 포함할 수 있으므로, 동위상 신호 경로 내의 비선형성들은 PA에 대한 직교 신호 경로 내의 비선형성들로부터 개별적으로 모델링될 수 있다. 따라서, 부가 계수들 및 독립된 비선형성 모델링은 PA의 프런트엔드 근처의 비선형성들, 즉 베이스밴드 비선형성들에 대한 보상을 향상시킬 수 있다.

- [0022] 대안적으로, 제 1 필터(110.2) 및 제 2 필터(110.3)는 PA 내의 컨트롤러(도시되지 않음)에 의해 제어될 수 있다.

- [0023] 본 개시의 특징에 따르면, 제 1 변환기(130)는 디지털-아날로그 변환기, 또는 복수의 신호 채널들을 갖는 복수의 디지털-아날로그 변환기들을 포함할 수 있다. 제 2 변환기(140)는 아날로그-디지털 변환기, 또는 복수의 신호 채널들을 갖는 복수의 아날로그-디지털 변환기들을 포함할 수 있다.

- [0024] 도 3은 PA에서 왜곡들을 보상하기 위한 예시적 방법(300)을 예시한다. 방법은 블록(310)에서 전치 왜곡 신호에 기초하여 제 1 변환기(130)에 의해 전치 증폭된 신호를 생성하는 단계를 포함한다. 블록(320)에서, 전력 증폭기(150)는 전치 증폭된 신호 및 입력 신호에 기초하여 출력 신호를 생성할 수 있다. 블록(330)에서, 제 2 변환기(140)는 피드백 신호를 생성하기 위해 출력 신호를 샘플링할 수 있다. 블록(340)에서, 전치 왜곡기(110)는 입력 신호의 동위상 성분에 기초하여 전치 왜곡 신호의 제 1 성분을 생성할 수 있다. 블록(350)에서, 전치 왜곡기(110)는 입력 신호의 직교 성분에 기초하여 전치 왜곡 신호의 제 2 성분을 생성할 수 있다. 블록(360)에서, 전치 왜곡기(110)는 입력 신호에 기초하여 PA에서의 비선형성을 보상하기 위해 전치 왜곡 신호의 제 1 성분 및 제 2 성분을 조합할 수 있다.

- [0025] 본 개시는 설명된 실시예들에 제한되지 않고, 상반되는 지정들이 존재하는 임의의 수의 시나리오들 및 실시예들이 해결될 수 있다는 점이 이해되어야 한다.

- [0026] 본 개시는 수개의 예시적 실시예들을 참조하여 설명되었지만, 사용되었던 단어들은 제한의 단어들보다는 설명 및 예시의 단어들인 점이 이해된다. 변경들은 그것의 양상들에서 본 개시의 범위 및 사상으로부터 벗어나는 것 없이, 현재 언급되고 보정된 바와 같이, 첨부된 청구항들의 범위 내에서 이루어질 수 있다. 본 개시는 특정 수단, 재료들 및 실시예들을 참조하여 설명되었지만, 본 개시는 개시된 상세에 제한되도록 의도되지 않으며; 오히려 본 개시는 첨부된 청구항들의 범위 내에 있는 것과 같이, 모두 기능적으로 동등한 구조들, 방법들, 및 사용들로 연장된다.

- [0027] 컴퓨터 관독가능 매체는 단일 매체로 설명될 수 있지만, "컴퓨터 관독가능 매체"라는 용어는 집중형 또는 분산형 데이터베이스, 및/또는 하나 이상의 명령어 세트들을 저장하는 연관된 캐시들 및 서버들과 같은 단일 매체 또는 다수의 매체를 포함한다. "컴퓨터 관독가능 매체"라는 용어는 또한 프로세서에 의한 실행을 위한 명령어 세트를 저장, 인코딩 또는 전달할 수 있거나 컴퓨터 시스템이 본 명세서에 개시된 실시예들 중 임의의 하나 이상을 수행하게 하는 임의의 매체를 포함할 것이다.

- [0028] 컴퓨터 관독가능 매체는 비일시적 컴퓨터 관독가능 매체 또는 매체를 포함하며/하거나 일시적 컴퓨터 관독가능 매체 또는 매체를 포함할 수 있다. 특정한 비제한 예시적 실시예에서, 컴퓨터 관독가능 매체는 하나 이상의 비휘발성 관독 전용 메모리들을 수용하는 메모리 카드 또는 다른 패키지와 같은 고체 상태 메모리를 포함할 수 있다. 게다가, 컴퓨터 관독가능 매체는 랜덤 액세스 메모리 또는 다른 휘발성 재기록가능 메모리일 수 있다. 부가적으로, 컴퓨터 관독가능 매체는 송신 매체를 통해 전달되는 신호와 같은 반송파 신호들을 캡처하기 위해 디스크 또는 테이프들 또는 다른 스토리지 디바이스와 같은 자기 광 또는 광 매체를 포함할 수 있다. 따라서, 본 개시는 데이터 또는 명령어들이 저장될 수 있는 임의의 컴퓨터 관독가능 매체 또는 다른 균등물들 및 후속(successor) 매체를 포함하는 것으로 간주된다.

- [0029] 본 출원은 코드 세그먼트들로서 컴퓨터 관독가능 매체에 구현될 수 있는 특정 실시예들을 설명하지만, 주문형 집적 회로들, 프로그램가능 로직 어레이들 및 다른 하드웨어 디바이스들과 같은 전용 하드웨어 구현들은 본 명세서에 설명된 실시예들 중 하나 이상을 구현하도록 구성될 수 있다는 점이 이해되어야 한다. 본 명세서에 설명된 다양한 실시예들을 포함할 수 있는 응용들은 다양한 전자 및 컴퓨터 시스템들을 광범위하게 포함할 수 있다. 따라서, 본 출원은 소프트웨어, 펌웨어, 및 하드웨어 구현들, 또는 그것의 조합들을 포함할 수 있다.

- [0030] 본 명세서는 특정 표준들 및 프로토콜들을 참조하여 특정 실시예들에 구현될 수 있는 구성요소들 및 기능들을 설명하며, 본 개시는 그러한 표준들 및 프로토콜들에 제한되지 않는다. 그러한 표준들은 본래 동일한 기능을 갖는 더 빠르거나 더 효율적인 균등물들로 주기적으로 대체된다. 따라서, 동일한 또는 유사한 기능을 갖는 대체 표준들 및 프로토콜들은 그것의 균등물들로 간주된다.

- [0031] 본 명세서에 설명되는 실시예들의 예시들은 다양한 실시예들의 일반적 이해를 제공하도록 의도된다. 예시들은 본 명세서에 설명된 구조들 또는 방법들을 이용하는 장치 및 시스템들의 요소들 및 특징들의 모두의 완전한 설명으로서 역할을 하도록 의도된다. 많은 다른 실시예들은 본 개시를 검토하면 당업자에게 분명할 수 있다. 다른 실시예들은 본 개시로부터 이용되고 유도될 수 있어, 구조적 및 논리적 치환들 및 변경들은 본 개시의 범위로부터

터 벗어나는 것 없이 이루어질 수 있다. 부가적으로, 예시들은 단지 표상적이고 축척에 따라 도시되지 않을 수 있다. 예시들 내의 특정 비율들은 과장될 수 있는 한편, 다른 비율들은 최소화될 수 있다. 따라서, 본 명세서 및 도면들은 제한적보다는 예시적인 것으로 간주되어야 한다.

[0032] 본 개시의 하나 이상의 실시예들은 단지 편의상 그리고 이러한 응용의 범위를 임의의 특정 개시 또는 발명의 개념에 임의로 제한하도록 의도되는 것 없이 "개시"라는 용어에 의해, 개별적으로 및/또는 집합적으로 본 명세서에 지칭될 수 있다. 더욱이, 특정 실시예들이 본 명세서에 예시되고 설명되었지만, 동일한 또는 유사한 목적을 달성하도록 설계되는 임의의 후속 배열은 도시된 특정 실시예들로 치환될 수 있다는 점이 이해되어야 한다. 본 개시는 다양한 실시예들의 임의의 및 모든 후속 개조들 또는 변형들을 커버하도록 의도된다. 상기 실시예들, 및 본 명세서에 구체적으로 설명되지 않은 다른 실시예들의 조합들은 설명을 검토하면 당업자들에게 분명할 것이다.

[0033] 게다가, 이전의 상세한 설명에서, 다양한 특징들은 본 개시를 간소화할 목적으로 단일 실시예에 함께 그룹화되거나 설명될 수 있다. 본 개시는 청구된 실시예들이 각각의 청구항에 분명히 열거된 것보다 더 많은 특징들을 필요로 한다는 의미를 반영하는 것으로 해석되지 않아야 한다. 오히려, 이하의 청구항들이 반영하는 바와 같이, 독창적인 발명 대상은 개시된 실시예들 중 어느 하나에 대한 모든 특징들보다 적은 것에 있다. 따라서, 이하의 청구항들은 상세한 설명에 포함되며, 각각의 청구항은 개별적으로 청구된 발명 대상을 정의하는 것으로서 그 자체에 기초한다.

[0034] 상기 개시된 발명 대상은 예시적이고, 비제한적인 것으로 간주되어야 하고, 첨부된 청구항들은 모든 그러한 수정들, 개선들, 및 본 개시의 사상 및 범위 내에 있는 다른 실시예들을 커버하도록 의도된다. 따라서, 법으로 허용되는 최대 범위까지, 본 개시의 범위는 이하의 청구항들 및 그들의 균등물들의 가장 넓은 허용 해석에 의해 결정되어야 하고, 이전의 상세한 설명에 의해 한정되거나 제한되지 않을 것이다.

도면

도면1

도면2

110.3

110.2

## 도면3