(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7564985号

(P7564985)

(45)発行日 令和6年10月10日(2024.10.10)

(24)登録日 令和6年10月2日(2024.10.2)

(51)国際特許分類

A 6 3 F 7/02 (2006.01)

F I

A 6 3 F

7/02

3 2 6 Z

A 6 3 F

7/02

3 2 0

請求項の数 1 (全124頁)

(21)出願番号 特願2020-135249(P2020-135249)

(22)出願日 令和2年8月7日(2020.8.7)

(65)公開番号 特開2022-30919(P2022-30919A)

(43)公開日 令和4年2月18日(2022.2.18)

審査請求日 令和5年7月31日(2023.7.31)

(73)特許権者 391010943

株式会社藤商事

大阪府大阪市中央区内本町一丁目1番4号

(74)代理人 110004495

弁理士法人ティクオフ

井上 孝司

大阪市中央区内本町一丁目1番4号 株式会社藤商事内

審査官 西田 光宏

最終頁に続く

(54)【発明の名称】 遊技機

## (57)【特許請求の範囲】

## 【請求項1】

液晶表示手段の表示制御を行う表示制御手段と、

電子部品が搭載された複数の基板と、を備え、

前記基板は、複数の配線層と、それら複数の配線層を互いに導通させるための板厚方向の

層間導通部とを有し、

前記電子部品は第1電子部品と第2電子部品とを含み、

前記表示制御手段は、前記第1電子部品により構成され、

前記液晶表示手段に、位置に対して連続的又は段階的に色情報が変化するグラデーション画像を表示可能な

遊技機において、

複数の前記層間導通部のうち、前記第2電子部品の配置領域に対応する領域内に配置される特定層間導通部を介して前記第1電子部品と前記第2電子部品とを接続し、

前記特定層間導通部を、前記複数の配線層のうち表層の第1面側から反対側の第2面側まで貫通させ、

前記基板の前記第2面における前記第2電子部品の配置領域に対応する領域内に所定電子部品を配置し、

前記基板の前記第2面における前記第2電子部品の配置領域に対応する領域内で前記特定層間導通部と前記所定電子部品とを接続し、

前記表示制御手段は、奇数画素に対応する奇数画像データと、前記奇数画素に隣接する

偶数画素に対応する偶数画像データと、互いに異なる配線路を介して前記液晶表示手段へと出力するように構成し、

前記表示制御手段が搭載され、前記液晶表示手段に対して前記奇数画像データ及び前記偶数画像データを送信するための第1信号線が形成された第1基板と、

前記奇数画像データ及び前記偶数画像データを送信するための第2信号線が形成され、当該奇数画像データ及び当該偶数画像データを前記液晶表示手段に出力するための出力コネクタが搭載された第2基板と、

前記第1基板の前記第1信号線と前記第2基板の前記第2信号線とを接続する接続コネクタと、を備え、

前記第2基板の前記第2信号線に対して保護回路及び／又はテストポイントを接続し、

前記グラデーション画像に対応する前記奇数画像データに設定される複数種類の色情報と、前記グラデーション画像に対応する前記偶数画像データに設定される複数種類の色情報とが略共通することにより、

前記奇数画像データと前記偶数画像データの何れが欠落した場合であっても、前記グラデーション画像を識別可能となるように構成した

ことを特徴とする遊技機。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パチンコ機、スロットマシン等の遊技機に関するものである。

20

【背景技術】

【0002】

パチンコ機等の遊技機では、演出画像等を表示するための液晶表示手段を搭載したものが主流となっている。この液晶表示手段は、制御基板に搭載されたVDP(Video Display Processor)回路から出力される画像データ信号、その他の制御信号に基づいて表示制御される(特許文献1)。

【先行技術文献】

【特許文献】

【0003】

【文献】特開2017-093632号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来の遊技機では、何らかのトラブルにより液晶制御に係る制御信号が一部でも欠落してしまうと、液晶表示手段には遊技者が識別不可能な画像が表示される等、遊技を正常に継続できない可能性があった。

本発明は上記事情に鑑みてなされたものであり、液晶制御関連のトラブル発生による遊技進行への悪影響を極力抑制することが可能な遊技機を提供することを目的とする。

【課題を解決するための手段】

【0005】

本発明は、液晶表示手段の表示制御を行う表示制御手段と、電子部品が搭載された複数の基板と、を備え、前記基板は、複数の配線層と、それら複数の配線層を互いに導通させるための板厚方向の層間導通部とを有し、前記電子部品は第1電子部品と第2電子部品とを含み、前記表示制御手段は、前記第1電子部品により構成され、前記液晶表示手段に、位置に対して連続的又は段階的に色情報が変化するグラデーション画像を表示可能な遊技機において、複数の前記層間導通部のうち、前記第2電子部品の配置領域に対応する領域内に配置される特定層間導通部を介して前記第1電子部品と前記第2電子部品とを接続し、前記特定層間導通部を、前記複数の配線層のうち表層の第1面側から反対側の第2面側まで貫通させ、前記基板の前記第2面における前記第2電子部品の配置領域に対応する領域内に所定電子部品を配置し、前記基板の前記第2面における前記第2電子部品の配置領

40

50

域に対応する領域内で前記特定層間導通部と前記所定電子部品とを接続し、前記表示制御手段は、奇数画素に対応する奇数画像データと、前記奇数画素に隣接する偶数画素に対応する偶数画像データとを、互いに異なる配線路を介して前記液晶表示手段へと出力するよう構成し、前記表示制御手段が搭載され、前記液晶表示手段に対して前記奇数画像データ及び前記偶数画像データを送信するための第1信号線が形成された第1基板と、前記奇数画像データ及び前記偶数画像データを送信するための第2信号線が形成され、当該奇数画像データ及び当該偶数画像データを前記液晶表示手段に出力するための出力コネクタが搭載された第2基板と、前記第1基板の前記第1信号線と前記第2基板の前記第2信号線とを接続する接続コネクタと、を備え、前記第2基板の前記第2信号線に対して保護回路及び/又はテストポイントを接続し、前記グラデーション画像に対応する前記奇数画像データに設定される複数種類の色情報と、前記グラデーション画像に対応する前記偶数画像データに設定される複数種類の色情報とが略共通することにより、前記奇数画像データと前記偶数画像データの何れが欠落した場合であっても、前記グラデーション画像を識別可能となるように構成したものである。

【発明の効果】

【0006】

本発明によれば、液晶制御関連のトラブル発生による遊技進行への悪影響を極力抑制することが可能となる。

【図面の簡単な説明】

【0007】

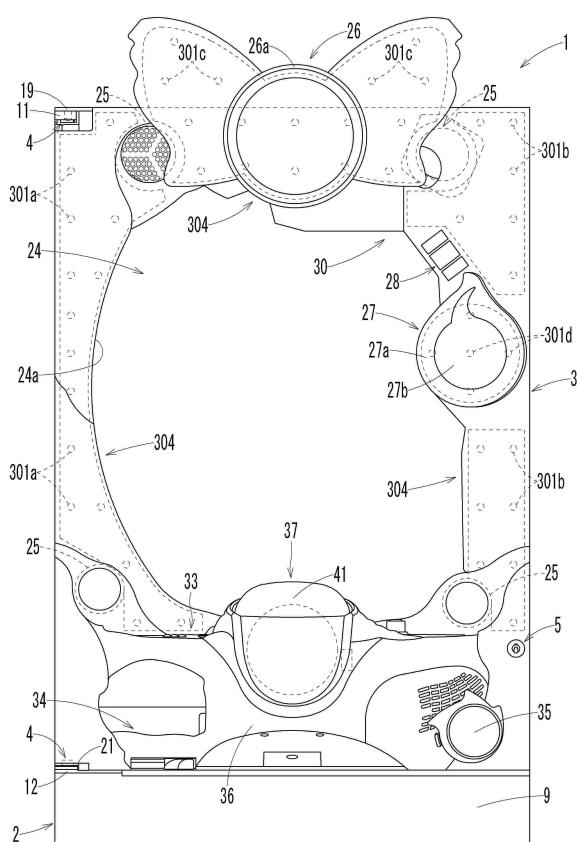

【図1】本発明の第1の実施形態に係るパチンコ機の全体正面図である。

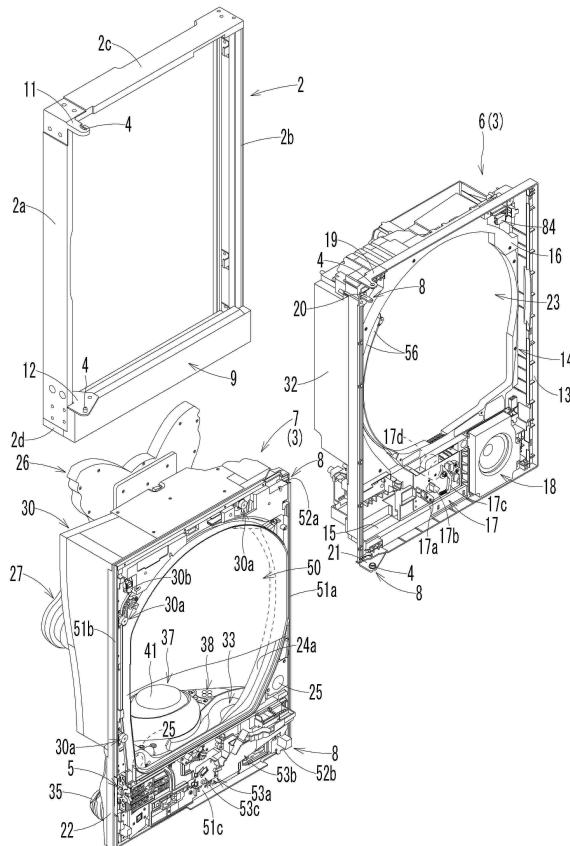

【図2】同パチンコ機の分解斜視図である。

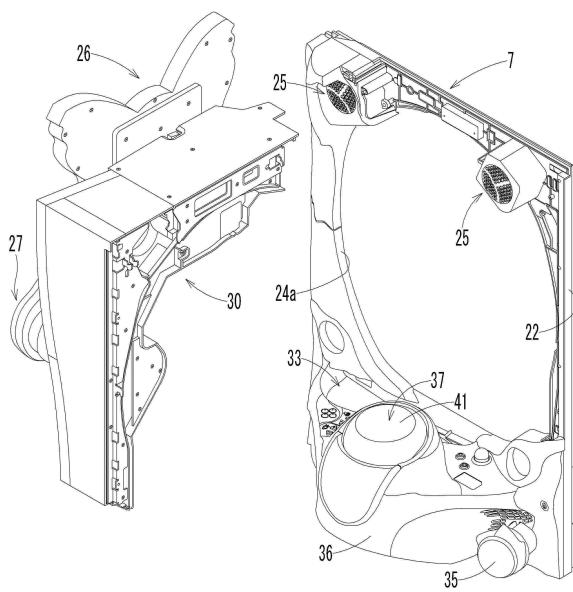

【図3】同パチンコ機のガラス扉の分解斜視図である。

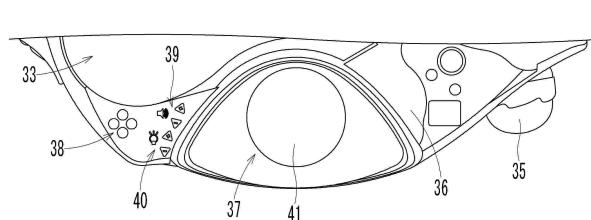

【図4】同パチンコ機の操作演出手段、十字操作ボタン、音量調整ボタン、光量調整ボタン等を示す要部平面図である。

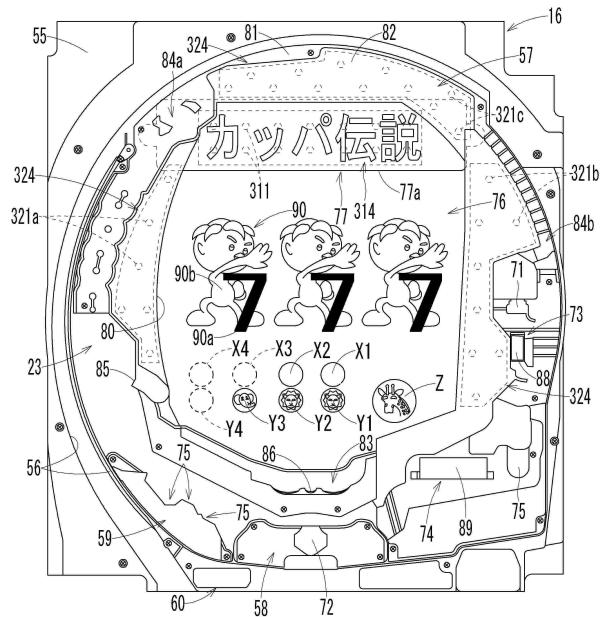

【図5】同パチンコ機の遊技盤の正面図である。

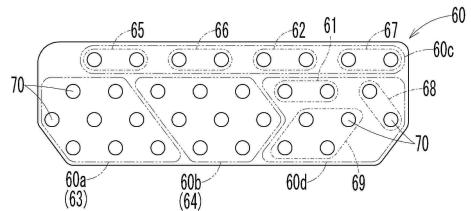

【図6】同パチンコ機の遊技情報表示手段の正面図である。

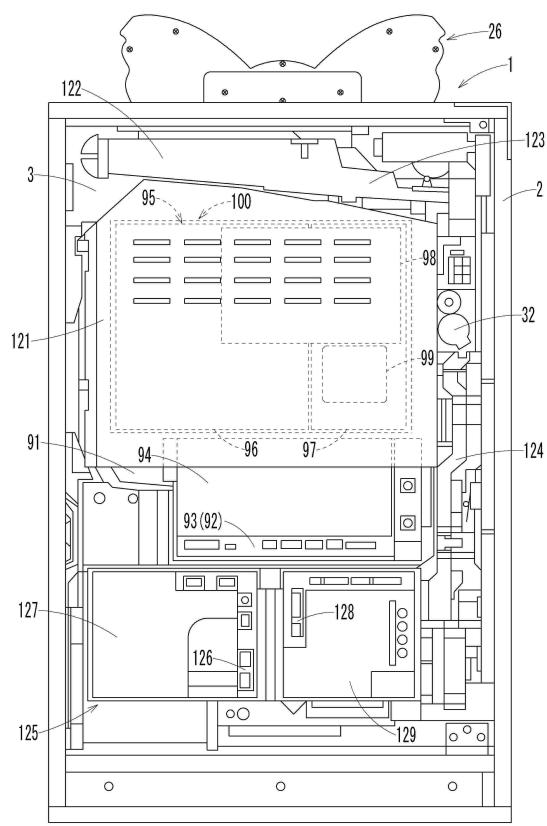

【図7】同パチンコ機の背面図である。

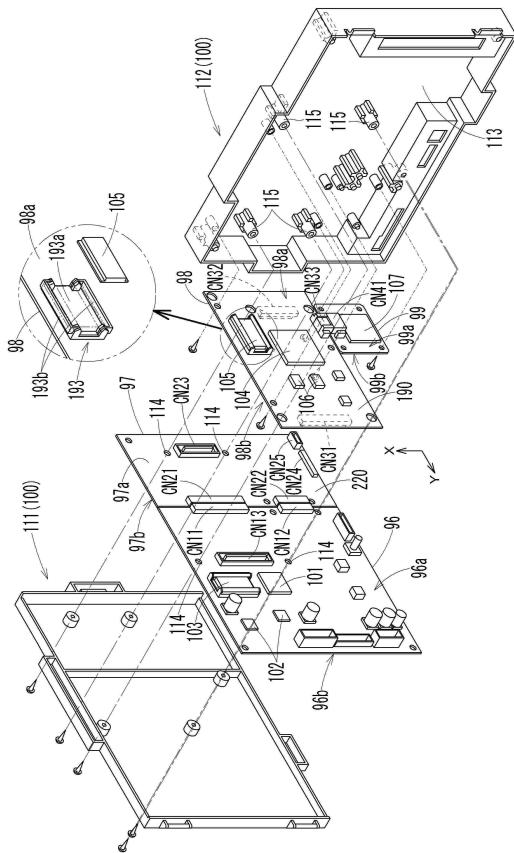

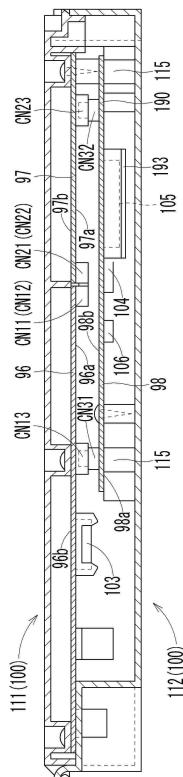

【図8】同パチンコ機の演出基板ケース及び演出制御部の分解斜視図である。

【図9】同パチンコ機の演出基板ケース及び演出制御部の平面断面図である。

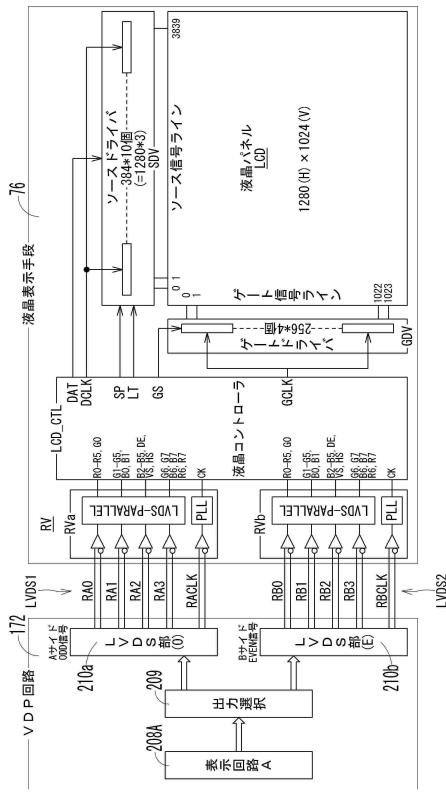

【図10】同パチンコ機の全体回路構成を示すブロック図である。

【図11】同パチンコ機における液晶表示手段の仕様に関する説明図である。

【図12】同パチンコ機における液晶制御信号の仕様に関する説明図である。

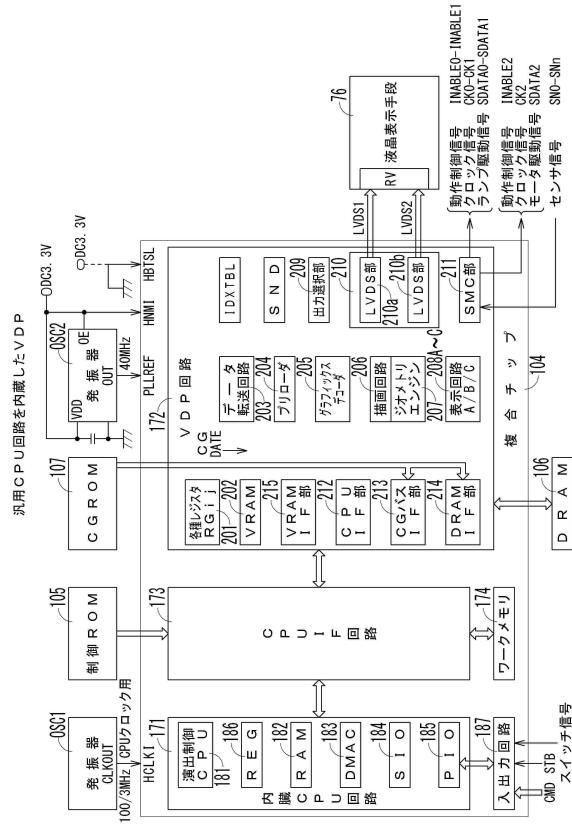

【図13】同パチンコ機における液晶表示手段の構成を示すブロック図である。

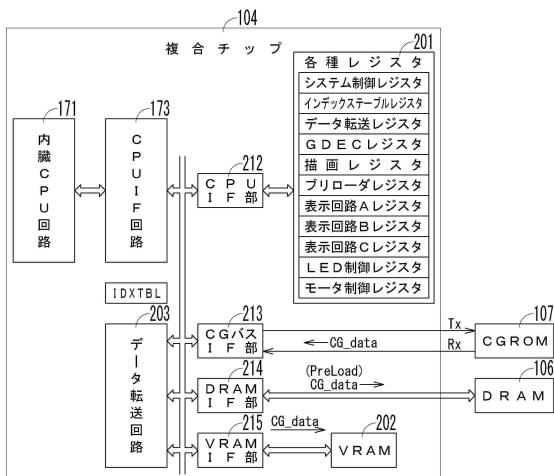

【図14】同パチンコ機における複合チップの全体構成を示すブロック図である。

【図15】同パチンコ機における複合チップの主要構成を示すブロック図である。

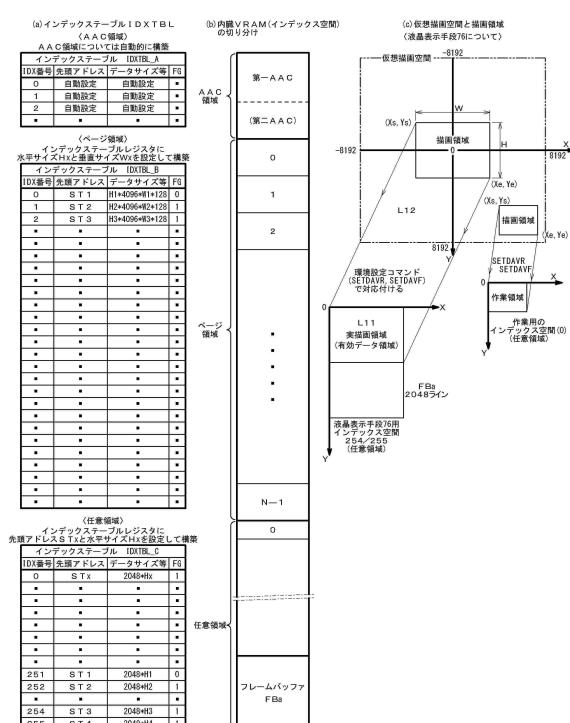

【図16】同パチンコ機におけるインデックス空間、インデックステーブル、仮想描画空間及び描画領域に関する説明図である。

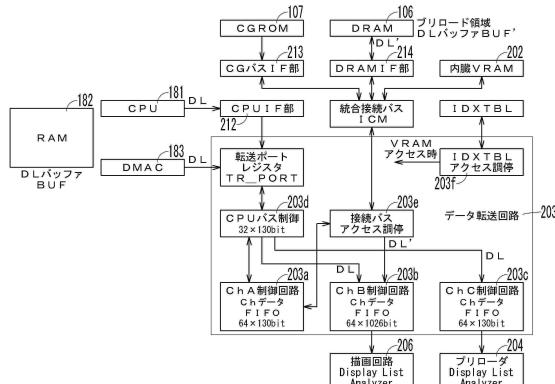

【図17】同パチンコ機におけるデータ転送回路の内部構成を、関連する回路構成と共に記載したブロック図である。

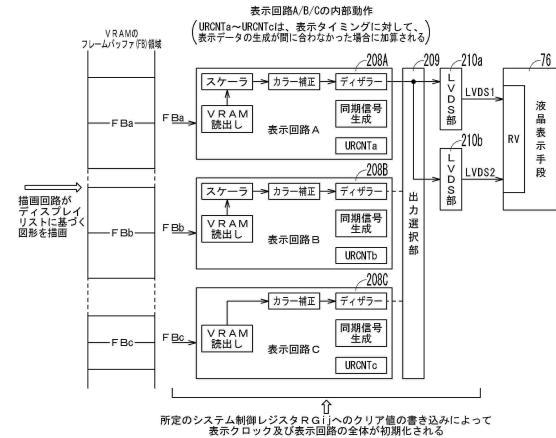

【図18】同パチンコ機における表示回路の内部構成を、関連する回路構成と共に記載したブロック図である。

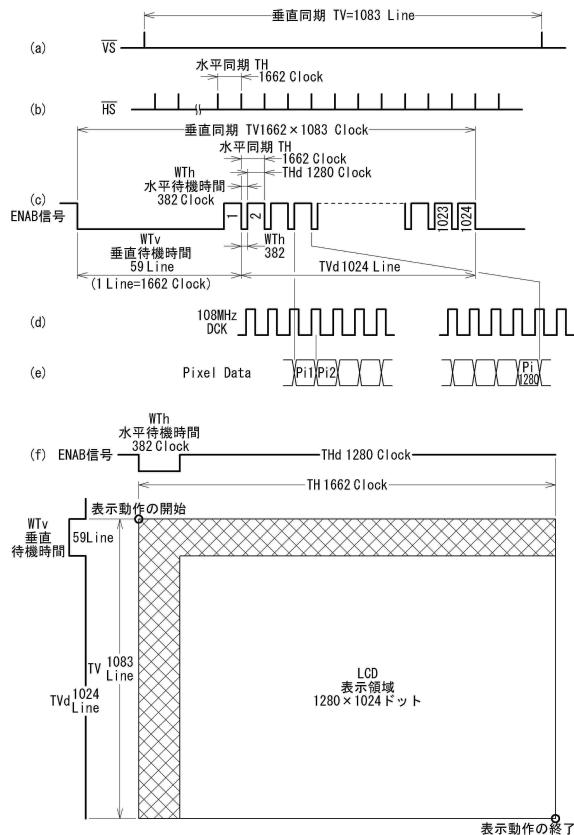

【図19】同パチンコ機におけるデータ有効信号E N A Bの説明図である。

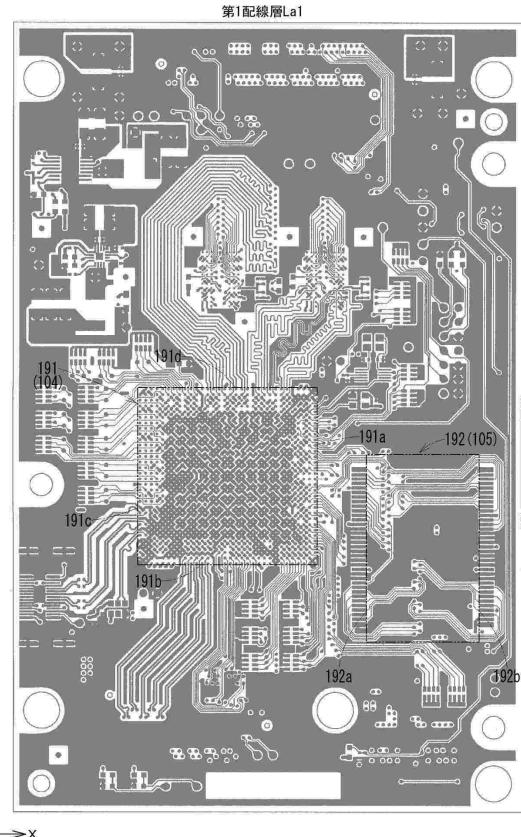

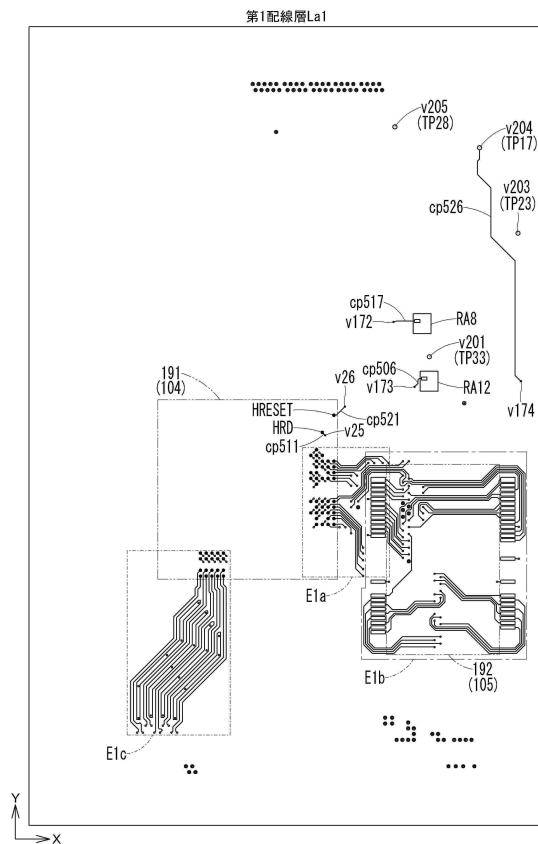

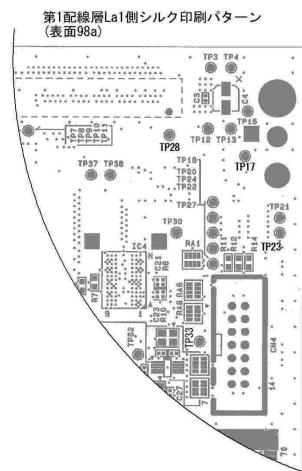

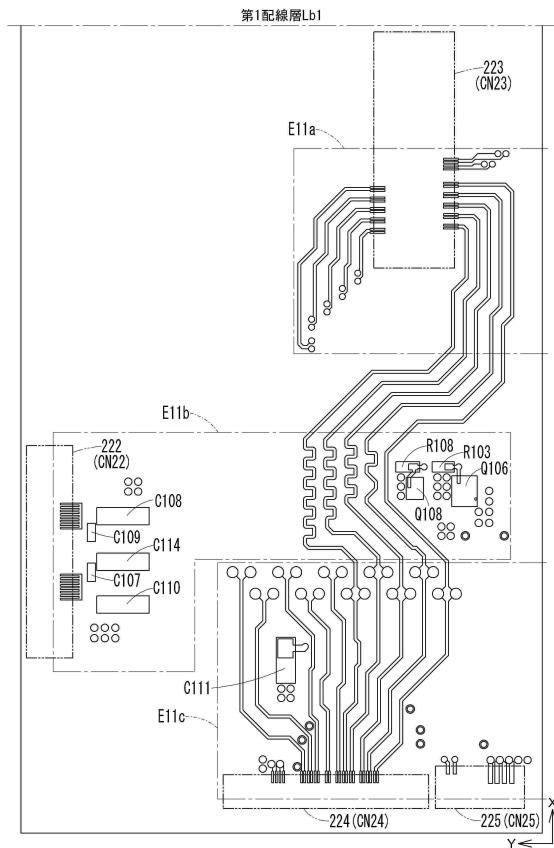

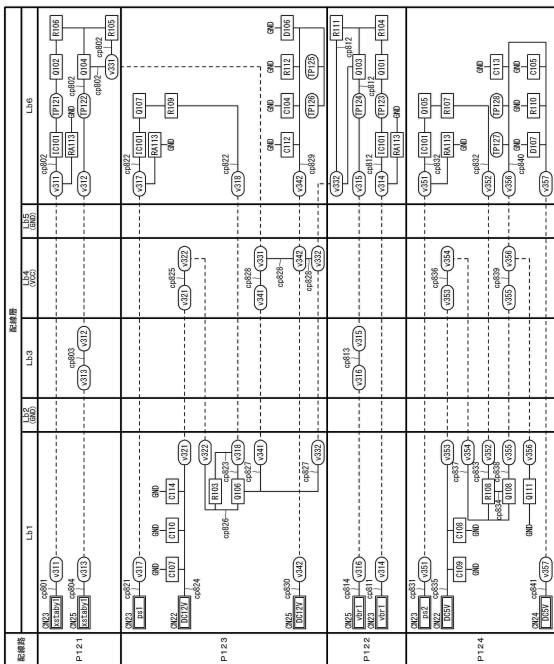

【図20】同パチンコ機の液晶制御基板における第1配線層を示す図である。

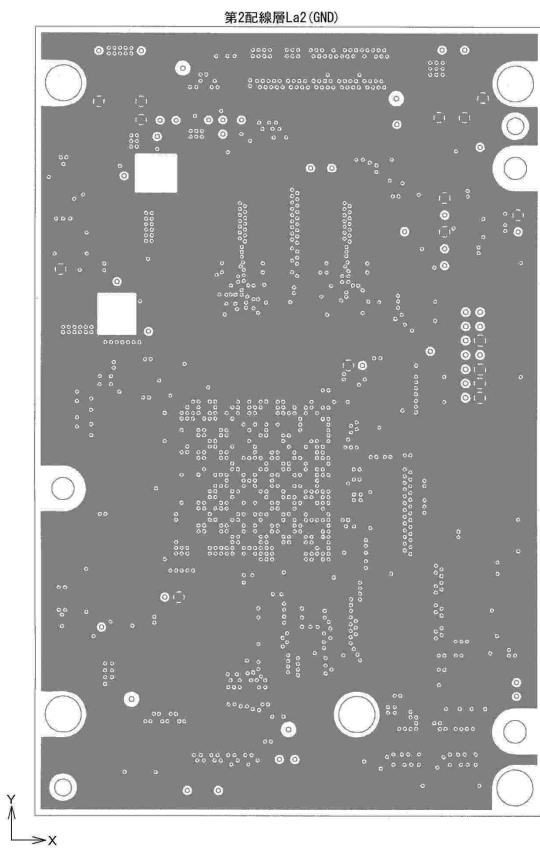

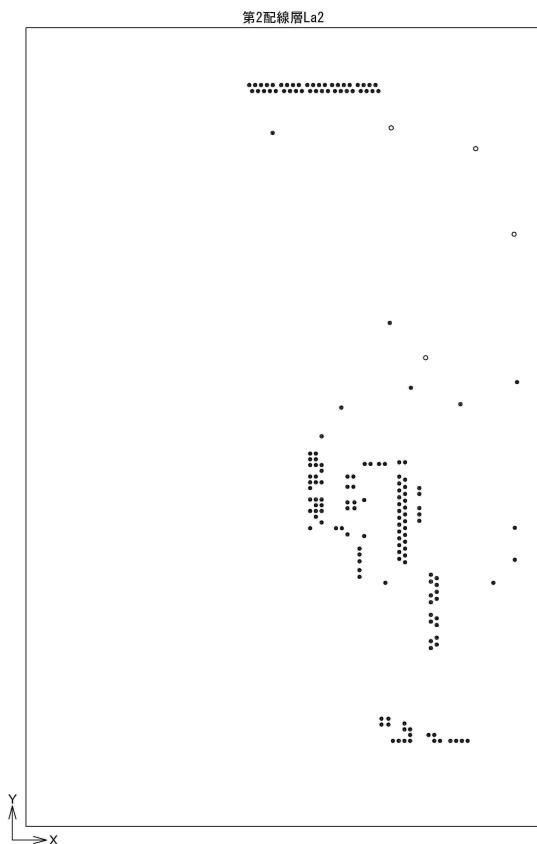

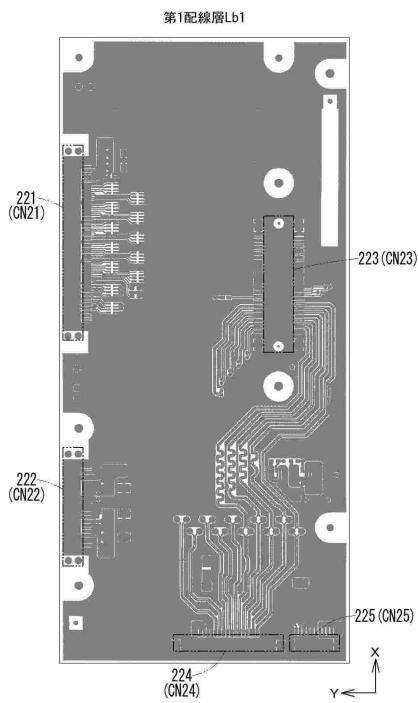

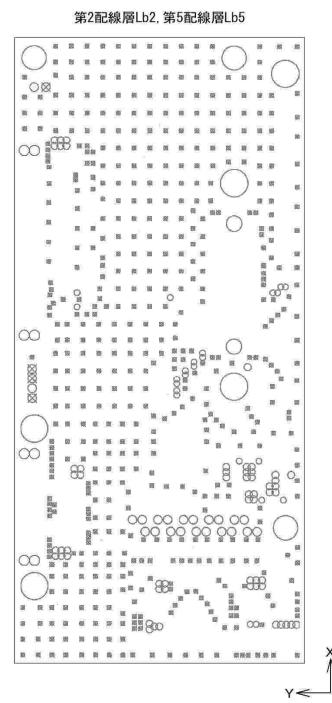

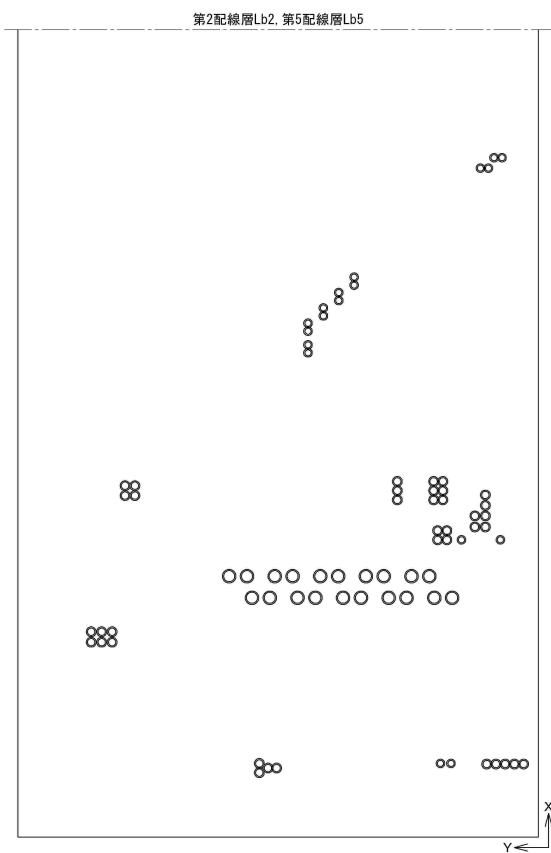

【図21】同液晶制御基板における第2配線層を示す図である。

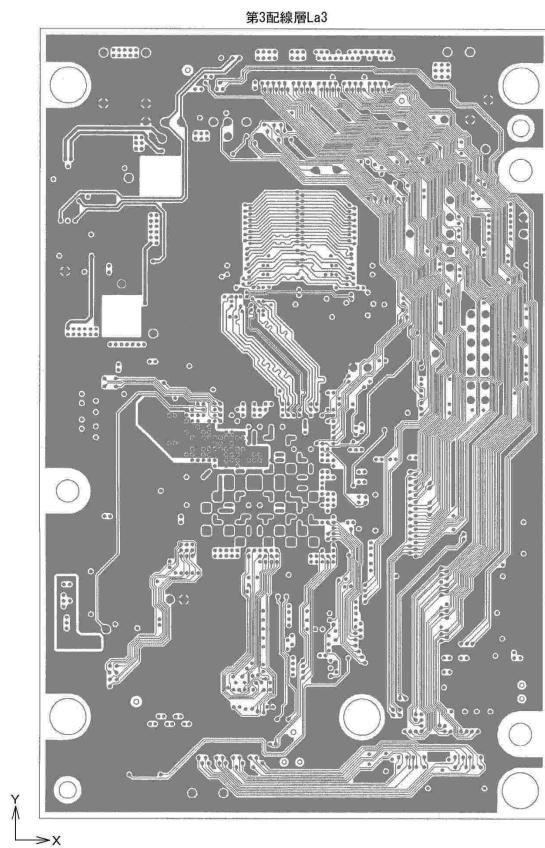

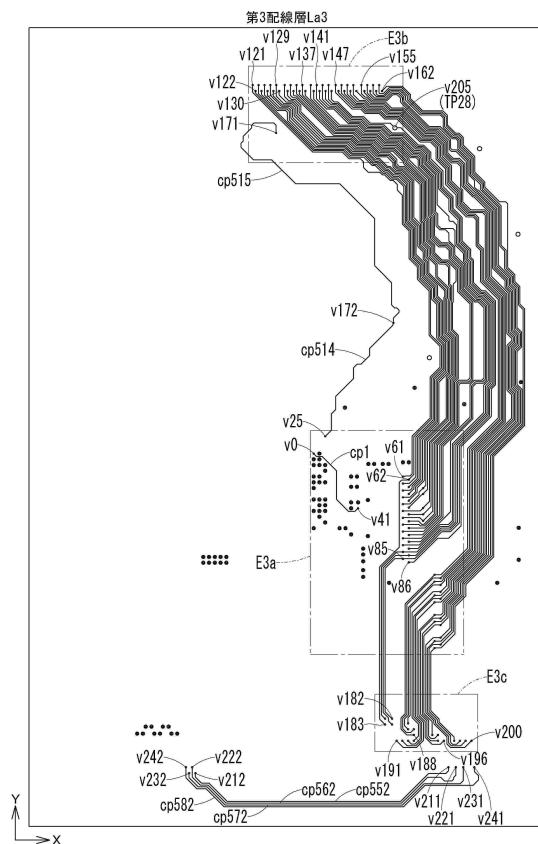

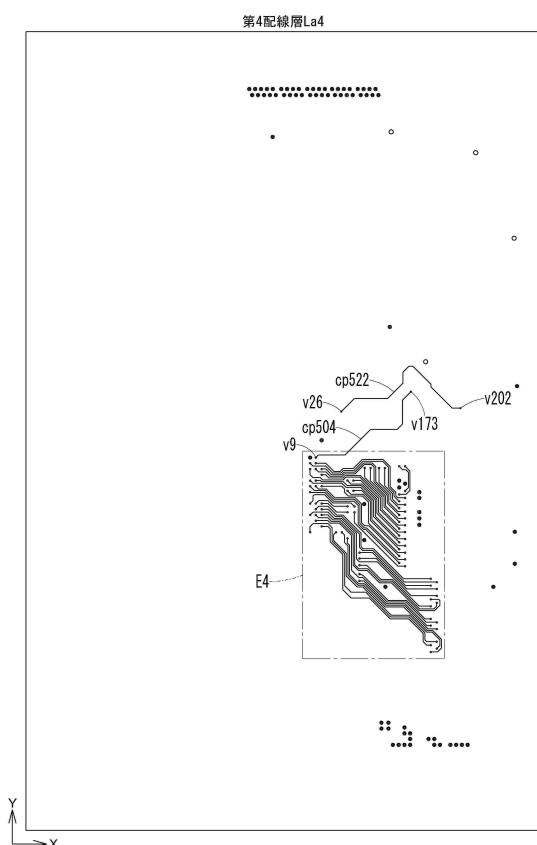

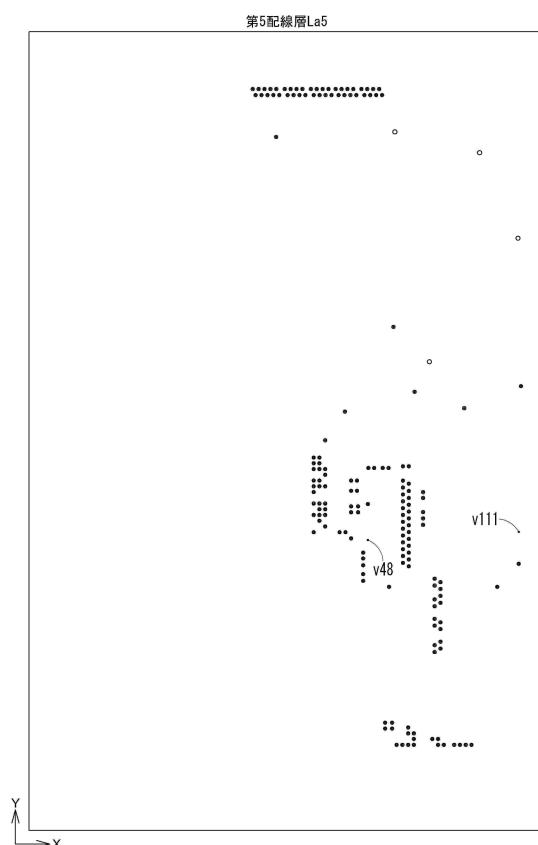

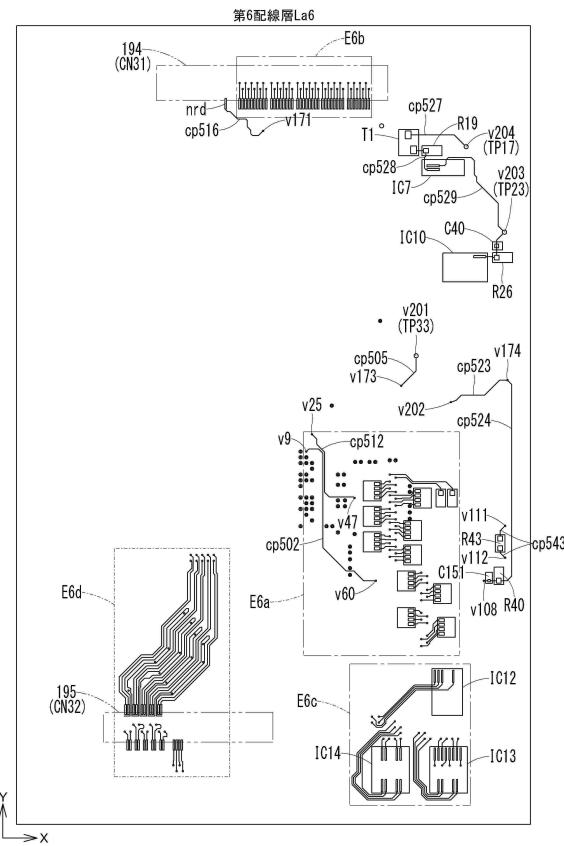

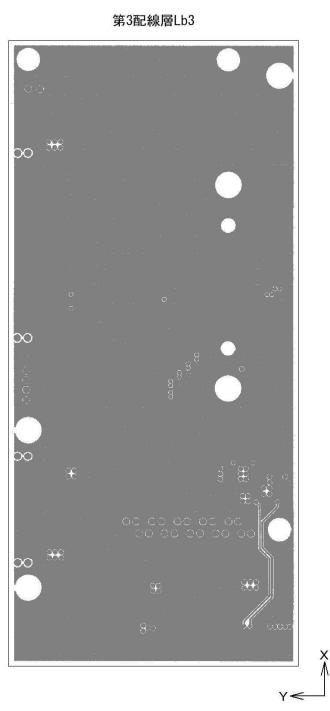

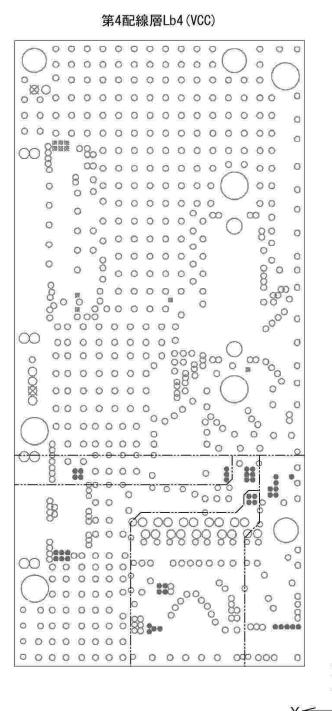

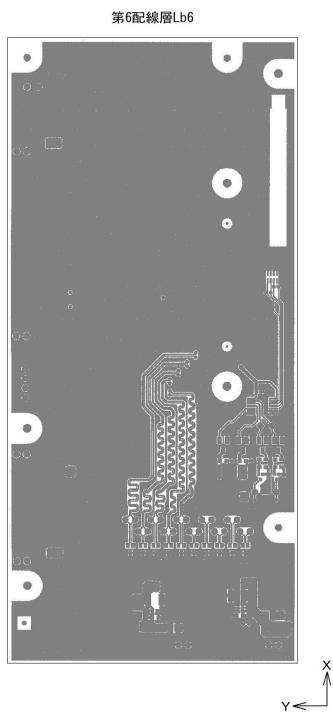

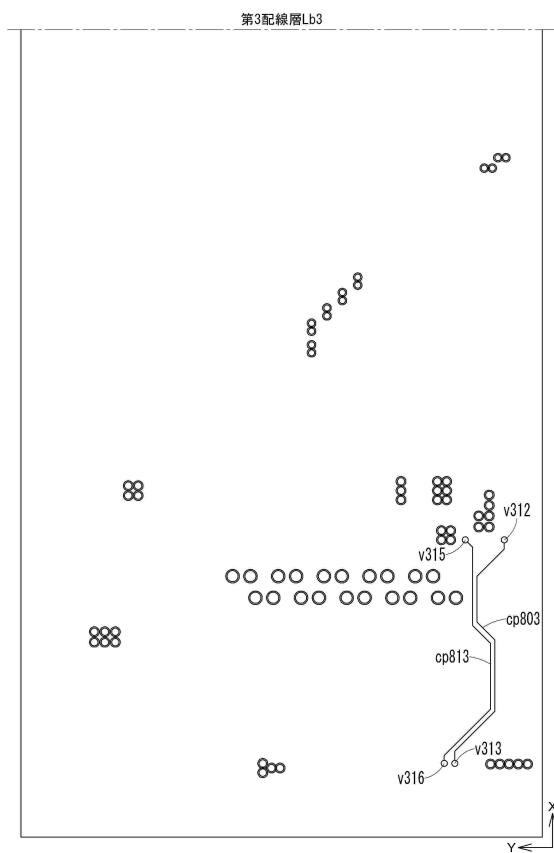

【図22】同液晶制御基板における第3配線層を示す図である。

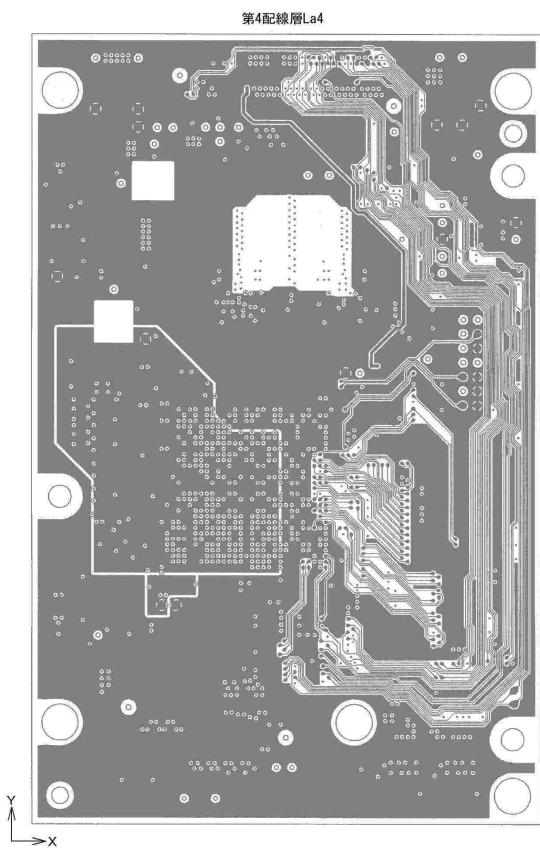

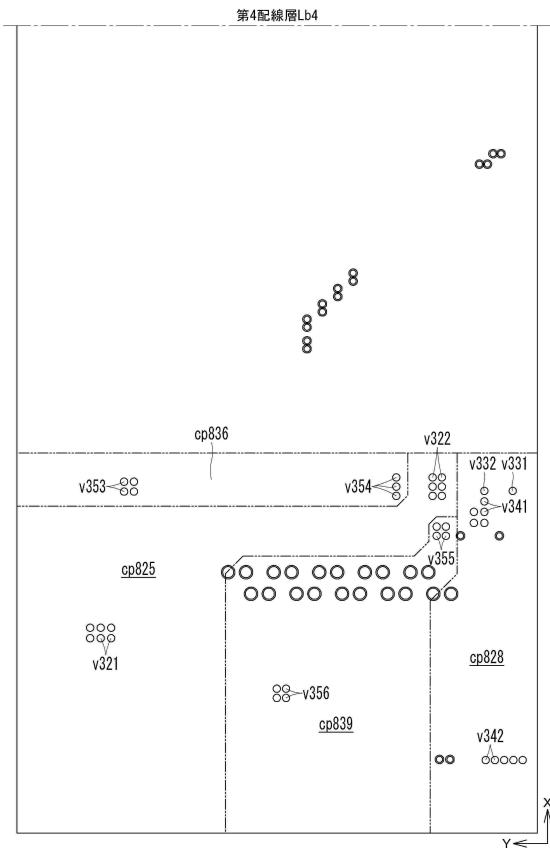

【図23】同液晶制御基板における第4配線層を示す図である。

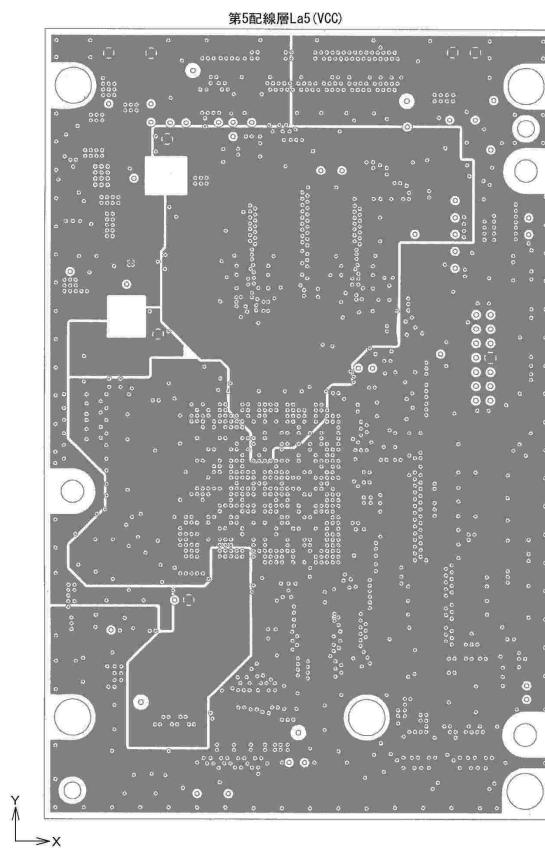

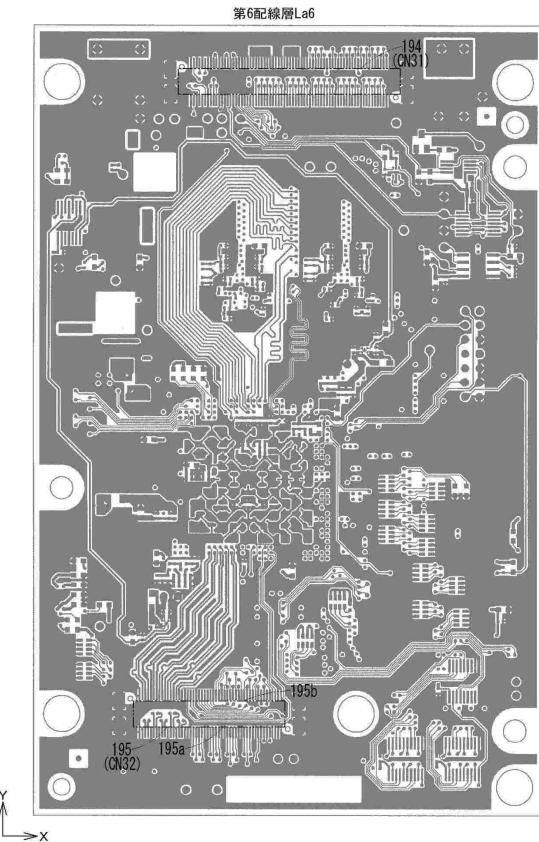

【図24】同液晶制御基板における第5配線層を示す図である。

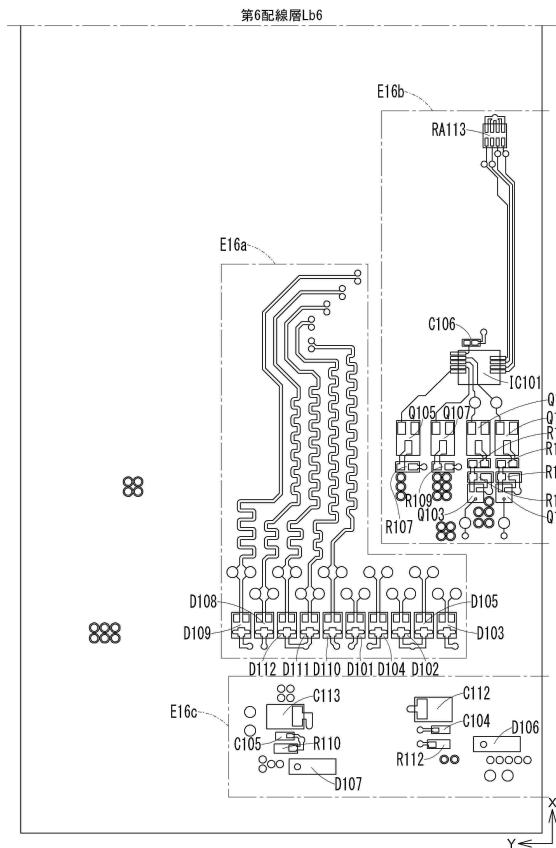

【図25】同液晶制御基板における第6配線層を示す図である。

【図26】同液晶制御基板に配置された複合チップの端子情報を示す図である。

10

20

30

40

50

- 【図 2 7】同液晶制御基板に配置された制御 ROM の端子情報を示す図である。

- 【図 2 8】同液晶制御基板の第 1 配線層から配線路 P 1 ~ P 7 1 を抽出した図である。

- 【図 2 9】同液晶制御基板の第 2 配線層から配線路 P 1 ~ P 7 1 を抽出した図である。

- 【図 3 0】同液晶制御基板の第 3 配線層から配線路 P 1 ~ P 7 1 を抽出した図である。

- 【図 3 1】同液晶制御基板の第 4 配線層から配線路 P 1 ~ P 7 1 を抽出した図である。

- 【図 3 2】同液晶制御基板の第 5 配線層から配線路 P 1 ~ P 7 1 を抽出した図である。

- 【図 3 3】同液晶制御基板の第 6 配線層から配線路 P 1 ~ P 7 1 を抽出した図である。

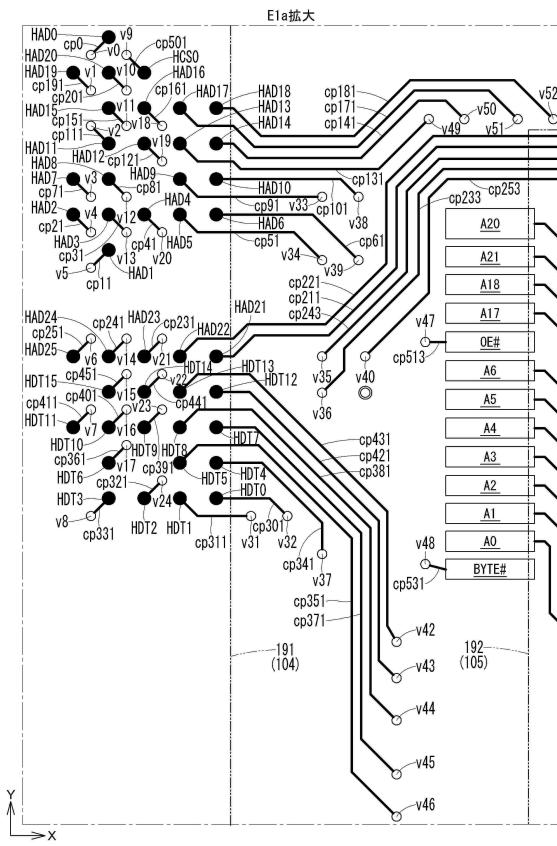

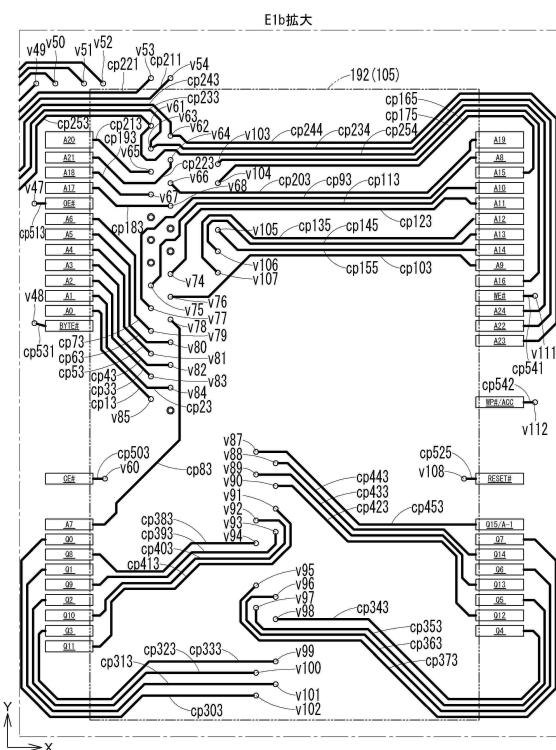

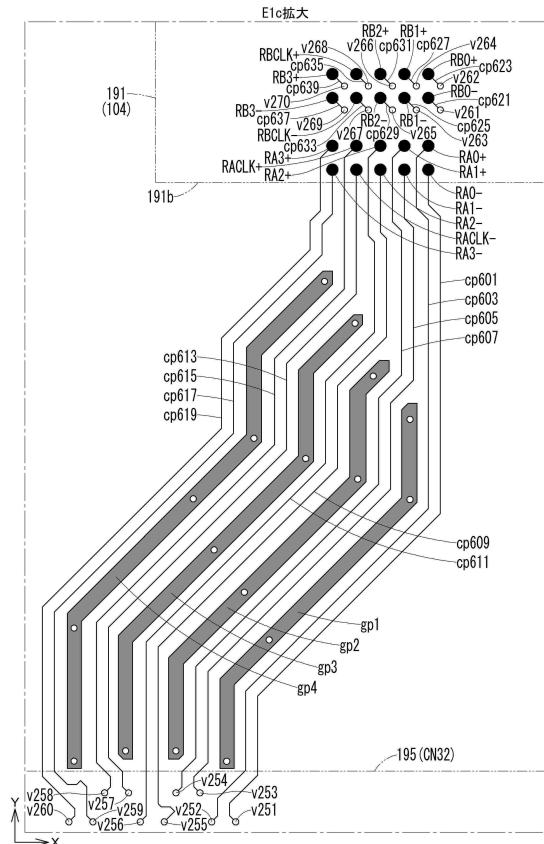

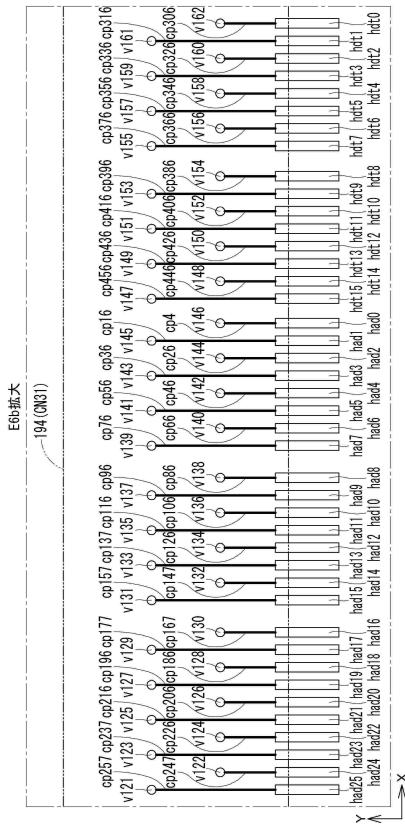

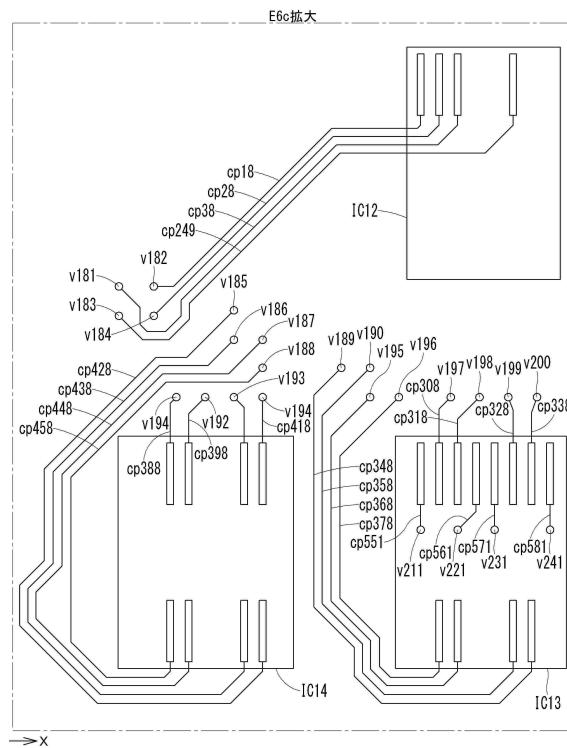

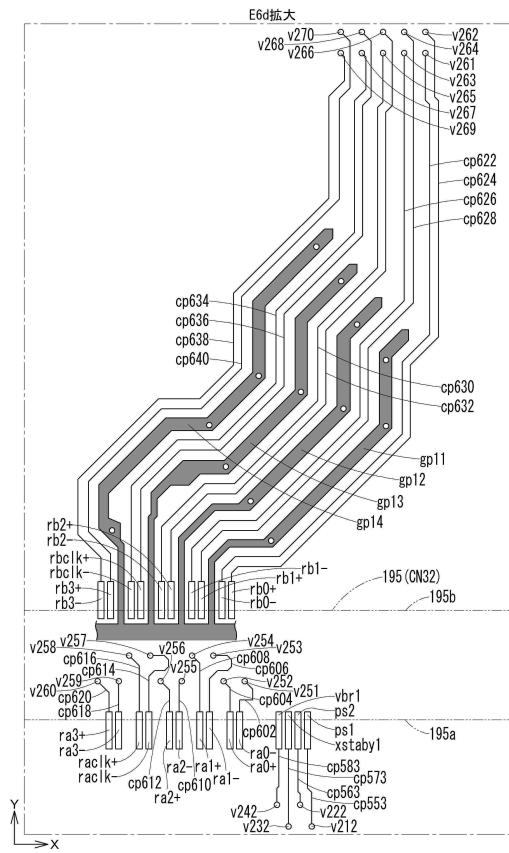

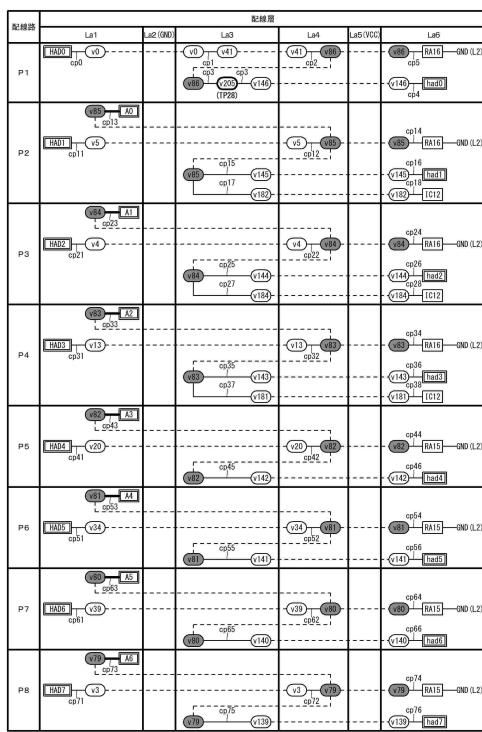

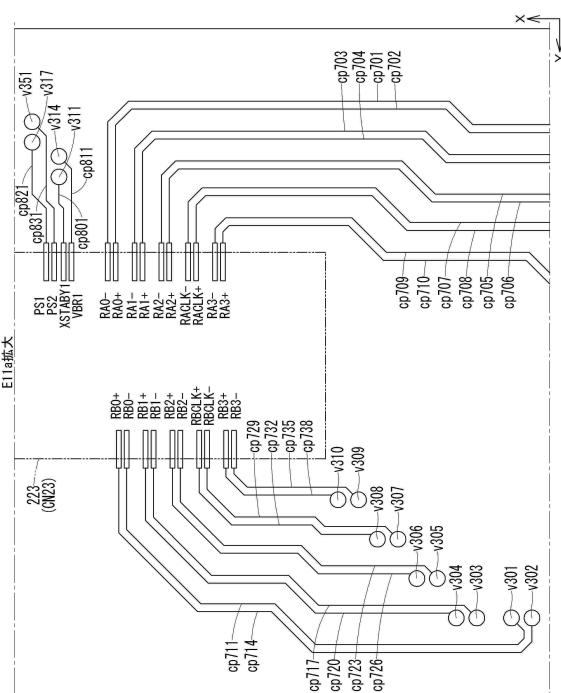

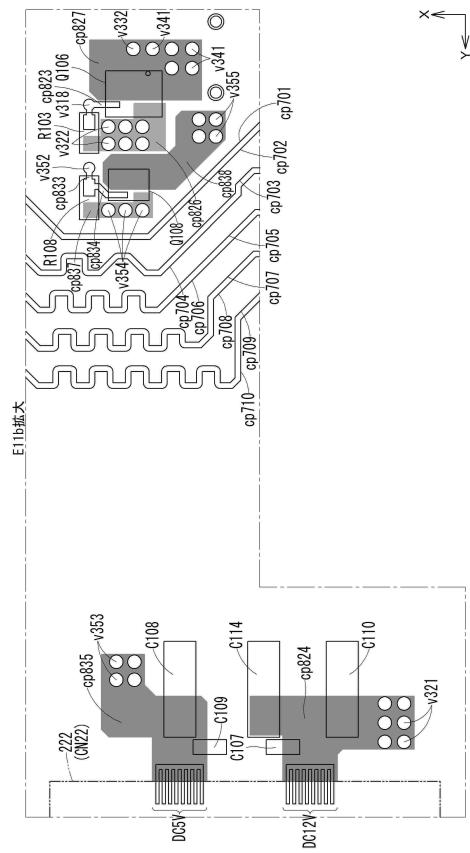

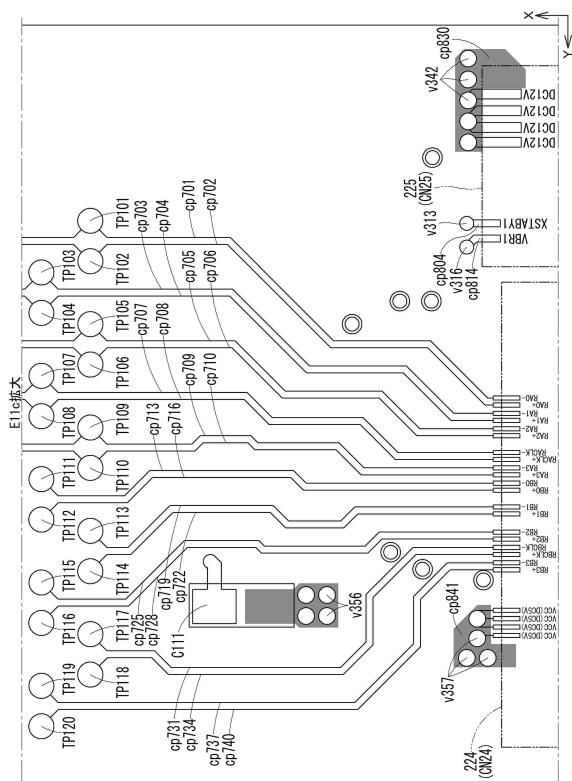

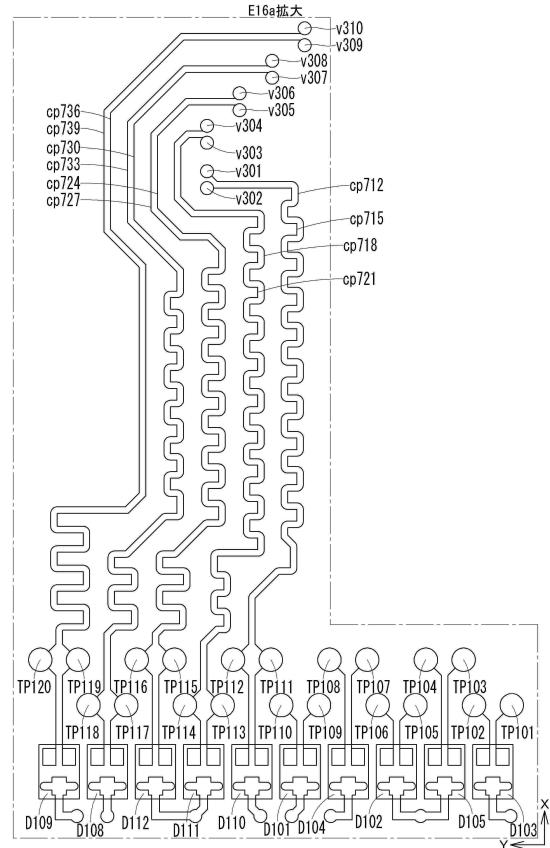

- 【図 3 4】図 2 8 における領域 E 1 a の拡大図である。

- 【図 3 5】図 2 8 における領域 E 1 b の拡大図である。

- 【図 3 6】図 2 8 における領域 E 1 c の拡大図である。

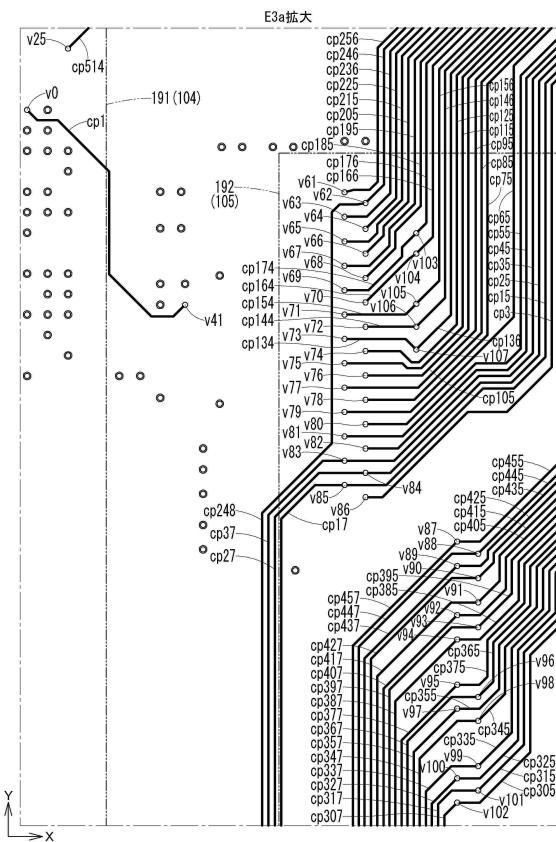

- 【図 3 7】図 3 0 における領域 E 3 a の拡大図である。

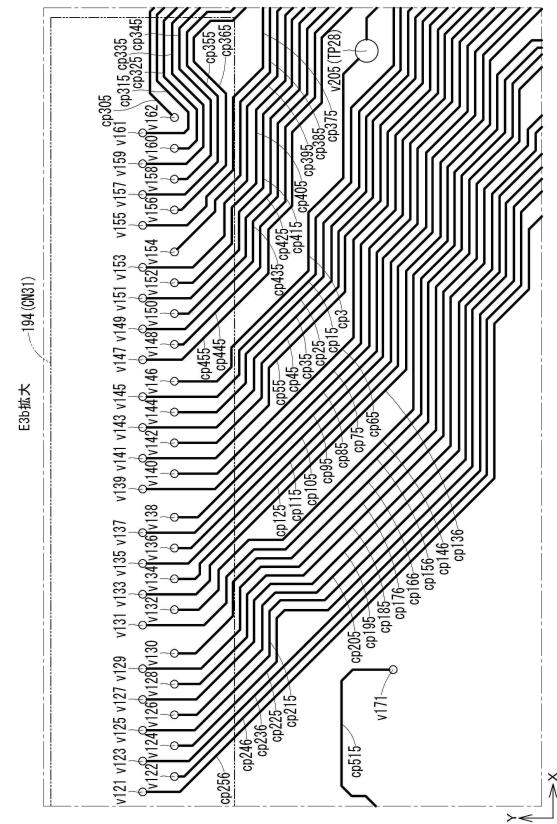

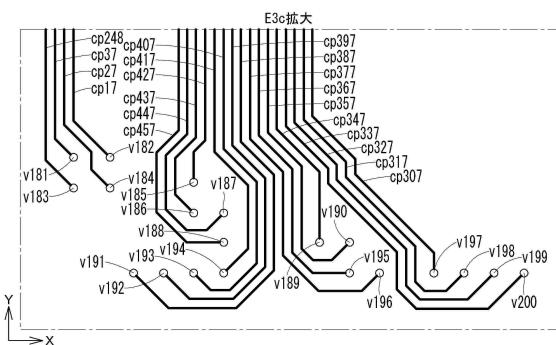

- 【図 3 8】図 3 0 における領域 E 3 b の拡大図である。

- 【図 3 9】図 3 0 における領域 E 3 c の拡大図である。

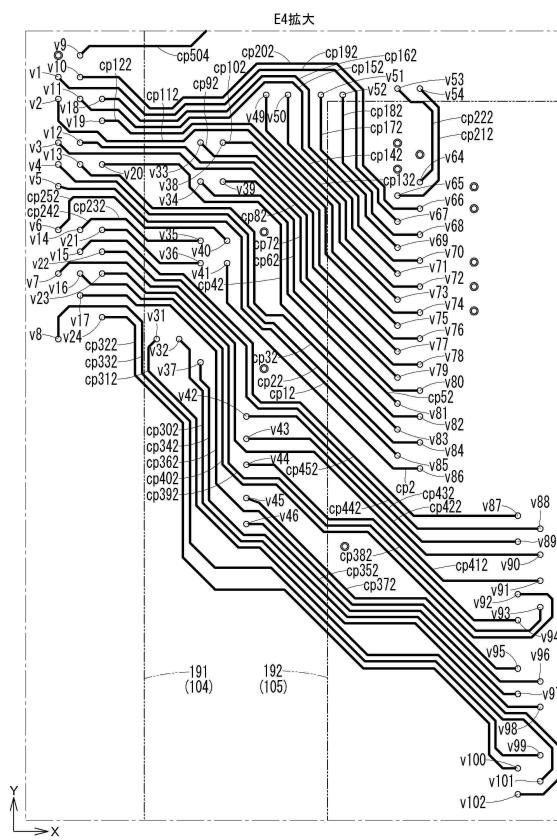

- 【図 4 0】図 3 1 における領域 E 4 の拡大図である。

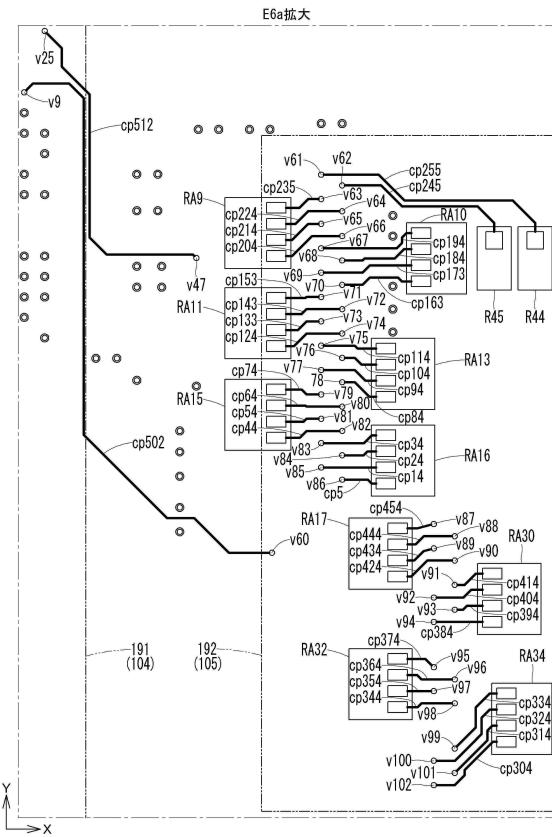

- 【図 4 1】図 3 3 における領域 E 6 a の拡大図である。

- 【図 4 2】図 3 3 における領域 E 6 b の拡大図である。

- 【図 4 3】図 3 3 における領域 E 6 c の拡大図である。

- 【図 4 4】図 3 3 における領域 E 6 d の拡大図である。

- 【図 4 5】本発明の第 1 の実施形態に係るパチンコ機の液晶制御基板における配線路 P 1 ~ P 8 の配線経路を模式的に示す図である。

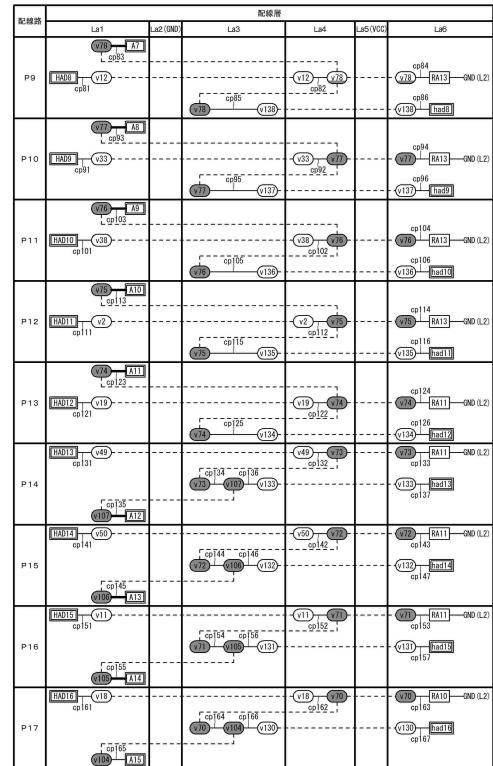

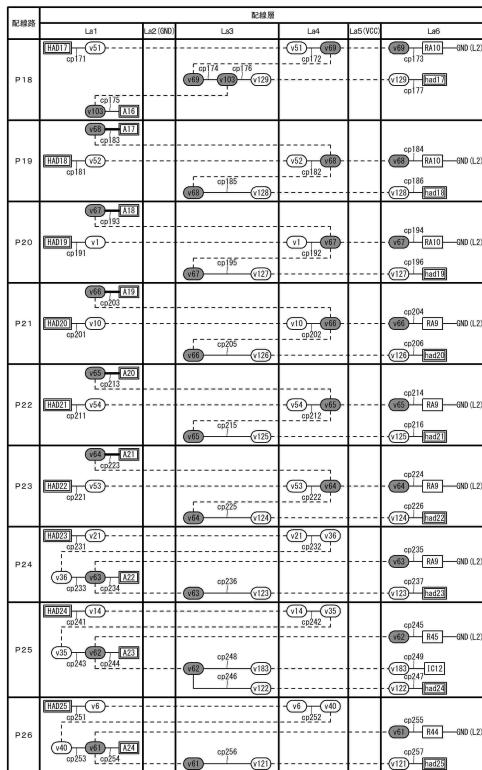

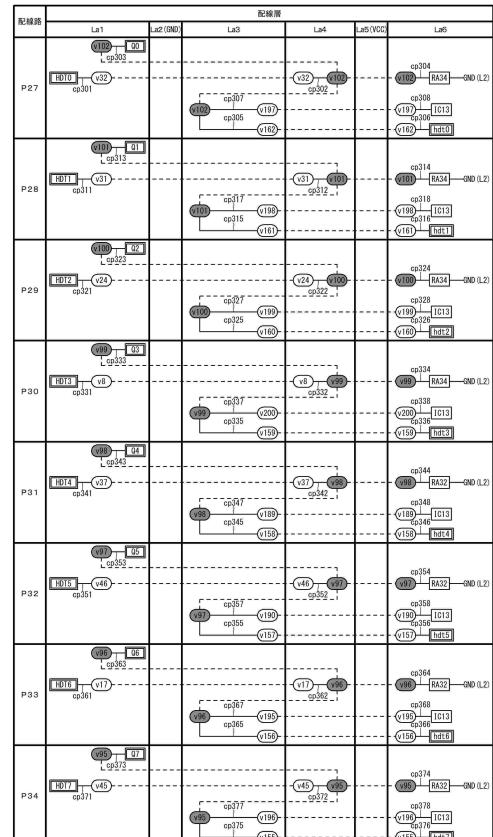

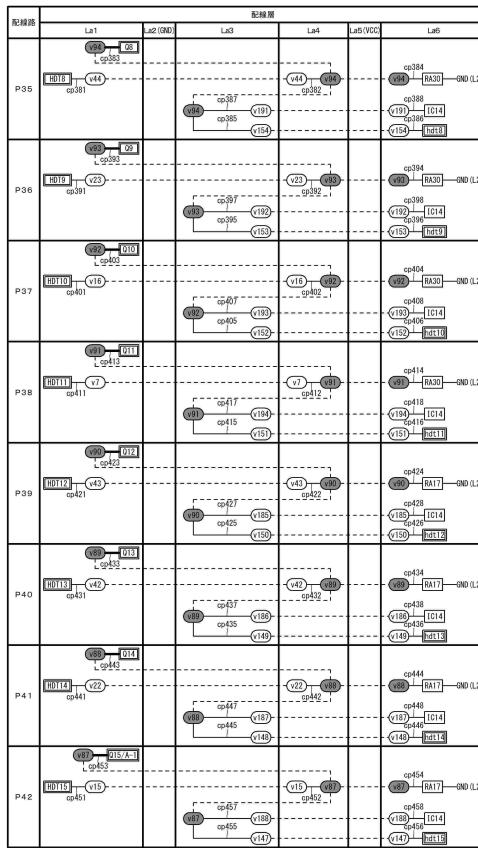

- 【図 4 6】同液晶制御基板における配線路 P 9 ~ P 1 7 を模式的に示す図である。

- 【図 4 7】同液晶制御基板における配線路 P 1 8 ~ P 2 6 を模式的に示す図である。

- 【図 4 8】同液晶制御基板における配線路 P 2 7 ~ P 3 4 を模式的に示す図である。

- 【図 4 9】同液晶制御基板における配線路 P 3 5 ~ P 4 2 を模式的に示す図である。

- 【図 5 0】同液晶制御基板における配線路 P 4 3 ~ P 4 7 を模式的に示す図である。

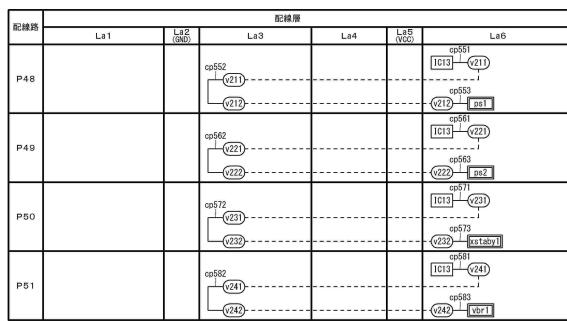

- 【図 5 1】同液晶制御基板における配線路 P 4 8 ~ P 5 1 を模式的に示す図である。

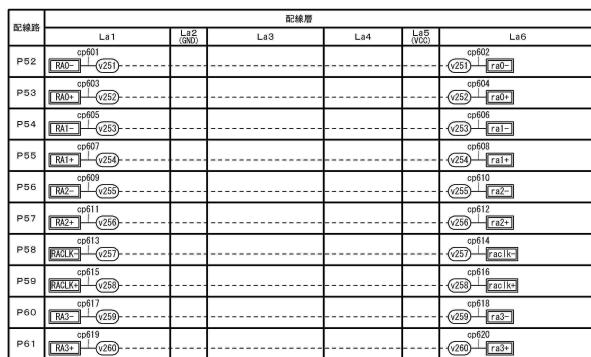

- 【図 5 2】同液晶制御基板における配線路 P 5 2 ~ P 6 1 を模式的に示す図である。

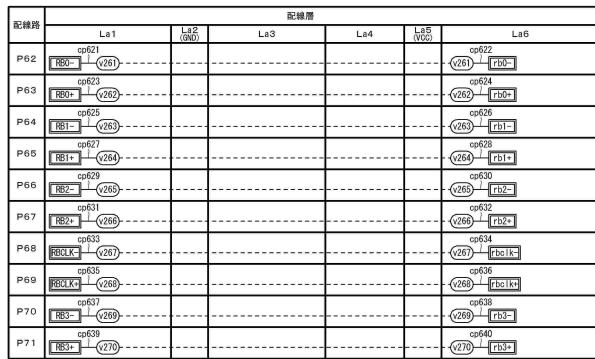

- 【図 5 3】同液晶制御基板における配線路 P 6 2 ~ P 7 1 を模式的に示す図である。

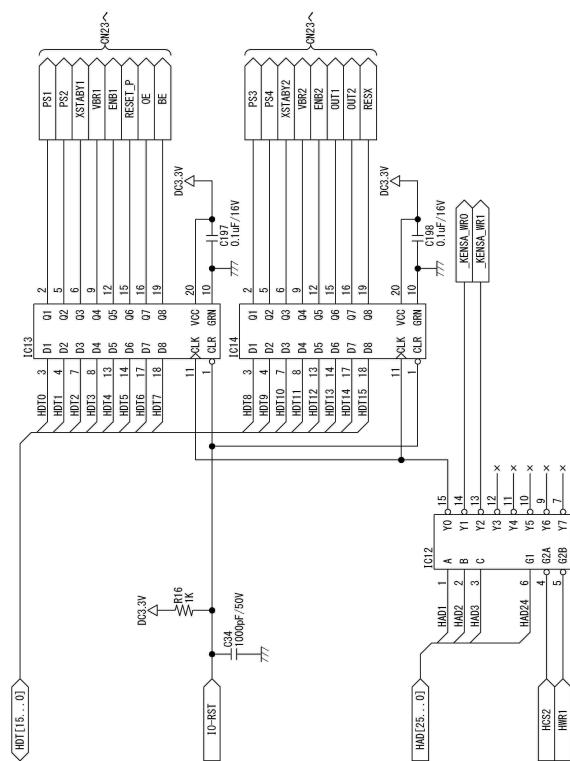

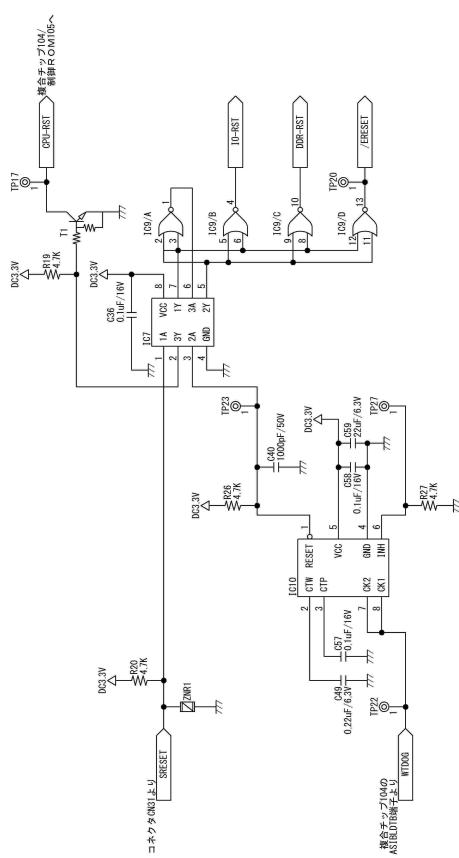

- 【図 5 4】同液晶制御基板におけるデコード回路の回路図である。

- 【図 5 5】同液晶制御基板におけるリセット回路の回路図である。

- 【図 5 6】同液晶制御基板における第 1 配線層側のシルク印刷パターンを示す図である。

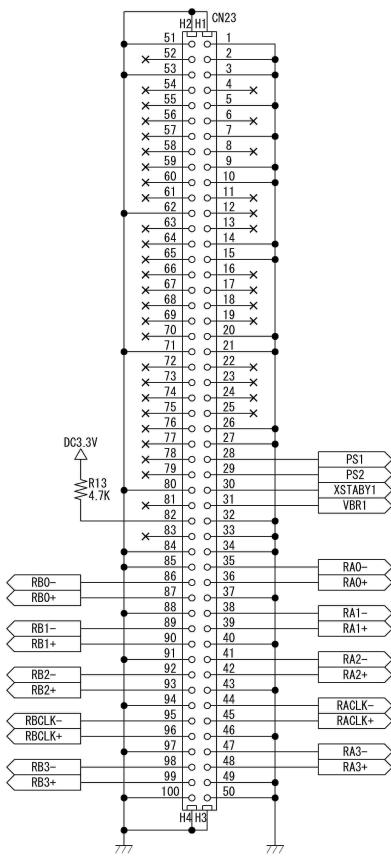

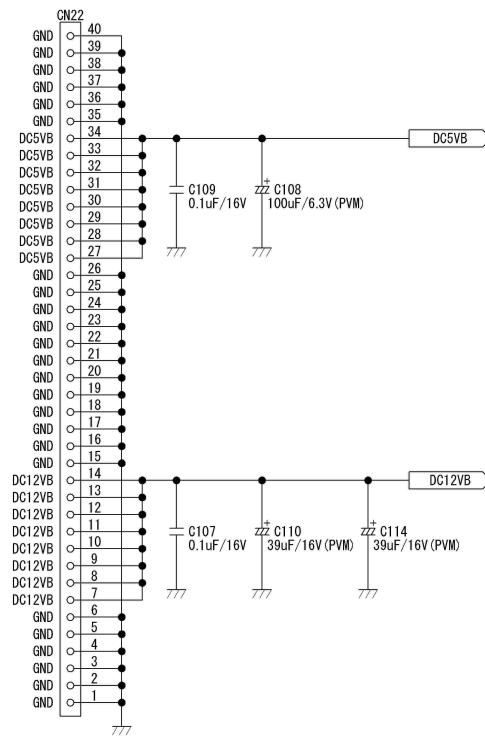

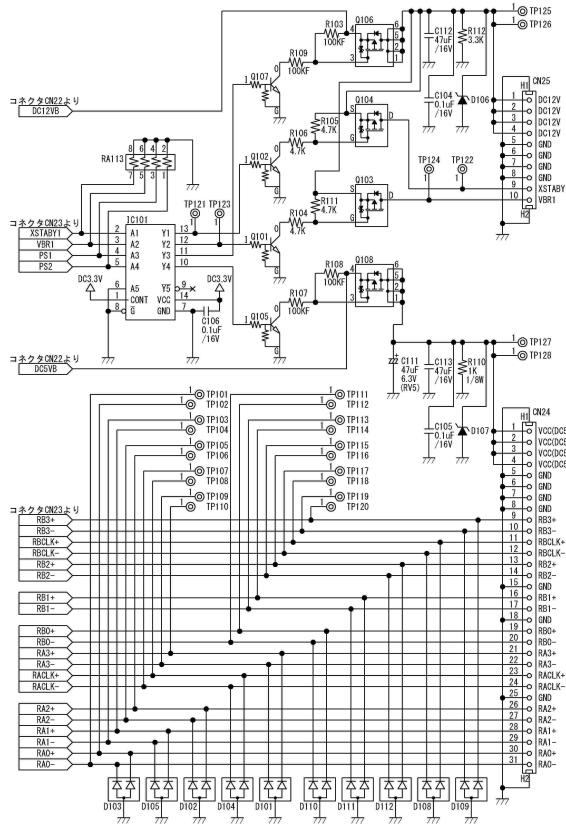

- 【図 5 7】同パチンコ機の液晶インターフェース基板における第 1 配線層を示す図である。

- 【図 5 8】同液晶インターフェース基板における第 2 , 第 5 配線層を示す図である。

- 【図 5 9】同液晶インターフェース基板における第 3 配線層を示す図である。

- 【図 6 0】同液晶インターフェース基板における第 4 配線層を示す図である。

- 【図 6 1】同液晶インターフェース基板における第 6 配線層を示す図である。

- 【図 6 2】同液晶インターフェース基板における第 1 配線層から配線路 P 1 0 1 ~ P 1 2 4 のみを抽出した図である。

- 【図 6 3】同液晶インターフェース基板の第 2 , 第 5 配線層から配線路 P 1 0 1 ~ P 1 2 4 を抽出した図である。

- 【図 6 4】同液晶インターフェース基板の第 3 配線層から配線路 P 1 0 1 ~ P 1 2 4 を抽出した図である。

- 【図 6 5】同液晶インターフェース基板の第 4 配線層から配線路 P 1 0 1 ~ P 1 2 4 を抽出した図である。

- 【図 6 6】同液晶インターフェース基板の第 6 配線層から配線路 P 1 0 1 ~ P 1 2 4 を抽出した図である。

- 【図 6 7】図 6 2 における領域 E 1 1 a の拡大図である。

- 【図 6 8】図 6 2 における領域 E 1 1 b の拡大図である。

- 【図 6 9】図 6 2 における領域 E 1 1 c の拡大図である。

- 【図 7 0】図 6 6 における領域 E 1 6 a の拡大図である。

10

20

30

40

50

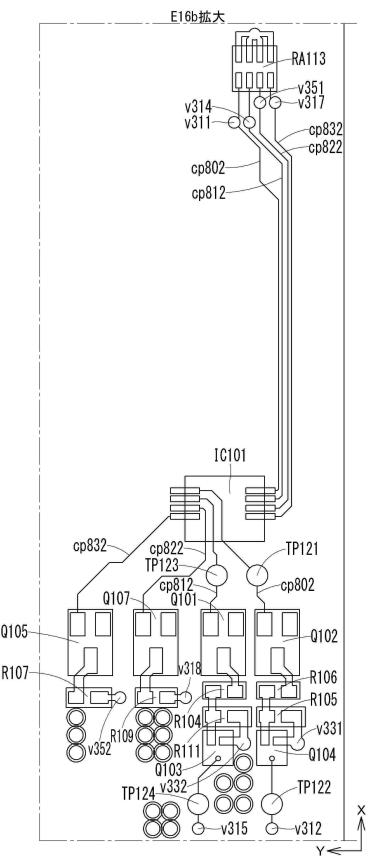

【図 7 1】図 6 6 における領域 E 1 6 b の拡大図である。

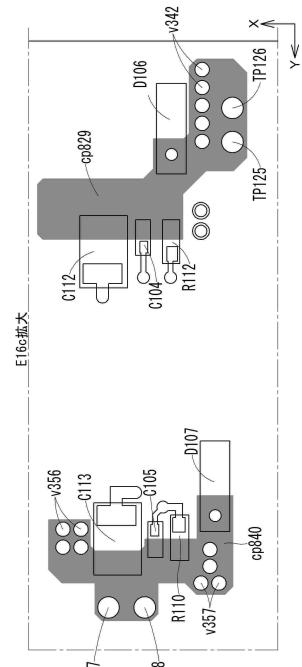

【図 7 2】図 6 6 における領域 E 1 6 c の拡大図である。

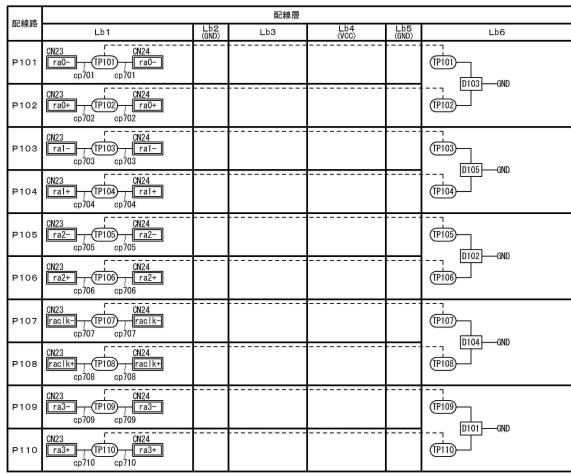

【図 7 3】本発明の第 1 の実施形態に係るパチンコ機の液晶インターフェース基板における配線路 P 1 0 1 ~ P 1 1 0 を模式的に示す図である。

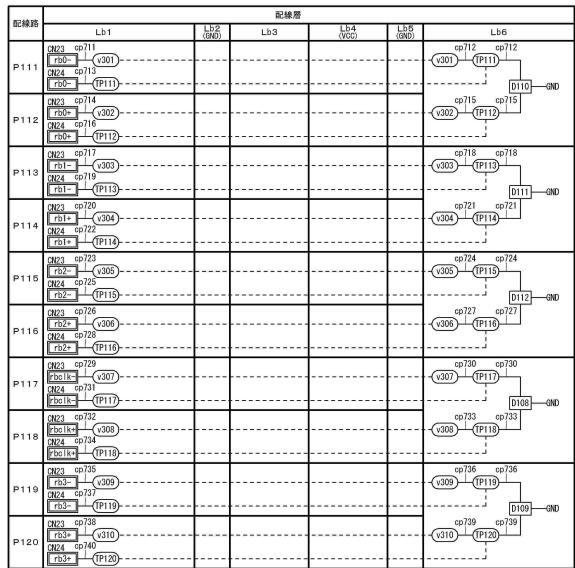

【図 7 4】同液晶インターフェース基板における配線路 P 1 1 1 ~ P 1 2 0 を模式的に示す図である。

【図 7 5】同液晶インターフェース基板における配線路 P 1 2 1 ~ P 1 2 4 を模式的に示す図である。

【図 7 6】同液晶インターフェース基板における液晶 I F 第 3 コネクタ近傍の回路図である。

【図 7 7】同液晶インターフェース基板における液晶 I F 第 2 コネクタ近傍の回路図である。

【図 7 8】同パチンコ機の液晶インターフェース基板における主要部の回路図である。

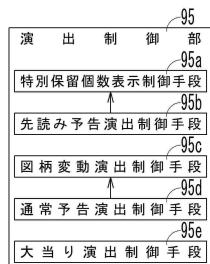

【図 7 9】同パチンコ機の演出制御部の概略構成を示すブロック図である。

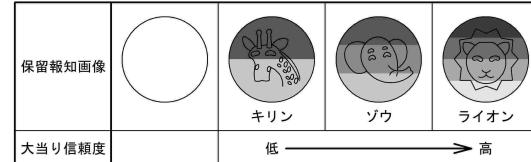

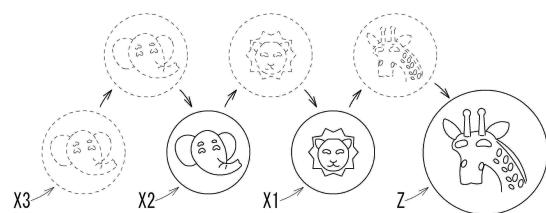

【図 8 0】同パチンコ機における保留報知画像の種類と大当たり信頼度とを示す図である。

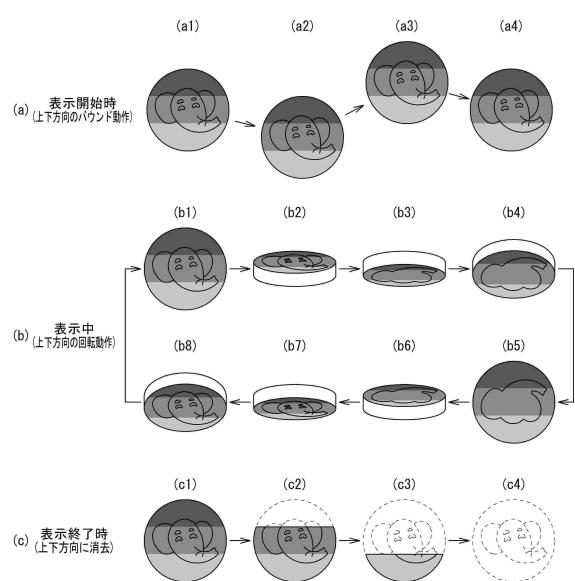

【図 8 1】同パチンコ機における保留報知画像の表示開始時、表示中及び表示終了時の動的表示の説明図である。

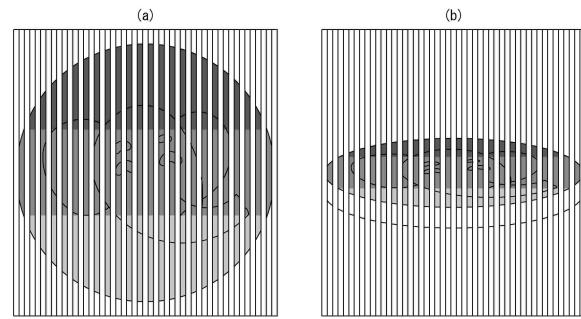

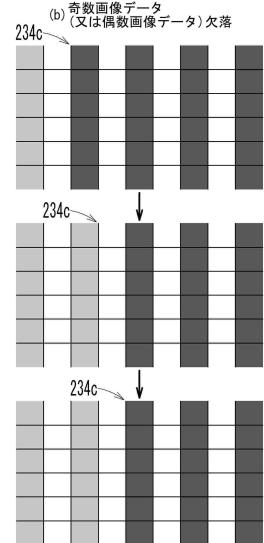

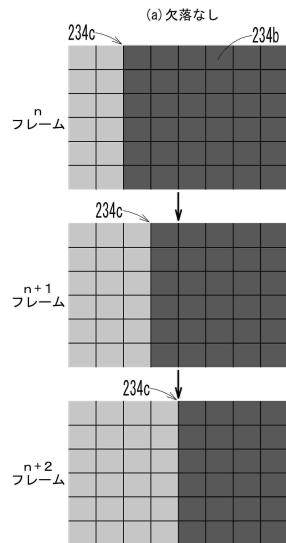

【図 8 2】同パチンコ機で奇数画像データと偶数画像データの何れかが欠落した場合の保留報知画像の表示状態を示す説明図である。

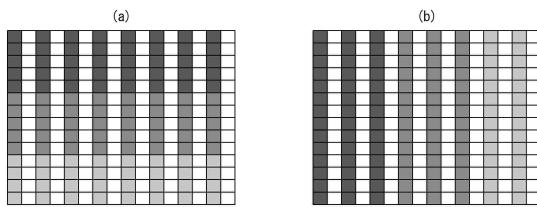

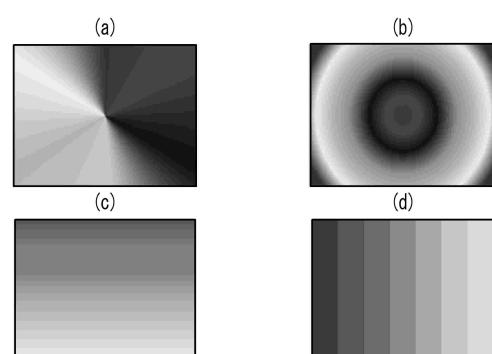

【図 8 3】同パチンコ機で奇数画像データと偶数画像データの何れかが欠落した場合の画素単位での色情報の分布を示す図であり、( a )は複数種類の色情報が縦方向に分布している場合を、( b )は同じく横方向に分布している場合を示している。

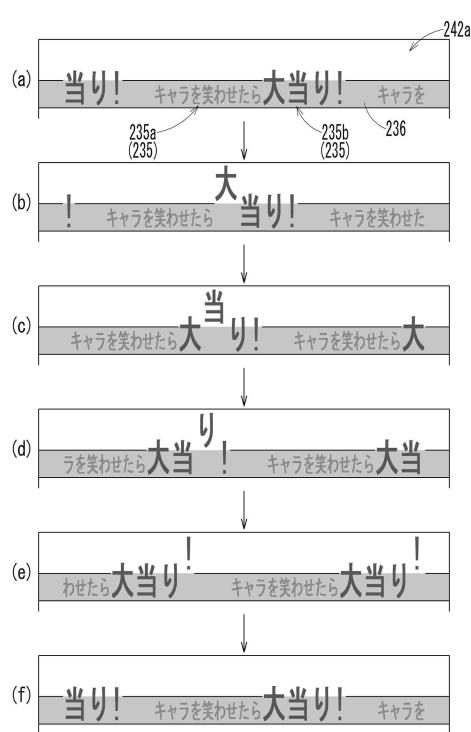

【図 8 4】同パチンコ機における保留報知画像のシフト時の動的表示の説明図である。

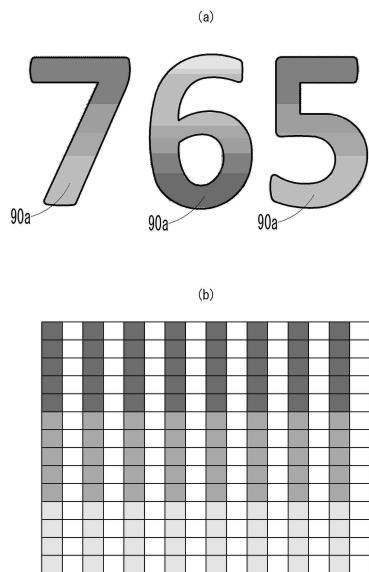

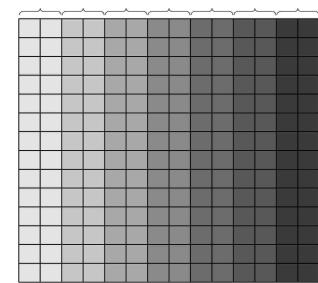

【図 8 5】同パチンコ機における装飾図柄の色分布を示す図である。

【図 8 6】同パチンコ機における装飾図柄の動的表示を示す図である。

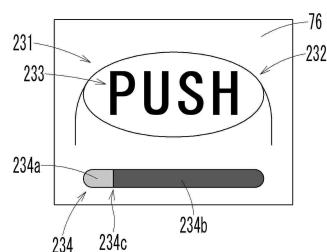

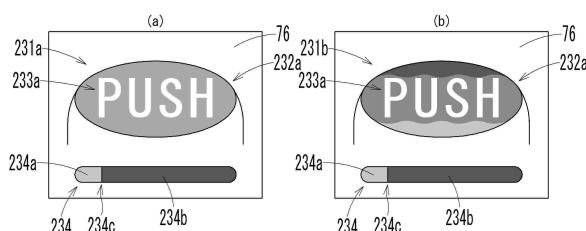

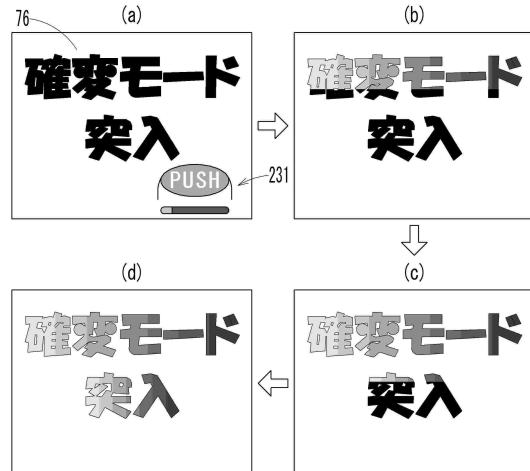

【図 8 7】同パチンコ機の操作誘導画像を示す図である。

【図 8 8】同パチンコ機の全面レインボー画像演出で用いられるレインボー背景画像の例を示す図である。

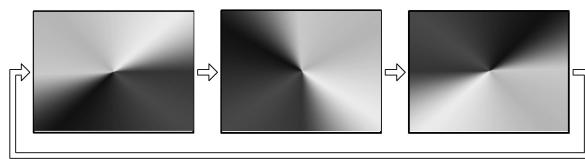

【図 8 9】同パチンコ機のレインボー背景画像の時間変化を示す図である。

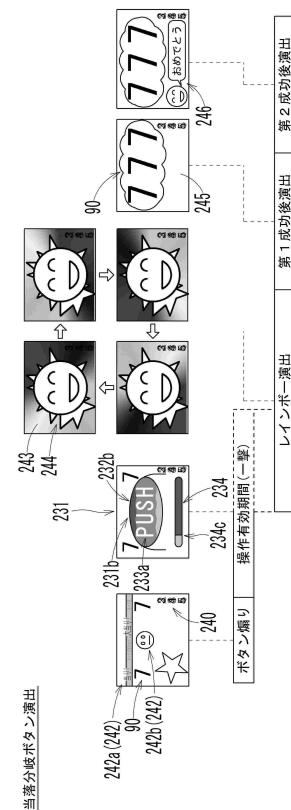

【図 9 0】同パチンコ機の当落分岐ボタン演出 N B 1 の具体例を示す図である。

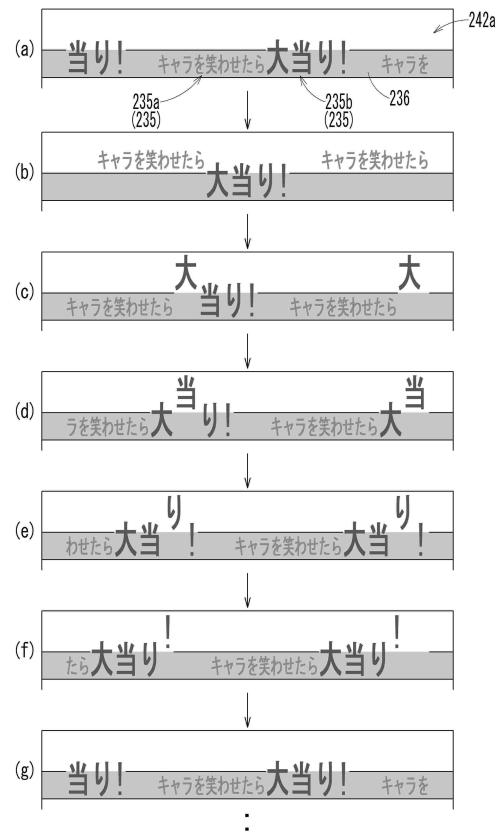

【図 9 1】同パチンコ機における帯演出画像の時間変化を示す図である。

【図 9 2】同パチンコ機における操作誘導画像の種類を示す図である。

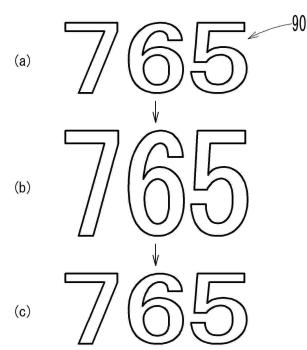

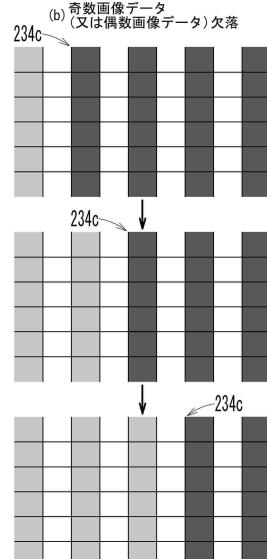

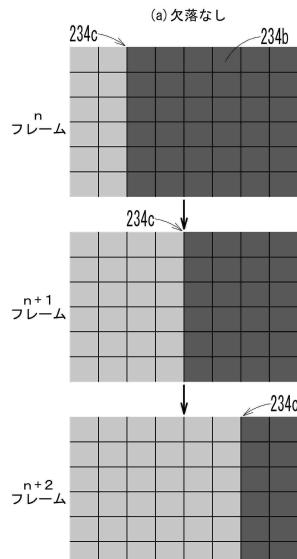

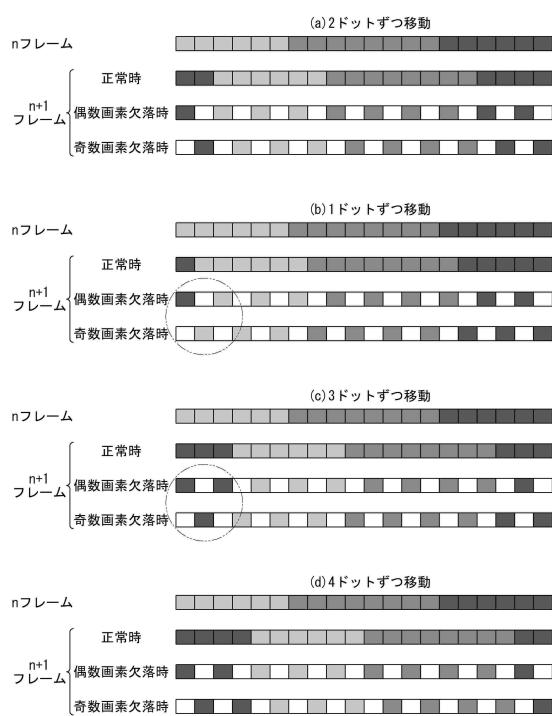

【図 9 3】同パチンコ機における操作有効期間報知画像の境界近傍での時間変化(1フレーム毎に2ドットずつ移動する場合)を示す図であり、( a )は画像データの欠落がない場合を、( b )は奇数画像データと偶数画像データの何れかが欠落した場合を示している。

【図 9 4】操作有効期間報知画像の境界が1フレーム毎に1ドットずつ移動する場合の時間変化を示す図であり、( a )は画像データの欠落がない場合を、( b )は奇数画像データと偶数画像データの何れかが欠落した場合を示している。

【図 9 5】同パチンコ機の部分レインボー画像演出において上下方向に色情報が変化する場合を示す図である。

【図 9 6】同パチンコ機の部分レインボー画像演出において左右方向に色情報が変化する場合を示す図である。

【図 9 7】同パチンコ機の設定示唆演出選択テーブルを示す図である。

【図 9 8】同パチンコ機の設定示唆演出における画面表示例を示す図である。

【図 9 9】同パチンコ機の位置及び時間に対して左右方向に変化するレインボー演出において1フレーム毎に所定ドットずつ移動する場合の正常時と偶数/奇数画素欠落時の画素単位での色分布を示す説明図である。

【図 1 0 0】本発明の第 2 の実施形態に係るパチンコ機における帯演出画像の時間変化を示す図である。

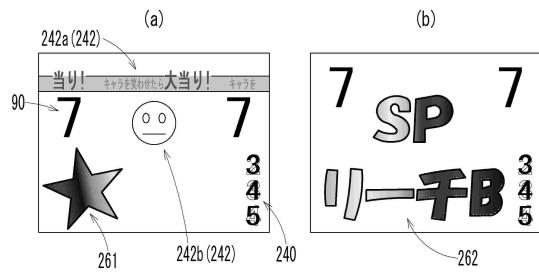

【図 1 0 1】( a )はリーチ演出中に表示される星形図形をレインボー画像とした例を、

10

20

30

40

50

(b) はリーチタイトル文字をレインボー画像とした例を示す図である。

【発明を実施するための最良の形態】

【0008】

以下、発明の実施形態を図面に基づいて詳述する。図1～図9は本発明をパチンコ機に採用した第1の実施形態を例示している。図1及び図2において、遊技機本体1は、外枠2と、この外枠2の前側に配置された前枠3とを備えている。前枠3は、左右方向一端側、例えば左端側に配置された上下方向の第1ヒンジ4を介して外枠2を開閉自在及び着脱自在に枢着されており、左右方向における第1ヒンジ4と反対側、例えば右端側に設けられた施錠手段5によって外枠2に対して閉状態で施錠可能となっている。

【0009】

前枠3は、内枠6と、その内枠6の前側に配置された前扉7とを備えている。前扉7は、左右方向一端側、例えば左端側に配置された上下方向の第2ヒンジ8を介して内枠6を開閉自在及び着脱自在に枢着されており、施錠手段5によって内枠6に対して閉状態で施錠可能となっている。

【0010】

外枠2は、図2に示すように左右一対の縦枠材2a, 2bと上下一対の横枠材2c, 2dとで矩形状に形成されている。外枠2の前側下部には、例えば合成樹脂製の前カバー部材9が、下横枠材2dの前縁に沿って左右の縦枠材2a, 2bの前側下部を連結するように装着されている。前カバー部材9は、左右の縦枠材2a, 2bよりも前側に突出しており、その上側に内枠6が配置されている。また外枠2には、第1ヒンジ4を構成する外枠上ヒンジ金具11が例えば左上部に、同じく外枠下ヒンジ金具12が左下部における前カバー部材9の上側に夫々配置されている。

【0011】

内枠6は合成樹脂製で、前カバー部材9の上側で外枠2の前縁側に略当接可能な矩形状の枠部13と、この枠部13内の上部側に設けられた遊技盤装着部14と、枠部13内の下部側に設けられた下部装着部15とを例えば一体に備えている。遊技盤装着部14には、遊技盤16が例えば前側から着脱自在に装着され、下部装着部15には、その前側に発射手段17、下部スピーカ18等が配置されている。また内枠6には、第1ヒンジ4を構成する本体枠上ヒンジ金具19と第2ヒンジ8を構成する本体枠上ヒンジ金具20とが例えば左上部に、第1, 第2ヒンジ4, 8を構成する本体枠下ヒンジ金具21が例えば左下部に夫々配置されている。

【0012】

前扉7は、内枠6の前面側に対応する矩形状に形成された樹脂製の扉ベース22を備えている。この扉ベース22には、遊技盤16に形成された遊技領域23の前側に対応してガラス窓24の窓孔24aが形成されると共に、例えば窓孔24aの周囲に複数（ここでは4つ）の上部スピーカ25、枠第1可動演出手段26、枠第2可動演出手段27、送風手段28等の各種演出手段が配置されている。

【0013】

扉ベース22の上部前側には、窓孔24aの外周の少なくとも一部、例えば窓孔24aの上側から右側に対応する正面視逆L字型の部分にサイドユニット30が装着されている（図1, 図3）。サイドユニット30は、図2, 図3等に示すように、前枠3を開いた状態で、特殊な工具を使用することなく、前枠3の裏側の固定ネジ30a、固定レバー30b等を操作することにより容易に着脱が可能となっている。サイドユニット30の前面側には、図1に示すように、枠第1可動体26aを有する枠第1可動演出手段26、枠第2可動体27aを有する枠第2可動演出手段27、送風手段28等の演出手段が搭載されている。

【0014】

枠第1可動演出手段26の枠第1可動体26aは、任意の立体形状（ここでは蝶をモチーフとした形状）に形成され、図外の駆動手段の駆動によって略前後方向へのスライド移動が可能となっている。枠第2可動演出手段27の枠第2可動体27aは、図外の駆動手

10

20

30

40

50

段の駆動による略前後方向へのスライド移動と、把持部 27b 内に配置された図外の振動手段による振動動作とが可能であり、また遊技者による把持部 27b の押し込み操作が可能となっている。また送風手段 28 は、遊技者が把持部 27b を把持するタイミングで、遊技者の手に向けて送風することが可能となっている。また、サイドユニット 30 を含む前扉 7 の前面側には、多数の LED 301a ~ 301d よりなる枠ランプ 304 が、ガラス窓（表示窓）24 を略取り囲むように配置されている。

【0015】

扉ベース 22 の下部前側には、内枠 6 の後側に配置された払出手段 32 から払い出された遊技球を貯留して発射手段 17 に供給する上皿 33、その上皿 33 が満杯のときの余剰球等を貯留する下皿 34、発射手段 17 を作動させるために操作する発射ハンドル 35 等が配置され、更に上皿 33、下皿 34 等を前側から略覆う下装飾カバー 36 が装着されている。下装飾カバー 36 は、例えば前向きの膨出状に形成されており、例えばその上部側に、操作演出手段 37、十字操作ボタン 38、音量調整ボタン 39、光量調整ボタン 40 等の各種操作手段が設けられている（図 4）。操作演出手段 37 は、図柄変動中の予告演出、その他の演出に用いられるもので、遊技者が押下操作可能な上下動式の演出ボタン 41 を備えている。

10

【0016】

扉ベース 22 の背面側には、図 2 に示すように窓孔 24a を後側から略塞ぐガラスユニット 50 が着脱自在に装着されると共に、第 1、第 2 ヒンジ 4、8 側の縁部に沿って配置される上下方向のヒンジ端側補強板金 51a と、開閉端側の縁部に沿って配置される上下方向の開閉端側補強板金 51b と、窓孔 24a の下側に配置される左右方向の下部補強板金 51c とがねじ止め等により着脱自在に固定されている。また扉ベース 22 には、第 2 ヒンジ 8 を構成するガラス扉上ヒンジ金具 52a が例えば左上部に、同じくガラス扉下ヒンジ金具 52b が例えば左下部に夫々配置されている。

20

【0017】

また、例えば下部補強板金 51c の背面側には、球送りユニット 53a、下皿案内ユニット 53b 等が装着されている。球送りユニット 53a は、上皿 33 内の遊技球を発射手段 17 に供給するためのもので、内枠 6 側に配置された発射手段 17 の前側に対応して配置されており、発射手段 17 の発射動作と同期して球送りソレノイド 53c を作動させることにより、上皿 33 内の遊技球を 1 個ずつ発射手段 17 の発射レール 17a 上に供給するようになっている。

30

【0018】

なお発射手段 17 は、正面視で左上がりの傾斜状に配置された発射レール 17a と、球送りユニット 53a により発射レール 17a 上に供給された遊技球を発射待機位置で支持する発射球ストッパ 17b と、発射レール 17a 上の発射待機位置に対応して配置され且つ前後方向の駆動軸廻りに搖動可能な打撃槌 17c と、打撃槌 17c を搖動駆動するロータリソレノイド等の発射駆動手段 17d とを備え、発射ハンドル 35 が回転操作されたときに、その操作量に応じた発射強度で発射駆動手段 17d により打撃槌 17c を打撃方向（時計方向）に連続的に駆動するようになっている。

40

【0019】

下皿案内ユニット 53b は、上皿 33 が満杯となったときの余剰球、及び発射手段 17 により発射されたにも拘わらず遊技領域 23 に達することなく戻ってきたファール球を下皿 34 に案内するためのもので、例えば球送りユニット 53a に隣接してその第 1、第 2 ヒンジ 4、8 側に配置されている。

【0020】

遊技盤 16 は、図 5 に示すように、ベニヤ板、ポリカーボネート板等よりなるベース板 55 を備え、そのベース板 55 の前側に、発射手段 17 から発射された遊技球を案内するガイドレール 56 が環状に配置されると共に、そのガイドレール 56 の内側の遊技領域 23 に、中央表示枠ユニット 57、始動入賞ユニット 58、普通入賞ユニット 59 等のユニット部品の他、多数の遊技釘（図示省略）が配置され、また、例えば遊技領域 23 の外側

50

下部には遊技情報表示手段 6 0 が配置されている。

【 0 0 2 1 】

遊技情報表示手段 6 0 は、図 6 に示すように、8 個の L E D 7 0 で構成される L E D グループを 4 つ備えており、それら計 3 2 個の L E D 7 0 が普通図柄表示手段 6 1、普通保留個数表示手段 6 2、第 1 特別図柄表示手段 6 3、第 2 特別図柄表示手段 6 4、第 1 特別保留個数表示手段 6 5、第 2 特別保留個数表示手段 6 6、変動短縮報知手段 6 7、右打ち報知手段 6 8 及びラウンド数報知手段 6 9 に所定個数ずつ割り当てられている。即ち、第 1、第 2 L E D グループ 6 0 a, 6 0 b に属する各 8 個の L E D 7 0 は夫々第 1、第 2 特別図柄表示手段 6 3, 6 4 を構成し、第 3 L E D グループ 6 0 c に属する 8 個の L E D 7 0 は、2 個ずつに分けられて夫々第 1 特別保留個数表示手段 6 5、第 2 特別保留個数表示手段 6 6、普通保留個数表示手段 6 2、変動短縮報知手段 6 7 を構成し、第 4 L E D グループ 6 0 d に属する 8 個の L E D 7 0 は、2 個が普通図柄表示手段 6 1 を、他の 2 個が右打ち報知手段 6 8 を、残りの 4 個がラウンド数報知手段 6 9 を夫々構成している。

【 0 0 2 2 】

遊技盤 1 6 の複数のユニット部品 5 7 ~ 5 9 上には、普通図柄始動手段 7 1、第 1 特別図柄始動手段 7 2、第 2 特別図柄始動手段 7 3、大入賞手段 7 4、複数の普通入賞手段 7 5 等が設けられている。またベース板 5 5 の後側には、液晶表示手段（画像表示手段）7 6 の他、液晶表示手段 7 6 の前側を移動可能な可動役物 7 7 a を備えた盤可動演出手段 7 7 等が配置されている。

【 0 0 2 3 】

可動役物 7 7 a は、横長状の矩形箱形に形成され、その左右両端側が、液晶表示手段 7 6 の側縁部外側で上下動可能に支持されており、図外の駆動手段の駆動により、液晶表示手段 7 6 の上側の原点位置（図 5 参照）と液晶表示手段 7 6 の前側の動作位置との間で昇降移動可能となっている。また、可動役物 7 7 a の前面側には、複数の L E D 3 1 1 よりなる可動役物ランプ 3 1 4 が配置されている。

【 0 0 2 4 】

中央表示枠ユニット 5 7 は、液晶表示手段 7 6 及び可動役物 7 7 a の表示枠を構成するもので、後側の液晶表示手段 7 6 に対応する開口窓 8 0 が略中央に形成されており、ベース板 5 5 に形成された前後方向貫通状の装着孔（図示省略）に対して前側から着脱自在に装着されている。この中央表示枠ユニット 5 7 は、図 5 に示すように、ベース板 5 5 の前面に沿って装着孔の外側に配置され且つその前側を遊技球が通過可能な前面装着板 8 1 と、液晶表示手段 7 6 の前側における左右両側から上部側にわたる正面視略門形状に配置され且つ前面装着板 8 1 の内周側で前向きに突設された装飾枠 8 2 と、その装飾枠 8 2 の左右の下端部間に配置されるステージ 8 3 とを備えている。発射手段 1 7 により発射され、遊技領域 2 3 の上部側に進入した遊技球は、装飾枠 8 2 の頂部で左右に振り分けられ、中央表示枠ユニット 5 7 の左側の左流下経路 8 4 a と右側の右流下経路 8 4 b との何れかを流下する。

【 0 0 2 5 】

中央表示枠ユニット 5 7 には、左流下経路 8 4 a 側と右流下経路 8 4 b 側との少なくとも一方側、例えば左流下経路 8 4 a 側に、遊技球が流入可能なワープ入口 8 5 が設けられている。左流下経路 8 4 a を流下中にワープ入口 8 5 に流入した遊技球は、ステージ 8 3 上で左右方向に自由に転動した後、遊技領域 2 3 の左右方向中央に対応して設けられた中央落下部 8 6 とそれ以外の部分との何れかから前側に落下する。

【 0 0 2 6 】

また、中央表示枠ユニット 5 7 の前面側には、多数の L E D 3 2 1 a ~ 3 2 1 c よりなる盤ランプ 3 2 4 が、液晶表示手段 7 6 の外周の少なくとも一部、例えば左右両側及び上側に対応して配置されている。なお、始動入賞ユニット 5 8、普通入賞ユニット 5 9 等にも盤ランプ 3 2 4 の一部を配置してもよい。

【 0 0 2 7 】

始動入賞ユニット 5 8 は、図 5 に示すように中央表示枠ユニット 5 7 の下側にガイドレ

10

20

30

40

50

ール 5 6 に沿って配置され、ベース板 5 5 に対して前側から着脱自在に装着されている。普通入賞ユニット 5 9 は、図 5 に示すように中央表示枠ユニット 5 7 の下側で始動入賞ユニット 5 8 の左側にガイドレール 5 6 に沿って配置され、ベース板 5 5 に対して前側から着脱自在に装着されている。

#### 【 0 0 2 8 】

普通図柄始動手段 7 1 は、普通図柄表示手段 6 1 による普通図柄の変動表示を開始させるためのもので、遊技球が通過可能な通過ゲート等により構成され、遊技球の通過を検出する遊技球検出スイッチ（図示省略）を備えている。この普通図柄始動手段 7 1 は、図 5 に示すように例えば中央表示枠ユニット 5 7 の右部における前面装着板 8 1 の前側に設けられており、右流下経路 8 4 b を流下する遊技球が通過可能となっている。

10

#### 【 0 0 2 9 】

普通図柄表示手段 6 1 は、普通図柄を変動表示するためのもので、図 6 に示すように遊技情報表示手段 6 0 における所定個数（ここでは 2 個）の LED 7 0 で構成されており、普通図柄始動手段 7 1 が遊技球を検出することに基づいて、普通図柄を構成するそれら 2 個の LED 7 0 が普通変動中発光パターンで発光した後、普通図柄始動手段 7 1 による遊技球検出時に取得された普通乱数情報に含まれる当り判定乱数値が予め定められた当り判定値と一致する場合には当り態様で、それ以外の場合にははずれ態様で変動を停止する。なお、普通図柄を構成する 2 個の LED 7 0 は、それらの発光態様（例えば点灯 / 消灯）の組み合わせにより一又は複数の当り態様と一又は複数のはずれ態様とを表示可能であり、また普通変動中発光パターンは、例えば特定の複数種類（ここでは 2 種類）の発光態様を所定時間（例えば 128 ms）毎に切り替えるようになっている。

20

#### 【 0 0 3 0 】

また、普通図柄表示手段 6 1 の図柄変動中と普通利益状態中とを含む普通保留期間中に普通図柄始動手段 7 1 が遊技球を検出した場合には、それによって取得された普通乱数情報が予め定められた上限保留個数、例えば 4 個を限度として保留記憶され、普通保留期間が終了する毎に 1 個ずつ消化されて普通図柄の変動が行われる。普通乱数情報の記憶個数（普通保留個数）は、普通保留個数表示手段 6 2 等によって遊技者に報知される。普通保留個数表示手段 6 2 は、図 6 に示すように遊技情報表示手段 6 0 における所定個数（ここでは 2 個）の LED 7 0 で構成されており、それら 2 個の LED 7 0 の夫々の発光態様（例えば点灯 / 点滅 / 消灯）の組み合わせにより、0 ~ 4 個の 5 種類の普通保留個数を表示可能となっている。

30

#### 【 0 0 3 1 】

第 1 特別図柄始動手段 7 2 は、第 1 特別図柄表示手段 6 3 による図柄変動を開始させるためのもので、開閉手段を有しない非開閉式入賞手段により構成され、入賞した遊技球を検出する遊技球検出スイッチ（図示省略）を備えている。この第 1 特別図柄始動手段 7 2 は、図 5 に示すように例えば始動入賞ユニット 5 8 に設けられ、ステージ 8 3 の中央落下部 8 6 に対応してその下側に上向き開口状に配置されており、左流下経路 8 4 a 側のワープ入口 8 5 からステージ 8 3 を経て入賞するルートが存在すること等により、右流下経路 8 4 b を流下してきた遊技球よりも左流下経路 8 4 a を流下してきた遊技球の方が高い確率で入賞可能となっている。なお、この第 1 特別図柄始動手段 7 2 に遊技球が入賞すると、一入賞当り所定個数の遊技球が賞球として払い出される。

40

#### 【 0 0 3 2 】

第 2 特別図柄始動手段 7 3 は、第 2 特別図柄表示手段 6 4 による図柄変動を開始させるためのもので、開閉部 8 8 の作動によって遊技球が入賞可能な開状態と入賞不可能（又は開状態よりも入賞困難）な閉状態とに変化可能な開閉式入賞手段により構成され、入賞した遊技球を検出する遊技球検出スイッチ（図示省略）と、開閉部 8 8 を開閉する電磁ソレノイド等の開閉駆動手段とを備えており、普通図柄表示手段 6 1 の変動後の停止図柄が当り態様となって普通利益状態が発生した場合に、開閉部 8 8 が所定時間閉状態から開状態に変化するようになっている。

#### 【 0 0 3 3 】

50

この第2特別図柄始動手段73は、図5に示すように例えば中央表示枠ユニット57の右部における前面装着板81上で且つ普通図柄始動手段71の下流側に配置されており、右流下経路84bを流下してきた遊技球が入賞可能となっている。なお、開閉部88は例えば下部側に設けられた左右方向の回転軸廻りに揺動可能であり、閉状態では前面装着板81と略面一となって遊技球が前側を通過可能となり、開状態では前面装着板81の前側で後ろ下がりの傾斜状となって遊技球を後向きに入賞させるようになっている。この第2特別図柄始動手段73に遊技球が入賞すると、一入賞当たり所定個数の遊技球が賞球として払い出される。

#### 【0034】

第1特別図柄表示手段(図柄表示手段)63は、図6に示すように遊技情報表示手段60における所定個数(ここでは8個)のLED70で構成されており、第1特別図柄始動手段72が遊技球を検出することを条件に、第1特別図柄を構成するそれら8個のLED70が特別変動中発光パターンで発光した後、第1特別図柄始動手段72による遊技球検出時(図柄始動条件が成立した場合)に取得された第1特別乱数情報に含まれる大当たり判定乱数値が予め定められた大当たり判定値と一致する場合(乱数抽選で大当たりとなった場合)には大当たり態様で、同じく小当たり判定値と一致する場合(乱数抽選で小当たりとなった場合)には小当たり態様で、それ以外の場合にははずれ態様で変動を停止するようになっている。第1特別図柄表示手段63の変動後の停止図柄が大当たり態様となった場合には大当たり遊技が、小当たり態様となった場合には小当たり遊技が実行される(利益状態発生手段)。

#### 【0035】

第2特別図柄表示手段(図柄表示手段)64は、図6に示すように遊技情報表示手段60における所定個数(ここでは8個)のLED70で構成されており、第2特別図柄始動手段73が遊技球を検出することを条件に、第2特別図柄を構成するそれら8個のLED70が特別変動中発光パターンで発光した後、第2特別図柄始動手段73による遊技球検出時(図柄始動条件が成立した場合)に取得された第2特別乱数情報に含まれる大当たり判定乱数値が予め定められた大当たり判定値と一致する場合(乱数抽選で大当たりとなった場合)には大当たり態様で、同じく小当たり判定値と一致する場合(乱数抽選で小当たりとなった場合)には小当たり態様で、それ以外の場合にははずれ態様で変動を停止するようになっている。第2特別図柄表示手段64の変動後の停止図柄が大当たり態様となった場合には大当たり遊技が、小当たり態様となった場合には小当たり遊技が実行される(利益状態発生手段)。

#### 【0036】

第1,第2特別図柄表示手段63,64は、各8個のLED70の発光態様(例えば点灯/消灯)の組み合わせにより一又は複数の大当たり態様、一又は複数の小当たり態様、一又は複数のはずれ態様を表示可能であり、また特別変動中発光パターンは、特定の複数種類(ここでは2種類)の発光態様を所定時間(例えば128ms)毎に切り替えるようになっている。

#### 【0037】

また、第1特別図柄表示手段63の図柄変動中、第2特別図柄表示手段64の図柄変動中及び大当たり遊技中を含む特別保留期間中に第1,第2特別図柄始動手段72,73が遊技球を検出した場合には、それによって取得された第1,第2特別乱数情報が夫々予め定められた上限保留個数、例えば各4個を限度として保留記憶手段に保留記憶される。そして、特別保留期間が終了した時点で第2特別図柄側の保留記憶が1以上の場合にはその第2特別図柄の保留記憶を1個消化して第2特別図柄の変動を行い、第1特別図柄側の保留記憶のみが1以上の場合にはその第1特別図柄の保留記憶を1個消化して第1特別図柄の変動を行う。このように本実施形態では、第1特別図柄と第2特別図柄とが共に変動になることはなく、また第1特別図柄側と第2特別図柄側との両方に保留記憶がある場合には、第2特別図柄の変動を優先的に行うようになっている。

#### 【0038】

なお本実施形態の場合、遊技者は後述する特別遊技状態中以外の通常遊技状態中は第1特別図柄始動手段72を狙って左打ちをし、特別遊技状態中は普通図柄始動手段71及び

10

20

30

40

50

第2特別図柄始動手段73を狙って右打ちをするため、通常遊技状態中は主として第1特別図柄が変動し、特別遊技状態中は主として第2特別図柄が変動する。

【0039】

保留記憶手段に保留記憶されている第1、第2特別乱数情報の個数（第1、第2特別保留個数）は、第1、第2特別保留個数表示手段65、66、液晶表示手段76等によって遊技者に報知される。ここで、第1、第2特別保留個数表示手段65、66は、図6に示すように遊技情報表示手段60における所定個数（ここでは各2個）のLED70で構成され、それらの発光態様（例えば点灯／点滅／消灯）の組み合わせにより、0～4個の5種類の第1、第2特別保留個数を表示可能となっている。

【0040】

また、第1、第2特別図柄始動手段72、73による遊技球検出に基づいて行われる大当たり判定（乱数抽選）で大当たりとなる確率（大当たり確率）には低確率と高確率の2種類があり、後述する特別遊技状態のうちの確変状態中は高確率に、それ以外は低確率に夫々設定される。また本実施形態では、設定値を複数段階（ここでは6段階）の何れかに設定可能であり、その設定値（設定1～6）に応じて大当たり確率（低確率及び高確率）が変化する。大当たり確率は、例えば設定値が大きいほど高くなっている。

【0041】

また、大当たり判定結果がはずれとなった場合には一又は複数種類のはずれの何れかを選択し、大当たり判定結果が小当たりとなった場合には一又は複数種類の小当たりの何れかを選択し、大当たり判定結果が大当たりとなった場合には一又は複数種類の大当たり（例えば確変大当たり、非確変大当たりの2種類）の何れかを選択するようになっている。ここで、確変大当たりは、大当たり遊技の終了後に特別遊技状態として確変状態（第1特別遊技状態）を発生させることとなる大当たり、非確変大当たりは、大当たり遊技の終了後に特別遊技状態として例えば時短状態（第2特別遊技状態）を発生させることとなる大当たりで、それらの振り分けは大当たり図柄乱数値等に基づいて行われる。

【0042】

時短状態中は、例えば第1、第2特別図柄に関して第1、第2特別図柄表示手段63、64の変動時間が通常変動時間よりも短い短縮変動時間に切り換えられる他、普通図柄に関して、当たり確率が通常確率から高確率へ、変動時間が通常変動時間から短縮変動時間へ、普通利益状態における第2特別図柄始動手段73の開閉パターンが通常開閉パターン（例えば0.2秒×1回開放）から特別開閉パターン（例えば2秒×3回開放）へ、夫々切り換えられるようになっている。なお、時短状態は大当たり遊技が終了した時点で開始し、例えば第1、第2特別図柄が所定回数（例えば50回）変動するか、それまでに次の大当たり遊技が発生した時点で終了する。また確変状態中は、例えば時短状態と同様の切り換えに加えて、大当たり確率が低確率から高確率に切り換えられるようになっている。なお、確変状態は大当たり遊技が終了した時点で開始し、例えば次の大当たり遊技が発生した時点で終了する。

【0043】

大入賞手段74は、遊技球が入賞可能な開状態と入賞不可能な閉状態とに切り換え可能な開閉板89を備えた開閉式入賞手段で、図5に示すように例えば中央表示枠ユニット57に設けられ、入賞した遊技球を検出する遊技球検出スイッチ（図示省略）と、開閉板89を開閉する電磁ソレノイド等の開閉駆動手段とを備えており、第2特別図柄始動手段73の下流側で且つ第1特別図柄始動手段72の上流側に配置されていることにより、左流下経路84aを流下してきた遊技球よりも右流下経路84bを流下してきた遊技球の方が高い確率で入賞可能となっている。この大入賞手段74は、第1、第2特別図柄表示手段63、64の第1、第2特別図柄が変動後に大当たり態様（特定態様）で停止した場合には所定の大当たり開放パターンで開放し（大当たり遊技）、同じく小当たり態様で停止した場合には所定の小当たり開放パターンで開放する（小当たり遊技）。この大入賞手段74に遊技球が入賞すると、一入賞当たり所定個数の遊技球が賞球として払い出される。

【0044】

10

20

30

40

50

また液晶表示手段 7 6 には、第 1 , 第 2 特別図柄表示手段 6 3 , 6 4 による第 1 , 第 2 特別図柄の変動表示と並行して装飾図柄 9 0 を変動表示可能である他、第 1 , 第 2 特別保留個数を示す第 1 , 第 2 保留報知画像 X 1 ~ X 4 , Y 1 ~ Y 4 , 変動中保留報知画像 Z 等の各種画像を表示可能となっている。

#### 【 0 0 4 5 】

ここで装飾図柄 9 0 は、数字図柄その他の複数個の図柄で構成される図柄列を複数（図 5 の例では左右方向に 3 つ）備えており、またそれら各図柄列を構成する各図柄は、図 5 に示すように、1 ~ 8 等の数字、その他で構成される図柄本体部 9 0 a と、この図柄本体部 9 0 a に付随するキャラクタその他の装飾部 9 0 b との結合で構成されている。なお装飾図柄 9 0 は、拡大又は縮小、表示位置の変更、装飾部 9 0 b の消去等、表示態様を任意に変化させることが可能である。

10

#### 【 0 0 4 6 】

装飾図柄 9 0 は、例えば第 1 , 第 2 特別図柄の変動開始と略同時に所定の変動パターンに従って図柄列毎に縦スクロール、横スクロール等による変動を開始すると共に、所定の有効ライン上の停止図柄が所定態様となるように例えば第 1 , 第 2 特別図柄の変動停止と略同時に最終停止する。なお装飾図柄 9 0 では、例えば有効ライン上の全ての停止図柄が同じ場合が大当たり演出態様、それ以外が小当たり演出態様又ははずれ演出態様となっており、第 1 , 第 2 特別図柄が大当たり態様となる場合には装飾図柄 9 0 は大当たり演出態様となり、第 1 , 第 2 特別図柄が小当たり態様となる場合には装飾図柄 9 0 は小当たり演出態様となり、第 1 , 第 2 特別図柄がはずれ態様となる場合には装飾図柄 9 0 ははずれ演出態様となる。

20

#### 【 0 0 4 7 】

また第 1 , 第 2 保留報知画像 X 1 ~ X 4 , Y 1 ~ Y 4 , 変動中保留報知画像 Z に関しては、第 1 , 第 2 特別図柄始動手段 7 2 , 7 3 が遊技球を検出することに基づいて第 1 , 第 2 特別保留個数が増加した場合に、第 1 , 第 2 保留報知画像 X 1 ~ , Y 1 ~ を液晶表示手段 7 6 上に 1 個追加表示し、また第 1 , 第 2 特別図柄表示手段 6 3 , 6 4 による第 1 , 第 2 特別図柄の新たな変動が開始することに基づいて第 1 , 第 2 特別保留個数が減少した場合に、例えば変動中保留報知画像 Z を消去し、第 1 , 第 2 保留報知画像 X 1 ~ , Y 1 ~ を待ち行列の前側（例えば画面右側）に向けて 1 個分ずつシフトすると共に、押し出された先頭の第 1 , 第 2 保留報知画像 X 1 , Y 1 を例えば所定位置まで移動させて新たな変動中保留報知画像 Z に変化させるようになっている。

30

#### 【 0 0 4 8 】

また遊技盤 1 6 の裏側には、図 7 に示すように、液晶表示手段 7 6 を遊技盤 1 6 の後側で支持するための裏ケース 9 1 が装着され、この裏ケース 9 1 の背面側に、主制御部 9 2 を構成する主制御基板 9 3 が格納された主基板ケース 9 4 、演出制御部 9 5 を構成する演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 、液晶制御基板 9 8 及び ROM 基板 9 9 が格納された演出基板ケース 1 0 0 等が着脱自在に装着されている。

30

#### 【 0 0 4 9 】

ここで、演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 、液晶制御基板 9 8 及び ROM 基板 9 9 について、演出基板ケース 1 0 0 への格納状態の詳細について図 8 , 図 9 を参照しつつ説明する。

40

#### 【 0 0 5 0 】

演出インターフェース基板 9 6 と液晶インターフェース基板 9 7 とは、夫々の表面 9 6 a , 9 7 a が後側となる向きで、左右に互いに近接した状態で配置されている。そして、演出インターフェース基板 9 6 と液晶インターフェース基板 9 7 とは、演出インターフェース基板 9 6 における液晶インターフェース基板 9 7 側の縁部に沿って配置された演出 IF 第 1 , 第 2 コネクタ C N 1 1 , C N 1 2 と、液晶インターフェース基板 9 7 における演出インターフェース基板 9 6 側の縁部に沿って配置された液晶 IF 第 1 , 第 2 コネクタ C N 2 1 , C N 2 2 とを夫々左右方向に直結することによって互いに一体化されている。なお、演出インターフェース基板 9 6 では、その表裏両面に各種電子部品が配置されているが、音声プロセッサ 1 0 1 、デジタルアンプ 1 0 2 等の各種 I C 、液晶 IF 第 1 ~ 第 3 コ

50

ネクタCN21～CN23等の各種コネクタ、音声ROM103等は表面96a側に配置されている。また液晶インターフェース基板97についても、その表裏両面に各種電子部品が配置されているが、液晶IF第1～第3コネクタCN21～CN23の他、液晶表示手段76を接続するための液晶接続第1，第2コネクタCN24，CN25等の各種コネクタについては表面97a側に配置されている。

#### 【0051】

また液晶制御基板98は、その表面98aが後向きとなり、裏面98bが演出インターフェース基板96及び液晶インターフェース基板97の表面96a，97aと対向するように、演出インターフェース基板96及び液晶インターフェース基板97の後側に配置されている。そして液晶制御基板98は、その裏面98b側に設けられた液晶制御第1コネクタCN31を演出インターフェース基板96側の演出IF第3コネクタCN13に、同じく裏面98b側に設けられた液晶制御第2コネクタCN32を液晶インターフェース基板97側の液晶IF第3コネクタCN23に夫々直結することにより、演出インターフェース基板96及び液晶インターフェース基板97と一体化されている。なお、液晶制御基板98では、その表裏両面に各種電子部品が配置されており、表面98a側には複合チップ104、制御ROM105、DRAM106、液晶制御第3コネクタCN33等が配置され、裏面98b側には液晶制御第1，第2コネクタCN31，CN32等が配置されている。

#### 【0052】

またROM基板99は、表面99aが後向きとなり、裏面99bが演出インターフェース基板96、液晶インターフェース基板97のうちの例えは液晶インターフェース基板97の表面97aと対向するように、液晶制御基板98に隣接して例えはその下側に配置されている。そしてROM基板99は、その表面99a側の上縁部に配置されているROM第1コネクタCN41を、液晶制御基板98の下縁部に配置されている液晶制御第3コネクタCN33に直結することにより液晶制御基板98と一体化されている。なお、ROM基板99では、その表裏両面に各種電子部品が配置されているが、CGROM107、ROM第1コネクタCN41等については表面99a側に配置されている。

#### 【0053】

以上説明したように、基板96～99は、互いのコネクタ同士を直結することにより、演出インターフェース基板96及び液晶インターフェース基板97の表面96a，97aと液晶制御基板98及びROM基板99の裏面98b，99bとを、所定の隙間を空けて対向させた状態で接続され、一体化される。従って、それら基板96～99を互いに接続した状態では、液晶制御基板98の裏面98b側は、演出インターフェース基板96及び液晶インターフェース基板97の陰になって目視することができない。

#### 【0054】

演出基板ケース100は透明な合成樹脂製で、基板96～99の裏面側を覆うベース体111と、基板96～99の表面側を覆うカバー体112とで略箱形に形成されている。基板96～99を演出基板ケース100に格納する際には、まず液晶制御基板98とROM基板99とを、コネクタの直結により互いに連結した状態で、カバー体112の内側の所定位置にねじ止めにより固定する。このとき、液晶制御基板98、ROM基板99の表面98a，99aが、カバー体112の背壁113の内面側に所定の隙間を挟んで対向する。

#### 【0055】

次に、演出インターフェース基板96と液晶インターフェース基板97とを、コネクタの直結により互いに連結した状態で、液晶制御基板98及びROM基板99の背面側からカバー体112の内側の所定位置に嵌め込む。このとき、演出インターフェース基板96側の演出IF第3コネクタCN13が液晶制御基板98側の液晶制御第1コネクタCN31に、液晶インターフェース基板97側の液晶IF第3コネクタCN23が液晶制御基板98側の液晶制御第2コネクタCN32に夫々結合される。

#### 【0056】

10

20

30

40

50

続いて、ベース体 111 を、演出インターフェース基板 96 及び液晶インターフェース基板 97 の裏面 96b, 97b 側からカバー体 112 に嵌め合わせる。そして更に、ベース体 111 の外側から演出インターフェース基板 96、液晶インターフェース基板 97 の通孔 114 を介してカバー体 112 側のねじ止め基部 115 に対してねじ止めすることにより、基板 96 ~ 99 は演出基板ケース 100 内の所定位置に固定される。基板 96 ~ 99 が格納された演出基板ケース 100 は、ベース体 111 を前側、カバー体 112 を後側に向けた状態で、裏ケース 91 の背面側に着脱自在に装着される。

#### 【0057】

また前枠 3 の裏側には、図 7 に示すように、遊技盤 16 の裏側を開閉自在に覆う裏カバー 121 が着脱自在に装着されると共に、その上側に遊技球タンク 122 とタンクレール 123 とが、左右一側に払出手段 32 と払出通路 124 とが夫々装着されており、遊技球が大入賞手段 74 等の入賞口に入賞したとき、又は国外の自動球貸し機から球貸し指令があったときに、遊技球タンク 122 内の遊技球をタンクレール 123 経由で払出手段 32 により払い出し、その遊技球を払出通路 124 経由で上皿 33 に案内するようになっている。なお、裏カバー 121 は、演出基板ケース 100 の略全体と主基板ケース 94 の上部側の一部分とを後側から覆うように配置されている。

10

#### 【0058】

また、前枠 3 の裏側下部には、基板装着台 125 が着脱自在に装着されており、この基板装着台 125 の背面側に、電源基板 126 が格納された電源基板ケース 127、払出発射制御基板 128 が格納された払出発射基板ケース 129 が夫々着脱自在に装着されている。

20

#### 【0059】

図 10 は本パチンコ機の制御系の全体構成を示すブロック図である。図 10 に示すように、本パチンコ機の全体回路構成は、遊技盤 16 側に搭載される盤側部材 131 と、前枠 3 側に搭載される枠側部材 132 とで構成されている。

20

#### 【0060】

まず盤側部材 131 の概要を説明する。盤側部材 131 は、主制御部 92 を構成する主制御基板 93、演出制御部 95 を構成する演出インターフェース基板 96、液晶インターフェース基板 97、液晶制御基板 98 及び ROM 基板 99 の他、遊技盤中継基板 133、LED 接続基板 134、主制御中継基板 135、電源中継基板 136、枠 LED 中継基板 137 等で構成されている。

30

#### 【0061】

主制御基板 93 は、遊技制御を統括的に行うもので、普通図柄始動手段 71 や大入賞手段 74 等に設けられた遊技球検出スイッチ、大入賞手段 74 等に設けられた開閉駆動手段、遊技盤 16 の各部に配置された磁気、電波、振動等の各種センサ、遊技情報表示手段 60 等が、遊技盤中継基板 133 等の中継基板を介して、或いは中継基板を介すことなく直接的に接続されている。また主制御基板 93 は、演出制御ハーネス 138 を介して演出インターフェース基板 96 に接続されており、制御コマンド CMD とストローブ信号 STB とを送信可能となっている。

#### 【0062】

主制御中継基板 135、電源中継基板 136 及び枠 LED 中継基板 137 は、盤側部材 131 を枠側部材 132 に接続するためのもので、主制御基板 93 は主制御中継基板 135 を介して払出発射制御基板 128 に接続され、演出インターフェース基板 96 は電源中継基板 136 を介して電源基板 126 に、枠 LED 中継基板 137 を介して枠下 LED 接続基板 139 に夫々接続されている。遊技盤 16 側の主制御中継基板 135、電源中継基板 136、枠 LED 中継基板 137 には、盤側第 1 ~ 第 3 コネクタ CN1a ~ CN3a が夫々遊技盤 16 の後側に対応して配置され、また内枠 6 側の遊技盤装着部 14 (図 2) には、枠側第 1 ~ 第 3 コネクタ CN1b ~ CN3b が夫々盤側第 1 ~ 第 3 コネクタ CN1a ~ CN3a に対向するように配置されており、遊技盤 16 が内枠 6 の遊技盤装着部 14 に前側から装着されたとき、盤側第 1 ~ 第 3 コネクタ CN1a ~ CN3a が枠側第 1 ~ 第 3

40

50

コネクタ C N 1 b ~ C N 3 b に夫々結合されるようになっている。なお、枠側第 1 コネクタ C N 1 b は、拡出発射制御基板 1 2 8 に接続される拡出発射制御中継ハーネス 1 4 1 の一端側に設けられ、枠側第 2 コネクタ C N 2 b は、電源基板 1 2 6 に接続される演出制御電源ハーネス 1 4 2 の一端側に設けられ、枠側第 3 コネクタ C N 3 b は、枠下 L E D 接続基板 1 3 9 に接続される枠下 L E D 接続ハーネス 1 4 3 の一端側に設けられている。

#### 【 0 0 6 3 】

演出制御部 9 5 を構成する演出インターフェース基板 9 6 、液晶インターフェース基板 9 7 、液晶制御基板 9 8 及び R O M 基板 9 9 は、既に説明したようにハーネスを介することなくコネクタ同士を直結することによって互いに一体化されている。

#### 【 0 0 6 4 】

また、液晶インターフェース基板 9 7 には、液晶接続第 1 , 第 2 コネクタ C N 2 4 , C N 2 5 から液晶接続第 1 , 第 2 ハーネス 1 4 4 , 1 4 5 を介して液晶表示手段 7 6 が接続されている。また演出インターフェース基板 9 6 には、L E D 接続ハーネス 1 4 6 を介して L E D 接続基板 1 3 4 が接続されている。L E D 接続基板 1 3 4 には、可動役物ランプ 3 1 4 を構成する L E D 基板 3 1 2 、盤ランプ 3 2 4 を構成する L E D 基板 3 2 2 a ~ 3 2 2 c 等の各種 L E D 基板の他、可動役物 7 7 a の駆動制御に使用するモータ、ソレノイド等の可動体駆動手段、位置検出スイッチ等が接続されている。

#### 【 0 0 6 5 】

ここで、図 1 1 等に基づいて、液晶表示手段 7 6 の仕様について説明する。液晶表示手段 7 6 は、横 1 2 8 0 画素 × 縦 1 0 2 4 画素の液晶カラーディスプレイであるが、左右方向に隣接する奇数画素 ( O D D ) 、偶数画素 ( E V E N ) に対応する制御信号 ( O D D 信号、 E V E N 信号 ) を、別々の L V D S ( Low Voltage Differential Signaling ) 伝送路を介して受信部 R V ( R V a + R V b ) で受ける構成となっている。そこで本実施形態では、この仕様に対応して、液晶接続第 1 コネクタ C N 2 4 , 液晶接続第 1 ハーネス 1 4 4 等による第 1 伝送路 L V D S 1 を経由して O D D 信号 ( 第 1 信号 ) を伝送し、同じく第 2 伝送路 L V D S 2 を経由して E V E N 信号 ( 第 2 信号 ) を伝送している ( 図 1 0 の左下部 ) 。

#### 【 0 0 6 6 】

また、この液晶表示手段 7 6 では、内部動作を規定する動作クロック C K は、その周波数を 4 0 M H z ~ 7 0 M H z の範囲とするべく規定されている ( 典型値は 5 4 M H z ) 。この動作クロック C K はドットクロック D C K に対応するが、以下の説明では、便宜上、動作クロック C K の周波数は典型値である 5 4 M H z とする。その 5 4 M H z の動作クロック C K において、一フレームの画像更新に要する更新時間 ( フレームレート ) を約 1 / 6 0 秒とする構成について説明する。

#### 【 0 0 6 7 】

液晶表示手段 7 6 は、その仕様として、第 1 伝送路 L V D S 1 から受けた O D D 信号と、第 2 伝送路 L V D S 2 から受けた E V E N 信号とに基づき、表示画面の左右方向に隣接する二画素を、一の動作クロック C K で同時に処理するように構成されている。その結果、水平方向一ラインに対応する 1 2 8 0 画素の画素データは、 $6 4 0 / 5 4 \text{ M H z} = 1 1 . 8 5 \mu \text{ s}$  の動作時間で更新され、この動作が垂直方向 1 0 2 4 ライン分繰り返されることで、一フレーム分  $1 2 8 0 \times 1 0 2 4$  画素の画像表示が更新される。なお、第 1 ライン 第 2 ライン . . . 第 1 0 2 4 ラインのように、一ラインごとにノンインタラース方式で画像が更新される。

#### 【 0 0 6 8 】

但し、図 1 1 に示す通り、液晶表示手段 7 6 の仕様として、水平方向に典型値としては 2 0 4 クロック分の待機時間 ( ブランク期間 ) W T h を設けること、及び垂直方向に典型値としては 4 2 行分の待機時間 ( ブランク期間 ) W T v を設けることが規定されている。従って、これらの待機時間 W T h , W T v を考慮した実際の画面更新周期は、上述した典型値に基づく計算において、 $( 2 0 4 + 6 4 0 ) \times ( 4 2 + 1 0 2 4 ) / 5 4 \text{ M H z} = 1 6 . 6 6 \text{ m s}$  となるため、フレームレートは約 6 0 H z となる。

## 【0069】

なお、水平方向待機時間W T hと垂直方向待機時間W T vには、各々典型値に対する許容幅が規定されており、実際には上述した典型値とは異なる値を選択可能である。但し、フレームレートを1/60秒とするため、(W T h + 640) × (W T v + 1024) / 54 MHz = 1/60秒となるよう、水平、垂直方向待機時間W T h、W T vを正確に設定する必要がある。

## 【0070】

また液晶表示手段76では、水平同期信号H Sと垂直同期信号V Sとが不要である一方、O D D信号とE V E N信号の伝送時にはHレベルのデータ有効信号E N A Bの伝送が要求される。即ち、第1、第2伝送路L V D S 1、L V D S 2に対して、有意な信号(O D D/E V E N信号)を伝送しているタイミングでは、データ有効信号E N A Bがアクティブレベル(Hレベル)である必要がある。

10

## 【0071】

そこで本実施形態では、上述した液晶表示手段76の仕様に基づき、液晶制御基板(表示制御手段)98と液晶表示手段76とを、ドットクロック(ピクセルクロック)D C Kが54 MHzのデュアルリンク伝送路でL V D S接続している(図13、図18)。また、液晶制御基板98に搭載されるV D P回路172(図14等)では、液晶表示手段76の仕様を満たす水平方向待機時間W T hと垂直方向待機時間W T vとを設けるとともに、画像データ(O D D/E V E N信号)の出力時は、データ有効信号E N A Bがアクティブレベル(Hレベル)になるようにしている。

20

## 【0072】

即ち、データ有効信号E N A Bは、図12(b)に示すように、水平同期周期T Hのうち、水平表示期間T H dだけがHレベルとなるよう構成されている。従って、データ有効信号E N A Bは、垂直同期周期T Vのうち、垂直表示期間T V d以外は必ずLレベルとなる(図12(c))。なお、水平方向待機時間W T hと垂直方向待機時間W T vは、各々の典型値(W T hは204、W T vは42)とは異なる値を採用しているが、具体的な設計値については図19に基づいて後述する。

## 【0073】

何れにしても、データ有効信号E N A Bは、図12(a)に示すように、差動信号ラインR A 2、R B 2を経由して、ドットクロックD C Kの各動作サイクルにおいて離散的なD E信号として繰り返し伝送される。図12(b)、(c)に示すデータ有効信号E N A Bは、L V D S伝送された離散データであるD E信号を復調したもので、離散的なD E信号を時間軸上に連続させたものである。なお、差動信号ラインR A 2、R B 2では、図12(a)に示すように、垂直同期信号V Sと水平同期信号H SについてもD E信号(データ有効信号E N A B)に続いて繰り返し伝送されているが、本実施形態の液晶表示手段76では同期信号V S、H Sを活用しておらず、これらの同期信号H S、V Sに関する内部動作は実行されることはない。

30

## 【0074】

即ち、本実施形態の液晶表示手段76における表示ラインの水平改行タイミングは、受信した水平同期信号H Sとは無関係に、データ有効信号E N A Bの立下りタイミングや、データ有効信号E N A Bの立上りタイミング後の動作クロックC K(ドットクロックD C Kに対応)の個数(本実施形態では640個)等に基づいて、液晶表示手段76の内部回路にとって最適なタイミングに規定される(図12(b)の下向き矢印)。

40

## 【0075】

この点は、一フレーム分の画像表示後の垂直改行タイミングについても同様であり、所定パルス幅のデータ有効信号E N A Bの連続個数(本実施形態では1024個)等に基づいて、液晶表示手段76の内部回路にとって最適なタイミングに規定され(図12(c)の下向き矢印)、受信した垂直同期信号V Sには影響されない。このように本実施形態では、液晶表示手段76に水平同期信号H Sや垂直同期信号V Sを伝送する必要がないため、同期信号H S、V Sのパルス幅P W h、P W v、フロントポーチF P h、F P v、バッ

50

クポーチ B P h , B P v 等を最適に設定する必要がなく、 V D P 回路 1 7 2 等の制御負担が大きく軽減される。

#### 【 0 0 7 6 】

また、液晶表示手段 7 6 の内部動作としても、自らの内部構成に基づく最適タイミングで水平改行や垂直改行の動作が実行されるため、不自然な表示動作のおそれが解消される。因みに、外部から受ける水平同期信号 H S や垂直同期信号 V S に基づいて動作する表示手段の場合には、同期信号 H S , V S のパルス幅や、同期信号 H S , V S に前後するフレームトポート期間、バックポート期間が不適切であれば正常な表示動作が損なわれるおそれがある。

#### 【 0 0 7 7 】

ところで、図 1 2 ( a )において、差動信号ライン R A 0 ~ R A 3 , R A C L K を使用する第 1 伝送路 L V D S 1 は、奇数番目の画素に対応する信号を伝送しており ( A サイドの O D D 信号 ) 、差動信号ライン R B 0 ~ R B 3 , R B C L K を使用する第 2 伝送路 L V D S 2 は、偶数番目の画素に対応する信号を伝送している ( B サイドの E V E N 信号 ) 。このように、本実施形態では O D D 信号と E V E N 信号とをデュアルリンク伝送路で伝送することで、ドットクロック D C K の周波数を実質的に 1 / 2 に低下させることができ、その分だけ耐ノイズ性を向上させ、また伝送距離を上げることもできる。

#### 【 0 0 7 8 】

一方、液晶表示手段 7 6 には、デュアルリンク伝送路で伝送された O D D 信号と E V E N 信号とを受信する受信部 R V が内蔵されており、二つの L V D S 信号 ( O D D 信号と E V E N 信号 ) から R G B 信号を復元して、一フレーム分 ( 1 2 8 0 × 1 0 2 4 画素 ) の画像を表示している。 R G B 信号は各々 8 b i t で構成されているので、液晶表示手段 7 6 には階調度  $2^8 \times 2^8 \times 2^8$  のフルカラー画像が表示される。

#### 【 0 0 7 9 】

図 1 3 は、液晶表示手段 7 6 の内部構成を、 V D P 回路 1 7 2 の関連部分と共に図示したブロック図である。図示の通り、 O D D 信号は、第 1 伝送路 L V D S 1 ( A サイド ) を経由して L V D S - パラレル変換部 R V a に伝送され、 E V E N 信号は、第 2 伝送路 L V D S 2 ( B サイド ) を経由して L V D S - パラレル変換部 R V b に伝送される。なお、第 1 伝送路 L V D S 1 は 5 本の差動信号ライン R A 0 ~ R A 3 , R A C L K を備え、また第 2 伝送路 L V D S 2 は、 5 本の差動信号ライン R B 0 ~ R B 3 , R B C L K を備えている。

#### 【 0 0 8 0 】

そして、差動信号ライン R A 0 / R B 0 からは、各 8 ピット長の R G B データのうち、画像データ R 0 ~ R 5 , G 0 が注出され、差動信号ライン R A 1 / R B 1 からは、同じく画像データ G 1 ~ G 5 , B 0 , B 1 が注出され、差動信号ライン R A 2 / R B 2 からは、同じく画像データ B 2 ~ B 5 , D E 信号 ( 即ちデータ有効信号 E N A B ) , V S 信号及び H S 信号が注出され、差動信号ライン R A 3 / R B 3 からは、同じく画像データ G 6 , G 7 , B 6 , B 7 , R 6 , R 7 が注出される。なお、注出された V S 信号と H S 信号が利用されないことは上述した通りである。

#### 【 0 0 8 1 】

また、差動信号ライン R A C L K / R B C L K のドットクロック D C K は、 P L L 回路に供給されることで、ドットクロック D C K と同一の周波数 5 4 M H z の動作クロック C K が生成される。この動作クロック C K は、液晶コントローラ L C D \_ C T L の内部動作を規定するもので、液晶コントローラ L C D \_ C T L は、液晶パネル L C D における左右方向に隣接する 2 個の R G B 画素 ( 8 ピット × 3 × 2 ) に対応する画像データを、一の動作クロック C K に同期してまとめて処理している。

#### 【 0 0 8 2 】

そのため、横方向 1 2 8 0 ( = 6 4 0 × 2 ) ドットの画素は、動作クロック C K 6 4 0 個分の処理時間 1 1 . 8 5 μ S ( = 6 4 0 / 5 4 M H z ) で処理を完了することになる。なお、一の画素に対応する画像データは、 R G B 各々 1 バイト長 ( 階調度  $2^8 \times 2^8 \times 2^8$  ) であるから、一ラインを構成する全画素 ( 1 2 8 0 ドット ) の画像データは、全体とし

10

20

30

40

50

て  $3 \times 1280$  バイト長となる。

【0083】

図13に示す通り、液晶コントローラLCD\_CTLは、1280本のソース信号ラインを各々 $2^8$  (=256)階調の駆動信号で駆動するソースドライバSDVと、1024本のゲート信号ラインをON/OFF制御するゲートドライバGDVとを適宜制御している。具体的には、液晶コントローラLCD\_CTLは、LVDS伝送路から注出したDE信号(データ有効信号ENAB)と動作クロックCKとに基づいて、各部を適宜に動作させることで、フレームレート60Hzの画像更新動作を実現している。

【0084】

液晶パネルLCDの画素は夫々RGB三色の基本画素で構成されており、一ライン分の全画素(1280ドット)に対応する基本画素数は $3 \times 1280$ 個となるため、ソースドライバSDVは、384本の出力端子を有するドライバ素子を10個配置して構成されている。なお、これら10個のドライバ素子には、液晶コントローラLCD\_CTLから画像データDATが順番に供給され、これがスタート信号SPや転送クロックDCLKに基づいて適宜転送される。そして、ラッチ信号LTに同期して、アナログ変換された駆動信号が3840本のソース信号ラインに供給される。先に説明した通り、液晶パネルLCDの一ラインの全画素(1280ドット)の更新に要する時間は $11.85\mu\text{s}$ (=640/54MHz)である。

10

【0085】

一方、液晶コントローラLCD\_CTLは、ゲートドライバGDVに対して、ゲートスタート信号GSやゲートクロック信号GCLKを供給することで、駆動対象となるゲート信号ラインを更新している。ここで、ゲートドライバGDVは、256本の出力端子を有するドライバ素子を4個配置して構成されている。

20

【0086】

なお、ゲート信号ラインの更新タイミングは、DE信号の立下りタイミングと動作クロックCKとに基づいて規定され、ゲート信号ラインの水平改行周期は、動作クロックCKでカウントして、典型値計算では $640 + 204$ クロックとされる(図11参照)。また、DE信号の個数(1024)に基づいて、駆動対象のゲート信号ラインが初期状態にリセットされ、最適なタイミングでゲートスタート信号GSが出力され、ゲートクロック信号GCLKの出力が再開される。ゲート信号ラインの垂直改行周期は、動作クロックCKでカウントして、典型値計算では $42 + 1024$ クロックである(図11参照)。但し、先に説明した通り、本実施形態では典型値とは異なる設計で液晶表示手段76を動作させている(図19参照)。

30

【0087】

続いて、図10に戻って枠側部材132の概要を説明する。枠側部材132は、電源基板126、拡出発射制御基板128を中心に構成されている。電源基板126は、AC24Vを受けて各種の直流電圧を出力するもので、拡出発射制御基板128にDC5V, DC12V, DC35Vを、枠下LED接続基板139にDC12Vを夫々出力する他、電源中継基板136を介して演出インターフェース基板96にDC5V, DC12V, DC35Vを出力するようになっている。拡出発射制御基板128にはバックアップ基板147が接続されており、拡出発射制御基板128から主制御基板93に対しては、電源基板126から受けたDC5V, DC12V, DC35Vの他、バックアップ電源、電源異常信号等が主制御中継基板135を介して出力される。

40

【0088】

また拡出発射制御基板128には、発射手段17を構成する発射駆動手段17d、外部のホストコンピュータ等に各種情報を出力するための外部端子板148、外部の遊技球貸出装置を接続するための貸出装置接続端子板149の他、枠中継基板150、受け皿中継基板151等が接続されている。

【0089】

枠中継基板150は、内枠6側に配置された拡出モータ32a、拡出計数スイッチ32

50

b、前扉・内枠開放スイッチ152等と拡出発射制御基板128との接続を中継するものである。また受け皿中継基板151は、前扉7側の発射接続基板153、球詰まり検出基板154、度数表示基板155等と拡出発射制御基板128との接続を中継するものである。発射接続基板153には、発射ハンドル35を構成する可変抵抗器35a、発射停止スイッチ35b、タッチセンサ35cの他、球送りユニット53aに設けられた球送りソレノイド53c等が接続されている。

#### 【0090】

また、枠下LED接続基板139には、内枠6側の下部スピーカ18の他、前扉7側の枠左下LED接続基板156が接続されている。枠左下LED接続基板156には、枠ランプ304を構成するLED基板302a～302d、発射ハンドル35に配置されるハンドルLED基板158、演出ボタン41やその内部のLED基板等が接続される演出ボタンLED接続基板159、音量/光量調整ボタン39, 40等が接続される音量光量ボタン基板160、上部スピーカ25、サイドユニット30に接続されるサイドユニット中継基板161等が接続されている。

10

#### 【0091】

続いて、演出制御部95を構成する演出インターフェース基板96、液晶インターフェース基板97、液晶制御基板98及びROM基板99の回路構成について、図10, 図14等を参照しつつ詳細に説明する。

#### 【0092】

図10に示すように、演出インターフェース基板96は、各種入出力バッファの他、液晶制御基板98の複合チップ104に搭載されているCPU回路171(図14)から受ける指示に基づいて音声信号を再生する音声プロセッサ101、再生される音声信号の元データである圧縮音声データ等を記憶する音声ROM103、音声プロセッサ101から出力される音声信号を受けるデジタルアンプ102等を備えている。音声プロセッサ101は、内部回路の異常動作時に内部回路の設定値を自動的にデフォルト値にリセットするWDT回路と、音声制御レジスタSRGとを内蔵しており、音声制御レジスタSRGが、複合チップ104のCPU回路171から受ける動作パラメータに基づいて音声ROM103にアクセスし、必要な音声信号を再生してデジタルアンプ102に出力するようになっている。

20

#### 【0093】

演出インターフェース基板96に搭載されている各種入出力バッファには、主制御基板93から制御コマンドCMDとストローブ信号STBとを受けて液晶制御基板98の複合チップ104に転送するための入力バッファ、枠LED中継基板137を経由して演出ボタン41等のスイッチ信号を受けて液晶制御基板98の複合チップ104に転送するための入力バッファ、液晶制御基板98から受けたシリアル信号を枠LED中継基板137を経由してLED基板等のドライバICに転送するための出力バッファ、LED接続基板134を経由して可動体の位置検出スイッチ等のスイッチ信号を受けて液晶制御基板98の複合チップ104に転送するための入力バッファ、液晶制御基板98から受けたシリアル信号をLED接続基板134を経由してLED基板等のドライバICに転送するための出力バッファ等がある。

30

#### 【0094】

また液晶制御基板98には、CPU回路171、VDP回路172等を内蔵する複合チップ(チップ)104と、CPU回路171の制御プログラムを記憶する制御ROM(チップと接続されるROM)105と、大量のデータを高速にアクセス可能なDRAM(Dynamic Random Access Memory)106等が搭載されており、その液晶制御基板98に接続されているROM基板99には、演出制御に必要な大量のCGデータを記憶するCGRAM107が搭載されている。

40

#### 【0095】

制御ROM105は、チップセレクト信号CS0で選択されるアドレス空間CS0に位置付けされている。またDRAM106は、チップセレクト信号CS5で選択されるアド

50

レス空間 C S 5 に位置付けされている。

【 0 0 9 6 】

図 1 4 は、液晶制御基板 9 8 に搭載される複合チップ 1 0 4 について、関連する回路素子も含めて図示した回路ブロック図である。図示の通り、複合チップ 1 0 4 には、所定時間毎にディスプレイリスト D L を発行する C P U 回路 1 7 1 と、発行されたディスプレイリスト D L に基づいて画像データを生成し、液晶表示手段 7 6 を駆動する V D P 回路 1 7 2 とが内蔵されている。そして、C P U 回路 1 7 1 と V D P 回路 1 7 2 とは、互いの送受信データを中継する C P U I F 回路 1 7 3 を介して接続されている。

【 0 0 9 7 】

C P U 回路 1 7 1 は、複合チップ 1 0 4 の H C L K I 端子で受けた発振器 O S C 1 からの発振出力（例えば 1 0 0 / 3 M H z ）を周波数倍（例えば 8 倍）して、2 6 6 . 7 M H z 程度の C P U 動作クロックとしている。ここで、発振器 O S C 1 は、スペクトラムス拡散波を出力するように構成されることで、電波障害 / 電磁妨害を防止する E M I ( Electromagnetic Interference ) 対策を図っている。

10

【 0 0 9 8 】

一方、V D P 回路 1 7 2 は、複合チップ 1 0 4 の P L L R E F 端子で受けた発振器 O S C 2 からの発振出力（例えば 4 0 M H z ）を、必要に応じて周波数倍した上で、V D P 回路 1 7 2 のシステムクロック、表示装置用の表示クロック（ドットクロックなど）、及び外付けの D R A M 1 0 6 の D D R クロックとして使用している。即ち、発振器 O S C 2 の出力は、V D P 回路 1 7 2 全体のリファレンスクロックとして機能している。

20

【 0 0 9 9 】

そこで、このリファレンスクロックの重要性を考慮して、発振器 O S C 2 を V D P 回路 1 7 2 と同じ電源電圧 3 . 3 V で動作させると共に、出力イネーブル端子 O E が H レベル (= 3 . 3 V ) であることを条件に、リファレンスクロックを発振出力し、電源電圧 3 . 3 V が所定レベル以下に低下した場合には、マスク不能の割込み ( N M I ) が生じるよう構成されている。

【 0 1 0 0 】

また複合チップ 1 0 4 には H B T S L 端子が設けられており、この H B T S L 端子の論理レベルに基づいて、電源投入 ( C P U リセット ) 後に実行されるブートプログラム（初期設定プログラム）を記憶する R O M を特定している。図示の通り、本実施形態では H B T S L = L に設定されており、C P U 回路 1 7 1 のアドレス空間 C S 0 のゼロ番地が制御 R O M 1 0 5 に割り当てられている。

30

【 0 1 0 1 】

C P U I F 回路 1 7 3 には、制御プログラムや必要な制御データを不揮発的に記憶する制御 R O M 1 0 5 と、2 M バイト程度の記憶容量を有するワークメモリ ( R A M ) 1 7 4 とが接続されており、各々 C P U 回路 1 7 1 、V D P 回路 1 7 2 からアクセス可能となっている。

【 0 1 0 2 】

なお、制御 R O M 1 0 5 は、チップセレクト信号 C S 0 で選択されるアドレス空間 C S 0 に位置付けられ、ワークメモリ 1 7 4 は、チップセレクト信号 C S 6 で選択されるアドレス空間 C S 6 に位置付けられている。このワークメモリ 1 7 4 には、液晶表示手段 7 6 の一フレームを特定する一連の指示コマンドが記載されたディスプレイリスト D L を一次的に記憶する D L バッファ B U F が確保されている。

40

【 0 1 0 3 】

C P U 回路 1 7 1 は、汎用のワンチップマイコンと同等の性能を有する回路であり、制御 R O M 1 0 5 の制御プログラムに基づいて画像演出を統括的に制御する演出制御 C P U 1 8 1 と、1 6 k バイト程度の記憶容量を有して C P U の作業領域として使用される内蔵 R A M 1 8 2 と、演出制御 C P U 1 8 1 を経由しないでデータ転送を実現するための D M A C ( Direct Memory Access Controller ) 1 8 3 と、複数の入力ポート S i 及び出力ポート S o を有するシリアル入出力ポート ( S I O ) 1 8 4 と、複数の入力ポート P i 及

50

び出力ポート P o を有するパラレル入出力ポート ( P I O ) 1 8 5 と、それら各部の動作を制御するべく設定値が設定される制御レジスタ ( R E G ) 1 8 6 等を備えている。

#### 【 0 1 0 4 】

パラレル入出力ポート 1 8 5 は、入出力回路 1 8 7 等を介して外部機器 ( 演出インターフェース基板 9 6 ) に接続されており、演出制御 C P U 1 8 1 は、入出力回路 1 8 7 を経て、演出ボタン 4 1 等のスイッチ信号、制御コマンド C M D 、割込み信号 S T B 等を受信するようになっている。

#### 【 0 1 0 5 】

次に、 V D P 回路 1 7 2 について説明する。 V D P 回路 1 7 2 には、画像演出等で利用する静止画や動画の構成要素となる圧縮データを記憶する C G R O M 1 0 7 と、 4 G b i t 程度の記憶容量を有する外付け D R A M 1 0 6 と、液晶表示手段 7 6 とが接続されている。本実施形態では、 D R A M 1 0 6 は D D R 3 ( Double-Data-Rate3 SDRAM ) で構成され、 C G R O M 1 0 7 は N A N D 型フラッシュメモリよりなるフラッシュ S S D ( solid state drive ) で構成されている。

10

#### 【 0 1 0 6 】

V D P 回路 1 7 2 は、図 1 4 に示すように、 V D P ( Video Display Processor ) の動作を規定する各種の動作パラメータを演出制御 C P U 1 8 1 によって設定可能な制御レジスタ群 2 0 1 と、液晶表示手段 7 6 に表示すべき画像データの生成時に使用される 4 8 M バイト程度の内蔵 V R A M ( video RAM ) 2 0 2 と、チップ内部の各部間のデータ送受信及びチップ外部とのデータ送受信を実行するデータ転送回路 2 0 3 と、内蔵 V R A M 2 0 2 に関して、 S o u r c e や D e s t i n a t i o n のアドレス情報を特定可能なインデックステーブル I D X T B L と、描画動作に先行して C G R O M 1 0 7 に R E A D アクセスするプリロード動作を実行可能なプリローダ 2 0 4 と、 C G R O M 1 0 7 から読み出した圧縮データをデコード ( 復号伸長 / 展開 ) するグラフィックスデコーダ ( G D E C ) 2 0 5 と、デコード ( 展開 ) 後の静止画データや動画データを適宜に組み合わせて液晶表示手段 7 6 の一フレーム分の画像データを生成する描画回路 2 0 6 と、描画回路 2 0 6 の動作の一部として、適宜な座標変換によって立体画像を生成するジオメトリエンジン 2 0 7 と、描画回路 2 0 6 が生成したフレームバッファ F B a の画像データを読み出して、適宜な画像処理を並列的に実行可能な複数系統、例えば 3 系統 ( A / B / C ) の表示回路 2 0 8 A ~ 2 0 8 C と、 3 系統 ( A / B / C ) の表示回路 2 0 8 A ~ 2 0 8 C の出力を適宜選択する出力選択部 2 0 9 と、出力選択部 2 0 9 が出力する画像データを L V D S 信号に変換する L V D S 部 2 1 0 と、シリアルデータ送受信可能な S M C 部 2 1 1 と、 C P U I F 回路 1 7 3 とのデータ送受信を中継する C P U I F 部 2 1 2 と、 C G R O M 1 0 7 からのデータ受信を中継する C G バス I F 部 2 1 3 と、外付け D R A M 1 0 6 とのデータ送受信を中継する D R A M I F 部 2 1 4 と、内蔵 V R A M 2 0 2 とのデータ送受信を中継する V R A M I F 部 2 1 5 と、音声回路 S N D とを備えている。

20

#### 【 0 1 0 7 】

図 1 5 には、 C P U I F 部 2 1 2 、 C G バス I F 部 2 1 3 、 D R A M I F 部 2 1 4 及び V R A M I F 部 2 1 5 と、制御レジスタ群 2 0 1 、 C G R O M 1 0 7 、 D R A M 1 0 6 及び内蔵 V R A M 2 0 2 との関係が図示されている。同図の通り、 C G R O M 1 0 7 から取得した C G データは、例えばプリロードデータとして、データ転送回路 2 0 3 及び D R A M I F 部 2 1 4 を経由して外付け D R A M 1 0 6 のプリロード領域に転送される。なお、このプリロード動作は必須ではなく、またデータ転送先についても外付け D R A M 1 0 6 に限定されるものではなく、内蔵 V R A M 2 0 2 であってもよい。例えばプリロード動作を実行しないように構成する場合には、 C G データは、データ転送回路 2 0 3 、 V R A M I F 部 2 1 5 を経由して内蔵 V R A M 2 0 2 に転送される。

30

#### 【 0 1 0 8 】

ところで、内蔵 V R A M 2 0 2 には、 C G R O M 1 0 7 から読み出した圧縮データの展開領域、表示装置の W × H 個の表示ピクセルの各 A R G B 情報 ( 3 2 b i t = 8 × 4 ) を特定する画像データを格納するフレームバッファ領域、及び各表示ピクセルの深度情報を

40

50

記憶する Z バッファ領域などが必要となる。なお、 A R G B 情報において、 A は 8 b i t の プレーンデータ、 R G B は三原色の 8 b i t データを意味する。

#### 【 0 1 0 9 】

ここで、内蔵 V R A M 2 0 2 の上記した各領域は、演出制御 C P U 1 8 1 がディスプレイリスト D L に記載した各種の指示コマンド（テクスチャやスプライトなど）に基づいて間接的にアクセスされるが、その R E A D / W R I T E アクセスにおいて、一々、内蔵 V R A M 2 0 2 の D e s t i n a t i o n アドレスや S o u r c e アドレスを特定するのでは煩雑である。そこで本実施形態では、 C P U リセット後の初期処理において、描画動作で必要となる一次元または二次元の論理アドレス空間（以下、インデックス空間という）を確保して、各インデックス空間にインデックス番号を付与することで、インデックス番号に基づくアクセスを可能にしている。

10

#### 【 0 1 1 0 】

具体的には、 C P U リセット後、内蔵 V R A M 2 0 2 を 3 種類のメモリ領域に大別すると共に、各メモリ領域に、必要数のインデックス空間を確保している。そして、インデックス空間とインデックス番号とを紐付けて記憶するインデックステーブル I D X T B L ( 図 1 6 ( a ) 参照 ) を構築することで、その後のインデックス番号に基づく動作を実現している。

#### 【 0 1 1 1 】

このインデックス空間は、（ 1 ）初期処理後に追加することや、逆に（ 2 ）開放することも必要となる。そこで、これら追加 / 開放の演出制御 C P U 1 8 1 の動作時に、追加 / 開放の処理が可能なタイミングか否か、また追加 / 開放などの処理が実際に完了したか否か等を判定可能なフラグ領域 F G をインデックステーブル I D X T B L に設けている。なお、内蔵 V R A M 2 0 2 は、以下に説明する 2 つの A A C 領域 ( a 1 , a 2 ) 、ページ領域 ( b ) 、任意領域 ( c ) の三種類のメモリ領域に大別され、この三種類のメモリ領域 ( a 1 , a 2 ) ( b ) ( c ) に対応して、インデックステーブル I D X T B L が 3 区分されている（図 1 6 ( a ) ）。図示の通り、この実施形態では、 A A C 領域 ( a ) として、第一 A A C 領域 ( a 1 ) と第二 A A C 領域 ( a 2 ) が確保されているが、これに限定されるものではなく、何れか一方だけでもよい。なお以下の説明では、第一と第二の A A C 領域 ( a 1 , a 2 ) を総称する場合には、 A A C 領域 ( a ) と称する場合がある。

20

#### 【 0 1 1 2 】

本実施形態の場合、内蔵 V R A M 2 0 2 は、（ a ）インデックス空間とそのインデックス番号が内部処理によって自動付与され、且つメモリキャッシュ機能を有する A A C 領域と、（ b ）例えば 4 0 9 6 b i t × 1 2 8 ラインの二次元空間を単位空間として、その整数倍の範囲でインデックス空間が確保可能なページ領域と、（ c ）先頭アドレス（空間先頭アドレス） S T x と水平サイズ H x が任意に設定できる任意領域とに区分可能に構成されている（図 1 6 ( b ) 参照）。但し、 V D P 回路 1 7 2 の内部動作を円滑化するため、任意領域 ( c ) において任意設定されるインデックス空間の空間先頭アドレス S T x は、その下位 1 1 b i t が 0 であって、所定ビット ( 2 0 4 8 b i t = 2 5 6 バイト ) 単位とする必要がある。

30

#### 【 0 1 1 3 】

そして、 C P U リセット後、各々に必要なアドレス空間の最大値と、領域先頭アドレス（下位 1 1 b i t = 0 ）を規定して、 A A C 領域 ( a 1 ) と、第二 A A C 領域 ( a 2 ) と、ページ領域 ( b ) とが確保され、その残りのメモリ領域が任意領域 ( c ) となる。 V D P 回路 1 7 2 の内部動作を円滑化するため、 A A C 領域のアドレス空間の最大値は 2 0 4 8 b i t 単位で規定され、ページ領域のアドレス空間の最大値は、上記した 4 0 9 6 b i t × 1 2 8 ラインの単位空間の整数倍とされる。

40

#### 【 0 1 1 4 】

次に、このように確保された各領域 ( a 1 , a 2 ) ( b ) ( c ) に必要個数のインデックス空間が設定される。なお、任意領域 ( c ) を使用する場合、 V D P 回路 1 7 2 の内部動作を円滑化するため、二次元データを扱うインデックス空間の水平サイズ H x は、 2 5

50

6 bit の倍数として任意に設定可能である一方、その垂直サイズは固定値（例えば 2048 ライン）となっている。

#### 【 0115 】

何れにしても、第一と第二の AAC 領域 ( a1 , a2 ) は、 VDP 回路 172 によってインデックス空間とインデックス番号が自動的に付与されるので、例えばテクスチャ設定系コマンドの SET INDEX コマンドによって、デコード先を AAC 領域 ( a ) に指定すれば、 CGROM107 から CG データを読み出す TXLOAD ( テクスチャロード ) コマンドでは、 CGROM107 の Source アドレスと、展開 ( デコード ) 後の水平・垂直サイズなどを指定するだけで足りることになる。そこで本実施形態では、予告演出時などに一時的に出現するキャラクタなどの静止画 ( テクスチャ ) やイストリーム動画については、そのデコード先を AAC 領域 ( a ) にしている。

10

#### 【 0116 】

この AAC 領域 ( a ) は、いずれもメモリキャッシュ機能が付与されているので、例えば、 CGROM107 の同一のテクスチャを複数回、 AAC 領域 ( a ) に読み出すような場合には、二度目以降は AAC 領域 ( a ) にキャッシュされているデコードデータが活用可能となり、余分な READ アクセスとデコード処理が抑制可能となる。もっとも、 AAC 領域 ( a ) を使い切った場合には、古いデータが自動的に破壊されるので、本実施形態では、 AAC 領域 ( a ) を使用する場合、原則として第一 AAC 領域 ( a1 ) を使用することとし、繰り返し使用する特定のテクスチャだけを第二 AAC 領域 ( a2 ) に取得するようになっている。

20

#### 【 0117 】

繰り返し使用するテクスチャとして、例えば所定の予告演出時に繰り返し出現するキャラクタや、背景画面を静止画で構築する場合の背景画などを例示することができる。このような場合、テクスチャ設定系コマンドの SET INDEX コマンドによって、デコード先を第二 AAC 領域 ( a2 ) に設定し、 TXLOAD コマンドによって、キャラクタや背景画などのテクスチャを第二 AAC 領域 ( a2 ) にデコードした後は、第二 AAC 領域 ( a2 ) を使用しないことで、デコード結果を保護する。

#### 【 0118 】

そしてその後、 SET INDEX コマンドによって、デコード先を第二 AAC 領域 ( a2 ) に指定した上で、取得済みのテクスチャを再取得する同一の TXLOAD コマンドを実行させると、取得済みのテクスチャがキャッシュヒットするので、 CGROM107 への READ アクセスとデコード処理に要する時間を削除することができる。このようなキャッシュヒット機能は、プリロード領域に先読みされたプリロードデータでも発揮されるが、プリロード領域でキャッシュヒットするプリロードデータは、デコード前の圧縮データであるのに対して、 AAC 領域でキャッシュヒットするのはデコード後の展開データである点に意義がある。

30

#### 【 0119 】

ところで、テクスチャ ( texture ) とは、一般に物の表面の質感、手触りなどを指す概念であるが、本実施形態では、静止画を構成するスプライト画像データ、動画一フレームを構成する画像データ、三角形や四角形などの描画プリミティブ ( primitive ) に貼り付ける画像データだけでなく、デコード後の画像データも含む概念として使用している。そして、内蔵 VRAM202 の内部で画像データをコピーする（以下、便宜上、移動と称する）場合には、テクスチャ設定系コマンドの SET INDEX コマンドによって、移動元の画像データをテクスチャとして設定した上で、 SPRITE コマンドを実行することになる。

40

#### 【 0120 】

なお、 SPRITE コマンドの実行により、移動元の Source 画像データが、形式上は図 16 ( c ) に示す仮想描画空間に描画されるが、表示装置に実際に描画される仮想描画空間内の描画領域と、フレームバッファとなるインデックス空間との対応関係を、予め環境設定コマンド ( SETDAVR , SETDAVF ) や、テクスチャ設定系コマンド

50

(SET INDEX)によって設定しておけば、例えばSPRITEコマンドによる仮想描画空間への描画により、所定のインデックス空間（フレームバッファ）には、移動元のSource画像データが描画されることになる（図16（c）参照）。

#### 【0121】

何れにしても、本実施形態では内蔵VRAM202がAAC領域（a1, a2）とページ領域（b）と任意領域（c）とに大別され、各々に適當数のインデックス空間を確保することができ、各インデックス空間は、各領域（a）（b）（c）ごとに独立のインデックス番号によって特定される。インデックス番号は、例えば1バイト長であり、（内部回路によって自動付与されるAAC領域（a）を除いた）ページ領域（b）と任意領域（c）については、0～255の範囲で演出制御CPU181がインデックス番号を自由に付与することができる。

10

#### 【0122】

そこで本実施形態では、図16（a）に示す通り、液晶表示手段76用として、任意領域（c）に一对のフレームバッファFBaを確保して、ダブルバッファ構造の双方に、インデックス番号255, 254を付与している。すなわち、液晶表示手段76用のフレームバッファFBaとして、トグル的に切り換えて使用されるインデックス空間255と、インデックス空間254を確保している。特に限定されないが、このインデックス空間255, 254は、液晶表示手段76の横方向ピクセル数に対応して水平サイズ1280をしている。なお、各ピクセルはARGB情報32bitで特定されるので、水平サイズ1280は、 $32 \times 1280 = 40960$ bit（256bitの倍数）を意味する。

20

#### 【0123】

なお、フレームバッファFBaを任意領域（c）に確保するのは、任意領域（c）には、32バイト（=256bit=8ピクセル分）の倍数として、任意の水平サイズに設定することができ、上記のように液晶表示手段76の水平ピクセル数に一致させれば、確保領域に無駄が生じないからである。一方、ページ領域（b）には128ピクセル×128ラインの単位空間の整数倍の水平／垂直サイズしか設定できない。但し、任意領域（c）に確保される二次元のインデックス空間は、その垂直サイズが固定値（例えば、2048ライン）となっている。そのため、フレームバッファFBaにおいて、水平サイズ1280×垂直サイズ1024の領域だけが、液晶表示手段76にとって有効データ領域となる。

30

#### 【0124】

また本実施形態では、フレームバッファFBaが確保された任意領域（c）に追加のインデックス空間（メモリ領域）を確保する場合には、0から始まるインデック番号を付与するようにしている。何ら限定されないが、本実施形態では、キャラクタやその他の静止画で構成された演出画像を、必要に応じて、適宜な回転姿勢で表示画面の一部に出現させる予告演出用の作業領域として、任意領域（c）にインデックス空間（0）を確保している。

#### 【0125】

但し、作業領域の使用は必須ではなく、また任意領域（c）に代えて、ページ領域（b）に作業領域としてのインデックス空間を確保してもよい。ページ領域（b）を使用すれば、水平サイズ128（=4096bit）×垂直サイズ128の正方形形状の単位空間の倍数寸法のインデックス空間を確保できるので、小型の演出画像を扱うには好適である。

40

#### 【0126】

ところで、本実施形態では、画像演出は背景画像も含めてほぼ動画のみで実現されている。特に変動演出時には、多数（通常10個以上）の動画が同時に描画される。これらの動画は、何れも一連の動画フレームとして、圧縮状態でGROM107に格納されているが、Iフレームのみで構成されたIストリーム動画と、IフレームとPフレームとで構成されたIPストリーム動画とに区分される。ここで、Iフレーム（Intra coded frame）とは、他画面とは独立して、入力画像をそのまま圧縮するフレームを意味する。一方、Pフレーム（Predictive coded frame）とは、前方向予測符号化を行うフレームを意味し、時間的に過去に位置するIフレームまたはPフレームが必要となる。

50

## 【0127】

そこで本実施形態では、IPストリーム動画については、旧データの破壊が懸念されるAAC領域(a)ではなく、ページ領域(b)に展開している。すなわち、水平サイズ128×垂直サイズ128の倍数寸法のインデックス空間を確保可能なページ領域(b)に多数のインデックス空間(IDX0～IDXN)を確保して、一連の動画フレームは、各動画MViに対応する、常に同一のインデックス空間IDXiを使用してデコードするようしている。すなわち、動画MV1はインデックス空間IDX1に展開され、動画MV2はインデックス空間IDX2に展開され、以下同様に、動画MViはインデックス空間IDXiに展開されるよう構成されている。

## 【0128】

動画MViについて、更に具体的に説明すると、SETINDEXコマンドによって、「IPストリーム動画MViのデコード先は、ページ領域(b)におけるインデックス番号iのインデックス空間(i)である」と予め指定した上で、IPストリーム動画MViの動画フレームを取得するTXLOADコマンドを実行させている。

## 【0129】

すると、TXLOADコマンドが特定するCGRM107上の動画フレーム(一連の動画フレームの何れか)が、先ずAAC領域(a)に取得され、その後、自動的に起動するグラフィックスデコーダ(GDEC)205によって、ページ領域(b)のインデックス空間(i)に、取得した動画フレームがデコードされて展開されることになる。

## 【0130】

一方、本実施形態では、ESTRIM動画については、静止画と同一扱いとしており、SETINDEXコマンドによって、「ESTRIM動画MVjのデコード先は、第一AAC領域(a1)である」と指定して、TXLOADコマンドを実行させる。その結果、動画フレームは第一AAC領域(a1)に取得され、その後、自動的に起動するグラフィックスデコーダ205が、第一ACC領域(a1)にデコードデータを展開している。先に説明した通り、AAC領域(a)のインデックス空間は自動的に生成されるので、インデックス番号を指定する必要はない。なお、インデックス空間に必要となる展開ボリューム、つまりデコードされたテクスチャ(動画フレーム)の水平サイズと垂直サイズは、展開先がAAC領域(a)かページ領域(b)かに拘らず、TXLOADコマンドによって特定される。

## 【0131】

ところで、IPストリーム動画MViやESTRIM動画MVjは、一般にN枚の動画フレーム(IフレームやPフレーム)で構成されている。そのため、TXLOADコマンドでは、例えばk枚目(1～k～N)の動画フレームが記憶されているCGRM107のSourceアドレスと、展開後の水平・垂直サイズなどを指定することになる。何ら限定されないが、静止画を殆ど使用しない本実施形態では、内蔵VRAM202のアドレス空間48Mバイトの大部分(30Mバイト程度)をページ領域(b)に割り当てている。そして、静止画を殆ど使用しない本実施形態では、AAC領域として、第一AAC領域(a1)だけを確保し、第二AAC領域(a2)を確保せず、また前記したAAC領域のキャッシュヒット機能も活用しない。

## 【0132】

なお、圧縮動画データのデコード処理を高速化するため、専用のGDEC(グラフィックスデコーダ)回路を設けることも考えられる。そして、専用のGDEC回路をVDP回路172に内蔵されれば、N枚の圧縮動画フレームで構成された圧縮動画データのデコード処理において、動画圧縮データの先頭アドレスをGDEC回路に指示すれば足りるので、N枚の圧縮動画フレームについて、1枚ごとに先頭アドレスを指定する必要がなくなる。

## 【0133】

しかし、このような専用のGDEC回路を、圧縮アルゴリズム毎に複数個内蔵せると、VDP回路172の内部構成が更に複雑化する。そこで本実施形態では、ソフトウェアGDECとし、IPストリーム動画、ESTRIM動画、静止画、その他 値などのデータ

10

20

30

40

50

タについて、各圧縮アルゴリズムに対応するソフトウェア処理によってデコード処理を実現している。なお、ハードウェア処理とソフトウェア処理の処理時間差はあまり問題にならず、処理時間が問題になるのは、もっぱら、CGROM107からのアクセス(READ)タイムである。

#### 【0134】

図14に戻って説明を続ける。データ転送回路203は、VDP回路内部のリソース(記憶媒体)と外部記憶媒体とを、転送元ポート又は転送先ポートとして、これらの間でDMA(Direct Memory Access)的にデータ転送動作を実行する回路である。図17は、このデータ転送回路203の内部構成を、関連する回路構成と共に記載したブロック図である。

10

#### 【0135】

図17に示す通り、データ転送回路203は、ルータ機能を有する統合接続バスICMを経由して、CGROM107、DRAM106及び内蔵VRAM202とデータを送受信するよう構成されている。なお、CGROM107とDRAM106は、CGバスIF部213やDMAIF部214を経由してアクセスされる。

#### 【0136】

一方、CPU回路171は、データ転送回路203に内蔵された転送ポートレジスタTR\_PORTを経由して、描画回路206やプリローダ204にディスプレイリストDLを発行している。なお、CPU回路171とデータ転送回路203は双方向に接続されているが、ディスプレイリストDLの発行時には、転送ポートレジスタTR\_PORTは、ディスプレイリストDLを構成する一単位のデータを受け入れるデータ書き込みポートとして機能する。なお、転送ポートレジスタTR\_PORTの書き込み単位(一単位データ長)は、CPUバス制御部203dの FIFO構造に対応して32bitとなる。

20

#### 【0137】

図示の通り、演出制御CPU181は、CPUIF部212を経由して転送ポートレジスタTR\_PORTをWRITEアクセスできる一方、DMAC回路183を活用する場合には、DMAC回路183が転送ポートレジスタTR\_PORTを直接的にWRITEアクセスすることになる。そして、転送ポートレジスタTR\_PORTに書き込まれた一連の指示コマンド(つまり、ディスプレイリストDLを構成する指示コマンド列)は、32bit単位で、FIFO構造(32bit×130段)のFIFOバッファを内蔵したCPUバス制御部203dに自動蓄積されるように構成されている。

30

#### 【0138】

また、このデータ転送回路203は、3チャンネルChA～ChCの伝送経路でデータの送受信動作を実行しており、FIFO構造(64bit×N段)のFIFOバッファを有するChA制御回路203a(N=130段)と、ChB制御回路203b(N=1026段)と、ChC制御回路203c(N=130段)とを有している。

#### 【0139】

そして、CPUバス制御部203dに蓄積された指示コマンド列(ディスプレイリストDL)は、演出制御CPU181によるデータ転送レジスタRGij(各種制御レジスタ201の一種)への設定値に基づき、描画回路206又はプリローダ204に転送される。矢印で示す通り、ディスプレイリストDLは、CPUバス制御部203dからChB制御回路203bのFIFOバッファを経由して描画回路206に転送され、ChC制御回路203cのFIFOバッファを経由してプリローダ204に転送されるように構成されている。

40

#### 【0140】

なお本実施形態では、ChB制御回路203bとChC制御回路203cは、ディスプレイリストDLの転送動作に特化されており、CPUバス制御部203dのFIFOバッファに蓄積されたデータは、ChB制御回路203bかChC制御回路203cのFIFOバッファを経由して、各々ディスプレイリストDLの一部として、描画回路206かプリローダ204のディスプレイリストアナライザ(Display List Analyzer)に転送され

50

る。

#### 【0141】

そして、描画回路206は、転送されたディスプレイリストDLに基づいた描画動作を開始する。一方、プリローダ204は、転送されたディスプレイリストDLに基づき、必要なプリロード動作を実行する。プリロード動作によって、CGROM107のCGデータが、DRAM106に確保されたプリロード領域に先読みされ、TXLOADコマンドなどに関して、テクスチャのSourceアドレスを変更したディスプレイリストDL（以下、書換えリストDLという）が、DRAM106に確保されたDLバッファ領域BUFに保存される。

#### 【0142】

一方、CGROM107、DRAM106、内蔵VRAM202等の記憶媒体の間のデータ転送には、ChA制御回路203aと接続バスアクセス調停回路203eとが機能する。また、インデックステーブルIDX\_TBLのアドレス情報が必要になる内蔵VRAM202のアクセス時には、IDX\_TBLアクセス調停回路203fが機能する。具体的には、ChA制御回路203aは、例えば（a）CGROM107の圧縮データを内蔵VRAM202に転送する場合や、（b）CGROM107の圧縮データをプリロード（先読み）して外付けDRAM106に転送する場合や、（c）プリロード領域の先読みデータを内蔵VRAM202に転送する場合に機能する。

#### 【0143】

ここで、ChA制御回路203aは、ChB制御回路203bやChC制御回路203cと並行して動作可能に構成されており、上記した（a）～（c）の動作は、ディスプレイリストDLの発行動作や書換えリストDL'の転送動作と並行して実行可能である。また、ChB制御回路203bとChC制御回路203cも同時実行可能である。但し、転送ポートレジスタTR\_PORTは単一であるので、何れか一方（203b/203c）が転送ポートレジスタTR\_PORTを使用しているタイミングでは、他方（203c/203b）は転送ポートレジスタTR\_PORTにアクセスすることはできない。

#### 【0144】

なお、ChA制御回路203aの動作時に、接続バスアクセス調停回路203eは、統合接続バスICMを経由する各記憶素子（CGROM107、DRAM106）とのデータ伝送を調停（Arbitration）している。一方、IDX\_TBLアクセス調停回路203fは、インデックステーブルIDX\_TBLに基づいてChA制御回路203aを制御することで、内蔵VRAM202とのデータ交信を調停している。なお、プリローダ204が機能する本実施形態の場合、DRAM106のDLバッファ領域BUFに保存された書換えリストDLは、接続バスアクセス調停回路203eとChB制御回路203bとを経由して描画回路206に転送される。

#### 【0145】

上記の通り、本実施形態のデータ転送回路203は、各種の記憶リソース（Resource）から任意に選択されたデータ転送元と、各種の記憶リソース（Resource）から任意に選択されたデータ転送先との間で、高速のデータ転送を実現している。なお、データ転送回路203が機能する記憶リソースには、内蔵VRAM202だけでなく、CPUIF部212、CGバスIF部213、DRAMIF部214を経由する外部デバイスも含まれる。

#### 【0146】

そして、CGROM107から1回に取得すべきデータ量（メモリシーケンシャルREAD）のように、ChA制御回路203aが機能する外部デバイスとのデータ転送量は、ChB制御回路203bやChC制御回路203cが機能するディスプレイリストDLの場合と比較して膨大であり、互いにデータ転送量が大きく相違する。

#### 【0147】

ここで、これら各種のデータ転送について、単位データ量や総転送データ量を細かく設定可能に構成することも考えらえるが、これではVDP内部の制御動作が煩雑化し、円滑

10

20

30

40

50

な転送動作が阻害される。そこで本実施形態では、データ転送の最低データ量  $D_{min}$  を一意に規定すると共に、総転送データ量を、最低データ量  $D_{Tmin}$  の整数倍となるよう制限することで、高速で円滑なデータ転送動作を実現している。特に限定されないが、本実施形態のデータ転送回路 203 では、最低データ量  $D_{min}$  ( 単位データ量 ) を 256 バイトとし、総転送データ量をこの整数倍に制限することにしている。

#### 【 0148 】

したがって、32bit 毎に CPU バス制御部 203d の FIFO バッファに蓄積されたディスプレイリスト DL の指示コマンド列は、その総量が最低データ量  $D_{min}$  に達したタイミングで ChB 制御回路 203b や ChC 制御回路 203b に転送され、各々の FIFO バッファに蓄積される。

10

#### 【 0149 】

ディスプレイリスト DL は、一連の指示コマンドで構成されているが、本実施形態では、転送ポートレジスタ TR\_PORT の書き込み単位 ( 32bit ) に対応して、ディスプレイリスト DL は、コマンド長が 32bit の整数 N 倍 (  $N > 0$  ) の指示コマンドのみで構成されている。したがって、データ転送回路 203 を経由して、ディスプレイリスト DL の指示コマンドを受ける描画回路 206 やプリローダ 204 は、素早く円滑にコマンド解析処理 ( DL analyze ) を開始することができる。なお、32bit の整数 N 倍のコマンド長は、その全てが有意ビットとは限らず、無意ビット ( Don't care bit ) も含んで 32bit の整数 N 倍という意味である。

#### 【 0150 】

次に、プリローダ 204 について説明する。プリローダ 204 は、データ転送回路 203 ( ChC 制御回路 203b ) から転送されたディスプレイリスト DL を解釈して、 TXLOAD コマンドが参照している CGROM107 上の CG データを、予め DRAM106 のプリロード領域に転送する回路である。またプリローダ 204 は、この TXLOAD コマンドに関し、 CG データの参照先を転送後のアドレスに書換えた書換えリスト DL を、 DRAM106 の DL バッファ BUF に記憶する。なお、 DL バッファ BUF やプリロード領域は、 CPU リセット後の初期処理時に予め確保されている。

20

#### 【 0151 】

そして、書換えリスト DL は、描画回路 206 の描画動作の開始時に、データ転送回路 203 の接続バスアクセス調停回路 203e や ChB 制御回路 203b を経由して描画回路 206 のディスプレイリストアナライザ ( DL Analyzer ) に転送される。そして、描画回路 206 は、書換えリスト DL に基づいて描画動作を実行する。したがって、 TCOLLOAD コマンドなどに基づき、本来は CGROM107 から取得すべき CG データが、プリロード領域に先読みされているプリロードデータとして DRAM106 のプリロード領域から取得される。この場合、プリロードデータは、上書き消去されない限り繰り返し使用可能であり、プリロード領域にキャッシュヒットしたプリロードデータは繰り返し再利用される。

30

#### 【 0152 】

本実施形態では、十分な記憶容量を有する外付け DRAM106 にプリロード領域を設定しているので、上記のキャッシュヒット機能が有効に機能する。また、外付け DRAM106 の記憶容量が大きいので、例えば複数フレーム分の CG データを一気にプリロードする多重プリロードも可能である。すなわち、プリローダ 204 の動作期間に関し、 CG データの先読み動作を含んだ一連のプリロード動作の動作期間を、 VDP 回路 172 の間欠動作時の動作周期 の整数倍の範囲内で適宜に設定することで多重プリロードが実現される。

40

#### 【 0153 】

但し以下の説明では、便宜上、多重プリロードのない構成について説明するので、本実施形態のプリローダ 204 は、一動作周期 ( ) の間に一フレーム分のプリロード動作を完了することとする。なお本実施形態では、 VDP 回路 172 の間欠動作時の動作周期は、液晶表示手段 76 の垂直同期信号の 2 倍周期である 1 / 30 秒である。

50

## 【0154】

次に、描画回路206は、データ転送回路203を経由して転送されたディスプレイリストDLや書換えリストDLの指示コマンド列を順番に解析して、グラフィックスデコーダ205やジオメトリエンジン207等と協働して、VRAM202に形成されたフレームバッファに液晶表示手段76の一フレーム分の画像を描画する回路である。

## 【0155】

上記の通り、プリローダ204を機能させる場合には、書換えリストDLのCGデータの参照先は、CGROM107ではなくDRAM106に設定されたプリロード領域である。そのため、描画回路206による描画の実行中に生じるCGデータへのシーケンシャルアクセスを迅速に実行することができ、動きの激しい高解像度の動画についても問題なく描画することができる。すなわち、本実施形態によれば、CGROM107として安価なSATAモジュールを活用しつつ、複雑高度な画像演出を実行することができる。

10

## 【0156】

ところで、プリローダ204を機能させるか否かに拘らず、ディスプレイリストDLや書換えリストDLの転送時に仮にデータ化けが発生しても、描画回路206はこれを検出することはできない。また、ノイズなどの影響で、描画回路206がフリーズして、内蔵VRAM202のREAD/WRITEアクセスが異常停止することも有り得る。そこで本実施形態では、描画回路206が不合理な指示コマンド(analyze不能のビット並び)を検出した場合や、一定期間、内蔵VRAM202に対してREAD/WRITEアクセスがない場合には、描画異常割込みを発生させるように構成されている(描画異常割込みが許可状態)。

20

## 【0157】

次に、図16に関して説明した通り、VRAM202の任意領域(c)に確保されたフレームバッファFBは、描画領域と読出領域に区分されたダブルバッファであり、2つの領域を、交互に用途を切り替えて使用する。また本実施形態では、1つの液晶表示手段76が接続されているので、図16に示す通り、1区画のフレームバッファFBaが確保されている。したがって、描画回路206は、液晶表示手段76用のフレームバッファFBaの描画領域(書き込み領域)に、一フレーム分の画像データを描画することになる。

## 【0158】

表示回路208A～208Cは、フレームバッファFBa～FBcの画像データを読み出して、最終的な画像処理を施した上で出力する回路である(図18参照)。最終的な画像処理には、例えば、画像を拡大/縮小するスケーラのスケーリング処理、微妙なカラー補正処理、画像全体の量子化誤差が最小化するディザリング処理が含まれている。そして、これらの画像処理を経たデジタルRGB信号(合計24bit)が、通常は、水平同期信号HSや垂直同期信号VSなどと共に出力される。

30

## 【0159】

図18に示す通り、本実施形態では、上記の動作を並列的に実行する3系統の表示回路A/B/Cが設けられており、各表示回路208A～208Cは、各々に対応するフレームバッファFBa/FBb/FBcの画像データを読み出して、上記の最終画像処理を実行する。但し、本実施形態では表示装置は1個であるので、フレームバッファFBb, FBcは確保されておらず、表示回路208B, 208Cが機能することもない。

40

## 【0160】

ここで、液晶表示手段76の仕様を確認すると、液晶表示手段76は、左右方向に隣接する奇数ピクセル(ODD)と偶数ピクセル(EVEN)とを、別々のLVDS(Low Voltage Differential Signaling)伝送路を通して受信部RV(RVa, RVb)で受け必要がある。また、液晶表示手段76のドットクロックDCKの周波数は、40～70MHz程度(典型値は54MHz)にする必要があり、(WTh+640)×(WTv+1024)/54MHz 1/60秒となるよう、水平/垂直方向の待機時間WTh/WTvを設定する必要がある。更に、液晶表示手段76に対して画像データ(ODD/EVEN信号)を出力するタイミングでは、アクティブルのデータ有効信号ENABLEを出

50

力する必要がある。

【0161】

そこで、表示回路208Aは、上記した全ての仕様を満たす信号を出力する必要がある。図19(a)～図19(e)は、表示回路208Aから出力される各種の信号を図示したものである。まず、ドットクロックDCKの周波数を決定する必要があるが、本実施形態では、液晶表示手段76を、典型値54MHzの動作クロックCKで動作させて、これに対応して、VDP回路172における設計上のドットクロックDCKを108MHz( $= 54 \times 2$ )としている。

【0162】

それは、横1280ドット×縦1024ラインの表示パネルLCD(図19(f)参照)において、左右に隣接する2つの画素が54MHzの動作クロックCKに同期して一気に処理されるので、実質的に108MHzのドットクロックDCKで動作するのと等価だからである。

【0163】

そして、表示回路208Aの動作を規定する各種の動作パラメータは、周波数108MHzのドットクロックDCKに基づいて規定される。先ず、 $(WT_h + 640) \times (WT_v + 1024) / 54\text{MHz} = 1/60\text{秒}$ となるよう、水平/垂直方向の待機時間WT<sub>h</sub>/WT<sub>v</sub>を設定する必要があるが、表示回路208Aについての動作パラメータWT<sub>h</sub>/WT<sub>v</sub>としては、 $(WT_h + 1280) \times (WT_v + 1024) / 108\text{MHz} = 1/60\text{秒}$ を満たす必要がある。

【0164】

また、水平/垂直方向の待機時間WT<sub>h</sub>/WT<sub>v</sub>について、液晶表示手段76の仕様上の許容範囲も考慮する必要がある。そこで本実施形態では、水平方向待機時間WT<sub>h</sub>を、108MHzのドットクロックDCKでカウントして382クロックとし、垂直方向待機時間WT<sub>v</sub>を59ラインとしている。したがって、一フレームの画像更新に要する時間は、 $(382 + 1280) \times (59 + 1024) / 108\text{MHz} = 16.666\text{mS}$ となり、フレームレートが1/60秒となる。

【0165】

この設定に対応して、データ有効信号ENABは、各ラインの画像更新動作において、382クロックに対応する待機時間WT<sub>h</sub>( $= 382 / 108\text{MHz}$ )はLレベルであり、その後、1280クロックに対応するアクティブ区間( $= 1280 / 108\text{MHz}$ )はアクティブ(H)レベルとなる(図19(c))。なお、図19(d), (e)に示す通り、データ有効信号ENABのアクティブ区間では、一ライン1280ドットの画素について、所定の時間( $11.85\mu\text{S} = 1280 / 108\text{MHz}$ )で画像更新動作が完了するように画像データが outputされる。すなわち、1280個のドットクロックDCKに同期して、1280個の画素データ(Pixel Data)が outputされる。なお、液晶表示手段76には階調度 $2^8 \times 2^8 \times 2^8$ のフルカラー画像が表示されるので、1画素の画素データは $3 \times 8$ ビット長である。

【0166】

ところで本実施形態では、液晶表示手段76では必要とはされないものの、垂直同期信号VSと水平同期信号HSを出力している。垂直同期信号VSは垂直方向待機時間WT<sub>v</sub>の時間内に出力され、水平同期信号HSは水平方向待機時間WT<sub>h</sub>の時間内に出力される。なお、図19(a), (b)には、理解の便宜上、各々の動作周期が示されている。また、図19(f)には、TH×TV( $= 1083 \times 1662$ クロック)で特定される矩形枠の左上と右下の頂点に○印を示して、夫々「表示動作の開始」「表示動作の終了」と記載されているが、この○印は1/60秒ごとに開始される「Vブランク開始」を意味する。表示動作を規定する $1083 \times 1662$ クロックが1/60秒に一致するので、「表示動作の開始」から「表示動作の終了」までの経過時間は1/60秒である。

【0167】

図18に戻って説明を続けると、本実施形態の出力選択部209は、表示回路208A

10

20

30

40

50

の出力信号を、108MHzのドットクロックDCKを2分周するデュアルリンクに分割して、各々LVDS部210aとLVDS部210bとに伝送している（図18、図13参照）。そして、各LVDS部210a, 210bは、画像データ（合計24bitのデジタルRGB信号）を第1, 第2LVDS信号に変換し、これにクロック信号（54MHz = 108 / 2）を伝送する一対を加えて、全五対の差動信号LVDS1, LVDS2として、2つの経路を経由して液晶表示手段76に出力している（図18, 図12参照）。

#### 【0168】

先に説明した通り、液晶表示手段76では、一画素分のODD信号と、隣接する一画素分の EVEN信号とが同じタイミングで処理されるので、実質的なドットクロックDCKの周波数は、表示回路208Aが出力する108MHzのドットクロックDCKに一致する。

10

#### 【0169】

ところで本実施形態の場合、表示回路208A～208Cには、表示タイミングに対して表示データの生成が間に合わなかったアンダーラン異常をカウントするアンダーランカウンタURCNTa～URCNTcが設けられている（図18参照）。そして、このアンダーランカウンタURCNTa～URCNTcのカウンタ値は、アンダーラン異常が発生するとVBLANK毎に自動的に加算されるよう構成されている。

#### 【0170】

次に、SMC（Serial Management Controller）部211は、LEDコントローラとMotorコントローラとを内蔵した複合コントローラである。そして、外部基板に搭載したLED/Motorドライバ（シフトレジスタを内蔵するドライバI/C）に対して、クロック信号に同期してLED駆動信号やモータ駆動信号を出力する一方、適宜なタイミングでラッチパルスを出力可能に構成されている。

20

#### 【0171】

上記したVDP回路172の内部回路及びその動作に関し、内部回路が実行すべき動作内容は、演出制御CPU181が制御レジスタ群201に設定する動作パラメータ（設定値）で規定され、VDP回路172の実行状態は、制御レジスタ群201の動作ステータス値をREADすることで特定できるようになっている。制御レジスタ群201は、演出制御CPU181のメモリマップ上、1Mバイト程度のアドレス空間（0～FFFFFH）にマッピングされた多数のVDPレジスタRGijを意味し、CPU回路171の演出制御CPU181は、CPUIF部212を経由して動作パラメータのWRITE（設定）動作と動作ステータス値のREAD動作とを実行するようになっている（図15参照）。

30

#### 【0172】

制御レジスタ群201（VDPレジスタRGij）には、図15に示すように、割り込み動作などシステム動作に関する初期設定値が書き込まれる「システム制御レジスタ」と、内蔵VRAM202にAAC領域（a）やページ領域（b）を確定すると共にインデックステーブルIDXTBLを構築又は変更するための「インデックステーブルレジスタ」と、演出制御CPU181とVDP回路172の内部回路との間のデータ転送回路203によるデータ転送処理に関する設定値などが書き込まれる「データ転送レジスタ」と、グラフィックスデコーダ205の実行状況を特定する「GDECレジスタ」と、指示コマンドや描画回路206に関する設定値が書き込まれる「描画レジスタ」と、プリローダ204の動作に関する設定値が書き込まれる「プリローダレジスタ」と、表示回路208の動作に関する設定値が書き込まれる「表示レジスタ」と、LEDコントローラ（SMC部211）に関する設定値が書き込まれる「LED制御レジスタ」と、Motorコントローラ（SMC部211）に関する設定値が書き込まれる「モータ制御レジスタ」と、音声回路SNDに関する設定値が書き込まれる「音声制御レジスタSRG」と、が含まれている。但し、本実施形態では音声回路SNDを活用していない。

40

#### 【0173】

何れにしても、演出制御CPU181は、所定のVDPレジスタRGijに適宜な設定値を書込むことでVDP回路172の内部動作を制御している。具体的には、演出制御C

50

P U 1 8 1 は、適宜な時間間隔で更新するディスプレイリスト D L と、所定の V D P レジスタ R G i j への設定値とに基づいて所定の画像演出を実現している。なお、本実施形態では、ランプ演出やモータ演出も含めて演出制御 C P U 1 8 1 が担当するので、V D P レジスタ R G i j には L E D 制御レジスタやモータ制御レジスタも含まれる。

#### 【 0 1 7 4 】

続いて、演出制御部 9 5 を構成する液晶制御基板 9 8 及び液晶インターフェース基板 9 7 について、配線パターン等の詳細を説明する。まずは液晶制御基板 9 8 について説明する。

#### 【 0 1 7 5 】

液晶制御基板 9 8 は、基板本体 1 9 0 ( 図 8 参照 ) に複数の配線層、具体的には表面 ( 第 1 面 ) 9 8 a 側の第 1 配線層 L a 1 と、裏面 ( 第 2 面 ) 9 8 b 側の第 6 配線層 L a 6 と、それらの間に配置される第 2 ~ 第 5 配線層 L a 2 ~ L a 5 とよりなる計 6 層の第 1 ~ 第 6 配線層 L a 1 ~ L a 6 ( 図 2 0 ~ 図 2 5 ) を備えている。なお、第 2 配線層 L a 2 ( 図 2 1 ) はグランドに接続されるベタ配線層、第 5 配線層 L a 5 ( 図 2 4 ) は電源に接続されるベタ配線層となっている。また、液晶制御基板 9 8 の基板本体 1 9 0 には多数のビア ( 層間導通部 ) が板厚方向に設けられており、複数の配線層 L a 1 ~ L a 6 はそれらのビア ( 層間導通部 ) を介して互いに導通されている。本実施形態で使用されるビアは、スルーホールにメッキを施したスルーホール型のビアで、基板本体 1 9 0 の表面 ( 第 1 面 ) 9 8 a から裏面 ( 第 2 面 ) 9 8 b まで貫通している。

#### 【 0 1 7 6 】

なお以下の説明では、各配線層 L a 1 ~ L a 6 の面内での方向や向きについては、図 2 0 ~ 図 2 5 に座標系で示すように、同図における左右方向を X 方向、同じく上下方向を Y 方向とし、右向き / 左向きを夫々 + X / - X 方向 ( 側 ) 、上向き / 下向きを夫々 + Y / - Y 方向 ( 側 ) とする。また、斜め方向についても斜め + X - Y 方向、斜め - X - Y 方向のように表現する。なお図 7 , 図 8 等より明らかなように、液晶制御基板 9 8 を遊技機本体 1 に装着した状態では、液晶制御基板 9 8 の + X 方向が上向き、同じく + Y 方向が遊技機本体 1 に向かって右向き ( 背面視で左向き ) となる。

#### 【 0 1 7 7 】

図 2 0 に示すように、表面 9 8 a 側の第 1 配線層 ( 甲配線層 ) L a 1 には、複合チップ ( 第 1 電子部品 ) 1 0 4 が配置される複合チップ配置領域 ( 第 1 配置領域 ) 1 9 1 と、制御 R O M ( 第 2 電子部品、特定電子部品 ) 1 0 5 が配置される制御 R O M 配置領域 ( 第 2 配置領域 ) 1 9 2 とが設けられている。複合チップ配置領域 1 9 1 は、複合チップ 1 0 4 の形状に対応する略正方形で、液晶制御基板 9 8 の表面 9 8 a における中央部付近に配置されている。複合チップ配置領域 1 9 1 内には、複合チップ 1 0 4 の各端子に対応するドット状の端子接続部が略等間隔でマトリックス状に配置されている。なお複合チップ 1 0 4 は、3 2 行 3 2 列 ( 但し四隅の 4 個は欠落 ) で配列される計 1 0 2 0 個の端子を底面側に備えており、それら各端子を夫々対応する端子接続部に接続させた状態で複合チップ配置領域 1 9 1 に装着されている。

#### 【 0 1 7 8 】

制御 R O M 配置領域 1 9 2 は、制御 R O M 1 0 5 を装着する R O M ソケット 1 9 3 ( 図 8 参照 ) の形状に対応して Y 方向に長い略長方形で、その長辺の長さが複合チップ配置領域 1 9 1 の一辺の長さと同程度となっている。制御 R O M 配置領域 1 9 2 は、複合チップ配置領域 1 9 1 に対して + X 側の近傍に配置されており、制御 R O M 配置領域 1 9 2 の - X 側 , + X 側の長辺である第 1 , 第 2 縁部 1 9 2 a , 1 9 2 b のうちの第 1 縁部 1 9 2 a が、複合チップ配置領域 1 9 1 の + X 側 , - Y 側 , - X 側 , + Y 側の第 1 ~ 第 4 縁部 1 9 1 a ~ 1 9 1 d のうちの第 1 縁部 1 9 1 a に対して、 - Y 方向にずれた状態で所定距離をあいて対向している。

#### 【 0 1 7 9 】

制御 R O M 配置領域 1 9 2 には、その両長辺、即ち第 1 , 第 2 縁部 1 9 2 a , 1 9 2 b に沿って夫々複数個 ( ここでは各 3 5 個 ) の端子接続部 ( R O M 端子接続部 ) が配列され

10

20

30

40

50

ている。また制御 ROM 配置領域 192 には、制御 ROM105 を着脱可能に支持する ROM ソケット 193 が固定されており、その ROM ソケット 193 に制御 ROM105 が着脱自在に装着されている(図 8)。制御 ROM105 には、その両端部に沿って夫々複数(ここでは各 35 個)の端子が配列されており、それら各端子が、ROM ソケット 193 を介して制御 ROM 配置領域 192 の各端子接続部に接続されている。

#### 【0180】

なお ROM ソケット 193 は、図 8 に示すように、制御 ROM 配置領域 192 に対応する略長方形の底壁 193a と、その底壁 193a 上に装着された制御 ROM105 の両縁部を係脱可能に保持する一対の ROM 保持部 193b とを備えており、底壁 193a が制御 ROM 配置領域 192 の略全体を覆う状態で液晶制御基板 98 の表面 98a に固定されている。従って、第 1 配線層 La1 における制御 ROM 配置領域 192 内の配線パターン(ビア等)については、ROM ソケット 193 から制御 ROM105 を取り外した状態でも ROM ソケット 193 の底壁(遮蔽壁) 193a によって遮蔽され、外部から視認することはできない。これにより、複合チップ 104 と制御 ROM105 とを接続する配線パターンを不正改造するなどのゴト行為に対する予防性を高めることが可能となる。また、制御 ROM 配置領域 192 内に配線パターンを引くことで、それ以外の領域に配線スペースを確保することが可能となる。

#### 【0181】

また図 25 に示すように、裏面 98b 側の第 6 配線層(乙配線層) La6 には、液晶制御第 1 コネクタ CN31 が配置される第 1 コネクタ配置領域 194 と、液晶制御第 2 コネクタ CN32 が配置される第 2 コネクタ配置領域 195 とが設けられている。第 1 コネクタ配置領域 194 は、X 方向に長い略長方形で、液晶制御基板 98 の裏面 98b における +Y 側の縁部近傍に配置されている。第 1 コネクタ配置領域 194 内には、液晶制御第 1 コネクタ CN31 の各端子に対応する端子接続部が、一対の長辺に沿って夫々複数(ここでは各 70 個)配列されている。また第 2 コネクタ配置領域 195 は、X 方向に長い略長方形で、液晶制御基板 98 の裏面 98b における -Y 側の縁部近傍に配置されている。第 2 コネクタ配置領域 195 内には、液晶制御第 2 コネクタ CN32 の各端子に対応する端子接続部が、一対の長辺に沿って夫々複数(ここでは各 50 個)配列されている。

#### 【0182】

複合チップ 104 の全ての端子のうち、制御 ROM105 に接続される端子については、複合チップ配置領域 191 における制御 ROM105 側の第 1 縁部 191a の近傍に集中的に配置されている。図 26 は、複合チップ 104 の全ての端子のうち、第 1 縁部 191a 近傍及び第 2 縁部 192b 近傍の各一部の端子についてその種類(端子情報)を示している。なお、図 26 における各端子の配列は、図 20 における複合チップ配置領域 191 内の端子接続部の配列と一致させている。

#### 【0183】

図 26(a)において、HAD0 ~ HAD25 がアドレス情報を出力するためのアドレス出力端子、HDT0 ~ HDT15 がデータ情報を入出力するためのデータ入出力端子、HCS0 がチップセレクト信号を出力するためのチップセレクト出力端子、HRD がリードストローブ信号を出力するためのリードストローブ出力端子、HRESET がシステムリセット信号を入力するためのシステムリセット端子である。

#### 【0184】

また図 26(b)において、RA0+, RA0- が、第 1 伝送路 LVDS1 側の差動信号ライン RA0 に対応するデータ出力端子、RA1+, RA1- が、第 1 伝送路 LVDS1 側の差動信号ライン RA1 に対応するデータ出力端子、RA2+, RA2- が、第 1 伝送路 LVDS1 側の差動信号ライン RA2 に対応するデータ出力端子、RA3+, RA3- が、第 1 伝送路 LVDS1 側の差動信号ライン RA3 に対応するデータ出力端子、RACLK+, RACLK- が、第 1 伝送路 LVDS1 側の差動信号ライン RACLK に対応するクロック出力端子、RB0+, RB0- が、第 2 伝送路 LVDS2 側の差動信号ライン RB0 に対応するデータ出力端子、RB1+, RB1- が、第 2 伝送路 LVDS2 側の

差動信号ライン R B 1 に対応するデータ出力端子、R B 2 + , R B 2 - が、第 2 伝送路 L V D S 2 側の差動信号ライン R B 2 に対応するデータ出力端子、R B 3 + , R B 3 - が、第 2 伝送路 L V D S 2 側の差動信号ライン R B 3 に対応するデータ出力端子、R B C L K + , R B C L K - が、第 2 伝送路 L V D S 2 側の差動信号ライン R B C L K に対応するクロック出力端子である。

#### 【 0 1 8 5 】

なお以下の説明では、複合チップ配置領域 1 9 1 内の端子接続部に、対応する複合チップ 1 0 4 の端子の符号 H A D 0 ~ H A D 2 5 , H D T 0 ~ H D T 1 5 , R A 1 + , R A 1 - , R B C L K + , R B C L K - 等をそのまま用いるものとする。例えば、端子接続部 H R D は、リードストローブ出力端子 H R D に対応する端子接続部を示している。

10

#### 【 0 1 8 6 】

また図 2 7 は、制御 R O M 1 0 5 の各端子についてその種類（端子情報）を示している。図 2 7 に示す各端子のうち、A 0 ~ A 2 4 はアドレス情報を入力するためのアドレス入力端子、Q 0 ~ Q 1 5 はデータ情報を入出力するためのデータ入出力端子で、夫々複合チップ 1 0 4 のアドレス出力端子、データ入出力端子と接続される。C E # はチップセレクト信号を入力するためのチップセレクト入力端子で、複合チップ 1 0 4 のチップセレクト出力端子と接続される。W E # は書き込み可能入力端子で、電源と接続して常に H レベルとすることにより、O E # 端子の値（H / L ）に応じてモードを切り替えることが可能となっている。なお、O E # は出力可能入力端子で、複合チップ 1 0 4 のリードストローブ出力端子と接続される。

20

#### 【 0 1 8 7 】

R E S E T # はリセット端子で、複合チップ 1 0 4 のシステムリセット入力端子 H R E S E T と共に電源電圧監視用集積回路（リセット I C ）と接続される。W P # / A C C は書き込み禁止 / プログラムインプット端子で、グランド（L レベル）又は電源（H レベル）に接続することで、書き込みの禁止 / 許容、プログラムの実行禁止 / 許容を切り替えることが可能となっている。本実施形態では、W P # / A C C 端子は電源に接続され、H レベルに設定されている。B Y T E # は 8 / 1 6 b i t モード選択端子で、グランド（L レベル）又は電源（H レベル）に接続することで、8 b i t 通信モードと 1 6 b i t 通信モードとの何れかを選択することが可能となっている。

30

#### 【 0 1 8 8 】

なお以下の説明では、制御 R O M 配置領域 1 9 2 に対応する端子接続部についても、対応する制御 R O M 1 0 5 の端子の符号 A 0 ~ A 2 4 , Q 0 ~ Q 1 5 , C E # 等をそのまま用いるものとする。例えば、端子接続部 R E S E T # は、リセット端子 R E S E T # に対応する端子接続部を示している。

#### 【 0 1 8 9 】

以下、液晶制御基板 9 8 上に設けられた多数の配線路のうち、複合チップ 1 0 4 と制御 R O M 1 0 5 、液晶制御第 1 コネクタ C N 3 1 、液晶制御第 2 コネクタ C N 3 2 等を接続している複数種類の配線路 P 1 ~ P 7 1 に着目し、その詳細について図面を参照しつつ説明する。なお、図 2 8 ~ 図 3 3 は、図 2 0 ~ 図 2 5 に示す第 1 ~ 第 6 配線層 L a 1 ~ L a 6 の各配線パターンから夫々配線路 P 1 ~ P 7 1 を構成する部分のみを抽出して示したもので、図 3 4 ~ 図 4 4 はその部分拡大図である。また、図 4 5 ~ 図 5 3 は、配線路 P 1 ~ P 7 1 の配線経路を模式的に示したものである。なお、図 4 5 ~ 図 5 0 において、グレーで表示したビア（例えば図 4 5 の配線路 P 1 におけるビア v 8 6 ）は、制御 R O M 配置領域 1 9 2 内に配置されているビア（特定層間導通部）を示し、太線で表示した配線路（例えば図 4 5 の配線路 P 2 における配線路 c p 1 3 ）は、制御 R O M 1 0 5 側の端子接続部に対して制御 R O M 配置領域 1 9 2 の内側から接続されている配線路を示している。

40

#### 【 0 1 9 0 】

まず初めに、複合チップ 1 0 4 のアドレス出力端子 H A D 0 ~ H A D 2 5 に接続される配線路 P 1 ~ P 2 6 について説明する。本実施形態では、アドレス出力端子 H A D 0 ~ H A D 2 5 のうち、H A D 1 ~ H A D 2 5 については、制御 R O M 1 0 5 側のアドレス入力

50

端子 A 0 ~ A 2 4 に夫々接続されるとともに、液晶制御第 1 コネクタ C N 3 1 にも接続されている。一方、アドレス出力端子 H A D 0 については、液晶制御第 1 コネクタ C N 3 1 には接続されているが、制御 R O M 1 0 5 側の端子とは接続されていない。

#### 【 0 1 9 1 】

なお、複合チップ 1 0 4 のアドレス出力端子 H A D 1 ~ H A D 2 5 の配列（図 2 6 ( a )）と、それに対応する制御 R O M 1 0 5 のアドレス入力端子 A 0 ~ A 2 4 の配列（図 2 7 ）とを比較すると、両者は明らかに相違している。即ち、複合チップ 1 0 4 のアドレス出力端子 H A D 1 ~ H A D 2 5 は、図 2 6 ( a ) に示すように 6 行に分けて配列されており、行毎に列数は異なるが並び順は一定しているのに対し、制御 R O M 1 0 5 のアドレス入力端子 A 0 ~ A 2 4 は、図 2 7 に示すように 2 列に分けて配列されており、各列における並び順に一定の規則性はない。しかも、複合チップ 1 0 4 と制御 R O M 1 0 5 の配置位置や配線パターンの数の多さが関係してくることで、配線パターンの引き回しが非常に複雑なものとなる。そのため、複合チップ 1 0 4 と制御 R O M 1 0 5 とを接続する配線パターンの引き回しを最適化することは非常に重要であり、それによって配線パターンの線長を短くすることができ、ノイズ低減や基板全体のスリム化を図ることにつながる。また、これらは複合チップ 1 0 4 と制御 R O M 1 0 5 との間の関係だけでなく、複合チップ 1 0 4 と各種コネクタ等の電子部品との関係性においても同様のことが言える。特に、H A D 1 ~ H A D 2 5 や H D T 1 ~ H D T 2 5 などの複合チップ 1 0 4 や制御 R O M 1 0 5 、各種コネクタなどの複数の電子部品と接続される配線パターンについては、上述の課題が大きい分、最適化することによる効果も大きいものとなる。

10

#### 【 0 1 9 2 】

配線路 P 1 ~ P 2 6 のうち、配線路 P 1 ( 図 4 5 ) では、図 3 4 に示すように、第 1 配線層 L a 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 0 が、配線路 c p 0 により、斜め - X - Y 方向の近傍に配置されたビア v 0 に接続されている。ビア v 0 は、その周囲に配置されている 4 つの端子接続部（端子接続部 H A D 0 を含む）の略中央に配置されている。このビア v 0 は、図 3 7 に示すように、第 3 配線層 L a 3 に設けられた配線路 c p 1 によりビア v 4 1 と接続されている。このビア v 4 1 は、複合チップ配置領域 1 9 1 と制御 R O M 配置領域 1 9 2 との間に配置されている。そしてビア v 4 1 は、図 4 0 に示すように、第 4 配線層 L a 4 に設けられた配線路 c p 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 8 6 と接続されている。このように、第 1 配線層 L a 1 で端子接続部 H A D 0 から引き出された配線路は、2 つの配線層 L a 3 , L a 4 を経て制御 R O M 配置領域 1 9 2 内のビア v 8 6 に接続されている。

20

#### 【 0 1 9 3 】

端子接続部 H A D 0 からビア v 8 6 に達した配線路は、このビア v 8 6 で 2 つに分岐している。第 1 の分岐路は、図 3 7 , 図 3 8 に示すように、第 3 配線層 L a 3 に設けられた配線路 c p 3 により、ビア v 8 6 からテストポイント T P 2 8 を構成するビア v 2 0 5 を経て第 1 コネクタ配置領域 1 9 4 内のビア v 1 4 6 に接続され、更に図 4 2 に示すように、第 6 配線層 L a 6 に設けられた配線路 c p 4 により、端子接続部 h a d 0 に対して第 1 コネクタ配置領域 1 9 4 の内側から接続されている。また第 2 の分岐路は、図 4 1 に示すように、第 6 配線層 L a 6 に設けられた配線路 c p 5 により、ビア v 8 6 から終端抵抗 R A 1 6 に接続されている。この終端抵抗 R A 1 6 は、他端側が所定のビアを介して第 2 配線層 L a 2 のベタ配線層 ( G N D ) に接続されている（配線図では省略）。

30

#### 【 0 1 9 4 】

配線路 P 2 ( 図 4 5 ) では、図 3 4 に示すように、第 1 配線層 L a 1 の複合チップ配置領域 1 9 1 に設けられた端子接続部 H A D 1 が、配線路 c p 1 1 により、斜め - X - Y 方向の近傍に配置されたビア v 5 に接続されている。ビア v 5 は、その周囲に配置されている 4 つの端子接続部（端子接続部 H A D 1 を含む）の略中央に配置されている。このビア v 5 は、図 4 0 に示すように、第 4 配線層 L a 4 に設けられた配線路 c p 1 2 により、制御 R O M 配置領域 1 9 2 内に配置されるビア v 8 5 に接続されている。このように、端子接続部 H A D 1 から引き出された配線路は、端子接続部 H A D 0 から引き出された配線路

40

50

とは異なり、第3配線層L a 3は経由せず、第4配線層L a 4を経て制御ROM配置領域192内のビアv 8 5に接続されている。

【0195】

端子接続部HAD1からビアv 8 5に達した配線路は、このビアv 8 5で4つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路cp 1 3により、ビアv 8 5から制御ROM105の端子接続部A 0に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路cp 1 4により、ビアv 8 5から終端抵抗RA16に接続されている。

【0196】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路cp 1 5により、ビアv 8 5から第1コネクタ配置領域194内のビアv 1 4 5に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路cp 1 6により、端子接続部had1に対して第1コネクタ配置領域194の内側から接続されている。また第4の分岐路は、図37、図39に示すように、第3配線層L a 3に設けられた配線路cp 1 7により、ビアv 8 5からビアv 1 8 2に接続され、更に図43に示すように、第6配線層L a 6に設けられた配線路cp 1 8により、デコード回路を構成するデコーダIC12に接続されている。

【0197】

なお、図43等の配線図では一部省略しているが、デコーダIC12～IC14を含むデコード回路は図54に示すように構成されている。図54に示すように、デコーダIC13、IC14は、液晶IF第3コネクタCN23等を介して液晶表示手段76等に接続されており、電源投入時に、複合チップ104のデータ入出力端子HDT0～HDT15からデータ情報が入力される。そしてデコーダIC13、IC14は、デコーダIC12から入力されるCPUと同期したクロックに基づいて、液晶表示手段76等にデータ情報を出力するため、固定のデータ情報をCPUが毎回送信する必要がない。これにより、CPUから所定時間毎に同一のデータ情報を出力する必要がなく、CPUはデータ情報の内容を変更する場合にのみ新たなデータ情報を送信するようにすればよいため、制御プログラムを簡素化することが可能となる。

【0198】

配線路P3(図45)では、図34に示すように、第1配線層L a 1の複合チップ配置領域191に設けられた端子接続部HAD2が、配線路cp 2 1により、斜め+X-Y方向の近傍に配置されたビアv 4に接続されている。ビアv 4は、その周囲に配置されている4つの端子接続部(端子接続部HAD2を含む)の略中央に配置されている。このビアv 4は、図40に示すように、第4配線層L a 4に設けられた配線路cp 2 2により、制御ROM配置領域192内に配置されるビアv 8 4に接続されている。

【0199】

端子接続部HAD2からビアv 8 4に達した配線路は、このビアv 8 4で4つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路cp 2 3により、ビアv 8 4から制御ROM105の端子接続部A 1に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路cp 2 4により、ビアv 8 4から終端抵抗RA16に接続されている。

【0200】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路cp 2 5により、ビアv 8 4から第1コネクタ配置領域194内のビアv 1 4 4に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路cp 2 6により、端子接続部had2に対して第1コネクタ配置領域194の内側から接続されている。また第4の分岐路は、図37、図39に示すように、第3配線層L a 3に設けられた配線路cp 2 7により、ビアv 8 4からビアv 1 8 4に接続され、更に図43に示すように、

10

20

30

40

50

第6配線層L a 6に設けられた配線路c p 2 8により、デコード回路を構成するデコーダI C 1 2に接続されている。

#### 【0201】

配線路P 4(図45)では、図34に示すように、第1配線層L a 1の複合チップ配置領域191に設けられた端子接続部H A D 3が、配線路c p 3 1により、斜め+X-Y方向の近傍に配置されたビアv 1 3に接続されている。ビアv 1 3は、その周囲に配置されている4つの端子接続部(端子接続部H A D 3を含む)の略中央に配置されている。このビアv 1 3は、図40に示すように、第4配線層L a 4に設けられた配線路c p 3 2により、制御ROM配置領域192内に配置されるビアv 8 3に接続されている。

#### 【0202】

端子接続部H A D 3からビアv 8 3に達した配線路は、このビアv 8 3で4つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路c p 3 3により、ビアv 8 3から制御ROM105の端子接続部A 2に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路c p 3 4により、ビアv 8 3から終端抵抗R A 1 6に接続されている。

#### 【0203】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路c p 3 5により、ビアv 8 3から第1コネクタ配置領域194内のビアv 1 4 3に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路c p 3 6により、端子接続部h a d 3に対して第1コネクタ配置領域194の内側から接続されている。また第4の分岐路は、図37、図39に示すように、第3配線層L a 3に設けられた配線路c p 3 7により、ビアv 8 3からビアv 1 8 1に接続され、更に図43に示すように、第6配線層L a 6に設けられた配線路c p 3 8により、デコード回路を構成するデコーダI C 1 2に接続されている。

#### 【0204】

配線路P 5(図45)では、図34に示すように、第1配線層L a 1の複合チップ配置領域191に設けられた端子接続部H A D 4が、配線路c p 4 1により、斜め+X-Y方向の近傍に配置されたビアv 2 0に接続されている。ビアv 2 0は、その周囲に配置されている4つの端子接続部(端子接続部H A D 4を含む)の略中央に配置されている。このビアv 2 0は、図40に示すように、第4配線層L a 4に設けられた配線路c p 4 2により、制御ROM配置領域192内に配置されるビアv 8 2に接続されている。

#### 【0205】

端子接続部H A D 4からビアv 8 2に達した配線路は、このビアv 8 2で3つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路c p 4 3により、ビアv 8 2から制御ROM105の端子接続部A 3に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路c p 4 4により、ビアv 8 2から終端抵抗R A 1 5に接続されている。この終端抵抗R A 1 5は、他端側が所定のビアを介して第2配線層L a 2のベタ配線層(G N D)に接続されている(配線図では省略)。

#### 【0206】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路c p 4 5により、ビアv 8 2から第1コネクタ配置領域194内のビアv 1 4 2に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路c p 4 6により、端子接続部h a d 4に対して第1コネクタ配置領域194の内側から接続されている。

#### 【0207】

配線路P 6(図45)では、図34に示すように、第1配線層L a 1の複合チップ配置領域191に設けられた端子接続部H A D 5が、配線路c p 5 1により、複合チップ配置領域191の外側、具体的には複合チップ配置領域191と制御ROM配置領域192との間に配置されたビアv 3 4に接続されている。なお、端子接続部H A D 5は、複合チッ

10

20

30

40

50

配置領域 191 の外周側から 2 列目に配置されている。ビア v34 は、図 40 に示すように、第 4 配線層 La4 に設けられた配線路 cp52 により、制御 ROM 配置領域 192 内に配置されるビア v81 に接続されている。

#### 【0208】

端子接続部 HAD5 からビア v81 に達した配線路は、このビア v81 で 3 つに分岐している。第 1 の分岐路は、図 35 に示すように、第 1 配線層 La1 に設けられた配線路 cp53 により、ビア v81 から制御 ROM105 の端子接続部 A4 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 41 に示すように、第 6 配線層 La6 に設けられた配線路 cp54 により、ビア v81 から終端抵抗 RA15 に接続されている。

10

#### 【0209】

また第 3 の分岐路は、図 37, 図 38 に示すように、第 3 配線層 La3 に設けられた配線路 cp55 により、ビア v81 から第 1 コネクタ配置領域 194 内のビア v141 に接続され、更に図 42 に示すように、第 6 配線層 La6 に設けられた配線路 cp56 により、端子接続部 had5 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

#### 【0210】

配線路 P7 (図 45) では、図 34 に示すように、第 1 配線層 La1 の複合チップ配置領域 191 に設けられた端子接続部 HAD6 が、配線路 cp61 により、複合チップ配置領域 191 の外側、具体的には複合チップ配置領域 191 と制御 ROM 配置領域 192 との間に配置されたビア v39 に接続されている。なお、端子接続部 HAD6 は、複合チップ配置領域 191 の最も外周側に配置されている。ビア v39 は、図 40 に示すように、第 4 配線層 La4 に設けられた配線路 cp62 により、制御 ROM 配置領域 192 内に配置されるビア v80 に接続されている。

20

#### 【0211】

端子接続部 HAD6 からビア v80 に達した配線路は、このビア v80 で 3 つに分岐している。第 1 の分岐路は、図 35 に示すように、第 1 配線層 La1 に設けられた配線路 cp63 により、ビア v80 から制御 ROM105 の端子接続部 A5 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 41 に示すように、第 6 配線層 La6 に設けられた配線路 cp64 により、ビア v80 から終端抵抗 RA15 に接続されている。

30

#### 【0212】

また第 3 の分岐路は、図 37, 図 38 に示すように、第 3 配線層 La3 に設けられた配線路 cp65 により、ビア v80 から第 1 コネクタ配置領域 194 内のビア v140 に接続され、更に図 42 に示すように、第 6 配線層 La6 に設けられた配線路 cp66 により、端子接続部 had6 に対して第 1 コネクタ配置領域 194 の内側から接続されている。

#### 【0213】

配線路 P8 (図 45) では、図 34 に示すように、第 1 配線層 La1 の複合チップ配置領域 191 に設けられた端子接続部 HAD7 が、配線路 cp71 により、斜め + X - Y 方向の近傍に配置されたビア v3 に接続されている。ビア v3 は、その周囲に配置されている 4 つの端子接続部 (端子接続部 HAD7 を含む) の略中央に配置されている。このビア v3 は、図 40 に示すように、第 4 配線層 La4 に設けられた配線路 cp72 により、制御 ROM 配置領域 192 内に配置されるビア v79 に接続されている。

40

#### 【0214】

端子接続部 HAD7 からビア v79 に達した配線路は、このビア v79 で 3 つに分岐している。第 1 の分岐路は、図 35 に示すように、第 1 配線層 La1 に設けられた配線路 cp73 により、ビア v79 から制御 ROM105 の端子接続部 A6 に対して制御 ROM 配置領域 192 の内側から接続されている。また第 2 の分岐路は、図 41 に示すように、第 6 配線層 La6 に設けられた配線路 cp74 により、ビア v79 から終端抵抗 RA15 に接続されている。

#### 【0215】

50

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路c p 7 5により、ビアv 7 9から第1コネクタ配置領域1 9 4内のビアv 1 3 9に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路c p 7 6により、端子接続部h a d 7に対して第1コネクタ配置領域1 9 4の内側から接続されている。

#### 【0216】

配線路P 9(図46)では、図34に示すように、第1配線層L a 1の複合チップ配置領域1 9 1に設けられた端子接続部H A D 8が、配線路c p 8 1により、斜め+X-Y方向の近傍に配置されたビアv 1 2に接続されている。ビアv 1 2は、その周囲に配置されている4つの端子接続部(端子接続部H A D 8を含む)の略中央に配置されている。このビアv 1 2は、図40に示すように、第4配線層L a 4に設けられた配線路c p 8 2により、制御ROM配置領域1 9 2内に配置されるビアv 7 8に接続されている。

10

#### 【0217】

端子接続部H A D 8からビアv 7 8に達した配線路は、このビアv 7 8で3つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路c p 8 3により、ビアv 7 8から制御ROM1 0 5の端子接続部A 7に対して制御ROM配置領域1 9 2の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路c p 8 4により、ビアv 7 8から終端抵抗R A 1 3に接続されている。この終端抵抗R A 1 3は、他端側が所定のビアを介して第2配線層L a 2のベタ配線層(GND)に接続されている(配線図では省略)。

20

#### 【0218】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路c p 8 5により、ビアv 7 8から第1コネクタ配置領域1 9 4内のビアv 1 3 8に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路c p 8 6により、端子接続部h a d 8に対して第1コネクタ配置領域1 9 4の内側から接続されている。

#### 【0219】

配線路P 1 0(図46)では、図34に示すように、第1配線層L a 1の複合チップ配置領域1 9 1に設けられた端子接続部H A D 9が、配線路c p 9 1により、複合チップ配置領域1 9 1の外側、具体的には複合チップ配置領域1 9 1と制御ROM配置領域1 9 2との間に配置されたビアv 3 3に接続されている。なお、端子接続部H A D 9は、複合チップ配置領域1 9 1の外周側から2列目に配置されている。ビアv 3 3は、図40に示すように、第4配線層L a 4に設けられた配線路c p 9 2により、制御ROM配置領域1 9 2内に配置されるビアv 7 7に接続されている。

30

#### 【0220】

端子接続部H A D 9からビアv 7 7に達した配線路は、このビアv 7 7で3つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路c p 9 3により、ビアv 7 7から制御ROM1 0 5の端子接続部A 8に対して制御ROM配置領域1 9 2の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路c p 9 4により、ビアv 7 7から終端抵抗R A 1 3に接続されている。

40

#### 【0221】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路c p 9 5により、ビアv 7 7から第1コネクタ配置領域1 9 4内のビアv 1 3 7に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路c p 9 6により、端子接続部h a d 9に対して第1コネクタ配置領域1 9 4の内側から接続されている。

#### 【0222】

配線路P 1 1(図46)では、図34に示すように、第1配線層L a 1の複合チップ配置領域1 9 1に設けられた端子接続部H A D 1 0が、配線路c p 1 0 1により、複合チップ配置領域1 9 1の外側、具体的には複合チップ配置領域1 9 1と制御ROM配置領域1 9 2との間に配置されたビアv 3 8に接続されている。なお、端子接続部H A D 1 0は、複合チップ配置領域1 9 1の最も外周側に配置されている。ビアv 3 8は、図40に示す

50

ように、第4配線層L a 4に設けられた配線路c p 1 0 2により、制御ROM配置領域192内に配置されるビアv 7 6に接続されている。

#### 【0223】

端子接続部HAD10からビアv 7 6に達した配線路は、このビアv 7 6で3つに分岐している。第1の分岐路は、図35に示すように、第1配線層L a 1に設けられた配線路c p 1 0 3により、ビアv 7 6から制御ROM105の端子接続部A 9に対して制御ROM配置領域192の内側から接続されている。また第2の分岐路は、図41に示すように、第6配線層L a 6に設けられた配線路c p 1 0 4により、ビアv 7 6から終端抵抗RA13に接続されている。

#### 【0224】

また第3の分岐路は、図37、図38に示すように、第3配線層L a 3に設けられた配線路c p 1 0 5により、ビアv 7 6から第1コネクタ配置領域194内のビアv 1 3 6に接続され、更に図42に示すように、第6配線層L a 6に設けられた配線路c p 1 0 6により、端子接続部had10に対して第1コネクタ配置領域194の内側から接続されている。

#### 【0225】

配線路P12(図46)では、図34に示すように、第1配線層L a 1の複合チップ配置領域191に設けられた端子接続部HAD11が、配線路c p 1 1 1により、斜め-X+Y方向の近傍に配置されたビアv 2に接続されている。ビアv 2は、その周囲に配置されている4つの端子接続部(端子接続部HAD11を含む)の略中央に配置されている。このビアv 2は、図40に示すように、第4配線層L a 4に設けられた配線路c p 1 1 2により、制御ROM配置領域192内に配置されるビアv 7 5に接続されている。

#### 【0226】