## (19) World Intellectual Property Organization International Bureau

## (43) International Publication Date 24 December 2003 (24.12.2003)

## **PCT**

# (10) International Publication Number WO 03/107570 A1

(51) International Patent Classification<sup>7</sup>: H04J 3/02, H04N 7/173, H03H 7/30

(21) International Application Number: PCT/US03/18416

(22) International Filing Date: 11 June 2003 (11.06.2003)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

10/172,035 13 June 2002 (13.06.2002) US

- (71) Applicant: TERAYON COMMUNICATION SYSTEMS, INC. [US/US]; 4988 Great America Parkway, Santa Clara, CA 95054 (US).

- (72) Inventors: YEHUDA, Azenkot; 1128 Little Oak Circle, San José, CA 95129 (US). SELIM, Shlomo, Rakib; 10271 West Acres, Cupertino, CA 95014 (US).

- (74) Agent: FISH, Ronald, Craig; Ronald Craig Fish, a Law Corporation, P.O. Box 2258, Morgan Hill, CA 95038 (US).

- (81) Designated States (national): CA, CN, JP, KR.

- (84) Designated States (regional): European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, RO, SE, SI, SK, TR).

#### Published:

- with international search report

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: MULTICHANNEL, MULTIMODE DOCSIS HEADEND RECEIVER

(57) Abstract: A multichannel, mixed mode cable modem termination system receiver capable of receiving multiple channels of digital data on one or more hybrid fiber coaxial cable (HFC) systems, each of the channels being either single mode or mixed-mode. Mixed mode channels are time division multiplexed and have overlapping bandwidth and each subchannel of a mixed mode channel can have a different center frequency, symbol rate and/or multiplexing type. The receiver is comprised of a plurality of analog front end receivers (18, 20, 21, 23) coupled to various HFC systems (10, 12, 14, 16), each selectively coupled to any one of a plurality of digital frond end receivers (22, 24, 26, 28). Control Circuitry (50) controls these circuits to receive multiple mixed-mode or single mode channels, simultaneously if necessary. An arbiter (48) decides which bursts get processed first in a back end shared demodulator (52) which recovers the data from each burst. The preferred shared demodulator includes an equalizer, predictor and rotational amplifier which processes both TDMA and SCDMA data bursts post despreader to reduce reception data errors.

VO 03/107570 A1

#### MULTICHANNEL, MULTIMODE DOCSIS HEADEND RECEIVER

#### Field of use

The invention finds use in the digital data receivers of cable modem termination systems (hereafter CMTS) of DOCSIS enabled cable television distribution systems. The DOCSIS 1.0 systems used time division multiplexed (hereafter TDMA) bursts only. However, the desire for higher speeds for transmission of digital data led to the development of DOCSIS 1.1 systems which  $\square$  were also TDMA systems but faster.

Upstream noise is a major problem in any system where digital data is transmitted

10 upstream over a cable television hybrid fiber coaxial (hereafter HFC) cable distribution

system to a cable modern termination system (hereafter CMTS). Privacy can also be a

problem with TDMA bursts. One way of overcoming these noise problems and insuring

privacy is to use code division multiplexing (hereafter CDMA) for upstream bursts. The code

gain of CDMA systems helps overcome the noise and the spread spectrum nature of the

15 signal prevents evesdropping by those without access to the spreading codes used in the

transmitters. Terayon Communication Systems, Inc. of Santa Clara, California has been a

leader in bringing spread spectrum cable modems to the market. Terayon's modems enjoy a

further noise advantage because they use sychronous code division multiplexing (hereafter

SCDMA) to cut down on intersymbol interference. SCDMA requires all remote modems to

20 perform a ranging process to determine a delay which is proper for their distance from the

CMTS such that frames of spread spectrum data transmitted from the remote modems all

arrive at the CMTS with their frame boundaries aligned in time. This minimizes intersymbol

interference caused by transmissions from other modems.

DOCSIS cable modem termination system receivers are under development by

Terayon which are capable of receiving both TDMA and SCDMA bursts on different channels as well as both TDMA and SCDMA bursts in separate time intervals (with different MAP messages applying to each) on the same frequency channel. DOCSIS defines a subchannels as bursts with frequencies and symbol rates such that there is overlapping bandwidth. Sub-channel bursts cannot be transmitted with overlap in time. Different type bursts with different multiplexing and/or different symbol rates can be transmitted during different time intervals on the same carrier, and because there is overlapping bandwidth, each interval would be a sub-channel. The term sub-channel, as it is used herein means bursts transmitted on the same or different frequencies with symbol rates and center frequencies of the RF carrier on which they are transmitted such that there is an overlap in the bandwidth, but multiplexed in time such that there is no overlap in time. Channels or frequency channel, as the terms are used herein means transmissions on carriers of different frequencies and at symbol rates such that there is no overlap in bandwidth.

Because there is no overlap in bandwidth, transmissions on different channels may overlap in time.

A prior art receiver that could not receive two sub-channels or channels at different center frequencies referred to as the Jasper I was developed by the assignee of the present invention and is currently on sale. A United States patent application serial number 09/792,815 filed by the assignee of the present invention on February 23, 2001 describes circuitry of Jasper I, and that patent application is hereby incorporated by reference. The receiver of the above identified patent application is capable of receiving 15 different SCDMA and TDMA burst types by adjusting the operation of its circuitry using burst parameter data that define the burst to be received. The differences in the various burst types relate to the symbol rate, type of multiplexing, type of modulation, function of the burst such as initial ranging or periodic station maintenance or data, etc.

When deploying new cable modems (hereafter CMs) capable of higher speed TDMA transmissions and high speed SCDMA bursts into a system with existing slower DOCSIS 1.0 or DOCSIS 1.1 modems, there arises a backward compatibility problem. Cable operators devote a certain portion of the bandwidth of the HFC to upstream digital data transmissions and there is no other available bandwidth upon which the higher speed TDMA or SCDMA upstream bursts can be transmitted. The bandwidth of a channel is related to its symbol rate. The symbol rate of DOCSIS 1.0 and 1.1 modems is slower (1.28 or 2.56 Msps) than the new advanced PHY TDMA and SCDMA modems (5.12 Msps), so the new modem channels have wider bandwidth when transmitting at the faster symbol rates. Thus, it is frequently necessary for wide-bandwidth, high-speed TDMA and SCDMA advanced PHY channels to overlap in bandwidth with lower-speed, more narrow bandwidth channels on which the older DOCSIS 1.0 and 1.1 modems transmit. This is because of the bandwidth and frequency band limit restrictions on upstream transmissions imposed on digital data delivery services by the cable operators.

The Jasper I receiver chip cannot receive mixed mode signals, *i.e.*, two different sub-channels at different symbol rates and/or different multiplexing types which have overlapping bandwidth and the same center frequency. Further, it could not receive two different sub-channels having overlapping bandwidth and different center frequencies. The Jasper I receiver also cannot receive different channels at different RF center frequencies. Further, the Jasper I receiver was capable of receiving bursts at a maximum of 5.12 Msps, so when it was receiving DOCSIS 1.0 or 1.1 bursts at 1.28 or 2.56 Msps, the digital circuitry was idle most of the time.

Therefore, there is a need for a receiver that can receive bursts on multiple different RF inputs to keep the shared back end digital circuitry busy all the time. Further, there is a need for a CMTS receiver that can receive, on each RF input, mixed mode transmissions,

35

that is having multiple sub-channels with overlapping bandwidth and either the same or different center frequencies. The receiver should be able to receive sub-channels of any type on the same frequency channel such as DOCSIS 1.0, Advanced PHY TDMA or advanced PHY SCDMA, and the different sub-channels may have different symbol rates.

5 The receiver should be able to receive different sub-channels having overlapping bandwidth and the same center frequency or different center frequencies. Further, the receiver should be able to receive, multiple different channels without overlapping bandwidth and having the same or different symbol rates and/or multiplexing types and different center frequencies which are spread far enough apart given the symbol rate that there is no overlap in 10 bandwidth. For example, there is a need for a receiver that can receive a single advanced PHY SCDMA channel having a symbol rate of 5.12 megasymbols per second (Msps) and a center frequency of F1 transmitted with its bandwidth overlapping the bandwidths of multiple separate other channels of DOCSIS 1.0 bursts having symbol rates of 1.28 Msps or 2.56 Msps and center frequencies on both sides of F1 and spaced apart so that the DOCSIS 15 1.0 channel bandwidths do not overlap each other. The receiver must be able to receive a different UCD message for each sub-channel type and switch between sub-channels on

Channels with overlapping bandwidth and different burst types are typically multiplexed in time so that two different burst types with overlapping bandwidth are not 20 transmitted at the same time, but there is also a need for a receiver that can simultaneously receive two or more sub-channels with overlapping bandwidth and overlapping in time. To receive overlapping bandwidth bursts of different types which are time division multiplexed, the circuitry of the needed CMTS receiver has to be adjusted using burst parameter data that defines the burst to be received during any particular time on a sub-channel or channel.

25

the fly during a guardtime between bursts on different sub-channels or different channels.

The Jasper I receiver could only receive one channel of RF signals at a time, i.e., it only had one RF input which could only be coupled to one physical transmission medium. Thus, if a headend cable modem termination system (CMTS) were coupled to four different HFC systems, four different Jasper I CMTS receivers would have to be used with attendant multiplication of space consumed and cost. Frequently, CMTS headend apparatus are 30 coupled to multiple HFC systems, each serving different groups of customers in different areas. Typically, each CMTS system has a mixture of older DOCSIS 1.0 and 1.1 type cable modems (CM) and newer advanced PHY TDMA and SCDMA CMs. Further, rack space and floor space is limited so footprint size of the CMTS equipment is an important consideration. Typically, cable operators have to buy the CMTS receiver equipment as well as thousands 35 of CMs to serve their customers that want broadband digital data services delivered over their cable TV system. Thus, expense of the CMTS system is an important factor to commercial success because costs will be passed along to customers.

Thus, there is also a need for a CMTS receiver which has multiple RF inputs for connection to multiple HFC systems and which is capable of receiving the different burst types which can be transmitted in a DOCSIS system with a mixed bag of DOCSIS 1.0 and 1.1 CMs plus advanced PHY ATDMA and SCDMA CMs. Such a receiver must be able to receive upstream digital data transmissions at each of these multiple RF inputs which have different multiplexing and/or different symbol rates. Further, the circuitry coupled to each RF input must be able to receive different sub-channels on the same frequency channel with some bursts on some sub-channels being DOCSIS 1.0 or 1.1 TDMA and other bursts on different sub-channels being advanced PHY TDMA or SCDMA (referred to herein as mixed mode)

with different symbol rates. Such a receiver must also be frequency agile on each of its RF inputs so as to be able to receive different frequency channels having different center frequencies without overlapping bandwidth.

### Summary of the Invention

20

25

30

The genus of the invention is defined by a central receiver for a distributed system of digital data transceivers which have the following characteristics that provide multichannel, mixed mode reception capability:

a plurality of channel receivers, each capable of receiving mixed mode upstream bursts in different sub-channels that have overlapping bandwidth but which are multiplexed in time, where each subchannel burst may have a different symbol rate, different RF frequency, different multiplexing type and different Synchronous Code Division Multiple Access (hereafter SCDMA) frame size;

a shared back end circuit for recovering the data from each burst, making measurements and calculations on at least some bursts transmitted by each cable modem which are sent down to the cable modem which sent said burst which are useful in establishing at least frame boundary and minislot boundary synchronization and upstream equalization;

an arbiter coupled to receive the data output by each said channel receiver and structured to supply received data to said shared back end circuit such that said shared back end circuit is shared so as to process all data from all said channel receivers at different times;

control circuitry for controlling at least said plurality of channel receivers and said shared back end circuit to provide multichannel, mixed-mode reception of digital data.

"Multichannel" refers to the capability to receive multiple channels simultaneously on different channel receivers. If the different channel receivers are coupled to different distributed systems such as different Hybrid Fiber Coaxial cable (HFC) distribution systems, the different channel can have overlapping bandwidth. However, if the different channel

receivers are coupled to the same HFC system, the different channels being received simultaneously cannot have overlapping bandwidth. "Mixed-mode" refers to the reception of different types of bursts on the same general channel, i.e., with overlapping bandwidth, but multiplexed in time. In other words, a single RF carrier is divided into an interval during which a burst of a first symbol rate and first multiplexing type is modulated on the carrier, and one or more other intervals when bursts having different symbol rates or multiplexing types are modulated onto the carrier. "Mixed-mode" also refers to the overlapping in bandwidth but not overlapping in time transmission of multiple subchannels on different carriers having different center frequencies which are not so different as to preclude overlapping

Although multiple channels can be received, and each channel can be mixed-mode, the total throughput through the backend circuit is limited to that circuit's capabilities, which, in the preferred embodiment, is 5.12 megasymbols per second. The advantage of the multiple front end receivers is that the backend circuit can be fully utilized as compared to the prior art wherein a single front end receiver circuit fed the back end circuit. Thus, if the burst being received had a symbol rate of less than 5.12 megasymbols per second, the full capability of the backend circuit was not used.

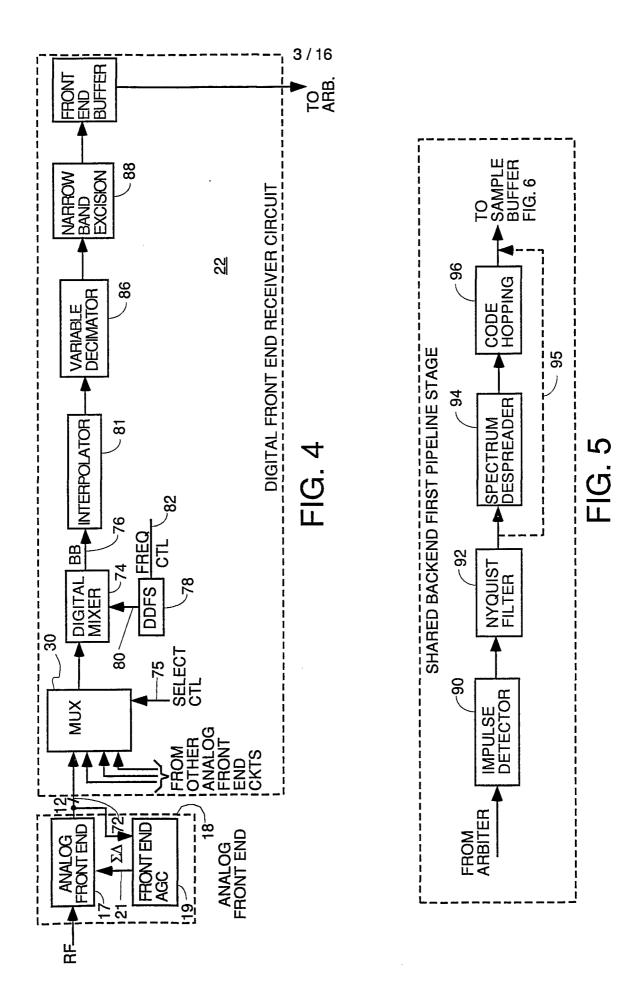

The analog front end circuits do wide band sampling. The digital front end receivers are controlled to connect to the right analog front end circuit, mix the samples of each 20 subchannel down to baseband using the correct local oscillator signal frequency. The samples are then resampled at the proper symbol rate, decimated down to a predetermined number of samples per symbol, typically two, and narrow band noise is excised. A shared back end demodulator detects impulse noise and marks symbols corrupted therewith with erasure bits, despreads the spectrum of SCDMA bursts, recovers the symbol clock and 25 makes start of burst measurements in support of ranging. The preamble of each burst is processed to develop phase and amplitude error correction factors and upstream equalization coefficients. The data symbols are then decoded in the appropriate type of decoder such as a Viterbi decoder for TCM bursts and the Reed-Solomon code words are reassembled and error corrected and the payload data is output. The erasure bits written 30 by the impulse detector are used to prevent corrupted symbols from being used by the tracking loops for symbol clock recovery or error correction factor development or equalization tap coefficient updating. A SOVA Viterbi decoder in the preferred embodiment uses erasure indications to control the branch metric values in the decoding process, and outputs erasure indications which are used to increase the range of error detection and 35 correction of the Reed-Solomon decoding circuitry.

## **Brief Description of the Drawings**

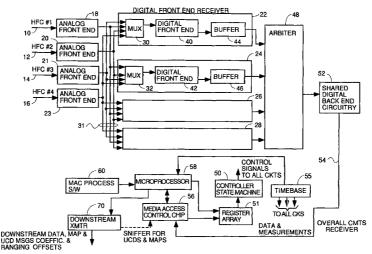

Figure 1 is a block diagram of the overall CMTS receiver system.

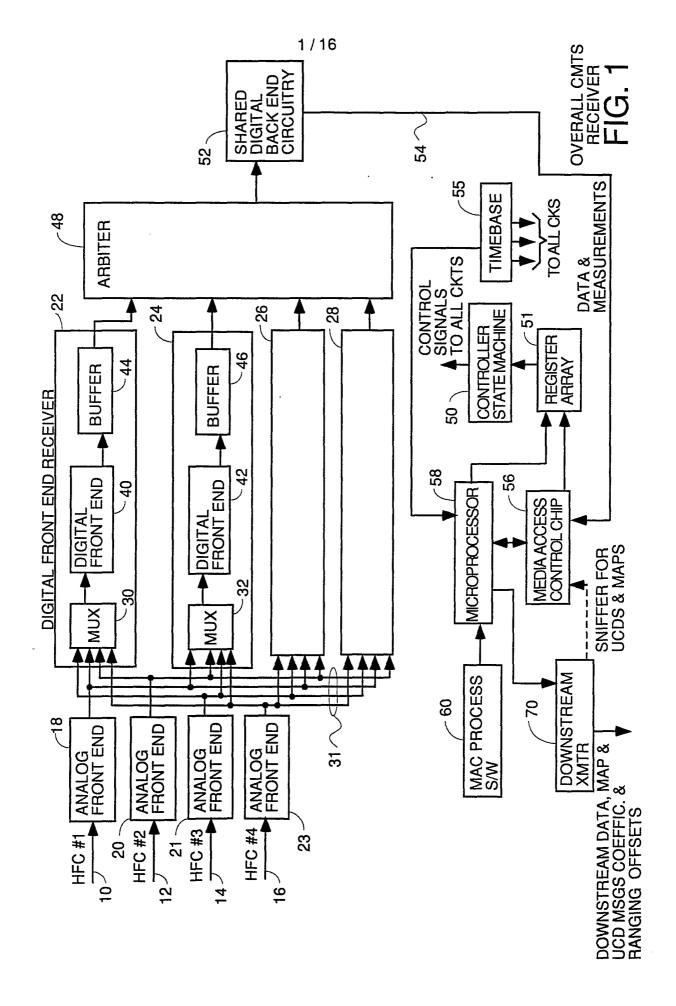

Figure 2 is a block diagram of the circuitry in each analog front end.

Figure 3A illustrates how different sub-channels with different multiplexing or symbol rates can share the same bandwidth on the same HFC system without collisions.

Figure 3B is an illustration of the time division multiplexing of two sub-channels at two different symbol rates and two different RF frequencies can be sent on the same HFC system and share the same bandwidth by time multiplexing.

Figure 3C is an illustration of how four different DOCSIS 1.0 sub-channels at 1.28 Msps symbol rates can share the same bandwidth with a single advanced PHY channel at 5.12 Msps on the same HFC system using time division multiplexing.

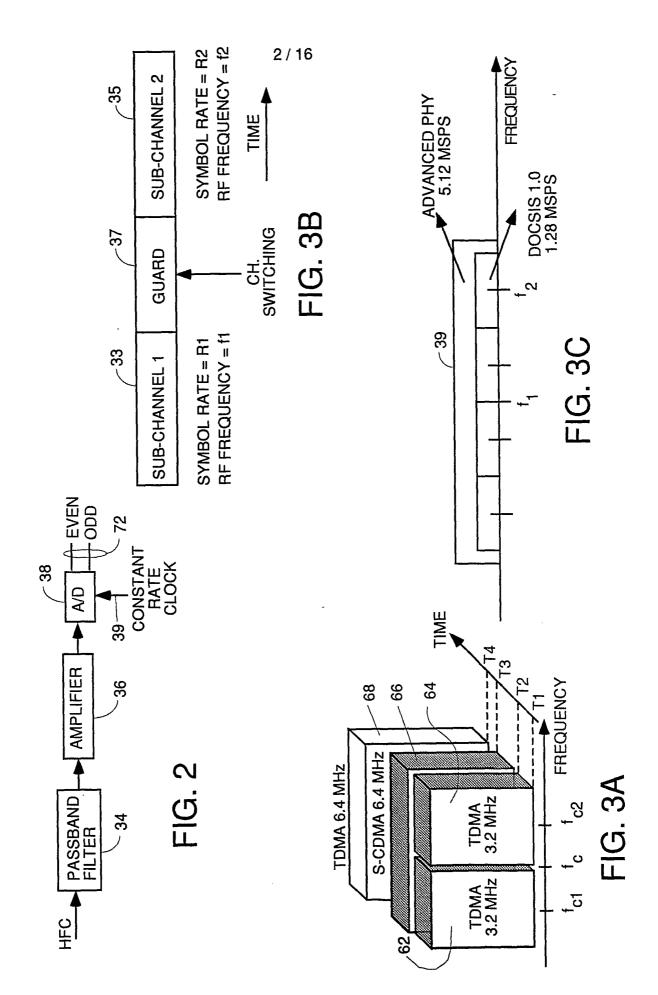

Figure 4 is a more detailed block diagram of the circuitry of each digital front end receiver.

10

30

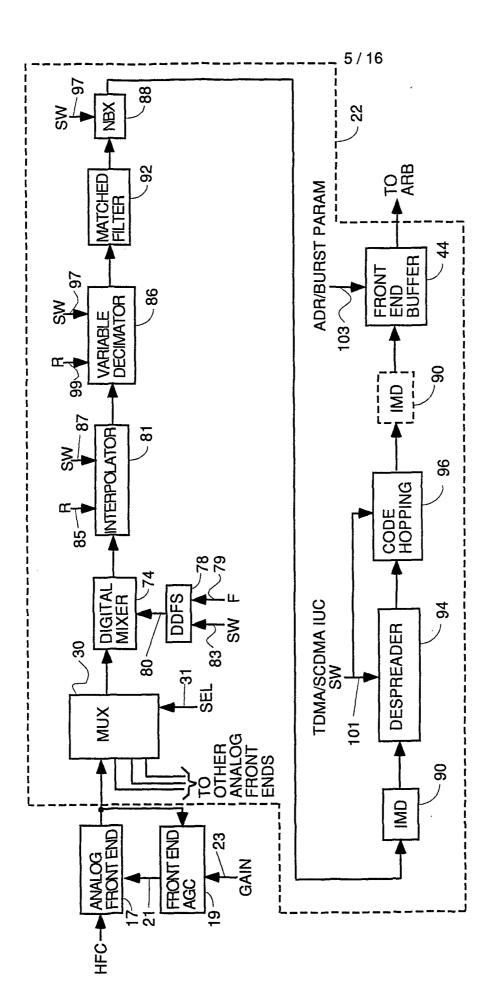

Figure 5 is a more detailed block diagram of the initial circuitry in the back end burst processing circuit 52 in Figure 1.

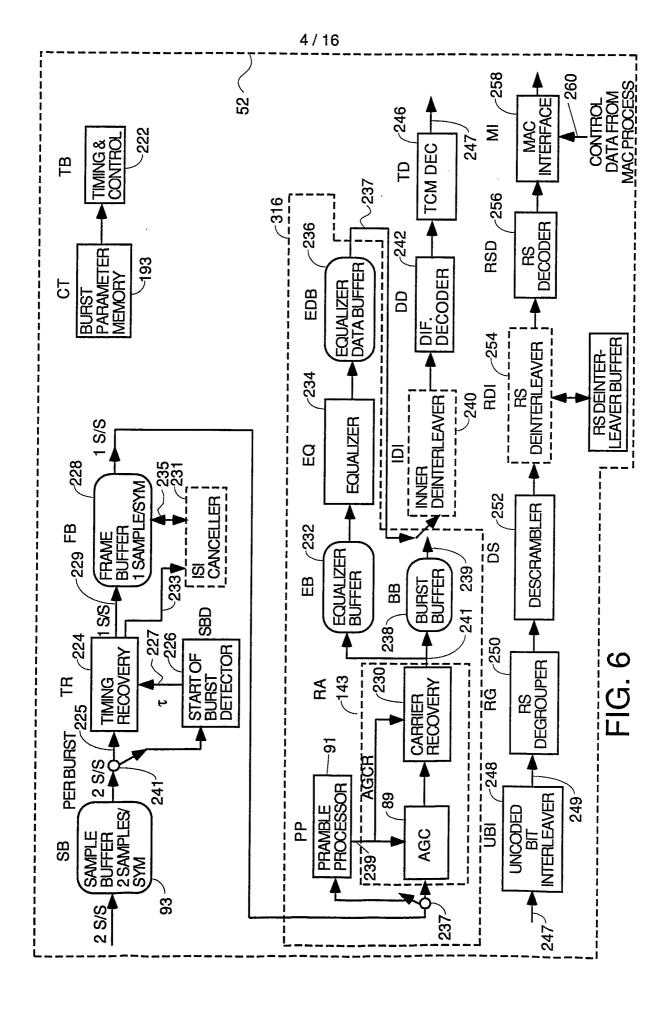

Figure 6 is a block diagram of the remainder of the back end burst processing circuitry 52 in Figure 1.

Figure 7 is a block diagram for the preferred embodiment for a digital front end circuit 22 having an impulse detector, matched filter, despreader and code hopping circuit all included.

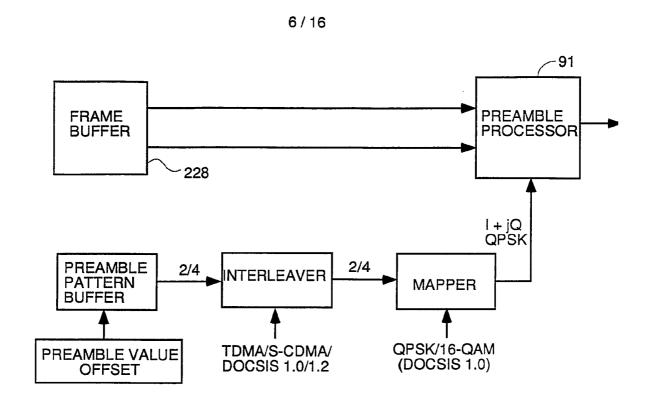

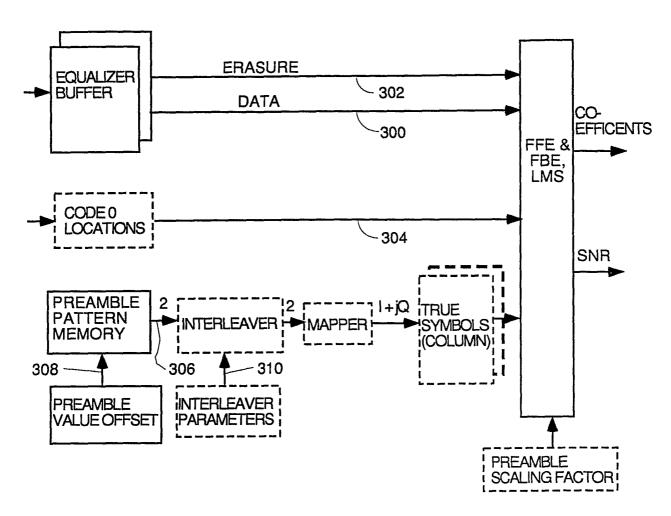

Figure 8 is a more detailed block diagram of the connection to the preamble 20 processor 91 in Figure 6.

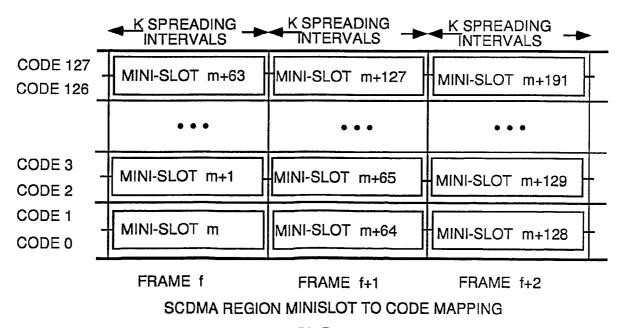

Figure 9 is a diagram of the mapping of minislots to spreading codes.

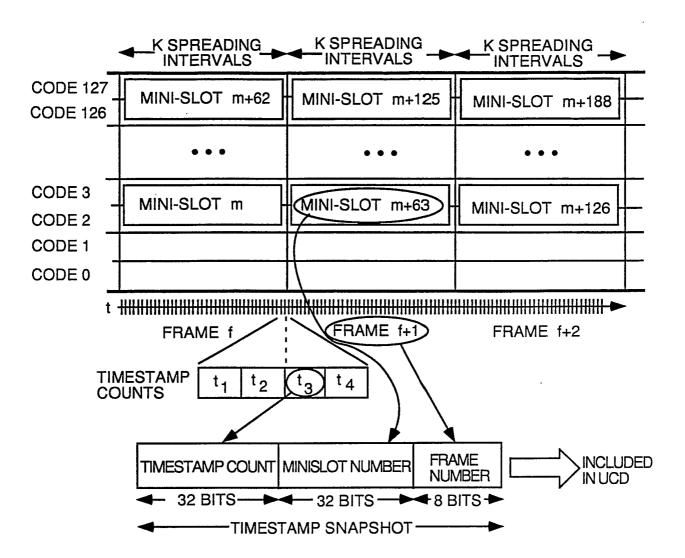

Figure 10 is a diagram of how the timestamp snapshot is composed from the timestamp counter count on a minislot boundary, the frame number and the minislot number for inclusion in the UCD message to keep the CMs frame synchronized.

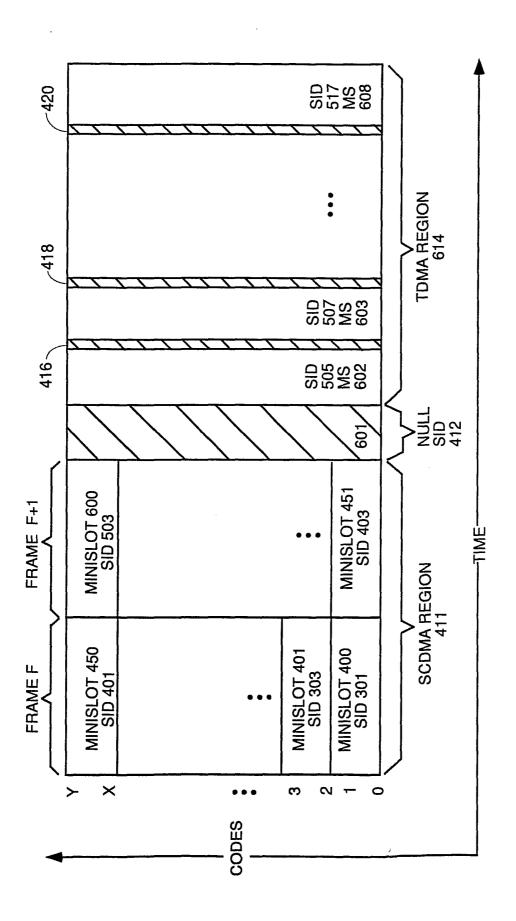

25 Figure 11 is a diagram of a MAP which has both SCDMA and TDMA regions and uses null SIDs to create a guardband between them.

Figure 12 is a more detailed diagram of the connections of the equalizer.

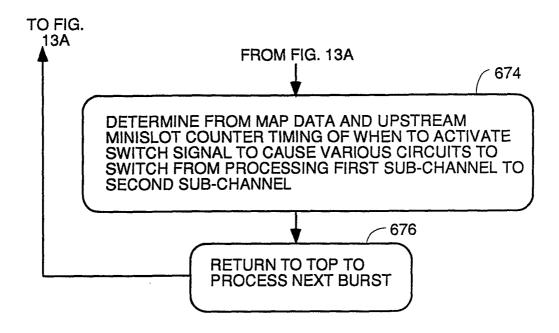

Figures 13A and 13B are a flowchart of one MAC control process to control a channel receiver to receive one channel which may or may not be mixed mode.

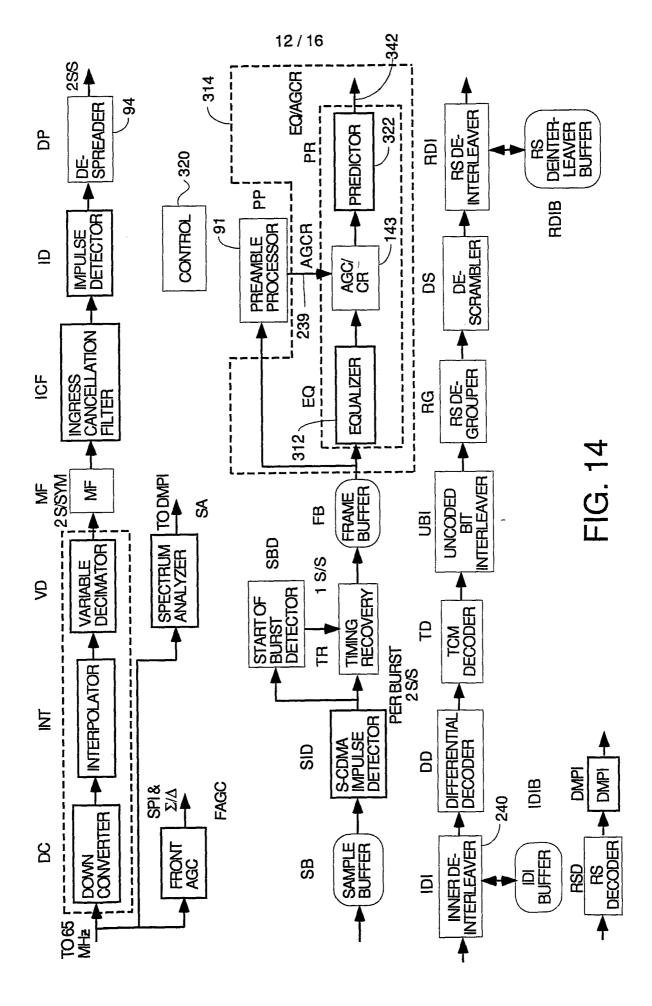

Figure 14 is a block diagram of a preferred embodiment for the front end and back end circuitry including an equalizer and predictor which are used not only to develop equalization coefficients but also to filter data bursts.

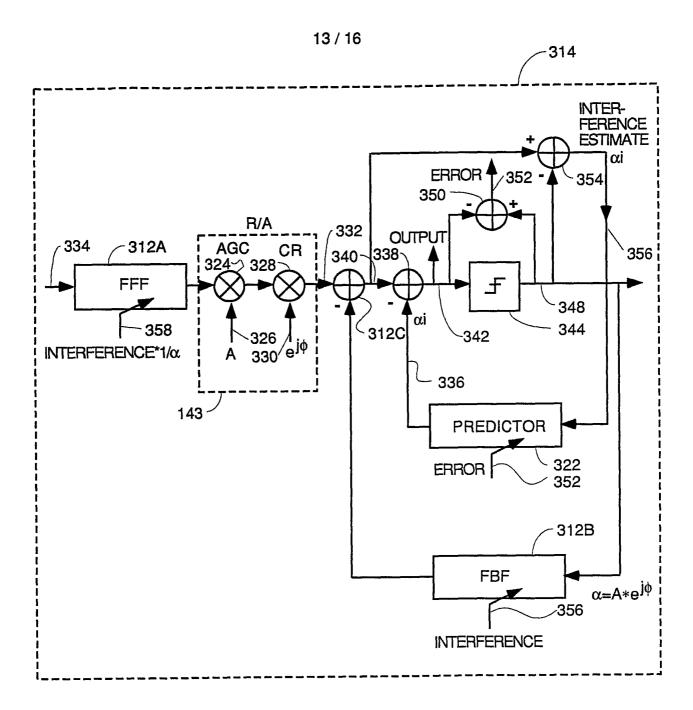

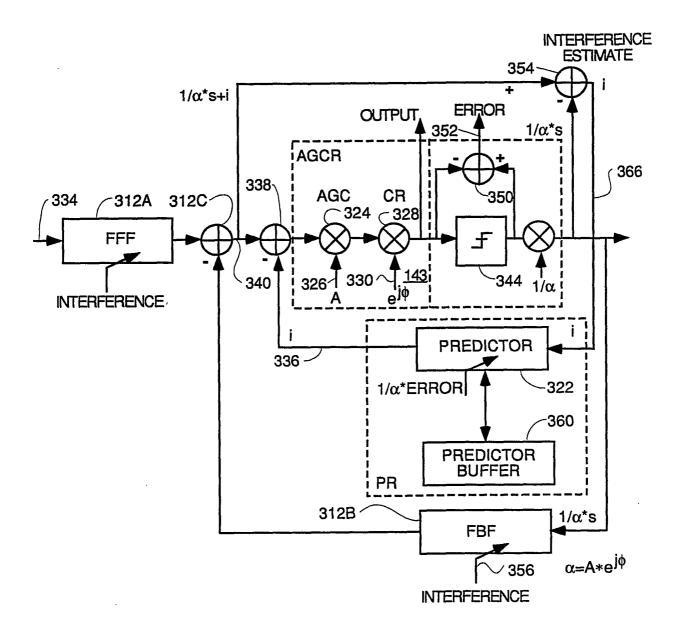

Figure 15 is a block diagram of an equalizer, predictor, rotational amplifier and preamble processor circuitry within dashed line 314 in Figure 14 which is useful for filtering TDMA and SCDMA spreader-off bursts.

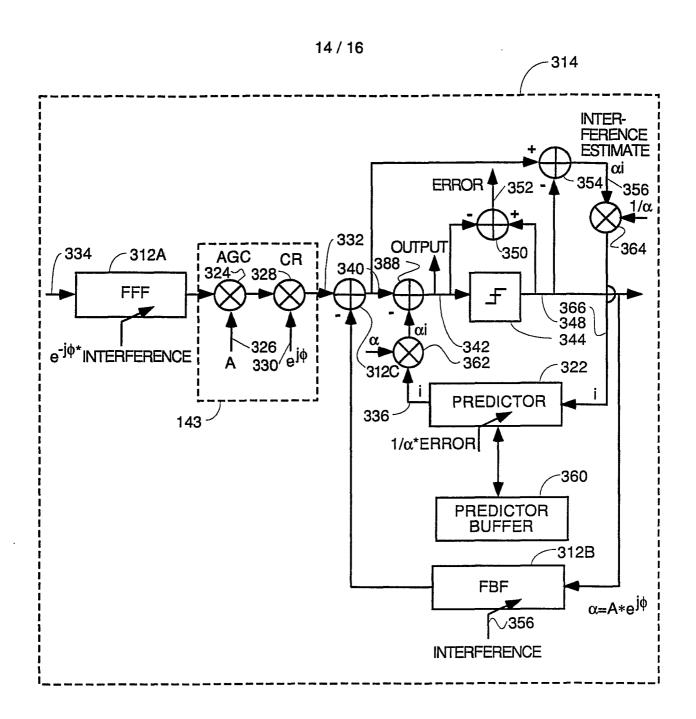

Figure 16 is a block diagram of an equalizer, predictor, rotational amplifier and preamble processor circuitry within dashed line 314 in Figure 14 which is useful for filtering SCDMA spreader-on bursts.

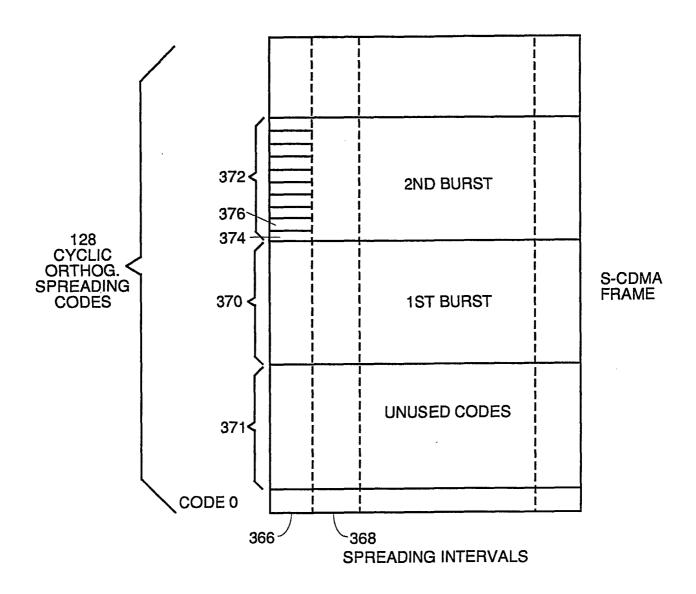

Figure 17 is a diagram of an SCDMA frame used to illustrate how control of the circuit of Figures 16 and 18 is implemented to process SCDMA bursts.

Figure 18 is a block diagram of the preferred form of an equalizer, predictor, rotational amplifier and preamble processor circuitry within dashed line 314 in Figure 14 which is useful for filtering SCDMA spreader-on bursts.

#### Detailed Description of the Preferred and Alternative Embodiments

Figure 1 is a block diagram of an overall CMTS receiver system that implements 10 multichannel, mixed-mode digital data reception of a plurality of upstream channels received from a plurality of different HFC cable systems according to the teachings of the invention. Overall, in the preferred embodiment, the receiver has four different radio frequency front end sections coupled by an arbitrator 48 to a shared digital back end demodulator circuit 52 15 which has a maximum throughput of 5.12 megasymbols per second (Msps). The first front end section is comprised of analog front end circuitry 18 and digital front end circuitry 22. The combination of the analog front end 18 and the digital front end 22 is one "channel receiver". Each channel receiver described herein can receive bursts having different symbol rates, transmitted on a carrier of a different RF frequency and having a different 20 SCDMA frame size. Each receiver channel can receive "mixed mode" wherein two or more sub-channels comprised of different time division multiplexed intervals during which different type bursts can be received. Different type bursts can have different symbol rates (160 Ksps, 320 Ksps, 640 Kspsh, 1.28 Msps, 2.56 Msps and 5.12 Msps) and/or different multiplexing types (DOCSIS 1.x, ATDMA, SCDMA). ATDMA is similar to DOCSIS 1.x but 25 modulation of up to 64-QAM can be used. These bursts during different sub channels are transmitted on the same or different RF center frequencies but the sub channels have overlapping bandwidth and all subchannel bandwidth is allocated within the bandwidth allocated to the mixed mode channel. In the preferred embodiment, only two sub-channels (called logical channels in DOCSIS parlance) per channel receiver are supported. The 30 preferred embodiment does not support two SCDMA sub-channels, but other embodiments do. Each sub-channel has its burst parameters and channel parameters such as symbol rate and center frequency defined by a separate Upstream Channel Descriptor (UCD) message. The two sub-channels may differ in RF center frequency but if they are on the same HFC and have overlapping bandwidth, they are referred to as sub-channels. This 35 differs from the prior art Jasper I receiver which could not receive mixed mode channels with subchannels at different symbol rates and/or different carrier frequencies. Switching between sub-channels is done on the fly, and there is a guardtime between sub-channels.

Switching between two TDMA sub-channels can be done any time after any burst, but switching between two sub-channels, one of which is SCDMA must be done on a frame boundary. For any particular logical channel, all CMs assigned to it will be of only one type such as DOCSIS 1.0 or advanced PHY configured to transmit only ATDMA. Each CM is sent a list of the logical channels in a downstream message, and, depending upon the CM capabilities, it picks which logical channel it wants to transmit on and thereafter its UCD and MAP messages will restrict it to transmitting on that logical channel.

Each channel receiver is frequency agile so that it can tune to any RF carrier center frequency in the upstream band. A "channel" (as opposed to a sub-channel) refers to a single allocation of bandwidth, and each channel may have a plurality of sub-channels or logical channels, which have different center frequencies but the bandwidths of the sub-channels overlap each other and are contained within the bandwidth allocated to the channel. Different channels which do not have overlapping bandwidth such that they can be transmitted simultaneously are simply referred to as channels. Channels which are mixed-mode, *i.e.*, having two different burst types multiplexed in time with overlapping bandwidth, will be referred to herein as mixed-mode channels.

There are two possible modes of operation: (1) the channels are received in nonoverlapping time; (2) the channels can be received in overlapping time simultaneously by

different channel receivers, and each channel receiver buffers the burst samples, and the

arbiters feeds the burst samples to the shared demodulator section with a maximum

aggregated symbol processing rate of 5.12 Msps. Each channel can be mixed-mode or not.

In non-overlapping time, the MAC process for each channel coordinates with all the other

MAC processes for the other channels to coordinate MAP allocations messages so the

channels do not overlap in time. All channels can be transmitted on the same HFC or on

some combination of different HFC systems. For example, four SCDMA channels at 5.12

Msps can be received at different times from four different HFC systems with an aggregate

symbol rate limited to 5.12 Msps. Another example would be three SCDMA channels at 5.12

Msps and one DOCSIS 1.x channels at 2.56 Msps. The aggregated symbol rate would be

less than 5.12 Msps depending upon the percentage of time that the DOCSIS 1.x channel

was being received so utilization of the shared back end demodulator would not be

maximized.

Allocation by the MAC processes of channels in overlapping time means that up to four channels can be received from the same or different HFC systems. The incoming bursts are buffered in the front end buffer 44 etc. of each digital front end receiver which is receiving a channel and then processed sequentially by the shared back end circuit 52 with a maximum aggregated symbol rate of 5.12 Msps. Examples would be simultaneous reception of four DOCSIS 1.x channels at 1.28 Msps each or two DOCSIS 1.x channels at

2.56 Msps each, or one SCDMA channel at 5.12 Msps and 3 DOCSIS 1.x channels at 1.28 Msps each.

Therefore, the multichannel capability of the receiver means it can receive multiple different channels either simultaneously or in non-overlapping time from the same or different HFC systems using multiple channel receivers and buffers but with the overall symbol processing rate limitation set by the throughput limit of the shared demodulator circuit 52. Multichannel capability is implemented by the architecture shown in Figure 1.

Different channels which are transmitted simultaneously must be received using different channel receivers but the different channels can be transmitted on the same HFC because each digital front end receiver has a multiplexer which can be controlled to couple it to any of the HFC systems to which the receiver is coupled, and each analog front end uses wideband RF sampling so that multiple channels can be simultaneously sampled. In other words, each channel receiver can receive only one channel at a time. However, each channel can be mixed-mode and have two or more sub-channels. The use of multiplexers to select the input to each digital front end receiver is advantageous since it prevents the need to combine the signals from two or more HFC systems which would increase the noise. All HFC systems can be kept separate by using multiplexers.

Each channel receiver is capable of receiving bursts having different symbol rates of up to 5.12 Msps, different multiplexing type (DOCSIS 1.x, ATDMA, SCDMA) and having a different RF frequency and having different SCDMA frame size. Each receiver channel is capable of changing the symbol rate, RF frequency and SCDMA frame size of each subchannel.

The overall receiver of Figure 1 is referred to as multichannel, mixed mode since the multiple receiver channels can each be receiving upstream channel transmissions

25 simultaneously, and each channel can be mixed mode. The individual receiver channels all must have their data processed by the shared back end circuitry 52, but that circuit can only process up to 5.12 Msps. It is the responsibility of the MAC software process 60 to allocate minislots to the various CMs on the various HFC systems and to tune the individual channel receivers such that the aggregate symbol rate from all channels through the shared back

30 end circuit 52 does not exceed 5.12 Msps.

The Jasper I receiver chip of the prior art could not receive 2 sub-channels with different symbol rates or different RF carrier frequencies.

Figure 3B is an illustration of mixed-mode transmission by time division multiplexing of two sub-channels on the same HFC system with each sub-channel at a different symbol rate and each at a different RF frequency but sharing the same bandwidth. Sub-channel 1 is transmitted during interval 33, and sub-channel 2 is transmitted during interval 35 with guardtime 37 used for switchover of the necessary receiver circuits from the symbol rate

R1 and RF frequency of f1 of sub-channel 1 so as to be able to correctly receive a burst at symbol rate R2 and RF frequency f2. The sub-channels 1 and 2 can be any type DOCSIS 1.x, ATDMA, or SCDMA, although, in the preferred embodiment, the sub-channels are not both SCDMA. Each sub-channel has its own UCD message which defines its parameters such as symbol rate and center frequency. Either one combined MAP or two separate MAP messages generated and sent by the CMTS may be used to control which CMs transmit during sub-channels 1 and 2 and when they transmit and their burst lengths and type. The switch between sub-channels is done "on the fly" during guardtime 37 and the guardtime prevents intersymbol interference. As an example, consider "mixed ATDMA/DOCSIS 1.x" mode. In this mode, there are two types of modems on the HFC system, ATDMA and 1.x. The modems share the same REQ (bandwidth requests) and ranging bursts (IUC 1, 2, 3 and 4). However, the DOCSIS 1.x modems use IUC 5 and 6 for data and the ATDMA modems use IUC 9, 10 and 11 for data.

Figure 3C is an illustration of mixed mode transmission with four different DOCSIS 1.0

sub-channels at 1.28 Msps symbol rates sharing the same bandwidth with a single advanced PHY channel at 5.12 Msps using time division multiplexing. The advanced PHY channel 39 can be an SCDMA or advanced TDMA burst with a symbol rate of 5.12 Msps and a center frequency of 20 MHz sharing the same bandwidth with DOCSIS 1.0 modems with symbol rates of 1.28 Msps and center frequency of 17.6 Mhz. Likewise, a 5.12 Msps

SCDMA burst on a 20 MHz carrier can share the same bandwidth with DOCSIS 1.0 and ATDMA sub-channel bursts at 1.28 Msps and center frequencies of 17.6 MHz. Likewise, an SCDMA burst at 5.12 Msps and center frequency of 20 MHz can share the same bandwidth with ATDMA modems at the same symbol rate and center frequency. Switching between TDMA sub-channels is done between bursts, but switching between two sub-channels when one is an SCDMA sub-channel is done on frame boundaries.

The second channel receiver is comprised of analog front end section 20 and digital front end section 24. The third and fourth RF channel receivers are comprised of analog front end 21 and digital front end 26, and analog front end 23 and digital front end 28, respectively. Each of the analog front end circuits 18, 20, 21 and 23 has identical construction. Each of digital front end circuits 22, 24, 26 and 28 has identical construction.

Each analog front end section 18, 20, 21 and 23 functions to tune to the appropriate center frequency of the frequency channel being received and digitize analog signals received from the HFC to which it is connected. Figure 2 is a simplified block diagram of the main circuitry in each analog front end. A passband filter 34 filters out all RF signals outside the upstream digital data band of from 5 - 42 MHz for U.S. DOCSIS systems and 5 - 65 MHz for European DOCSIS systems. The output signals from the passband filter are amplified at 36 and digitized in an A/D converter 38. The A/D converter samples at a constant rate set

by the clock signal on line 39 regardless of frequency of the channel being received at any particular moment. This sampling frequency is established by A/D sampling frequency configuration data stored in a register (not shown) so that the sampling frequency can be changed between the Euro-DOCSIS sampling frequency and the U.S. sampling frequency. 5 Wherever the CMTS is operating, the constant rate clock is set to operate at a frequency which is twice as high as the highest frequency channel to be received to satisfy the Nyquist criteria. In some embodiments, the A/D clock rate is 125 KHz, but in Euro-DOCSIS, the clock rate is different. The controller state machine controls the A/D clock rate in some embodiments based upon configuration data written into the configuration register.

10

RF wideband sampling is used so that the sample rate clock is set to satisfy the Nyquist criteria based upon the widest bandwidth of the upstream band of frequencies to be received. Wideband sampling allows the analog front end to allow two or more channels transmitted on the same HFC system to be simultaneously sampled. Note in Figure 1 that each analog front end circuit has its output coupled to each of the digital front end circuits 15 but the input of each analog front end circuit is coupled to only one HFC system. Thus, if two different channels with non overlapping bandwidth transmitted on the same HFC system are to be received simultaneously, the single analog front end coupled to that HFC system can sample both channels, and two different digital front end circuits can be assigned to process the same samples but to process them to mix each different channel down to 20 baseband.

There are at least four alternative embodiments for the analog front end within the scope of the invention. First, the RF band from 5 to 65 MHz can be divided into two bands with an overlap of 6.4 MHz. The first band is from 5 MHz to 53.5 MHz and is sampled at a rate of 125 MHz. The second band is from 47.1 MHz.to 65 MHz, and is sampled at 75 MHz 25 using IF sampling which shifts the spectrum below fs/2 to 10 MHz till 27.9 MHz. The second embodiment samples the entire band from 5 MHz to 65 MHz using one fast A/D sampling at a 200 MHz rate. The A/D outputs two buses of odd and even samples at a rate of about 100 MHz apiece in one embodiment but uses only a single bus in other embodiments, with the number of buses active controlled by configuration data in an A/D number of buses register 30 (not shown). Two buses is the embodiment shown in Figure 2. The third embodiment samples a spectrum of 6.4 MHz bandwidth around a 5.12 MHz sample rate channel at exactly 20.48 MHz as was done in the prior art Jasper I receiver. The fourth embodiment divides the RF spectrum into three bands. Other A/D sampling rates are possible. Preferably, the A/D clock accuracy is 10 ppm minimum. Other parameter control data 35 registers that can be altered to alter the operation of the analog front end circuitry are: spectrum inversion on/off; A/D sampling at IF of 5.12 MHz on/off; A/D output mode: 2's complement/binary offset; and analog front end select (2 bits for each digital front end).

There is one set of register for the two sub-channels of each mixed mode channel, and there is a shadow register for each parameter which stores the parameter to be loaded into the active register on a sub-channel switch. The contents of the shadow register are loaded to the active register when the timestamp count equals the contents of an 5 analog front end\_activation\_timestamp register which is loaded by the software with the timestamp count when a switch to new analog front end parameters is to occur.

#### **Digital Front End Circuits**

20

Each analog front end section is coupled by a data path to an input of a four input multiplexer in each of the digital front end circuits 22, 24, 26 and 28. These four data paths 10 are collectively indicated at 31. This allows each digital front end to receive digital signals from any of the four analog front end circuits by proper control of the multiplexers, of which 30 and 32 are typical. Control of the multiplexers is implemented by control signals from controller state machine 50 by loading of appropriate data into the register array 51 by microprocessor 58 under the control of MAC process software 60. In alternative 15 embodiments, the state machine 50 and control registers 51 are eliminated, and a microprocessor controlled by one of more media access control processes to generate the proper control signals is coupled to the various circuits that need to be controlled to tune to a channel and receive the data thereof or to change the control signals to the appropriate circuits at the appropriate time to receive the data in mixed mode.

Assuming there can be only two sub-channels of each channel tuned by one of the four "receiver channels", i.e., one analog front end circuit and one digital front end circuit, then there are eight possible sub-channels or channels which the receiver can "simultaneously" receive. The back end circuit 52 can only process at a maximum rate of 5.12 MHz per second, but it is pipelined such that several bursts may be in processing in the 25 various stages of the pipeline simultaneously. Meanwhile, each of the "receiver channels" in front of the arbiter may be tuned to a separate channel, and each of the separate channels may have two or more sub-channels. Assuming only two sub-channels per channel, in the preferred embodiment, the MAC process software will have a separate control process for each sub-channel and there will be eight separate media access control chips 56, one for 30 each channel. Each MAC control unit for a sub-channel will have three buffers to store burst parameters: channel characteristics, burst attributes (IUC), and assigment (MAP). In some embodiments, the two separate MAPs for each sub-channel will be merged into a single MAP. In the single MAP embodiment, the MAP data has two unique words called dummylEs, each of which indicates whether the IE assignment which follows a dummylE is 35 for sub-channel 1 or sub-channel 2.

Each burst data which is output from any of the front end buffers such as 44 has a header which has the following fields therein: channel with two bits that designate whether

the burst came from receiver channel 0 to 3; sub-channel with one bit indicating whether the burst was from sub-channel 1 or sub-channel 0 of the channel identified in the channel field; sub-channel mode having two bits indicating the mode of the burst as SCDMA, DOCSIS 1.0. ATDMA; DOCSIS 1.0 & ATDMA. In the preferred embodiment, as symbolized by Figure 7, 5 bus 103, the burst parameter data for each burst is prepended to each burst's data in the front end buffer 44 so as to travel with the burst data through each pipeline stage in the shared back end demodulator 52. Each receiver channel has a channel\_mode register (not shown) which stores four bits, two for each sub-channel. The two bits for each subchannel define the sub-channel mode as SCDMA, DOCSIS 1.0, ATDMA or DOCSIS 1.0 & 10 ATDMA (same RF frequency and symbol rate).

Each of the four analog front end circuits and digital front end circuits is designed to be capable of receiving channel bursts having a symbol rate of up to 5.12 megasymbols per second (hereafter Msps). However, the maximum aggregated symbol rate which the receiver can support is limited to 5.12 Msps since that is the maximum rate the shared back 15 end circuitry 52 can process at any one time.

In the preferred embodiment, there are four RF inputs 10, 12, 14 and 16 which represent four different HFC systems and four different physical channels. However, in other embodiments, there could be more than four of fewer than four so long as there are at least two.

20

A physical channel refers to a wire or HFC RF input. Each physical channel can carry a mix of "channels" or "sub-channels". Sub-channels have overlapping bandwidth and may or may not have the same center frequencies. Sub-channels are multiplexed in time so bursts on different sub-channels never opelap in time. Channels have no overlap in bandwidth and always have different center frequencies. Because there is no overlap in 25 bandwidth, there can be overlap in time. However, the circuitry on each RF input can receive only one burst at at time although the circuitry coupled to different RF inputs can simultaneously receive bursts. The data from the bursts simultaneously received in different front end circuits is stored in the buffers of those circuits such as buffers 44 and 46. This allows the data to be fed, one buffer at a time, to the shared back end circuit 52. Each front 30 end buffer operates as a FIFO.

Each front end circuit coupled to an RF input may receive mixed mode signals with two or more sub-channels. A "channel" or a "sub-channel" is an RF carrier modulated with bursts of digital data of the advanced PHY TDMA or SCDMA multiplexing types or DOCSIS 1.0 or 1.1 bursts. Symbol rates can be different on different channels and on different sub-35 channels modulated on the same carrier.

Figure 3A is an illustration of four sub-channels with overlapping bandwidth, two of which have different center frequencies and two of which have the same center

frequency. Figure 3A illustrates the result of the CMTS using different DOCSIS UCD messages and MAP messages for each of the four sub-channels to implement sharing the same bandwidth between older DOCSIS 1.0 modems and newer advanced PHY DOCSIS modems. Four UCD messages define the characteristics of the four sub-channels. Four MAP messages are used to schedule the four sub-channel bursts so as to prevent collisions.

In Figure 3A, four different sub-channels are shown at 62, 64, 66 and 68. The frequency dimension is from left to right on the paper, and time is the axis going down into the paper. The sub-channels 62 and 64 are TDMA logical channels assigned to older DOCSIS 1.0 or 1.1 modems which transmit at a lower symbol rate so as to have a bandwidth of only 3.2 MHz. Sub-channel 66 is assigned to advanced PHY SCDMA modems which transmit at a higher symbol rate so as to have a bandwidth of 6.4 MHz. Sub-channel 68 is assigned to advanced PHY modems which are configured to transmit TDMA bursts at a faster symbol rate which causes the channel to have a 6.4 MHz bandwidth.

So as to maximize the use of the existing available bandwidth for upstream digital data transmissions while not requiring any new bandwidth to be assigned to the advanced PHY CMs, the CMTS uses the UCD messages to define the symbol rate, center frequency and multiplexing type (among other things) of the four logical channels so that they have overlapping bandwidth. The CMTS media access control process implemented by software 60 in Figure 1 then generates MAP messages to schedule the timing and length of bursts on each of the four sub-channels so as to prevent collisions between bursts on different channels having overlapping bandwidth. Different channels without overlapping bandwidth may also be defined and controlled in this way. To receive the four sub channels shown in Figure 3A, one receiver channel could be assigned to receive sub-channels 64, 66 and 68 at the three different times these bursts arrive, and another receiver channel could be assigned to receive sub-channel 62 simultaneously with reception of sub-channel 64.

Each wire or HFC system can carry more than one channel or sub-channel. And individual RF carriers can carry more than one sub-channel. For example, since sub-channels 66 and 68 have the same center frequency, these two sub-channels can be transmitted on the same carrier during different time intervals. Sub-channels 66 and 68 may also be transmitted on on two different physical HFC systems using two different carriers, both having center frequency f<sub>c</sub> in which case there is no need to multiplex sub-channels 66 and 68 in time. If they are on different physical channels and not be separated in time, the bursts of sub-channels 66 and 68 must be processed by different front end circuits since one front end circuit cannot process two bursts which overlap both in time and bandwidth.

The receiver disclosed herein could simultaneously process bursts on channels 62 and 64 transmitted at the same time using different analog and digital front ends. This is because the combined symbol rate does not exceed the maximum back end processing throughput of 5.12 Msps. The back end circuitry 52 would be shared to do this, but since it 5 is piplined, both bursts can be in the pipeline at different stages at the same time.

Since the bandwidth of the two logical channels 66 and 68 overlap, and MAP messages are used to control the time of beginning and durations of SCDMA bursts on logical channel 66 and TDMA bursts on logical channel 68 so there is no overlap in time, the same front end circuitry can process both bursts. In Figure 3, this use of the MAP 10 messages is illustrated by scheduling SCDMA bursts on logical channel 66 to start at time T2 and end at time T3 and scheduling TDMA bursts on logical channel 68 to start at time T4.

TDMA bursts on logical channels 62 and 64 can overlap in time since these two logical channels have UCD messages which define their symbol rates so as to yield bandwidths of only 32 MHz, and the UCD messages for these two logical channels set center frequencies  $f_{c1}$  and  $f_{c2}$  so as to be offset in frequency from center frequency  $f_c$  such that the bandwidth of logical channels 62 and 64 do not overlap. Figure 3 shows TDMA bursts on logical channels 62 and 64 overlapping in time with each other but not overlapping in bandwidth and not overlapping in time with bursts on logical channels 66 or 68. Specifically, bursts are occurring on each of logical channels 62 and 64 starting at time T1 and ending just before time T2 when SCDMA bursts on logical channel 66 starts (there is actually a short guard time between bursts). In the preferred embodiment, all four logical channels in Figure 3 could be received by the one CMTS receiver shown in Figure 1 even if these four logical channels carried signals from four different HFC networks. Some switching of configuration or operation of various circuits etc. must occur in the digital front 25 end circuitry shown in Figure 1 to be able to receive all four logical channels in Figure 3 "simultaneously". That is, one receiver chip can be used to receive all four sub-channels even though the bursts do not, for the most part overlap in time. To allow for the necessary switchover and frequency changes to do this, a short guardtime between different time intervals on different logical channels is used.

There are four digital channel circuits 22, 24, 26 and 28 each of which has a digital sample input coupled to each of the analog front end circuits. Each of the digital front end circuits has a multiplexer of which 30 and 32 are typical. These multiplexers each have four inputs for receiving digital samples. One of these inputs of each multiplexer is coupled to the first analog front end circuit 18. Another of these inputs on each multiplexer is coupled to 35 the second analog front end circuit 20. Likewise, the third and fourth inputs of each multiplexer is coupled to the third and fourth analog front end circuits (not shown). Each of

30

these digital front end circuits do several functions to be described below to down convert the frequency, filter to reduce noise in match filters, perform narrow band excision processes to remove noise, do impulse detection to determine which samples should be ignored, do digital sample processing such as interpolation and decimation and despread the 5 spectrum of any spread spectrum bursts. Each digital front end circuit recovers an entire burst and stores the processed samples of the burst in a FIFO front end buffer of which 44 and 46 are typical. Each FIFO front end buffer can store more than one burst.

An arbiter 48 retrieves the burst samples from the front end FIFO buffers in some order determined by the priority scheme of the arbiter and stores them in a sample buffer in 10 the shared back end circuit 52. In the preferred embodiment, the bursts are retrieved from the FIFO buffers on a first-come, first-served basis based upon the times of notification that the bursts had been stored. Another priority scheme is to retrieve the bursts from the buffers which are closest to overflowing first. Other possible embodiments are: NULL SIDs first with no sample read out; priority based upon the burst IUC number with higher priority 15 IUC bursts serviced first with the MAC process setting a priority table with a priority number from 0 to 15 for each IUC thereby allowing maintenance bursts, etc. to be given highest priority; priority based upon burst size with short bursts such as voice-over-IP or request bursts serviced first with overflow prevention implemented by giving higher priority to bursts that were skipped. In some embodiments, the order in which bursts are read from the buffers by the arbiter 48 is controlled by a controller state machine 50 under control of the MAC process 60. Any arbiter scheme suitable for the SIDs that are being handled by the system will suffice.

Whichever burst is read out by the arbiter is sent for processing to a shared digital back end circuit 52. The back end circuit 52, in the preferred embodiment, is the same burst processing circuitry used in the prior art Jasper 1 receiver and described in U.S. patent application serial number serial number 09/792,815 filed by the assignee of the present invention on February 23, 2001.

25

30

In some embodiments, the arbitrator 48 is controlled by the MAC process to give higher priority to various services which cannot tolerate too much latency. The MAC process knows for example when bursts for video teleconferencing, voice-over-IP or video or other services which cannot tolerate latency are arriving and on which HFC system these bursts are arriving. The MAC process knows this since it generates the UCD and MAP messages that tell each service when it can transmit. Using this information, the MAC process writes suitable data into register array 51 to control controller state machine 50 to 35 generate control signals to control the arbitrator 48 such that services with low latency tolerance are serviced with high priority. The details of the arbitrator 48 are not critical to the

invention, and any arbitrator from the prior art that can service the multiple digital front end receivers in the manner described herein will suffice to practice the invention.

The controller state machine 50 functions to generate control signals to all circuitry in the analog or digital front end, the arbitrator 48 or the digital back end circuitry that needs to 5 be configured to receive particular burst types. The nature of the configuration control signals for each channel generated by the controller state machine and the timing of these control signals is based upon the data in the UCD messages and MAP messages sent downstream by the transmitter to control the burst which is currently being processed by the digital front end circuit being controlled. The timing of the control signals is controlled by 10 the MAP data and the count in an upstream minislot counter counting the upstream minislot of the HFC system on which the burst being processed was transmitted. There are four upstream minislot counters in embodiments with four digital front end receivers, each counting the upstream minislot count of one HFC system. The media access control chip 56 and/or the microprocessor 58 under control of the MAC software monitors the upstream 15 minislot count for each HFC system and knows from the UCD and MAP messages which type bursts will be arriving at each receiver channel and when. The microprocessor and/or media access control chip then loads the appropriate data into register array 51 at the proper time to cause the controller state machine 50 to generate appropriate control signals to cause each type burst to be properly received. These control signals control and 20 configure the modes of operation of the various circuits in the digital front end and shared back end circuits at the appropriate time to process each particular burst type as it is received. In some embodiments, the burst's UCD data is sent through the shared back end circuit pipeline stages with the samples of the burst to control the circuitry of each stage to receive the burst.

The following parameters can be changed on the fly in each digital front end circuit: symbol rate; RF frequency; and, SCDMA frame size. The new parameters are loaded from the UCD data before the occurrence of switching to a new sub-channel carrying a burst characterized by the new parameters.

25

Symbol rate switching is accomplished with a dead time smaller than 96 symbols as required by DOCSIS. When the symbol rate changes, the delay through the digital front end circuitry does not change in the preferred embodiment. How this is implemented is discussed elsewhere herein, but preferably is accomplished by shifting the minislot clock signal for the pertinent channel by the known amount of the delay change in the various circuits such as the variable decimator 86 and interpolator when switching between symbol rates. The gain in the digital front end circuitry also adjusts as necessary without intevention by the controller state machine 50 or MAC software 60.

The DDFS local oscillator 78 in Figure 4 implements the frequency change on the fly to generate a new local oscillator signal on bus 80 to cause mixer 74 to mix the new subchannel down to baseband. The MAC software 60 will convert the RF frequency defined in the UCD data to a phase step appropriate to control the DDFS to generate the proper local oscillator frequency. The MAC process 60 then loads the appropriate data into the register array 51 to cause the controller state machine to generate the proper control signal on bus 82 in Figure 4 to control the DDFS. This all happens within 96 symbol times plus 100 msec to comply with DOCSIS 1.1 requirements for the CM.

The back end circuit 52 does the following functions: start of burst detection to

measure timing offsets; carrier recovery; processing of the preamble of each burst to

measure a timing offset and develop equalization coefficients and develop phase and

amplitude error correction factors; de-interleaving and descrambling of the data of each

burst if necessary; differential decoding and decoding of trellis code modulated burst data if

differential decoding or TCM is turned on; reassembly of the Reed-Solomon groups; de

interleaving and error correction of the Reed Solomon groups; and, output of the recovered

data of each burst along with equalization coefficients, timing offset measurements and any

other measurements made. The data and measurements are output on line 54 to a media

access control circuit 56. The media access control circuit 56 passes the recovered data

and measurements to a media access control process executing in microprocessor 58. This

media access control process is controlled by media access control process software 60

stored in memory which is external or internal to microprocessor 58.

The media access control process 60 receives upstream bandwidth requests from the CMs on the four HFC systems served and does coordinated bandwidth allocation by generating Upstream Channel Descriptor messages (hereafter UCD messages) and MAP messages to allocate bandwidth to those modems that need it. There is one UCD message for every logical channel and every sub-channel transmitted on a physical channel. The UCD message defines the characteristics of the bursts transmitted on that logical channel. The MAP messages represent bandwidth awards. The MAP messages tell which CMs can transmit and when. These MAP messages assign specific upstream intervals of minislots to specific burst types and service identifiers. The service identifiers or SIDs tell the CMs which CMs can transmit because each CM has one or more unique SIDs assigned to it.

A MAP message is comprised of one or more information elements called IEs. Each IE corresponds to one grant of bandwidth. Each IE contains a service identifier (SID - which identifies the CM which can transmit), an interval usage code (IUC - which defines the burst type) and an offset (which defines the time in minislots offset from a reference when transmission may begin). The SID identifies which service may transmit data during the burst corresponding to the IE, and the SID is used by each CM to determine whether the

grant is for it or for some other CM. Each different source of data coupled to a CM has a different SID. The IUC identifies which of the 15 different SCDMA and TDMA burst types at various symbol rates and modulation types that may be transmitted.

The burst length is calculated by subtracting the offset in one IE from the offset in the 5 next IE of the MAP. Each CM must generate each burst at the appropriate time so that the beginning of the burst arrives at the CMTS at the assigned first minislot boundary specified in the MAP message. This is done by keeping an upstream minislot counter in the CM synchronized with an upstream minislot counter in the CMTS.

## Channel Parameters, Burst Parameters, User Unique Parameters

10

Basically, the transmission characteristics of each logical channel, as defined by the corresponding UCD message, are separated into three portions: 1) channel parameters; 2) burst profile attributes, and 3) user unique parameters. In the appended claims, the term "burst parameters" is intended to include all those channel parameters, burst profile attributes and user unique parameters needed by the shared back end demodulator to 15 properly process each burst.

The logical channel parameters include: a) the symbol rate which can be any one of 6 different rates from 160 ksym/sec to 5.12 Msym/sec in octave steps; b) the center frequency; and c) the 1536-bit preamble superstring that is prepended to at least some bursts; and d) the SCDMA channel parameters. These characteristics are shared by all 20 users on a given channel or sub-channel (hereafter logical channel may be used to refer to either channel or sub-channel).

The burst profile transmission characteristics of a logical channel, in the preferred embodiment, include: modulation (QPSK, 64 QAM, 128 QAM etc.), differential encoding on or off; Trellis or TCM encoding on or off; preamble length, preamble value offset; preamble type 25 (QPSK 0 or QPSK1), RS error correction T value from 0 to 16 where 0 is no FEC bits to 16 for the maximum where the number of codeword parity bytes is 2xT, RS codeword length (fixed or shortened), scrambler seed, max burst length in minislots, guardtime from 5 to 255 symbols for TDMA channels and 1 symbol for SCDMA channels, last codeword length, scrambler on or off, byte interleaver depth, byte interleaver block size, SCDMA spreading on 30 or off, codes per subframe, and SCDMA interleaver step size.

User unique parameters may vary from user to user even when on the same channel and same burst type and include such things as: power level; offset frequency (defines center frequency of channel to transmit on); ranging offset to achieve minislot boundary alignment at CMTS (which also achieves upstream chip clock alignment between 35 the upstream chip clock generated at the CMTS and the chip clock embedded in the received signal at the CMTS receiver - a state which is referred to herein as "phase coherence"), burst length in minislots if variable on the specified channel (changes from burst to burst);

and the transmit equalizer coefficients (up to 64 coefficients specified by 4 bytes per coefficient - 2 real and 2 complex).

The ranging offset is measured by the digital back end circuitry 52 of the CMTS and is the fine tuning delay correction applied by the CM to the CMTS Upstream Frame Time 5 derived at the CM during the coarse ranging process. It is an advancement equal to roughly the round-trip delay of the CM from the CMTS, and is needed to synchronize upstream transmissions in the TDMA and SCDMA bursts so that frames or spreading intervals of spread spectrum data from different CMs all arrive at the CMTS with their frame boundaries aligned in time so as to minimize intersymbol interference. The CMTS measures the required 10 ranging offset for each CM based on reception of one or more successfully received training bursts, and provides feedback of this offset value to the CM. Training bursts are transmitted by CMs initially upon power up in response to ranging invitation messages from the CMTS and periodically thereafter, also in response to invitations to the CMTS. The MAC process 60 controls the process of sending downstream messages via downstream 15 transmitter 70 telling the CMs when the ranging intervals are in terms of upstream minislot numbers and what each CM's measured ranging offset is for CMs who have successfully completed ranging. Downstream UCD and MAP messages are also composed by the MAC process software and sent downstream by transmitter 70.

A single RF carrier may have two or more sub-channels which are controlled by the MAP messages so as to not overlap in time such as separate TDMA and SCDMA time intervals. The TDMA time intervals are one sub-channel and the characteristics of the bursts transmitted during the TDMA time intervals are defined in one UCD message for that sub-channel. The SCDMA time intervals are a second sub-channel with burst characteristics of which are defined by a second UCD message. Two sub-channels on the same physical channel can both be the same multiplexing type but have different symbol rates.

## MORE DETAIL ABOUT THE STRUCTURE AND OPERATION OF EACH BLOCK

The above discussion was an overview of the overall structure. We will now address the individual circuit elements in more detail. Referring to Figure 4, there is shown a more detailed block diagram of one embodiment of the digital front end receiver. Analog front end circuit 17 is comprised of the circuitry of Figure 2 or any of the alternative embodiments for that circuit discussed herein. A front end automatic gain control circuit 19 functions to generate a signal on line 21 which controls a variable analog attenuator (not shown in Figure 2) in series with the A/D converter 38. The function of the analog attenuator is to receive the attenuation control signal on line 21 and impose an amount of attenuation controlled by the signal on line 21 such that the analog signal entering the A/D converter has some nominal power level specified by the cable operator. The nominal power level is set to utilize the full

dynamic range of the A/D converter without exceeding its range of linearity. The front end AGC circuit has the structure disclosed in U.S. patent application serial number 09/999,060, filed 11/15/2001, which is hereby incorporated by reference. Basically, it comprises a power measurement circuit to measure the power in the samples on bus 72. The power 5 measurement circuit is coupled to a control word generator and a loop filter. The loop filter is coupled though a mode switch to a control word register. The control word generator is coupled to a sigma-delta modulator to generate an analog control signal on line 21 based upon the value of the control word. An analog filter filters the generated analog signal to smoothen it.

The digital front end circuitry 22 (representing one of four channels in the preferred embodiment) is coupled to receive the output sample stream on bus 72. A multiplexer 30 receives a stream of 12 bit samples from analog front end circuit 18 on bus 72 in one embodiment but bus 72 is actually an odd and even bus in another embodiment. In the pictured embodiment, bus 72 carries a stream of samples of the output of A/D converter 38 15 in Figure 2 at a 125 MHz sampling rate. In an alternative embodiment, bus 72 is comprised of two 12-bit parallel buses, each carrying 12-bit samples at a 100 MHz rate to multiplexer 30.

10

The multiplexer 30 has four such inputs to receive samples from each of the four analog front end circuits. A select control signal on line 75 generated by the controller state machine 50 under control of the MAC process 60 generates the select control signal to 20 control which HFC system is coupled to the digital front end 22. This allows different digital front end circuits to receive different channels from either the same HFC and the same analog front end (via wideband sampling) or from different HFC systems and different analog front end circuits.

A digital mixer 74 mixes the sample stream down to base band on bus 76. A direct 25 digital frequency synthesizer generates a digital local oscillator sample stream on bus 80 for use by the mixer 74 with the frequency of the local oscillator signal controlled by a frequency control signal on bus 82 from the controller state machine 50 in Figure 1. The frequency control signal is established by the MAC process 60 based upon the center frequency of each sub-channel or channel to be received at any particular time. In other 30 words, in mixed mode when two sub-channel bursts are to be received at two different times with two different center frequencies, the frequency control signal is set first to control the DDFS 78 to generate a proper frequency local oscillator signal to receive the first sub-channel, and then, during the guardtime between sub-channel bursts, the controller state machine generates a new frequency control signal to cause DDFS 78 to generate a 35 proper frequency local oscillator signal to mix the second sub-channel burst down to baseband. Center frequency data for the two sub-channels is obtained from their UCD

messages, and the timing as to when the two different sub-channel bursts are expected is obtained from the MAP messages for these two bursts.

An interpolator 81 re-samples at the symbol clock rate the samples on bus 76. The samples on bus 76 were taken at the rate of the constant rate A/D clock 39 in Figure 2. That 5 rate can be switched to support Euro-DOCSIS. The symbol clock rate of the burst being processed is supplied from a timebase.

A master timestamp count shared by all HFC systems and all digital front end circuits is generated in timebase 55 in Figure 1, and this timestamp information is used to generate downstream sync and snapshot messages for each HFC system.

10

The timebase 55 serves to generate timing information needed by various circuits in the CMTS receiver. The timebase 55 has a master timestamp counter, an upstream minislot counter for each HFC system, a frame counter used for SCMDA bursts only and a spreading interval counter used for SCDMA bursts only. In the preferred embodiment, each of the four "channels" (combination of analog front end circuit with a digital front end circuit) has its own timebase such that all the counts are independent except the timestamp count which is common to all four channels. Separate snapshot messages are generated for each HFC system using the common timestamp count shared by all channels. This collection of individual timebases is preferred so that each HFC system can have its own minislot size. Symbol rates for the various types of bursts are fixed by the DOCSIS specifications, but 20 minislot size and the number of SCDMA spreading intervals per frame and the number of codes per minislot are matters of discretion for each HFC system with a few restrictions. The timebase also implements an upstream minislot counter for each HFC system. Each CM on a particular HFC maintains an upstream minislot counter which is synchronized by the snapshot messages to the upstream minislot counter in the timebase in the CMTS assigned 25 to the HFC system of which the CM is a part. The minislot counter in the CMTS for each particular HFC system is used to control timing of processing of bursts from that HFC system. The MAC process assigns CMs on each system to particular minislots on that system when they are authorized to transmit using UCD and MAP messages. The CMTS receiver circuitry then uses the UCD and MAP message data for each burst and the minislot 30 counter for that HFC system to properly configure itself at the right time to process the burst. For example, an SCDMA burst from HFC system 1 may have minislot lengths which are 16 symbol times long and may be assigned to minislots 100 to 150 for that system. The burst may be defined as having TCM turned on, RS codeword length and T values equal to certain values, scrambling turned on with scrambling seed X, etc. The CMTS circuitry knows from 35 the HFC system 1 minislot counter in the timebase when minislot 100 is about to happen on that system. The CMTS circuitry also knows the burst parameters and which CM is sending the burst from the UCD and MAP messages. The controller state machine is then controlled

by writing the appropriate data into the register array 51 just before minislot 100 to generate the proper control signals to process that particular burst. For example, frequency control signal for the DDFS 78 will be set to generate the proper frequency, the variable decimator 84 will be informed of the symbol rate of the burst, and the TCD decoder in the back end circuit 52 will be turned on. Likewise, the RS decoding circuitry will be informed what the codeword length and T value are and the descrambling circuitry will be given the scrambler seed that was used to scramble the data. If the spreading codes are not permanently assigned to specific minislot numbers (which they are in the preferred embodiment) but are assigned specifically to each burst, then the proper codes will be supplied to the despreader circuitry to despread the spectrum. Any other control signals to configure the various circuits in the CMTS that process the burst will also be generated.

The timebase also maintains a frame counter and a spreading interval counter for each HFC system to which it is coupled, both of which are used to control timing of processing for SCDMA bursts from the system to which the frame and spreading interval counters pertain. These timebase signals are coupled by connections not shown to all circuits in the CMTS that need them to process particular types of bursts. The snapshot downstream messages include the current timestamp count when the snapshot was taken, the current upstream minislot count, and the current frame count. These snapshot messages are sent downstream to the CMs occasionally on frame boundaries. The snapshot messages allow the CMs to send upstream SCDMA bursts that are properly synchronized and framed after the CM completes the DOCSIS or any other suitable ranging process. The ranging process allows each CM to achieve minislot boundary alignment such that upstream bursts scheduled by MAP messages to be sent during specified minislots arrive at the CMTS aligned with the assigned minislot boundaries. TDMA bursts can be properly synchronized by deriving the minislot count solely from the timestamp messages included within the normal DOCSIS sync messages.

The master symbol clock is recovered in each CM and used to synchronize a local upstream symbol clock in the CM to the master symbol clock in the CMTS. The CMTS therefore uses its own master symbol clock to process bursts in some embodiments but recovers and tracks the symbol clock used by each CM in other embodiments.

Returning to consideration of the interpolator 81, samples on path 76 are at the A/D sample clock rate, but this rate can be switched by the controller state machine for EURO-DOCSIS bursts although the A/D clock rate will not be switched when switching between sub-channels in mixed mode operation or switching to another channel when operating in the U.S. But if an A/D sample rate switch occurs, the interpolator output sample rate might also occur. The function of interpolator 81 is to figure out what the value of the I and Q values are at each symbol time from the incoming symbol stream and generates output

samples at a sample rate which is a multiple of the symbol clock rate for the symbol clock of the HFC system from which the burst came. If the sample stream has a sample rate of between 8 to 16 times the DOCSIS 2.0 symbol clock rate of 5.12 MHz, the interpolator will interpolate the sample stream down to 8 times the DOCSIS 2.0 symbol clock rate of 5.12 MHz. Sampling rates that are higher will be interpolated to 16 times the DOCSIS 2.0 symbol clock rate. There is also a bypass mode where the interpolator is not used for sample streams with a sampling rate equal to the ASIC clock rate of 20.48 MHz.

A variable decimator 86 receives the output sample stream from the interpolator 81. In some embodiments, the decimator 86 includes a matched filter. The purpose of the decimator is to filter and decimate the baseband sample stream to reduce the sample rate to 2 samples per symbol based upon the symbol rate of the burst being received. Samples are not thrown away but filtered down to the 2-samples-per-symbol rate. The structure of the variable decimator is an array of half band filters as used in the Jasper I prior art. The number of half band filters used depends upon the symbol rate of the burst being processed. Since the number of decimation stages depends on the signal symbol rate, the controller state machine sends the symbol rate of the burst to be processed to the variable decimator to control how many stages are used. The data rate output by the decimator 86 is 10.24 MHz maximum, but depends upon the sub-channel symbol rate and is adjusted based upon the UCD data for the burst being processed. The variable decimator is designed so that the delay therethrough is the same regardless of symbol rate, so there is no sample loss when switching between different symbol rate sub-channels.

Because symbol rates can change between time intervals for different sub-channels in mixed mode or when a new channel is tuned in multimode, the delay through the variable decimator will change. The delay through the decimator should be the same for all symbol rates to prevent errors because the CMTS is expecting to see a burst at the start of whatever minislot the burst was assigned. If the variable decimator causes an unknown delay, the burst does not arrive in the back end circuit 52 at the start of the assigned minislot, and errors occur in receiving the data. Further, the timing error may cause the CMTS to send a message downstream telling the CM that sent the burst to do its ranging process again when the CM is actually correctly ranged. This causes delay and unnecessary overhead.

There are three possible embodiments that represent solutions to this variable delay caused by the decimator problem. The first embodiment is to use a variable delay element and a conventional decimator. In this embodiment, the controller state machine controls the variable delay element in accordance with the symbol rate of each burst as it is processed such that, regardless of the symbol rate, the delay the burst experiences as it passes through the variable decimator is the same. A variable delay element controlled by the

controller state machine should also be used with any other element that causes a variable amount of delay depending upon the symbol rate so as to make the delay the same for all bursts regardless of symbol rates.

In the second embodiment, the variable decimator 86 imposes a different delay for 5 each different symbol rate, and the burden to compensate for the delay is shifted to the CM. This is done by the MAC software in scheduling bursts. The MAC software in this embodiment keeps track of the symbol rate of each burst it schedules. When there is a change in symbol rate between a first burst and a second burst, the MAC software schedules a ranging interval between the first burst and the second burst, and sends a 10 downstream message to the CM that is to send the second burst telling it to perform a ranging algorithm again. This compensates for the changed delay in the decimator, because a start of burst detector which detects when the ranging burst arrives is located in the back end circuitry 52 and is located after the decimator. Therefore, the timing measurement will compensate for the new delay in the decimator and the downstream message with the 15 timing measurement will cause the CM to alter its burst transmission time to compensate for the changed delay of the decimator.

The third embodiment is the preferred one, and involves shifting the timebase minislot clock in the CMTS corresponding to the HFC system from which a burst with a different symbol rate is scheduled so as to compensate for the known delay imposed by the 20 decimator for that symbol rate. The delay in the decimator for each symbol rate is known, so fixed adjustments to the timebase minislot counter can be made by switching fixed delays in or out depending upon the symbol rate of the burst to be processed. The preferred way of shifting the timebase minislot or symbol clock count is to add or subtract an appropriate number from the timestamp count used by the timebase for the HFC from which the burst originated. This timebase shifting is easiest because it eliminates the need for as many gates as the first alternative and eliminates the overhead and delays of the ranging process.

The variable decimator can have the same structure as the variable decimator in the Jasper I prior art receiver. In the preferred embodiment however, IIR halfband filters are used instead of FIR filters with coefficients selected to minimize the gate count.

30