### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2008-103675 (P2008-103675A)

(43) 公開日 平成20年5月1日(2008.5.1)

| (51) Int.Cl. |         |           | FΙ          |           | テーマコート     | (参考)   |

|--------------|---------|-----------|-------------|-----------|------------|--------|

| HO1L         | 21/822  | (2006.01) | HO1L 27/04  | F         | 5F038      |        |

| HO1L         | 27/04   | (2006.01) | HO1L 27/08  | 102C      | 5F048      |        |

| HO1L         | 21/8234 | (2006.01) | HO1L 27/10  | 434       | 5F083      |        |

| HO1L         | 27/088  | (2006.01) | HO1L 29/78  | 371       | 5 F 1 O 1  |        |

| HO1L         | 21/8247 | (2006.01) | HO1L 27/04  | A         |            |        |

|              |         |           | 審査請求 未請求 請求 | 求項の数 24 O | L (全 37 頁) | 最終頁に続く |

(21) 出願番号 特願2007-186344 (P2007-186344) (22) 出願日 平成19年7月17日 (2007.7.17) (31) 優先権主張番号 特願2006-257752 (P2006-257752)

(32) 優先日 平成18年9月22日 (2006. 9. 22)

(33) 優先権主張国 日本国(JP)

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100058479

弁理士 鈴江 武彦

(74)代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74)代理人 100075672

弁理士 峰 隆司

(74)代理人 100109830

弁理士 福原 淑弘

最終頁に続く

# (54) 【発明の名称】半導体集積回路

# (57)【要約】

【課題】エージングデバイスの寿命を簡単な回路により 制御する。

【解決手段】本発明の例に関わる半導体集積回路は、半導体基板11と、半導体基板11の表面領域に形成される素子分離絶縁層21により分離され、第2方向に隣接する第1及び第2素子領域内にそれぞれ形成される第1及び第2MIS型デバイスA1,A2とを備え、第1及び第2MIS型デバイスA1,A2は、それぞれ、フローティングゲート及びコントロールゲート電極を持つスタックゲート構造を有し、第1MIS型デバイスA1は、エージングデバイスとして機能し、第2MIS型デバイスA2は、エージングデバイスの電荷保持特性を制御する制御デバイスとして機能する。

【選択図】 図4

☑ 4

#### 【特許請求の範囲】

### 【請求項1】

半導体基板と、前記半導体基板の表面領域に形成される素子分離絶縁層と、前記素子分離絶縁層により分離され、第1方向に直交する第2方向に隣接する第1及び第2素子領域内にそれぞれ形成される第1及び第2MIS型デバイスとを具備し、前記第1及び第2MIS型デバイスは、前記第1及び第2MIS型デバイスは、エージングデバイスとして機能し、前記第2MIS型デバイスは、エージングデバイスとして機能し、前記第2MIS型デバイスは、前記エージングデバイスの電荷保持特性を制御する制御デバイスとして機能することを特徴とする半導体集積回路。

#### 【請求項2】

前記第1及び第2MIS型デバイスのコントロールゲート電極は、それぞれ独立に制御されることを特徴とする請求項1に記載の半導体集積回路。

#### 【請求項3】

前記第1MIS型デバイスのフローティングゲートは、前記第1MIS型デバイス直下の前記半導体基板の表面領域の導電型と同じ導電型であり、前記第2MIS型デバイスのフローティングゲートは、前記第2MIS型デバイス直下の前記半導体基板の表面領域の導電型と逆の導電型であることを特徴とする請求項1又は2に記載の半導体集積回路。

#### 【請求項4】

前記第1素子領域の前記第2方向の幅は、前記第2素子領域の前記第2方向の幅よりも狭いことを特徴とする請求項1乃至3のいずれか1項に記載の半導体集積回路。

#### 【請求項5】

前記第1MIS型デバイスに関し、前記フローティングゲートの前記第2方向の幅は、前記フローティングゲートの前記第1方向の長さよりも短いことを特徴とする請求項1乃至4のいずれか1項に記載の半導体集積回路。

#### 【請求項6】

前記第1MIS型デバイスに関し、前記フローティングゲートの前記第1方向の両辺には、窪みが設けられていることを特徴とする請求項1乃至4のいずれか1項に記載の半導体集積回路。

### 【請求項7】

前記第2MIS型デバイスに関し、前記フローティングゲートの前記第2方向の幅は、前記フローティングゲートの前記第1方向の長さよりも長いことを特徴とする請求項1乃至6のいずれか1項に記載の半導体集積回路。

#### 【請求項8】

前記第1及び第2MIS型デバイスは、それぞれ、2つのセレクトゲートトランジスタにより挟み込まれ、かつ、前記2つのセレクトゲートトランジスタに直列接続されることを特徴とする請求項1乃至7のいずれか1項に記載の半導体集積回路。

#### 【請求項9】

前記第1及び第2素子領域間の前記素子分離絶縁層の前記第2方向の幅は、前記2つのセレクトゲートトランジスタのうちの1つのゲート電極から前記第1又は第2MIS型デバイスの前記フローティングゲートまでの前記第1方向の幅よりも狭いことを特徴とする請求項8に記載の半導体集積回路。

#### 【請求項10】

前記第1MIS型デバイスを挟み込む前記2つのセレクトゲートトランジスタのゲート電極の前記第2方向の幅は、前記ゲート電極の前記第1方向の長さよりも短いことを特徴とする請求項8又は9に記載の半導体集積回路。

# 【請求項11】

前記第1及び第2MIS型デバイスの前記フローティングゲートの前記第1方向の長さは、互いに等しいことを特徴とする請求項1乃至10のいずれか1項に記載の半導体集積回路。

# 【請求項12】

10

20

30

40

前記第1及び第2MIS型デバイスを挟み込む前記4つのセレクトゲートトランジスタのうち、前記素子分離絶縁層を挟んで対向する、それぞれ2つの前記セレクトゲートトランジスタのゲート電極の前記第1方向の長さは、互いに等しいことを特徴とする請求項1乃至11のいずれか1項に記載の半導体集積回路。

### 【請求項13】

前記素子分離絶縁層により前記第1及び第2素子領域と分離され、前記第1素子領域に隣接して形成される第3素子領域と、前記第3素子領域内に形成される第3MIS型デバイスとを具備し、前記第2及び第3MIS型デバイスは、前記第1MIS型デバイスを挟み込み、前記第3MIS型デバイスは、前記エージングデバイスの電荷保持特性を制御する制御デバイスとして機能することを特徴とする請求項1乃至12のいずれか1項に記載の半導体集積回路。

#### 【請求項14】

前記第1MIS型デバイスに関し、前記フローティングゲートの前記第2方向の幅は、前記第1素子領域の前記第2方向の幅よりも広いことを特徴とする請求項1乃至13のいずれか1項に記載の半導体集積回路。

#### 【請求項15】

前記第2MIS型デバイスに関し、前記フローティングゲートの前記第2方向の幅は、前記第2素子領域の前記第2方向の幅よりも広いことを特徴とする請求項1乃至14のいずれか1項に記載の半導体集積回路。

### 【請求項16】

前記素子分離絶縁層の前記第2方向の幅は、前記第1素子領域の前記第2方向の幅及び前記第2素子領域の前記第2方向の幅よりも広いことを特徴とする請求項1乃至15のいずれか1項に記載の半導体集積回路。

#### 【請求項17】

前記第1MIS型デバイスのフローティングゲートの前記第2方向の幅は、前記第2MIS型デバイスのフローティングゲートの前記第2方向の幅よりも狭いことを特徴とする請求項1乃至16のいずれか1項に記載の半導体集積回路。

#### 【請求項18】

請求項13に記載の半導体集積回路において、前記第2又は第3MIS型デバイスの前記フローティングゲートに電荷を注入し、この後、前記第1MIS型デバイスの前記フローティングゲートに電荷を注入して初期設定を完了することを特徴とする書き込み方法。

# 【請求項19】

前記第1、第2又は第3MIS型デバイスの前記フローティングゲートに対する電荷の注入は、同一の第1矩形パルス、又は、大きさ若しくは幅が段階的に変化する第2矩形パルスを、前記コントロールゲート電極に繰り返し印加する書き込みにより行い、前記第1又は第2矩形パルスを印加した直後に、前記第1又は第2MIS型デバイスの状態を確認する読み出しを行い、前記第1又は第2MIS型デバイスの状態が所定の状態になるまで、前記書き込みと前記読み出しを繰り返すことを特徴とする請求項18に記載の書き込み方法。

#### 【請求項20】

半導体基板と、前記半導体基板の表面領域に形成される素子分離絶縁層と、前記素子分離絶縁層により取り囲まれる素子領域内に形成される第1導電型の1つの拡散層と、前記拡散層上で第1方向に並んで形成される第1及び第2MIS型デバイスと、前記拡散層の前記第1方向の2つの端部にそれぞれ1つずつ配置される2つのセレクトゲートトランジスタとを具備し、前記第1及び第2MIS型デバイスは、それぞれ、フローティングゲート及びコントロールゲート電極を持つスタックゲート構造を有し、前記第1MIS型デバイスは、エージングデバイスとして機能し、前記第2MIS型デバイスは、前記エージングデバイスの電荷保持特性を制御する制御デバイスとして機能することを特徴とする半導体集積回路。

### 【請求項21】

10

20

30

前記第1及び第2MIS型デバイスのコントロールゲート電極は、それぞれ独立に制御されることを特徴とする請求項20に記載の半導体集積回路。

### 【請求項22】

前記第1 M I S 型デバイスのフローティングゲートは、前記第1 導電型であり、前記第2 M I S 型デバイスのフローティングゲートは、前記第1 導電型とは異なる第2 導電型であることを特徴とする請求項20 又は21 に記載の半導体集積回路。

#### 【請求項23】

請求項20乃至22のいずれか1項に記載の半導体集積回路において、前記第2MIS型デバイスの前記フローティングゲートに電荷を注入し、この後、前記第1MIS型デバイスの前記フローティングゲートに電荷を注入して初期設定を完了することを特徴とする書き込み方法。

#### 【請求項24】

前記第1MIS型デバイスの前記フローティングゲートに電荷を注入した後に、前記第 2MIS型デバイスの前記フローティングゲート内の電荷を抜き取る書き戻しを行うこと を特徴とする請求項23に記載の書き込み方法。

【発明の詳細な説明】

### 【技術分野】

#### [0001]

本発明は、バッテリーの要らない電子タイマーを搭載した半導体集積回路に関する。

### 【背景技術】

#### [0002]

近年、バッテリーの要らない電子タイマー、即ち、時間の経過と共に出力が変化する経時変化デバイス(以下、エージングデバイス)が、コンテンツ配信、クレジットカード、デジタル製品のレンタル、デジタルソフトのレンタルなどの分野で使用が検討され始めている。

# [0003]

エージングデバイスは、フローティングゲートとコントロールゲート電極とからなるスタックゲート構造を有し、フローティングゲート内の電荷の保持特性(寿命)により一定期間を計測する電子タイマーとして機能する(例えば、特許文献1,2参照)。

#### [ 0 0 0 4 ]

このようなエージングデバイスによれば、例えば、トンネル絶縁膜の厚さを変えることにより、その寿命を変化させることができる。

#### [00005]

しかし、フローティングゲートからの電荷リークは、製造ばらつきにより変化するため、エージングデバイスを正確な電子タイマーとして機能させるには、その製造ばらつきによる誤差をなくすための複雑な回路が必要になる。

# [0006]

また、エージングデバイスが使用される分野が広がるにつれて、それぞれのビジネスモデルに対応するようにその寿命を設定しなければならない。これは、エージングデバイスの製造ラインを、その寿命に対応させて複数設けなければならないことを意味するため、製造コストの増大を招く。

【特許文献1】特開2004-172404号公報

【特許文献2】特開2005-310824号公報

# 【発明の開示】

【発明が解決しようとする課題】

# [0007]

本発明の例では、エージングデバイスの寿命を、トンネル絶縁膜の厚さによらず、簡単な回路により変更できる半導体集積回路を提案する。

### 【課題を解決するための手段】

### [0008]

50

10

20

30

10

20

30

40

50

本発明の例に関わる半導体集積回路は、半導体基板と、半導体基板の表面領域に形成される素子分離絶縁層と、素子分離絶縁層により分離され、第1方向に直交する第2方向に隣接する第1及び第2素子領域内にそれぞれ形成される第1及び第2MIS型デバイスとを備え、第1及び第2MIS型デバイスは、それぞれ、フローティングゲート及びコントロールゲート電極を持つスタックゲート構造を有し、第1MIS型デバイスは、エージングデバイスとして機能し、第2MIS型デバイスは、エージングデバイスの電荷保持特性を制御する制御デバイスとして機能する。

### [0009]

本発明の例に関わる半導体集積回路は、半導体基板と、半導体基板の表面領域に形成される素子分離絶縁層と、素子分離絶縁層により取り囲まれる素子領域内に形成される第1 導電型の1つの拡散層と、拡散層上で第1方向に並んで形成される第1及び第2MIS型 デバイスと、拡散層の第1方向の2つの端部にそれぞれ1つずつ配置される2つのセレク トゲートトランジスタとを備え、第1及び第2MIS型デバイスは、それぞれ、フローティングゲート及びコントロールゲート電極を持つスタックゲート構造を有し、第1MIS 型デバイスは、エージングデバイスとして機能し、第2MIS型デバイスは、エージング デバイスの電荷保持特性を制御する制御デバイスとして機能する。

### 【発明の効果】

#### [ 0 0 1 0 ]

本発明の例によれば、エージングデバイスの寿命を、トンネル絶縁膜の厚さによらず、 簡単な回路により変更できる。

【発明を実施するための最良の形態】

#### [0011]

以下、図面を参照しながら、本発明の例を実施するための最良の形態について詳細に説明する。

# [0012]

# 1. 概要

本発明の例では、エージングデバイスの寿命を、トンネル絶縁膜の厚さではなく、エージングデバイスを挟み込む 2 つの制御デバイスにより制御する。

#### [0013]

エージングデバイス及び制御デバイスは、それぞれ、MIS型デバイスから構成し、フローティングゲート及びコントロールゲート電極を有するスタックゲート構造とする。

# [0014]

この場合、エージングデバイスのフローティングゲートと制御デバイスのフローティングゲートとの間には寄生容量が発生するため、制御デバイスのフローティングゲート内に注入する電荷量に応じて、エージングデバイスの寿命を制御できる。

#### [0015]

即ち、制御デバイスのフローティングゲート内の電荷量が多ければ、エージングデバイスのフローティングゲート内の電荷が抜ける時間が短くなり、エージングデバイスの寿命が短くなる。

### [0016]

反対に、制御デバイスのフローティングゲート内の電荷量が少なければ、エージングデバイスの寿命が長くなる。

# [0017]

このような構成により、エージングデバイスの寿命を、トンネル絶縁膜の厚さによらず 、簡単な回路により変更できるようになる。

# [0018]

ここで、制御デバイスについては、フラッシュメモリのメモリセルのように、フローティングゲート内の電荷のリークが発生し難い構造とする。

### [0019]

例えば、エージングデバイスのチャネルと制御デバイスの拡散層とを同一導電型(n/p)

の不純物で形成する。

- [0020]

- 2. 実施の形態

- (1) エージングデバイス

まず、エージングデバイスについて説明する。

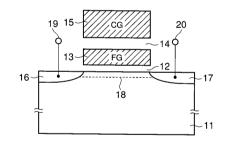

[ 0 0 2 1 ]

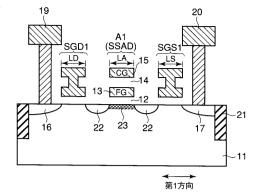

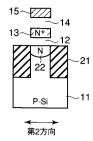

図1は、エージングデバイスの基本ユニットの例を示している。

[0022]

エージングデバイスの基本ユニットは、スタックゲート構造を有するMIS型デバイスから構成される。即ち、半導体基板11上には、トンネル絶縁膜12を介してフローティングゲート13が形成される。また、フローティングゲート13上には、電極間絶縁層14を介してコントロールゲート電極15が形成される。

[0023]

本例では、エージングデバイスの基本ユニットは、MISFETを構成している。具体的には、半導体基板11内には、ドレイン拡散層16とソース拡散層17が形成され、これらの間のチャネル領域18の上部には、フローティングゲート13が形成される。

[0024]

尚、基本ユニットは、必ずしもMISFETである必要はない。

[0025]

このようなエージングデバイスの基本ユニットに対する書き込み(初期設定)は、フラッシュメモリにおける技術を利用する。例えば、コントロールゲート電極15の電位をチャネル領域18の電位よりも十分に高い値に設定することにより、FN(Fowler-Nordheim)トンネリングを利用して、電子をチャネル領域18からフローティングゲート15内に注入する。

[0026]

ここで、エージングデバイスは、フローティングゲート 1 3 内に蓄積された電荷量の経時変化、即ち、電荷リークによりチャネル領域 1 8 の電位が変化する現象を利用して一定期間を計測する。つまり、この経時変化が、ドレイン電極 1 9 とソース電極 2 0 との間に流れる電流(ドレイン電流 I d )を経時変化(エージング)させる。

[0027]

従って、フローティングゲート13内の電荷の保持量を正確に制御することが重要である。

[0028]

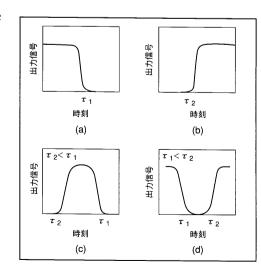

図2は、エージングデバイスの4つの基本機能を示している。

[0029]

同図(a)は、エージングデバイスの寿命( 1)に到達すると、それまであった出力信号が消滅するものである。ここで、エージングデバイスの寿命とは、書き込み(初期設定)から電荷リークにより出力信号が変化するまでの期間のことであり、電荷保持特性に依存する。

[0030]

同図(b)は、エージングデバイスの寿命( 2)に到達すると、それまでなかった出力信号が発生するものである。

[0031]

同図(c)は、エージングデバイスの第1寿命(2)に到達すると、それまでなかった出力信号が発生し、第2寿命(1)に到達すると、それまであった出力信号が消滅するものである。

[0032]

ここで分かることは、電荷リークにより出力信号が変化する時点は1つに制限されないことである。つまり、例えば、複数の基本ユニットを組み合わせてエージングデバイスを構成することによりエージングデバイスに複数の寿命を持たせることもできる。

10

20

30

40

#### [ 0 0 3 3 ]

同図(d)は、エージングデバイスの第1寿命(1)に到達すると、それまであった 出力信号が消滅し、第2寿命(2)に到達すると、それまでなかった出力信号が発生す るものである。

# [0034]

ここで、出力信号の消滅とは、急減衰のことである。

エージングデバイスにより一定期間を計測するメカニズムは、表1に示すように、基本 ユニットで考えると4通り存在する。

### 【表1】

表 1

|     | 「忘れる」   | の実現方法   | 「思い出す」の実現方法 |         |  |

|-----|---------|---------|-------------|---------|--|

|     | pMOSFET | nMOSFET | pMOSFET     | nMOSFET |  |

| タイプ | ノーマ     | リオフ     | ノーマリオン      |         |  |

| 動作  | オン → オフ |         | オフ → オン     |         |  |

| 電荷  | 電子      | 正孔      | 正孔          | 電子      |  |

#### [0036]

ノーマリオン型は、「思い出す」という機能を実現し、ノーマリオフ型は、「忘れる」 という機能を実現する。

### [0037]

ノーマリオフ型の場合、まず、書き込み(初期設定)により、フローティングゲート内 に電子(pチャネルMOSFET)又は正孔(nチャネルMOSFET)を蓄積し、トラ ンジスタ(基本ユニット)をオンにする。

#### [0038]

書 き 込 み 時 か ら 時 間 が 経 過 す る に つ れ て フ ロ ー テ ィ ン グ ゲ ー ト 内 の 電 子 又 は 正 孔 が リ ー クし、ある時点で、トランジスタは、オンからオフに変化する。この時、出力信号は、図 2 ( a ) に示すようになる。

### [0039]

ノーマリオン型の場合、まず、書き込み(初期設定)により、フローティングゲート内 に電子(nチャネルMOSFET)又は正孔(pチャネルMOSFET)を蓄積し、トラ ンジスタ(基本ユニット)をオフにする。

# [0040]

書 き 込 み 時 か ら 時 間 が 経 過 す る に つ れ て フ ロ ー テ ィ ン グ ゲ ー ト 内 の 電 子 又 は 正 孔 が リ ー クし、ある時点で、トランジスタは、オフからオンに変化する。この時、出力信号は、図 2 (b) に示すようになる。

# [0041]

ところで、図2(c)の機能は、短い寿命のノーマリオン型基本ユニットと長い寿命の ノーマリオフ型基本ユニットを直列接続することにより実現できる。また、図2(d)の 機 能 は 、 短 い 寿 命 の ノ ー マ リ オ フ 型 基 本 ユ ニ ッ ト と 長 い 寿 命 の ノ ー マ リ オ ン 型 基 本 ユ ニ ッ トを並列接続することにより実現できる。

# [0042]

(2) 第1実施の形態

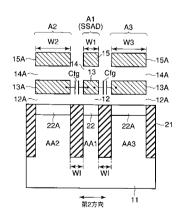

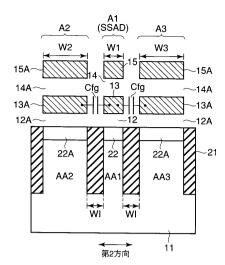

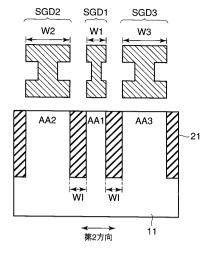

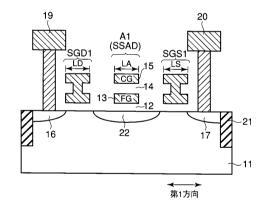

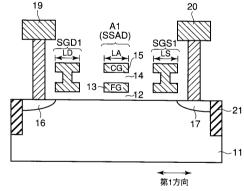

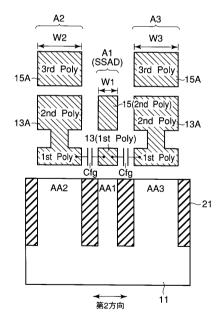

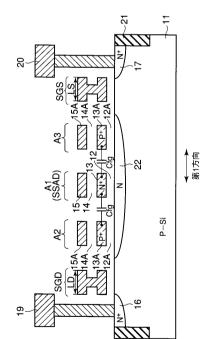

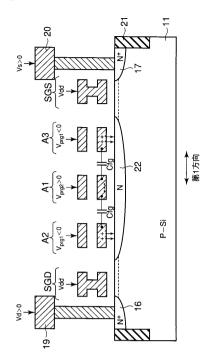

図3は、第1実施の形態に関わる半導体集積回路の平面図を示している。

#### [ 0 0 4 3 ]

図4は、図3のIV-IV線に沿う断面図、図5は、図3のV-V線に沿う断面図、図

20

10

30

40

6 は、図3のVI - VI線に沿う断面図、図7は、図3のVII - VII線に沿う断面図である。

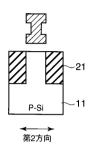

[0044]

半導体基板 1 1 内には、STI (shallow trench isolation)構造の素子分離絶縁層 2 1が形成される。第 1、第 2 及び第 3 素子領域(アクティブエリア) A A 1 , A A 2 , A A 3 は、素子分離絶縁層 2 1 により分離され、第 1 方向に直交する第 2 方向に互いに隣接して配置される。

[0045]

第 1 素子領域 A A 1 の第 2 方向の幅 W 1 は、第 2 及び第 3 素子領域 A A 2 , A A 3 の第 2 方向の幅 W 2 , W 3 よりも狭くなるようにレイアウトされる。

[0046]

第 1 素子領域 A A 1 内には、エージングデバイスとして機能する第 1 M I S 型デバイス A 1 (SSAD: solid state aging device)及びこれを挟み込む 2 つのセレクトゲートトランジスタ S G D 1 , S G S 1 が配置される。第 1 M I S 型デバイス A 1 及び 2 つのセレクトゲートトランジスタ S G D 1 , S G S 1 は、直列接続される。

[0047]

第 1 M I S 型デバイス A 1 は、スタックゲート構造を有する。即ち、半導体基板 1 1 上には、トンネル絶縁膜 1 2 を介してフローティングゲート(F G ) 1 3 が形成され、フローティングゲート 1 3 上には、電極間絶縁層 1 4 を介してコントロールゲート電極(C G ) 1 5 が形成される。

[ 0 0 4 8 ]

フローティングゲート 1 3 の第 2 方向の幅 W 1 は、フローティングゲート 1 3 の第 1 方向の長さ L A よりも短くなるようにレイアウトされる。

[0049]

第1MIS型デバイスA1の直下の半導体基板11内には、拡散層22が形成される。

[0050]

セレクトゲートトランジスタSGD1のドレイン拡散層16は、コンタクトプラグを介してドレイン電極19に接続される。セレクトゲートトランジスタSGS1のソース拡散層17は、コンタクトプラグを介してソース電極20に接続される。

[0051]

セレクトゲートトランジスタSGD1,SGS1のゲート電極の第2方向の幅W1は、セレクトゲートトランジスタSGD1,SGS1のゲート電極の第1方向の長さLD,LSよりも短くなるようにレイアウトされる。

[0052]

第2素子領域AA2内には、制御デバイスとして機能する第2MIS型デバイスA2及びこれを挟み込む2つのセレクトゲートトランジスタSGD2,SGS2が配置される。第2MIS型デバイスA2及び2つのセレクトゲートトランジスタSGD2,SGS2は、直列接続される。

[0053]

第2 M I S 型デバイス A 2 は、第1 M I S 型デバイス A 1 と同様に、スタックゲート構造を有する。即ち、半導体基板 1 1 上には、トンネル絶縁膜 1 2 A を介してフローティングゲート(F G) 1 3 A が形成され、フローティングゲート 1 3 A 上には、電極間絶縁層 1 4 A を介してコントロールゲート電極(C G) 1 5 A が形成される。

[ 0 0 5 4 ]

フローティングゲート 1 3 A の第 2 方向の幅W 2 は、フローティングゲート 1 3 A の第 1 方向の長さ L A よりも長くなるようにレイアウトされる。

[0055]

第2MIS型デバイスA2の直下の半導体基板11内には、拡散層22Aが形成される

[0056]

30

10

20

40

10

20

30

40

50

セレクトゲートトランジスタSGD2のドレイン拡散層16Aは、コンタクトプラグを介してドレイン電極19Aに接続される。セレクトゲートトランジスタSGS2のソース拡散層17Aは、コンタクトプラグを介してソース電極20Aに接続される。

[0057]

第3素子領域AA3内には、制御デバイスとして機能する第3MIS型デバイスA3及びこれを挟み込む2つのセレクトゲートトランジスタSGD3,SGS3が配置される。 第3MIS型デバイスA3及び2つのセレクトゲートトランジスタSGD3,SGS3は、直列接続される。

[0058]

第3MIS型デバイスA3の構造は、第2MIS型デバイスA2と同じであり、また、第3MIS型デバイスA3を挟み込む2つのセレクトゲートトランジスタSGD3,SGS3の構造は、第2MIS型デバイスA2を挟み込む2つのセレクトゲートトランジスタSGD2,SGS2の構造と同じであるため、ここでは、その説明を省略する。

[0059]

このような半導体集積回路において、第1、第2及び第3MIS型デバイスA1,A2 ,A3のコントロールゲート電極(CG)15,15Aは、それぞれ独立に制御される。

[0060]

また、第1及び第2素子領域AA1,AA2間の素子分離絶縁層21の第2方向の幅W Iは、セレクトゲートトランジスタSGD1,SGS1,SGD2,SGS2のうちの1つのゲート電極から第1及び第2MIS型デバイスA1,A2のフローティングゲート(FG)13,13Aまでの第1方向の幅Wsよりも狭くなるようにレイアウトされる。

[0061]

同様に、第1及び第3素子領域AA1,AA3間の素子分離絶縁層21の第2方向の幅WIについても、セレクトゲートトランジスタSGD1,SGS1,SGD3,SGS3のうちの1つのゲート電極から第1及び第3MIS型デバイスA1,A3のフローティングゲート(FG)13,13Aまでの第1方向の幅Wsよりも狭くなるようにレイアウトされる。

[0062]

第 1 、 第 2 及 び 第 3 M I S 型 デ バ イ ス A 1 , A 2 , A 3 の フ ロ ー テ ィ ン グ ゲ ー ト ( F G ) 1 3 , 1 3 A の 第 1 方 向 の 長 さ L A は 、 互 い に 等 し く な る よ う に レ イ ア ウ ト さ れ 、 セ レ ク ト ゲ ー ト ト ラ ン ジ ス タ S G D 1 , S G S 1 , S G D 2 , S G S 2 , S G D 3 , S G S 3 の ゲ ー ト 電 極 の 第 1 方 向 の 長 さ L D , L S は 、 互 い に 等 し く な る よ う に レ イ ア ウ ト さ れ る

[0063]

セレクトゲートトランジスタSGD1,SGS1,SGD2,SGS2,SGD3,SGS3は、第1、第2及び第3MIS型デバイスA1,A2,A3と同様に、スタックゲート構造を有するが、上側のゲート電極と下側のゲート電極とが導電プラグにより互いに接続される。

[0064]

このような半導体集積回路は、フラッシュメモリの製造プロセスを利用して容易に形成することができる。但し、第1、第2及び第3MIS型デバイスA1,A2,A3のコントロールゲート電極(CG)15,15Aを互いに分離する必要があるため、マスクパターンの変更が必要である。

[0065]

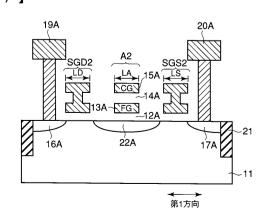

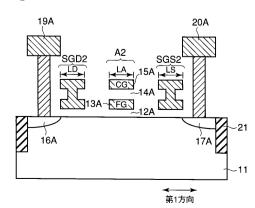

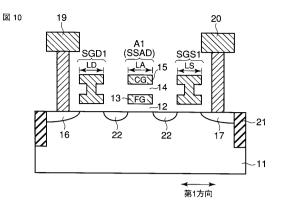

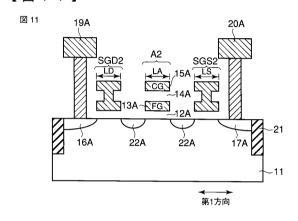

図6及び図7の半導体集積回路では、MIS型デバイスA1,A2,A3は、MISFETになっていないが、例えば、図10及び図11に示すように、MISFETとすることも可能である。

[0066]

図 8 及び図 9 は、図 1 0 及び図 1 1 の拡散層 2 2 , 2 2 A を除いたものである。これでも、エージングデバイスとしての所定の機能を実現できる。

#### [0067]

図 1 0 及び図 1 1 は、図 6 及び図 7 に対応する第 1 方向の断面図である。第 2 方向の断面図は、図 4 及び図 5 と同じなので、ここでは、省略する。

#### [0068]

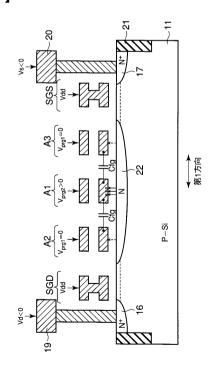

B. 動作

図 3 乃至図 7 の半導体集積回路では、制御デバイスとしての M I S 型デバイス A 2 , A 3 を用いて、 M I S 型デバイス ( エージングデバイス ) A 1 の寿命を制御する。この制御とは、フローティングゲート 1 3 , 1 3 A 間の容量カップリング C f g を利用する、というものである。

### [0069]

フローティングゲート 1 3 からのリーク電流は、フローティングゲート 1 3 の自己電位によって決まる。一方、容量カップリング C f g を利用することで、制御デバイス A 2 , A 3 のフローティングゲート 1 3 A がエージングデバイスのフローティングゲート 1 3 の自己電位を制御することができる。

# [0070]

従って、制御デバイスとしてのMIS型デバイスA2,A3のフローティングゲート13A内の電荷量を調節して、フローティングゲート13Aの自己電位を操作すれば、エージングデバイスA1のフローティングゲート13からの電荷のリーク量を制御できる。

#### [0071]

制御デバイス A 2 , A 3 によるエージングデバイス A 1 の寿命の制御性を向上するには、容量カップリング C f g を十分に強くしておく必要がある。

#### [0072]

その方法は、いくつか考えられるが、代表的なものを3つ挙げておく。

i) 素子分離絶縁層(例えば、STI)21の第2方向の幅WIをできるだけ狭くする。これは、フローティングゲート13,13A間の距離を短くして容量カップリング Cfgを強くすることを目的としたものである。

### [0073]

ii) エージングデバイスA1のフローティングゲート13のゲート長(第1方向の長さ)LAをできるだけ長くする。これは、フローティングゲート13,13Aが対向する面積を大きくして容量カップリングCfgを強くすることを目的としたものである。

### [0074]

iii) フローティングゲート13,13A間に高い誘電率を持つ絶縁層を配置する。これは、フローティングゲート13,13A間の絶縁層の比誘電率を高くして容量カップリングCfgを強くすることを目的としたものである。

# [0075]

このうち、iii)を採用する場合には、他の領域(例えば、メモリセル)のプロセスとの整合性を損なう可能性がある。従って、いずれを採用するかは、周辺事情を考慮し、例えば、i)~iii)のうち、必要と思われるものを適宜選択して採用することが重要である。

# [0076]

書き込み(初期設定)は、フラッシュメモリと同様に、MIS型デバイスA1,A2,A3のフローティングゲート13,13A内に電荷を注入することにより行う。

#### [0077]

例えば、FNトンネリングにより、制御デバイスA2,A3のフローティングゲート1 3A内に電荷を注入した後、エージングデバイスA1のフローティングゲート13内に電荷を注入する。

# [0078]

制御デバイスA2,A3に対する書き込みは、例えば、電子を注入する場合には、ドレイン側セレクトゲートトランジスタSGD2,SGD3及びソース側セレクトゲートトランジスタSGS2,SGS3のうちの少なくとも1つをオンにし、拡散層22Aにソース又はドレインの接地電位を転送し、コントロールゲート電極15Aにプラスの書き込み電

10

20

30

40

位を与えることにより行う。

[0079]

制御デバイスA2,A3に対する書き込みは、両者を同時に行ってもよいし、別々に行ってもよい。

[0800]

エージングデバイスA1に対する書き込みは、例えば、電子を注入する場合には、ドレイン側セレクトゲートトランジスタSGD1及びソース側セレクトゲートトランジスタSGS1のうちの少なくとも1つをオンにし、拡散層22にソース又はドレインの接地電位を転送し、コントロールゲート電極15にプラスの書き込み電位を与えることにより行う

[0081]

書き込みについては、フローティングゲート 1 3 , 1 3 A 内に注入する電荷量をベリファイ(verify)技術により制御できる。

[0082]

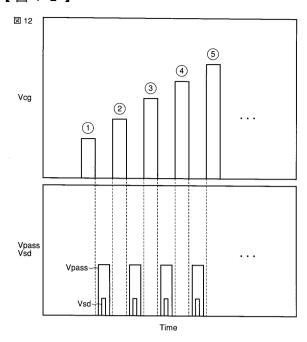

図 1 2 は、書き込み電位 V c g を次第に大きくし、フローティングゲート 1 3 , 1 3 A 内に注入する電荷量を制御する技術である。

[0083]

コントロールゲート電極 1 5 , 1 5 A には、大きさが段階的に変化する矩形パルス 1 , 2 , 3 , 4 , 5 , ・・・が一定間隔で印加される。

[0084]

矩形パルス1,2,3,4,5,・・・の間のインターバルには、読み出しを行うため、セレクトゲートトランジスタSGD1,SGS1,SGD2,SGS2,SGD3,SGS3をオンにするための電圧Vpassを印加する。但し、Vpassは、一般にVcgよりも小さい。このVpassが印加されている間に、読み出しパルスVsdがソース及びドレイン間に印加される。

[0085]

読み出しデータに応じて、フローティングゲート13,13A内に注入された電荷量を 把握できるため、正確な電荷量の制御が可能になる。

[0086]

読み出しデータが期待値に到達していない場合には、期待値になるまで、書き込みのための矩形パルス(Vcg) 1 , 2 , 3 , 4 , 5 ,・・・をコントロールゲート電極 1 5 , 1 5 A に与えると共に、 V passをセレクトゲートトランジスタ S G D 1 , S G S 1 , S G D 2 , S G S 2 , S G D 3 , S G S 3 のゲート電極に与える。

[0087]

Vpassを印加している間に、読み出し電圧 Vsdをソース及びドレイン間に印加する。この例では、MIS型デバイスA2,A3に対して書き込みを行った後に、MIS型デバイスA1に対する書き込みを実行する。しかし、この順序を逆にしても、同様の効果を得ることができる。

[0088]

読み出しデータが期待値になったときは、書き込みを終了する。

[0089]

この例では、矩形パルス1,2,3,4,5,・・・が大きくなり過ぎないように、最大値を設定しておくことが重要である。矩形パルス1,2,3,4,5,・・・の大きさが最大値に到達したときに、読み出しデータが期待値になっていないときは、全てをリセットした後、再び、書き込みを行うか、又は、書き込み不良とする。

[0090]

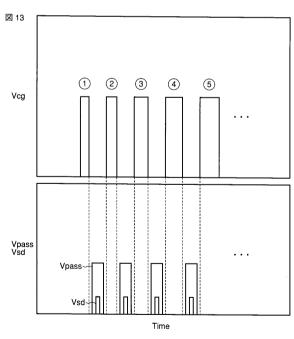

ベリファイ技術としては、図12以外にも、図13に示すように、書き込み電位Vcgの幅を次第に広くしていく技術がある。この場合、コントロールゲート電極15,15Aには、幅が段階的に変化する矩形パルス1,2,3,4,5,・・・が一定間隔で印加される。

10

20

30

40

10

20

30

40

50

[0091]

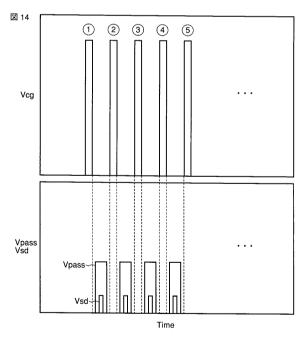

また、図14に示すように、書き込み電位Vcgの大きさ及び幅が一定の矩形パルス1,2,3,4,5,・・・を一定間隔でコントロールゲート電極15,15Aに印加してもよい。

[0092]

このように、ベリファイ技術を利用することにより、エージングデバイス A 1 及び制御デバイス A 2 , A 3 の双方に対して、フローティングゲート 1 3 , 1 3 A 内に注入する電荷量を正確に制御できる。

[0093]

従って、制御デバイスの制御性を向上できると共に、エージングデバイスの寿命の誤差 も小さくできる。

- [0094]

- C. 寿命の制御性

エージングデバイスの寿命の制御性を向上させるには、制御デバイスの寿命をエージングデバイスの寿命よりも長くすることが必要である。

[0095]

そのためには、制御デバイスのトンネル絶縁膜の厚さをエージングデバイスのトンネル 絶縁膜の厚さよりも大きくしてもよいが、成膜プロセスの複雑化を避けるため、制御デバ イスとエージングデバイスのトンネル絶縁膜の厚さについては、互いに同じにし、以下の 構成を採用することが有効な手段である。

[0096]

制御デバイスのフローティングゲートの体積をエージングデバイスのフローティングゲートの体積よりも大きくする。

[0097]

・制御デバイスのフローティングゲート内の不純物の導電型とその直下の半導体基板内 の拡散層の不純物の導電型とを異ならせ、エージングデバイスのフローティングゲート内 の不純物の導電型とその直下の半導体基板内の拡散層の不純物の導電型とを同じにする。

[0098]

前者は自明なので、後者の手段が有効である理由について述べる。

[0099]

エージングデバイス及び制御デバイスのそれぞれの寿命は、フローティングゲートから の電荷のリーク量により決定される。

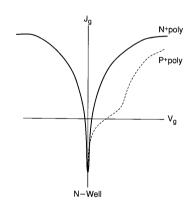

[0100]

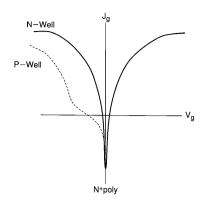

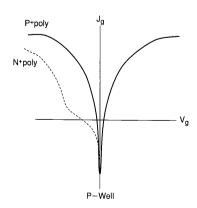

図15及び図16は、ウェル領域、フローティングゲート及びこれらの間の酸化層からなるMOSキャパシタのJV特性を示している。

[0101]

図 1 5 の例では、フローティングゲートは、 N 型ポリシリコン(N+poly)から構成され、図 1 6 の例では、フローティングゲートは、 P 型ポリシリコン(P+poly)から構成される。

[0102]

これらの図から分かることは、ウェル領域内の不純物の導電型とフローティングゲート 内の不純物の導電型が異なるときは、両者が同じときよりも、リーク電流 Jg が小さくなる、ということである。

[0103]

例えば、ゲート電位 V g が負の場合、 P 型ウェル領域 (P-WeII) と N 型ポリシリコン (N+poly) のペアで M O S キャパシタを構成するときは、 N 型ウェル領域 (N-WeII) と N 型ポリシリコン (N+poly) のペアで M O S キャパシタを構成するときよりも、 リーク電流が小さくなる。

[0104]

また、ゲート電位Vgが正の場合、N型ウェル領域(N-Well)とP型ポリシリコン(P+poly)のペアでMOSキャパシタを構成するときは、P型ウェル領域(P-Well)とP型ポリシリ

10

20

30

40

50

コン (P+poly) のペアで M O S キャパシタを構成するときよりも、 リーク電流が小さくなる

[0105]

図 6 及び図 7 の構造を例にとると、拡散層 2 2 , 2 2 A を N 型とすると、エージングデバイス A 1 のフローティングゲート 1 3 は、 N 型ポリシリコン層から構成し、また、制御デバイス A 2 , A 3 のフローティングゲート 1 3 A は、 P 型ポリシリコン層から構成する

[0106]

同様に、拡散層 2 2 , 2 2 A を P 型とすると、エージングデバイス A 1 のフローティングゲート 1 3 は、 P 型ポリシリコン層から構成し、また、制御デバイス A 2 , A 3 のフローティングゲート 1 3 A は、 N 型ポリシリコン層から構成する。

[0107]

ここで、図 6 及び図 7 の構造では、エージングデバイス A 1 のフローティングゲート 1 3 の導電型と制御デバイス A 2 , A 3 のフローティングゲート 1 3 A の導電型とが互いに異なることになる。

[0108]

そこで、制御デバイスA2,A3のフローティングゲート13A直下の拡散層22Aを 省略して、図9に示すような構造にするか、若しくは、図11のように、FETにすれば 、フローティングゲート13,13Aの導電型を同じにすることもできる。

[0109]

この場合、半導体基板が P 型、拡散層 2 2 が N 型であるとすると、エージングデバイス A 1 のフローティングゲート 1 3 及び制御デバイス A 2 , A 3 のフローティングゲート 1 3 A は、それぞれ、N 型ポリシリコン層から構成する。

[0110]

このようにすれば、書き込み時、例えば、コントロールゲート電極15,15Aには、共に、正の電位を与え、電子をフローティングゲート13,13A内に注入できる。電子注入後の状態は、図15のVg<0となる。

[0111]

また、半導体基板がN型、拡散層 2 2 が P 型であるとすると、エージングデバイス A 1 のフローティングゲート 1 3 及び制御デバイス A 2 , A 3 のフローティングゲート 1 3 A は、それぞれ、 P 型ポリシリコン層から構成する。

[0112]

このようにすれば、書き込み時、例えば、コントロールゲート電極 1 5 , 1 5 A には、共に、負の電位を与え、正孔をフローティングゲート 1 3 , 1 3 A 内に注入できる。正孔注入後の状態は、図 1 6 の V g > 0 となる。

[0113]

尚、図8に示すように、図6の拡散層22を省略することもできる。

- [0114]

- D. エージングデバイスのタイプ

図3万至図7におけるMIS型デバイスは、エンハンスメント型であり、この場合、エージングデバイスとしては、表1におけるノーマリオン型となる。

[0115]

ノーマリオフ型のエージングデバイスを実現するには、 MIS型デバイスをディプレッション型にする必要があるが、この場合、リーク電流が大きくなり過ぎる危険性がある。

[0116]

そこで、例えば、ディプレッション型である図10及び図11の構造において、MIS型デバイス(MISFET)のチャネル領域に不純物をドーピングし、チャネル領域の不純物濃度を薄くするカウンタードーピング技術を採用する。

[0117]

即ち、図17に示すように、エージングデバイスA1(SSAD)のチャネル領域に不純物を

ドーピングし、カウンタードーピング領域23とする。

### [0118]

この場合、図15及び図16で示したN型ウェル領域(N-Well)とP型ウェル領域(P-Well)との電位差がやや小さくなるが、上述と同様の効果が得られる。

### [0119]

もう一つの方法は、図18に示すように、制御デバイスA2,A3のフローティングゲート13Aの体積を、エージングデバイスA1のフローティングゲート13の体積よりもできるだけ大きくすることにより、リーク電流差(寿命の差)を十分に確保することができる。

### [0120]

図 1 8 の構造は、カウンタードーピング技術との相性が良いが、エージングデバイスの寿命の制御性を高めるという意味では、カウンタードーピング技術と併用しなくてもよい

# [0121]

また、図18の構造は、フラッシュメモリの製造技術を応用することにより容易に得る ことができる。

# [0122]

例えば、第 1 、第 2 及び第 3 導電性ポリシリコン層(1st Poly/2nd Poly/3rd Poly)をスタックした後、これら第 1 、第 2 及び第 3 導電性ポリシリコン層をパターニングすればよい。

#### [ 0 1 2 3 ]

ここで、第1素子領域AA1上の第1及び第2導電性ポリシリコン層は、それぞれ、フローティングゲート13及びコントロールゲート電極15となる。また、第2及び第3素子領域AA2,AA3上の第1及び第2導電性ポリシリコン層は、プラグにより結合され、フローティングゲート13Aとなり、第3導電性ポリシリコン層は、コントロールゲート電極15Aとなる。

#### [0124]

ノーマリオフ型エージングデバイスは、図10及び図11の構造において容易に実現することができる。

# [0125]

図 1 9 は、図 1 0 のエージングデバイス A 1 をノーマリオフ型として使用するもう一つの場合の構造を示している。

#### [0126]

半導体基板 1 1 は、 P 型、ウェル領域 2 4 は、 N 型、拡散層 1 6 , 1 7 , 2 2 は、それぞれ P 型とする。また、フローティングゲート 1 3 及びコントロールゲート電極 1 5 は、 N 型の導電性ポリシリコン層から構成する。

### [0127]

この場合、例えば、チャネル領域に接地電位を印加し、コントロールゲート電極15に正の書き込み電位を印加すると、FNトンネリングにより、電子がチャネル領域からフローティングゲート13内に注入される。

# [0128]

フローティングゲート 1 3 内に電子が注入された状態では、MIS型デバイス(MIS FET) A 1 のチャネル領域は、N型からP型に反転するため、MIS型デバイス A 1 と しては、オン状態である。

# [0129]

そして、フローティングゲート13内の電子は、時間の経過と共に放出され、ある時点で、MIS型デバイスA1のチャネル領域は、P型からN型に戻り、MIS型デバイスA1としては、オフ状態になる。

### [0130]

このオフになった時点が寿命である。

10

20

30

40

10

20

30

40

50

[0131]

このように、図19の構造を用いて、ノーマリオフ型エージングデバイスを実現できる

[0132]

尚、図19の構造において、半導体基板11をN型、ウェル領域24をP型、拡散層16,17,22をN型とし、フローティングゲート13及びコントロールゲート電極15をP型の導電性ポリシリコン層から構成しても、ノーマリオフ型エージングデバイスを実現できる。

[0133]

この場合、書き込み(初期設定)は、例えば、チャネル領域に接地電位を印加し、コントロールゲート電極15に負の書き込み電位を印加し、正孔をフローティングゲート13内に注入することにより行う。

[ 0 1 3 4 ]

フローティングゲート13内に正孔が注入された状態では、MIS型デバイス(MISFET)A1のチャネル領域は、P型からN型に反転するため、MIS型デバイスA1としては、オン状態である。

[0135]

そして、フローティングゲート13内の正孔は、時間の経過と共に放出され、ある時点で、エージングデバイスA1のチャネル領域は、N型からP型に戻り、エージングデバイスA1としては、オフ状態になる。

[0136]

以上、ノーマリオン型エージングデバイスとノーマリオフ型エージングデバイスとを実現できたので、この 2 種類のエージングデバイスを組み合わせて、表 1 に示す 4 つの機能を実現できる。

[ 0 1 3 7 ]

E. その他

ベリファイ読み出しについて、図6及び図7のノーマリオン型エージングデバイスを例に説明する。

[0138]

半導体基板 1 1 は、N型、拡散層 1 6 , 1 7 , 2 2 は、P型とし、フローティングゲート 1 3 及びコントロールゲート電極 1 5 は、P型の導電性ポリシリコン層とする。

[0139]

まず、コントロールゲート電極15に書き込み電位を印加しない状態で、セレクトゲートトランジスタSGD1,SGS1のゲート電極に負電位を印加し、これらをオン状態にする。この時、エージングデバイスの状態(フローティングゲート13内の電荷量)に応じて、ドレイン拡散層16とソース拡散層17の間に流れる電流(ドレイン電流)が変わるため、これをセンスアンプにより検出する。

[0140]

尚、コントロールゲート電極15に書き込みパルスを印加しているときは、例えば、チャネル領域を接地電位にしておかなければならないため、セレクトゲートトランジスタSGD1,SGS1の少なくとも1つをオンにし、接地電位をチャネル領域に転送する。

[0141]

また、ベリファイについては、制御デバイス及びエージングデバイスに対する書き込みが完了した後に、さらに、寿命の調整のために繰り返し行ってもよい。

[ 0 1 4 2 ]

制御デバイス内のフローティングゲート内に注入される電荷量が多ければ多いほど、エージングデバイスの寿命は短くなるため、制御デバイスとエージングデバイスのトンネル 絶縁膜の厚さが同じであっても、エージングデバイスの寿命の制御が可能になる。

[ 0 1 4 3 ]

エージングデバイスのリーク特性の製造ばらつきについては、出荷前に、リーク特性を

検査し、その結果に応じて、制御デバイスに対する書き込み(電荷の注入)方法の条件を 決定することが可能である。

### [0144]

この方法を採用すると、同じラインで製造したエージングデバイスでも、制御デバイスのフローティングゲート内に注入する電荷量を変えることにより、異なる寿命を持つ複数のエージングデバイスを提供できるようになる。

#### [ 0 1 4 5 ]

従って、ユーザは、その目的に応じ、上述の条件を用いてエージングデバイスの寿命を 設定できるようになると共に、製造ばらつきによる寿命誤差も抑制できる。

### [0146]

また、エージングデバイス搭載製品を購入したエンドユーザは、このような事情を知ることなく、製品提供者が設定した期間のみ、製品の使用が可能となる。つまり、エンドユーザが製品をネットワークに接続しようが、外部電源から切断しようが、この使用期間外で製品を使用することが不可能になる。

### [0147]

(3) 第2実施の形態

A. 構造

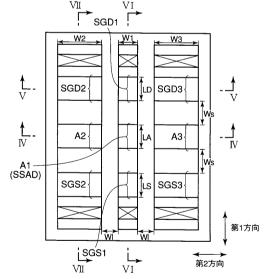

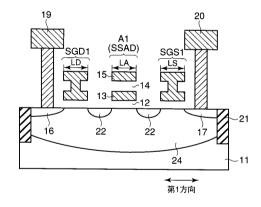

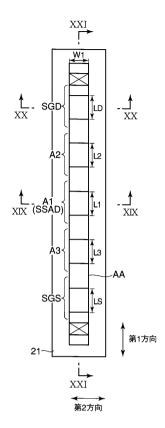

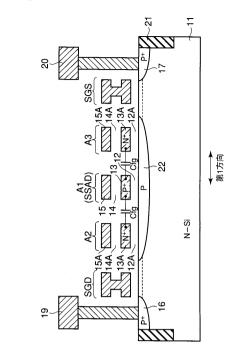

図20は、第2実施の形態に関わる半導体集積回路の平面図を示している。

#### [ 0 1 4 8 ]

図 2 1 は、図 2 0 の X I X - X I X 線に沿う断面図、図 2 2 は、図 2 0 の X X - X X 線に沿う断面図、図 2 3 は、図 2 0 の X X I - X X I 線に沿う断面図である。

#### [0149]

第1実施の形態では、制御デバイス/エージングデバイス/制御デバイスの列が素子分離絶縁層を介して形成されるが、第2実施の形態では、1つの素子領域内に、制御デバイス/エージングデバイス/制御デバイスの列が形成される。

### [0150]

半導体基板11内には、STI構造の素子分離絶縁層21が形成される。素子領域(アクティブエリア)AAは、素子分離絶縁層21に取り囲まれる。素子領域AAの第2方向の幅は、W1に設定される。

# [0151]

素子領域 A A 内には、エージングデバイスとして機能する第 1 M I S 型デバイス A 1 (S SAD) 及びこれを挟み込む制御デバイスとしての第 2 及び第 3 M I S 型デバイス A 2 , A 3 が配置される。また、素子領域 A A 内には、第 1 、第 2 及び第 3 M I S 型デバイス A 1 , A 2 , A 3 を挟み込む 2 つのセレクトゲートトランジスタ S G D , S G S が配置される。

# [0152]

第 1 、 第 2 及び第 3 M I S 型デバイス A 1 , A 2 , A 3 及び 2 つのセレクトゲートトランジスタ S G D , S G S は、直列接続される。

### [0153]

第1MIS型デバイスA1は、スタックゲート構造を有する。即ち、半導体基板11上には、トンネル絶縁膜12を介してフローティングゲート13が形成され、フローティングゲート13上には、電極間絶縁層14を介してコントロールゲート電極15が形成される。

### [0154]

フローティングゲート 1 3 の第 1 方向の長さは、 L 1 、第 2 方向の幅は、 W 1 に設定される。

# [0155]

第 2 及び第 3 M I S 型デバイス A 2 , A 3 は、第 1 M I S 型デバイス A 1 と同様に、スタックゲート構造を有する。即ち、図 2 3 に示すように、半導体基板 1 1 上には、トンネル絶縁膜 1 2 A を介してフローティングゲート 1 3 A 上には、電極間絶縁層 1 4 A を介してコントロールゲート電極 1 5 A が形成される

10

20

30

40

- -

[0156]

但し、トンネル絶縁膜12A及び電極間絶縁層14Aは、それぞれ、トンネル絶縁膜1 2及び電極間絶縁層14と共通であるのが望ましい。

[0157]

フローティングゲート 1 3 A の第 1 方向の長さは、 L 2 又は L 3 、第 2 方向の幅は、 W 1 に設定される。

[ 0 1 5 8 ]

拡散層22は、第1、第2及び第3MIS型デバイスA1,A2,A3の直下の半導体基板11内に形成される。

[0159]

セレクトゲートトランジスタSGDのドレイン拡散層16は、コンタクトプラグを介してドレイン電極19に接続される。セレクトゲートトランジスタSGSのソース拡散層1 7は、コンタクトプラグを介してソース電極20に接続される。

[0160]

セレクトゲートトランジスタSGD,SGSは、第1、第2及び第3MIS型デバイス A1,A2,A3と同様に、スタックゲート構造を有するが、上側のゲート電極と下側の ゲート電極とが導電プラグにより互いに接続される。

[0161]

このような半導体集積回路において、第1、第2及び第3MIS型デバイスA1,A2 ,A3のコントロールゲート電極15,15Aは、それぞれ独立に制御される。

[0162]

また、拡散層 2 2 及びフローティングゲート 1 3 は、同じ導電型に設定され、拡散層 2 2 及びフローティングゲート 1 3 A は、異なる導電型に設定される。本例では、半導体基板は、 P 型、拡散層 1 6 , 1 7 , 2 2 は、 N 型であるため、フローティングゲート 1 3 A は、 P <sup>+</sup> 型ポリシリコン層とする。

[0163]

さらに、フローティングゲート13,13A間に発生する容量カップリングCfgの強さが十分であれば、制御デバイスA2,A3に注入する電荷量を用いてエージングデバイスA1の寿命を制御できる。

[0164]

このような半導体集積回路は、第1実施の形態と同様に、フラッシュメモリの製造プロセスを利用して容易に形成することができる。但し、第1、第2及び第3MIS型デバイスA1,A2,A3のコントロールゲート電極15,15Aを互いに分離する必要があるため、マスクパターンの変更が必要である。

- [0165]

- B. 動作

第2実施の形態の特徴の一つは、エージングデバイスとしてのMIS型デバイスA1のフローティングゲートの導電型と、制御デバイスとしてのMIS型デバイスA2,A3のフローティングゲートの導電型とが異なる点にある。

[0166]

図20乃至図23の構造を例にとると、まず、制御デバイスに対する書き込み(初期設定)を行い、その後、エージングデバイスに対する書き込みを行うことが好ましい。これは、両方の書き込みを同時に行うことを避けるためであり、同時でなければ、順序は逆でも構わない。

[0167]

尚、各々の書き込みにおいては、第1実施の形態で述べたように、ベリファイ技術(図 12乃至図14)を採用し、エージングデバイスの寿命の制御を正確に行う。

[0168]

50

10

20

30

第2実施の形態では、エージングデバイス及び制御デバイスのうちのいずれか一方に対して書き込みを実行しているときに、他方に対しても、弱く書き込みが行われてしまう、という現象が生じる恐れがある。

[0169]

図24は、その一例を示している。

[0170]

エージングデバイスとしての第 1 M I S 型デバイス A 1 に対する書き込み時の様子である。

[0171]

第 1 M I S 型デバイス A 1 のコントロールゲート電極に書き込み電位 V prg2 (>0)を印加し、第 2 及び第 3 M I S 型デバイス A 2 , A 3 のコントロールゲート電極に接地電位 V s s (=0V)を印加し、セレクトゲートトランジスタ S G D , S G S のゲート電極に電源電位 V d d を印加する。

[0172]

また、ドレイン電極 1 9 及びソース電極 2 0 には、それぞれ、 0 V 未満の電位 V d , V s を印加する。

[0173]

この時、セレクトゲートトランジスタSGD,SGSは、オンになるため、0V未満の電位Vd,Vsが拡散層22に転送される。すると、第1MIS型デバイスA1のトンネル絶縁膜には、高電界がかかり、FNトンネリングにより、電子が拡散層22から第1MIS型デバイスA1のフローティングゲート内に注入される。

[0174]

同時に、第2及び第3MIS型デバイスA2,A3においても、そのフローティングゲート内に電子が弱く注入される。

[0175]

そこで、第1MIS型デバイスA1に対する書き込み動作後に、第2及び第3MIS型デバイスA2,A3に対して書き戻し動作を行う。

[0176]

図25は、書き戻し動作の例を示している。

[0177]

第 1 M I S 型デバイス A 1 のコントロールゲート電極に書き込み電位 V prg2 (>0)を印加した状態で、第 2 及び第 3 M I S 型デバイス A 2 , A 3 のコントロールゲート電極を、接地電位 V s s (=0V)から V prg1 (<0)に変える。また、ドレイン電極 1 9 及びソース電極 2 0 には、それぞれ、 0 V を超える電位 V d , V s を印加する。

[0178]

Vprq1、Vd及びVsの大きさは、書き戻しの程度に応じて最適な値に設定される。

[0179]

セレクトゲートトランジスタSGD, SGSのゲート電極については、電源電位Vdd のままとする。

[0180]

この時、セレクトゲートトランジスタSGD,SGSは、オンになるため、0Vを超える電位Vd,Vsが拡散層22に転送される。すると、第2及び第3MIS型デバイスA2,A3のトンネル絶縁膜には、高電界がかかり、FNトンネリングにより、電子が第2及び第3MIS型デバイスA2,A3のフローティングゲートから拡散層22内に放出される。

[0181]

図 2 0 乃至図 2 3 の構造では、各部分の導電型を逆にしても同様の効果を得ることができる。

[0182]

図26は、その例を示している。

10

20

30

[ 0 1 8 3 ]

半導体基板は、N型、拡散層 1 6 , 1 7 , 2 2 は、P型であり、フローティングゲート 1 3 は、P  $^{+}$ 型ポリシリコン層とし、フローティングゲート 1 3 A は、N  $^{+}$ 型ポリシリコン層とする。

[0184]

エージングデバイスとしての M I S 型デバイス A 1 の寿命は、フローティングゲート 1 3 , 1 3 A 間に発生する容量カップリング C f g の強さが十分であれば、制御デバイスとしての M I S 型デバイス A 2 , A 3 のフローティングゲート 1 3 A に注入した電荷量で調節できる。

[0185]

C. 寿命の制御性

第2実施の形態においても、制御デバイスの寿命は、エージングデバイスの寿命よりも 十分に長く、制御デバイスによるエージングデバイスの寿命の制御性が向上する。

[0186]

図27及び図28は、ウェル領域、フローティングゲート及びこれらの間の酸化層からなるMOSキャパシタのJV特性を示している。

[0187]

図 2 7 の例は、図 2 3 に示すように、拡散層 2 2 が N 型 (N-Well) である場合である。この場合、フローティングゲートが P 型ポリシリコン (P+poly) から構成されるときは、 N 型ポリシリコン (N+poly) から構成されるときよりも、リーク電流が減少する。

[ 0 1 8 8 ]

図 2 8 の例は、図 2 6 に示すように、拡散層 2 2 が P 型 (P-Well) である場合である。この場合、フローティングゲートが N 型ポリシリコン (N+poly) から構成されるときは、 P 型ポリシリコン (P+poly) から構成されるときよりも、リーク電流が減少する。

[0189]

つまり、いずれの場合においても、制御デバイスとしての第2及び第3MIS型デバイスA2,A3の寿命は、エージングデバイスとしての第1MIS型デバイスA1の寿命よりも長くなるため、エージングデバイスの寿命の制御性が向上する。

- [0190]

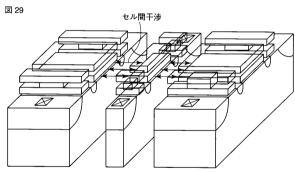

- (4) 第3実施の形態

第3実施の形態は、第1実施の形態の変形例である。

[0191]

エージングデバイスとしての性能を向上させるには、エージングデバイスと制御デバイスとの干渉を大きくすると共に、エージングデバイスとセレクトゲートトランジスタとの干渉を小さくすることが好ましい。

[0192]

第1実施の形態では、そのための手段の一つとして、図29に示すように、エージングデバイスとしての第1MIS型デバイスA1のフローティングゲートの第1方向の幅を第2方向の幅よりも広くする。

[0193]

これに対し、第3実施の形態では、エージングデバイスのフローティングゲートの第1 方向の両辺に窪みを設け、エージングデバイスと制御デバイスとの干渉を大きくすると共 に、エージングデバイスとセレクトゲートトランジスタとの干渉を小さくする。

[0194]

A. 構造

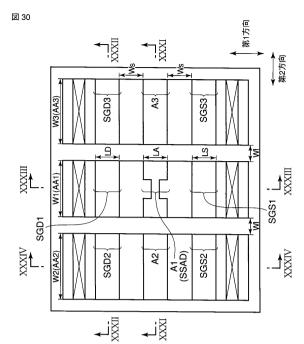

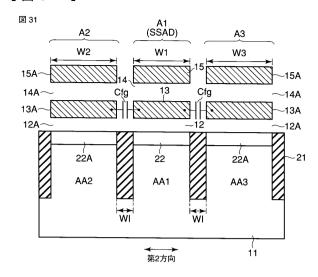

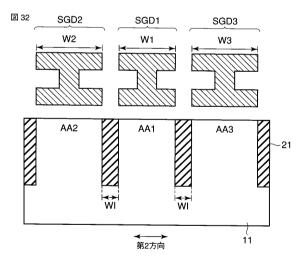

図30は、第3実施の形態に関わる半導体集積回路の平面図を示している。

[0195]

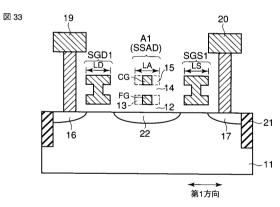

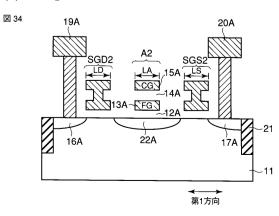

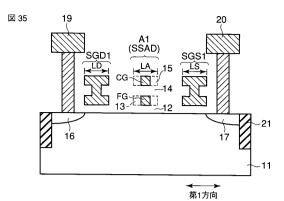

図 3 1 は、図 3 0 の X X X I - X X X I 線に沿う断面図、図 3 2 は、図 3 0 の X X X I I - X X X I I I 線に沿う断面図、図 3 3 は、図 3 0 の X X X I I I I - X X X I I I I 線に沿う断面図、図 3 4 は、図 3 0 の X X X I V - X X X I V 線に沿う断面図である。

10

20

30

40

[0196]

半導体基板11内には、STI構造の素子分離絶縁層21が形成される。第1、第2及 び 第 3 素 子 領 域 ( ア ク テ ィ ブ エ リ ア ) A A 1 , A A 2 , A A 3 は 、 素 子 分 離 絶 縁 層 2 1 に より分離され、第1方向に直交する第2方向に互いに隣接して配置される。

[0197]

第1素子領域AA1の第2方向の幅W1は、第2及び第3素子領域AA2,AA3の第 2 方向の幅W2,W3よりも狭い。

[0198]

第1素子領域AA1内には、エージングデバイスとして機能する第1MIS型デバイス A 1 (SSAD) 及びこれを挟み込む 2 つのセレクトゲートトランジスタSGD1,SGS1が 配置される。第1MIS型デバイスA1及び2つのセレクトゲートトランジスタSGD1 , S G S 1 は、直列接続される。

[0199]

第 1 MIS型デバイスA1は、スタックゲート構造を有する。即ち、半導体基板 1 1 上 には、トンネル絶縁膜12を介してフローティングゲート(FG)13が形成され、フロ ーティングゲート13上には、電極間絶縁層14を介してコントロールゲート電極(CG ) 15が形成される。

[0200]

フローティングゲート13の第2方向の幅W1は、フローティングゲート13の第1方 向の長さLAよりも長い。また、フローティングゲート13の第2方向の幅W1は、第1 素子領域AA1の幅と同じである。さらに、フローティングゲート13の第1方向の両辺 には、窪みが設けられる。

[0201]

第1MIS型デバイスA1の直下の半導体基板11内には、拡散層22が形成される。

[ 0 2 0 2 ]

セレクトゲートトランジスタSGD1のドレイン拡散層16は、コンタクトプラグを介 してドレイン電極19に接続される。セレクトゲートトランジスタSGS1のソース拡散 層17は、コンタクトプラグを介してソース電極20に接続される。

[0203]

セレクトゲートトランジスタSGD1,SGS1のゲート電極の第2方向の幅W1は、 セレクトゲートトランジスタSGD1,SGS1のゲート電極の第1方向の長さLD,L Sよりも長い。

[0204]

第 2 素 子 領 域 A A 2 内 に は 、 制 御 デ バ イ ス と し て 機 能 す る 第 2 M I S 型 デ バ イ ス A 2 及 びこれを挟み込む2つのセレクトゲートトランジスタSGD2,SGS2が配置される。 第 2 MIS型 デバイスA2及び2つのセレクトゲートトランジスタSGD2,SGS2は 、直列接続される。

[0205]

第 2 MIS型 デバイスA2は、 第 1 MIS型 デバイスA1と同様に、スタックゲート構 造を有する。即ち、半導体基板11上には、トンネル絶縁膜12Aを介してフローティン グゲート(FG)13Aが形成され、フローティングゲート13A上には、電極間絶縁層 14Aを介してコントロールゲート電極(CG)15Aが形成される。

[0206]

フローティングゲート13Aの第2方向の幅W2は、フローティングゲート13Aの第 1方向の長さLAよりも長い。また、フローティングゲート13Aの第2方向の幅W2は 、 第 2 素 子 領 域 A A 2 の 幅 と 同 じ で あ る 。

[0207]

第2MIS型デバイスA2の直下の半導体基板11内には、拡散層22Aが形成される

[0208]

50

30

10

20

セレクトゲートトランジスタSGD2のドレイン拡散層16Aは、コンタクトプラグを介してドレイン電極19Aに接続される。セレクトゲートトランジスタSGS2のソース拡散層17Aは、コンタクトプラグを介してソース電極20Aに接続される。

[0209]

第3素子領域AA3内には、制御デバイスとして機能する第3MIS型デバイスA3及びこれを挟み込む2つのセレクトゲートトランジスタSGD3,SGS3が配置される。 第3MIS型デバイスA3及び2つのセレクトゲートトランジスタSGD3,SGS3は、直列接続される。

[ 0 2 1 0 ]

第3MIS型デバイスA3の構造は、第2MIS型デバイスA2と同じであり、また、第3MIS型デバイスA3を挟み込む2つのセレクトゲートトランジスタSGD3,SGS3の構造は、第2MIS型デバイスA2を挟み込む2つのセレクトゲートトランジスタSGD2,SGS2の構造と同じであるため、ここでは、その説明を省略する。

[0211]

このような半導体集積回路において、第1、第2及び第3MIS型デバイスA1,A2 ,A3のコントロールゲート電極(CG)15,15Aは、それぞれ独立に制御される。

[0212]

また、第1及び第2素子領域AA1,AA2間の素子分離絶縁層21の第2方向の幅W Iは、セレクトゲートトランジスタSGD1,SGS1,SGD2,SGS2のうちの1つのゲート電極から第1及び第2MIS型デバイスA1,A2のフローティングゲート(FG)13,13Aまでの第1方向の幅Wsよりも狭い。

[0213]

同様に、第1及び第3素子領域 A A 1 , A A 3 間の素子分離絶縁層 2 1 の第 2 方向の幅W I についても、セレクトゲートトランジスタSGD1,SGS1,SGD3,SGS3のうちの1つのゲート電極から第1及び第3 M I S 型デバイス A 1 , A 3 のフローティングゲート(FG)13 , 1 3 A までの第1方向の幅W S よりも狭い。

[ 0 2 1 4 ]

第 1 、 第 2 及び第 3 M I S 型デバイス A 1 , A 2 , A 3 のフローティングゲート(F G ) 1 3 , 1 3 A の第 1 方向の長さ L A は、互いに等しくなるようにレイアウトされ、セレクトゲートトランジスタ S G D 1 , S G S 1 , S G D 2 , S G S 2 , S G D 3 , S G S 3 のゲート電極の第 1 方向の長さ L D , L S は、互いに等しくなるようにレイアウトされる

[0215]

セレクトゲートトランジスタSGD1,SGS1,SGD2,SGS2,SGD3,SGS3は、第1、第2及び第3MIS型デバイスA1,A2,A3と同様に、スタックゲート構造を有するが、上側のゲート電極と下側のゲート電極とが導電プラグにより互いに接続される。

[0216]

このような半導体集積回路は、フラッシュメモリの製造プロセスを利用して容易に形成することができる。但し、第1、第2及び第3MIS型デバイスA1,A2,A3のコントロールゲート電極(CG)15,15Aを互いに分離する必要があるため、マスクパターンの変更が必要である。

[0217]

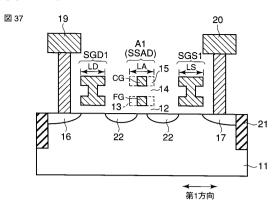

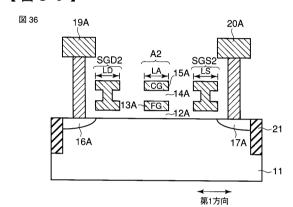

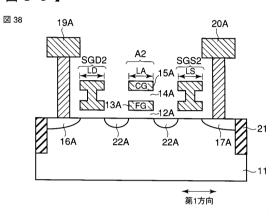

図33及び図34の半導体集積回路では、MIS型デバイスA1,A2,A3は、MISFETになっていないが、例えば、図37及び図38に示すように、MISFETとすることも可能である。

[0218]

図 3 5 及び図 3 6 は、図 3 7 及び図 3 8 の拡散層 2 2 , 2 2 A を除いたものである。これでも、エージングデバイスとしての所定の機能を実現できる。

[0219]

50

10

20

30

図37及び図38は、図33及び図34に対応する第1方向の断面図である。第2方向の断面図は、図31及び図32と同じなので、ここでは、省略する。

[0220]

B. 動作

図30万至図34の半導体集積回路では、制御デバイスとしてのMIS型デバイスA2,A3を用いて、MIS型デバイス(エージングデバイス)A1の寿命を制御する。この制御には、フローティングゲート13,13A間の容量カップリングCfgを利用する。

[0221]

尚、動作については、第1実施の形態と同じであるので、ここでは、その説明を省略する。

10

20

30

40

[0222]

C. 寿命の制御性

エージングデバイスの寿命の制御性を向上させるには、制御デバイスの寿命をエージングデバイスの寿命よりも長くすることが必要である。

[ 0 2 2 3 ]

寿命の制御性についても、第1実施の形態と同じであるので、ここでは、その説明を省略する。

[0224]

E. むすび

第3実施の形態によれば、エージングデバイスとしての第1MIS型トランジスタのフローティングゲートの形状を工夫することにより、第1実施の形態のように、第1MIS型トランジスタのフローティングゲートの第1方向の幅を第2方向の幅よりも長くしなくても、第1実施の形態と同様の効果を得ることができる。

[ 0 2 2 5 ]

(5) 第4実施の形態

第4実施の形態は、第3実施の形態の変形例である。

両実施の形態の異なる点は、第1素子領域の幅にある。

[0226]

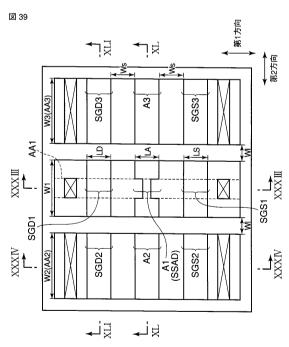

図39は、第4実施の形態に関わる半導体集積回路の平面図を示している。

[ 0 2 2 7 ]

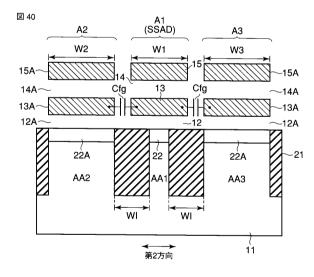

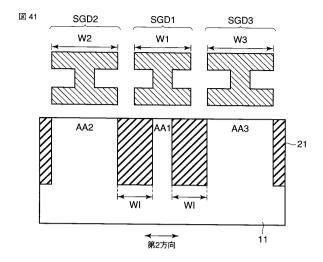

図 4 0 は、図 3 9 の X L - X L 線に沿う断面図、図 4 1 は、図 3 9 の X L I - X L I 線に沿う断面図である。

[0228]

尚、図39のXXXIII-XXXIII線に沿う断面図は、図33に示すようになり、図39のXXXIV-XXXIV線に沿う断面図は、図34に示すようになる。

[0229]

半導体基板11内には、STI構造の素子分離絶縁層21が形成される。第1、第2及び第3素子領域(アクティブエリア)AA1,AA2,AA3は、素子分離絶縁層21により分離され、第1方向に直交する第2方向に互いに隣接して配置される。

[0230]

第1素子領域 A A 1 の第2方向の幅W 1 は、第2及び第3素子領域 A A 2 , A A 3 の第2方向の幅W 2 , W 3 よりも狭い。

[0231]

第 1 素子領域 A A 1 内には、エージングデバイスとして機能する第 1 M I S 型デバイス A 1 (SSAD)及びこれを挟み込む 2 つのセレクトゲートトランジスタ S G D 1 , S G S 1 が配置される。第 1 M I S 型デバイス A 1 及び 2 つのセレクトゲートトランジスタ S G D 1 , S G S 1 は、直列接続される。

[0232]

第1MIS型デバイスA1は、スタックゲート構造を有する。即ち、半導体基板11上には、トンネル絶縁膜12を介してフローティングゲート(FG)13が形成され、フロ

ーティングゲート 1 3 上には、電極間絶縁層 1 4 を介してコントロールゲート電極( C G ) 1 5 が形成される。

[0233]

フローティングゲート 1 3 の第 2 方向の幅 W 1 は、第 1 素子領域 A A 1 の幅よりも広い。さらに、フローティングゲート 1 3 の第 1 方向の両辺には、窪みが設けられる。

[ 0 2 3 4 ]

第1MIS型デバイスA1の直下の半導体基板11内には、拡散層22が形成される。

[0235]

セレクトゲートトランジスタSGD1のドレイン拡散層16は、コンタクトプラグを介してドレイン電極19に接続される。セレクトゲートトランジスタSGS1のソース拡散層17は、コンタクトプラグを介してソース電極20に接続される。

[0236]

また、セレクトゲートトランジスタSGD1,SGS1のゲート電極の第 2 方向の幅 W 1 は、第 1 素子領域 A A 1 の幅よりも広い。

[0237]

第2素子領域AA2内には、制御デバイスとして機能する第2MIS型デバイスA2及びこれを挟み込む2つのセレクトゲートトランジスタSGD2,SGS2が配置される。 第2MIS型デバイスA2及び2つのセレクトゲートトランジスタSGD2,SGS2は、直列接続される。

[0238]

第2 M I S 型デバイス A 2 は、第1 M I S 型デバイス A 1 と同様に、スタックゲート構造を有する。即ち、半導体基板 1 1 上には、トンネル絶縁膜 1 2 A を介してフローティングゲート(FG) 1 3 A が形成され、フローティングゲート 1 3 A 上には、電極間絶縁層 1 4 A を介してコントロールゲート電極(CG) 1 5 A が形成される。

[0239]

フローティングゲート 1 3 A の第 2 方向の幅W 2 は、第 2 素子領域 A A 2 の幅と同じである。

[0240]

第2MIS型デバイスA2の直下の半導体基板11内には、拡散層22Aが形成される、

[0241]

セレクトゲートトランジスタSGD2のドレイン拡散層16Aは、コンタクトプラグを介してドレイン電極19Aに接続される。セレクトゲートトランジスタSGS2のソース拡散層17Aは、コンタクトプラグを介してソース電極20Aに接続される。

[0242]

第3素子領域AA3内には、制御デバイスとして機能する第3MIS型デバイスA3及びこれを挟み込む2つのセレクトゲートトランジスタSGD3,SGS3が配置される。 第3MIS型デバイスA3及び2つのセレクトゲートトランジスタSGD3,SGS3は、直列接続される。

[0243]

第3 M I S 型デバイス A 3 の構造は、第2 M I S 型デバイス A 2 と同じであり、また、第3 M I S 型デバイス A 3 を挟み込む 2 つのセレクトゲートトランジスタ S G D 2 , S G S 2 の構造と同じであるため、ここでは、その説明を省略する。

[ 0 2 4 4 ]

第4実施の形態によれば、エージングデバイスとしての第1MIS型トランジスタのフローティングゲートの形状を工夫することにより、第1実施の形態のように、第1MIS型トランジスタのフローティングゲートの第1方向の幅を第2方向の幅よりも長くしなくても、第1実施の形態と同様の効果を得ることができる。

[0245]

50

10

20

30

(6) 第5実施の形態

第5実施の形態は、第4実施の形態の変形例である。

両実施の形態の異なる点は、第2及び第3素子領域の幅にある。

[0246]

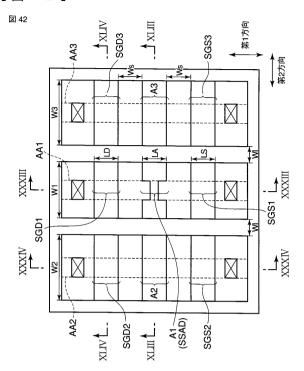

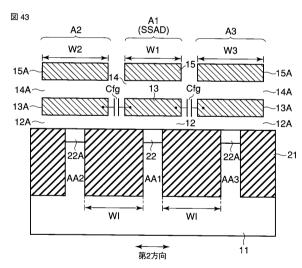

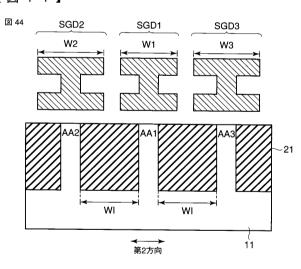

図42は、第5実施の形態に関わる半導体集積回路の平面図を示している。

[0247]

図 4 3 は、図 4 2 の X L I I I - X L I I I 線に沿う断面図、図 4 4 は、図 4 2 の X L I V - X L I V 線に沿う断面図である。

[0248]

尚、図42のXXXIII-XXXIII線に沿う断面図は、図33に示すようになり、図42のXXXIV-XXXIV線に沿う断面図は、図34に示すようになる。

[0249]

半導体基板11内には、STI構造の素子分離絶縁層21が形成される。第1、第2及び第3素子領域(アクティブエリア)AA1,AA2,AA3は、素子分離絶縁層21により分離され、第1方向に直交する第2方向に互いに隣接して配置される。

[ 0 2 5 0 ]

第 1 素子領域 A A 1 内には、エージングデバイスとして機能する第 1 M I S 型デバイス A 1 (SSAD)及びこれを挟み込む 2 つのセレクトゲートトランジスタ S G D 1 , S G S 1 が配置される。第 1 M I S 型デバイス A 1 及び 2 つのセレクトゲートトランジスタ S G D 1 , S G S 1 は、直列接続される。

[0251]

第1MIS型デバイスA1は、スタックゲート構造を有する。即ち、半導体基板11上には、トンネル絶縁膜12を介してフローティングゲート(FG)13が形成され、フローティングゲート13上には、電極間絶縁層14を介してコントロールゲート電極(CG)15が形成される。

[0252]

フローティングゲート 1 3 の第 2 方向の幅 W 1 は、第 1 素子領域 A A 1 の幅よりも広い。さらに、フローティングゲート 1 3 の第 1 方向の両辺には、窪みが設けられる。

[ 0 2 5 3 ]

第1MIS型デバイスA1の直下の半導体基板11内には、拡散層22が形成される。

[0254]

セレクトゲートトランジスタSGD1のドレイン拡散層16は、コンタクトプラグを介してドレイン電極19に接続される。セレクトゲートトランジスタSGS1のソース拡散層17は、コンタクトプラグを介してソース電極20に接続される。

[0255]

また、セレクトゲートトランジスタSGD1,SGS1のゲート電極の第 2 方向の幅W1は、第 1 素子領域 A A 1 の幅よりも広い。

[0256]

第2素子領域AA2内には、制御デバイスとして機能する第2MIS型デバイスA2及びこれを挟み込む2つのセレクトゲートトランジスタSGD2,SGS2が配置される。第2MIS型デバイスA2及び2つのセレクトゲートトランジスタSGD2,SGS2は、直列接続される。

[0257]

第2 M I S 型デバイス A 2 は、第1 M I S 型デバイス A 1 と同様に、スタックゲート構造を有する。即ち、半導体基板 1 1 上には、トンネル絶縁膜 1 2 A を介してフローティングゲート(F G) 1 3 A が形成され、フローティングゲート 1 3 A 上には、電極間絶縁層 1 4 A を介してコントロールゲート電極(C G) 1 5 A が形成される。

[0258]

フローティングゲート 1 3 A の第 2 方向の幅W 2 は、第 2 素子領域 A A 2 の幅よりも広い。

10

20

30

40

[0259]

第2MIS型デバイスA2の直下の半導体基板11内には、拡散層22Aが形成される

[0260]

セレクトゲートトランジスタSGD2のドレイン拡散層16Aは、コンタクトプラグを介してドレイン電極19Aに接続される。セレクトゲートトランジスタSGS2のソース拡散層17Aは、コンタクトプラグを介してソース電極20Aに接続される。

[0261]

また、セレクトゲートトランジスタSGD2, SGS2のゲート電極の第2方向の幅W2は、第2素子領域AA2の幅よりも広い。

[0262]

第3素子領域AA3内には、制御デバイスとして機能する第3MIS型デバイスA3及びこれを挟み込む2つのセレクトゲートトランジスタSGD3,SGS3が配置される。 第3MIS型デバイスA3及び2つのセレクトゲートトランジスタSGD3,SGS3は、直列接続される。

[ 0 2 6 3 ]

第3 M I S 型デバイス A 3 の構造は、第2 M I S 型デバイス A 2 と同じであり、また、第3 M I S 型デバイス A 3 を挟み込む 2 つのセレクトゲートトランジスタ S G D 2 、 S G S 2 の構造と同じであるため、ここでは、その説明を省略する。

[0264]

第5実施の形態によれば、エージングデバイスとしての第1MIS型トランジスタのフローティングゲートの形状を工夫することにより、第1実施の形態のように、第1MIS型トランジスタのフローティングゲートの第1方向の幅を第2方向の幅よりも長くしなくても、第1実施の形態と同様の効果を得ることができる。

- [0265]

- (7) その他

第 1 乃至第 5 実施の形態では、 2 つの制御デバイスにより 1 つのエージングデバイスを挟み込む構造を提案する。

[0266]

しかし、本発明の本質は、制御デバイスのフローティングゲートとエージングデバイスのフローティングゲートとの間に発生する容量カップリングを利用して、トンネル絶縁膜の厚さによらず、エージングデバイスの寿命を制御する、という点にある。

[0267]

従って、制御デバイスの数は、2つに制限されず、例えば、エージングデバイスに隣接する形で1つのみ設けてもよい。また、制御デバイスの数は、3つ以上であっても構わない。

[0268]

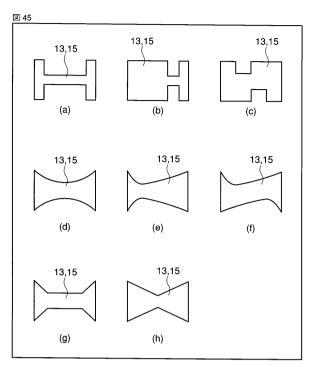

また、第3乃至第5実施の形態において、エージングデバイスとしての第1MIS型トランジスタA1のフローティングゲートの形状は、様々な変形が可能である。例えば、図45にその例について示す。

[0269]

重要な点は、第1MIS型トランジスタA1のフローティングゲートの第1方向の両辺に窪みを設け、エージングデバイスとセレクトゲートトランジスタとの干渉を弱くすることにある。

- [0270]

- 3 . 適用例

本発明のエージングデバイスは、様々な半導体集積回路に適用可能であるが、特に、プロセス上の観点からすれば、スタックゲート構造のメモリセルを有する不揮発性半導体メモリとの混載に有望である。

10

20

30

40

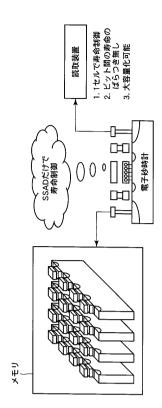

#### [0271]

例えば、図46に示すように、不揮発性半導体メモリに対するデータの読み出し/書き 込 み を 本 発 明 の エ ー ジン グ デ バ イ ス を 介 し て 行 え ば 、 デ ー タ の 読 み 出 し / 書 き 込 み を 許 可 する期間をエージングデバイスにより制御できる。

# [0272]

このようなシステムを構成すれば、1つのエージングデバイスで不揮発性半導体メモリ 全体の寿命を制御できるため、各ビットの寿命を各々制御する場合に比べて、ビット間の 寿命のばらつきが発生することはない。従って、寿命制御可能な不揮発性半導体メモリの 大容量化にも貢献できる。

### [0273]

4. むすび

本発明の例によれば、エージングデバイスの寿命を、トンネル絶縁膜の厚さによらず、 簡単な回路により変更できる。

# [0274]

本発明の例は、上述の実施の形態に限定されるものではなく、その要旨を逸脱しない範 囲で、各構成要素を変形して具体化できる。また、上述の実施の形態に開示されている複 数の構成要素の適宜な組み合せにより種々の発明を構成できる。例えば、上述の実施の形 態に開示される全構成要素から幾つかの構成要素を削除してもよいし、異なる実施の形態 の構成要素を適宜組み合わせてもよい。

# 【図面の簡単な説明】

[0275]

- 【図1】基本ユニットの構造を示す図。

- 【図2】エージングデバイスの4つの基本機能を示す図。

- 【図3】第1実施の形態の半導体集積回路を示す平面図。

- 【図4】図3のIV-IV線に沿う断面図。

- 【図5】図3のV-V線に沿う断面図。

- 【図6】図3のVI-VI線に沿う断面図。

- 【図7】図3のVII-VII線に沿う断面図。

- 【図8】図6の変形例を示す断面図。

- 【図9】図7の変形例を示す断面図。

- 【図10】第1実施の形態の変形例を示す断面図。

- 【図11】第1実施の形態の変形例を示す断面図。

- 【図12】ステップアップ書き込みの例を示す図。

- 【図13】ステップアップ書き込みの例を示す図。

- 【図14】ステップアップ書き込みの例を示す図。

- 【図15】MOSキャパシタのJV(リーク)特性を示す図。

- 【図16】MOSキャパシタのJV(リーク)特性を示す図。

- 【図17】カウンタードーピング技術の適用例を示す断面図。

- 【図18】第1実施の形態の変形例を示す断面図。

- 【図19】第1実施の形態の変形例を示す断面図。

- 【図20】第2実施の形態の半導体集積回路を示す平面図。

- 【図21】図20のXIX-XIX線に沿う断面図。

- 【図22】図20のXX-XX線に沿う断面図。

- 【図23】図20のXXI-XXI線に沿う断面図。

- 【図24】書き込み時の様子を示す断面図。

- 【図25】書き戻し時の様子を示す断面図。

- 【図26】第2実施の形態の変形例を示す断面図。

- 【図27】MOSキャパシタのJV(リーク)特性を示す図。

- 【図28】MOSキャパシタのJV(リーク)特性を示す図。

- 【図29】第1実施の形態の半導体集積回路を示す斜視図。

10

20

30

40

- 【図30】第3実施の形態の半導体集積回路を示す平面図。

- 【図31】図30のXXXI-XXXI線に沿う断面図。

- 【図32】図30のXXXII-XXXII線に沿う断面図。

- 【図33】図30のXXXIII-XXXIII線に沿う断面図。

- 【図34】図30のXXXIV-XXXIV線に沿う断面図。

- 【図35】図30のXXXIII-XXXXIII線に沿う断面図。

- 【図36】図30のXXXIV-XXXIV線に沿う断面図。

- 【図37】図35の変形例を示す断面図。

- 【図38】図36の変形例を示す断面図。

- 【図39】第4実施の形態の半導体集積回路を示す平面図。

- 【図40】図39のXL-XL線に沿う断面図。

- 【図41】図39のXLI-XLI線に沿う断面図。

- 【図42】第5実施の形態の半導体集積回路を示す平面図。

- 【図43】図42のXLIII-XLIII線に沿う断面図。

- 【図44】図42のXLIV・XLIV線に沿う断面図。

- 【図45】フローティングゲートの形状の変形例を示す図。

- 【図46】適用例としてのシステムを示す図。

# 【符号の説明】

### [0276]

1 1 : 半導体基板、 1 2 , 1 2 A : トンネル絶縁膜、 1 3 , 1 3 A : フローティングゲート、 1 4 , 1 4 A : 電極間絶縁層、 1 5 , 1 5 A : コントロールゲート電極、 1 6 : ドレイン拡散層、 1 7 : ソース拡散層、 1 8 : チャネル領域、 1 9 : ドレイン電極、 2 0 : ソース電極、 2 1 : 素子分離絶縁層、 2 : 拡散層、 2 3 : カウンタードーピング領域、 2 4 : ウェル領域。

# 【図1】

図 1

# 【図2】

図 2

# 【図3】

図 3

20

# 【図4】

図 4

# 【図5】

図 5

# 【図6】

図 6

# 【図8】

図 8

# 【図7】

図 7

# 【図9】

# 【図10】

# 【図11】

# 【図12】

# 【図13】

# 【図14】

# 【図15】

図 15

# 【図17】

図 17

# 【図16】

図 16

# 【図18】

図 18

# 【図19】

# 【図20】

図 20

# 【図21】

図 21

# 【図22】

図 22

# 【図23】

図 23

# 【図24】

# 【図25】

図 25

# 【図26】

図 26

# 【図27】

図 27

# 【図29】

# 【図28】

# 【図30】

# 【図31】

# 【図32】

# 【図33】

【図34】

# 【図35】

# 【図37】

# 【図36】

# 【図38】

# 【図39】

# 【図40】

【図41】

【図42】

【図43】

【図44】

# 【図45】

# 【図46】

# フロントページの続き

(51) Int.CI. F I テーマコード (参考)

**H01L 27/115 (2006.01)** H01L 27/06 102A

H 0 1 L 29/788 (2006.01) H 0 1 L 29/792 (2006.01)

H 0 1 L 29/792 (2006.01) H 0 1 L 27/06 (2006.01)

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

(72)発明者 渡辺 浩志

東京都港区芝浦一丁目1番1号 株式会社東芝内

(72) 発明者 西山 彰

東京都港区芝浦一丁目1番1号 株式会社東芝内

F ターム(参考) 5F038 AC03 AC04 AC05 AZ02 CA02 CA06 EZ20

5F048 AB01 AB10 AC01 AC10 BA01 BB01 BB03 BB06 BB07 BD04

BF16 BG13

5F083 EP02 EP23 EP33 EP34 ER03 ER09 ER21 GA30 MA06 MA19

NA01

5F101 BA01 BB05 BC02 BD22 BD35 BE07 BG10