(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5106083号

(P5106083)

(45) 発行日 平成24年12月26日(2012.12.26)

(24) 登録日 平成24年10月12日(2012.10.12)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 16/06 | (2006.01) | G 11 C 17/00 | 6 3 4 B |

| G 11 C 16/02 | (2006.01) | G 11 C 17/00 | 6 1 1 F |

| G 11 C 16/04 | (2006.01) | G 11 C 17/00 | 6 2 2 E |

請求項の数 23 (全 23 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2007-326144 (P2007-326144)  |

| (22) 出願日     | 平成19年12月18日 (2007.12.18)      |

| (65) 公開番号    | 特開2008-159244 (P2008-159244A) |

| (43) 公開日     | 平成20年7月10日 (2008.7.10)        |

| 審査請求日        | 平成22年11月8日 (2010.11.8)        |

| (31) 優先権主張番号 | 10-2006-0132813               |

| (32) 優先日     | 平成18年12月22日 (2006.12.22)      |

| (33) 優先権主張国  | 韓国 (KR)                       |

|           |                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics<br>Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路 129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic<br>of Korea |

| (74) 代理人  | 100093779<br>弁理士 服部 雅紀                                                                                                                                          |

| (72) 発明者  | 朴 起台<br>大韓民国京畿道城南市盆唐区盆唐洞セッピ<br>ヨルマウルサムブアパート 410 棟 304<br>号                                                                                                      |

最終頁に続く

(54) 【発明の名称】不揮発性メモリ装置におけるプログラム方法及びこのプログラムを適用する不揮発性メモリ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

増加型ステップパルスを選択ワードラインに順次に印加するプログラム電圧として使用する不揮発性メモリ装置におけるプログラム方法であって、

プリチャージ電圧及び前記プリチャージ電圧より高いブースト電圧が交代して充電されるように偶数ビットライン及び奇数ビットラインに前記プリチャージ電圧を印加する段階と、

前記偶数ビットライン及び前記奇数ビットラインのうち、選択ビットラインに記入データのビット値に相応するビットライン電圧を印加する段階と、

を含み、

前記偶数ビットライン及び前記奇数ビットラインに前記プリチャージ電圧を印加する段階は、

前記プリチャージ電圧が印加された前記偶数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記奇数ビットラインに印加する段階と、

前記プリチャージ電圧が印加された前記奇数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記偶数ビットラインに印加する段階と、

を含むことを特徴とする不揮発性メモリ装置におけるプログラム方法。

## 【請求項 2】

前記偶数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記奇数ビットラインに印加する段階、及び前記奇数ビットラインをフローティングさせた後、前記

プリチャージ電圧を前記偶数ビットラインに印加する段階は、

前記データの記入を完了するまで交代して反復することを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

#### 【請求項3】

前記偶数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記奇数ビットラインに印加する段階は、

前記偶数ビットラインに前記プリチャージ電圧を印加する段階と、

前記偶数ビットライン及び前記偶数ビットラインに連結されたメモリセルのチャンネルが前記プリチャージ電圧に充電された後、前記偶数ビットラインをフローティングさせる段階と、

10

前記奇数ビットラインに前記プリチャージ電圧を印加して前記フローティングされた偶数ビットラインを前記ブースト電圧に充電させる段階と、を含むことを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

#### 【請求項4】

前記奇数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記偶数ビットラインに印加する段階は、

前記奇数ビットラインに前記プリチャージ電圧を印加する段階と、

前記奇数ビットライン及び前記奇数ビットラインに連結されたメモリセルのチャンネルが前記プリチャージ電圧に充電された後、前記奇数ビットラインをフローティングさせる段階と、

20

前記偶数ビットラインに前記プリチャージ電圧を印加して前記フローティングされた奇数ビットラインを前記ブースト電圧に充電させる段階と、

を含むことを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

#### 【請求項5】

前記増加型ステップパルスのそれぞれが前記選択ワードラインに印加される時、前記プリチャージ電圧に充電されたビットラインに連結されたメモリセルのチャンネルは第1電圧にブーストされ、前記ブースト電圧に充電されたビートラインに連結されたメモリセルのチャンネルは、前記第1電圧より高い第2電圧にブーストされることを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

#### 【請求項6】

前記偶数ビットライン及び前記奇数ビットラインに前記プリチャージ電圧を印加する段階は、

前記偶数ビットラインに前記プリチャージ電圧を印加するタイミングを制御するための第1トランジスタを連結する段階と、

前記奇数ビットラインに前記プリチャージ電圧を印加するタイミングを制御するための第2トランジスタを連結する段階と、

前記偶数ビットライン及び前記奇数ビットラインに前記プリチャージ電圧及び前記ブースト電圧が交代して充電されるように前記第1トランジスタ及び前記第2トランジスタのスイッチングタイミングを制御する段階と、

を含むことを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

30

#### 【請求項7】

前記スイッチングタイミングを制御する段階は、

前記第1トランジスタをターンオフさせた後、前記第2トランジスタをターンオンさせる段階と、

前記第2トランジスタをターンオフさせた後、前記第1トランジスタをターンオンさせる段階と、

を含むことを特徴とする請求項6記載の不揮発性メモリ装置におけるプログラム方法。

#### 【請求項8】

前記第1トランジスタをターンオフさせた後、前記第2トランジスタをターンオンさせる段階と、前記第2トランジスタをターンオフさせた後、前記第1トランジスタをターン

40

50

オンさせる段階とは、前記データの記入を完了するまで交代して反復することを特徴とする請求項7記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項9】**

前記第1トランジスタをターンオフさせた後、前記第2トランジスタをターンオンさせる段階は、

前記偶数ビットラインに前記プリチャージ電圧を印加するために前記第1トランジスタをターンオンさせる段階と、

前記偶数ビットライン及び前記奇数ビットラインに連結されたメモリセルのチャンネルが前記プリチャージ電圧に充電された後、前記第1トランジスタをターンオフさせる段階と、

10

前記奇数ビットラインに前記プリチャージ電圧を印加するために、前記第2トランジスタをターンオンさせる段階と、を含むことを特徴とする請求項7記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項10】**

前記第2トランジスタをターンオフさせた後、前記第1トランジスタをターンオンさせる段階は、

前記奇数ビットラインに前記プリチャージ電圧を印加するために前記第2トランジスタをターンオンさせる段階と、

前記奇数ビットライン及び前記奇数ビットラインに連結されたメモリセルのチャンネルが前記プリチャージ電圧に充電された後、前記第2トランジスタをターンオフさせる段階と、

20

前記偶数ビットラインに前記プリチャージ電圧を印加するために前記第1トランジスタをターンオンさせる段階と、

を含むことを特徴とする請求項7記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項11】**

前記偶数ビットライン及び前記奇数ビットラインに前記プリチャージ電圧を印加する段階は、

前記パルスのうち、N番目パルスに相応するプリチャージ動作時、前記プリチャージ電圧が印加された前記偶数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記奇数ビットラインに印加する段階と、

30

前記パルスのうち、(N+1)番目パルスに相応するプリチャージ動作時、前記プリチャージ電圧が印加された前記奇数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記偶数ビットラインに印加する段階と、

を含むことを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項12】**

前記プリチャージ電圧は、前記不揮発性メモリ装置の内部電源電圧であることを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項13】**

前記ビットライン電圧を印加する段階は、

前記記入データのビット値が論理ローである場合、前記選択ビットラインにプログラム許容電圧を印加する段階と、

40

前記記入データのビット値が論理ハイである場合、前記選択ビットラインに充電された前記プリチャージ電圧及び前記ブースト電圧のうちの1つを維持する段階と、

を含むことを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項14】**

前記不揮発性メモリ装置は、NAND型フラッシュメモリ装置であることを特徴とする請求項1記載の不揮発性メモリ装置におけるプログラム方法。

**【請求項15】**

複数のワードライン及び複数のビットラインにそれぞれ連結された複数のメモリセルを含むメモリセルアレイと、

50

プリチャージ電圧及び前記プリチャージ電圧より高いブースト電圧が交代して充電されるように偶数ビットライン及び奇数ビットラインに前記プリチャージ電圧を印加するプリチャージ回路と、

前記偶数ビットライン及び前記奇数ビットラインのうち、選択ビットラインに記入データのビット値に相応するビットライン電圧を印加するページバッファブロックと、

少なくとも1つ以上のパルスを選択ワードラインに順次に印加する行選択回路と、

を含み、

前記プリチャージ回路は、

前記パルスのうち、N番目パルスに相応するプリチャージ動作時、前記プリチャージ電圧が印加された前記偶数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記奇数ビットラインに印加し、

前記パルスのうち、(N+1)番目パルスに相応するプリチャージ動作時、前記プリチャージ電圧が印加された前記奇数ビットラインをフローティングさせた後、前記プリチャージ電圧を前記偶数ビットラインに印加することを特徴とする不揮発性メモリ装置。

#### 【請求項16】

前記プリチャージ回路は、

プリチャージ電圧供給ラインと前記偶数ビットラインとの間の電気的連結を制御する第1トランジスタと、

前記プリチャージ電圧供給ラインと前記奇数ビットラインとの間の電気的連結を制御する第2トランジスタと、を含むことを特徴とする請求項15記載の不揮発性メモリ装置。

#### 【請求項17】

前記パルスのうち、N番目パルスに相応するプリチャージ動作時、前記第1トランジスタがターンオフされた後に前記第2トランジスタがターンオンされ、

前記パルスのうち、(N+1)番目パルスに相応するプリチャージ動作時、前記第2トランジスタがターンオフされた後に前記第1トランジスタがターンオンされることを特徴とする請求項16記載の不揮発性メモリ装置。

#### 【請求項18】

前記第1トランジスタのゲートに印加される第1プリチャージ信号及び前記第2トランジスタのゲートに印加される第2プリチャージ信号を発生するプリチャージ制御回路を更に含み、

前記パルスのうち、N番目パルスに相応するプリチャージ動作時、前記第1プリチャージ信号が非活性化された後に前記第2プリチャージ信号が活性化され、

前記パルスのうち、(N+1)番目パルスに相応するプリチャージ動作時、前記第2プリチャージ信号が非活性化された後、前記第1プリチャージ信号が活性化されることを特徴とする請求項16記載の不揮発性メモリ装置。

#### 【請求項19】

前記ブースト電圧は、隣接したビットライン間の容量性結合によって誘導されることを特徴とする請求項15記載の不揮発性メモリ装置。

#### 【請求項20】

前記プリチャージ電圧に充電されたビットラインに連結されたメモリセルのチャンネルは第1電圧にブーストされ、前記ブースト電圧に充電されたビットラインに連結されたメモリセルのチャンネルは前記第1電圧より高い第2電圧にブーストされることを特徴とする請求項15記載の不揮発性メモリ装置。

#### 【請求項21】

前記プリチャージ電圧は、前記不揮発性メモリ装置の内部電源電圧であることを特徴とする請求項15記載の不揮発性メモリ装置。

#### 【請求項22】

前記メモリセルアレイは、少なくとも1つ以上の前記メモリセルが直列で連結された複数のNANDストリングを含むことを特徴とする請求項15記載の不揮発性メモリ装置。

#### 【請求項23】

10

20

30

40

50

前記ページバッファブロックは、

前記記入データのビット値が論理ローである場合、前記選択ビットラインにプログラム許容電圧を印加し、

前記記入データのビット値が論理ハイである場合、前記選択ビットラインに充電された前記プリチャージ電圧及び前記ブースト電圧のうちの1つを維持することを特徴とする請求項15記載の不揮発性メモリ装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は半導体装置に関し、より詳細には、不揮発性メモリ装置におけるプログラム方法及びこのプログラムを適用する不揮発性メモリ装置に関する。 10

**【背景技術】**

**【0002】**

半導体メモリ装置は、電源供給が中断される時に保存されたデータを喪失するか否かによって、揮発性メモリ装置と不揮発性メモリ装置とに区分することができる。不揮発性メモリ装置は、電気的に消去とプログラムを実行可能なEEPROM (E l e c t r i c a l l y E r a s a b l e P r o g r a m m a b l e R e a d - o n l y M e m o r y) を含む。

**【0003】**

EEPROMの動作モードは、メモリセルにデータを記入するプログラムモード、メモリセルに保存されたデータを判読する読み出モード、及び保存されたデータを削除してメモリセルを初期化する消去モードに区分することができる。一般に、増加型ステップパルスプログラム (I S P P、I n c r e m e n t a l S t e p P u l s e P r o g r a m) 方式では、複数のパルスを順次に選択ワードラインに印加しながら、検証を完了するまで検証動作と検証後の再プログラム動作とを反復する。 20

**【0004】**

フラッシュメモリ装置はEEPROMに属し、消去動作がブロック又はセクター単位で同時に行われ、共通のワードラインに連結されたメモリセルに対してページ単位でプログラム動作が行われるという特徴を有する。フラッシュメモリ装置はメモリセルアレイの構造によって、ビットラインと接地との間にセルトランジスタが直列で配置されたN A N D型フラッシュメモリ装置と、並列で配置されたN O R型フラッシュメモリ装置とに区分される。N O R型フラッシュメモリ装置と比較すると、N A N D型フラッシュメモリ装置は、読み出動作及びプログラム動作時、バイト単位でのアクセスが不可能であるという短所があるが、プログラム及び消去速度が速いという長所がある。 30

**【0005】**

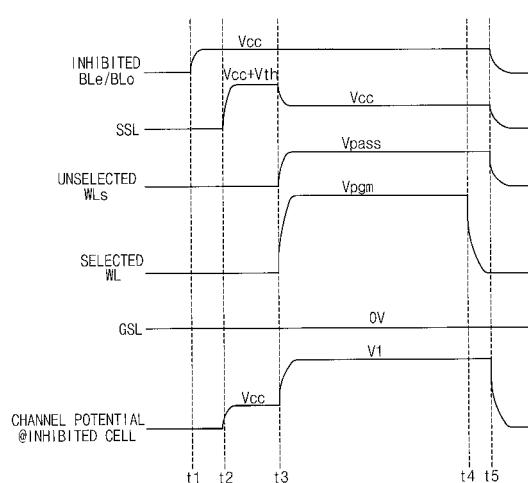

図1は、従来の不揮発性メモリ装置におけるプログラム方法を示すタイミング図である。

**【0006】**

図1を参照すると、時間t1で偶数ビットラインB L e 及び奇数ビットラインB L oに電源電圧V c c が同時に印加される。時間t2でストリング選択ラインS S Lに電源電圧V c c とストリング選択トランジスタのしきい電圧V t hとの和に相応する電圧(V c c + V t h)が印加され、ストリング選択トランジスタがターンオンされメモリセルのチャネルは電源電圧V c c にプリチャージされる。 40

**【0007】**

時間t3で選択されたワードラインにプログラム電圧V p g mが印加され、非選択ワードラインにバス電圧V p a s sが印加されると、プログラムが禁止されるメモリセルのチャネルは容量性結合によって電源電圧V c c より高い電圧V 1にブーストされる。時間t4でプログラム電圧V p g mが非活性化され時間t5でプログラム動作が終了する。

**【0008】**

図1には、プログラムが禁止されるビットラインに、例えば、電源電圧V c c がプログ 50

ラム禁止電圧として印加され、プログラムが禁止されるビットラインに連結されたメモリセルのチャンネルが電源電圧 Vcc より高い電圧 V1 にブーストされる場合のみが図示されている。これに対し、例えば、接地電圧 (0V) は、プログラム許容電圧としてプログラムが許容されるビットラインに印加される。従って、プログラムが許容されるビットラインに連結されたメモリセルでは、フローティングゲートとチャンネルとの間の大きい電圧差によって F - N トンネリング (Fowler - Nordheim Tunneling) が発生して前記メモリセル (又は、メモリセルのしきい電圧) がプログラムされる。

#### 【0009】

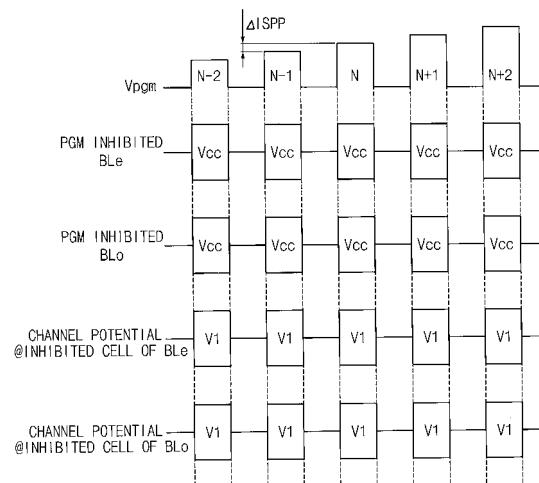

図 2 は、図 1 の従来の不揮発性メモリ装置におけるプログラム方法によるビットラインとチャンネルの電圧変化を示す図である。

10

#### 【0010】

図 2 には、一定の電圧 (ISPP) だけ順次に増加する増加型ステップパルスプログラム方式の場合について、プログラムが禁止されるビットライン (BLE, BLO) 及びメモリセルのチャンネルの電圧が図示されている。

#### 【0011】

(N - 2) 番目乃至 (N + 2) 番目パルスが順次にワードラインに印加され、各パルスが印加される前のプリチャージ動作時、偶数ビットライン及び奇数ビットラインにプリチャージ電圧 (例えば、電源電圧 Vcc) が同時に印加される。従って、プログラムが禁止される奇数ビットライン及び偶数ビットラインの電圧は常に電源電圧 Vcc になり、これに連結されたメモリセルのチャンネルは電源電圧 Vcc より高い電圧 V1 にブーストされる。

20

#### 【0012】

例えば、偶数ビットライン及び奇数ビットラインのうち、偶数ビットラインがデータを記入するように選択された場合、偶数ビットラインの電圧は記入データのビット値によって電源電圧 Vcc 又は接地電圧 (0V) になり得る。図 2 には、説明の便宜のために、プログラムが禁止される場合 (例えば、記入データのビット値が論理ローに相応する場合) に該当する偶数ビットラインの電圧のみが図示されている。選択されない奇数ビットラインは、データのビット値に関係なく全部プログラムが禁止されるので、奇数ビットラインの電圧は全部プログラム禁止電圧、例えば、電源電圧 Vcc になる。

#### 【0013】

30

メモリセルのサイズが漸次小さくなり、集積度が増加するほど、チャンネルとフローティングゲートとの間のキャパシタンスが増加してチャンネルから基板等への漏洩電流が増加する。このようなキャパシタンス及び漏洩電流の増加は、チャンネルにブーストされる電圧 V1 の減少を誘発して、結果的にプログラム搅乱 (program disturbance) が増加する。ここで、プログラム搅乱とは、プログラムが禁止されなければならないメモリセルのフローティングゲートとチャンネルとの間に形成された電圧差が F - N トンネリングを発生する程度に大きく、所望しないプログラムが行われることを意味する。

#### 【0014】

又、低いレベルの電源電圧 Vcc をプリチャージ電圧等として使用する不揮発性メモリ装置では、このプログラム搅乱が更に増大される。このプログラム搅乱を減少させるためにチャンネルにプリチャージされる電圧を増加させるには、高い電源電圧を必要とする。従って、同一の電源電圧を使用しながらブースト効率を増加して高いチャンネル電圧を得る方案が模索されている。その方案の 1 つとして、ビットライン間の容量性結合を利用してチャンネル電圧を増加させる方法が特許文献 1 に開示されている。

40

#### 【特許文献 1】特開平 11 - 120779 号公報

#### 【0015】

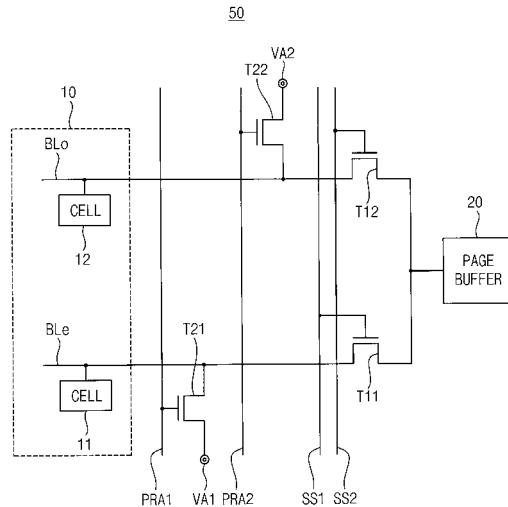

図 3 は、従来の不揮発性メモリ装置を示す回路図である。

#### 【0016】

図 3 を参照すると、不揮発性メモリ装置 50 は、偶数ビットライン BLE に連結された

50

メモリセル 11 と奇数ビットライン BLo に連結されたメモリセル 12 を含むメモリセルアレイ 10 を含む。一対のビットライン BL<sub>e</sub>、BL<sub>o</sub> は、ビットライン選択トランジスタ T11、T12 を通じてページバッファ 20 に共通に連結されている。

#### 【0017】

ビットライン選択トランジスタ T11、T12 のスイッチング動作は、ゲートに印加される選択信号 SS1、SS2 によって制御される。又、それぞれのビットライン BL<sub>e</sub>、BL<sub>o</sub> には、プリチャージ電圧 VA1、VA2 を印加するためのトランジスタ T21、T22 が接続されており、前記トランジスタ T21、T22 はゲートに印加されるプリチャージ信号 PRA1、PRA2 によって制御される。

#### 【0018】

図 3 の不揮発性メモリ装置 50 は、プリチャージ信号 PRA1、PRA2 が印加されるタイミングを調節してプリチャージ電圧 VA1、VA2 に充電されたビットラインをブースト電圧に充電した後、ビットライン選択トランジスタ T11、T12 を同時にターンオンさせる。従って、偶数ビットライン BL<sub>e</sub> 及び奇数ビットライン BL<sub>o</sub> はプリチャージ動作が完了すると、式 1 に表現された電圧に同一に充電される。

#### 【0019】

#### 【数 1】

$$V_{bst} = (V_{cc} + \beta V_{cc}) / 2 = (1 + \beta / 2) V_{cc}$$

10

20

#### 【0020】

ここで、V<sub>bst</sub> はビットラインのブースト電圧で、V<sub>cc</sub> はプリチャージ電圧として利用された電源電圧である。ビットラインカップリング係数  $\beta$  は、基板に形成されるメモリセルの構造によって決定される。

#### 【0021】

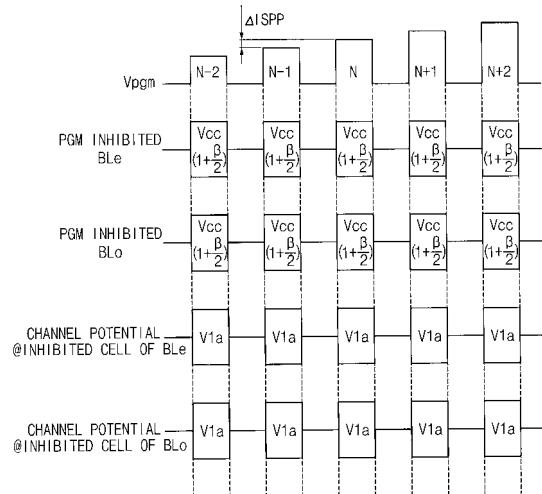

図 4 は、図 3 の従来の不揮発性メモリ装置におけるプログラム方法によるビットラインとチャンネルの電圧変化を示す図である。

#### 【0022】

30

図 4 に示すように、ビットラインカップリング係数  $\beta$  は正の値なので、プログラムが禁止されるビットラインの電圧は電源電圧 V<sub>cc</sub> より大きいブースト電圧 V<sub>bst</sub> に増加することが分かる。従って、図 4 に図示されたチャンネル電圧 V<sub>1a</sub> は、図 2 に図示されたチャンネル電圧 V<sub>1</sub> より大きい値になる。

#### 【0023】

図 3 の不揮発性メモリ装置 50 は、隣接したビットライン間の容量性結合によってチャンネル電圧を増加させることができる。しかし、隣接した偶数ビットライン BL<sub>e</sub> 及び奇数ビットライン BL<sub>o</sub> 間の電荷共有のために、ビットライン選択トランジスタ (T11、T12) が同時にターンオンされる時間が必要なので、プログラム時間が増加するという問題がある。ワードラインプログラム電圧 V<sub>pgm</sub> として増加型ステップパルスを使用する場合には、それぞれのパルスに対してビットライン選択トランジスタ T11、T12 が同時にターンオンされる時間が必要なので、全体プログラム時間はより増加することになる。

40

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0024】

上述したような問題点を解決するため、本発明の目的は、プログラム時間を増加させることなく、メモリセルのプログラム搅乱を減少させることができた不揮発性メモリ装置におけるプログラム方法を提供することである。

#### 【0025】

50

又、本発明のもう一つの目的は、プログラム時間を増加させることなく、メモリセルのプログラム搅乱を減少させることができが可能な不揮発性メモリ装置を提供することである。

**【課題を解決するための手段】**

**【0026】**

上述した目的を達成するために、本発明の一実施態様による不揮発性メモリ装置におけるプログラム方法は、少なくとも1つ以上のパルスを選択ワードラインに順次に印加するプログラム方法である。プリチャージ電圧及びプリチャージ電圧より高いブースト電圧が交代して充電されるように偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加し、偶数ビットライン及び奇数ビットラインのうち、選択ビットラインに記入データのビット値に相応するビットライン電圧を印加する。

10

**【0027】**

偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する段階は、プリチャージ電圧が印加された偶数ビットラインをフローティングさせた後、プリチャージ電圧を奇数ビットラインに印加する段階、及びプリチャージ電圧が印加された奇数ビットラインをフローティングさせた後、プリチャージ電圧を偶数ビットラインに印加する段階を含むことができる。

**【0028】**

上記の偶数ビットラインをフローティングさせた後、プリチャージ電圧を奇数ビットラインに印加する段階、及び奇数ビットラインをフローティングさせた後、プリチャージ電圧を偶数ビットラインに印加する段階は、データの記入を完了するまで交代して反復することができる。

20

**【0029】**

上記の偶数ビットラインをフローティングさせた後、プリチャージ電圧を奇数ビットラインに印加する段階は、偶数ビットラインにプリチャージ電圧を印加する段階と、偶数ビットライン及び偶数ビットラインに連結されたメモリセルのチャンネルがプリチャージ電圧に充電された後、偶数ビットラインをフローティングさせる段階と、奇数ビットラインにプリチャージ電圧を印加してフローティングされた偶数ビットラインをブースト電圧に充電する段階とを含むことができる。

**【0030】**

上記の奇数ビットラインをフローティングさせた後、プリチャージ電圧を偶数ビットラインに印加する段階は、奇数ビットラインにプリチャージ電圧を印加する段階と、奇数ビットライン及び奇数ビットラインに連結されたメモリセルのチャンネルがプリチャージ電圧に充電された後、奇数ビットラインをフローティングさせる段階と、偶数ビットラインにプリチャージ電圧を印加してフローティングされた奇数ビットラインをブースト電圧に充電する段階とを含むことができる。

30

**【0031】**

このブースト電圧は、隣接したビットライン間の容量性結合によって誘導することができる。プリチャージ電圧に充電されたビットラインに連結されたメモリセルのチャンネルは第1電圧にブーストされ、ブースト電圧に充電されたビットラインに連結されたメモリセルのチャンネルは、この第1電圧より高い第2電圧にブーストされる。

40

**【0032】**

一実施態様において、上述した偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する段階は、偶数ビットラインにプリチャージ電圧を印加するタイミングを制御するための第1トランジスタを連結する段階と、奇数ビットラインにプリチャージ電圧を印加するタイミングを制御するための第2トランジスタを連結する段階と、偶数ビットライン及び奇数ビットラインにプリチャージ電圧及びブースト電圧が交代して充電されるように第1トランジスタ及び第2トランジスタのスイッチングタイミングを制御する段階とを含むことができる。

**【0033】**

このスイッチングタイミングを制御する段階は、第1トランジスタをターンオフさせた

50

後、第2トランジスタをターンオンさせる段階、及び第2トランジスタをターンオフさせた後、第1トランジスタをターンオンさせる段階を含むことができる。

**【0034】**

第1トランジスタをターンオフさせた後、第2トランジスタをターンオンさせる段階、及び第2トランジスタをターンオフさせた後、第1トランジスタをターンオンさせる段階は、データの記入を完了するまで交代して反復することができる。

**【0035】**

第1トランジスタをターンオフさせた後、第2トランジスタをターンオンさせる段階は、偶数ビットラインにプリチャージ電圧を印加するために第1トランジスタをターンオンさせる段階、偶数ビットライン及び前記ビットラインに連結されたメモリセルのチャンネルがプリチャージ電圧に充電された後、第1トランジスタをターンオフさせる段階、及び奇数ビットラインにプリチャージ電圧を印加するために、第2トランジスタをターンオンさせる段階を含むことができる。10

**【0036】**

第2トランジスタをターンオフさせた後、第1トランジスタをターンオンさせる段階は、奇数ビットラインにプリチャージ電圧を印加するために第2トランジスタをターンオンさせる段階、奇数ビットライン及び奇数ビットラインに連結されたメモリセルのチャンネルがプリチャージ電圧に充電された後、第2トランジスタをターンオフさせる段階、及び偶数ビットラインにプリチャージ電圧を印加するために第1トランジスタをターンオンさせる段階を含むことができる。20

**【0037】**

上述した一実施態様において、選択ワードラインに順次に印加する少なくとも1つ以上のパルスとして、順次に電圧レベルが増加する増加型ステップパルスを利用することができる。

**【0038】**

一方、偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する段階は、N番目パルスに相応するプリチャージ動作時、プリチャージ電圧が印加された偶数ビットラインをフローティングさせた後、プリチャージ電圧を奇数ビットラインに印加する段階、及び(N+1)番目パルスに相応するプリチャージ動作時、プリチャージ電圧が印加された奇数ビットラインをフローティングさせた後、プリチャージ電圧を偶数ビットラインに印加する段階を含むことができる。30

**【0039】**

上記のプリチャージ電圧として、不揮発性メモリ装置の内部電源電圧を利用することができる。

**【0040】**

ビットライン電圧を印加する段階は、記入データのビット値が論理ローである場合、選択ビットラインにプログラム許容電圧を印加する段階、及び記入されるデータのビット値が論理ハイである場合、選択ビットラインに充電されたプリチャージ電圧及びブースト電圧のうちの1つを維持する段階を含むことができる。不揮発性メモリ装置は、NAND型フラッシュメモリ装置であってもよい。40

**【0041】**

又、上述した目的を達成するための本発明の一実施態様による不揮発性メモリ装置は、メモリセルアレイ、プリチャージ回路、ページバッファブロック、及び行選択回路を含む。

**【0042】**

メモリセルアレイは、複数のワードライン及び複数のビットラインにそれぞれ連結された複数のメモリセルを含む。プリチャージ回路は、プリチャージ電圧及びプリチャージ電圧より高いブースト電圧が交代して充電されるように偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する。ページバッファブロックは、偶数ビットライン及び奇数ビットラインのうち、選択ビットラインに記入データのビット値に相応するビットラ50

イン電圧を印加する。行選択回路は、少なくとも1つ以上のパルスを選択ワードラインに順次に印加する。

#### 【0043】

一実施態様として、行選択回路は、順次に電圧レベルが増加する増加型ステップパルスを選択ワードラインに印加することができる。

#### 【0044】

プリチャージ回路は、N番目パルスに相応するプリチャージ動作時、プリチャージ電圧が印加された偶数ビットラインをフローティングさせた後、プリチャージ電圧を奇数ビットラインに印加し、(N+1)番目パルスに相応するプリチャージ動作時、プリチャージ電圧が印加された奇数ビットラインをフローティングさせた後、プリチャージ電圧を偶数ビットラインに印加することができる。10

#### 【0045】

プリチャージ回路は、プリチャージ電圧供給ラインと偶数ビットラインとの間の電気的連結を制御する第1トランジスタ、及びプリチャージ電圧供給ラインと奇数ビットラインとの間の電気的連結を制御する第2トランジスタを含むことができる。

#### 【0046】

N番目パルスに相応するプリチャージ動作時、第1トランジスタがターンオフされた後に第2トランジスタをターンオンさせ、(N+1)番目パルスに相応するプリチャージ動作時、第2トランジスタがターンオフされた後に第1トランジスタをターンオンさせることができる。20

#### 【0047】

一実施態様において、不揮発性メモリ装置は更に、第1トランジスタのゲートに印加される第1プリチャージ信号及び第2トランジスタのゲートに印加される第2プリチャージ信号を発生するプリチャージ制御回路を含むことができる。N番目パルスに相応するプリチャージ動作時、第1プリチャージ信号が非活性化された後に第2プリチャージ信号を活性化させ、(N+1)番目パルスに相応するプリチャージ動作時、第2プリチャージ信号が非活性化された後、第1プリチャージ信号を活性化させることができる。

#### 【0048】

ブースト電圧は、隣接したビットライン間の容量性結合によって誘導することができる。プリチャージ電圧に充電されたビットラインに連結されたメモリセルのチャンネルは第1電圧にブーストさせ、ブースト電圧に充電されたビットラインに連結されたメモリセルのチャンネルは第1電圧より高い第2電圧にブーストさせることができる。30

#### 【0049】

プリチャージ電圧として、不揮発性メモリ装置の内部電源電圧を利用することができる。メモリセルアレイは、少なくとも1つ以上のメモリセルが直列に連結された複数のNANDストリングを含むことができる。

#### 【0050】

ページバッファブロックは、記入データのビット値が論理ローである場合、選択ビットラインにプログラム許容電圧を印加し、記入されるデータのビット値が論理ハイである場合、選択ビットラインに充電されたプリチャージ電圧及びブースト電圧のうち、1つを維持することができる。40

#### 【0051】

以上により、プログラム時間を増加させることなく、不揮発性メモリ装置におけるプログラム搅乱を減少させることができる。

#### 【発明を実施するための最良の形態】

#### 【0052】

以下、本発明の好ましい実施例を図面に基づいて詳細に説明する。

#### 【0053】

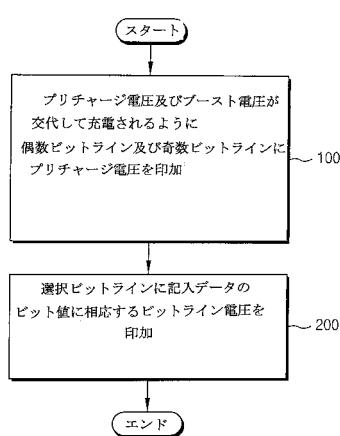

図5は、本発明の一実施例による不揮発性メモリ装置におけるプログラム方法を示す流れ図である。50

**【 0 0 5 4 】**

図5には、少なくとも1つ以上のパルスを選択ワードラインに順次に印加する不揮発性メモリ装置におけるプログラム方法が図示されている。

**【 0 0 5 5 】**

図5によると、本発明の一実施例では、プリチャージ電圧及びプリチャージ電圧より高いブースト電圧が交代して充電されるように偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する(S100)。少なくとも1つ以上のパルスを選択ワードラインに順次に印加するプログラム方法では、一般に、プログラムが完了するまで検証及び再プログラムを反復する。このようにプログラムを反復する度に偶数ビットライン及び奇数ビットラインが交代してブースト電圧に充電されるようにプリチャージ電圧を印加する。

10

**【 0 0 5 6 】**

偶数ビットライン及び奇数ビットラインがプリチャージ電圧及びブースト電圧のうちいずれか一方ずつにそれぞれ充電された後、偶数ビットライン及び奇数ビットラインのうちから選択された選択ビットラインに記入データのビット値に相応するビットライン電圧を印加する(S200)。本発明の一実施例による不揮発性メモリ装置では、行方向に配置され1つのワードラインに共通に連結された複数のメモリセルは、行方向に交代して配置された偶数ビットラインと奇数ビットラインとにそれぞれ連結される。

**【 0 0 5 7 】**

偶数ビットラインに連結されたメモリセルは1つのページを形成し、奇数ビットラインに連結されたメモリセルは他の1つのページを形成する。不揮発性メモリ装置におけるプログラムは、一般に、ページ単位で行われ、偶数ビットラインと奇数ビットラインのうちから選択された選択ビットラインにはデータのビット値に相応するビットライン電圧が印加され、非選択ビットラインは充電されたプリチャージ電圧又はブースト電圧を維持する。

20

**【 0 0 5 8 】**

このように、ビットラインにプログラムを禁止又は許容するための電圧が安定化した後に、選択ワードラインにプログラム電圧を印加し、非選択ワードラインにパス電圧を印加する。更にプログラムが完了するまで検証及び再プログラムを反復し、少なくとも1つ以上のパルスが選択ワードラインに印加される。即ち、プリチャージ電圧の印加段階(S100)と記入データのビット値に相応するビットライン電圧の印加段階(S200)とは、少なくとも一回以上反復される。選択ワードラインに印加されるパルスの数は、メモリセルの特性によって変更することができる。

30

**【 0 0 5 9 】**

偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する段階(S100)は、プリチャージ電圧が印加された偶数ビットラインをフローティングさせた後、プリチャージ電圧を奇数ビットラインに印加するプリチャージ動作と、これとは逆に、プリチャージ電圧が印加された奇数ビットラインをフローティングさせた後、プリチャージ電圧を偶数ビットラインに印加するプリチャージ動作とを交代して行うことができる。このような2つのプリチャージ動作は、データの記入が完了するまで交代して反復することができる。

40

**【 0 0 6 0 】**

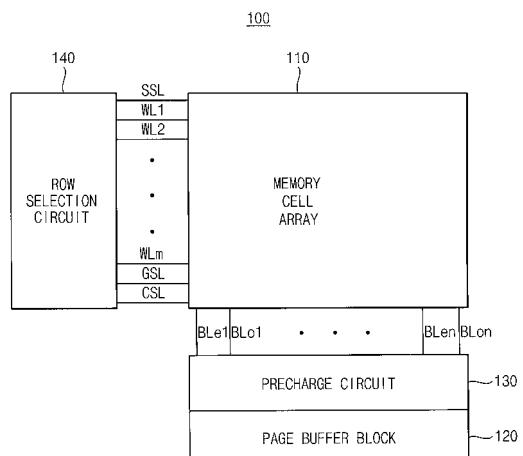

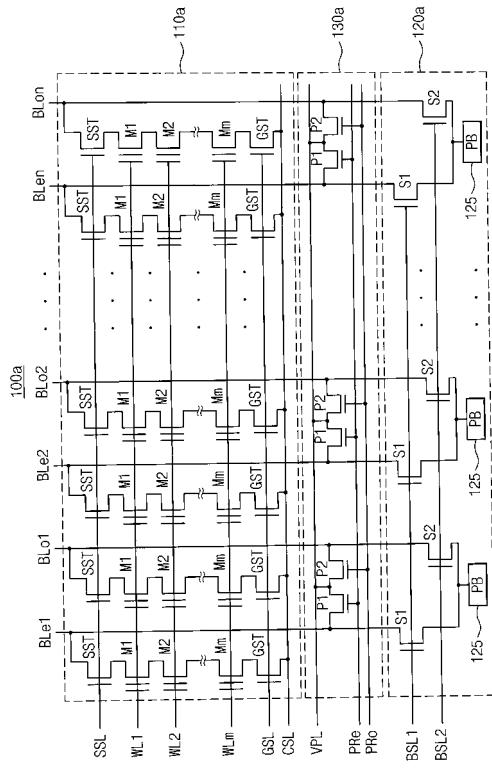

図6は、本発明の一実施例による不揮発性メモリ装置を示すブロック図である。

**【 0 0 6 1 】**

図6によると、不揮発性メモリ装置100は、メモリセルアレイ110、ページバッファブロック120、プリチャージ回路130、及び行選択回路140を含む。

**【 0 0 6 2 】**

メモリセルアレイ110は、複数のワードライン(WL1, WL2, ..., WLm)及び複数のビットライン(BL1, BL2, ..., BLn)にそれぞれ連結された複数のメモリセルを含む。メモリセルアレイ110は、少なくとも1つ以上のメモリセルが直列に連結された複数のNANDストリングを含むことができる。

50

## 【0063】

この場合、図6に示すように、ストリング選択ラインS S Lを通じて印加される信号によってビットライン(B L 1、B L 2、...、B L n)と前記N A N Dストリングとの間の電気的な連結が制御され、接地選択ラインG S Lを通じて印加される信号によって共通ソースラインC S Lと前記N A N Dストリングとの間の電気的な連結が制御される。

## 【0064】

プリチャージ回路130は、プリチャージ電圧及びプリチャージ電圧より高いブースト電圧が交代して充電されるように偶数ビットラインB L e及び奇数ビットラインB L oにプリチャージ電圧を印加する。例えば、不揮発性メモリ装置100の内部電源電圧をプリチャージ電圧として利用することができる。10

## 【0065】

ページバッファブロック120は、偶数ビットラインB L e及び奇数ビットラインB L oのうちから選択された選択ビットラインに、記入データのビット値に相応するビットライン電圧を印加する。

## 【0066】

例えば、ページバッファブロック120は、記入データのビット値が「0」である場合、プログラム許容電圧として接地電圧(0V)を選択ビットラインに印加する。又、ページバッファブロック120は、記入データのビット値が「1」である場合、プログラム禁止電圧として電源電圧V c cを選択ビットラインに印加するか、プリチャージ回路130によって選択ビットラインに充電されたプリチャージ電圧又はブースト電圧を維持することができる。20

## 【0067】

行選択回路140は、少なくとも1つ以上のパルスを選択ワードラインに順次に印加する。即ち、プログラム動作時に行選択回路140は、行アドレス信号に応答して1つのワードラインを選択し、選択ワードラインにはプログラム電圧、非選択ワードラインにはバス電圧をそれぞれ印加する。

## 【0068】

選択ワードラインに印加されるプログラム電圧としては、複数のパルスを利用することができます。本実施例は、順次に電圧レベルが増加する増加型ステップパルスをプログラム電圧として利用する。この場合、プログラム強度を増加させながらプログラムが完了するまで検証と再プログラムとを反復する。30

## 【0069】

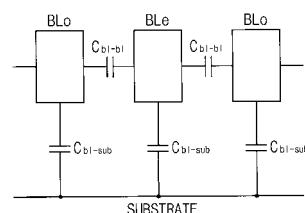

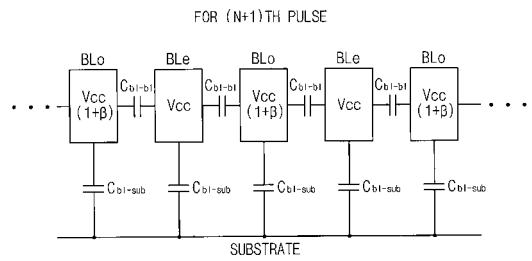

図7は、本発明の一実施例におけるビットライン間の容量性結合を示す図である。

## 【0070】

図7に示すように、ビットライン間にはC<sub>b1-b1</sub>で表示された寄生キャパシタンスが存在し、ビットラインと基板との間にはC<sub>b1-sub</sub>で表示された寄生キャパシタンスが存在する。

## 【0071】

例えば、偶数ビットラインに電源電圧V c cを印加してフローティングさせた後、隣接した奇数ビットラインに電源電圧V c cを印加すると、ビットライン間の容量性結合によってフローティングされた偶数ビットラインの電圧は式2に示すようにブースト電圧に充電される。40

## 【0072】

## 【数2】

$$V_{boost} = V_{cc} + \beta V_{cc} = (1 + \beta) V_{cc}$$

ここで、V<sub>boost</sub>はビットラインのブースト電圧で、V<sub>cc</sub>はプリチャージ電圧と50

して使用された電源電圧である。ビットラインカップリング係数 は基板に形成されるメモリセルの構造によって決定され、数式 3 で表現される。

【 0 0 7 3 】

【 数 3 】

$$\beta = 2 C_{b1-b1} / (2 C_{b1-b1} + C_{b1-sub})$$

【 0 0 7 4 】

メモリセルアレイの集積度を増加させるためには、ビットライン間の間隔がより小さくなり、これによってビットラインカップリング係数 が増加する。例えば、 $C_{b1-b1}$  が  $C_{b1-sub}$  の約 2 . 3 倍である場合、 $\beta$  は約 0 . 8 2 の値を有する。

【 0 0 7 5 】

このようなビットライン間の容量性結合を利用するため、ビットラインに供給される電源電圧  $V_{cc}$  より更に高いブースト電圧  $V_{boost}$  にビットラインを充電させることができる。

【 0 0 7 6 】

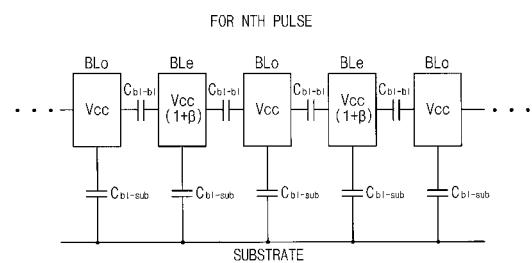

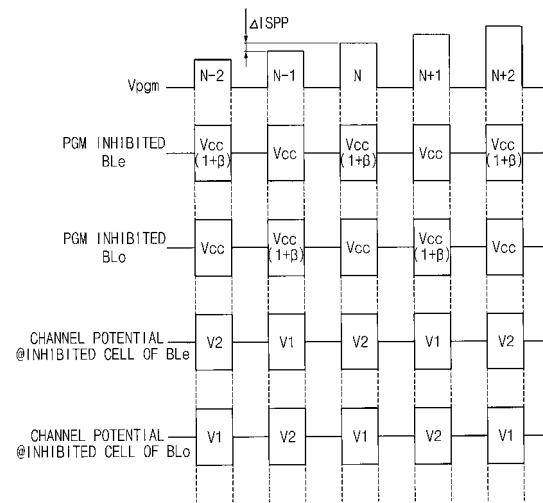

図 8 及び図 9 は、図 6 に示した本発明の一実施例による不揮発性メモリ装置において順次に印加されるパルスに相応するビットラインの電圧を示す図である。

【 0 0 7 7 】

図 8 及び図 9 には、プリチャージ電圧として電源電圧  $V_{cc}$  を利用する場合に、順次に選択ワードラインに印加される N 番目パルス及び (N + 1) 番目パルスに対して、プログラムが禁止されるビットラインの電圧をそれぞれ示す。図 8 及び図 9 に図示しないプログラム許容電圧が印加されるビットラインは、例えば、接地電圧 (0 V) になる。

【 0 0 7 8 】

N 番目パルスが印加される間、図 8 に示すように、プログラムが禁止される奇数ビットライン  $BL_o$  は電源電圧  $V_{cc}$  に充電され、プログラムが禁止される偶数ビットライン  $BL_e$  は電源電圧  $V_{cc}$  より高いブースト電圧  $V_{boost}$ 、即ち、(1+)  $V_{cc}$  に充電される。

【 0 0 7 9 】

これとは逆に、(N + 1) 番目パルスが印加される間、図 9 に示すように、プログラムが禁止される偶数ビットライン  $BL_e$  は電源電圧  $V_{cc}$  に充電され、プログラムが禁止される奇数ビットライン  $BL_o$  は電源電圧  $V_{cc}$  より高いブースト電圧  $V_{boost}$  に充電される。

【 0 0 8 0 】

このように、プリチャージ電圧（例えば、電源電圧  $V_{cc}$ ）及びプリチャージ電圧より高いブースト電圧  $V_{boost}$  はプログラムが禁止される偶数ビットライン  $BL_e$  と奇数ビットライン  $BL_o$  とに交代して充電されるため、プログラム時間が増加することなく、偶数ビットライン  $BL_e$  と奇数ビットライン  $BL_o$  のプログラム搅乱は均一に減少させることができる。

【 0 0 8 1 】

図 10 は、本発明の一実施例による不揮発性メモリ装置におけるプログラム方法によるビットラインとチャンネルの電圧変化を示す図である。

【 0 0 8 2 】

図 10 には、一定の電圧 (ISPP) だけ順次に増加する増加型ステップパルス (Incremental Step Pulse) をプログラム電圧  $V_{pgm}$  として利用する場合について、プログラムが禁止される偶数ビットライン  $BL_e$  と奇数ビットライン  $BL_o$  に充電される電圧 ( $V_{cc}$ 、 $V_{cc}(1+)$ )、及びチャンネルのブースト電圧 ( $V_1$ 、 $V_2$ ) をそれぞれ示す。

【 0 0 8 3 】

10

20

30

40

50

(N - 2) 番目パルスから (N + 2) 番目パルスまでそれぞれのパルスがワードラインに順次に印加される度に、プログラムが禁止される偶数ビットライン B L e 及び奇数ビットライン B L e は交代して電源電圧 V c c 及びブースト電圧 V c c (1+) に充電される。これによって、プログラムが禁止されるメモリセルのチャンネル電圧も第1電圧 V 1 及び第2電圧 V 2 に交代してブーストされる。

#### 【0084】

図10には選択ビットラインのうち、プログラムが禁止される場合（例えば、記入データのビット値が論理ローに相応する場合）に該当する選択ビットラインの電圧のみを示している。プログラムが許容される選択ビットライン及びこれに連結されたメモリセルのチャンネル電圧は、プログラム許容電圧（例えば、接地電圧）になり、図10では図示せず省略した。非選択ビットラインは、データのビット値に関係なく全部プログラムが禁止されるので、非選択ビットラインの電圧は全部プログラム禁止電圧、例えば、電源電圧 V c c 又はブースト電圧 V b o o s t になる。10

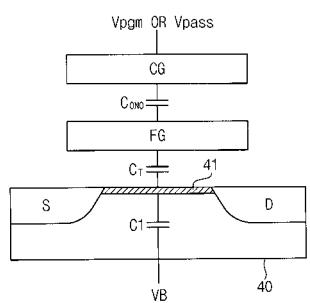

#### 【0085】

図11は、本発明の一実施例によるチャンネルのブースト効果を説明するためのメモリセルの断面図である。

#### 【0086】

図11によると、メモリセルを形成するために、基板40の上部にソースSとドレインDが形成され、ソースSとドレインDとの間の基板上に制御ゲート(C G : C o n t r o l G a t e)と浮遊ゲート又はフローティングゲート(F G : F l o a t i n g G a t e)が積層される。制御ゲートC Gと浮遊ゲートF Gとの間にはONO(oxide/nitride/oxide)膜のような誘電層が介在し、浮遊ゲートF Gと基板上面との間にはトンネリング酸化膜が介在する。誘電層とトンネリング酸化膜はそれぞれのキャパシタンス(C O N O、C T)を有する。20

#### 【0087】

制御ゲートC Gにプログラム電圧 V p g m 又はバス電圧 V p a s s が印加されると、ソースSとドレインDとの間の基板上部にチャンネル41が形成される。基板電圧 V B とチャンネル41との間のキャパシタンスを C 1 とし、チャンネル41と制御ゲートC Gとの間の等価キャパシタンスを C 2 とすると、カップリング係数 r は式4で表示される。

#### 【0088】

#### 【数4】

$$r = C_2 / (C_1 + C_2)$$

#### 【0089】

プログラム電圧 V p g m 及びバス電圧 V p a s s が、直列に連結されてN A N Dストリングを形成するメモリセルのゲートにそれぞれ印加されると、直列に連結されたメモリセルの容量性結合によって、チャンネルの電圧がブーストされる。チャンネルのブースト電圧は、カップリング係数 r と、N A N Dストリングに含まれるメモリセルの個数と、メモリセルのゲートに印加される電圧とに依存する。40

#### 【0090】

プリチャージ動作によりメモリセルのチャンネルに充電された電圧が大きいほど、チャンネルはより高い電圧にブーストされる。図10によると、電源電圧 V c c より高い電圧 ((1+) V c c) からブーストされるチャンネルの第2電圧 V 2 は、電源電圧 V c c からブーストされるチャンネルの第1電圧 V 1 より大きくなる。

#### 【0091】

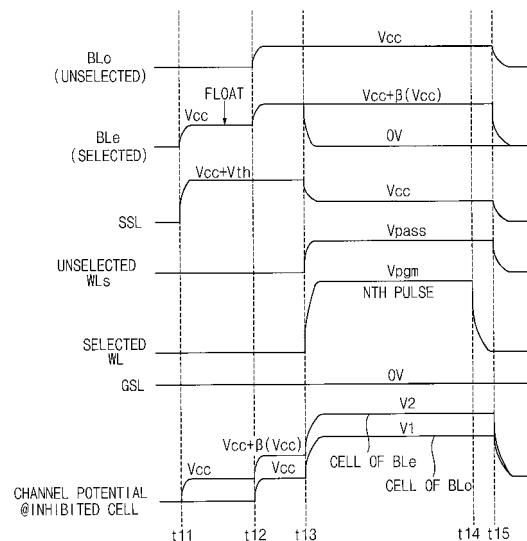

図12及び図13は、図5に示した本発明の一実施例による不揮発性メモリ装置におけるプログラム方法を説明するためのタイミング図である。

#### 【0092】

例えば、偶数ビットライン B L e 及び奇数ビットライン B L o のうち、偶数ビットライン B L e がプログラムされるように選択された選択ビットラインである場合について説明する。

#### 【 0 0 9 3 】

図 1 2 によると、時間 t 1 1 では偶数ビットライン B L e にプリチャージ電圧、例えば、電源電圧 V c c が印加される。これと共に、ストリング選択ライン S S L に電源電圧 V c c とストリング選択トランジスタのしきい電圧 V t h との和に相応する電圧 ( V c c + V t h ) が印加され、ストリング選択トランジスタがターンオンされ、偶数ビットライン B L e に連結されたメモリセルのチャンネルは電源電圧 V c c にプリチャージされる。

#### 【 0 0 9 4 】

時間 t 1 1 から偶数ビットライン B L e と連結されたメモリセルのチャンネルとがプリチャージ電圧に充電される時間が経過した後、偶数ビットライン B L e がフローティングされる。

#### 【 0 0 9 5 】

時間 t 1 2 で奇数ビットライン B L o にプリチャージ電圧が印加されると、フローティングされた偶数ビットライン B L e は、ビットライン間の容量性結合によってブースト電圧に充電される。結果的に、偶数ビットライン B L e はブースト電圧 V b o o s t に充電され、奇数ビットライン B L o は電源電圧 V c c に充電される。

#### 【 0 0 9 6 】

時間 t 1 3 では、選択ビットラインである偶数ビットライン B L e にデータのビット値に相応するビットライン電圧が印加される。例えば、ビット値が「 1 」である場合、偶数ビットライン B L e はプリチャージ動作によって充電されたブースト電圧を維持し、ビット値が「 0 」である場合、偶数ビットライン B L e にプログラム許容電圧（例えば、接地電圧）が印加される。

#### 【 0 0 9 7 】

又、時間 t 1 3 で選択ワードラインにプログラム電圧 V p g m の N 番目パルスが印加され、非選択ワードラインにバス電圧 V p a s s が印加される。従って、時間 t 1 3 では、プログラムが禁止される奇数ビットライン B L o に連結されたメモリセルのチャンネル電圧は、第 1 電圧 V 1 にブーストされる。又、プログラムが禁止される偶数ビットライン B L e に連結されたメモリセルのチャンネル電圧は、第 1 電圧 V 1 より高い第 2 電圧 V 2 にブーストされる。

#### 【 0 0 9 8 】

時間 t 1 4 でプログラム電圧 V p g m 及びバス電圧 V p a s s が非活性化され、時間 t 1 5 で N 番目パルスによるプログラム動作が終了する。接地選択ライン G S L の信号は非活性化され、N A N D ストリングと共に接地ラインは電気的に遮断される。

#### 【 0 0 9 9 】

図 1 3 によると、図 1 2 の N 番目パルスによるプログラム動作とは反対で、( N + 1 ) 番目パルスによるプログラム動作ではプリチャージされた奇数ビットライン B L o がフローティングされた後、偶数ビットライン B L e にプリチャージ電圧が印加される。

#### 【 0 1 0 0 】

時間 t 2 1 で奇数ビットライン B L o にプリチャージ電圧、例えば、電源電圧 V c c が印加され、時間 t 2 1 から奇数ビットラインがプリチャージ電圧に充電される時間が経過した後、奇数ビットライン B L o がフローティングされる。

#### 【 0 1 0 1 】

時間 t 2 2 で偶数ビットライン B L e にプリチャージ電圧が印加されると、フローティングされた奇数ビットライン B L o はビットライン間の容量性結合によってブースト電圧に充電される。結果的に、奇数ビットライン B L o はブースト電圧 V b o o s t に充電され、偶数ビットライン B L e は電源電圧 V c c に充電される。

#### 【 0 1 0 2 】

時間 t 2 3 で選択された偶数ビットライン B L e にデータのビット値に相応するビット

10

20

30

40

50

ライン電圧が印加される。又、時間  $t_{23}$  で選択ワードラインにプログラム電圧  $V_{pgm}$  の ( $N + 1$ ) 番目パルスが印加され非選択ワードラインにバス電圧  $V_{pass}$  が印加される。

#### 【0103】

従って、時間  $t_{23}$  では、プログラムが禁止される偶数ビットライン  $BLe$  に連結されたメモリセルのチャンネル電圧は第1電圧  $V_1$  にブーストされる。又、プログラムが禁止される奇数ビットライン  $BL_o$  に連結されたメモリセルのチャンネル電圧は第1電圧  $V_1$  より高い第2電圧  $V_2$  にブーストされる。

#### 【0104】

時間  $t_{24}$  でプログラム電圧  $V_{pgm}$  及びバス電圧  $V_{pass}$  が非活性化され、時間  $t_{25}$  で ( $N + 1$ ) 番目パルスによるプログラム動作が終了される。接地選択ライン  $GSL$  は継続非活性化され、 $NAND$ ストリングと共に接地ラインは電気的に遮断される。

#### 【0105】

このように、ビットライン間の容量性結合を利用して、プログラムが完了するまでそれぞれのパルス毎に偶数ビットライン  $BLe$  及び奇数ビットライン  $BL_o$  が交代してブースト電圧  $V_{boost}$  に充電される。

#### 【0106】

図14は、図6に示した本発明の一実施例による不揮発性メモリ装置を示す回路図である。

#### 【0107】

図14に示すように、本実施例によると、メモリセルアレイ110aは、列方向に延長された複数のNANDストリングで構成される。NANDストリングは、ストリング選択トランジスタSSSTと接地選択トランジスタGSTとの間に直列で連結された複数のメモリセル (M1乃至Mm) から構成され、互いに異なるNANDストリングに属する複数のメモリセルがそれぞれのワードライン (WL1、WL2、...、WLm) に共通に連結される。

#### 【0108】

ストリング選択トランジスタSSSTは、ストリング選択ラインSSLに共通に連結され、接地選択トランジスタGSTは接地選択ラインGSLに共通に連結される。各ストリング選択トランジスタSSSTは列方向に延長されたビットライン (BLe、BLo) とそれぞれ連結され、各接地選択トランジスタGSTは共通ソースラインCSLに連結される。

#### 【0109】

図14には、NAND型メモリセルアレイ110aを示したが、本発明は、NAND型フラッシュメモリ装置のみに限らず、奇数ビットラインと偶数ビットラインとがそれぞれ1つのページを形成してプログラム電圧として複数のパルスを使用する不揮発性メモリ装置に適用することができる。

#### 【0110】

図6に図示された行選択回路140は、ストリング選択ラインSSL、接地選択ラインGSL及び複数のワードライン (WL1、WL2、...、WLm) を通じてメモリセルアレイ110と連結される。

#### 【0111】

行選択回路140は、プログラム動作時、行アドレス信号によって選択されたワードラインにプログラム電圧を印加して、選択されないワードラインにバス電圧を印加する。例えば、行選択回路140は、順次に電圧レベルが増加する増加型ステップパルスをプログラム電圧として選択ワードラインに印加することができる。

#### 【0112】

ページバッファブロック120aは、一対のビットライン  $BLe$ 、 $BL_o$  にそれぞれ連結された複数のページバッファ125を含む。偶数ビットライン  $BLe$  に連結された1つのページに該当するメモリセルと奇数ビットライン  $BL_o$  に連結された他の1つのページに該当するメモリセルとは、選択信号  $B_{SL1}$ 、 $B_{SL2}$  に応答してスイッチング動作す

10

20

30

40

50

るトランジスタ S<sub>1</sub>、S<sub>2</sub>によって選択される。

【0113】

図示しないコントローラは、プログラム動作のための電圧レベルを制御し、メモリセルアレイ 110、ページバッファブロック 120、及び行選択回路 140 の動作タイミングを制御する。

【0114】

プリチャージ回路 130a は、プリチャージ電圧及びプリチャージ電圧より高いブースト電圧が交代して充電されるように、偶数ビットライン及び奇数ビットラインにプリチャージ電圧を印加する。

【0115】

プリチャージ回路 130a は、選択ワードラインに印加されるパルスのうち、N 番目パルスに相応するプリチャージ動作時、プリチャージ電圧が印加された偶数ビットライン BL<sub>o</sub> をフローティングさせた後、プリチャージ電圧を奇数ビットライン BL<sub>e</sub> に印加する。これとは逆に、プリチャージ回路 130a は、(N+1) 番目パルスに相応するプリチャージ動作時、プリチャージ電圧が印加された奇数ビットライン BL<sub>e</sub> をフローティングさせた後、プリチャージ電圧を前記偶数ビットライン BL<sub>o</sub> に印加する。

10

【0116】

プリチャージ回路 130a は、プリチャージ電圧供給ライン V<sub>PL</sub> と偶数ビットライン BL<sub>e</sub> との間の電気的連結を制御する第 1 トランジスタ P<sub>1</sub>、及びプリチャージ電圧供給ライン V<sub>PL</sub> と奇数ビットライン BL<sub>o</sub> との間の電気的連結を制御する第 2 トランジスタ P<sub>2</sub> を含むことができる。

20

【0117】

選択ワードラインに印加されるパルスのうち、N 番目パルスに相応するプリチャージ動作時、第 1 トランジスタ P<sub>2</sub> がターンオフされた後、第 2 トランジスタ P<sub>1</sub> がターンオンされ、(N+1) 番目パルスに相応するプリチャージ動作時、第 2 トランジスタ P<sub>1</sub> がターンオフされた後、第 1 トランジスタ P<sub>2</sub> がターンオンされる。

【0118】

即ち、プリチャージ回路 130a は、パルス毎に偶数ビットライン BL<sub>e</sub> 及び奇数ビットライン BL<sub>o</sub> が交代してブースト電圧 V<sub>bvoost</sub> に充電されるように、プリチャージ電圧の供給タイミングを制御する。

30

【0119】

不揮発性メモリ装置 100a は更に、第 1 トランジスタのゲートに印加される第 1 プリチャージ信号 P<sub>Re</sub> 及び第 1 トランジスタのゲートに印加される第 2 プリチャージ信号 P<sub>Ro</sub> を発生する、図示しないプリチャージ制御回路を含むことができる。このようなプリチャージ制御回路はプリチャージ回路 130a に含めることもでき、全体プログラム動作を制御する図示しないコントローラの一部において構成することもできる。

【0120】

図 15 は、図 14 に示した本発明の一実施例によるプリチャージ回路の動作を説明するためのタイミング図である。

40

【0121】

図 15 には、プリチャージ信号 (P<sub>Re</sub>、P<sub>Ro</sub>) 及びプリチャージ信号 (P<sub>Re</sub>、P<sub>Ro</sub>) の遷移によるビットライン (BL<sub>e</sub>、BL<sub>o</sub>) の電圧が図示されている。

【0122】

時間 t<sub>31</sub> 乃至時間 t<sub>34</sub> は、N 番目パルスに相応するプログラム区間で、時間 t<sub>41</sub> 乃至時間 t<sub>44</sub> は、(N+1) 番目パルスに相応するプログラム区間である。

【0123】

時間 t<sub>31</sub> で第 1 プリチャージ信号 P<sub>Re</sub> が活性化されると、第 1 トランジスタ P<sub>1</sub> がターンオンされ、偶数ビットライン BL<sub>e</sub> にプリチャージ電圧、例えば、電源電圧 V<sub>cc</sub> が印加される。

【0124】

50

時間  $t_{31}$  からは、プログラムが禁止される偶数ビットライン  $BLe$  及びこれに連結されたメモリセルのチャンネルが電源電圧  $Vcc$  に充電された後、第1プリチャージ信号  $PRE$  が非活性化され偶数ビットライン  $BLe$  がフローティングされる。

#### 【0125】

時間  $t_{32}$  で第2プリチャージ信号  $PRO$  が活性化されると、第2トランジスタ  $P2$  がターンオンされ、奇数ビットライン  $BL_o$  に電源電圧  $Vcc$  が印加される。

#### 【0126】

従って、時間  $t_{32}$  で偶数ビットライン  $BLe$  はブースト電圧 ( $Vcc(1+ \dots)$ ) に、奇数ビットライン  $BL_o$  は電源電圧  $Vcc$  に充電される。

#### 【0127】

時間  $t_{33}$  で、第2プリチャージ信号が非活性化されると、選択ワードラインにN番目パルスが印加されプログラムが行われる。

10

#### 【0128】

これとは逆に、時間  $t_{41}$  では第2プリチャージ信号  $PRO$  がまず活性化され、奇数ビットライン  $BL_o$  及びここに連結されたメモリセルのチャンネルが電源電圧  $Vcc$  に安定化された後、第2プリチャージ信号が非活性化される。その後、時間  $t_{42}$  で第1プリチャージ信号  $PRE$  が活性化され、時間  $T_{43}$  で第1プリチャージ信号  $PRE$  が非活性化された後、選択ワードラインに ( $N + 1$ ) 番目パルスが印加される。

#### 【0129】

従って、N番目パルスに相応するプログラムとは逆に、偶数ビットライン  $BLe$  は電源電圧  $Vcc$  に、奇数ビットライン  $BL_o$  はブースト電圧 ( $Vcc(1+ \dots)$ ) に充電される。

20

#### 【0130】

以上の実施例では、NAND型フラッシュメモリ装置を例として本発明を説明したが、本発明は、NAND型フラッシュメモリ装置のみに適用されるわけではなく、奇数ビットラインと偶数ビットラインとがそれぞれ1つのページを形成してプログラム電圧として複数のパルスを使用する不揮発性メモリ装置にも適用することができる。

#### 【産業上の利用可能性】

#### 【0131】

前述したように、本発明の実施例による不揮発性メモリ装置におけるプログラム方法及びこのプログラムを適用する不揮発性メモリ装置は、ビットライン間の容量性結合を利用してメモリセルのプログラム搅乱を減少させることができ、バス電圧のウィンドウマージンを増加することができる。

30

#### 【0132】

又、本発明の実施例による不揮発性メモリ装置におけるプログラム方法及びこのプログラムを適用する不揮発性メモリ装置は、既存の装置を大きく変更することなく、またプログラム時間を増加させることなく、プログラム搅乱を減少させることができる。

#### 【0133】

以上、本発明の実施例によって詳細に説明したが、本発明はこれに限定されず、本発明が属する技術分野において通常の知識を有するものであれば本発明の思想と精神を離れることなく、本発明を修正または変更することができる。

40

#### 【図面の簡単な説明】

#### 【0134】

【図1】従来の不揮発性メモリ装置におけるプログラム方法を示すタイミング図である。

【図2】図1の従来の不揮発性メモリ装置におけるプログラム方法によるビットラインとチャンネルの電圧変化を示す図である。

#### 【図3】従来の不揮発性メモリ装置を示す回路図である。

【図4】図3の従来の不揮発性メモリ装置におけるプログラム方法によるビットラインとチャンネルの電圧変化を示す図である。

#### 【図5】本発明の一実施例による不揮発性メモリ装置におけるプログラム方法を示す流れ

50

図である。

【図6】本発明の一実施例による不揮発性メモリ装置を示すブロック図である。

【図7】本発明の一実施例によるビットライン間の容量性結合を示す図である。

【図8】図6の本発明の一実施例による不揮発性メモリ装置で順次に印加されるパルスに相忾するビットラインの電圧を示す図である。

【図9】図6の本発明の一実施例による不揮発性メモリ装置で順次に印加されるパルスに相忾するビットラインの電圧を示す図である。

【図10】本発明の一実施例による不揮発性メモリ装置におけるプログラム方法によるビットラインとチャンネルの電圧変化を示す図である。

【図11】本発明の一実施例によるチャンネルのブースト効果を説明するためのメモリセルの断面図である。 10

【図12】図5の本発明の一実施例による不揮発性メモリ装置におけるプログラム方法を説明するためのタイミング図である。

【図13】図5の本発明の一実施例による不揮発性メモリ装置におけるプログラム方法を説明するためのタイミング図である。

【図14】図6の本発明の一実施例による不揮発性メモリ装置を示す回路図である。

【図15】図14の本発明の一実施例によるプリチャージ回路の動作を説明するためのタイミング図である。

【符号の説明】

【0135】

110、110a：メモリセルアレイ、120、120a：ページバッファブロック、125：ページバッファ、130、130a：プリチャージ回路、140：行選択回路、WL：ワードライン、BLE：偶数ビットライン、BLO：奇数ビットライン 20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図 1 3】

【図 1 4】

---

フロントページの続き

(72)発明者 李 永宅

大韓民国ソウル特別市松坡区可樂本洞デリムアパート5棟510号

(72)発明者 金 奇南

大韓民国ソウル特別市江南区大峙洞511番地ハンボミドアパート109棟1206号

(72)発明者 金 杜坤

大韓民国京畿道水原市靈通区靈通洞1013-5番地屋塔号

審査官 滝谷 亮一

(56)参考文献 特開平11-251896(JP,A)

特開2002-251896(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 16 / 06

G 11 C 16 / 02

G 11 C 16 / 04