(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4082706号

(P4082706)

(45) 発行日 平成20年4月30日(2008.4.30)

(24) 登録日 平成20年2月22日(2008.2.22)

(51) Int.Cl.

G06F 9/45 (2006.01)

F 1

G06F 9/44 322 F

請求項の数 6 (全 33 頁)

(21) 出願番号 特願2005-114842 (P2005-114842)

(22) 出願日 平成17年4月12日 (2005.4.12)

(65) 公開番号 特開2006-293768 (P2006-293768A)

(43) 公開日 平成18年10月26日 (2006.10.26)

審査請求日 平成19年3月2日 (2007.3.2)

早期審査対象出願

前置審査

(73) 特許権者 899000068

学校法人早稲田大学

東京都新宿区戸塚町1丁目104番地

(74) 代理人 100075513

弁理士 後藤 政喜

(72) 発明者 笠原 博徳

東京都新宿区大久保3丁目4番1号 学校

法人 早稲田大学 理工学部内

(72) 発明者 木村 啓二

東京都新宿区大久保3丁目4番1号 学校

法人 早稲田大学 理工学部内

(72) 発明者 白子 準

東京都新宿区大久保3丁目4番1号 学校

法人 早稲田大学 理工学部内

最終頁に続く

(54) 【発明の名称】マルチプロセッサシステム及びマルチグレイン並列化コンパイラ

## (57) 【特許請求の範囲】

## 【請求項 1】

单一または複数種類のプロセッサユニットを複数個有するマルチプロセッサシステムに実行させる目的プログラムを生成するコンパイラであって、

前記プロセッサユニットは、特定用途プロセッサユニットと汎用プロセッサユニットとを含み、

入力プログラムを読み込む処理と、

前記入力プログラムを解析し、前記入力プログラムを複数の粒度の単位ブロックに分割する処理と、

前記単位ブロック間の制御依存性、及びデータ依存性を解析し、前記単位ブロックの並列性を抽出する処理と、

前記マルチプロセッサシステムが具備する各プロセッサユニットで前記単位ブロックを処理するために必要な演算サイクル時間をコスト情報として求める処理と、

前記コスト情報に基づいて前記入力プログラムの処理時間が最小となるように、前記単位ブロックを処理するのに必要な前記特定用途プロセッサユニットを選択し、さらに少なくともひとつの中間プロセッサユニットを選択し、これら特定用途プロセッサユニットと汎用プロセッサユニットを1つのグループとして前記単位ブロックを割り当てるスケジューリングコードを生成する処理と、

前記スケジューリングコードを入力プログラムに付加し、前記各プロセッサユニット毎の実行コードを生成し、目的コードとして出力する処理と、

10

20

を計算機に実行させることを特徴とするマルチグレイン並列化コンパイラ。

【請求項 2】

单一または複数種類のプロセッサユニットを複数個有するマルチプロセッサシステムに実行させる目的プログラムを生成するコンパイラであって、

前記プロセッサユニットは、特定用途プロセッサユニットと汎用プロセッサユニットとを含み、

入力プログラムを読み込む処理と、

前記入力プログラムを解析し、前記入力プログラムを複数の粒度の単位ブロックに分割する処理と、

前記単位ブロック間の制御依存性、及びデータ依存性を解析し、前記単位ブロックの並列性を抽出する処理と、

前記マルチプロセッサシステムが具備する各プロセッサユニットで前記単位ブロックを処理するために必要な電力をコスト情報として求める処理と、

前記コスト情報に基づいて前記入力プログラムの処理時間が最小となるように、前記単位ブロックを処理するのに必要な前記特定用途プロセッサユニットを選択し、さらに少なくともひとつの汎用プロセッサユニットを選択し、これら特定用途プロセッサユニットと汎用プロセッサユニットを1つのグループとして前記単位ブロックを割り当てるスケジューリングコードを生成する処理と、

前記スケジューリングコードを入力プログラムに付加し、前記各プロセッサユニット毎の実行コードを生成し、目的コードとして出力する処理と、

を計算機に実行させることを特徴とするマルチグレイン並列化コンパイラ。

【請求項 3】

前記スケジューリングコードを生成する処理は、

前記単位ブロックをスケジューリングによって割り当てられたプロセッサユニットで演算した際に、前記演算に必要とする時間が前記スケジューリングで許容された時間内であった場合は、

前記プロセッサユニットの演算に際して消費する電力を低減するためプロセッサユニットに与える動作電圧及び動作クロックを変化または遮断するための制御コードを生成する処理を含むことを特徴とする請求項1または請求項2に記載のマルチグレイン並列化コンパイラ。

【請求項 4】

前記スケジューリングコードを生成する処理は、

前記単位ブロックをスケジューリングによって割り当てられたプロセッサユニット以外のプロセッサユニットについて、動作クロック及び動作電源の供給を遮断するための制御コードを生成することを特徴とする請求項1または請求項2に記載のマルチグレイン並列化コンパイラ。

【請求項 5】

前記実行コードを生成し、目的コードとして出力する処理は、

前記各プロセッサユニットの種類に応じたローカルコンパイラを用いて前記実行コードを生成することを特徴とする請求項1または請求項2に記載のマルチグレイン並列化コンパイラ。

【請求項 6】

前記マルチプロセッサシステムは、前記プロセッサユニットに複数のクロック周波数の内の一つを動作クロックとして供給するクロック供給部と、前記プロセッサユニットに複数の電圧の内の一つを動作電圧として供給する供給する電力供給部と、前記クロック供給部及び電力供給部がプロセッサユニットに供給する動作クロックと動作電圧とを設定するシステム制御レジスタを有し、

前記スケジューリングコードを生成する処理は、

前記単位ブロックをスケジューリングによって割り当てられたプロセッサユニットで演算した際に、前記演算に必要とする時間が前記スケジューリングで許容された時間内であ

10

20

30

40

50

つた場合は、

前記プロセッサユニットの演算に際して消費する電力を低減するため前記システム制御レジスタに設定する値を変更する制御コードを生成する処理を含むことを特徴とする請求項1または請求項2に記載のマルチグレイン並列化コンパイラ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のプロセッサユニットで構成されるマルチプロセッサシステムにおいて、当該複数プロセッサユニットを効率よく動作させることを可能とするマルチプロセッサシステムのハードウェア構成及びプログラムを生成するコンパイラに関する。 10

【背景技術】

【0002】

半導体製造技術の進歩による素子の微細化により、膨大な数のトランジスタを集積することが可能となっている。それと同時にプロセッサの高周波数化も進むが、動作時電力の増加、またリーク電流に起因する待機時電力の増加により、従来のプロセッサが歩んできた動作周波数の向上と論理方式の改善により達成してきた性能向上に限界が見え始めている。

【0003】

そこで現在、性能改善と低電力化を実現する手段として、従来のCPU、DSPといったプロセッサユニット（以下、PUとする）を複数個オンチップで搭載し、処理を並列で行うことで、動作周波数を向上させなくとも、高い演算性能を得ることが可能、マルチプロセッサシステム（シングルチップ・マルチプロセッサシステム）が有望となっている。将来、微細化がさらに進むことで、PUをオンチップで100個～1000個積載することも可能となると予測される。 20

【0004】

このようなマルチプロセッサシステムにおいて、PUの数に比例した演算性能を得るためにには、搭載されたPUを同時に稼動させプログラムを処理する必要がある。しかしながら、通常の入力プログラムは処理が時系列で逐次的に記述されているため、複数のPUを搭載するにも拘わらず、当該複数PUに比例して期待される演算性能を得ることができない。 30

【0005】

この問題点を解決するための一つの方法として、プログラム開発者が自らプログラムの並列性を考慮し、当該プログラムを実行させるマルチプロセッサシステムの構成に基づいて、当該プログラムを複数のPUで実行させるための並列化コードを付加する必要がある。しかしながら、本手法はPUが数個のシステムにおいては有効であるが、将来の数十～数千といった数のPUが積載されたシステムにおいては、また特にPUが異種で構成される場合は、開発時間、実効性能の点で実用的ではない。

【0006】

そこで、構成及び演算性能が同種の複数PUで構成されたマルチプロセッサシステムにおいて、入力プログラムを解析し、当該プログラム中から並列に動作可能な部分を抽出し、当該部分を複数のPUに割り当て同時に実行することを可能とする、自動並列化コンパイラの研究がすでに行われている。例えば、入力ソースプログラムを解析し、当該プログラムをサブルーチンやループなどさまざまな粒度のブロック（タスク）に分割し、当該複数タスク間の並列性を解析すると共に、タスクとそれらがアクセスするデータをキャッシュあるいはローカルメモリに適合するサイズに分割し、それらを各PUに対して当該タスクを最適割り当てすることによって、マルチプロセッサシステムを効率よく動かす目的プログラムを生成するコンパイル方式が、特許文献1に開示されている。またマルチグレイン並列処理の機能をサポートするチップマルチプロセッサのアーキテクチャとしては、特許文献2に開示されている。 40

【0007】

50

また、電力消費の低減及び排熱の低減のため、マルチプロセッサシステムにおいて各PUの低電力化が必須となるが、個別のプロセッサに関して低電力化する手法に関し、様々な提案が行われている。例えば、リアルタイム処理制約内でプロセッサの動作クロックを低減させ、そのクロック周波数に応じた電圧プロセッサに供給する、という周波数・電圧を動的に制御することにより低電力化を達成する手法が、特許文献3、4で開示されている。

#### 【0008】

また、画像処理など予め処理の手順が判明しているアプリケーションにおいて、各処理の特性に合わせてCPUやDSPなどの種類の異なる複数のプロセッサを組み合わせ、当該プロセッサ上での処理時間や消費電力情報を予め測定し与えておくことで、当該情報により動的に一連の処理を当該各プロセッサに割り当てる手法が、特許文献5に開示されている。

10

【特許文献1】特開2004-252728号

【特許文献2】特開2001-175619号

【特許文献3】特許第3138737号

【特許文献4】特開2004-234126号

【特許文献5】特開2004-252900号

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0009】

20

現在、自動車のナビゲーションシステム、携帯電話、デジタルテレビなどといった、画像、音声、データベース情報など多様なデータを同時に扱う新アプリケーションが生まれる中で、様々な種類の入力データを、当該データ夫々に最適な方法で同時に処理するために、プロセッサは複数種類のPUを搭載することになると考えられる。従来のマルチプロセッサシステムでは、上記特許文献1で開示されているように同じ構成のPUを複数搭載したホモジニアスなプロセッサシステムであった。

#### 【0010】

しかしながらこのように、多様なアプリケーションが同時に多種のPU上で処理される将来のヘテロジニアスマルチプロセッサシステムにおいて、搭載するPUの種類と数に比例して処理性能を得るために、PUの種類を考慮したプログラムの並列化と配置が必須となるという問題がある。

30

#### 【0011】

また従来、複数のPU上でプログラムを効率よく実行するためには、小規模なプログラムや処理シーケンスが常に固定的に実行できる場合、スケジューリングを行うための実行時間などのスケジュール情報を得るために、一度プログラムを当該システム上で実行して処理時間などを測定することが必要となり、当該測定値を元に開発者が予め当該スケジュール情報を手動で生成する必要があり、多大な労力と時間がかかる。

#### 【0012】

この場合、事前に処理の内容やシーケンスが不明な一般的のプログラムの場合、特に規模が大きなプログラムの場合は、当該情報を事前に手動で生成することが困難となる。またPUの種類や数が増加した場合も同じく、当該情報を手動で生成することが困難となる。

40

#### 【0013】

また、多数のPUが搭載されるシステムでは、プロセッサ全体の消費電力増大が懸念されるため、特に携帯電話などのモバイル機器や、家庭で使用されるデジタルテレビなどに適用することを考慮すると、従来のOSによるFV(動作周波数と駆動電圧)制御のみならず、各アプリケーションプログラム内でのソフトウェアによる各PUの処理状況によりきめ細かい電源管理や動作周波数制御が必要となる。

#### 【0014】

特に、処理性能を落とさずに消費電力を低減する必要がある。また、実時間処理を要求するプログラムを実行するに際しても、時間制約を遵守しつつ、電力を低減する必要があ

50

る。

【0015】

そこで本発明は、多様な種類のPUを搭載するマルチプロセッサシステムにおいて、処理対象となる入力プログラムから自動的に並列性を持つタスクを抽出し、各PUの特性に合わせて当該タスクを配置することで当該PUを効率よく動かし、さらに当該PUの処理量を見積もることで動作周波数や電源電圧を最適化するコードを生成し、目的プログラムに付加するコンパイラ及びその最適化を可能とするマルチプロセッサシステムを提供することを目的とする。

【課題を解決するための手段】

【0017】

本発明は、单一または複数種類のプロセッサユニットを複数個有するマルチプロセッサシステムに実行させる目的プログラムを生成するコンパイラであって、前記プロセッサユニットは、特定用途プロセッサユニットと汎用プロセッサユニットとを含み、入力プログラムを読み込む処理と、前記入力プログラムを解析し、前記入力プログラムを複数の粒度の単位ブロックに分割する処理と、前記単位ブロック間の制御依存性、及びデータ依存性を解析し、前記単位ブロックの並列性を抽出する処理と、前記マルチプロセッサシステムが具備する各プロセッサユニットで前記単位ブロックを処理するために必要な演算サイクル時間をコスト情報として求める処理と、前記コスト情報に基づいて前記入力プログラムの処理時間が最小となるように、前記単位ブロックを処理するのに必要な前記特定用途プロセッサユニットを選択し、さらに少なくとも一つの汎用プロセッサユニットを選択し、これら特定用途プロセッサユニットと汎用プロセッサユニットを一つのグループとして前記単位ブロックを割り当てるスケジューリングコードを生成する処理と、前記スケジューリングコードを入力プログラムに付加し、前記各プロセッサユニット毎の実行コードを生成し、目的コードとして出力する処理と、を計算機に実行させる。

また、单一または複数種類のプロセッサユニットを複数個有するマルチプロセッサシステムに実行させる目的プログラムを生成するコンパイラであって、前記プロセッサユニットは、特定用途プロセッサユニットと汎用プロセッサユニットとを含み、入力プログラムを読み込む処理と、前記入力プログラムを解析し、前記入力プログラムを複数の粒度の単位ブロックに分割する処理と、前記単位ブロック間の制御依存性、及びデータ依存性を解析し、前記単位ブロックの並列性を抽出する処理と、前記マルチプロセッサシステムが具備する各プロセッサユニットで前記単位ブロックを処理するために必要な電力をコスト情報として求める処理と、前記コスト情報に基づいて前記入力プログラムの処理時間が最小となるように、前記単位ブロックを処理するのに必要な前記特定用途プロセッサユニットを選択し、さらに少なくとも一つの汎用プロセッサユニットを選択し、これら特定用途プロセッサユニットと汎用プロセッサユニットを一つのグループとして前記単位ブロックを割り当てるスケジューリングコードを生成する処理と、前記スケジューリングコードを入力プログラムに付加し、前記各プロセッサユニット毎の実行コードを生成し、目的コードとして出力する処理と、を計算機に実行させる。

【発明の効果】

【0021】

したがって、本発明により、入力プログラムをコンパイルする際に、プロセッサユニットの構成に基づきコンパイラが予め事前の処理時間を見積もり、コンパイル時に処理順序を静的に決定できる部分に関しては事前に処理手順を決定しておき、また実行時にならないと処理順序が決定できない部分に関しては、コンパイラが実行時間を含んだ処理情報に基づいたスケジューリングを動的に行うプログラムを生成することで、一般的のプログラムを多種のプロセッサユニットで構成されるマルチプロセッサシステム上で効率よく処理できる。

【0022】

また、入力プログラムをコンパイラが解析し、事前に処理手順を決定した後に処理時間を見積もり、時間制約に対する当該処理時間の余裕度を見てプロセッサユニット毎に電源

10

20

30

40

50

管理や周波数制御をきめ細かく行うことで、電力を大きく低減できる。

【0023】

また、異種のプロセッサユニットで構成されるマルチプロセッサにおいて、実行時間最小となるよう入力プログラムを並列化しスケジューリングした後、各プロセッサユニット間で処理時間が最小となるよう、プロセッサユニット毎にきめ細かく動作周波数制御及び電源管理を行うことで、性能を損なわずに電力を最適化できる。

【発明を実施するための最良の形態】

【0024】

以下、本発明の一実施形態を添付図面に基づいて説明する。

【0025】

<実施形態の全体構成>

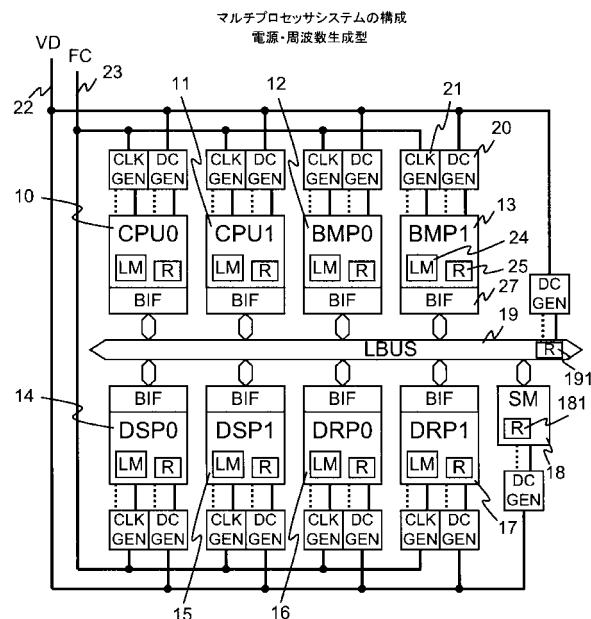

図1は、本発明の一実施形態であるマルチプロセッサシステムの構成を示す。図1において、マルチプロセッサシステムは、複数の異種のプロセッサユニット（以下、PUとする）10～17と、これら共有メモリ（以下、SMとする）18を主体にして構成される。当該各PU10～17は、それぞれのバスインターフェース（BIF）27を介し、ローカルバス（LBUSとする）19に接続される。また、SM18はLBUS19に接続され、各PU10～17からアクセスすることができる。当該各PU10～17は、当該PUに対し電源電圧及び動作クロックを供給する電源電圧生成回路（DCGEN）20、及びクロック生成回路（CLKGEN）21が接続されている。なお、本マルチプロセッサシステムは、異種のプロセッサユニットで構成されたヘテロジニアスマルチプロセッサシステムの例を示す。

【0026】

本実施形態ではPUの種類と個数を、2個の汎用処理プロセッサ（以下、CPU）10、11と、2個の信号処理プロセッサ（以下、DSP）14、15と、2個の動的再構成可能プロセッサ（以下、DRP）16、17と、及び2個のビット演算処理プロセッサ（以下、BMP）12、13で構成した例を示す。なお、上記PUの種類や数は本実施形態で示した限りではなく、さまざまな構成を取り得る。また、従来の同種のPUのみによる構成（例えばCPUのみ4個で構成）としても良い。また、本実施形態では、DSP（0、1）14、15と、DRP（0、1）16、17と、BMP（0、1）12、13を特定用途プロセッサユニットとし、CPU（0、1）10、11を汎用プロセッサユニットとする。

【0027】

また、動的再構成可能プロセッサ16、17は、処理回路を動的に再構成することができるプロセッサを指し、限られたコア内で仮想的に回路を変更することができる。

【0028】

上記各PU10～17は、各PUで処理されるプログラムやデータを一時的に保存するローカルメモリ（またはキャッシュ）（LM）24及び、当該PUに対する供給電圧（VL）や動作周波数（FL）を決定する周波数・電源電圧（FV）制御、及びPU間の同期制御を行うためのシステム制御レジスタ（R）25を具備する。なお、ローカルメモリ（LM）24は、他のPU及び当該LMを持つ自PUからアクセス可能なグローバルアドレスがマッピングされている領域と、当該自PUのみアクセス可能なプライベートアドレスがマッピングされている領域に分割される。なお、LBUS19に接続された共有メモリ（SM）18はグローバルアドレスがマッピングされており、複数のPUからアクセス可能である。なお、以上は本発明における適用構成の一例に過ぎず、実施の形態としてはこの限りでない。例えば図1では表現されていないが、LBUS19には入出力処理、割り込み処理、タイマ、デバッグ回路、等の周辺回路を必要に応じて接続することとなる。また、バスブリッジを介して、同種類または異種類のバスを階層的に接続してもよい。

【0029】

また、各PU10～17で共有されるSM18には、SM18に供給する供給電圧（VL）や動作周波数（FL）を設定して、周波数・電源電圧（FV）制御を行うためのシス

10

20

30

40

50

システム制御レジスタ (R) 181を具備する。また、前記PU及び前記SMを相互に接続するローカルバスLBUS19には、LBUS19に供給するVLやFLを設定して、FV制御を行うためのシステム制御レジスタR191を具備する。なお、このシステム制御レジスタ (R) 181に代わって、各PU10～17のシステム制御レジスタ (R) 25のそれぞれに、SM18及びLBUS19のFV制御用のレジスタを設けても良い。また、システム制御レジスタ (R) 181は、PU10～17のいずれか一つによって設定される。

#### 【0030】

なお、上記PU10～17は、一つのチップ (LSI) 上に構成された場合を示すが、PU10～17を構成する複数のLSIを結合し、一つのチップまたはモジュールとしたものであっても良い。 10

#### 【0031】

また、SM18は、プロセッサの種類毎 (CPU、DSP、DRP、BMP毎) に共有するようにしても良く、例えば、後述する図10のように、SM18の領域をバンクに分割し、各バンクをプロセッサの種類毎に共有することもできる。あるいは、SM18の一部を複数のPUで共有するようにしても良い。

#### 【0032】

＜電圧・周波数可変回路＞

次に、各PUに接続された電源電圧生成回路 (DCGEN) 20及びクロック生成回路 (CLKGEN) 21の構成について説明する。 20

#### 【0033】

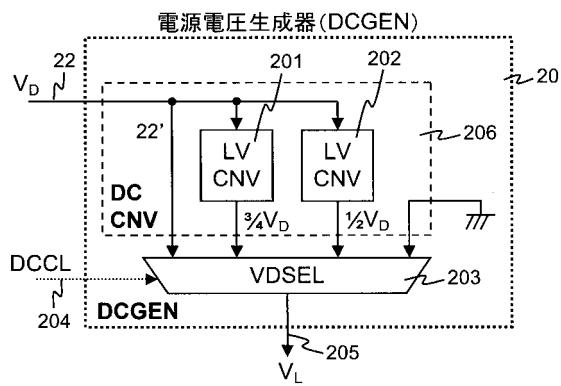

図2は、DCGEN20の構成を示す。DCGEN20は外部より供給された通常の電源電圧 (VD) 22を予め指定した複数の供給電圧 (VL) 205に降圧 (または昇圧) する回路 (DCCNV) 206、生成した複数の当該供給電圧よりPUへ供給する電圧を選択する供給電圧選択回路 (VDSSEL) 203、及び電源電圧を遮断する回路 (後述) で構成する。

#### 【0034】

なお降圧 (または昇圧) 回路 (DCCNV) 206は、複数の電圧降下部を含み、例えば、図2のように、電源電圧VDをそのまま供給する回路22'、電源電圧VDを3/4に低下する降圧回路 (LVCNV) 201と、電源電圧VDを1/2に低下する降圧回路 (LVCNV) 202とから構成される。 30

#### 【0035】

各PU10～17は、当該PUが持つシステム制御レジスタ (R) 25内のFV制御レジスタに設定されたFV (駆動周波数及び駆動電圧) モードにより制御線 (DCCCL) 204を介して供給電圧選択回路 (VDSSEL) 203を制御することで、降圧回路 (DCCNV) 206で生成された複数の電圧のうちいずれかひとつを選択し、当該選択された供給電圧VLが対応するPU10～17に供給される。なお、FV制御レジスタはシステム制御レジスタ25の内の所定の領域に設定されるものである。

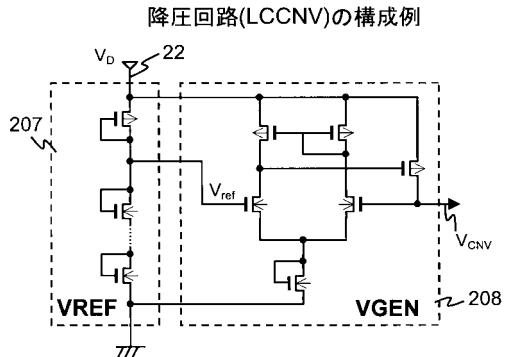

#### 【0036】

電源電圧を降圧する回路 (LVCNV) の構成の一例を図3に示す。上記図2の降圧回路LVCNV201、202は、供給電圧 (3/4VD) を決定する参照電圧生成回路 (VREF) 207、及び参照電圧で指定した電圧まで降圧しPUに対し電流を供給する電源生成回路 (VGEN) 208で構成され、電源生成回路208の出力が図2の供給電圧選択回路203に入力される。 40

#### 【0037】

降圧回路LVCNVの出力電圧 (V<sub>CNV</sub>) は、参照電圧を決定する参照電圧生成回路 (VREF) 207内のnMOSFETの段数により決まり、FV制御レジスタで指定する電圧を供給するよう、LVCNVの構成は決定される。以上の回路で降圧した複数の電圧から、PUからの制御線204により指定された電圧を選択し、各PU10～17へ出力 (205) する。 50

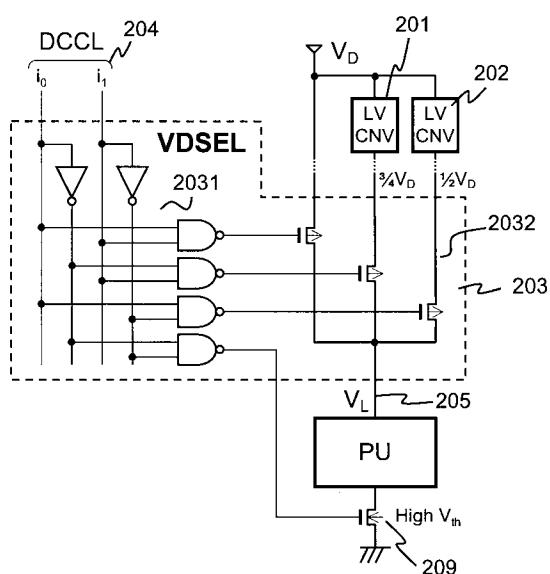

## 【0038】

図4は、供給電圧選択回路(VDSEL)203の構成の一例を示す。供給電圧選択回路(VDSEL)203は制御信号デコード部2031と電圧選択スイッチ2032で構成する。また、PUのソース電圧供給部にしきい値の高いnMOSFET209を挿入することで、当該PUの電源遮断時に流れるリーク電流を低減することができる。なお、図3、図4の構成は、降圧回路LVCNVの機能を実現するための一つの構成に過ぎず、他の様々な電源電圧生成回路方式を適用しても良い。

## 【0039】

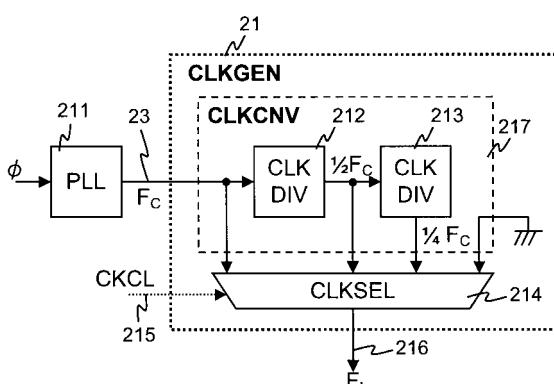

続いて図5に、クロック生成回路(CLKGEN)21の構成の一例について説明する。CLKGEN21は、内部クロックFC(23)を当該内部クロックの1/2、1/4など内部クロックFCを整数分の1に低減する分周回路212、213、及び分周生成した複数のクロックから、当該PUへ供給するクロック(FL)216を選択する、クロックパルス選択器(CLKSEL)214で構成する。なお、内部クロックFC(23)は、PLL(Phase Locked Loop)回路211にて、外部から入力されたシステムクロックを、指定した倍率で倍率することで生成される。

## 【0040】

クロックパルス選択器(CLKSEL)214の構成の一例を図6に示す。CLKSEL214は入力制御信号CKCLのデコード部2171と、クロック信号選択部2172で構成する。各PUは、当該PUが持つFV制御レジスタのモードにより制御線(CKCL)215を介してDCSEL214を制御することで、生成された複数のクロックより指定されたFLが選択され、当該クロックFL216の供給を受ける。

## 【0041】

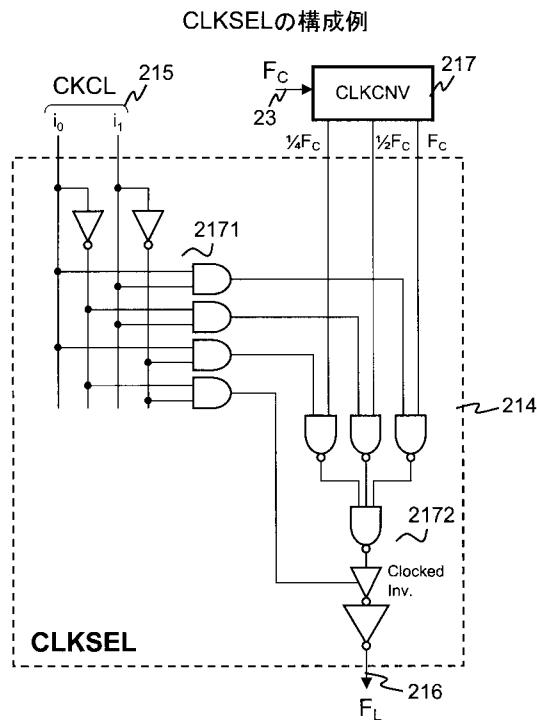

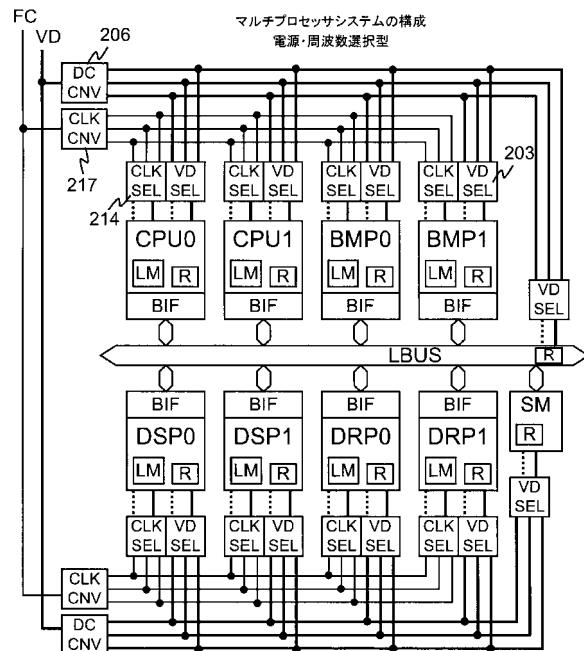

なお、上記図1に示した構成の他にも図7に示すように、電源電圧、クロックパルスを変換する回路(DCCNV206、CLKCNV217)を複数PU(またはPU全体)に対し各1個付加し、各PU側に生成した複数種類の電源電圧及びクロックパルスを選択する回路(VDSEL203、CLKSEL214)を付加する構成としても良い。図7の例では、2組の電源電圧生成回路206とクロック生成回路217が、それぞれ4つのPUに電力とクロックを供給する場合を示す。

## 【0042】

このように、電源電圧及びクロックパルスを生成、供給する回路は様々な構成を取り得ることができ、その構成は以上に示した限りではない。例えば、電源電圧を変換する回路DCCNV206を複数PU(またはPU全体)に対し1個付加し、クロックパルスを生成する回路CLKCNV217はPU側にPU毎に付加する構成とすることもできる。また、例えば、クロックパルスを生成する回路CLKCNV217を複数PU(またはPU全体)に対し1個付加し、電源電圧を変換する回路DCCNV206はPU側にPU毎に付加する構成とすることもできる。また、例えばチップ内にDCCNV206を搭載せず、チップ外部にて生成した複数種類の電源電圧を入力し、VDSELにて所望の供給電圧VL205を選択供給する構成としてもよい。

## 【0043】

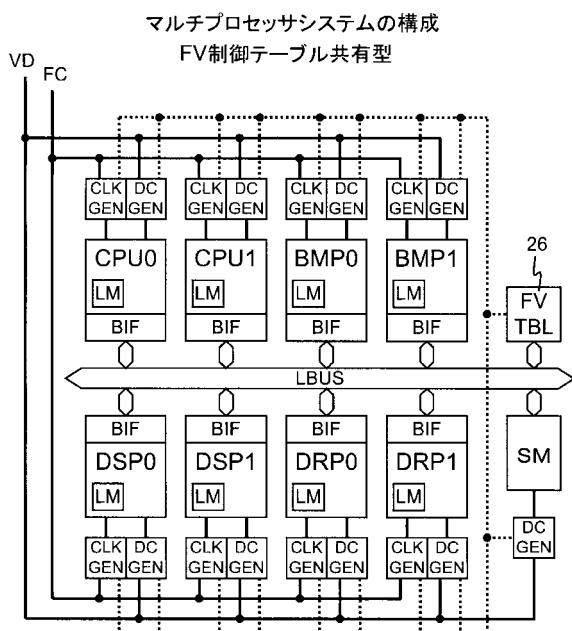

また、FV制御モードを設定する手段として、図1や図7に示した各PUが当該PUのFV制御を行うFV制御レジスタ(システム制御レジスタ(R)25)を持つ構成とする他に、図8に示すように各PU10~17のFV制御モードを一括して保持するFV制御テーブル(FVTBL)26をLBUS19に接続する構成としてもよい。図8においては、図1においてシステム制御レジスタ25に含まれていたFV制御レジスタを、ローカルバスLBUS19に接続されたFV制御テーブル26とし、集約したものである。

## 【0044】

FV制御テーブル(FVTBL)26は各PU10~17からアクセス可能であって、共有メモリSMの一部に設定されてもよいし、共有メモリSMから独立したメモリ(またはレジスタ)で構成されても良い。

## 【0045】

10

20

30

40

50

## &lt;バスIF&gt;

以上のように、各PU10～17は電源電圧を個別に設定することが可能なため、当該PUと接続されたLBUS19間においては、信号の電圧レベルが異なることになる。そこで、PU10～17とLBUS19間に接続されたバスインターフェース(BIF)27は信号レベル変換回路(図示省略)を具備し、バスLBUS19とPU10～17間の信号レベル変換を行う。

## 【0046】

## &lt;PUに対する電圧・周波数モードの与え方&gt;

次に、電源電圧生成回路(DCGEN)20及びクロック生成回路(CLKGREN)21で生成する電源電圧(VL)205及び動作クロック(FL)216を決定するハードウェア機構について説明する。

## 【0047】

電源電圧生成回路DCGEN20及びクロック生成回路CLKGREN21の動作モード(供給するVL、FL値)は設計時に予め決定されており、各PUは前記回路に対し当該PUが具備するFV制御レジスタの値によって制御線DCCCL、CKCLを介して指定する。VL、FLの設定方法の詳細に関しては後述するが、コンパイラがFV制御レジスタをセットする制御コードを生成し、当該コードを実行する汎用プロセッサCPU0またはCPU1が、メモリマップされたFV制御レジスタにアクセスして値を書き換える。

## 【0048】

本実施形態におけるPU10～17のFVモードは、VL、FLの組み合わせを4段階(FV制御レジスタ内の2ビット)として設定する。図9にPU10～17の動作モード一覧を示す。つまり、FV制御レジスタの2ビットの値が“00”においてはVL=0、FL=0の電圧・周波数遮断となるOFFモードに設定され、上記レジスタ値が“11”においては、VL=VDでシステムの電源電圧と等価、FL=FCでシステムの動作周波数と等価とするFULLモードが設定される。

## 【0049】

またレジスタ値が“01”ではVL=(1/2)VD、FL=(1/4)FCとなるLOWモードに設定され、レジスタ値が“10”ではVL=(3/4)VD、FL=(1/2)FCとなるMIDDLEに設定される。なお、VL・FLモードの数、またVL値・FL値は、構築するシステムの形態やアプリケーション、使用するプロセス技術、等により、決定される。

## 【0050】

## &lt;PU内の部分的なFV制御&gt;

以上ではFV制御を対象とする範囲をPU全体とし、一括でFV制御モードを設定するとして説明したが、PU10～17に搭載するローカルメモリ(LM)やFV制御レジスタ、また他のプロセッサ周辺回路に対し、夫々異なるFV制御モード設定を行っても良い。これは、FV制御レジスタのビットフィールドを拡張し、被FV制御部に対応したFV制御モードを設定するフィールドを持たせることで実現できる。例えば、ローカルメモリLMまたはシステム制御レジスタ(R)25といったデータ保持が必要な回路部に対しては、独立にFL、VLを設定する機構とすることが考えられる。つまりローカルメモリLMやFV制御レジスタに対し独立してFV制御を行うことで、前記PUのFVが遮断状態としても、当該LM及びRのデータが保持され、また対象PUが遮断状態においても、他のPUから当該PUのLMに対しアクセスすることも可能となる。

## 【0051】

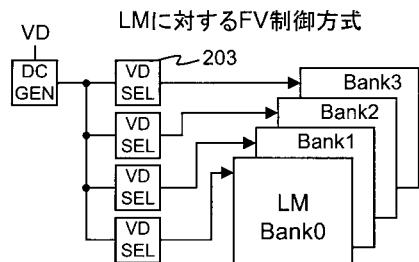

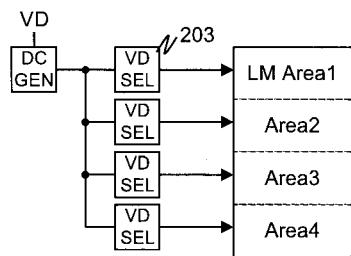

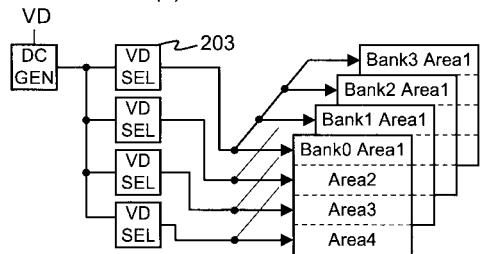

またさらに、ローカルメモリLMの構成によりFV制御対象を複数設定することができる。図10にローカルメモリLMに対するFV制御方式を示す。

## 【0052】

例えば、図10(a)に示す通りローカルメモリLMをバンク構成とし、各バンク毎(Bank0～Bank3)に対してそれぞれFV制御を実施する。このため、各Bank0～3にはそれぞれ供給電圧選択回路(VDSEL)203が接続される。

10

20

30

40

50

## 【0053】

つまり、データの保持が必要なバンクのみ通常電圧、またはデータ保持に必要な最低限の電圧を供給し、当該バンク以外の他のバンクは電源を遮断することで電力を削減すると共に、データの退避処理を行う必要がなくなるためPUの電源遮断時から通常動作時への復帰を高速に行うことが可能となる。

## 【0054】

またさらには、図10(b)に示す通り、ローカルメモリLMのアドレス空間を一定の連続したアドレス区間(Area1~Area4)で分割し、当該区間単位でFV制御を行うことで、不要なアドレス区間(記憶領域)に対する電源を遮断することで電力を削減できる。

10

## 【0055】

このため、ローカルメモリLMの各アドレス区間(Area1~Area4)毎に供給電圧選択回路(VDSEL)203が接続される。

## 【0056】

また、図10(c)に示す通り、ローカルメモリLMがバンク構成としたとき、各バンク(Bank0~3)に跨る一定の連続したアドレス区間(Area1~Area4)で分割した単位でFV制御を行う。

## 【0057】

このため、ローカルメモリLMの各Bank0~3に跨る各アドレス区間(Area1~Area4)毎に供給電圧選択回路(VDSEL)203が接続される。この構成により、バンク構成を活用しメモリアクセスを高速化するメモリインターブを実現しつつ低電力化が可能となる。

20

## 【0058】

なお、ローカルメモリLMは、機能的に当該LMを搭載するPUのみからアクセスできる部分(非共有メモリ)と、当該PUのみならず他のPUからもアクセス可能な部分(分散共有メモリ)に分割して実装してもよく、以上の2つのメモリ機能単位別でFV制御を行うことも考えられる。このため、図示はしないが、上記非共有メモリと分散共有メモリの領域毎にそれぞれ供給電圧選択回路(VDSEL)が接続される。

## 【0059】

また、図10に示したメモリ分割手法は、前記メモリ機能単位、また共有メモリSMなど、システムが搭載する様々なメモリや機能部位単位に対しても、同様に適用することが可能である。例えばPU外に配置した共有メモリSMに対しても複数バンク構成とし、各バンクに対するアクセス頻度やシステム状態(スタンバイ、スリープなど)に対応して、別途FV制御を行うようにしてもよい。

30

## 【0060】

例えば、図10(a)の構成をローカルメモリLMに代わって共有メモリSM18に適用し、共有メモリSM18をバンク(Bank0~3)に分割して、各バンク毎に供給電圧選択回路(VDSEL)203を接続することでバンク単位で電力制御を行うことができる。また、図10(b)の構成をローカルメモリLMに代わって共有メモリSM18に適用し、共有メモリSM18のアドレス空間を一定の連続したアドレス区間(Area1~Area4)で分割し、当該区間単位でFV制御を行うことで、不要なアドレス区間(記憶領域)に対する電源を遮断することで電力を削減できる。また、図10(c)の構成をローカルメモリLMに代わって共有メモリSM18に適用し、各バンク(Bank0~3)に跨る一定の連続したアドレス区間(Area1~Area4)で分割した単位でFV制御(電力制御)を行うことも可能である。なお、図10(a)~(c)を共有メモリSM18に適用する場合には、図中「LM」を「SM」と読み替えるものとする。

40

## 【0061】

<ローカルメモリLMに対するFV制御モード>

FV制御対象をPU内の複数部分(機能部分)とする例として、ローカルメモリLMに対してPUとは独立してFV制御を行う方法を以下に説明する。本例ではローカルメモリ

50

LMは図10(a)で示したように4パンク(Bank 0~3)で構成し、FV制御対象はPU及びLMパンク毎とする。

#### 【0062】

PUのFV制御モードは上記図9に示した通りである。図13にローカルメモリLMのFV制御モードの一覧を示す。LMの動作モードに関しては対象がメモリとなるため、本実施形態では通常メモリアクセス及びデータ保持が可能である通常動作モード(VL=VD、FL=FC、レジスタ値“11”)と、メモリアクセスは不可であるがデータを保持可能なデータ保持モード(VL=1/2VD、FL=0、レジスタ値“01”)と、データ保持を行わず完全に電源を遮断する、電源遮断モード(VL=0、FL=0、レジスタ値“00”)の3モードとする。

10

#### 【0063】

続いて、ローカルメモリLMを図10(a)または図10(c)のように複数のパンクで構成し、パンク毎のFV制御に対応したFV制御レジスタのフォーマットを図14(a)に示す。本例では、各PU10~17毎に、FV制御レジスタ1250を一メモリアドレスにマップし、そのフィールド(マップしたアドレス)で制御対象毎にFV制御モードを決定する。1フィールドが図示のように32ビットの場合、つまりビット1、0をPUのFV制御モード(PUFV)、ビット3、2をLMパンク0(Bank 0)のFV制御モード(LM0FV)、ビット5、4をLMパンク1(Bank 1)のFV制御モード(LM1FV)、ビット7、6をLMパンク2(Bank 2)のFV制御モード(LM2FV)、ビット9、8をLMパンク3(Bank 3)のFV制御モード(LM3FV)として、所望のフィールドをアクセスし、図13のテーブルからローカルメモリLMの動作モードを決定し、FV制御を行う。なお、PUの動作モードは、図9のテーブルに基づいて決定する。

20

#### 【0064】

FV制御レジスタ1250の設定例を図14(b)に示す。本例では、PUのモードは図14(a)のPUFVにMIDDLE(“1、0”)が設定され、ローカルメモリLMのパンク0のみを活性化し通常動作させるようLM0FVには“1、1”が設定され、LMのパンク1はデータ保持モードとなるようLM1FVには“1、0”が設定され、パンク2及びパンク3はLM2FV、LM3FVに“0、0”を設定し電源遮断としている。

30

#### 【0065】

また、上記の他にもFV制御レジスタに対し、制御対象毎にアドレスを割り振る構成としても良い。例えば、図14(c)で示すようにFV制御対象毎にレジスタをメモリアドレスにマップしたFV制御レジスタのフォーマットを示す。図14(c)では、アドレスの順にPUのFV制御モードとLMのFV制御モードを示すPUFV、LM0FV~LM3FVが格納され。

#### 【0066】

上記図14(a)で示したように、FV制御レジスタのビットフィールドで制御対象のFV制御モードを切り替える場合、当該フィールドの値を設定するためのビット演算が必要となるが、図14(c)の構成では直接当該制御対象レジスタがマップされたアドレスに直接アクセスすれば良く、FV制御レジスタの設定に関する命令数を削減することができる。しかしその反面、アドレスリソースが図14(a)と比較し多く必要となる。

40

#### 【0067】

以上では、各PUが持つFV制御レジスタを設定することで、PUやLMのFV制御モードを設定する例として説明したが、図8で説明したように各PU10~17のFV制御モードを示すFV制御レジスタを、ローカルバスLBUS19に接続されたFV制御テーブル(FVTBL)26として持たせる場合では、図15に示すように当該FVTBLを構成する。

#### 【0068】

図15は、図8で示したFV制御テーブルFVTBLのフォーマットを示す。当該FV

50

TBLの1ラインは、PU番号(PUN250)、当該PUのFV制御モード(PUFV251)、LMのFV制御モード(LM0FV252、LM1FV253、LM2FV254、LM3FV255)、後述するローカルバスLBUSのFV制御モード(BUSFV)に対応し、任意のPUに対する当該PU、LM、LBUSのFV動作モードを決定できる。

#### 【0069】

そして、CPU0等がこのFV制御テーブルFVTBLを読み込んで、各PU10~17毎にPUとローカルメモリLM(各バンク毎)及びローカルバスのFV制御モードを決定し、電圧生成回路(DCGEN)20及びクロック生成回路(CLKGEN)21を制御する。

10

#### 【0070】

<バスに対する電源制御>

また、各PU10~17を接続するローカルバス(LBUS)19に対しても、マルチプロセッサシステムの機能部位単位のFV制御として、部分的に電源制御(電源遮断)することができる。

#### 【0071】

例えば、PU10~17の何れかが非動作時で電源遮断されている場合、該当するPUのバスインターフェース(BIF)はアクセスされないため、当該BIFの電源遮断を行うことができ、その結果リーク電流を削減することができる。また、バス構成をクロスバとした場合、当該PUに接続するバスを決定するスイッチ部の電源を制御し遮断することもできる。

20

#### 【0072】

図11に、クロスバ構成のバスに対する電源制御の概念を示す。例えば、DSP0(14)を電源遮断状態としDSP0に対する通信トラフィックが無いとすると、DSP0に付随するBIF(27)、及びDSP0に対し他のPU及び共有メモリSMからのバスネットワークを接続するスイッチ群(192)、に対する電源も遮断する。

#### 【0073】

これにより、非動作状態となったDSP0のスイッチ群192の電力消費を削減できる。

#### 【0074】

30

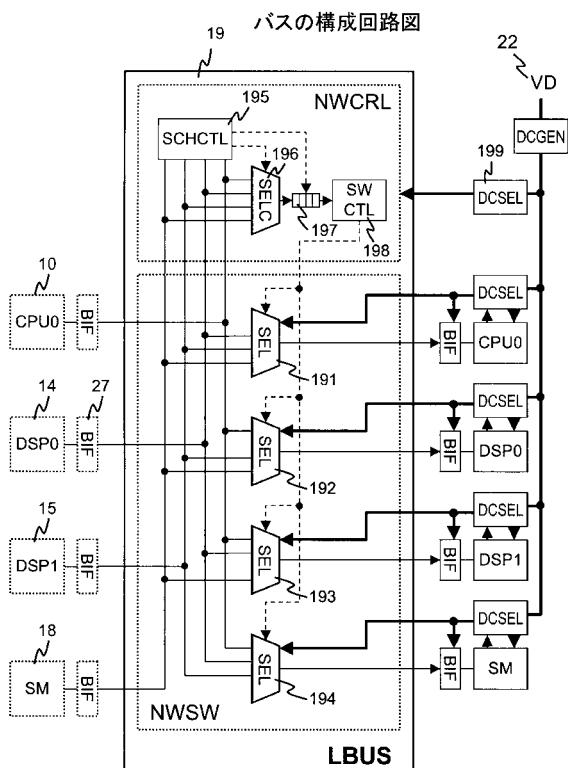

図12に、クロスバネットワークに対する電源制御を実現するための回路構成を示す。なお本図では、CPU0、DSP0、DSP1及び共有メモリSMを、クロスバネットワークで構成されたローカルバスLBUS19に接続した構成を示す。本回路は、各PU10~17が送出したパケットデータを解析し、図11に示したスイッチ群192の制御を行うネットワーク制御部NWCRLと、当該パケットデータの送出元と送出先のネットワークを接続するネットワークスイッチ部(NWSW)で構成する。

#### 【0075】

ネットワーク制御部NWCRLは、PU10~17が送出したパケットを解析しパケット処理の優先度を決定するSHCTL195と、SHCTL195により優先度決定された当該パケットを選択するセレクタ(SELC)196と、当該パケットを一時的に保持するキュー197と、当該パケットを解析し送出先及び送出元のネットワークを接続するセレクタスイッチ191~194を制御するSWCTL198から構成される。

40

#### 【0076】

また、ネットワークスイッチNWSWは各PU間のネットワークを接続するセレクタスイッチ(SEL)191~194で構成する。

#### 【0077】

各PU10~17とネットワーク制御部NWCRLには、電源生成回路DCGENと選択的に接続するスイッチ(DCSEL)199がそれぞれ設けられる。そして、スイッチ(DCSEL)199から各PU10~17及びBIF27と、当該PUが接続されるセレクタスイッチ191~194に対し電源供給を行う。

50

## 【0078】

例えばDSP0を電源遮断状態とし、DSP0に対する通信トラフィックが発生しないとすると、DSP0に付加したスイッチDSEL199は、当該DSP0のみならず当該DSP0に接続されたBIF27及び、当該DSP0へのネットワークを選択するセレクタスイッチSEL1(192)に対する電源を遮断する。これにより、電源遮断状態としたDSP0のみならず、周辺の回路への電力を遮断することで電力消費をさらに削減できる。なお、ネットワーク全体を待機状態、つまり電源遮断状態とするときは、NWCRLに対しても当該NWCRLへ電源供給するスイッチDSEL199により、電源遮断を行う。

## 【0079】

< FV制御レジスタの設定方法 >

次に、FV制御レジスタ1250を設定する具体的な方法について説明する。なお以下では、レジスタフォーマットを図14(a)の構成として説明する。

## 【0080】

各PUのFV制御レジスタ25には、全PUから一意にアクセス可能なグローバルアドレスがそれぞれ割り振られ、コンパイラが予め決定したタスク管理用のPU(つまり、スケジューラまたはOSを実行するPU)が当該アドレスにアクセスし、当該レジスタ値を変更することでFV制御モードを設定する。

## 【0081】

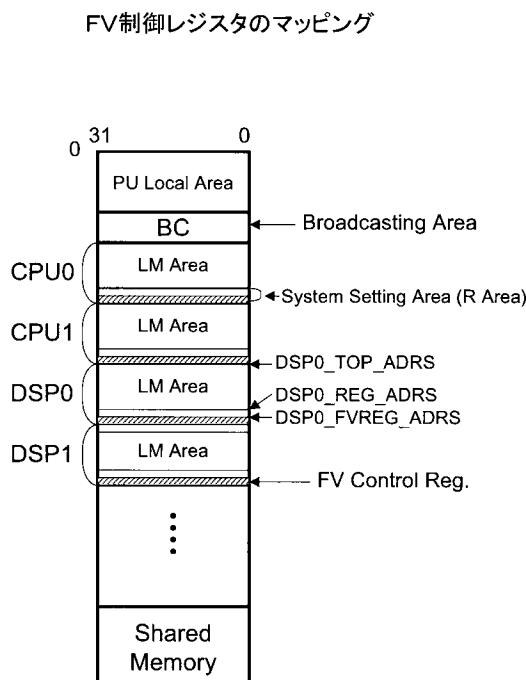

図16にマルチプロセッサシステム全体のグローバルアドレス空間マップを示す。本実施形態では、先頭アドレスより所定のアドレスまでPU自身のローカルリソース(LM、FV制御レジスタ1250を含むシステム設定レジスタ)が見える領域、ブロードキャスト(BC)領域を定義する。BC領域に関しては後述する。そして、BC領域の後に各PU毎のアドレス空間を割り振り、さらに各PU内のアドレス空間にローカルメモリLMアドレス、及びシステム設定レジスタアドレスを割り振る。FV制御レジスタは、前記システム設定レジスタアドレス内の1アドレスを持ち、当該アドレスをアクセスすることでFV制御モードを設定できる。なお図16では、CPU0、CPU1、DSP0、DSP1、の順に先頭空間よりアドレスがマップされ、例えばDSP0のFV制御レジスタを設定する際は、アドレス“DSP0\_FVREG\_ADDRESS”をアクセスすることとなる。また、当該空間の各PU領域の後には共有メモリSMのアドレスを割り振る。

## 【0082】

FV制御レジスタの設定は、コンパイラが決定したタスク管理用のPUがレジスタアクセス用のオブジェクトコードを実行し、ローカルバスLBUS19を介して制御先PUのFV制御レジスタをアクセスすることで行う。コンパイラが当該オブジェクトコードを生成する具体的な方法に関しては後述するが以下簡単に説明すると、コンパイラがタスクを複数PUに割り当てる際、当該複数のPUをグループ化し、グループ内のタスクの起動や同期処理を行うタスク管理PUを決定する。コンパイラは、当該管理PU上でFV制御を行うコードを生成し、当該管理PUは当該コードを実行することで、グループ内のPUのFV制御を行う。なお、上記コンパイラは図示しない計算機上で実行されるものである。

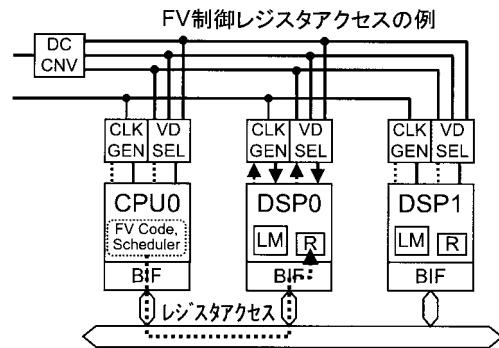

## 【0083】

図17(a)にFV制御レジスタを設定する例を示す。コンパイラがCPU0、DSP0、DSP1をグループ化し、CPU0がタスク管理を行い、当該CPU0がDSP0に対しFV制御を行うとする。CPU0は、コンパイラが生成したFV設定を行うオブジェクトコードを実行することで、DSP0のFV制御モードを設定する。

## 【0084】

図17(b)にDSP0のFV制御モードを設定するオブジェクトコードの例を示す。本例ではDSP0内のFV制御レジスタのアドレスを予め定義しておき、CPU0内の汎用レジスタに当該FV制御レジスタのアドレス、及びFV設定値を転送し、当該設定値を当該アドレスで指定されたレジスタに書き込むことで、設定を完了する。

## 【0085】

10

20

30

40

50

なお、F V 設定を行う方法として、タスク管理 P U がレジスタを直接アクセスするオブジェクトコードを実行するとしたが、例えば、図 17 (c) に示すように、O S が各 P U の F V 動作モードを管理するとした場合では、O S の F V 制御用 A P I をコールすることで、O S の管理下で P U の F V 制御モード設定を行うことができる。

#### 【0086】

なお、システム全体の F V 制御用レジスタを設け、このレジスタ内にすべての P U 10 ~ 17 の F V 制御モードを設定するレジスタを設けて、各レジスタにモードを設定すると、全 P U 10 ~ 17 の F V モードが自動で設定される機構を持たせても良い。例えば、図 8 の F V 制御テーブル 26 のように全 P U 10 ~ 17 で共有するレジスタを設け、当該レジスタを更新することで、全 P U 10 ~ 17 の F V 制御モードを変更することができる。10

#### 【0087】

また、当該システム全体の制御用レジスタに汎用処理 P U 群 (C P U)、専用処理 P U 群 (D S P、D R P、B M P) など、プロセッサの種類に対応して、当該種類ごとの P U について F V モードを同期して設定する複数の F V 制御レジスタを設けるようにしても良い。この場合、図 8 の F V 制御テーブル 26 にプロセッサの種類毎に F V 制御レジスタを設け、各 C P U、D S P、D R P、B M P 毎に F V 制御レジスタを共有することにより、一つのレジスタを変更することにより、プロセッサの種類毎に F V 制御モードを変更することができる。

#### 【0088】

##### < B C 領域 >

続いて、上記図 16 で示したメモリマップの先頭領域に設けたブロードキャスト (B C) 領域について、以下に説明する。当該 B C 領域は書き込み専用の領域であり、一 P U が当該 B C 領域のアドレスに対しデータの書き込みを行うと、当該アドレスに予め対応させた全 P U の各 L M エントリに当該データを、ローカルバス L B U S 19 を介して同時に書き込む。これにより、全 P U で共有するデータを同時に各 P U のローカルメモリ L M が持つこととなり、各 P U 10 ~ 17 は共有メモリ S M にアクセスしなくとも高速に L M 上の当該データにアクセスすることが可能となる。

#### 【0089】

また、F V 制御などのシステム制御を行うに際しても、当該ブロードキャストを行うことで全 P U に対し一斉に制御情報を送信することが可能となる。また、P U 範囲を指定するマスク情報を併せてブロードキャスト送信することで、P U の範囲を限定してデータや制御情報を送信するマルチキャスト機能を実現することも可能である。この結果、例えばコンパイラが、あるタスクを並列処理する複数 P U で構成する P U グループを定義する場合、当該 P U グループ内で一斉にタスク処理を開始したり、F V 制御を実行したりすることが可能となり、システム全体のスループットが向上する。30

#### 【0090】

##### < タスク処理時の F V 制御概念 >

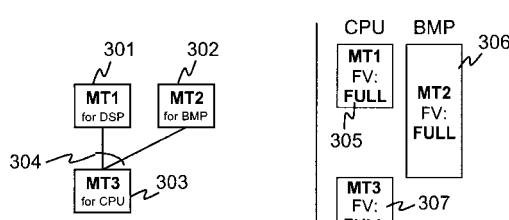

次に、図 18 を用いて各 P U 10 ~ 17 におけるタスク処理時の電源電圧、動作周波数 (F V) 制御方法の概念について説明する。各 P U で実行するタスク (プログラム) は、後述するコンパイラによって入力プログラムから生成される。つまり、当該入力プログラムは、まず後述するコンパイルにより、当該プログラムの構造を解析することで、代入文のみからなるベーシックブロック (B B)、繰り返しブロック (R B)、サブルーチン (S B) といった粒度が大きなステートメント・ブロックをマクロタスク (M T) として分割する。本例では、3 個のマクロタスク M T 301 ~ 303 に分割されるとする。ここで、マクロタスクは、入力プログラム (ソースコード) を複数の粒度の単位ブロックに分割したものである。つまり、マクロタスクに分割することで、サブルーチン等の粗粒度タスク間の並列処理を利用するマクロデータフロー処理、ループレベルの並列処理である中粒度並列処理に、基本ブロック内部のステートメントレベルの並列性を利用する近細粒度並列処理とを階層的に組み合わせて並列処理を行うマルチグレイン並列処理を行う。また、4050

本実施形態では、プログラムの構成要素をマクロタスクとし、マクロタスクの構成要素をタスクとし、タスクをPU10～17に割り当てるものとする。

【0091】

続いて、当該マクロタスクMTの任意のPUにおける演算コスト等の特性情報を算出することで、当該マクロタスクMTをどのPU上で実行するかを決定し、また当該マクロタスクMT間のデータ依存性や制御依存性を解析することで、タスクの実行順序を決定する。

【0092】

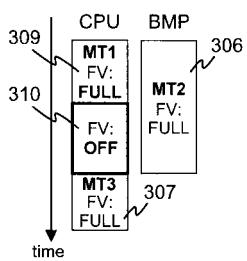

図18(a)は、タスク間の並列実行依存性を示したマクロタスクグラフである。本グラフは、マクロタスクMT1(301)とマクロタスクMT2(302)は同時に実行できることを示し、さらにマクロタスクMT3(303)は、マクロタスクMT1(301)及びMT2(302)の実行が終了後に、実行できることを示している。また本例では、マクロタスクMT1はPU10(CPU0)に、マクロタスクMT2はPU12(BMP0)12に、マクロタスクMT3はPU10(CPU0)に配置される。

【0093】

以上のようにスケジューリングされたマクロタスクを通常処理(電圧・周波数制御なし)したときの処理ガントチャートを図18(b)に示す。

【0094】

図18(b)において、マクロタスクMT1とMT2は並列実行可能なため、MT1はCPU(CPU0)にて(305)、MT2はBMP(BMP0)にて(306)同時に処理が開始される。通常処理時はCPU、BMP共に供給される電圧は通常のVD、また動作周波数も通常のFCが供給されている。本例では、CPUにおけるマクロタスクMT1の処理サイクル数は、BMPにおけるマクロタスクMT2の処理サイクル数より小さいため、CPUにおけるマクロタスクMT1の処理(305)が、BMPにおけるMT2の処理(306)に先行して終了する。

【0095】

CPUはマクロタスクMT1の処理(305)を終了したため、次にマクロタスクMT3を処理(307)することになるが、マクロタスクMT間の依存関係からBMPにおけるMT2の処理(306)が終了するまでは、CPUにおいて次に処理すべきマクロタスクMT3を実行することができない。そのため、CPUはBMPでのマクロタスクMT2の処理が終了するまでアイドル状態となる。当該アイドル状態においても、CPUに対しては通常の電源電圧VD及びクロックFCが供給されているため、余分な電力を消費することになる。

【0096】

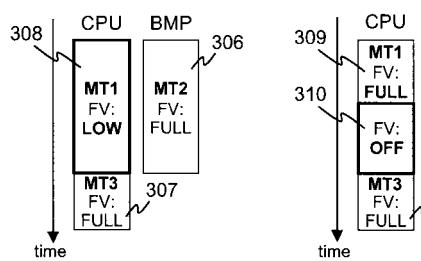

そこで以上を解決する一方法として、CPUにおいてマクロタスクMT1を実行する際に、BMPがマクロタスクMT2の処理に必要とする時間と、CPUで実行するマクロタスクMT1の処理時間が等しくなるよう、CPUの動作周波数を通常時(FULLモード)よりも低減させるLOWモード(図9の1/4FCを供給するモード)で駆動する(308)。つまり、BMPを通常時のFV制御モード(FULL)で駆動する一方、CPUのFV制御モードをLOWモードとし、処理が早く終了する方のPUの動作周波数及び低減し、並列処理を行うPU間でFV制御モードが異なるようにFV制御レジスタの設定を行う。本手法によるFV制御適用時のガントチャートを図18(c)に示す。コンパイラは、CPU(CPU0)におけるマクロタスクMT1の処理サイクル数及び、BMP(BMP0)におけるマクロタスクMT2の処理サイクル数を見積もることで、双方の処理時間が等しくなるようCPUの動作周波数を決定する。この結果、CPUの動作周波数が低減されるため、当該PUに対する電源電圧VLも低減することが可能となり、消費電力を最適化できる。

【0097】

つまりこの例では、マクロタスクMT1について、CPUのFV制御モードを図9の「LOWモード」に設定し、並列的に処理が行われるBMPのFV制御モードを「FULL」

10

20

30

40

50

」に設定する。

【0098】

また、上記図18(b)のCPUアイドル状態を解決する別の方法として、CPUにおけるマクロタスクMT1の処理(309)が終了した時点で、CPUの電源電圧及び動作クロックの供給を遮断し待機状態とする(310)。つまり、CPUがマクロタスクMT1の処理を完了すると、CPUのFV制御モードを図9の「OFF」に設定する。そして、マクロタスクMT3の開始時に、FV制御モードを「FULL」に設定し、処理を再開する。本手法によるFV制御適用時のガントチャートを図18(d)に示す。

【0099】

図18(d)において、CPUによるマクロタスクMT1の処理はBMPにおけるマクロタスクMT2(306)より先行して終了するが、当該終了時点でCPUを待機状態(OFF)とし、BMPがマクロタスクMT2の処理(306)が終了した時点で再びCPUを通常の電源電圧及び動作クロックを供給することで通常状態に復帰させ、マクロタスクMT3の処理(307)を開始する。この結果、CPUをアイドルさせることなく動作が停止するため、消費電力を低減できる。

【0100】

このように、プログラム(タスク)をコンパイルする時、PUの構成に基づきコンパイラが予め事前の処理時間を見積もり、コンパイル時に処理順序を静的に決定できる部分に関しては事前に処理手順を決定し、PU毎にきめ細かく動作周波数制御及び電源管理を行うことで、マルチプロセッサシステムの性能を損なわずに電力を最適化することが可能となるのである。

【0101】

<タスク処理時(リアルタイム制約時)のFV制御概念>

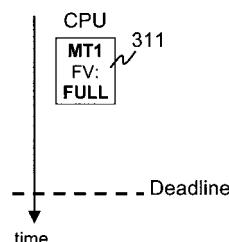

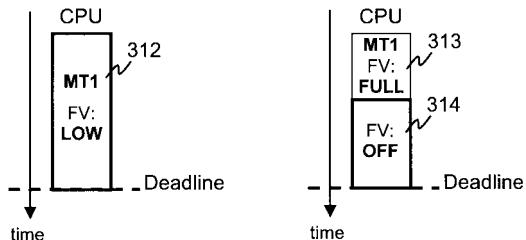

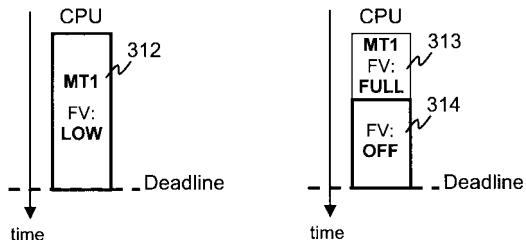

以上では、マクロタスク(MT)の実行条件が他のマクロタスクMTに依存する場合のFV制御方法を説明したが、他にもタスクがある一定時間内に処理すべき制約を持つ、すなわち図19(a)で図示するような、当該タスクの処理期限(許容時間)が決定されているリアルタイム処理タスクを対象としたFV制御方法も考えることができる。

【0102】

図19(a)で例示したマクロタスク(MT1)311では、「FULL」モード、つまり通常の電源電圧及びクロック周波数で動作するCPUで処理した場合、処理期限(Deadline)よりも先行して処理が終了する。この場合、処理が終了した時点でCPUはアイドル状態となるが、本来の処理期限に対して余裕があるため、処理期限内でのCPUの動作周波数を低減させる(312)ことが可能となる。

【0103】

本手法によるFV制御適用時のガントチャートを図19(b)に示す。コンパイラは処理期限までに処理を完了可能な動作周波数を見積もり、図示のようにCPUのFV制御モードを「LOW」モードに決定する。その結果、供給電圧VLも低減することができ、消費電力を最適化できる。

【0104】

また、同様にマクロタスクMT1の処理(313)が終了した時点でCPUの電源及び動作クロックを遮断する(314)ことで、消費電力を低減するようにしてもよい。本手法によるFV制御適用時のガントチャートを図19(c)に示す。この場合、CPUは「FULL」モードでマクロタスクMT1を処理し、処理期限前に処理を完了することになるが、マクロタスクMT1の完了時に動作モードを「OFF」とすることで、無駄な電力消費を回避することができる。

【0105】

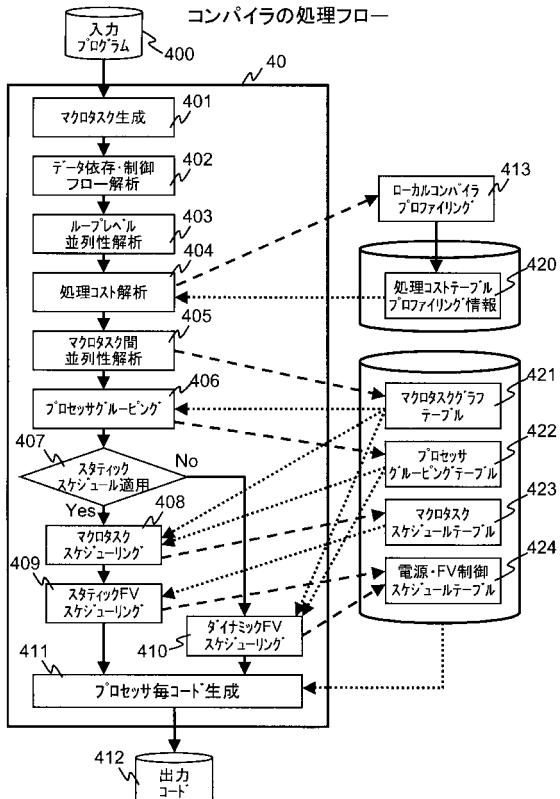

<コンパイラの処理フロー>

次に前述したマルチプロセッサ・アーキテクチャ上で、プロセッサユニット(PU)の特性に合わせたスケジューリングと電圧・周波数の動的変化による消費電力の最適制御を行うコードを生成するコンパイル方法と、当該手法を実装したコンパイラの処理について

10

20

30

40

50

以下順を追って説明していく。図20に本手法を実装したコンパイラ40の処理フローを示す。

【0106】

<マクロタスクの生成>

CやFortran等の高級言語で記述された逐次構造の入力プログラム400は、まず、当該プログラム構造を解析することで、繰り返しブロック(RB:Repetition Block)、サブルーチン(SB:Sub Routine)、擬似代入文ブロック(BPA:Block of Pseudo Assignment statements)の3種類の粒度が大きなマクロタスク(MT)に分割し、各マクロタスクを生成する(401)。RBはループブロックで各階層での最も外側のループであり、BPAはスケジューリングオーバーヘッドあるいは並列性を考慮し、代入文からなる複数の基本ブロックを融合あるいは分割したブロックである。図21に、上記のような入力プログラム(ソースプログラム400)の一例を示す。

【0107】

<Directive指定>

なお、当該ソースプログラム400中には、予めPUの割り当てを記述することが可能であり、例えばあるサブルーチンをDSPに、またあるサブルーチンをCPUに割り当てるなどを明示的に指定することも可能である。その結果、当該DSPサブルーチンはコンパイラ40によりさらに並列性の解析が行われ、例えばDSPが4個ある場合、当該4個のDSPに対してコンパイラ40は並列化スケジューリングを実施する。

【0108】

<データ依存・制御フロー解析>

続いて、分割生成された当該マクロタスク間の制御フロー及びデータ依存性を解析し、マクロタスクMTの実行順序関係を抽出する(402)。図21の入力プログラム400は、逐次的に記述されているため、通常のコンパイラ40によって生成される実行コードは、当該プログラムの構造と同様に逐次的な順序で実行されるが、マクロタスクMT間で見ると必ずしも記述された順序で実行する必要がないことが多い。

【0109】

つまり、マクロタスクMTにおいて、制御またはデータ参照の依存性がない場合、特にマルチプロセッサシステムにおいては、複数のPUに複数のマクロタスクMTを配置して同時に、または順序を変更して、全体の実行時間が短くなるようスケジューリングすることが重要となる。

【0110】

このようなスケジューリングを行うためには、MT間の並列性を解析する必要がある。そこで、この解析に向けた準備として、データ依存・制御フロー解析処理402により、マクロタスクMT間の実行順序関係を抽出する。

【0111】

<ループレベル並列性解析>

続いて、マクロタスクMT内の中粒度レベルの並列性解析として、ループレベルの並列化を行う(403)。ループレベル並列化403では、ループの繰り返し(イタレーション)単位間のデータ依存性を解析して、各イタレーションが独立に処理できるかを判断し、可能な場合は各イタレーションを複数のPUに割り当てて並列処理を行う。

【0112】

また、単一のループを複数のループに分割して並列性を高めたり、データのコピーや配列変数の拡張により、各ループ間のデータ依存性を削除することで並列化したり、また複数のループを単一のループに融合することでループ制御に必要なオーバーヘッドを軽減したり、といった様々な手法によりループの並列化を実現する。

【0113】

<処理コスト解析>

次に、上記生成されたマクロタスクMTを各PUで実行した際に必要となる処理サイク

10

20

30

40

50

ルを見積もる、処理コスト解析を行う(404)。処理コスト(演算コスト)の見積もり方法としては、例えばCPUなどに関しては、乗算や加算など命令レベルで必要とするサイクル数を処理コストテーブル420にプロファイリング情報として保持しておき、当該テーブル420を参照することで、マクロタスクMTを当該PUで実行する際の逐次処理サイクル数を見積もることができる。

#### 【0114】

また、DRPやDSPなど、プログラム中から表現される命令レベルでのサイクル数の見積もりが困難な場合は、一度当該ブロックのプログラムをDRPやDSP用の実行コードを生成する夫々のローカルコンパイラを呼び出し、変換した実行コードを元にプロファイリングを行い、処理コストを求める(413)。なお、ローカルコンパイラは、PUの種類に応じて予め設定され、例えば、DSPであればDSPのローカルコンパイラプロファイリング情報を、DRPであればDRPのローカルコンパイラプロファイリング情報を用いる。

#### 【0115】

また、例えば分岐を含む場合、あるいはループのサイズや配列のサイズが、マクロタスクMTの実行前では定まらないような場合においては、ローカルなコンパイラで一度プロファイリングすることにより、精度を高めた処理コストの算出を行うこともできる。なお、本プロファイリングを行わずマクロタスクMTが分岐を含む場合は、分岐確率を50%としてコスト算出を行う。また、同じくプロファイリングを行わずループや配列のサイズが定まらない場合は、例えばループを固定回数とし、また配列宣言時の最大サイズとする、等の方法を適用する。

#### 【0116】

以上では処理コストを、処理サイクル数(時間)として定義したが、他にコストを電力として定義することで、電力が最小となるようなスケジューリングを行うことも可能である。例えば、処理サイクル数とマクロタスクMTを完了すべき処理期限から、設定可能なFV制御モード(周波数、動作電圧)のうち処理期限内で最小の消費電力となる動作モードを選択する。あるいは、PUの消費電力は、

$$\text{消費電力} = \text{動作電圧}^2 \times \text{駆動周波数}$$

と見積もることができるので、処理期限内で消費電力が最小となるFV制御モードの組み合わせを選択し、スケジューリングすればよい。例えば、図19(b)のようにLOWモードのみで、処理を実行する場合や、図19(c)のように複数のFV制御モードを組み合わせる。あるいは、処理時間が最小かつ消費電力が最小となるFV制御モードの組み合わせを選択することもできる。

#### 【0117】

<マクロタスク間並列性解析=最早実行条件解析>

コンパイラ40はマクロタスクMTの処理コストが決定した後、データ依存・制御フロー解析処理402で抽出したマクロタスクMT間の制御フローと、データ依存性を同時に解析した結果から、マクロタスクMT間の並列性、つまり各マクロタスクMTの実行を最も早く実行してよい条件(最早実行条件)を決定する(405)。

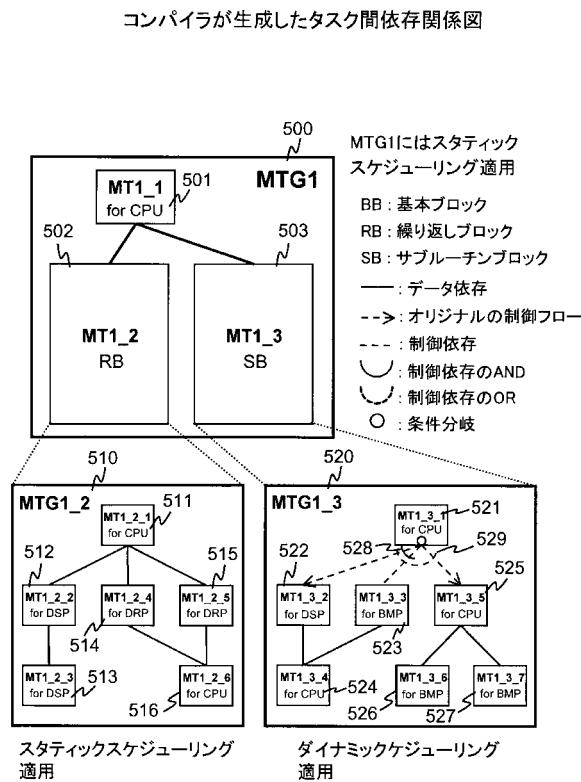

#### 【0118】

この最早実行条件をグラフで可視的に示したものがマクロタスクグラフ(MTG)である。図21の入力プログラムを解析し生成されたMTGを、図22に示す。なお、マクロタスク間並列性解析結果は、マクロタスクグラフテーブル421として外部記憶装置に保持され、後段のコンパイル処理で使用される。なお、この外部記憶装置は、コンパイラ40を実行する図示しない計算機のものを指す。

#### 【0119】

<マクロタスクグラフの説明>

以下、図22を参照しながら、マクロタスクグラフMTGについて説明する。本グラフ中の各ノードはマクロタスクMTを示し、ノード間の実線はマクロタスク間のデータ依存関係を、ノード間の破線はマクロタスク間の制御依存関係を、ノード内の小円が条件分岐

10

20

30

40

50

を表している。例えば、マクロタスクMT1\_1(501)からMT1\_2(502)及びMT1\_3(503)に対して実線が伸びているが、これは粒度の大きいマクロタスクMT1\_2及びMT1\_3がMT1\_1を実行した結果生じたデータを入力データとして用い、処理を実行しているという依存関係があることを示している。そのため、実行順序として、MT1\_2及びMT1\_3はMT1\_1の終了後、実行できることを示す。

#### 【0120】

また、入力プログラム400から求めたマクロタスクMT1\_2(502)は、複数のループやサブルーチンで構成された粒度の大きいブロックなので、コンパイラ40は当該マクロタスクMTをさらに複数のマクロタスクMTに階層的に分割する。よって、当該マクロタスクグラフMTGではMT1\_2中に、別階層でさらにマクロタスクグラフMTG1\_2を構成する。マクロタスクMT1\_3(503)も同様に別階層のマクロタスクグラフMTGMTG1\_3を構成する。

10

#### 【0121】

マクロタスクMT1\_2(502)内のマクロタスクグラフMTG1\_2(510)を見ると、タスクMT1\_2\_1(511)からはタスクMT1\_2\_2(512)、タスクMT1\_2\_4(514)、タスクMT1\_2\_5(515)に実線が伸びているため、MT1\_2\_1(511)終了後、同時にこれら3つのタスク512、514、515を実行することが可能である。

#### 【0122】

また、タスクMT1\_2\_2(512)はさらにタスクMT1\_2\_3(513)へ依存があるが、これはMT1\_2\_2(512)のタスクが終了後、MT1\_2\_3(513)のタスクを実行すればよい。また、タスクMT1\_2\_4(514)及びMT1\_2\_5(515)からタスクMT1\_2\_6(516)に対して実線が伸びているため、タスクMT1\_2\_4(514)及びタスクMT1\_2\_5(515)双方の実行が終了した時点でMT1\_2\_6(516)が実行できる。

20

#### 【0123】

以上のように、マクロタスクMT1\_2は実行前に並列順序関係は確定されており、あらかじめ固定的(静的)にタスクをスケジューリング可能である。

#### 【0124】

続いて、マクロタスクMT1\_3(503)内のマクロタスクグラフMTG(520)を見ると、マクロタスクMT1\_3\_1(521)には小円が存在するが、これはタスクMT1\_3\_1(521)が条件分岐を含むことを示している。小円からタスクMT1\_3\_2(522)、MT1\_3\_5(525)へは矢印のある破線が伸びており、また制御依存のOR条件を表す点線のアーケ529が重なっているため、当該条件がタスクMT1\_3\_2またはMT1\_3\_5の何れかに分岐することを示している。

30

#### 【0125】

また、タスクMT1\_3\_3(523)へは矢印のない破線が伸びてあり、タスクMT1\_3\_3(522)への矢印のない当該破線と、タスクMT1\_3\_2(523)に接続される破線上には、制御依存のAND条件を表す実線のアーケ528が重なっている。これは、もし当該条件で、矢印で指されているタスクMT1\_3\_2の方向に分岐する、同一の分岐に制御依存しているタスクMT1\_3\_3が同時に実行可能なことを示している。なお、図中破線はタスクの実行が確定される制御依存関係と、データ依存しているタスクが実行されない場合の条件を表している。また、矢印がついた破線は、データ依存・制御フロー解析(402)で求めた制御フローと同一(つまり、オリジナル)であることを表す。

40

#### 【0126】

なお、タスクMT1\_3\_1(521)の条件分岐は、当該タスクMT1\_3\_1を実行しないと分岐方向が確定しないため、実行時の状況に応じたスケジューリングを行う必要がある。当該条件分岐が確定し、タスクMT1\_3\_2(522)及びタスクMT1\_3\_3(523)方向に分岐した場合、タスクMT1\_3\_2(522)及びタスクMT

50

1\_3\_3 ( 523 ) からタスク M T 1\_3\_4 ( 524 ) にデータ依存関係を示す実線があるため、双方のタスク M T ( 522, 523 ) 処理の実行が終了した時点で、タスク M T 1\_3\_4 ( 524 ) の処理を実行できる。

【 0127 】

また、タスク M T 1\_3\_5 ( 525 ) 方向に分岐した場合、同様にデータ依存関係から当該タスク 525 が終了した時点で、タスク M T 1\_3\_6 ( 526 ) 及びタスク M T 1\_3\_7 ( 527 ) の処理を実行できる。

【 0128 】

< プロセッサグループ >

次にコンパイラ 40 は、生成されたマクロタスクグラフ M T G テーブル 421 を参照し、マクロタスクグラフの形状や並列性に応じた、またはユーザからの指定に応じたプロセッサのグループ化を行う ( 406 )。

【 0129 】

つまり、マクロタスクグラフ M T G で表現された上位階層のマクロタスク M T、例えばマクロタスク M T 1\_2 ( 502 )、M T 1\_3 ( 503 ) の形状、並列性を解析し、当該マクロタスク M T の処理に必要となる P U 10 ~ 17 をグループ化し、当該グループに対してタスク M T を割り当てる。なお、1 つのグループは、当該グループ内の特定用途プロセッサ ( D S P、D R P、B M P ) を制御するための汎用プロセッサ ( C P U ) を少なくとも一つ含む集合となる。具体的には、マクロタスクグラフ M T G の構成によりにコンパイル時に適切なプロセッサ P U のグループ構成が判断できる場合、コンパイラ 40 は特定用途プロセッサを含めたグループ化を行う。

【 0130 】

また、マクロタスクグラフ M T G の構成によりコンパイル時にプロセッサグループ化できない場合、つまり特殊用途プロセッサが使用すべきタスクが多階層に存在し、グループ化が適切に行えない場合では、コンパイル時にコンパイラ 40 、または実行時にスケジューラとしての役割を果たす汎用プロセッサが、タスクを特定用途プロセッサグループに対し割り当てる。この際、特定用途プロセッサへの負荷が大きい場合、汎用プロセッサで処理を代行する。なお、決定したグループ化情報は、プロセッサグループテーブル 422 として外部記憶装置に保持され、後段の処理で使用される。

【 0131 】

本実施形態では、図 22 のマクロタスクグラフ M T G 1 ( 500 ) においてマクロタスク M T 1\_2 ( 502 ) と M T 1\_3 ( 503 ) の処理コストが同等であり、これらマクロタスク内部のマクロタスクグラフ M T G 1\_2 ( 510 )、M T G 1\_3 ( 520 ) の実行には汎用プロセッサによる特定用途プロセッサの制御が必要であるため、2 個のプロセッサグループを定義する。

【 0132 】

次に、マクロタスク M T 1\_2、M T 1\_3 の各 P U に対する処理コストや並列性に応じ、各プロセッサグループ内で必要とされる特定用途プロセッサの構成を決定する。本実施形態においては、必要とされるプロセッサ構成がマクロタスクグラフ M T G 1 上の利用可能なリソースで実現できるため、プロセッサグループを、C P U 0、D S P 0、D R P 0、D R P 1、及び C P U 1、D S P 1、B M P 0、B M P 1 とコンパイル時に決定する。

【 0133 】

< スタティックスケジュールとダイナミックスケジュール >

コンパイラ 40 は次にスケジューリング方法として、スタティックスケジュールかダイナミックスケジュールかを判断する ( 407 )。夫々のスケジューリング方法の詳細は後述するが、以下簡単に説明する。まず、もし、タスク M T に条件分岐がなく最早実行条件が予め決定できる M T フローであれば、前者のスタティックスケジュールを適用し、コンパイラ 40 が予めタスク M T のスケジューリングを行い、同期コード及び F V 制御コード ( スケジューリングコード ) をタスク間に挿入する。

10

20

30

40

50

## 【0134】

また、もし、タスクMTに条件分岐がある、あるいはタスクMTの処理時間が実行時に変動するなど、コンパイル時に予測できないMTフローであれば、後者のダイナミックスケジュールを適用し、コンパイラ40は、分岐などの状況に応じた制御を実行時に行うスケジューリングプログラムを生成する。コンパイラ40がスケジューリングプログラム（スケジューリングコード）を生成する利点は、従来のマルチプロセッサのようにOSあるいはライブラリに粗粒度タスクの生成、スケジューリングを依頼すると、数千から数万クロックのオーバーヘッドが生じてしまう可能性があり、それを避けるためである。

## 【0135】

&lt;スタティックスケジューリング&gt;

10

まず、スタティックスケジューリングの処理フローについて説明する。スタティックスケジューリングでは、コンパイル時にタスクMTの割り当てと実行順序がすでに決定しているため、まず、マクロタスクスケジューリング処理408により、マクロタスクテーブル421及びプロセッサグループテーブル422情報を参照し、PU間ににおける実行タスク間の同期や他タスクの起動等を行う制御情報を生成し、当該制御情報の挿入箇所を決定する。

## 【0136】

また、さらに、タスクプログラムまたはタスクが必要とするデータを、他PUのローカルメモリLMや共有メモリSMより当該PUのローカルメモリLMにロードするといったデータ転送情報も併せて生成する。このような、データローカライゼーション手法により、ローカルメモリLMを効率的に活用し、データの転送量を最小化する。以上の処理により生成されたスケジュール情報は、マクロタスクスケジュールテーブル423として、外部記憶装置に保持される。

20

## 【0137】

続いて、コンパイラ40は、スタティックFVスケジューリング処理409を行う。本処理では、図18で説明したタスク並列処理実行時のFV制御概念に基づき、マクロタスクスケジューリング408で生成されたスケジュール情報（マクロタスクスケジュールテーブル）より、タスクの処理コスト及びスケジュール期限（処理期限）で決定される余裕度を判定し、当該余裕度に応じた動作周波数・供給電圧を決定するPU動作モードを設定するため、FV制御情報を生成する。当該FV制御情報は、電源・FV制御スケジュールテーブル424として、外部記憶装置に保持される。なお、余裕度は、例えば、実行開始から実行完了までの処理時間と、処理期限までの時間から求まるものであり、各PU10～17の性能上の余裕の度合いを示す。例えば、図19(a)のように、CPU0の実行完了から処理期限までの時間が長い場合には余裕度が大きいと判定し、逆に実行完了から処理期限までの時間が短い場合には余裕度が小さいと判定できる。

30

## 【0138】

また、処理期限（許容時間）は、入力プログラムに記述したり、コンパイラ40の処理時に図示しないコンソールから入力してもよい。

## 【0139】

&lt;ダイナミックスケジューリング&gt;

40

次に、ダイナミックスケジューリングの処理フローについて説明する。ダイナミックスケジューリング時は、タスクMT内の条件分岐等の不確定要素によりコンパイル時にスケジューリング内容を決定することができない。このためコンパイラ40は、タスクMTの処理結果に基づき、プログラム実行時に動的にスケジューリングを行うスケジューリングプログラムを生成する（410）。本プログラムは、処理結果に基づきタスクMTの起動や同期、及び当該MTが必要とするデータのロードを行う。また、さらに図18で説明したタスク並列処理実行時のFV制御概念に基づき、PUの動作周波数・供給電圧を決定する動作モード（FV制御モード）を設定する。生成したスケジューリングプログラムは、電源・FV制御スケジュールテーブル424として、外部記憶装置に保持される。

## 【0140】

50

## &lt;スケジューリングコードの生成&gt;

コンパイラ40は以上の処理により、入力プログラム400のPU10～17へのスケジューリングを完了する。これまでの処理で生成したスケジューリング情報は外部記憶装置にテーブル(421～424)として保持されている。コンパイラ40は、当該テーブル(421～424)にアクセスし、タスクの実行順序やデータ転送情報、及びFV制御情報を読み込み、入力プログラムに対してスタティックスケジュール部には制御コード(スケジューリングコード)を、またダイナミックスケジュール部にはスケジューリングプログラムを附加する(411)。制御コードは、例えば分散メモリ型並列計算機における並列プログラミング標準インターフェースであるMPI(Message Passing Interface)などを用いて生成する。当該コードが附加された入力プログラムは、さらに各PUの種類毎に用意されたローカルコンパイラで処理することにより、当該PUにおける実行バイナリコードに変換される(412)。なお、ローカルコンパイラは、上述のようにCPU、DSP、DRP、BMPのPUの種類毎に予め用意され、コンパイラ40から各PUの種類に応じたローカルコンパイラを呼び出して実行バイナリコードを生成するものである。

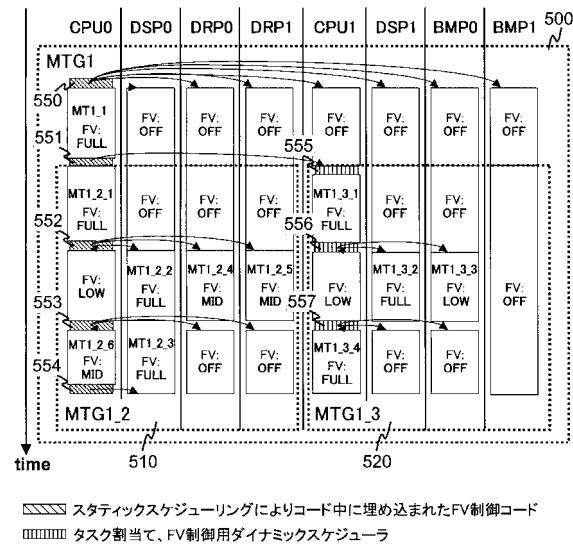

## 【0141】

## &lt;スケジューリングの結果&gt;

本スケジューリング結果の例を図23に示す。図23は、MTのスケジューリング結果をPU毎に時間軸で示している。本例ではCPU0がタスクの起動や同期、FV制御などの管理を行うため、最初にCPU0上にコンパイラ40が生成した制御コード550がコードされる。当該制御コード550は、各PUのFV制御を行うコード、及びCPU0においてマクロタスクMT1\_1を起動するコードで表現されている。つまりCPU0は、マクロタスクMT1\_1を実行するCPU0に対し動作モードをFULLにするようFV制御レジスタの値を“3”に設定する。また、他のPUに対しては処理すべきMTがないため、動作モードをOFFにするようFV制御レジスタの値を“0”に設定する。次に、CPU0は自CPU0にてマクロタスクMT1\_1の処理を開始する。

## 【0142】

CPU0でマクロタスクMT1\_1処理終了後、コンパイラ40が生成した制御コード551を実行し、FV制御モードの設定を行う。次に処理すべきタスクは、マクロタスクMT1\_2及びMT1\_3の下位層のマクロタスクグラフMTGで指定されたタスクMT1\_2\_1及びタスクMT1\_3\_1であり、前者はCPU0にて、後者はCPU1にて実行される。

## 【0143】

従ってCPU0はタスクMT1\_3\_1を処理するCPU1のFV制御レジスタを通常モード(FULL)に設定する。またCPU0に関しても、すでにFV制御モードは通常モードであるが、引き続きMT1\_2\_1を処理するため通常モード(FULL)としておく。

## 【0144】

このとき、前記タスクMT1\_2\_1及び前記タスクMT1\_3\_1の処理中は、他のPU上での処理タスクは存在しないため、当該他のPUは引き続き動作モードをOFFとしておく。続いてCPU0は、自CPU0においてタスクMT1\_2\_1を、またCPU1においてタスクMT1\_3\_1の処理を開始する。

## 【0145】

なお前述した通り、マクロタスクMTG1\_2は条件分岐を含まないためコンパイル時すでにスケジューリングが行われており(スタティックスケジューリング)、CPU0、DSP0、DRP0、DP1グループへタスクMTを割り振る。またマクロタスクMTG1\_3は条件分岐を含むため、実行時にスケジューリングを行うプログラムを付加し、実行結果によってCPU1、DSP1、BMP0、BMP1のグループへタスクMTを割り振る。

## 【0146】

10

20

30

40

50

続いてマクロタスクグラフ M T G 1 \_ 2 のタスク M T グループのスケジューリングについて説明する。タスク M T 1 \_ 2 \_ 1 の実行が C P U 0 において終了すると、 C P U 0 は制御コード 5 5 2 を実行し、タスク M T 1 \_ 2 \_ 2 を処理するために D S P 0 を通常動作モード F U L L とするよう、 F V 制御レジスタを “ 3 ” に設定する。またタスク M T 1 \_ 2 \_ 4 及び M T 1 \_ 2 \_ 5 はコンパイル時の F V スケジューリングによるタスクの余裕度判定により D R P 0 、 D R P 1 を低電力動作モード M I D D L E とするよう、 F V 制御レジスタを “ 2 ” に設定する。また、 C P U 0 においては実行すべき M T はないが、スケジューラを実行し D S P 0 、 D R P 0 、及び D R P 1 のタスクの同期管理を行っているため、スケジューラは C P U 0 に対して低電力動作モード L O W とするよう、 F V 制御レジスタを “ 1 ” に設定する。そして、タスク M T 1 \_ 2 \_ 2 、タスク M T 1 \_ 2 \_ 4 、及びタスク M T 1 \_ 2 \_ 5 の処理を開始する。なお、タスク M T 1 \_ 2 \_ 2 は当該 M T 処理終了後、同じく D S P 0 においてタスク M T 1 \_ 2 \_ 3 を実行することとなるため、この時点 10 でタスク M T 1 \_ 2 \_ 2 終了後にタスク M T 1 \_ 2 \_ 3 を起動するようタスクの起動予約（タスクレディキューへのタスクの登録）をしておく。

#### 【 0 1 4 7 】

次に前記タスク M T 1 \_ 2 \_ 4 及びタスク M T 1 \_ 2 \_ 5 の処理が双方とも終了したことを C P U 0 が判定すると、当該 C P U 0 は制御コード 5 5 3 を実行し、 C P U 0 はタスク M T 1 \_ 2 \_ 6 を処理する自 C P U 0 の動作モードを M I D D L E に、また D R P 0 及び D R P 1 は処理すべきタスクが存在しないため、動作モードを O F F に設定し、通常よりも電圧と動作周波数を低減した状態で前記タスク M T 1 \_ 2 \_ 6 の処理を開始する。前記タスク M T 1 \_ 2 \_ 6 の処理が終了すると、 C P U 0 は制御コード 5 5 4 を実行しタスク M T 1 \_ 2 \_ 3 の処理終了を判定すると、 M T G 1 \_ 2 グループ内のタスク処理が完了したため、 C P U 0 は D S P 0 の動作モードを O F F に設定する。 20

#### 【 0 1 4 8 】

続いて M T G 1 \_ 3 のタスク M T グループについて説明する。マクロタスク M T 1 \_ 3 は内部に分岐を持つため、タスクを実行しないと分岐方向がわからない。従って、実行時の状況によりタスク、データのロード、タスクの起動、同期及び F V 制御コードの管理を行うダイナミックスケジューラ 5 5 5 を、 C P U 1 において実行する。当該スケジューラ 5 5 5 は、まずタスク M T 1 \_ 3 \_ 1 を実行するため C P U 1 の動作モードを F U L L に設定し、タスク M T 1 \_ 3 \_ 1 を起動する。タスク M T 1 \_ 3 \_ 1 実行終了後、スケジューラ 5 5 6 は分岐方向を判定し、次に起動するタスクを判断する。 30

#### 【 0 1 4 9 】

図 2 3 に示したスケジューリングでは、タスク M T 1 \_ 3 \_ 2 が D S P 1 にて、タスク M T 1 \_ 3 \_ 3 が B M P 0 にて処理される。当該処理の起動前に、スケジューラ 5 5 6 は F V スケジューリング結果に従い D S P 1 の動作モードを F U L L に、また B M P 0 の動作モードを L O W に設定する。 C P U 1 においては、実行すべきタスク M T はないが、スケジューラ 5 5 6 を実行し D S P 1 及び B M P 0 のタスク管理を行っているため、スケジューラ 5 5 6 は C P U 1 の動作モードを低電力モード L O W に設定する。

#### 【 0 1 5 0 】

次に、 C P U 0 上のダイナミックスケジューラ 5 5 7 は、前記タスク M T 1 \_ 3 \_ 2 及びタスク M T 1 \_ 3 \_ 3 の双方の処理終了を判定すると、次にタスク M T 1 \_ 3 \_ 4 を処理する自 C P U 0 の動作モード（ F V 制御モード）を F U L L に、また実行すべきタスクが存在しない D S P 1 及び B M P 0 の動作モードを O F F に設定する。そして、自 C P U 0 において、前記タスク M T 1 \_ 3 \_ 4 を実行する。 40

#### 【 0 1 5 1 】

以上により、異種の P U 1 0 ~ 1 7 で構成されるマルチプロセッサにおいて、マルチグレイン並列処理により、実行時間が最小となるよう入力プログラムを並列化しスケジューリングした後、各 P U 間で処理時間が均一となるよう、 P U 毎にきめ細かく動作周波数制御及び電源管理を行うことで、最小の実行時間で性能を損なわずに消費電力の低減を図ることが可能となるのである。 50

## 【0152】

<コンパイラが生成する目的プログラム>

コンパイラ40により、以上で説明したようなスケジュールを行うスケジューリングコードを、入力プログラム400に付加しPU毎に出力した出力プログラム（目的コード）の一例を図24及び図25に示す。図24、図25は、上記図23で示した処理を記述したもので、図24はマクロタスクMTG1\_2を処理するプロセッサのグループとしてCPU0、DSP0、DRP0、DRP1の各PU用の実行コードを示す。また、図25は、マクロタスクMTG1\_3を処理するプロセッサのグループとしてCPU1、DSP1、BMP0、1の各PU用の実行コードを示す。コンパイラ40の生成コードは擬似コードで表現されているが、前述したように実際はMPI等のインターフェース規格に従って表現される。10

## 【0153】

<まとめ>

以上のように、本発明によれば、多種のプロセッサユニットPUを集積するマルチプロセッサシステムにおいて、当該PUを効率よく動作させるプログラムの分割配置および制御コードを生成するコンパイラ40により、当該プロセッサシステムの性能を最大限活用しつつ、最小限の処理時間内に低電力にて効率よく処理することが可能となる。また、さらにはソフトウェア開発者がプロセッサの構成を意識することなく、短時間で極めて効率の良いプログラム作成が可能となる。20

## 【0154】

<補足>

なお、上記実施形態においては、一つのチップに複数のPU10～17を備えたマルチプロセッサシステムに本発明を適用した例を示したが、図1に示したチップを複数備えた並列計算機に適用することも可能であり、上記と同様の作用効果を得ることができる。

## 【0155】

また、請求項14、請求項22、請求項30において、前記プロセッサユニット毎に設定されたプロファイリング情報に基づいて前記単位ブロックを処理する処理サイクル数を求め、当該処理サイクルから前記演算サイクル時間を求ることを特徴とするマルチグレイン並列化コンパイラ。30

## 【0156】

また、請求項14、請求項22、請求項30において、前記演算サイクル時間は、前記プロセッサユニット毎に設定されたローカルコンパイラにより前記単位ブロックを実行コードに変換し、前記プロセッサユニット毎に設定されたプロファイリング情報に基づいて前記単位ブロックを処理する処理サイクル数を求め、当該処理サイクル数に基づいて前記演算サイクル時間を求ることを特徴とするマルチグレイン並列化コンパイラ。

## 【0157】

また、請求項15、請求項23、請求項31において、前記プロセッサユニット毎に設定されたプロファイリング情報に基づいて前記単位ブロックを処理する処理サイクル数を求め、当該処理サイクルから前記電力を求ることを特徴とするマルチグレイン並列化コンパイラ。40

## 【0158】

また、請求項15、請求項23、請求項31において、前記演算サイクル時間は、前記プロセッサユニット毎に設定されたローカルコンパイラにより前記単位ブロックを実行コードに変換し、前記プロセッサユニット毎に設定されたプロファイリング情報に基づいて前記単位ブロックを処理する処理サイクル数を求め、当該処理サイクル数に基づいて前記電力を求ることを特徴とするマルチグレイン並列化コンパイラ。

## 【0159】

また、請求項13、請求項21、請求項29において、前記単位ブロックの並列性を抽出する処理は、前記抽出した単位ブロックをマクロタスクグラフテーブルに格納し、前記単位ブロックを処理するのに必要なプロセッサユニットをグループ化してプロセッサグル50

—ピングテーブルに格納する処理とを含み、

前記スケジューリングコードを生成する処理は、前記マクロタスクグラフテーブルとプロセッサグルーピングテーブル及びコスト情報を参照してプロセッサユニットの制御コードを生成する処理と、前記単位ブロックの実行順序に応じて前記制御コードを挿入する処理を含むことを特徴とするマルチグレイン並列化コンパイラ。

#### 【0160】

また、請求項13、請求項21、請求項29において、前記単位ブロックの並列性を抽出する処理は、前記抽出した単位ブロックをマクロタスクグラフテーブルに格納し、前記単位ブロックを処理するのに必要なプロセッサユニットをグループ化してプロセッサグルーピングテーブルに格納する処理とを含み、

10

前記スケジューリングコードを生成する処理は、前記マクロタスクグラフテーブルとプロセッサグルーピングテーブル及びコスト情報を参照して、動的に前記単位ブロックのスケジューリングを行うスケジューリングプログラムを生成する処理と、前記単位ブロックの実行順序に応じて前記スケジューリングプログラムを挿入する処理を含むことを特徴とするマルチグレイン並列化コンパイラ。

#### 【産業上の利用可能性】

#### 【0161】

以上のように、本発明は、多様なPUを集積するマルチプロセッサシステムにおいて、当該PUを効率よく動作させるプログラムの分割配置および制御コードを生成するコンパイラにより、当該プロセッサシステムの性能を最大限活用しつつ、低電力にて効率よく処理することが可能となる。また、さらにはソフトウェア開発者がプロセッサの構成を意識することなく、短時間で効率良いプログラム作成が可能となる。その結果、高い演算性能を持ちかつ低電力に処理することが強く望まれる、カーナビゲーションシステムや携帯電話、情報家電向けのLSIに本発明を適用することができ、高品質の動画像や音声処理、また画像認識や音声認識といった機能を実現することが可能となる。また、自動車における情報系、制御系システム向けLSIに対しても適用することができ、自動運転や安全運転システム等を実現することが可能となる。またさらには、将来非常に高い演算性能を有しつつ低電力化が必須となる、スーパーコンピュータへの適用も可能である。

20

#### 【図面の簡単な説明】

#### 【0162】

30

【図1】本発明の一実施形態を示すマルチプロセッサシステムのブロック図。

【図2】電源電圧生成回路のブロック図。

【図3】降圧回路のブロック図。

【図4】供給電圧選択回路のブロック図。

【図5】クロック生成回路のブロック図。

【図6】クロックパルス選択器のブロック図。

【図7】マルチプロセッサシステムの他の例を示し、電源電圧生成回路とクロック生成回路を集約したマルチプロセッサシステムのブロック図。

【図8】マルチプロセッサシステムの他の例を示し、各プロセッサユニットのFV制御レジスタを集約したFV制御テーブルを有するマルチプロセッサシステムのブロック図。

40

【図9】FV制御によるプロセッサユニットの動作モードを示す説明図。

【図10】ローカルメモリのFV制御を示す説明図で、(a)はローカルメモリLMを複数バンクで構成してバンク毎にFV制御を行う例を示し、(b)はローカルメモリLMを複数のアドレス区間毎にFV制御を行う例を示し、(c)複数バンクに設定したアドレス区間毎にFV制御を行う例を示す。

【図11】ローカルバスL BUSをクロスバで構成した場合の電源制御の説明図。

【図12】図11に示したローカルバスL BUSの構成図。

【図13】FV制御によるローカルメモリLMの動作モードを示す説明図。

【図14】FV制御レジスタフォーマットを示す説明図で、(a)はローカルメモリLMを4バンクで構成した場合のレジスタフォーマットを示し、(b)は同じくレジスタの設

50

定例を示し、(c)は他のレジスタフォーマットを示す。

【図15】図8に示したFV設定テーブルのフォーマットの例を示す説明図。

【図16】FV制御レジスタのマッピングを示すマルチプロセッサシステム全体のメモリマップ。

【図17】FV制御レジスタアクセスの例を示す説明図で、(a)はCPU0がDSP0のFV制御レジスタにアクセスする例を示し、(b)はCPU0がDSP0のFV制御レジスタにアクセスする場合のオブジェクトコードを示し、(c)はOSのAPIを用いてFV制御レジスタを操作する場合のオブジェクトコードを示す。

【図18】タスクを並列処理する場合のFV制御の概念を示し、(a)はマクロタスクの並列実行依存性を示すマクロタスクグラフで、(b)はFV制御を行わない場合(FULモード)のガントチャートを示し、(c)はCPUを継続して動作させる場合のFV制御の例を示すガントチャートで、(d)はCPUを一時的に停止させる場合のFV制御の例を示すガントチャート。

【図19】リアルタイム制約時のFV制御を示し、(a)は通常処理によるリアルタイム処理のガントチャート、(b)はCPUを継続して動作させる場合のFV制御の例を示すガントチャートで、(d)はCPUを一時的に停止させる場合のFV制御の例を示すガントチャート。

【図20】コンパイラの処理を示すフローチャート。

【図21】入力プログラムの一例を示すソースコード。

【図22】コンパイラが生成したタスク間の依存関係図。

【図23】タスク・FV制御スケジューリング結果を示す時系列的なチャート。

【図24】コンパイラが生成するコードの例を示し、CPU0、DSP0、DRP0、BRP1向けのコード。

【図25】同じくコンパイラが生成するコードの例を示し、CPU1、DSP1、BMP0、BMP1向けのコード。

#### 【符号の説明】

##### 【0163】

10、11 CPU (プロセッサユニット)

12、13 BMP (プロセッサユニット)

14、15 DSP (プロセッサユニット)

16、17 DRP (プロセッサユニット)

18 共有メモリSM

19 ローカルバス

20 電源電圧生成回路 (DCGEN)

21 クロック生成回路 (CLKGEN)

24 ローカルメモリ (LM)

25 システム制御レジスタ

10

20

30

【図1】

CPU: 汎用プロセッサ

DSP: 信号処理プロセッサ

DRP: 動的再構成可能プロセッサ

BMP: ビット演算処理プロセッサ

CLKGEN: クロック生成回路

DCGEN: 電圧生成回路

LM: ローカルメモリ(キャッシュ)

R: FV制御レジスタ

SM: 共有メモリ

LBUS: ローカルバス

BIF: バスインターフェース

【図2】

【図3】

【図4】

VDSELの構成例

【図5】

周波数生成器(CLKGEN)の例

【図6】

【図7】

CPU: 汎用プロセッサ

DSP: 信号処理プロセッサ

DRP: 動的再構成可能プロセッサ

BMP: ビット演算処理プロセッサ

CLKGEN: クロック生成回路

CLKSEL: クロック選択回路

DCCNV: 電圧変換回路

DCSEL: 電圧選択回路

LM: ローカルメモリ（キャッシュ）

R: FV制御レジスタ

SM: 共有メモリ

LBUS: ローカルバス

BIF: バスインターフェース

【図8】

【図9】

プロセッサ・ユニットの動作モード

| モード名   | FV制御<br>レジスタ値 | 供給電圧<br>(VL)   | 供給クロック<br>周波数(FL) |

|--------|---------------|----------------|-------------------|

| OFF    | 00            | 0<br>(遮断)      | 0<br>(遮断)         |

| LOW    | 01            | $1/2$ VD       | $1/4$ FC          |

| MIDDLE | 10            | $3/4$ VD       | $1/2$ FC          |

| FULL   | 11            | VD<br>(システム電圧) | FC<br>(システムクロック)  |

CPU: 汎用プロセッサ

DSP: 信号処理プロセッサ

DRP: 動的再構成可能プロセッサ

BMP: ビット演算処理プロセッサ

CLKGEN: クロック生成回路

DCGEN: 電圧変換回路

LM: ローカルメモリ（キャッシュ）

FVTBL: FV制御テーブル

SM: 共有メモリ

LBUS: ローカルバス

BIF: バスインターフェース

【図10】

(a) バンク毎

(b) 一定空間毎

(c) バンク間一定領域毎

【図12】

【図11】

バスの構成例(クロスバ)と電源制御方法

【図13】

LMの動作モード

| モード名         | FV制御<br>レジスタ値 | 供給電圧<br>(VL)     | 供給クロック<br>周波数(FL) |

|--------------|---------------|------------------|-------------------|

| OFF<br>完全遮断  | 00            | 0<br>(遮断)        | 0<br>(遮断)         |

| SLP<br>データ保持 | 01            | $\frac{1}{2}$ VD | 0                 |

| FULL<br>通常   | 11            | VD<br>(システム電圧)   | FC<br>(システムクロック)  |

【図14】

FV制御レジスタフォーマット

PUFV: PU本体のFVモード

LM\*FV: LM(バンク番号\*)のFVモード

(a) FV制御レジスタフォーマット (LMを4バンク構成とした例)

|    |      |     |     |     |     |          |

|----|------|-----|-----|-----|-----|----------|

| 31 | 1250 | 8   | 6   | 4   | 2   | 0        |

|    |      | LM3 | LM2 | LM1 | LM0 | PU<br>FV |

(b) FV制御レジスタ設定例

|       |   |   |   |   |   |   |   |   |   |

|-------|---|---|---|---|---|---|---|---|---|

| ..... | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

|-------|---|---|---|---|---|---|---|---|---|

LM, Bank2,3 LM, Bank1 LM, Bank0 PUのモードは

は電源遮断 はデータ保持 は通常動作 MIDDLE

(c) 制御対象毎にアドレスを割り振ったFV制御レジスタフォーマットの例 (LMを4バンク構成とした例)

アドレス フィールド 0

|            |           |

|------------|-----------|

| PUx_FV     | PU<br>FV  |

| PUx_LM0_FV | LM0<br>FV |

| PUx_LM1_FV | LM1<br>FV |

| PUx_LM2_FV | LM2<br>FV |

| PUx_LM3_FV | LM3<br>FV |

【図16】

【図15】

FVTBLのフォーマット

|     |      |           |           |           |           |           |

|-----|------|-----------|-----------|-----------|-----------|-----------|

| 250 | 251  | 252       | 253       | 254       | 255       | 256       |

| PUN | PUFV | LM0<br>FV | LM1<br>FV | LM2<br>FV | LM3<br>FV | BUS<br>FV |

| 0   | 01   | 11        | 01        | 00        | 00        | 11        |

| ⋮   | ⋮    | ⋮         | ⋮         | ⋮         | ⋮         | ⋮         |

【図17】

(a) FV制御レジスタアクセス

(b) コンパイラが挿入する、レジスタセットを行うオブジェクトコードの例

; FV REGS ADDRESS SET

; Obtain a registers top address for each PU

CPU0\_REG\_ADDRS EQU CPU0\_TOP\_ADDRS+SYSREG\_OFFSET

DSP0\_REG\_ADDRS EQU DSP0\_TOP\_ADDRS+SYSREG\_OFFSET

DSP1\_REG\_ADDRS EQU DSP1\_TOP\_ADDRS+SYSREG\_OFFSET

; Obtain an FV register address for each PU

CPU0\_FVREG\_ADDRS EQU CPU0\_REG\_ADDRS+FVREG\_OFFSET

DSP0\_FVREG\_ADDRS EQU DSP0\_REG\_ADDRS+FVREG\_OFFSET

DSP1\_FVREG\_ADDRS EQU DSP1\_REG\_ADDRS+FVREG\_OFFSET

; Set the target FV register for DSP0

MOV.L #DSP0\_FVREG\_ADDRS,R0 ; Set target reg. address to R0

MOV.W #H'0000001D,R1 ; Set fv reg. value to R1

MOV.W R1,@R0 ; Determine the mode setting

(c) OS APIを用いたレジスタセットの例

set\_fv\_regs( PUの種類, PUのFVモード, LMnバンク0のFVモード, バンク, バンク2, バンク3 );

例) set\_fv\_regs( CPU0, MID, FULL, SLP, OFF, OFF );

【図18】

タスク並列処理時のFV制御概念

(a) マクロタスクグラフ

(b) 通常処理ガントチャート

(c) FV制御時ガントチャート(1)

(d) FV制御時ガントチャート(2)

【図19】

リアルタイム制約時のFV制御概念

(a) 処理ガントチャート

(b) FV制御時ガントチャート(1)

(c) FV制御時ガントチャート(2)

【図20】

【図21】

入力プログラム例

```

/* MT1_1 */

for (j = 0; j < m; j++)

scanf( "%d %d", &a[0][j], &x[j] );

/* MT1_2 */

for (i = 1; i < n; i++) {

/* MT1_2_1 */

for (j = 0; j < m; j++) a[i][j] = a[i-1][j];

/* MT1_2_2 */

func1(a, b);

/* MT1_2_3 */

func2(b, c);

/* MT1_2_4 */

for (j = 0; j < m; j++) d[i][j] = a[i][j] * 2;

/* MT1_2_5 */

for (j = 0; j < m; j++) e[i][j] = a[i][j] / 2;

/* MT1_2_6 */

func3(d, e, f);

}

/* MT1_3 */

func4(x, y, z);

void func4(x, y, z)

{

/* MT1_3_1 */

t = (x(0) + x(m)) / 2

if (t > g(m/2)) {

/* MT1_3_2 */

for (j = 0; j < m; j++) y[j] = x[j] * 2;

/* MT1_3_3 */

for (j = 0; j < m; j++) z[j] = x[j] + 1;

/* MT1_3_4 */

func4a(x, y, z);

} else {

/* MT1_3_5 */

func4b(x, y, z);

/* MT1_3_6 */

for (j = 0; j < m; j++) y[j] = x[j] + 2;

/* MT1_3_7 */

for (j = 0; j < m; j++) z[j] = x[j] + 3;

}

}

```

/\* ~ \*/ はコメント文

400

【図22】

【図23】

タスク・FV制御スケジューリング結果

---

フロントページの続き

(72)発明者 伊藤 雅樹

東京都町田市本町田 9 6 9 番地 7 号

(72)発明者 鹿野 裕明

東京都国分寺市西恋ヶ窪 3 丁目 8 番地 1 号

審査官 久保 光宏

(56)参考文献 特開2004-199139 (JP, A)

特開2005-062956 (JP, A)

特開平07-287699 (JP, A)

特開平04-195619 (JP, A)

小出洋・他, 「メタスケジューリング」, bit, 日本, 共立出版株式会社, 2001年 4月

1日, Vol.33, No.4, pp.36-41, ISSN:0385-6984

笠原博徳, 「最先端の自動並列化コンパイラ技術」, 情報処理, 日本, 社団法人情報処理学会,

2003年 4月 15 日, Vol.44, No.4, pp.384-392, ISSN:0447-8053

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 45 ,

G 06 F 9 / 46 - 9 / 54 ,

G 06 F 15 / 16 - 15 / 177 ,

G 06 F 1 / 04 - 1 / 14 ,

J S T P l u s ( J D r e a m 2 ) ,

C S D B ( 日本国特許庁 )