(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년07월06일

(11) 등록번호 10-1534117

(24) 등록일자 2015년06월30일

(51) 국제특허분류(Int. Cl.)

H04N 5/361 (2011.01) H04N 5/369 (2011.01)

(21) 출원번호 10-2008-0127805

(22) 출원일자 2008년12월16일

심사청구일자 2013년11월27일

(65) 공개번호 10-2009-0066227

(43) 공개일자 2009년06월23일

(30) 우선권주장

JP-P-2007-326175 2007년12월18일 일본(JP)

(56) 선행기술조사문현

JP평성07078959 A

JP2003152172 A

JP2006108379 A

(73) 특허권자

소니 주식회사

일본국 도쿄도 미나토구 코난 1-7-1

(72) 발명자

히로타 이사오

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이사내

하라다 고이치

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시

끼 가이사내

(뒷면에 계속)

(74) 대리인

유미특허법인

전체 청구항 수 : 총 20 항

심사관 : 이성현

(54) 발명의 명칭 고체 활상 장치 및 카메라

**(57) 요약**

고체 활상 장치는, 광이 조사되는 제1 기판면 측과 소자가 형성되는 제2 기판면 측을 가지는 기판에 형성되고, 1 화소 셀마다 또는 복수 화소 셀을 단위로 하여 인접 셀 그룹과 소자 분리층(element separation layer)에 의해 분리된 화소 셀을 포함한다. 각각의 상기 화소 셀은, 상기 제1 기판면 측에 형성된 제1 도전형 웨, 및 상기 제2 기판면 측에 형성된 제2 도전형 웨를 포함한다. 상기 제1 도전형 웨은, 상기 제1 기판면 측으로부터의 광을 수광하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가진다. 상기 제2 도전형 웨에는, 상기 제1 도전형 웨에서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 트랜지스터가 형성되어 있다.

**대 표 도 - 도2**

(72) 발명자

**가라사와 노부히로**

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시끼

가이샤내

**마루야마 야스시**

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시끼

가이샤내

**낫타 요시카즈**

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시끼

가이샤내

---

**데라카고 히로유키**

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시끼

가이샤내

**다카시마 하지메**

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시끼

가이샤내

**노무라 히데오**

일본국 도쿄도 미나토구 코난 1-7-1 소니 가부시끼

가이샤내

## 명세서

### 청구범위

#### 청구항 1

광이 조사되는 제1 기판면 측과 소자가 형성되는 제2 기판면 측을 가지는 기판에 형성되고, 1 화소 셀마다 또는 복수 화소 셀을 단위로 하여 인접 셀 그룹과 소자 분리층(element separation layer)에 의해 분리된 화소 셀을 포함하고,

각각의 상기 화소 셀은,

상기 제1 기판면 측에 형성된 제1 도전형 웨; 및

상기 제2 기판면 측에 형성된 제2 도전형 웨

을 포함하고,

상기 제1 도전형 웨은, 상기 제1 기판면 측으로부터의 광을 수광하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가지고,

상기 제2 도전형 웨에는, 상기 제1 도전형 웨에서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 트랜지스터가 형성되어 있는, 고체 활상 장치.

#### 청구항 2

제1항에 있어서,

상기 축적 전하와 신호 전하는 동일 캐리어인, 고체 활상 장치.

#### 청구항 3

제1항에 있어서,

상기 트랜지스터는, 판독 트랜지스터로서의 기능과, 리셋 트랜지스터로서의 기능과, 선택 트랜지스터로서의 기능을 가지는, 고체 활상 장치.

#### 청구항 4

제1항에 있어서,

상기 화소 셀은, 저 조도 시에 변조가 높아지는 감마 특성을 가지는, 고체 활상 장치.

#### 청구항 5

제4항에 있어서,

상기 화소 셀은, 대신호 출력 시에 용량이 증대하는 구조를 가지고, 감마 특성에 의한 고다이나믹 레인지로 실현하는 기능을 가지는, 고체 활상 장치.

#### 청구항 6

제1항에 있어서,

상기 제1 도전형 웨 및 상기 제2 도전형 웨 중 적어도 상기 제1 도전형 웨의 측부에 제2 도전형 분리층이 형성되어 있는, 고체 활상 장치.

#### 청구항 7

제6항에 있어서,

상기 제2 도전형 웨 또는 제2 도전형 분리층에는, 제1 도전형 소스 영역 및 제1 도전형 드레인 영역이 형성되고,

상기 기판의 상기 제2 기판면 측에서의 상기 소스 영역과 상기 드레인 사이의 상기 제2 도전형 웰 중의 채널 형성 영역 상에 게이트 전극이 형성되어 있는, 고체 활상 장치.

#### 청구항 8

제7항에 있어서,

복수의 상기 화소 셀이 어레이형으로 배열되고, 인접 화소 셀과 상기 드레인, 또는 소스, 또는 웰, 또는 게이트의 컨택트를, 일부 또는 복수 공유하는, 고체 활상 장치.

#### 청구항 9

제7항에 있어서,

복수의 상기 화소 셀이 어레이형으로 배열되고,

상기 화소 셀의 게이트 전극이 상기 화소 배열의 한쪽 방향으로 스트라이프형으로 복수 화소 셀에 대해 공통으로 형성되고,

상기 소스 영역 측 또는 상기 드레인 영역 측에 웰 컨택트가 형성되어 있는, 고체 활상 장치.

#### 청구항 10

제9항에 있어서,

상기 제2 도전형 분리층에 웰 컨택트 영역이 형성되어 있는, 고체 활상 장치.

#### 청구항 11

제10항에 있어서,

상기 웰 컨택트 영역은, 상기 제1 기판면 측의 상기 제2 도전형 분리층에 형성되어 있는, 고체 활상 장치.

#### 청구항 12

제9항에 있어서,

상기 웰 컨택트가 드레인 측에 형성되어 있는 경우는, 상기 웰 컨택트는 드레인 폭을 줄인 핀치 형상(pinch shape)으로 형성되어 있는, 고체 활상 장치.

#### 청구항 13

제1항에 있어서,

어레이형의 화소 셀의 배열에 있어서, 열 중 드레인 컨택트를 2개 이상의 그룹으로 나누어 신호 판독 처리계의 컬럼 회로를 공유하고 있는, 고체 활상 장치.

#### 청구항 14

제3항에 있어서,

상기 제2 기판면 측의 트랜지스터의 게이트 전극, 또는, 게이트 전극의 추가의 앞면 부에, 상기 기판을 투과한 광을 반사하여 상기 기판의 제2 도전형 웰, 및 제1 도전형 웰에 입사시키는 리플렉터를 가지는, 고체 활상 장치.

#### 청구항 15

제14항에 있어서,

상기 리플렉터가 소정의 배선층으로 겹용되는, 고체 활상 장치.

#### 청구항 16

제3항에 있어서,

화소 리셋 직전에 상기 트랜지스터의 드레인으로부터 화소에 전하를 주입하고나서 상기 화소를 리셋 동작시키는, 고체 활상 장치.

### 청구항 17

제4항에 있어서,

상기 화소 셀의 상기 트랜지스터와 동일한 구조의 백 게이트 단자를 가진 트랜지스터를 사용하여 역감마 보정을 행하는 역 γ 보정 회로를 더 포함하는, 고체 활상 장치.

### 청구항 18

제16항에 있어서,

상기 화소 셀로부터 신호를 판독하기 위한 신호 처리계를 더 포함하고,

상기 신호 처리계는, 비교기를 포함하고, 상기 비교기의 기준 레벨로서, 전 라인(preceding line)의 리셋 레벨을 이용하는, 고체 활상 장치.

### 청구항 19

제1항에 있어서,

화소로부터의 신호 판독시에, 화소 리셋을 하지 않고 광전 변환을 계속하는 파괴 읽기(destructive readout)를 행하는 신호 처리계를 더 포함하는, 고체 활상 장치.

### 청구항 20

기판의 제1 기판면 측으로부터 광을 수광하는 고체 활상 장치;

상기 고체 활상 장치의 상기 제1 기판면 측에 입사광을 안내하는 광학계; 및

상기 고체 활상 장치의 출력 신호를 처리하는 신호 처리 회로

를 포함하고,

상기 고체 활상 장치는,

광이 조사되는 제1 기판면 측과 소자가 형성되는 제2 기판면 측을 가지는 기판에 형성되고, 1 화소 셀마다 또는 복수 화소 셀을 단위로 하여 인접 셀 그룹과 소자 분리층에 의해 분리된 화소 셀을 포함하고,

각각의 상기 화소 셀은,

상기 제1 기판면 측에 형성된 제1 도전형 웨; 및

상기 제2 기판면 측에 형성된 제2 도전형 웨

을 포함하고,

상기 제1 도전형 웨은, 상기 제1 기판면 측으로부터의 광을 수광하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가지며,

상기 제2 도전형 웨에는, 상기 제1 도전형 웨에서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 트랜지스터가 형성되어 있는, 카메라.

## 발명의 설명

### 발명의 상세한 설명

#### 기술 분야

[0001] 본 발명은 광전 변환 소자를 가지는 고체 활상 장치 및 카메라에 관한 것이다.

## 배경기술

- [0002] 고체 활상 장치, 예를 들면, CCD 이미지 센서나 CMOS 이미지 센서에서는, 수광부의 광전 변환 소자인 포토 다이오드 중의 결정 결함(crystal defect)이나, 수광부와 그 위의 절연막과의 계면에서의 계면 준위(deep level defect)가 암 전류(dark current)의 발생원인으로 되는 것이 알려져 있다.

- [0003] 그 중, 계면 준위에 기인한 암 전류의 발생을 억제하는 방법으로서는, 매립형 포토 다이오드 구조가 유효하다. 이 매립형 포토 다이오드는, 예를 들면, n형 반도체 영역을 형성하고, 이 n형 반도체 영역의 표면, 즉 절연막과의 계면 근방에, 암 전류 억제를 위한 얇고 불순물 농도가 진한 p형 반도체 영역(정공 축적 영역)을 형성하여 구성된다.

- [0004] 상기 매립형 포토 다이오드의 제작 방법으로서는, p형 불순물로 되는 B나  $BF_2$ 를 이온 주입하고, 어닐 처리하여, 포토 다이오드를 구성하는 n형 반도체 영역과 절연막과의 계면 근방에 p형 반도체 영역을 제작하는 것이 일반적이다.

- [0005] 또한, CMOS 이미지 센서에서는, 각 화소가, 포토 다이오드, 및 판독, 리셋, 증폭 등의 각종의 트랜지스터를 포함하여 형성된다. 포토 다이오드에 의해 광전 변환된 신호는, 이들 트랜지스터에 의해 처리된다. 각 화소의 상부에는 다층의 금속 배선을 포함하는 배선층이 형성된다. 배선층 상에는, 포토 다이오드에 입사하는 광의 파장을 규정하는 컬러 필터나, 포토 다이오드에 광을 집광하는 온 침 렌즈가 형성된다.

- [0006] 이와 같은 CMOS 이미지 센서로서는, 각종의 특징을 가지는 디바이스 구조가 제안되어 있다.

- [0007] 구체적으로는, 광전 변환 소자 구조에 CCD형 특징을 채용한 전하 변조 디바이스(CMD: Charge Modulation Device, 일본 특허 제1938092호 공보, 일본 특허출원 공개번호 평6-120473호 공보, 및 일본 특허출원 공개번호 소60-140752호 공보 참조), 벌크 전하 변조 디바이스(BCMD: Bulk Charge Modulation Device, 일본 특허출원 공개번호 소 64-14959호 공보 참조), 극대점에 축적되는 포토 홀의 전하량에 따라 표면에 채널이 형성되고, 이 표면의 전하량에 의해 소스/드레인 전류가 변화되고, 그 결과 신호 전하에 따른 판독이 가능해지는 플로팅 웰형 증폭기(FWA: Floating Well Amplifier, 일본 특허 제2692218호 공보 및 일본 특허 제3752773호 공보 참조), 수광부와 신호 검출부를 분류 인접하여 배치한 임계값 변조형 이미지 센서(VMIS: Vth Modulation Image Sensor, 일본 특허출원 공개번호 평2-304973호 공보, 일본 특허출원 공개번호 2005-244434호 공보, 일본 특허 제2935492호 공보, 및 일본 특허출원 공개번호 2005-85999호 공보 참조) 등의 각종 디바이스가 제안되어 있다.

- [0008] 또한, 입사광에 의해 광전 변환을 행하고, 광전 변환에 의해 얻어진 신호 전하를 축적하고, 축적된 신호 전하의 전하량에 따라 신호 전압을 출력하는 기능을 겸비하는 수광 소자가, 평면적으로 보아 같은 개소에서 신호 전하가 축적되기 쉽고, 또한 표면 채널 전류가 흐르기 쉬워지는 포텐셜 분포(potential distribution)를 가지고 있는 고체 활상 소자가 제안되어 있다(일본 특허출원 공개번호 2003-31785호 공보 참조).

- [0009] 이들 CMOS 이미지 센서는, 기본적으로 디바이스의 앞면측으로부터 광을 조사하는 앞면 조사형의 고체 활상 장치이다.

- [0010] 이에 대하여, 포토 다이오드나 각종의 트랜지스터를 형성한 실리콘 기판의 배면측을 연마함으로써 박막화하고, 기판 배면 측으로부터 광을 입사시켜 광전 변환하는 이면(배면) 조사형의 고체 활상 장치가 제안되어 있다(일본 특허출원 공개번호 평 10-65138호 공보 참조).

## 발명의 내용

### 해결 하고자하는 과제

- [0011] 그런데 전술한 앞면 조사형의 CMD나 BCMD, FWA, VMIS 등에서는, 기판을 오버플로로서 이용하고 있으므로 이면(배면) 조사가 불가능하고, 또한 리셋 전압도 높았다.

- [0012] 앞면 조사형의 CMD나 BCMD, FWA, VMIS 등에서는, 수광부는, 광업 트랜지스터의 가로로 배치하므로, 개구율이 저하되는 문제점이 있다.

- [0013] 또한, 기존의 포토 게이트 구조에서는, 박막 게이트를 통해 수광하기 위하여, 청감도(blue sensitivity)가 저하되는 문제점이 있다.

- [0014] 또한, BCMD와 같이, 앞면 조사형으로 n-층 상에 포토 게이트형 MOS형 트랜지스터를 형성한 경우, 광 조사에 의한 캐리어 생성이 반도체 표면 근처에서 행해지므로, 반도체-절연막 계면에 존재하는 트랩에 캐리어가 포획되어 축적 캐리어가 리셋 전압을 인가해도 바로는 배출되지 않고, 디바이스 특성에 영향을 주는 문제점이 있다.

- [0015] 또한, VMIS와 같이, 앞면 조사형으로, 수광 포토 다이오드 영역과 신호 검출 트랜지스터를 인접 배치하는 것과 같은 경우에는, 수광에 의해 생성된 전하의 축적과 변조 조작은 다이나믹한 동작이 아니고, 시간적으로 별도의 시간에 행해지므로, 고속 신호 처리에 불리하게 된다.

- [0016] 마찬가지로, 앞면 조사형으로, 수광 포토 다이오드 영역과 신호 검출 트랜지스터를 인접 배치하는 것과 같은 경우에는, 신호 검출부의 상부에 차광막을 설치하는 등의 연구가 필요해지고, 소자 제조 프로세스가 복잡하게 되는 등의 문제점이 있다.

- [0017] 또한, 앞면 조사형의 BCMD형 이미지 센서에서는, 포토 게이트 전극 아래의 채널 영역 전역이 전하 축적층으로 되므로, 전류 전압 특성(ID-VDD)이 포화 특성이 되지 않고, 3극관 특성이 되어 버려, 소스 폴로워 형으로 사용하는 경우, 사용하기 어렵다는 문제점이 있다.

- [0018] 그리고 상기한 앞면 조사형의 CMOS 이미지 센서에서는, 화소의 상부의 배선에 의해 광이 차단되어, 각 화소의 감도가 저하되고, 또한 이들 배선으로 반사된 광이 인접 화소에 입사하면 색혼합 등의 원인으로 되는 문제점이 있다.

- [0019] 일본 특허출원 공개번호 2003-31785호 공보에 개시된 고체 활상 소자에서는, 싱글 웨로 1트랜지스터를 실현하기 위하여, 2층 게이트 구조를 사용하고 있지만, 이것으로는, 소자 분리 영역에 특수한 세공이 필요해지고, 소자 제조 프로세스가 복잡하게 되는 등의 문제점이 있다.

- [0020] 또한, 이 고체 활상 소자도 앞면 조사형이므로, 전술한 앞면 조사형의 청감도의 저하나 색혼합 색 등의 문제를 가지고 있다.

- [0021] 일본 특허출원 공개번호 평 10-65138호 공보에 개시된 배면 조사형의 고체 활상 장치의 경우, 정공 축적 영역은 기판의 표면 측 및 배면 측에 형성되지만, 이온 주입에 의한 얇고 진한 p형 반도체 영역의 형성에는 한계가 있다. 그러므로 암 전류의 억제를 위해서 p형 반도체 영역의 불순물 농도를 더 올리려고 하면, p형 반도체 영역이 깊어진다. p형 반도체 영역이 깊어지면, 포토 다이오드의 pn접합이 전송 게이트로부터 이격되므로, 전송 게이트에 의한 관독 해 능력이 저하될 우려가 있다.

- [0022] 그러므로 포토 캐리어의 생성, 축적, 전하의 관독, 잔류 전하의 송출(리셋)과 같은 일련의 동작을 효율적으로 고속으로 행하고, 광의 청에 대한 감도를 열화시키지 않고, 광에 의한 캐리어의 실리콘 계면에서의 트랩 영향을 막아, 고감도화와 화소의 미세화를 도모할 수 있는 고체 활상 장치 및 카메라를 제공하는 것이 바람직하다.

### 과제 해결수단

- [0023] 본 발명의 일실시예에 따르면, 고체 활상 장치는, 광이 조사되는 제1 기판면 측과 소자가 형성되는 제2 기판면 측을 가지는 기판에 형성되고, 1 화소 셀마다 또는 복수 화소 셀을 단위로 하여 인접 셀 그룹과 소자 분리층에 의해 분리된 화소 셀을 포함하고, 상기 화소 셀은, 상기 제1 기판면 측에 형성된 제1 도전형 웨와 상기 제2 기판면 측에 형성된 제2 도전형 웨를 가지고, 상기 제1 도전형 웨은, 상기 제1 기판면 측으로부터의 광을 수광하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가지고, 상기 제2 도전형 웨에는, 상기 제1 도전형 웨에서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 트랜지스터가 형성되어 있다.

- [0024] 바람직하게는, 축적 전하와 신호 전하가 동일 캐리어이다.

- [0025] 바람직하게는, 상기 트랜지스터는, 관독 트랜지스터로서의 기능과, 리셋 트랜지스터로서의 기능과, 선택 트랜지스터로서의 기능을 포함한다.

- [0026] 바람직하게는, 상기 트랜지스터는, 소스 및 드레인, 상기 소스 및 드레인 사이의 채널 형성 영역 상에 형성되는 게이트 전극을 가지고, 화소 신호 리셋은, 전하를 상기 드레인에 버리는 동작이다.

- [0027] 바람직하게는, 상기 화소 셀은, 저 조도 시에 변조가 높아지게 되는 감마 특성을 포함한다.

- [0028] 바람직하게는, 상기 화소 셀은, 대신호 출력 시에 용량이 증대하는 구조를 가지고, 감마 특성에 의한 고다이나믹 레인저로 실현하는 기능을 가진다.

- [0029] 바람직하게는, 상기 제1 도전형 웨 및 상기 제2 도전형 웨 중 적어도 상기 제1 도전형 웨의 측부에 제2 도전형

분리층이 형성되어 있다.

[0030] 바람직하게는, 상기 제2 도전형 웨爾 또는 제2 도전형 분리층에는, 제1 도전형 소스 영역 및 제1 도전형 드레인 영역이 형성되고, 상기 기판의 상기 제2 기판면 측에 있어서의 상기 소스 영역과 상기 드레인 사이의 상기 제2 도전형 웨爾 중의 채널 형성 영역 상에 게이트 전극이 형성되어 있다.

[0031] 바람직하게는, 복수의 상기 화소 셀이 어레이형으로 배열되고, 인접 화소 셀과 상기 드레인 또는 소스 또는 웨爾 또는 게이트의 컨택트를, 일부 또는 복수 공유한다.

[0032] 바람직하게는, 상기 드레인, 소스, 웨爾, 및 게이트의 컨택트가 상기 게이트의 화소 배열의 4방향으로 배치되어 있다.

[0033] 바람직하게는, 복수의 상기 화소 셀이 어레이형으로 배열되고, 상기 화소 셀의 게이트 전극이 상기 화소 배열의 한쪽 방향으로 스트라이프형으로 복수 화소 셀로 공통으로 형성되고, 상기 소스 영역 측 또는 상기 드레인 영역 측에 웨爾 컨택트가 형성되어 있다.

[0034] 바람직하게는, 상기 제2 도전형 분리층에 웨爾 컨택트 영역이 형성되어 있다.

[0035] 바람직하게는, 상기 웨爾 컨택트 영역은, 상기 제1 기판면 측의 상기 제2 도전형 분리층에 형성되어 있다.

[0036] 바람직하게는, 웨爾 컨택트가 드레인 측에 형성되어 있는 경우는, 드레인 폭을 줄인 핀치 형상으로 되어 있다.

[0037] 바람직하게는, 어레이형의 화소 셀의 배열에 있어서, 열 중 드레인 컨택트를 2개 이상의 그룹으로 나누어 신호 판독 처리계의 컬럼 회로를 공유하고 있다.

[0038] 바람직하게는, 드레인 라인 배선은, 저저항화를 위해 도전체로 보장받고 있다.

[0039] 바람직하게는, 상기 제2 기판면 측의 트랜지스터의 게이트 전극 또는 추가의 앞면 부에 상기 기판을 투과한 광을 반사하여 상기 기판의 제2 도전형 웨爾, 및 제1 도전형 웨爾에 입사시키는 리플렉터를 가진다.

[0040] 바람직하게는, 상기 기판 두께가, 상기 리플렉터의 반사광으로서 근적외광을 활용 가능한 두께로 설정되어 있다.

[0041] 바람직하게는, 바람직하게는, 상기 기판 두께가, 상기 리플렉터의 반사광으로서 적(R)광을 활용 가능한 두께로 설정되어 있다.

[0042] 바람직하게는, 전극 배선이, 가시광 투과율이 높은 투명막에 의해 형성되어 있다.

[0043] 바람직하게는, 상기 리플렉터가, 소정의 배선층으로 겸용되고 있다.

[0044] 바람직하게는, 화소 리셋 직전에 상기 드레인으로부터 화소에 전하를 주입하고나서 리셋 동작시킨다.

[0045] 바람직하게는, 상기 화소 셀의 상기 트랜지스터와 동일한 구조의 백 게이트 단자를 가진 트랜지스터를 사용하여 역감마 보정을 행하는 역 γ 보정 회로를 가진다.

[0046] 바람직하게는 상기 화소 셀로부터 신호를 판독하기 위한 신호 처리계를 가지고, 상기 신호 처리계는, 비교기를 포함하고, 상기 비교기의 기준 레벨로서, 전 라인(preceding line)의 리셋 레벨을 이용한다.

[0047] 바람직하게는, 상기 신호 처리계는, D 상 판독(D phase readout) 시는 아날로그, P 상 판독 디지털의 샘플링을 행하는 기능을 가진다.

[0048] 바람직하게는, 상기 화소 셀을 어레이형으로 배열하여, 복수 화소로 하나의 출력 신호로 하는 구성을 가진다.

[0049] 바람직하게는, 상기 화소 셀을 어레이형으로 배열하여, 복수 화소 단위에 소자 분리층에 의해 분리하고, 하나의 출력 신호로 하는 구성을 가진다.

[0050] 바람직하게는, 화소로부터의 신호 판독시에, 화소 리셋을 하지 않고 광전 변환을 계속하는 과정 읽기를 행하는 신호 처리계를 가진다.

[0051] 본 발명의 다른 실시예에 따르면, 카메라는, 기판의 제1 기판면 측으로부터 광을 수광하는 고체 활상 장치와, 상기 고체 활상 장치의 상기 제1 기판면 측에 입사광을 안내하는 광학계와, 상기 고체 활상 장치의 출력 신호를 처리하는 신호 처리 회로를 가지고, 상기 고체 활상 장치는, 광이 조사되는 제1 기판면 측과 소자가 형성되는 제2 기판면 측을 가지는 기판에 형성되고, 1 화소 셀마다 또는 복수 화소 셀을 단위로 하여 인접 셀 그룹과 소자 분리층에 의해 분리된 화소 셀을 포함하고, 상기 화소 셀은, 상기 제1 기판면 측에 형성된 제1 도전형 웨爾과

상기 제2 기판면 측에 형성된 제2 도전형 웨를 가지고, 상기 제1 도전형 웨은, 상기 제1 기판면 측으로부터의 광을 수광하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가지고, 상기 제2 도전형 웨에는, 상기 제1 도전형 웨에서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 트랜지스터가 형성되어 있다.

[0052] 본 발명의 일실시예에 의하면, 셀 구조의 화소에 기판 배면(제1 기판면) 측으로부터 광을 조사하고, 제1 도전형 웨에 있어서 수광된 광의 광전 변환을 행하고, 그 전하를 축적한다.

[0053] 그리고 전하 축적을 검출하고, 제2 도전형 웨에 형성된 트랜지스터의 임계값 변조를 행함으로써, 신호를 인출한다.

[0054] 이와 같이, 화소 셀은 배면 조사형으로 더블 웨 구조를 가지고, 축적 전하와 채널 전류(신호 전하)가 동일 캐리어이다.

### 효과

[0055] 본 발명의 실시예에 의하면, 포토 캐리어의 생성, 축적, 전하의 판독, 잔류 전하의 송출(리셋)과 같은 일련의 동작을 효율적으로, 고속으로 행할 수 있다.

[0056] 또한, 광의 청에 대한 감도를 열화시키지 않고, 광에 의한 캐리어의 실리콘 계면에서의 트랩 영향을 막아, 고감도화와 화소의 미세화를 도모할 수 있다.

### 발명의 실시를 위한 구체적인 내용

[0057] 이하에, 본 발명의 실시예에 대하여, 도면을 참조하여 설명한다.

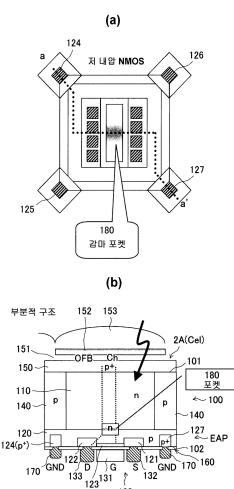

[0058] 도 1은, 본 실시예에 따른 고체 활상 장치의 개략 구성을 나타낸 블록도이다.

[0059] 고체 활상 장치(1)는, 도 1에 나타낸 바와 같이, 센싱부로서의 화소부(2), 행방향(Y 방향) 제어 회로(3), 열방향(X 방향) 제어 회로(4), 및 타이밍 제어 회로(5)를 가진다.

[0060] 화소부(2)는, 다음에 설명하는 바와 같이, 복수의 화소 셀(2A)이 예를 들면, 매트릭스형으로 배치되어 구성된다.

[0061] 본 실시예의 화소부(2)의 화소 셀(2A)은, 이면(배면) 조사로, 더블 웨 구조, 임계값 변조(CMD) 방식의 이미지 센서로서 구성되어 있다.

[0062] 그리고 본 실시예에 따른 화소부(2)는, 더블 웨 구조를 채용하고 있다. 화소부(2)에서, 축적 전하와 채널 전류가 동일 캐리어이다. 화소부(2)는 또한 판독 트랜지스터와 리셋 트랜지스터와 선택 트랜지스터의 기능을 1트랜지스터로 공유하는 1트랜지스터 아키텍처(구조)를 가진다.

[0063] 또한, 화소부(2)에 있어서는, 화소 배열에 있어서, 동일 행에 배열된 화소 셀(2A)이 공통의 행선 H0, H1, 등에 접속되고, 동일 열에 배열된 화소 셀(2A)이 공통의 열선 V0, V1, 등에 접속되어 있다.

[0064] 또한, 고체 활상 장치(1)에 있어서는, 화소부(2)의 신호를 차례로 판독하기 위한 제어 회로로서, 내부 클록을 생성하는 타이밍 제어 회로(5), 행 어드레스와 행 주사를 제어하는 행방향(Y 방향) 제어 회로(3), 그리고 열 어드레스와 열 주사를 제어하는 열방향(X 방향) 제어 회로(4)가 배치된다.

[0065] 행방향(Y 방향) 제어 회로(3)는, 타이밍 제어 회로(5)의 타이밍 제어 펄스를 받아, 소정의 행선 H0, H1, 등을 구동한다.

[0066] 열방향(X 방향) 제어 회로(4)는, 타이밍 제어 회로(5)의 타이밍 제어 펄스를 받아, 소정의 열선 V0, V1, 등에 판독되는 신호를 받아 소정의 처리(CDS(Correlated Double Sampling)상관 이중 샘플링 처리)나 아날로그/디지털 변환 처리 등을 행한다.

[0067] 이 열방향 제어 회로(4)에 있어서의 화소 셀(2A)로부터의 신호 판독 처리에 관한 구성, 기능에 대하여는 다음에, 상세하게 설명한다.

[0068] 이하에, 본 실시예에 따른 고체 활상 장치의 화소부의 구체적인 디바이스 구조에 대하여 설명한다.

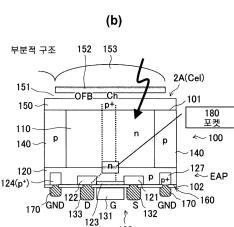

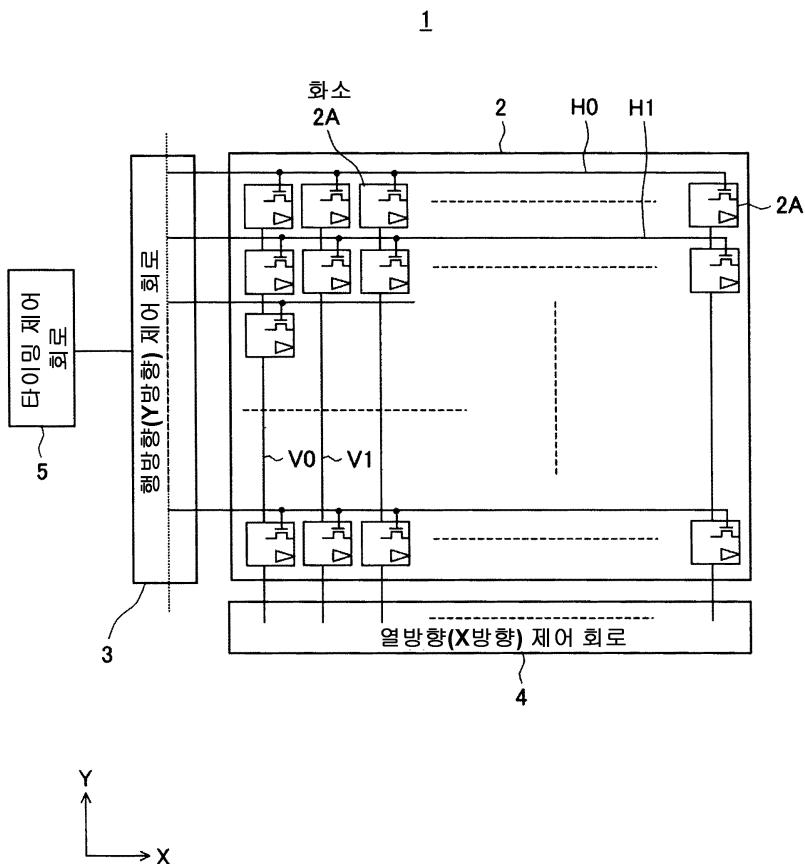

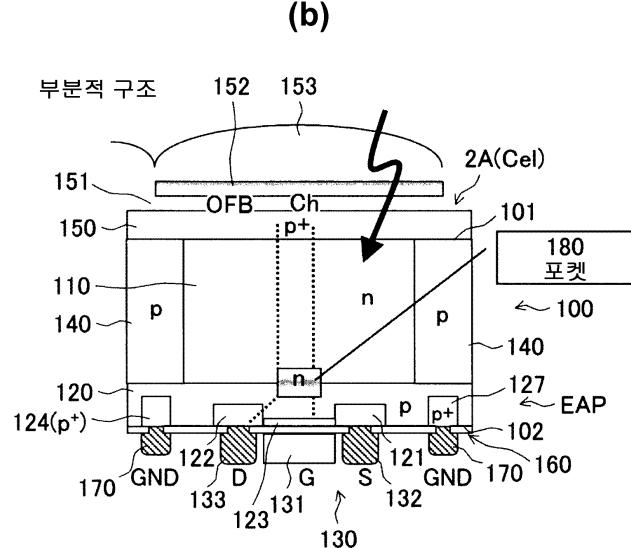

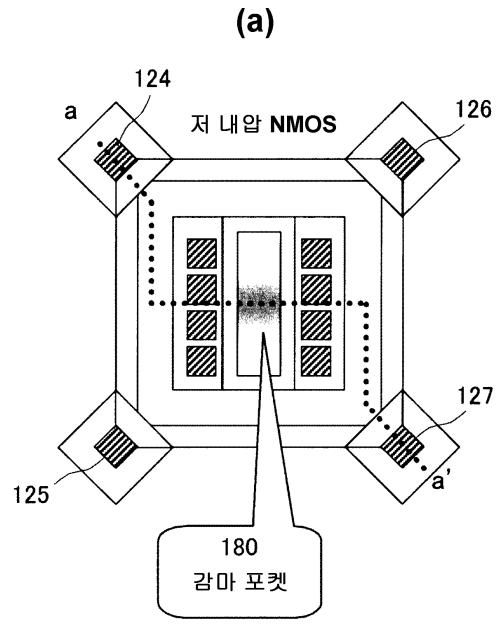

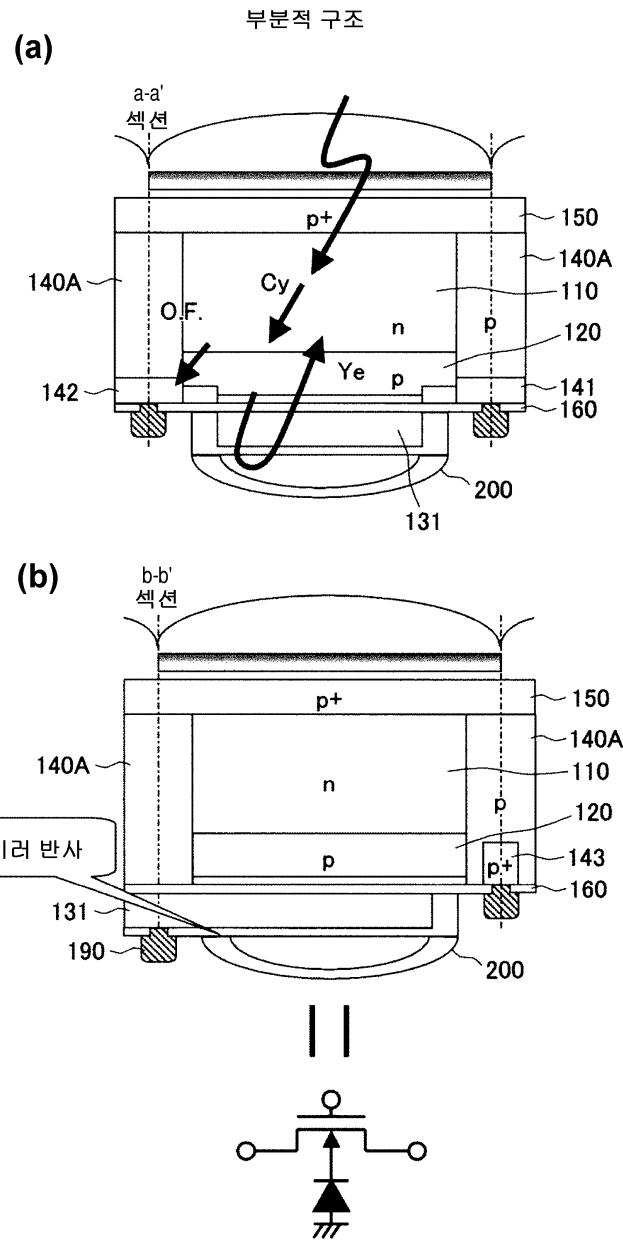

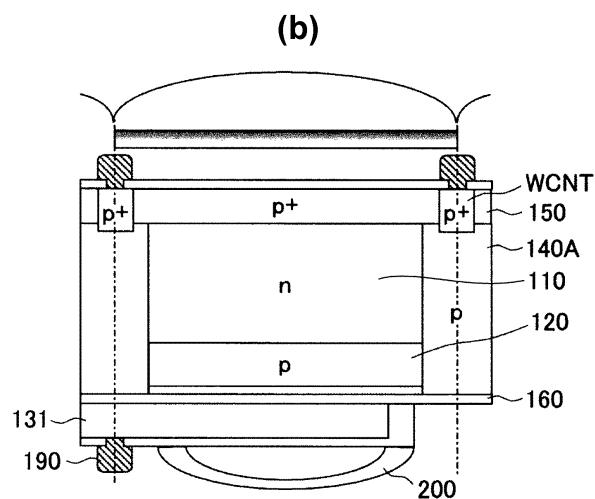

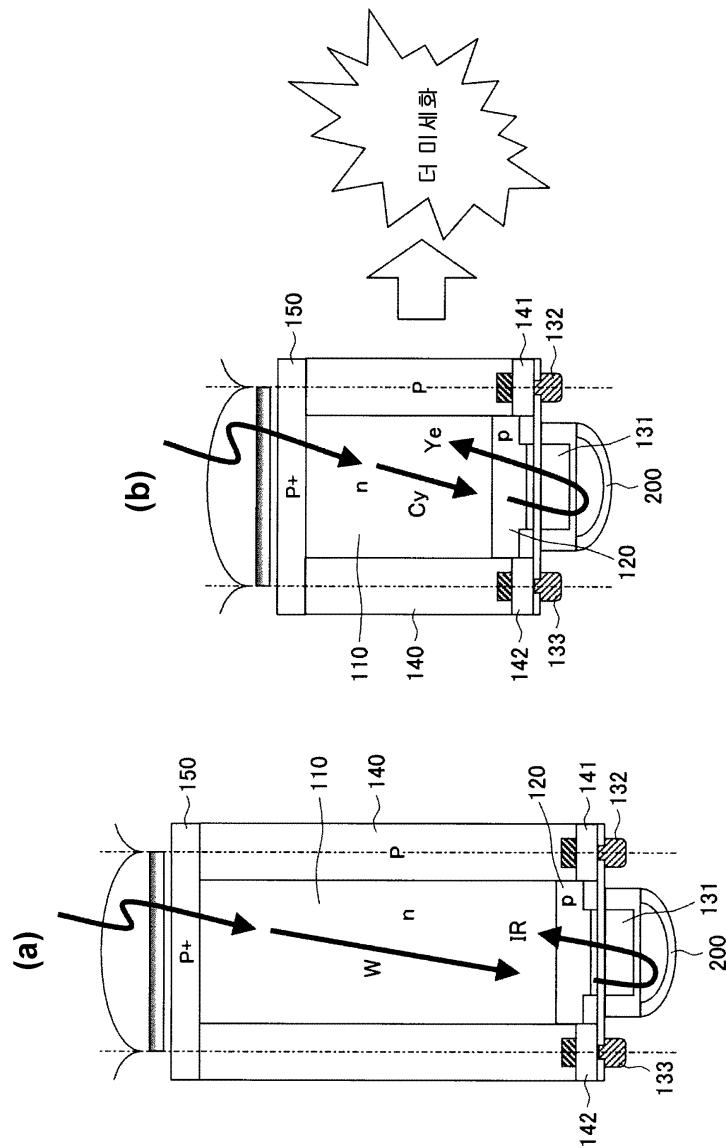

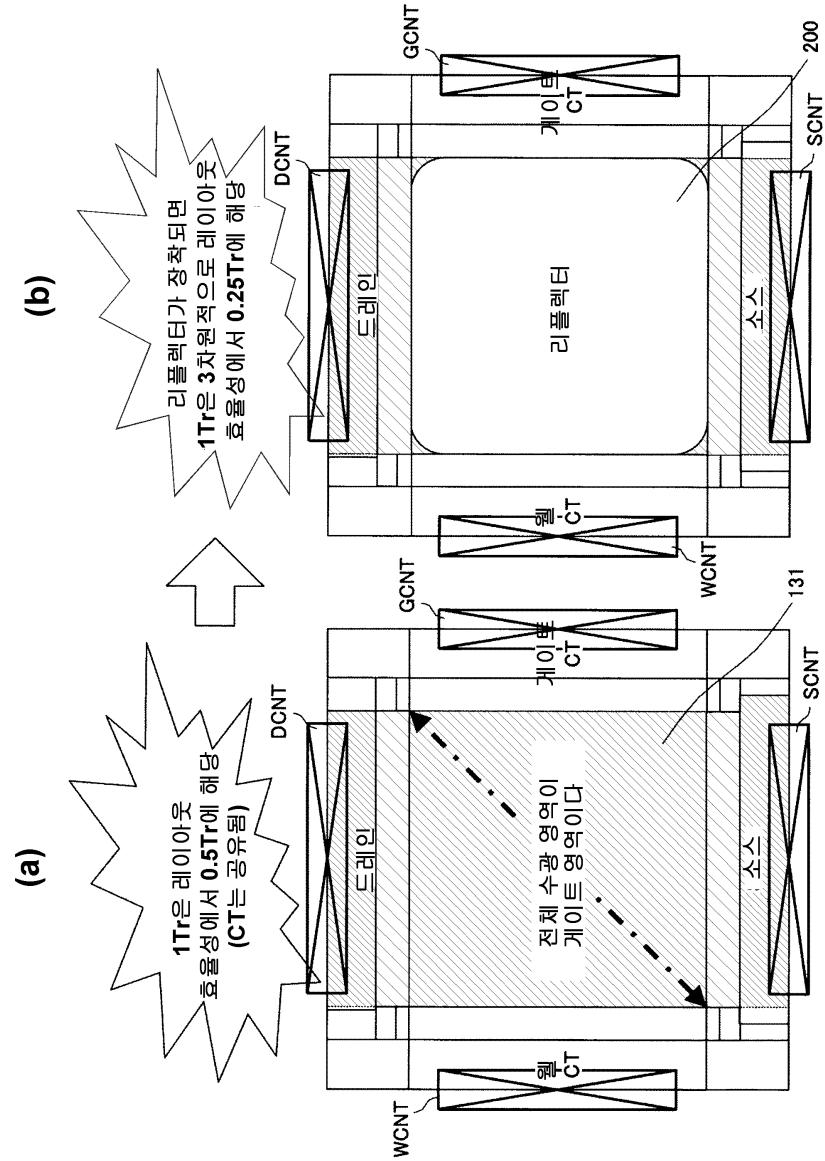

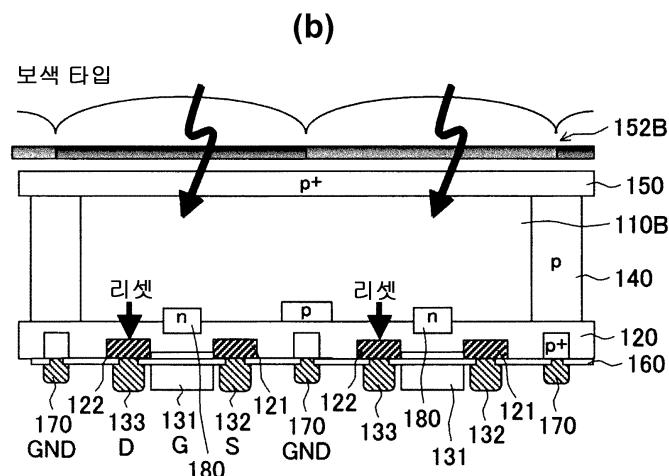

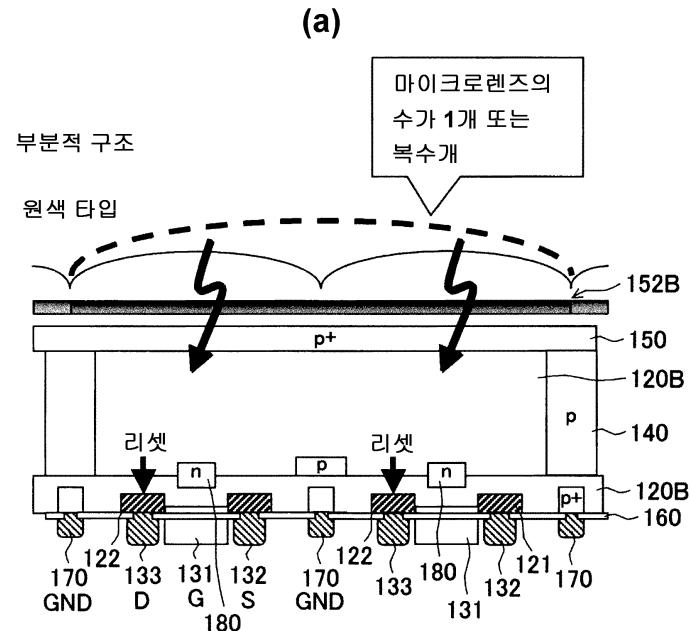

[0069] 도 2a 및 도 2b는, 본 실시예에 따른 고체 활상 장치의 화소부의 기본 구조를 나타낸 도면으로서, 도 2a는 평면도로, 도 2b는 도 2a에 있어서의 a-a'선에 있어서의 간략 단면도이다.

- [0070] 도 2a 및 도 2b에 나타낸 바와 같이, 고체 활상 장치(1)는, 기판(실리콘 기판)(100)의 제1 기판면(101) 측(배면 측)으로부터 광을 입사시켜, 제2 기판면(102) 측(앞면 측)에 MOS형 트랜지스터가 형성되는 소자 영역부 EAP를 형성한 이면(배면) 조사형 디바이스로서 형성되어 있다.

- [0071] 기판(100)은, 배면으로부터 광을 입사할 수 있도록, 실리콘 웨이퍼를 박막화하는 것으로 형성된다. 기판(100)의 두께는, 고체 활상 장치(1)의 종류에도 좌우되지만, 예를 들면, 가시광용의 경우에는  $2 \sim 6 \mu\text{m}$ 이며, 근적외 광용에서는  $6 \sim 10 \mu\text{m}$ 로 된다.

- [0072] 이와 같이, 기판(100)은, 광이 조사되는 제1 기판면(101) 측과 소자가 형성되는 제2 기판면(102) 측을 가지고, 인접 셀과 소자 분리층에 의해 분리된 복수의 화소 셀 Cel(2A)이 형성되어 있다.

- [0073] 본 실시예에 있어서, 기판(100)은, 1 화소 셀마다 또는 복수 화소 셀을 단위로 하여 인접 셀 그룹과 소자 분리 층에 의해 분리된 복수의 화소 셀 Cel(2A)이 형성된다.

- [0074] 화소 셀 Cel은, 제1 기판면(101) 측에 형성된 제1 도전형(본 실시예에 있어서는 n형) 웨(이하, 제1 웨이라 함)(110)과, 제1 웨(110)보다 제2 기판면(102) 측에 형성된 제2 도전형(p형) 웨(이하, 제2 웨이라 함)(120)을 가지고 있다.

- [0075] n형의 제1 웨(110)은, 제1 기판면(101) 측으로부터의 광을 수광부로서 수광부로서 기능하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가진다.

- [0076] 제2 웨(120)에는, 제1 웨(110)의 수광부에 있어서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 MOS형의 트랜지스터(130)가 형성되어 있다.

- [0077] 제1 웨(110)의 측벽에는 이들을 에워싸도록 제1 도전형(본 실시예에서는 n형)의 역의 도전형의 제2 도전형인 p형 소자 분리층(도전 층)(140)이 형성된다. 기판(100)의 광 입사면인 제1 기판면(101)에  $p^+$  층(150)이 형성되어 있다.

- [0078]  $p^+$  층(150)의 광 입사면 측에는, 예를 들면, 산화 실리콘으로 이루어지는 절연막이나 보호막(151)이 형성되어 있다. 그리고 보호막(151) 상에는, 원하는 과정 영역의 광만을 통과시키는 컬러 필터(152)가 형성되어 있다. 또한, 컬러 필터(152) 상에는, 입사광을 제1 웨(110)의 수광부에 집광시키는 마이크로 렌즈(153)가 형성되어 있다.

- [0079] p형의 제2 웨(120)에는, 그 중앙부에  $n^+$  층으로 이루어지는 소스 영역(121) 및 드레인 영역(122)이 소정 간격을 두고 형성되어 있다. 소스 영역(121)과 드레인 영역(122) 사이에는, 채널 형성 영역(123)이 형성된다.

- [0080] 또한, 제2 웨(120)에 있어서의 제1 웨(110)과 겹치지 않는 영역(단부 측 영역)에는,  $p^+$  층으로 이루어지는 웨(기판) 컨택트 영역(124~127)이 형성되어 있다.

- [0081] 또한, 소스 영역(121), 드레인 영역(122), 웨 컨택트 영역(124~127)이 형성되는 기판(100)의 제2 기판면(102)의 표면에 소정의 프로세스에 의해 산화 실리콘 등의 절연막(160)이 선택적으로 형성되어 있다.

- [0082] 그리고 기판(100)의 제2 기판면(102) 측에 있어서의 소스 영역(121)과 드레인 영역(122) 사이의 채널 형성 영역(123) 상에 절연막(160)을 통하여 트랜지스터(130)의 게이트 전극(131)이 형성되어 있다.

- [0083] 또한, 소스 영역(121) 상의 절연막(160)의 일부가 개구되어 소스 영역(121)과 접속되는 트랜지스터(130)의 소스 전극(132)이 형성되어 있다.

- [0084] 마찬가지로, 드레인 영역(122) 상의 절연막(160)의 일부가 개구되어 드레인 영역(122)과 접속되는 트랜지스터(130)의 드레인 전극(133)이 형성되어 있다.

- [0085] 또한, 웨 컨택트 영역(124~127) 상의 절연막의 일부가 개구되어 웨 컨택트 영역(124~127)과 접속되는 웨 컨택트 전극(170)이 형성되어 있다. 웨 컨택트 전극(170)의 레벨은, 예를 들면, 접지 전위 GND(OV)나 또는 -1.2V 등에 설정된다.

- [0086] 이상의 구성에 있어서, 제2 기판면(102) 측의 제2 웨(120)에 형성된 소스 영역(121), 드레인 영역(122), 채널 형성 영역(123), 제2 기판면(102)의 표면 측에 형성된 게이트 전극(131), 소스 전극(132), 및 드레인 전극(133)에 의해 절연 게이트형 전계 효과 트랜지스터(MOS 트랜지스터를 청함)에 의한 트랜지스터(130)가 형성되어 있

다.

[0087] 도 2에 있어서, S는 트랜지스터(130)의 소스를, D는 트랜지스터(130)의 드레인을, G는 트랜지스터(130)의 게이트를, 각각 나타내고 있다.

[0088] 이와 같이, 본 실시예의 각 화소 셀 Cel(2A)은, 이면(배면) 조사로, 더블 웰 구조, 임계값 변조(CMD) 방식의 이미지 센서로서 구성되어 있다.

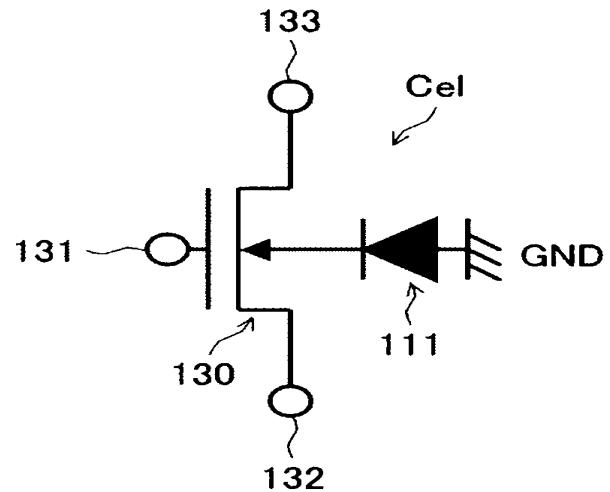

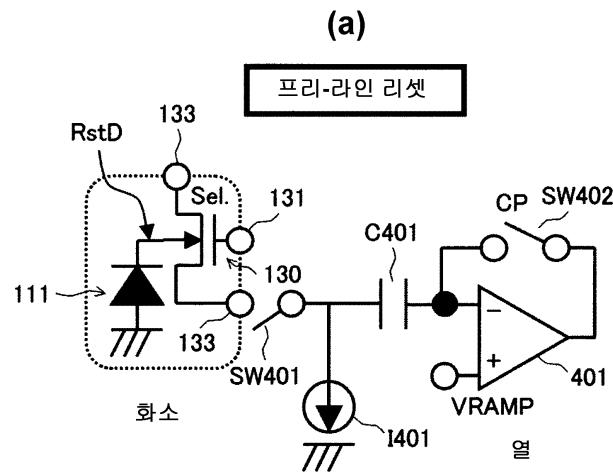

[0089] 도 3은, 본 실시예에 따른 화소 셀의 등가 회로를 나타낸 도면이다.

[0090] 화소 셀(2A)(Cel)은, 도 3에 나타낸 바와 같이, 제1 웰(110)에 형성되는 광전 변환 및 전하 축적 소자부(111), 및 제2 웰(120) 및 제2 기판면(120) 측의 전극에 의해 형성되는 1개의 트랜지스터(130)에 의해 구성된다.

[0091] 전술한 바와 같이, 본 실시예에 따른 화소 셀 Cel은, 배면 조사로, 더블 웰 구조를 가지고, 축적 전하와 채널 전류가 동일 캐리어이며, 또한 판독 트랜지스터와 리셋 트랜지스터와 선택 트랜지스터의 기능을 1트랜지스터로 공유하는 1트랜지스터 아키텍처(구조)를 가진다.

[0092] 환연하면, 본 실시예에 있어서, 배면 조사로 더블 웰(Double-Well) 구조를 채용하고, 싱글 웰(Single-Well) 변조 방식을 채용하고 있지 않다. 그 이유를 이하에 나타낸다.

[0093] 싱글 웰 변조 방식을 채용하면, 선형성(linearity) 개선을 위한 포켓 임플란테이션(pocket implantation)이 필요해 지므로, 이로써, 축적 면적을 감소시키기 위해 화소 미세화시에 포화 전하 Qs가 잡히지 않게 된다.

[0094] 싱글 웰 구조에서는, 변조 및 변환 효율이 높아도, 결함에 대하여 약하다. 싱글 웰 구조에서는, 선형성의 화소 불균일(고양이 다리처럼 생긴 다리)이 다발하기 쉽고, 발생한 경우에는 보정이 곤란하다.

[0095] 또한, 판독 중에 피닝(Pinning)이 벗어나도록 하기 위하여, 컬럼 디지털 CDS와 양립하지 않는다. 아날로그 CDS로 한 경우는, 용량의 면적 비대로 미세화에 장애로 된다.

[0096] 배면 조사와 조합시켜도 리셋 트랜지스터가 필요하며 2트랜지스터 구성으로 됨으로써 화소 미세화에 불리하다.

[0097] 한편, 본 실시예에 있어서는, 배면 조사로, 더블 웰 구조를 가지고, 축적 전하와 채널 전류가 동일 캐리어이며, 소자 분리가 독립된 캐리어에 의해 수행될 수 있다. 그러므로 트랜지스터 구조가 링일 필요가 없다. 트랜지스터는 통상 트랜지스터와 같은 드레인(D)/게이트(G)/소스(S)의 이른바 일방향의 구조로 구성하는 것이 가능하게 되어 있다.

[0098] 본 실시예에 있어서는, 신호 캐리어를 트랜지스터(130)의 드레인에 배출시키는 구조를 채용하고 있다. 이로써 1트랜지스터 판독(픽업) 트랜지스터와 리셋 트랜지스터와 선택 트랜지스터를 공유하는, 완전한 1트랜지스터로, 래터럴 리셋 구조가 실현되어 있다.

[0099] 환연하면, 본 실시예의 화소 셀 구조에 의하면, 2층 게이트 구조가 아닌, 1층 게이트 구조일 수밖에 없기 때문에, 소자 분리 영역에 특수한 세공이 불필요하다.

[0100] 또한, 인접 화소와 드레인 공유나 소스 공유나 게이트 공유가 가능하며, 레이아웃 효율을 비약적으로 높여 화소 미세화가 가능해진다.

[0101] 또한, 트랜지스터의 드레인에 의한 래터럴 리셋을 채용하고 있는 것으로부터, 드레인을 옆배선으로 하는 것과, 공유 화소 단위로 별배선으로 함으로써, 컬럼 공유가 가능해지고 컬럼 회로의 축소(shrink)가 가능하다.

[0102] 또한, 트랜지스터의 게이트 상에 스페이스가 생기기 때문에, 여기에 배선의 메탈 등을 이용한 리플렉터 구조를 설치하는 것이 가능해진다. 그 결과, 실리콘(Si) 기판을 투과한 광을 반사시켜 다시 Si 중에 광전 변환시켜, 예를 들면, 극적외 감도를 향상시킬 수 있다.

[0103] 또한, 기존 구조에서는, 수광 기간 중에 게이트를 오프하고, 실리콘(Si) 기판 표면을 피닝(pinning)시키는 것으로, 계면에서 발생하는 암 전류를 홀(Hole)과 재결합시키고 있으므로, 완전히 재결합하지 않는 성분이 암 전류 불균일이나 흰색점 결함의 원인으로 되는 문제가 있다.

[0104] 이에 대하여, 본 실시예의 구조에서는, 더블 웰 구조가 채용되기 때문에, Si 표면에서 발생하는 암 전류 전자를, 채널로부터 드레인으로 배출시킬 수 있고, 계면에서 발생하는 암 전류나 흰색점을 완전히 봉쇄(shut out)할 수 있는 이점이 있다.

[0105] 그 결과, 컬럼 판독시에 게이트를 온 해도, 암 전류나 흰색점이 문제가 되지 않으므로, 신호의 비파괴 판독이

가능해진다.

[0106] 화소 미세화를 실현하는 배열 구조나, 리플렉터를 갖도록 한 구성, 신호 판독 처리계의 구성 및 기능, 신호의 비파괴 판독 처리에 대하여는 다음에, 상세하게 설명한다.

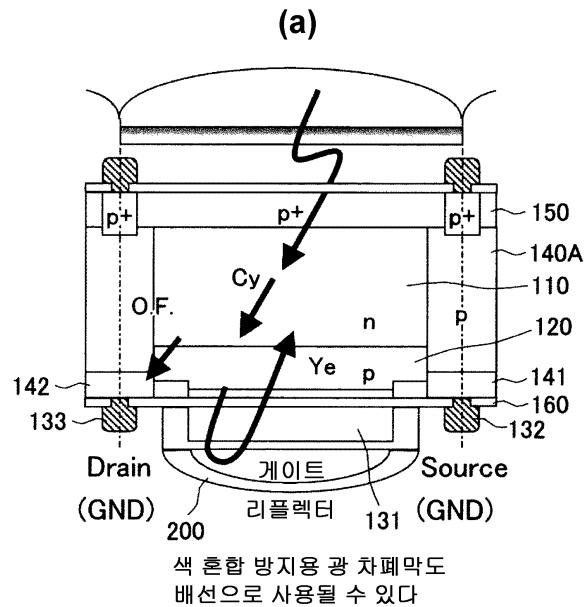

[0107] 여기서, 상기 구성을 가지는 화소 셀에 있어서의 동작에 대하여 설명한다.

[0108] 배면 측에서 있는 제1 기판면(배면)(101)보다 화소 셀 내에 광을 입사시켜, 화소 셀 내의 n형의 제1 웨(110) 내에서 주로 광전 효과에 의해 전자 및 홀 쌍이 발생되고, 발생된 홀이 셀의 벽면을 형성하는 p형 소자 분리층(140)을 통해 외부로 배출된다.

[0109] 그리고 전자만이 n형의 제1 웨(110)에 축적되어 MOS 트랜지스터로서의 트랜지스터(130)의 소스와 드레인 사이의 게이트 영역 반도체 표면 근방에 형성되는 전위 웨(potential well) 내에 축적된다. 트랜지스터(130)를 통하여, 축적 전하의 신호가 증폭되어 검출되고, 축적 전하가 적당히 배출되고, 색혼합이나 포화 전하량의 제어가 행해진다.

[0110] 또한, 고체 활상 장치(1)의 센서의 반도체층의 두께는  $2\text{ }\mu\text{m} \sim 10\text{ }\mu\text{m}$  정도이며, 광의 파장 범위에서 광전 변환의 양자 효율이 충분히 발휘되는 정도의 두께로 되어 있다.

[0111] 이에 대하여, 앞면 조사형의 경우, 통상, 반도체 기판의 두께는 소자가 갈라지기 어려운 두께(~수백  $\mu\text{m}$ )에 유지할 필요가 있다. 그러므로 소자의 기판을 통해 소스와 드레인 사이의 리크 전류를 무시하지 못하고, 문제가 되는 경우가 있다.

[0112] 이에 대하여, 본 실시예에 있어서는, 소자의 두께를 충분히 얇게 하고 있으므로, 기판을 통한 리크 전류를 줄일 수가 있어 이 문제도 회피하고 있다.

[0113] 이상, 본 실시예에 따른 고체 활상 장치(1)의 구성 및 기능에 대하여 설명하였다.

[0114] 이하에, 본 실시예에 따른 고체 활상 장치(1)에 대하여 보다 상세하게 고찰한다.

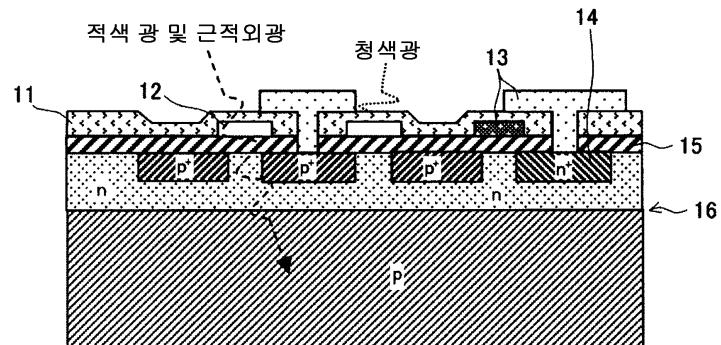

[0115] 도 4는, 앞면 조사형 BMCD의 경우에 대하여, 입사광의 파장이 트랜지스터의 배치와 어떠한 관계가 되는지를 나타낸 도면이다.

[0116] 도 4의 앞면 조사형 BMCD(10)는, 기판 앞면측에 절연막(11), 투명 전극(12), 차광 전극(13) 등이 형성되어 있다. 또한, 도면번호 14는 래터럴 드레인, 15는 게이트 절연막, 16은 실리콘 기판을 나타내고 있다.

[0117] 도 4의 앞면 조사의 경우, 트랜지스터가 설치되어 있는 측으로부터 광이 진입하지만, 그때, 래터럴 드레인 영역(14)은 차광 전극(13)으로 덮여 있고, 그 이외의 개구부로부터 절연막(11)이나 투명 전극(12), 게이트 절연막(15) 등을 투과하여, 실리콘 기판(16) 내에 광이 침입하는 구조로 되어 있다. 파장이 긴 적색광이나 근적외광은 실리콘의 표면으로부터 비교적 내부까지 들어가지만, 청색광이나 근 자외광은 그만큼 깊게까지 들어가지 않는 장소에서 광전 변환이 행해진다. 또한, 파장이 얇은 광은 표면의 절연 다층막을 통과할 때, 산란이나 흡수 또는 충격면에서의 반사 등에 의해, 에너지의 손실을 받기 쉽다.

[0118] 이에 대하여, 도 2의 본 발명에 의한 배면 조사의 경우는, 트랜지스터(130)가 배치되어 있지 않은 측으로부터 광이 기판(실리콘 기판)(100) 내에 침입하는 구조로 되어 있으므로, 파장이 긴 광의 대부분은 트랜지스터 근방에 도달 하지만, 파장이 얇은 광은 매우 일부 밖에 도달하지 않는다.

[0119] 입사광의 파장도 포함하여 양자 효율을 최대로 하기 위하여, 소스와 드레인의 확산층이나 웨층을 어떻게 형성해야 할지에 대하여 여러 가지 제안이 이루어져 있다.

[0120] 그러나 실리콘 산화막(절연막)을 통과하는 광이 트랜지스터 특성에 영향을 미칠 가능성에 대한 논의는 적다. 본 실시예에서는, 이 점에 대하여 정성적인 것(qualitatively)은 아니지만 그 메커니즘을 어느 정도 분명히 한다.

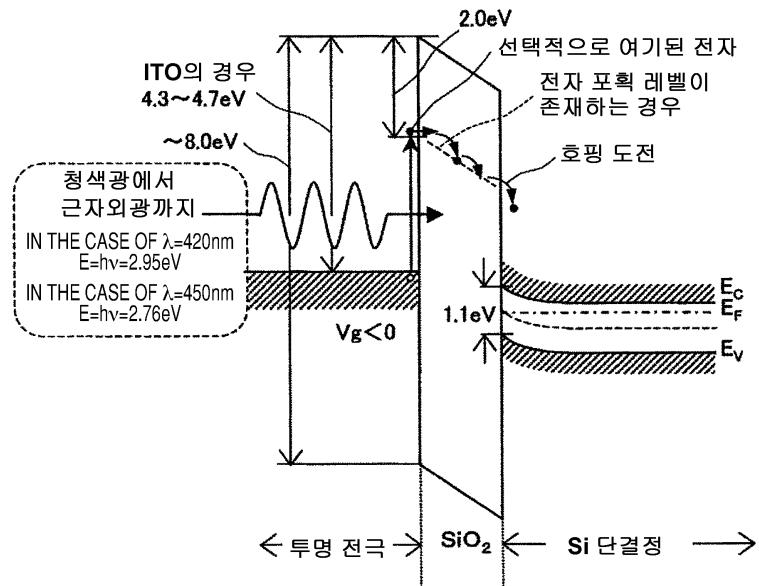

[0121] 도 5는, 앞면 조사형의 경우에, 투명 전극/게이트 실리콘 산화막/실리콘 단결정이 형성하는 에너지 벤드 상태의 개략을 나타낸 도면이다.

[0122] 게이트 산화막은 제법이나 처리에 의해 성질이 현저하게 상위한 경우가 있고, 제법이 너무 제어되어 있지 않은 경우에는, 산화막 중에 전자나 홀을 포획하는 트랩이 잔존한다. 도면에서는 실리콘 산화막의 전도대 아래, 2.0eV의 위치에 전자를 포획하는 트랩이 존재하는 경우를 나타내고 있다.

- [0123] 실리콘 열산화막의 경우, 밴드 갭은 약 8.0eV이며, 투명 전극으로서 ITO를 사용하는 경우는, 일 함수는 약 4.3~4.7eV이므로, 열산화막의 에너지 갭의 한가운데보다 조금 아래에 투명 전극의 페르미 레벨이 위치하게 된다.

- [0124] 지금, 입사광 중 청색광 성분, 예를 들면, 파장  $\lambda = 450\text{nm}$ 에 대하여 주목해 보면, 아인슈타인의 광양자식  $E=h\nu$ 로부터,  $E=2.76\text{eV}$ 에 상당한다. 이 에너지는 도시한 바와 같이, 투명 전극의 페르미 레벨로부터 측정한 산화막 중의 전자 트랩의 에너지 레벨의 위치와 대략 같다.

- [0125] 이때, 실리콘 기판에 대하여 투명 게이트 전극에 비교적 큰 마이너스의 전압을 인가하면, 광전 효과에 의해 금속 표면(투명 전극)으로부터 뛰쳐나온 전자가, 산화막 중에 여기해서 트랩에 포획된다.

- [0126] 트랩에 포획된 전자는 전계에 의해 재방출되어 흡평 전도(hopping conduction)에 의해 실리콘 단결정의 전도대에 흘러들어, 게이트 전극과 실리콘 사이를 약한 도통 상태(weak conduction state)로 하고, 트랜지스터 특성이 신호량에 불균일을 생기게 한다.

- [0127] 본 실시예의 배면 조사에서는, 에너지가 크고 파장이 짧은 광은, 트랜지스터 영역에 도달하기까지 대략 실리콘 기판 내에서 포토 캐리어 생성에 그 에너지를 소비해 버리므로, 앞면 조사와 같은 문제점이 없는 것이 큰 특징이 되어 있다.

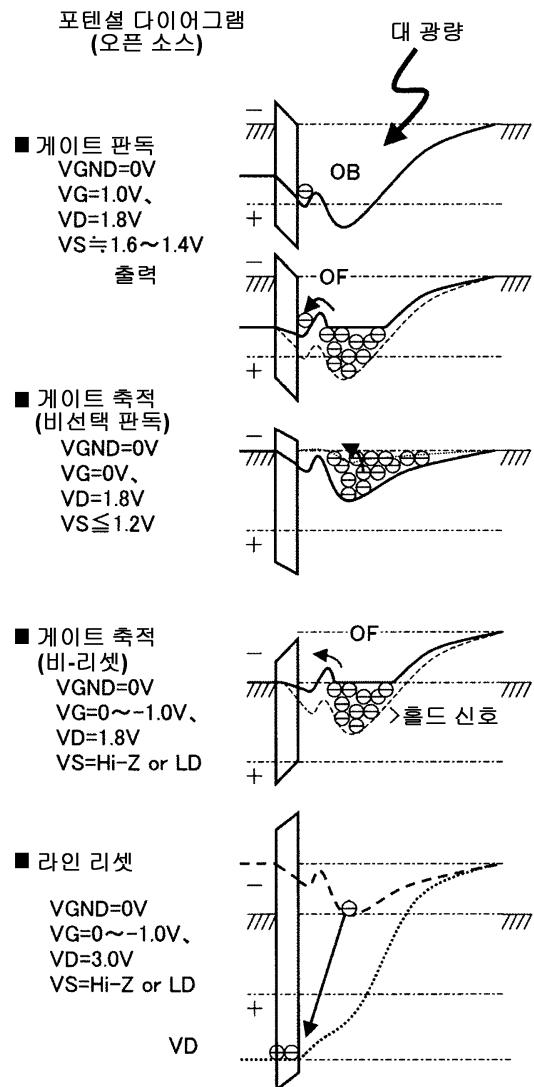

- [0128] 도 6은, 도 2에서 나타내는 장치의 전위 상태 변화에 따른 각 영역에 있어서의 반도체 기판면과 수직 방향의 반도체 기판 내의 전자에 대한 전위의 변화를 나타낸 도면이다.

- [0129] 어느 상태에 있어서도, 웨爾 컨택트 전극(170)의 전압 VGND는 0V에 설정된다.

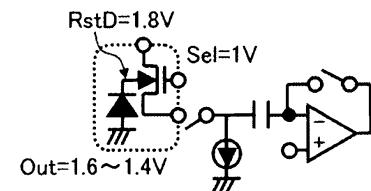

- [0130] (i) 게이트 판독

- [0131] 트랜지스터(130)의 게이트 전압 VG를 1.0V, 드레인 전압 VD를 1.8V로 하면, 소스 전압 VS는 1.6V ~ 1.4V 정도이며, 축적 전하(전자)는 감소하고, 소스로부터 드레인에 흐르는 채널 전자 전류가 그만큼 변조되어 감소한다. 이 전류 변화분을 측정하면, 축적 전자의 전하 변화량이 알 수 있다.

- [0132] (ii) 게이트 축적(비판독 상태)

- [0133] 트랜지스터(130)의 게이트 전압 VG를 0V, 드레인 전압 VD를 1.8V로 하면, 소스 전압 VS는 1.2V 또는 그것 이하이며, 트랜지스터(130)의 소스와 드레인 사이의 게이트 영역에 있어서의 반도체 표면 근방에 형성되는 전위 웨爾 내에 전자가 축적된다.

- [0134] (iii) 게이트 축적(비-리셋 상태, 하드 리셋)

- [0135] 트랜지스터(130)의 게이트 전압 VG를 0V ~ -1.0V, 드레인 전압 VD를 1.8V로 하면, 소스 전압 VS는 하이 임피던스 Hi-Z 또는 LD이며, 축적된 전자가 오버플로(overflow)하는 상태로 된다. 환연하면, 화소 셀 Cel을 포화시킨다. 이때 신호를 유지한다.

- [0136] (iv) 리셋

- [0137] 트랜지스터(130)의 게이트 전압 VG를 0 ~ -1.0V, 드레인 전압 VD를 3.0V 이상, 예를 들면, 3.7V로 하면, 소스 전압 VS는 하이 임피던스 Hi-Z 또는 LD이며, 축적 웨爾 내에 존재하는 전자를, 드레인 전극을 통해 외부에 배출시킨다.

- [0138] 전술한 바와 같이, 본 실시예에 있어서는, 화소 신호 리셋으로서 드레인 전압 VD, 경우에 따라서는 게이트 전압을 포함하여 변조함으로써(도 6의 예에서는 드레인 - 게이트 사이의 전위차를 크게 하여), 드레인 전극에 축적된 신호 전하(전자)를 배출시킨다.

- [0139] 또한, 본 실시예에 있어서는, 저 조도 시에 변조, 변환 효율이 높아지도록, 이른바 감마( $\gamma$ ) 특성을 갖게 하고 있다.

- [0140] 그리고 본 실시예에 있어서는,  $\gamma$  특성을 고다이나믹 레인지(DR)에 활용하고 있다.

- [0141] 여기서, 이 화소 셀의  $\gamma$  특성에 대하여 설명한다.

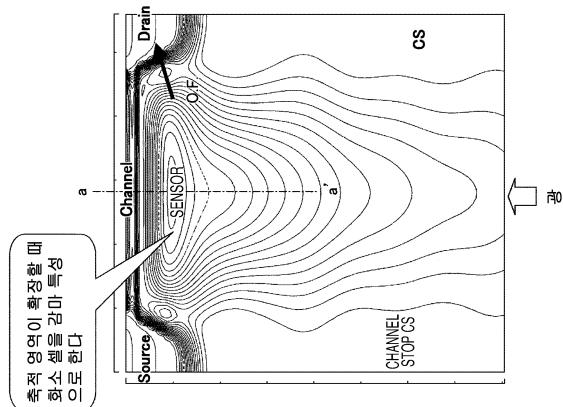

- [0142] 도 7은, 도 2a에 있어서의 a-a'선에 있어서의 포텐셜 분포의 일례를 나타낸 도면이다.

- [0143] 더블 웨爾의 특징의 하나로서, 도 7에 나타낸 바와 같이, 센서 축적 영역이 넓은 포텐셜 형상으로 된다. 이 때문에, 신호량에 의해 용량이 변화되고, 비선형성( $\gamma$  특성)을 가지는 것이다.

- [0144] 그러나 싱글 웰 구조의 비선형성 및 소신호 시에 신호가 결락되는 것에 대하여, 상기 소신호 시에 개인이 올라가는  $\gamma$  특성의 경우는, 역  $\gamma$  보정이 가능한데다가 저 조도 시의 개인이 마이너스로 되므로, 신호와 동시에 노이즈도 압축된다. 이에 따라 저노이즈화가 가능해진다.

- [0145] 이와 같이, 본 실시예에 있어서는,  $\gamma$  특성을 적극적으로 활용하고, 도 2에 나타낸 바와 같이, 소신호를 축적하는 n형에서 깊은 감마 포켓(180)을 설치하고 있다.

- [0146] 이 감마 포켓(180)에 있어서, 신호 캐리어와 신호 전류가 1점에 집중하고, 소신호 변조가 향상된다.

- [0147] 또한, 후단의 신호 처리를 행하는 DSP로 역감마 보정하고, 전노이즈 압축을 실현할 수 있다.

- [0148] 또한, 도 7에 나타낸 바와 같이, 화소 셀 Cel은 대신호 출력 시에 용량이 중대하는 구조를 가지고,  $\gamma$  특성에 의한 고다이나믹 레인지(DR)로 하고 있다.

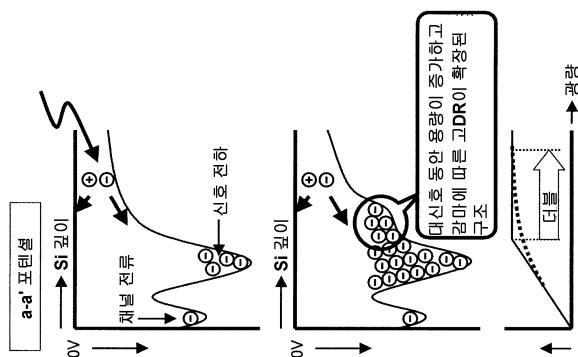

- [0149] 도 8은, 본 실시예의 신호 판독 처리계의 구성을 모식적으로 나타낸 도면이다.

- [0150] 열(X) 방향 제어 회로(4)는, CDS 회로(41)를 포함하고, 신호 전송로 SL, 스위치 SW를 통하여, 온 상태에 있는 화소 셀 Cel의 축적 신호가 전송된다. 그리고 IS는 소스 폴로워를 형성하기 위한 전류원을 나타낸다.

- [0151] 이상, 본 실시예에 따른 화소 셀의 구성 및 기능에 대하여 설명하였다.

- [0152] 이하, 화소부(2)의 화소 셀의 배열, 리플렉터를 가지는 구성 등에 대하여 설명한다.

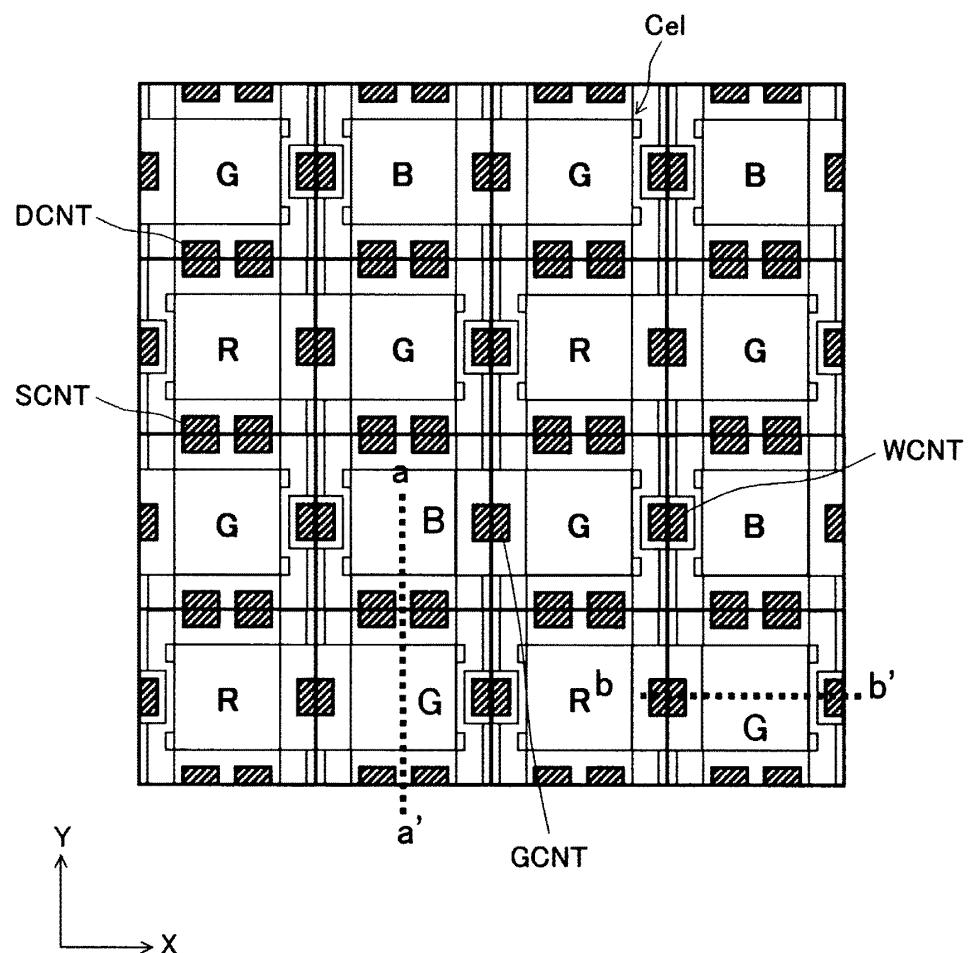

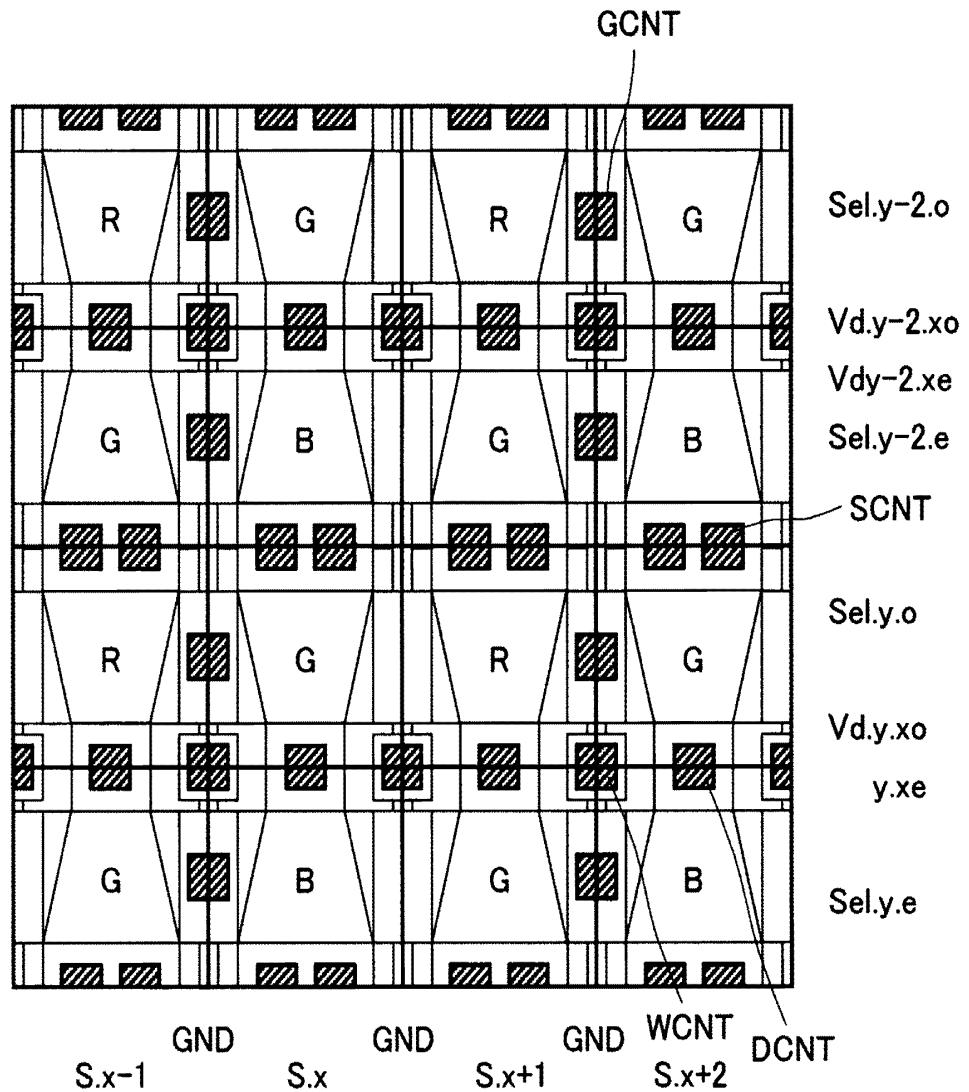

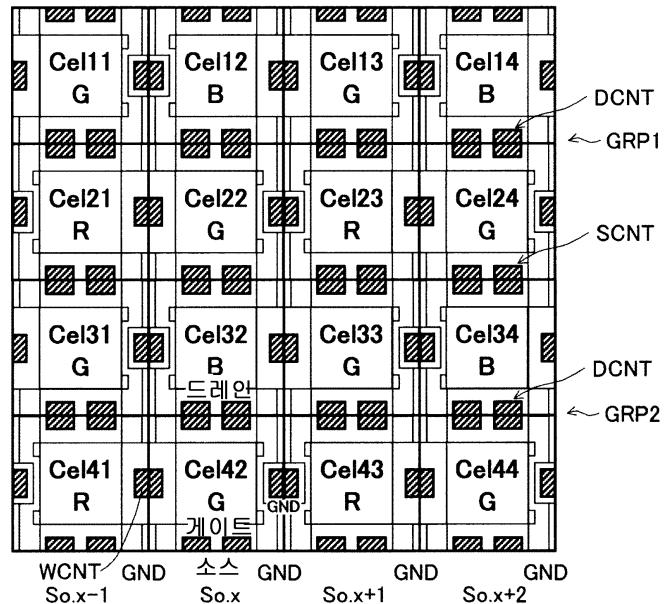

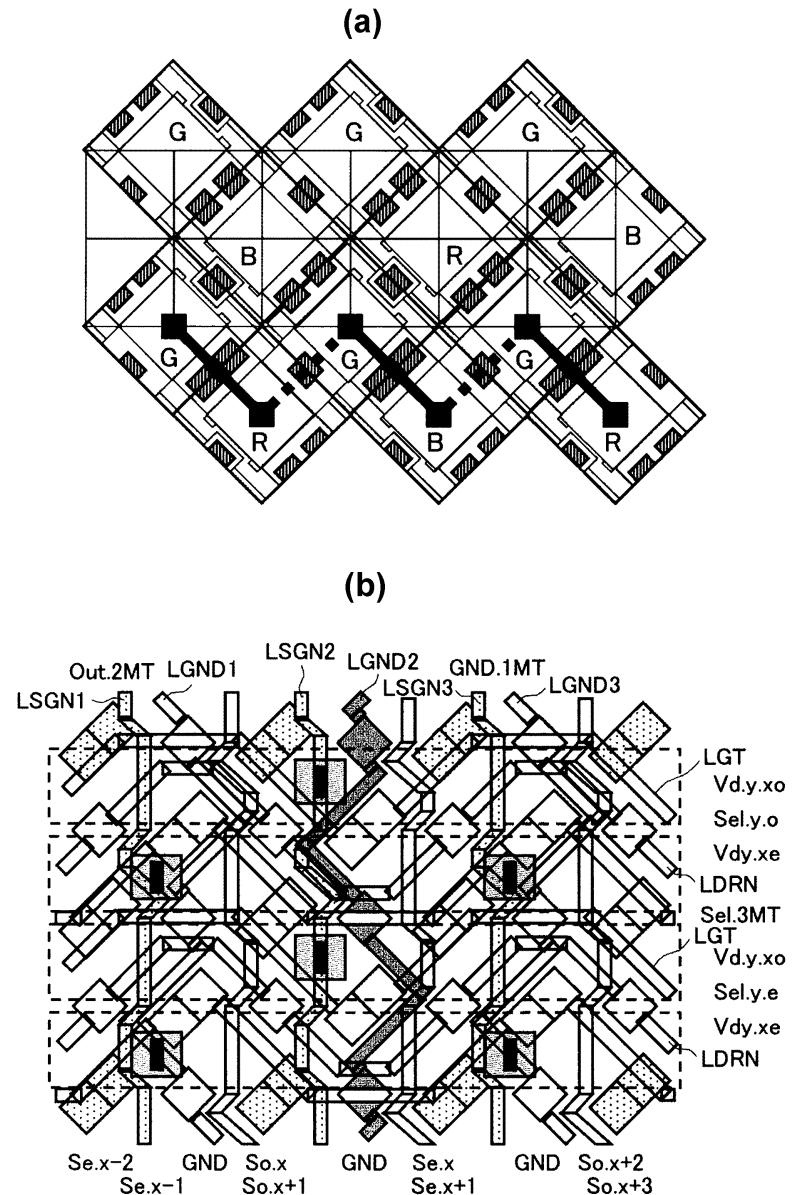

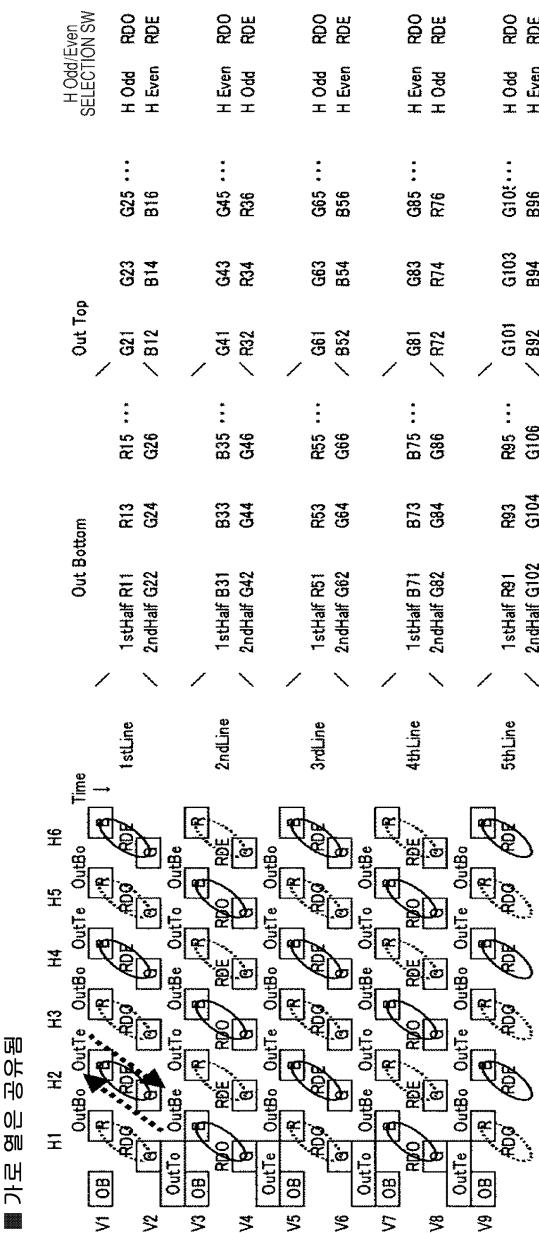

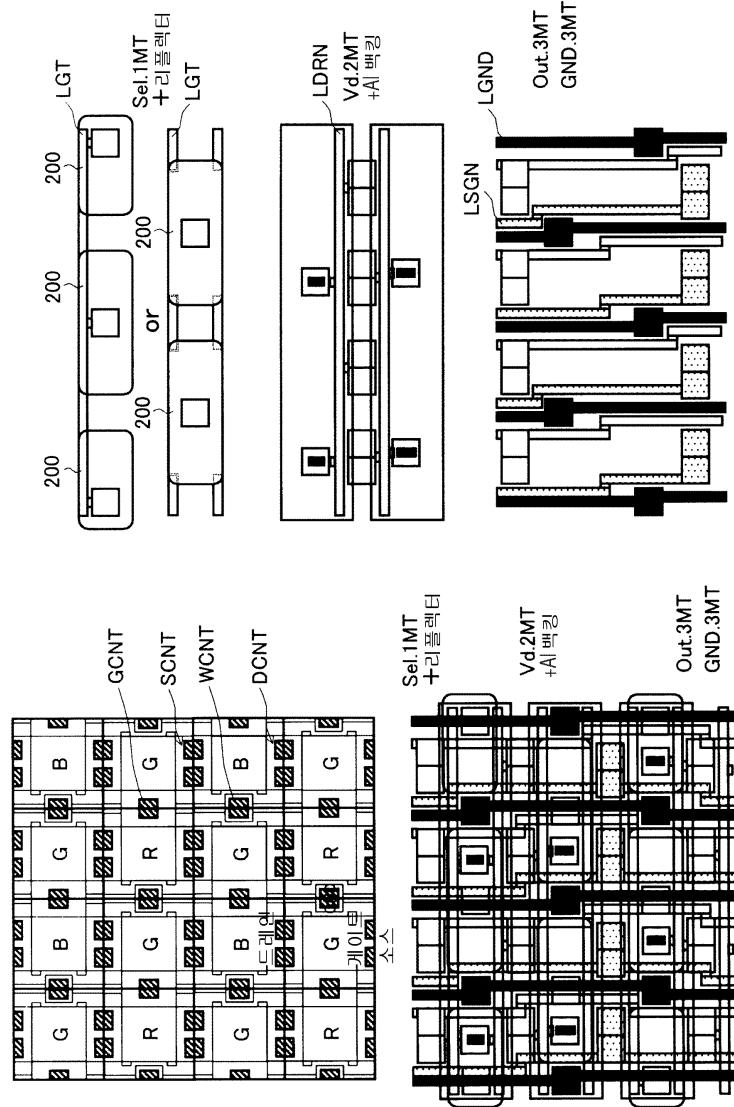

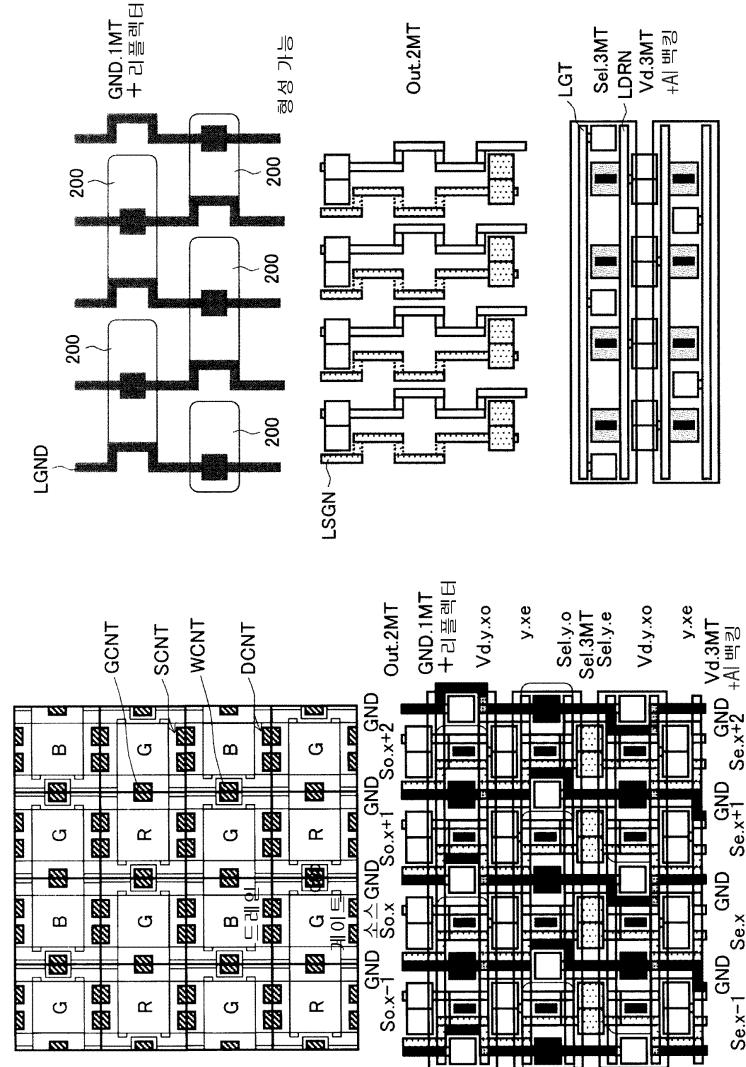

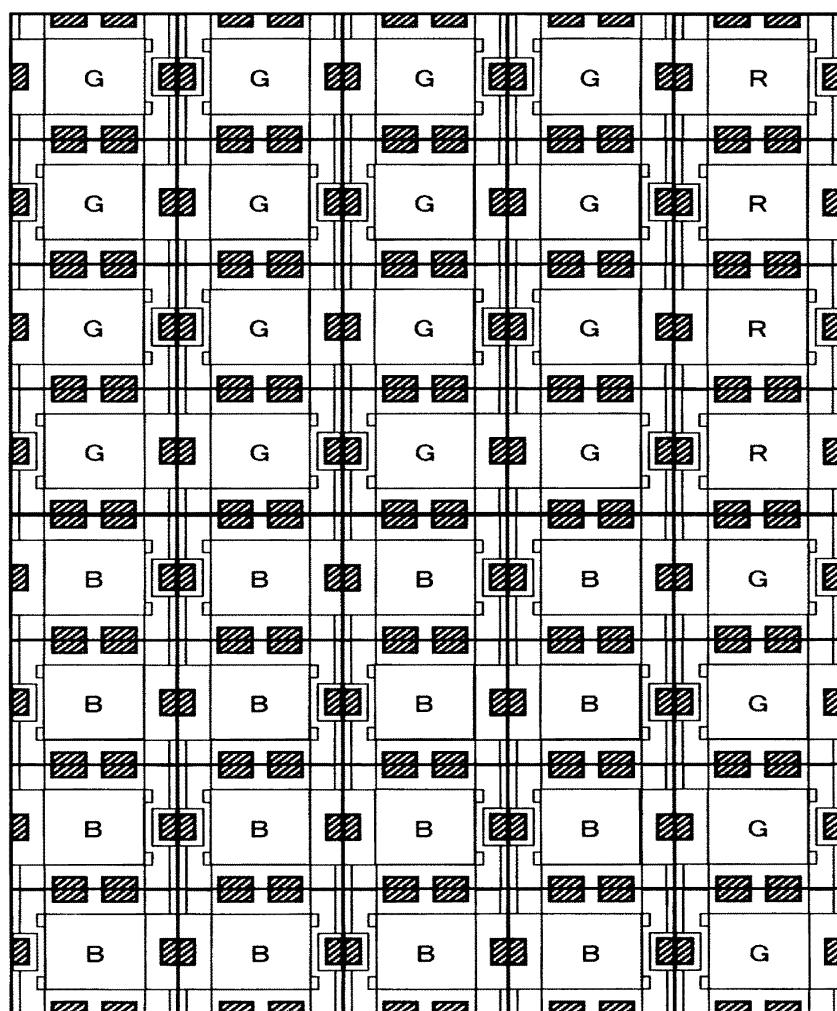

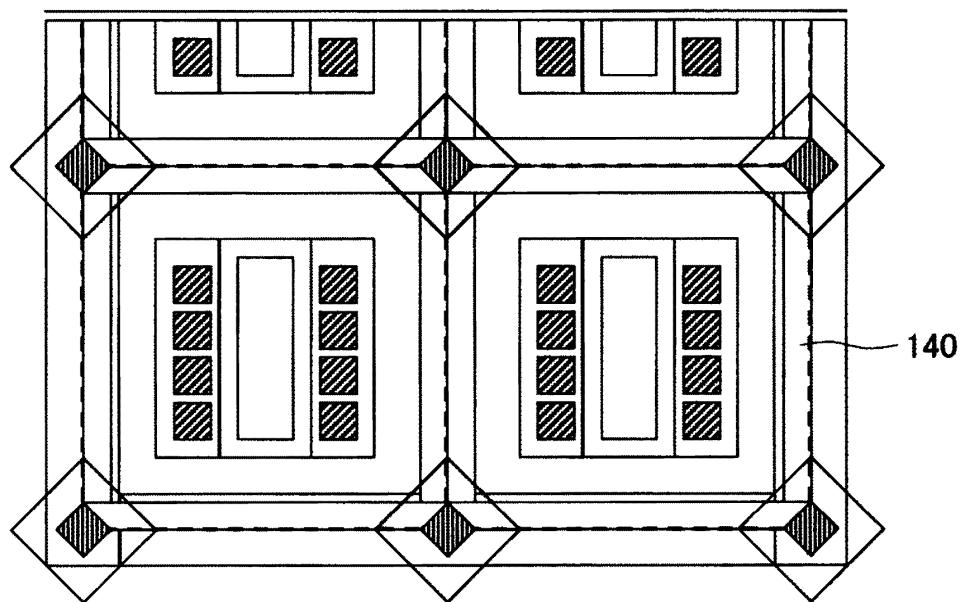

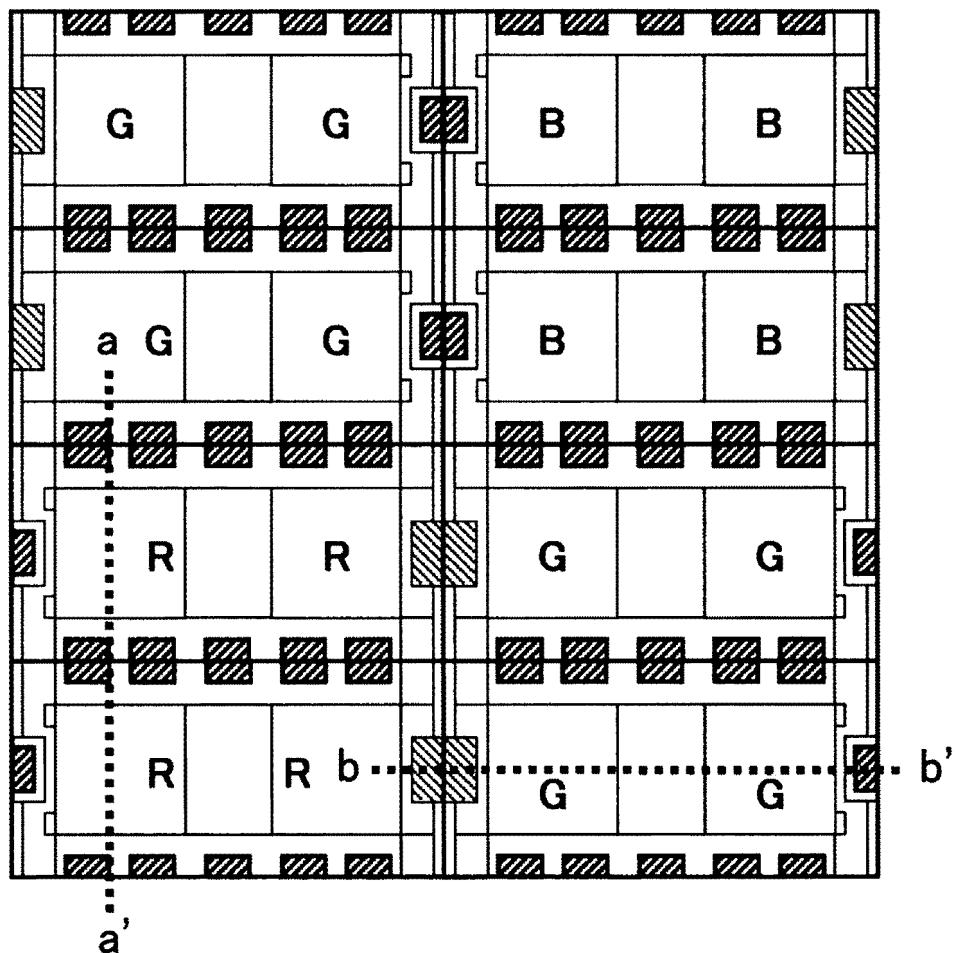

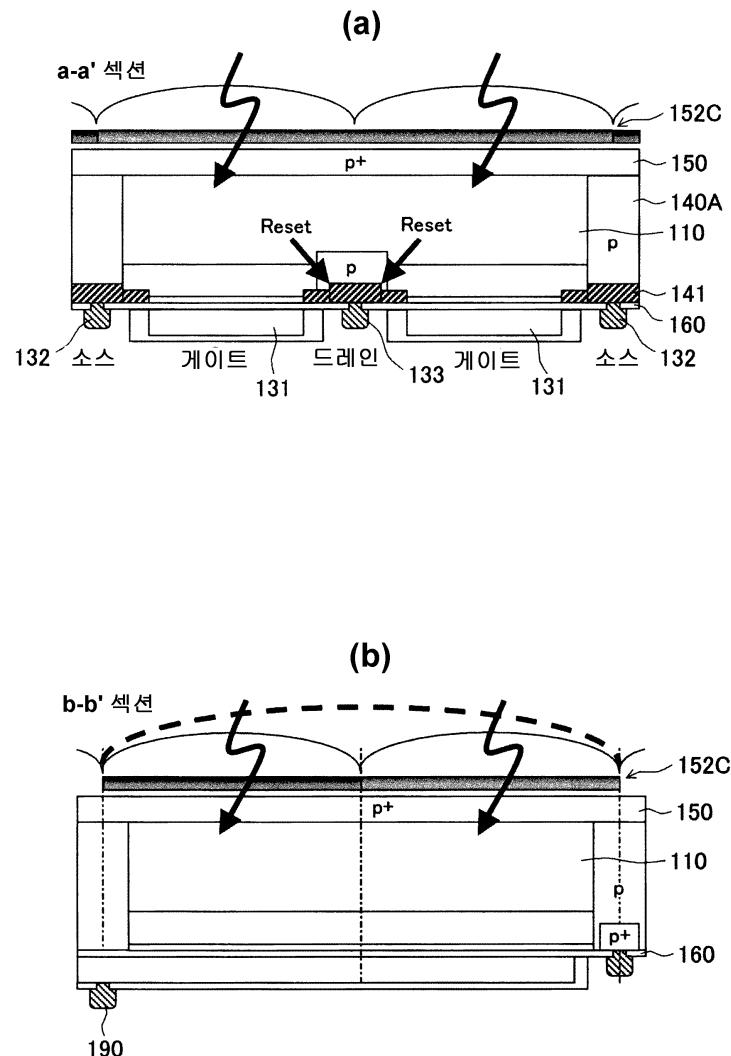

- [0153] 도 9는, 본 실시예에 따른 화소부에 있어서의 화소 셀의 레이아웃의 일례를 나타낸 도면이다. 또한, 도 10a은 도 9의 a-a'선에 있어서의 간략 단면도, 도 1b는 도 9의 b-b'선에 있어서의 간략 단면도이다.

- [0154] 이 예에서는, 화소 셀 Cel가 매트릭스형으로 배열되어 있다. 또한, 베이어 배열을 채용하고 있다.

- [0155] 그리고 p형 소자 분리층(도전 층)(140A)이 제1 웰(110) 및 제2 웰(120)의 측벽에 형성되고, 이 p형 소자 분리층(140A) 내에 트랜지스터(130)를 형성하는 n<sup>+</sup> 층으로 이루어지는 소스 영역(141), 드레인 영역(142)이 형성되고, 웰 컨택트 영역(143)이 소스 영역(141) 측 또는 드레인 영역(142) 측에 형성된다. 이 예에서는, 소스 영역 측에 형성되어 있다.

- [0156] 그리고 p형 소자 분리층(140A)에 대향하는 위치에 게이트 컨택트 전극(190)이 형성되어 있다.

- [0157] 또한, 소자 분리층(140A)을 제외한 화소 셀 Cel의 게이트 전극(131)의 앞면측(광이 조사되지 않은 측)에 리플렉터(200)가 형성되어 있다.

- [0158] 이와 같이, 인접 화소 셀과 드레인 또는 소스 또는 기판(웰) 또는 게이트의 컨택트를, 일부 또는 복수 공유함으로써 레이아웃 효율을 높일 수 있다.

- [0159] 환연하면, 1트랜지스터로 구성할 수 있는 것은, 드레인, 소스, 게이트, 웰의 컨택트가 소자 분리 위의 사방으로 배치되고, 게이트가 화소 전체를 차지하는 구조로 되어, 트랜지스터의 랜덤 노이즈가 비약적으로 저감한다.

- [0160] 도 9의 레이아웃 예에 있어서는, 드레인 컨택트 DCNT 및 소스 컨택트 SCNT는, 도면 중에 나타내는 X, Y 방향(세로 방향, 행방향) 중, Y 방향으로 인접하는 화소 셀끼리로 공유되고, 게이트 컨택트 GCNT 및 웰 컨택트 WCNT는 X 방향(가로 방향, 열방향)에 인접하는 화소 셀로 공유된다.

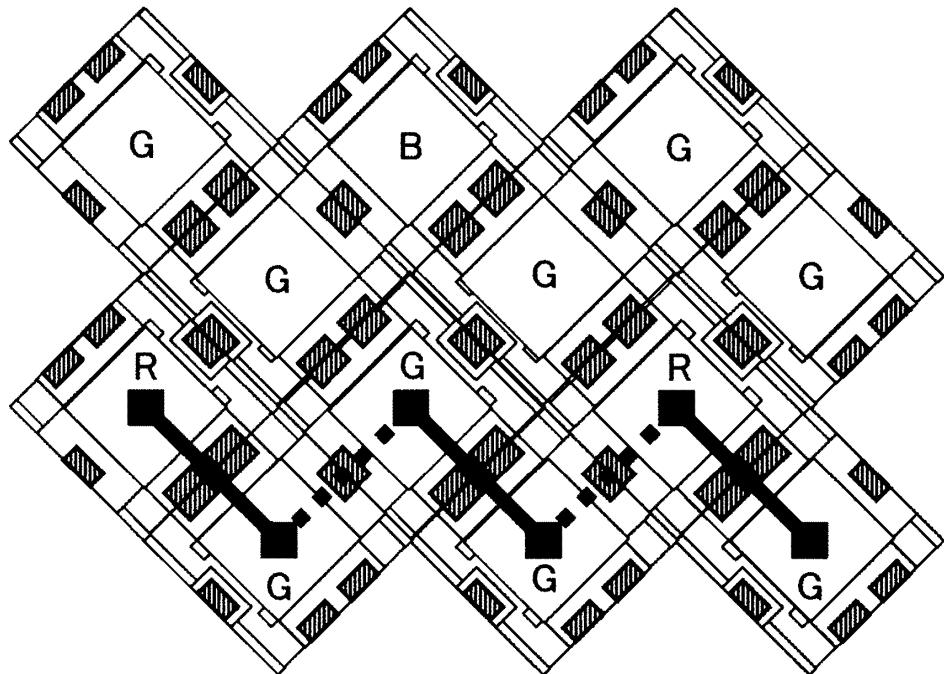

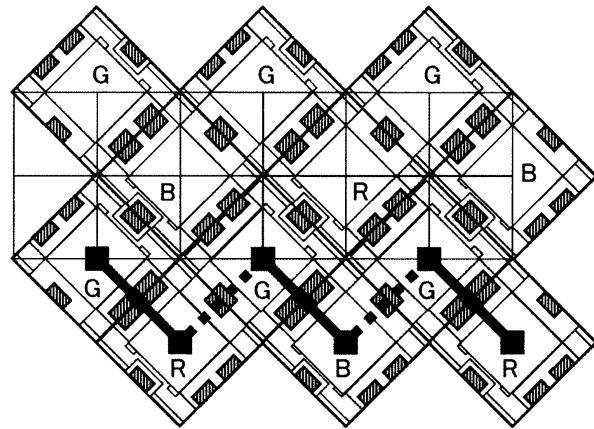

- [0161] 이와 같이, 드레인 컨택트 DCNT, 소스 컨택트 SCNT, 게이트 컨택트 GCNT, 및 웰(기판) 컨택트 WCNT가, 게이트의 4방향으로 배치하는 것이 가능하므로, 도 11에 나타낸 바와 같이, 이른바 지그재그(ZigZag) 배열에서도 겸용할 수 있는 레이아웃으로 되어 있다.

- [0162] 도 11의 예는, 도 9의 배치를 45도 회전시켜 배열하고 구조로 되어 있다.

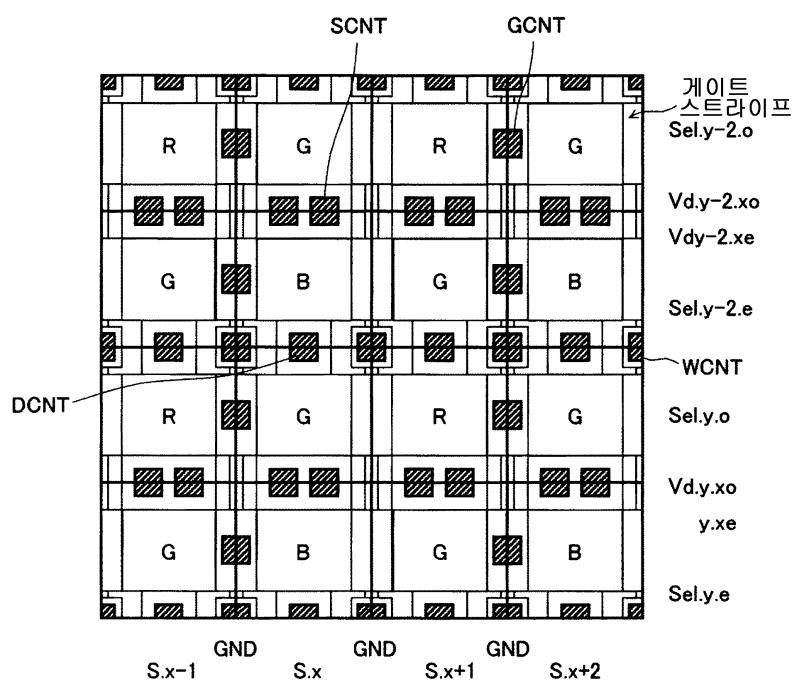

- [0163] 도 12는, 게이트를 X 방향(가로 방향) 스트라이프에서 공통으로 한 레이아웃 예를 나타낸 도면이다.

- [0164] 도면에 나타낸 바와 같이, 게이트를 옆스트라이프에서 공통으로 하고, 소스측 또는 드레인 측에 웰(기판) 컨택트 WCNT를 취하는 레이아웃으로서 리플렉터(200)를 만들기 쉽게 할 수 있다.

- [0165] 이 경우, 웰(기판) 컨택트 WCNT는, X(수평) 방향으로 매 다른 간격으로 해도 상관없다.

- [0166] 또한, 웰(기판) 컨택트 WCNT를 드레인 측으로 할지 소스 측으로 할지는, 내압이나 레이아웃에 의해 결정하면 된다.

- [0167] 웰(기판) 컨택트 WCNT가 소스 측으로 하면, 전위차가 줄어들기 때문에 미세화가 쉬워지는 이점이 있다.

- [0168] 도 13은, 드레인 측을 편치로 한 레이아웃예를 나타낸 도면이다.

- [0169] 웰(기판) 컨택트 WCNT를 드레인 측으로 하는 경우는, 내압 확보를 위해 드레인 폭을 줄여 이른바 편치로 한다.

- [0170] 이로써, 소스 측의 채널이 넓어지고, 소스측이 깊어지고, 신호가 모이는 부분과 변조가 걸리기 쉬운 부분이 서로 일치하기 때문에, 고변조 특성을 얻을 수 있다.

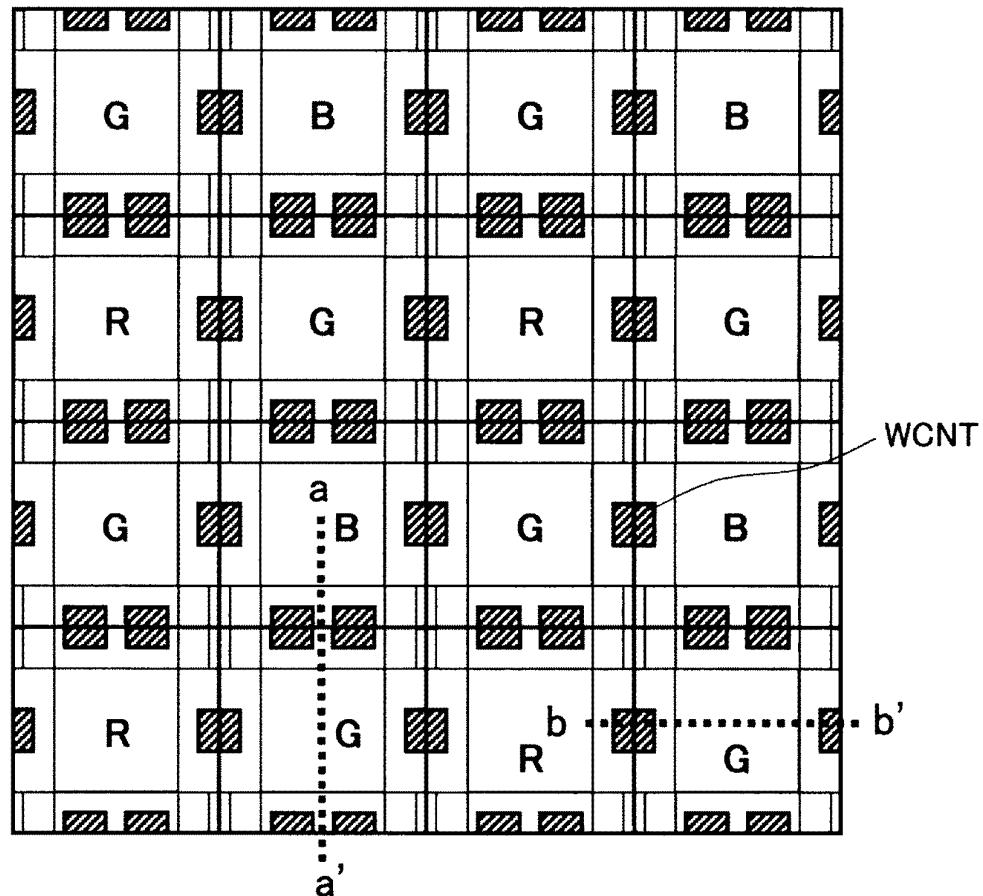

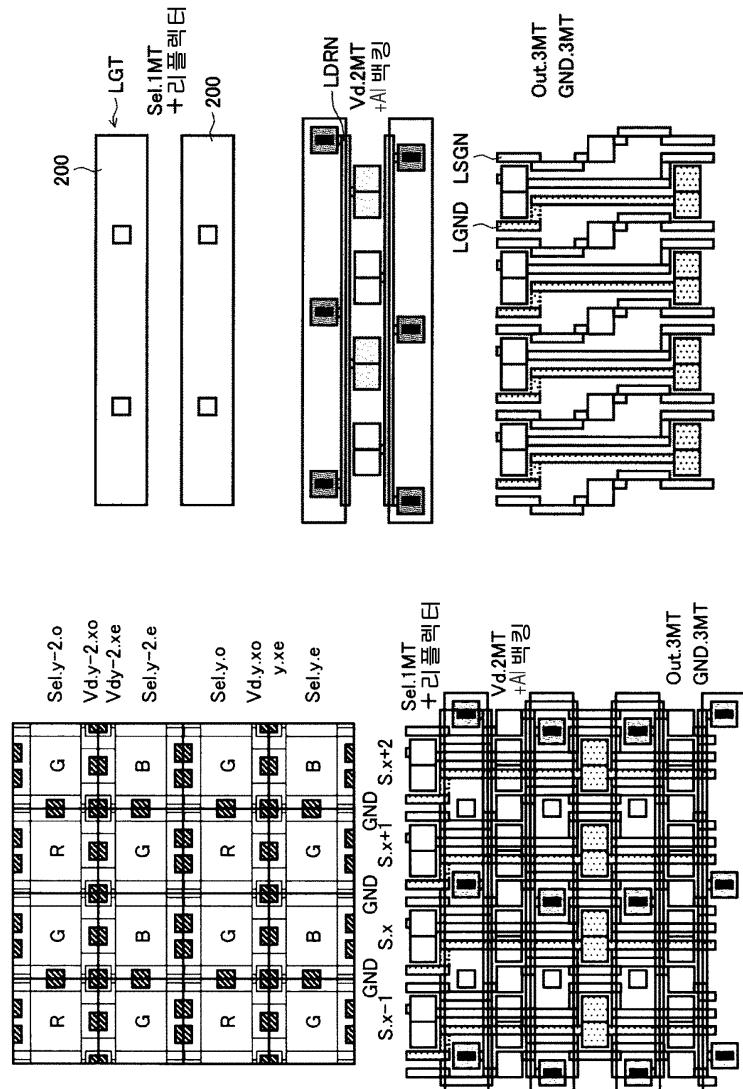

- [0171] 도 14는, 본 실시예에 따른 화소부에 있어서의 화소 셀의 레이아웃의 다른 예를 나타낸 도면이다. 또한, 도 15a는 도 14의 a-a'선에 있어서의 간략 단면도, 도 15b는 도 14의 b-b'선에 있어서의 간략 단면도이다.

- [0172] 도 14의 레이아웃은 도 9의 예와 같지만, 이 예에서는, 웰(기판) 컨택트(WCNT)가 기판(100)의 제2 기판면(102) 측에는 없고, 제1 기판면(101)(배면) 측에 형성되어 있다. 게이트 전극(131)은, 제2 기판면(102) 측의 p형 소자 분리층(140A)을 포함하는 화소 셀 전체에 걸쳐 형성되어 있다.

- [0173] 이 경우, 도시하지 않은 색혼합 방지용 차광막과 배선을 겸용할 수 있다.

- [0174] 이와 같은 구성을 채용함으로써, 리플렉터(200)의 배선이 대칭형으로 되어, 내압의 면에서 유리하다.

- [0175] 여기서, 리플렉터(200)에 대하여 보다 상세하게 설명한다.

- [0176] 배면 조사로, 더블 웰 구조를 채용하는 본 실시예에 따른 화소 셀 Cel은, 트랜지스터(130)의 게이트 전극(131) 상에 스페이스가 생기므로, 배선의 메탈 등을 이용한 리플렉터 구조를 형성할 수 있다.

- [0177] 이 리플렉터(200)에 의해 실리콘 기판(100)을 투과한 광을 반사시켜 재차 실리콘 기판(100)의 제1 웰(110)에서 광전 변환시키고, 예를 들면, 근적외 감도를 향상시킬 수 있다.

- [0178] 이 경우, 도 16a에 나타낸 바와 같이, 기판은 비교적 두껍고( $6\text{ }\mu\text{m} \sim 10\text{ }\mu\text{m}$  정도), 리플렉터(200)에 의한 근적외 광의 반사 이용에 의해, 예를 들면, 암시 감시 카메라로의 응용이 가능해진다.

- [0179] 또한, 도 16b에 나타낸 바와 같이, 적극적으로 기판(100)의 두께를 얇게 하고 G~R 광을 반사하는 두께로 하면, 반 정도의 기판 두께로 해결되기 때문에, 화소 사이즈를 또한 반으로 줄이는 것이 가능해지고, 색혼합을 방지하는 것이 가능해진다.

- [0180] 통상 가시광에는 실리콘 기판은  $2\text{ }\mu\text{m} \sim 3\text{ }\mu\text{m}$ 의 두께가 필요하며, 광 입사각은 25도 정도까지 수광하지 않으면 안 되므로, 어스펙트비(aspect ratio)로 1:2 정도가 한계였기 때문에  $1\text{ }\mu\text{m} \sim 1.5\text{ }\mu\text{m}$  정도가 화소 사이즈의 한계라고 말해지고 있었다.

- [0181] 그러나 본 실시예와 같이, 리플렉터(200)를 이용하면 절반의 실리콘 기판 두께  $1\text{ }\mu\text{m} \sim 1.5\text{ }\mu\text{m}$ 로 충분하기 때문에, 화소 사이즈도 서브 미크론 화소가 가능해진다.

- [0182] 또한, 이 경우, 전극에 가시광 투과율이 높은 ITO막을 사용하는 것이 바람직하다.

- [0183] 본 실시예에 있어서는, 리플렉터(200)가 메탈계의 배선(A1 등)으로 된다. 이 구성예에 대하여는 다음에, 설명한다.

- [0184] 그리고 구체적인 설명은 행하지 않지만, 리플렉터가 비도전성의 절연막 등으로 구성될 수도 있다.

- [0185] 다음에, 컬럼 회로를 공유하여 다운사이징을 도모할 수 있는 구성을 대하여 설명한다.

- [0186] 이 경우, 화소부(2)에 있어서의 화소 셀의 매트릭스형 배열에 있어서, 열 중 드레인 컨택트를 2개 이상의 그룹으로 나누는 것으로 열방향(X 방향) 제어 회로(4)에 있어서의 컬럼 회로를 공유하여 다운사이징을 도모한다.

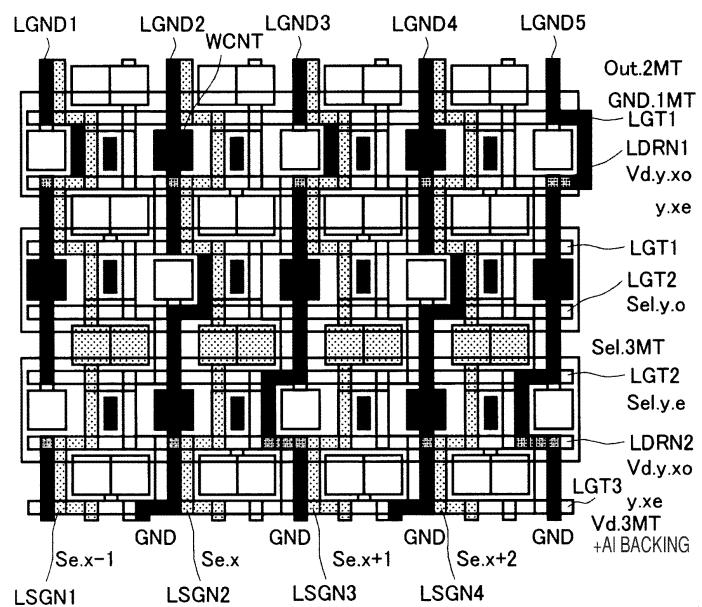

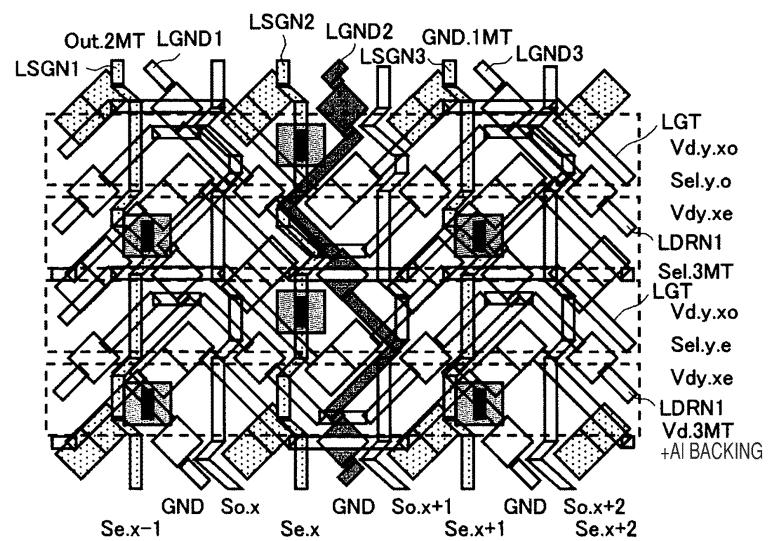

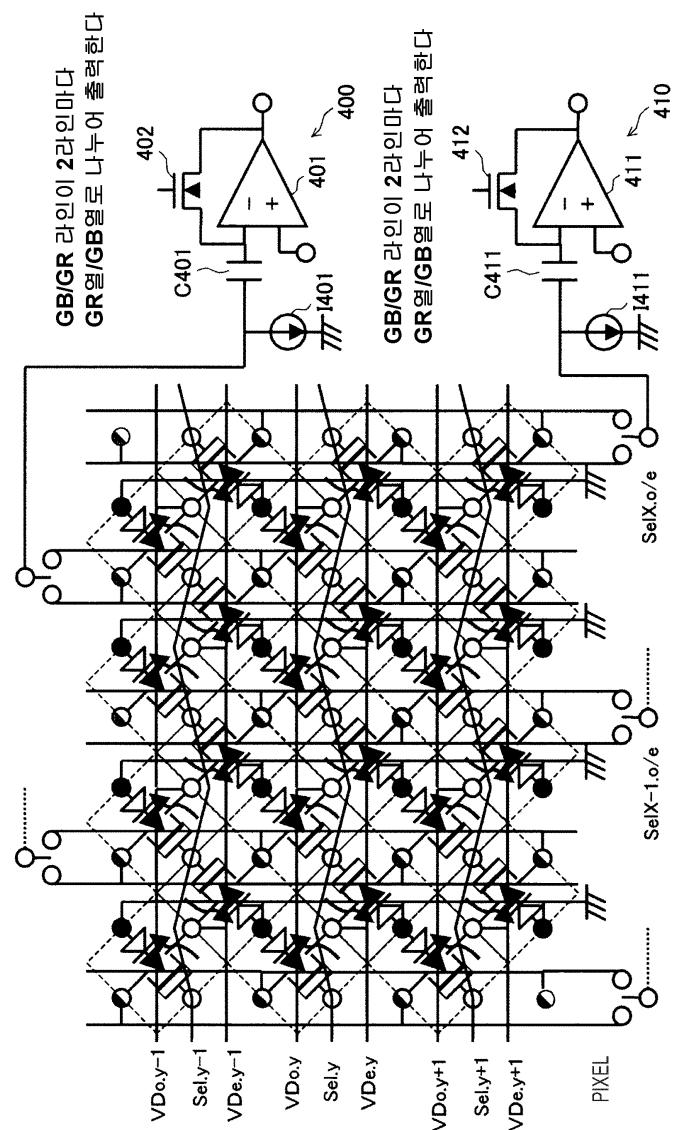

- [0187] 도 17a 및 도 17b는, 컨택트 공유형 화소부의 화소 셀 배열예를 나타낸 도면이며, 도 17a은 화소 셀의 레이아웃의 예를 나타낸 도면이며, 도 17b는 도 17a에 대응하는 패턴 레이아웃을 나타낸 도면이다.

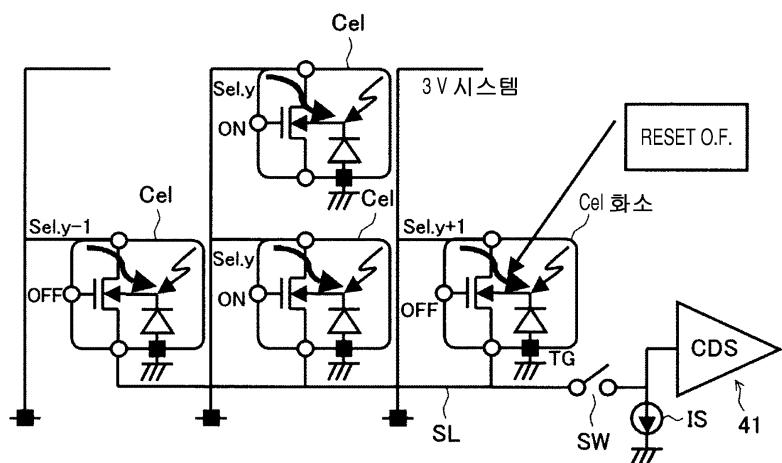

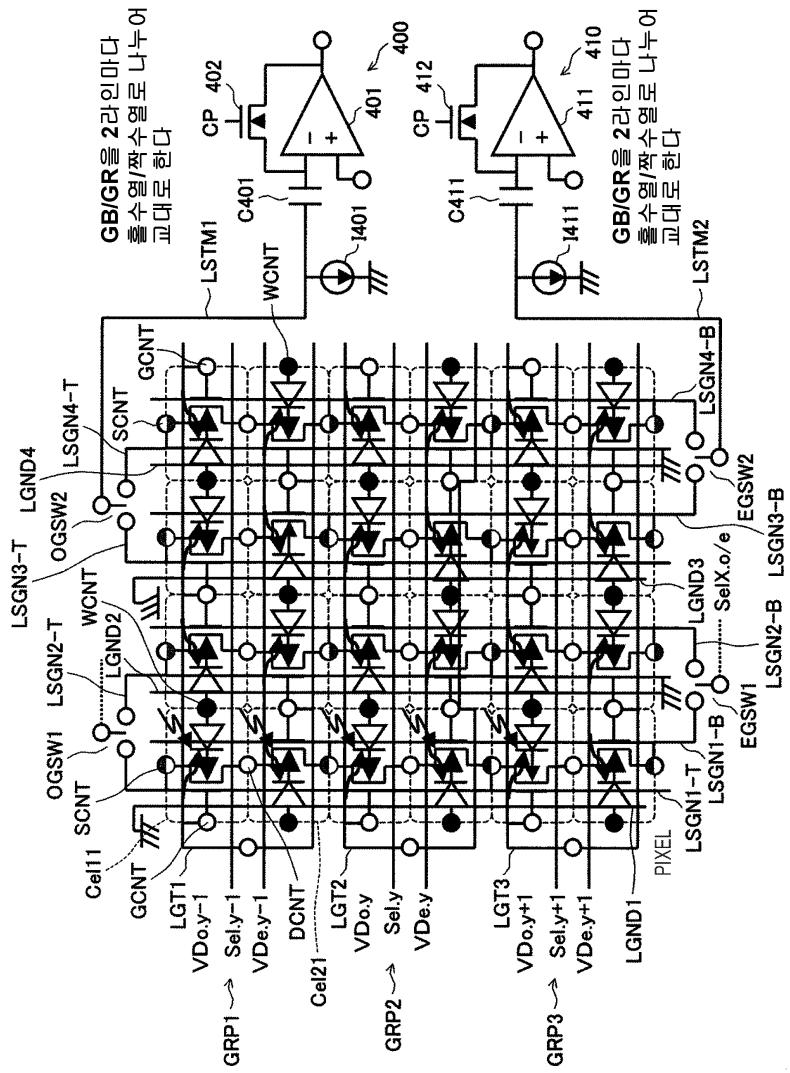

- [0188] 또한, 도 18은 도 17a의 레이아웃을 채용하여 컬럼 회로를 공유하는 신호 처리계와 화소부를 간략화한 등가 회로를 나타낸 도면이다.

- [0189] 그리고 이하에서는, 선택된 트랜지스터의 게이트에는 신호 Sel이 공급되는 것으로 한다.

- [0190] 이 예에서는, 수직 2라인에서 드레인을 공유하고 있다.

- [0191] 도 17a의 예에서는, 선택하여 도시한 16개의 셀 Ce1이 매트릭스형으로 배열되어 있다.

- [0192] 기본적으로 베이어 배열(Bayer array)이 채용되고 있고, 1행1열째에 G(녹, Gr)의 화소 셀 Ce111이 배열되고, 1행2열면에 B(청)의 화소 셀 Ce112가 배열, 2행1열째에 R(적)의 화소 셀 Ce121이 배열되고, 2행2열째에 G(Gb)의 화소 셀 Ce122가 배열되어 있다.

- [0193] 마찬가지로, 1행3열째에 G(Gr)의 화소 셀 Ce113이 배치되고, 1행4열면에 B의 화소 셀 Ce114가 배열, 2행3열째에 R의 화소 셀 Ce123이 배열되고, 2행2열째에 G(Gb)의 화소 셀 Ce124가 배열되어 있다.

- [0194] 3행1열째에 G의 화소 셀 Ce131이 배치되고, 3행2열면에 B의 화소 셀 Ce132가 배열, 4행1열째에 R의 화소 셀 Ce141이 배열되고, 4행2열째에 G(Gb)의 화소 셀 Ce142가 배열되어 있다.

- [0195] 마찬가지로, 3행3열째에 G(Gr)의 화소 셀 Ce133이 배치되고, 3행4열면에 B의 화소 셀 Ce134가 배열되고, 4행3열째에 R의 화소 셀 Ce143이 배열되고, 4행4열째에 G(Gb)의 화소 셀 Ce144가 배열되어 있다.

- [0196] 그리고 화소 셀 배열의 각 열에 있어서, 인접하는 홀수행과 짝수행의 화소 셀끼리가 드레인 컨택트를 공유하고 있다.

- [0197] 도 17a의 예에서는, 화소 셀 Ce111과 Ce121이 드레인 컨택트 DCNT를 공유하고, 화소 셀 Ce131과 Ce141이 드레인 컨택트 DCNT를 공유하고 있다.

- [0198] 마찬가지로, 화소 셀 Ce112와 Ce122가 드레인 컨택트 DCNT를 공유하고, 화소 셀 Ce132와 Ce142가 드레인 컨택트 DCNT를 공유하고 있다.

- [0199] 화소 셀 Ce113과 Ce123이 드레인 컨택트 DCNT를 공유하고, 화소 셀 Ce133과 Ce143이 드레인 컨택트 DCNT를 공유하고 있다.

- [0200] 화소 셀 Ce114와 Ce124가 드레인 컨택트 DCNT를 공유하고, 화소 셀 Ce134와 Ce144가 드레인 컨택트 DCNT를 공유하고 있다.

- [0201] 도 17a의 예에서는, 드레인 컨택트 DCNT를 공유하는 1행째의 화소 셀 Ce111 ~ Ce114 및 2행째의 화소 셀 Ce121 ~ Ce124에 의해 그룹 GRP1이 형성되어 있다.

- [0202] 마찬가지로, 드레인 컨택트 DCNT를 공유하는 3행째의 화소 셀 Ce131 ~ Ce134 및 4행째의 화소 셀 Ce141 ~ Ce144에 의해 그룹 GRP2가 형성되어 있다.

- [0203] 그리고 인접하는 그룹 사이의 각 열에 있어서 인접하는 화소 셀끼리로 소스 컨택트 SCNT를 공유하고 있다.

- [0204] 도 17a의 예에서는, 그룹 GRP1의 화소 셀 Ce121과 그룹 GRP2의 화소 셀 Ce131이 소스 컨택트 SCNT를 공유하고 있다.

- [0205] 그룹 GRP1의 화소 셀 Ce122와 그룹 GRP2의 화소 셀 Ce132가 소스 컨택트 SCNT를 공유하고 있다.

- [0206] 그룹 GRP1의 화소 셀 Ce123과 그룹 GRP2의 화소 셀 Ce133이 소스 컨택트 SCNT를 공유하고 있다.

- [0207] 그룹 GRP1의 화소 셀 Ce124와 그룹 GRP2의 화소 셀 Ce134가 소스 컨택트 SCNT를 공유하고 있다.

- [0208] 또한, 도 17b에 있어서, 참조 신호 LGND1~LGND5 등은 웨尔 컨택트 WCNT에 접속되는 그라운드 라인을, LSGN1~LSGN4 등은 소스 컨택트 SCNT에 접속되는 신호 라인을, LGT1~LGT3 등은 게이트 컨택트에 접속되는 게이트 라인을, LDRN1~LDRN4 등은 드레인 컨택트에 접속되는 드레인 라인을 각각 나타내고 있다.

- [0209] 그라운드 라인 LGND 및 신호 라인 LSGN은 Y 방향(행방향)에 열마다 배선되어 있다.

- [0210] 또한, 게이트 라인 LGT와 드레인 라인 LDRN은 X 방향(열방향)에 행마다 배선되어 있다.

- [0211] 이 그라운드 라인 LGND, 신호 라인 LSGN, 게이트 라인 LGT, 및 드레인 라인 LDRN은 배선의 적층 구조에 의해 형성된다.

- [0212] 예를 들면, 그라운드 라인 LGND는 최하층의 제1 메탈 배선(1MT)에 의해 형성된다.

- [0213] 신호 라인 LSGN은 2번째에 하층의 제2 메탈 배선(2MT)에 의해 형성된다.

- [0214] 게이트 라인 LGT, 및 드레인 라인 LDRN은 양자 사이에 절연막을 통하여 절연성을 지지하여 최상층의 제3 메탈 배선(3MT)에 의해 형성된다.

- [0215] 실시예에 있어서는, 제3 메탈 배선에 의해 형성되는 드레인 라인 LDRN은 IR드롭에 대한 대책으로서 저저항화를 위하여, 예를 들면, Al배선 Lal에 의해 보장받고 있다.

- [0216] 본 실시예에 있어서는, 도 17a 및 도 17b 및 도 18에 나타낸 바와 같이, 각 그룹 GRP1~GRP3에서, 드레인 컨택트를 공유하는 화소 셀에 있어서는, 게이트 컨택트 GCNT와 웨(기판) 컨택트 WCNT가 X 방향(열방향)에 있어서 역방향으로 되도록 형성되어 있다.

- [0217] 홀수열과 짝수열에서, 게이트 컨택트 GCNT와 웨(기판) 컨택트 WCNT는 그 방향이 또한 역으로 되도록 형성되어 있다.

- [0218] 구체적으로는, 그룹 GRP1에 있어서, 1열째의 화소 셀 Cel11의 게이트 컨택트 GCNT는 X 방향의 도면 중 좌측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 우측에 형성되어 있다.

- [0219] 1열째의 화소 셀 Cel21에 게이트 컨택트 GCNT는 X 방향의 도면 중 우측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 좌측에 형성되어 있다.

- [0220] 화소 셀 Cel11의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 2열째에 배선된 그라운드 라인 LGND2에 접속되어 있다.

- [0221] 화소 셀 Cel21의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 1열째에 배선된 그라운드 라인 LGND1에 접속되어 있다.

- [0222] 2열째의 화소 셀 Cel12의 게이트 컨택트 GCNT는 X 방향의 도면 중 우측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 좌측에 형성되어 있다.

- [0223] 2열째의 화소 셀 Cel22에 게이트 컨택트 GCNT는 X 방향의 도면 중 좌측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 우측에 형성되어 있다.

- [0224] 화소 셀 Cel12의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 2열째에 배선된 그라운드 라인 LGND2에 접속되어 있다.

- [0225] 화소 셀 Cel22의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 3열째에 배선된 그라운드 라인 LGND3에 접속되어 있다.

- [0226] 3열째의 화소 셀 Cel13의 게이트 컨택트 GCNT는 X 방향의 도면 중 좌측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 우측에 형성되어 있다.

- [0227] 1열째의 화소 셀 Cel23에 게이트 컨택트 GCNT는 X 방향의 도면 중 우측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 좌측에 형성되어 있다.

- [0228] 화소 셀 Cel13의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 4열째에 배선된 그라운드 라인 LGND4에 접속되어 있다.

- [0229] 화소 셀 Cel23의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 3열째에 배선된 그라운드 라인 LGND3에 접속되어 있다.

- [0230] 4열째의 화소 셀 Cel14의 게이트 컨택트 GCNT는 X 방향의 도면 중 우측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 좌측에 형성되어 있다.

- [0231] 2열째의 화소 셀 Cel24에 게이트 컨택트 GCNT는 X 방향의 도면 중 좌측에 형성되고, 웨 컨택트 WCNT는 X 방향의 도면 중 우측에 형성되어 있다.

- [0232] 화소 셀 Cel14의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 4열째에 배선된 그라운드 라인 LGND4에 접속되어 있다.

- [0233] 화소 셀 Cel24의 트랜지스터(130)의 게이트가 게이트 컨택트 GCNT를 통하여 게이트 라인 LGT1에 접속되고, 웨 컨택트 WCNT가 5열째에 배선된 그라운드 라인 LGND5(도시하지 않음)에 접속되어 있다.

- [0234] 그룹 GRP2, GRP3도 기본적으로 같은 패턴을 가지고 형성되어 있다. 따라서, 그 상세한 설명은 생략한다.

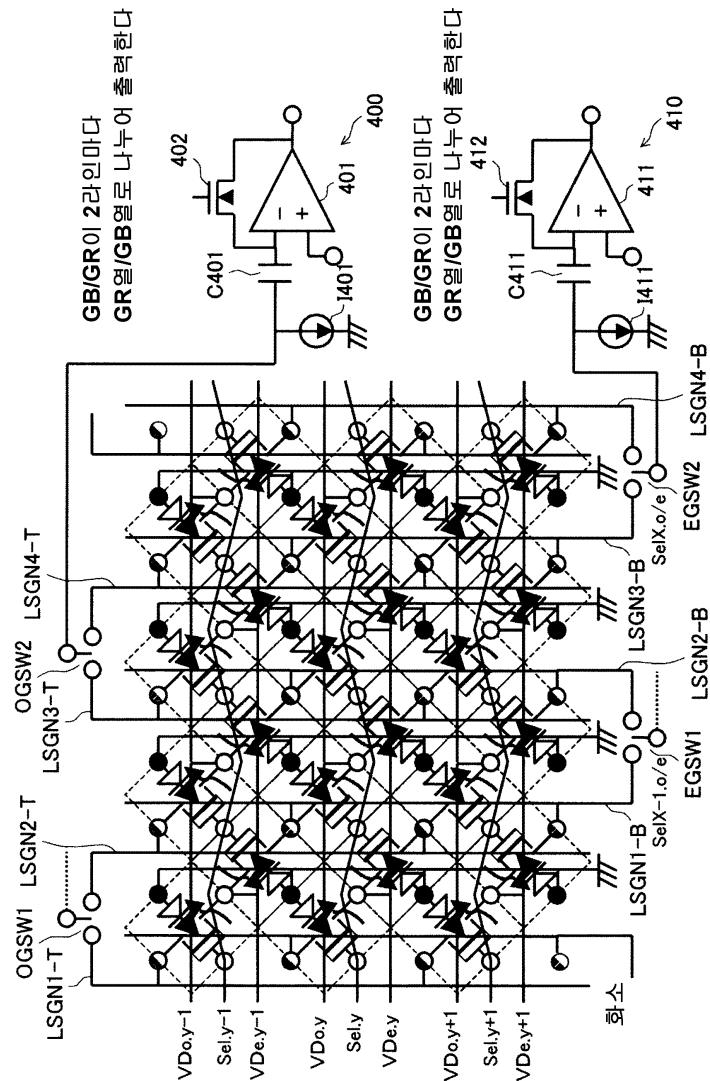

- [0235] 도 18에 나타낸 바와 같이, 신호 라인 LSGN1~LSGN4 등은, 탑 판독(top readout)과 보텀 판독(bottom readout)을 위해 2개의 신호 라인 LSGN1-T 및 LSGN1-B, LSGN2-T 및 LSGN2-B, LSGN3-T 및 LSGN3-B, LSGN4-T 및

LSGN4-B 등으로 분할된다.

[0236] 그리고 2열 단위로 홀수 셀렉트 스위치(탑 스위치) OGSW1과 짹수 그룹 셀렉트 스위치(보텀 스위치) EGSW1, 탑 스위치 OGW2와 보텀 스위치 EGSW2가 설치되어 있다.

[0237] 탑 스위치 OGSW1의 2개의 전환 단자에 신호 라인 LSGN1-T, LSGN2-T가 접속되고, 보텀 스위치 EGSW1의 2개의 전환 단자에 신호 라인 LSGN1-B, LSGN2-B가 접속되어 있다. 신호 라인 LSGN1-T, LSGN2-T는 홀수 그룹 GRP1, GRP3 등의 소스 컨택트 SCNT에 접속되고, 신호 라인 LSGN1-B, LSGN2-B는 짹수 그룹 GRP2, GRP4 등의 소스 컨택트 SCNT에 접속된다.

[0238] 마찬가지로, 탑 스위치 OGSW2의 2개의 전환 단자에 신호 라인 LSGN3-T, LSGN4-T가 접속되고, 보텀 스위치 EGSW2의 2개의 전환 단자에 신호 라인 LSGN3-B, LSGN4-B가 접속되어 있다. 신호 라인 LSGN3-T, LSGN4-T는 홀수 그룹 GRP1, GRP3 등의 소스 컨택트 SCNT에 접속되고, 신호 라인 LSGN3-B, LSGN4-B는 짹수 그룹 GRP2, GRP4 등의 소스 컨택트 SCNT에 접속된다.

[0239] 그리고 각 탑 스위치 OGSW1, OGSW2 등의 고정 단자가 제1 신호 전송 라인 LSTM1에 접속되고, 보텀 스위치 EGSW1, EGSW2의 고정 단자가 제2 신호 전송 라인 LSTM2에 접속되어 있다.

[0240] 제1 신호 전송 라인 LSTM1에는 전류원 I401이 접속되고, 그 접속점은 커패시터 C401을 통하여 컬럼 회로(400)의 비교기(401)에 접속되어 있다.

[0241] 비교기(401)는, 반전 입력(−)이 커패시터 C401에 접속되고, 비반전 입력(+)에는 참조 전위가 부여된다.

[0242] 비교기(401)의 반전 입력(−)과 출력의 사이에는 리셋용 스위치(402)가 접속되어 있다. 스위치(402)는, 예를 들면, MOS 트랜지스터에 의해 형성된다.

[0243] 제2 신호 전송 라인 LSTM2에는 전류원 I411이 접속되고, 그 접속점은 커패시터 C411을 통하여 컬럼 회로(410)의 비교기(411)에 접속되어 있다.

[0244] 비교기(411)는, 반전 입력(−)이 커패시터 C411에 접속되고, 비반전 입력(+)에는 참조 전위가 부여된다.

[0245] 비교기(411)의 반전 입력(−)과 출력의 사이에는 리셋용 스위치(412)가 접속되어 있다. 스위치(412)는, 예를 들면, MOS 트랜지스터에 의해 형성된다.

[0246] 이와 같은 구성에 있어서는, 리셋을 홀수와 짹수로 나누어 홀수의 D 상(phase) Do, 홀수의 P 상 Po, 짹수의 D 상 De, 짹수의 P 상 Pe의 차례로 샘플링하는 것이 가능하며, 세로 및 가로 모두 디지털 가산(세로는 카운터 가산)으로, 같은 색 화소로부터의 신호의 임의의 가산 처리가 가능하다.

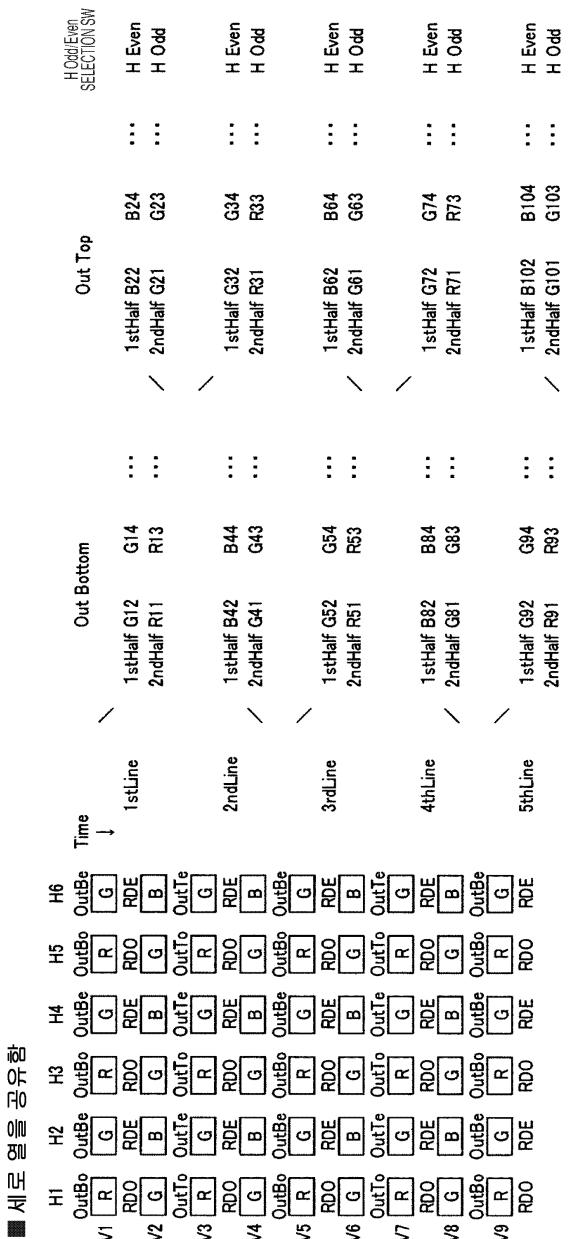

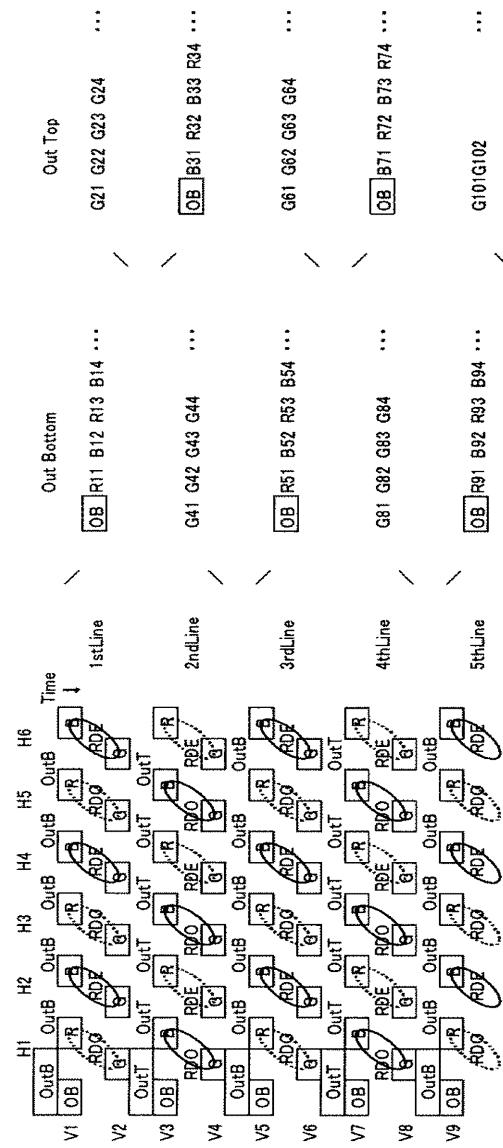

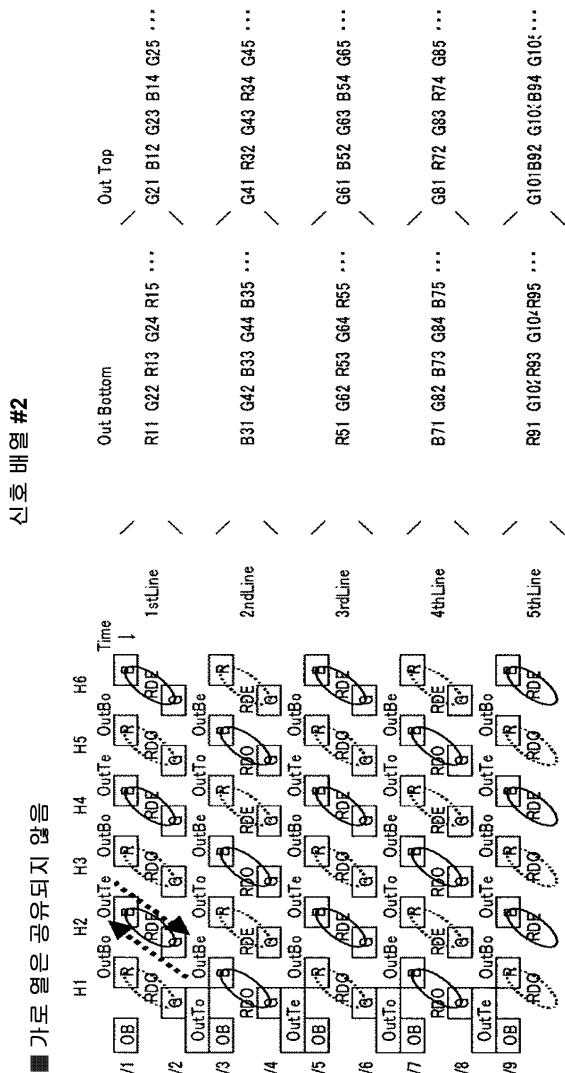

[0247] 도 19a 및 도 19b는, 도 17a 및 도 17b와 같은 정방 배열시의 신호 출력 순서를 나타낸 도면이다. 도 19a는 수평 컬럼 공유 없음의 경우를 나타내고, 도 19b는 수평 컬럼 공유의 경우에 신호를 출력하기 위한 신호 출력 순서를 나타내고 있다.

[0248] 도 19a 및 도 19b에 있어서는, 신호 출력 순서로 화소 셀을 배열하기 위하여, 레이아웃 도면에 도시된 화소의 배치와는 상하 반전시키고 있다.

[0249] 이 예는, V행 H열로서 그 각 행, 각 열에 번호를 부여하고, 출력 신호는 화소 셀의 RGB의 구별과 행렬 배열에 따른 번호를 부여하고 있다. 예를 들면 1행1열째의 신호는 R11, 1행2열째는 G12로 되어 있다.

[0250] 도 19a의 예의 경우에는, 보텀측도 탑측도 화소 셀 배열에 따라 차례대로 신호가 출력된다.

[0251] 도 19b의 예의 경우에는, 시분할적으로 출력되어 간다.

[0252] 예를 들면, 보텀 측에서 최초에 화소 셀 G12, G14 등의 신호를 판독하고, 탑 측에서 화소 셀 B22, B24를 판독하고, 보텀 측에서 2번째에 화소 셀 R11, R13 등의 신호를 판독하고, 탑 측에서 화소 셀 G21, G23을 판독한다.

[0253] 이와 같이, 같은 색마다 신호 판독을 행하는 것이 가능하며, 임의의 같은 색 가산이 가능해진다.

[0254] 이상 설명한 바와 같이, 도 17a 및 도 17b 및 도 18에 나타낸 예에서는, 2라인마다 Gb, Gr을 교대로 판독하고, 홀수 컬럼과 짹수 컬럼으로 나누어 판독한다.

[0255] 본 예에서는, 2라인으로 드레인 공유를 하기 때문에, 상하 컬럼 배열에 의한 패러렐 처리(2배속)가 필요해진다. 또한, 2라인마다 교대로 Gr/Gb라인이 상하로부터 출력되므로 디지털 가산 또는 2/4 속아내기(thinning-out)가

수행된다.

[0256] 수평 리셋 드레인의 분리(예를 들면, 홀수열과 짝수열)에 의해, 수평 2 이상의 컬럼 공유가 가능해진다( $1/n$  감속).

[0257] 또한, 컬럼 축소(column shrinking)가 가능하다.

[0258] 또한, 색코딩 동기로, 동일 열신호 내에서 디지털 가산에 의한 임의의 같은 색 가산이 가능해진다.

[0259] 또한, 드레인 라인 LDRN의 열배선은 저저항화이기 때문에 A1에 의해 보장받으므로, 드레인 라인에 전송되는 신호 전압의 저하를 방지할 수 있다.

[0260] 도 20a 및 도 20b는, 도 17과 같은 정방 배열을 45도 회전시킨 지그재그(ZigZag) 배열을 나타낸 도면이며, 도 20a는 화소 셀의 레이아웃의 예를 나타낸 도면이며, 도 20b는 도 20a에 대응하는 패턴 레이아웃을 나타낸 도면이다.

[0261] 또한, 도 21은, 도 20a의 레이아웃을 채용하여 컬럼 회로를 공유하는 신호 처리계와 화소부를 간략화한 등가 회로를 나타낸 도면이다.

[0262] 지그재그(ZigZag) 배열은, 전극 이하의 구조는, 단순하게 45도 회전하고, 배선을 지그재그 배열용으로 연구함으로써, 실현 가능하다.

[0263] 이 경우도 기본적인 동작은 도 17a 및 도 17b 및 도 18의 정방 배열의 경우와 마찬가지이며, 리셋을 홀수와 짝수로 나누어 홀수의 D 상 Do, 홀수의 P 상 Po, 짝수의 D 상 De, 짝수의 P 상 Pe의 차례로 샘플링하는 것이 가능하며, 세로 및 가로 모두 디지털 가산(세로는 카운터 가산)으로, 같은 색 화소로부터의 신호의 임의의 가산 처리가 가능하다.

[0264] 도 22a 및 도 22b는, 도 17a 및 도 17b와 같은 정방 배열을 45도 회전시킨 다른 지그재그(ZigZag) 배열을 나타낸 도면이며, 도 22a는 화소 셀의 레이아웃의 예를 나타낸 도면이며, 도 22b는 도 22a에 대응하는 패턴 레이아웃을 나타낸 도면이다.

[0265] 또한, 도 23은, 도 22a의 레이아웃을 채용하여 컬럼 회로를 공유하는 신호 처리계와 화소부를 간략화한 등가 회로를 나타낸 도면이다.

[0266] 도 20a 및 도 20b 및 도 21의 예는, 신호 판독의 형태도 도 17a 및 도 17b 및 도 18의 경우와 마찬가지의 형태였지만, 도 22a 및 도 22b 및 도 23의 예에서는 보텀으로 하는 열과 탑으로 하는 열을 교대로 하는 형태를 취하고 있다.

[0267] 이 경우도 기본적인 동작은 도 17a 및 도 17b 및 도 18의 정방 배열의 경우와 마찬가지이며, 리셋을 홀수와 짝수로 나누어 홀수의 D 상 Do, 홀수의 P 상 Po, 짝수의 D 상 De, 짝수의 P 상 Pe의 차례로 샘플링하는 것이 가능하며, 세로 및 가로 모두 디지털 가산(세로는 카운터 가산)으로, 같은 색 화소로부터의 신호의 임의의 가산 처리가 가능하다.

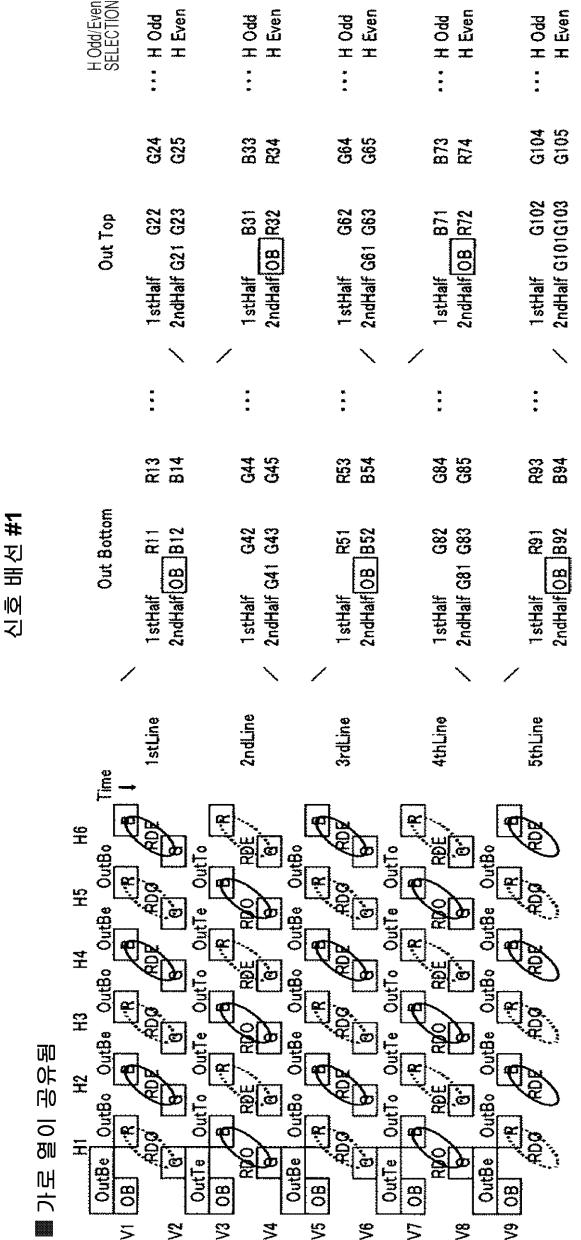

[0268] 도 24a 및 도 24b는, 도 20a 및 도 20b와 같은 지그재그 배열시의 신호 출력 순서를 나타낸 도면이며, 도 24a는 수평 컬럼 공유 없음의 경우를 나타내고, 도 24b는 수평 컬럼을 공유할 때 신호를 출력하기 위한 신호 출력 순서를 나타내고 있다.

[0269] 또한, 이 예는, V행 H열로서 그 각 행, 각 열에 번호를 부여하고, 출력 신호는 화소 셀의 RGB의 구별과 행렬 배열에 따른 번호를 부여하고 있다.

[0270] 도 24a의 예의 경우에는, 보텀측도 탑측도 화소 셀 배열에 따라 차례대로 신호가 출력된다.

[0271] 도 24b의 예의 경우에는, 시분할적으로 출력되어 간다.

[0272] 예를 들면, 보텀 측에서 최초에 화소 셀 R11, R13 등의 신호를 판독하고, 탑 측에서 화소 셀 G22, G24를 판독하고, 보텀 측에서 2번째에 화소 셀 B11, B14 등의 신호를 판독하고, 탑 측에서 화소 셀 G23, G25를 판독한다.

[0273] 이와 같이, 같은 색마다 신호 판독을 행하는 것이 가능하며, 임의의 같은 색 가산이 가능해진다.

[0274] 도 25a 및 도 25b는, 도 22와 같은 지그재그 배열시의 신호 출력 순서를 나타낸 도면이며, 도 25a는 수평 컬럼 공유 없음의 경우를 나타내고, 도 25b는 수평 컬럼을 공유할 때 신호를 출력하기 위한 신호 출력 순서를 나타내고 있다.

- [0275] 또한, 이 예는, V행 H열로서 그 각 행, 각 열에 번호를 부여하고, 출력 신호는 화소 셀의 RGB의 구별과 행렬 배열에 따른 번호를 부여하고 있다.

- [0276] 도 25a의 예의 경우에는, 보텀측도 탑측도 화소 셀 배열에 따라 차례대로 신호가 출력된다.

- [0277] 도 25b의 예의 경우에는, 시분할적으로 출력되어 간다.

- [0278] 예를 들면, 보텀 측에서 최초에 화소 셀 R11, R13, R15 등의 신호를 판독하고, 탑 측에서 화소 셀 G21, G23, G25를 판독하고, 보텀 측에서 2번째에 화소 셀 G22, G24, G26 등의 신호를 판독하고, 탑 측에서 화소 셀 B12, B14, B16를 판독한다.

- [0279] 이와 같이, 같은 색마다 신호 판독을 행하는 것이 가능하며, 같은 색 화소로부터의 신호의 임의의 가산 처리가 가능해진다.

- [0280] 이상, 화소 셀 배열의 구체예에 대하여 설명하였다.

- [0281] 여기서, 전술한 도 17a 및 도 17b의 정방 배열을 채용한 경우의 리플렉터의 형성 예에 대하여 설명한다.

- [0282] 본 실시예의 화소 셀 배열에 있어서는, 드레인 컨택트 DCNT, 소스 컨택트 SCNT, 게이트 컨택트 GCNT, 및 웨(기판) 컨택트 WCNT가, 게이트의 4방향으로 배치하는 것이 가능하므로, 도 26a에 나타낸 바와 같이, 수광 영역 전체가 게이트 영역으로 된다.

- [0283] 따라서, 도 26b에 나타낸 바와 같이, 기본적으로 게이트 영역 전체에 중첩되도록 리플렉터(200)를 형성할 수 있다.

- [0284] 한편, 도 17a 및 도 17b의 정방 배열을 채용한 경우, 리플렉터를 적층 구조 중 어느 것인가의 배선을 이용하여 형성하는 것도 가능하다.

- [0285] 이하, 제1 예 ~ 제3 예에 대하여 설명한다.

- [0286] 도 27은 리플렉터와 배선 공유 레이아웃의 제1 예를 나타낸 도면이다.

- [0287] 도 28은 리플렉터와 배선 공유 레이아웃의 제2 예를 나타낸 도면이다.

- [0288] 도 29는 리플렉터와 배선 공유 레이아웃의 제3 예를 나타낸 도면이다.

- [0289] 도 27의 제1 예는, 도 17a 및 도 17b의 예와 달리, 게이트 라인 LGT를 제1 메탈 배선으로 하고, 드레인 라인 LDRN를 제2 메탈 배선으로 하고, 신호 라인 LSGN와 그라운드 라인 LGND를 제3 메탈 배선으로 한 경우이다.

- [0290] 이 경우, 게이트 라인 LGT의 제1 메탈 배선을 리플렉터(200)로서 사용한다. 리플렉터(200)는 게이트 영역에 대응하여 선택적으로 형성된다.

- [0291] 도 28의 제2 예는, 도 17a 및 도 17b와 마찬가지로, 그라운드 라인 LGND를 제1 메탈 배선으로 하고, 신호 라인 LSGN를 제2 메탈 배선으로 하고, 게이트 라인 LGT와 드레인 라인 LDRN를 제3 메탈 배선으로 한 경우이다.

- [0292] 이 경우, 그라운드 라인 LGND의 제1 메탈 배선을, 리플렉터(200)로서 사용한다.

- [0293] 도 29의 제3 예는, 도 27의 예와 마찬가지로, 게이트 라인 LGT를 제1 메탈 배선으로 하고, 드레인 라인 LDRN를 제2 메탈 배선으로 하고, 신호 라인 LSGN와 그라운드 라인 LGND를 제3 메탈 배선으로 한 경우이다.

- [0294] 이 경우, 게이트 라인 LGT의 제1 메탈 배선을, 리플렉터(200)로서 사용하지만, 스트라이프형으로 하여 리플렉터(200)가 형성된다.

- [0295] 이상, 화소 셀 구조, 배열, 리플렉터의 형성 예에 대하여 설명하였다.

- [0296] 이하에서는, 컬럼 회로 측을 포함한 신호 처리계의 특징적인 구성, 기능에 대하여 설명한다.

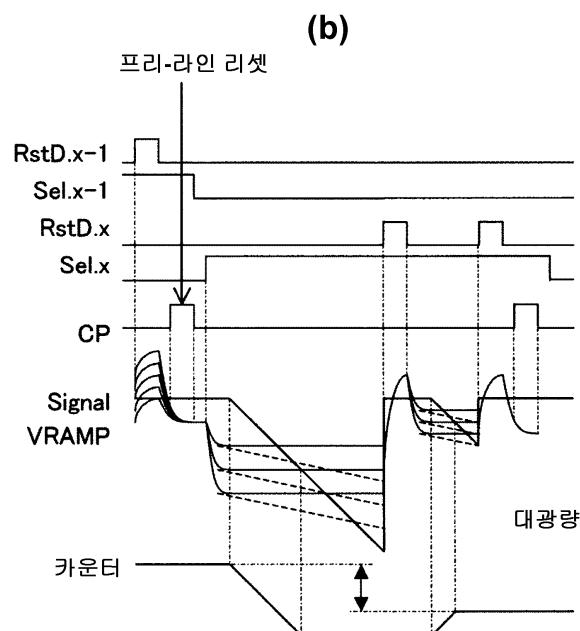

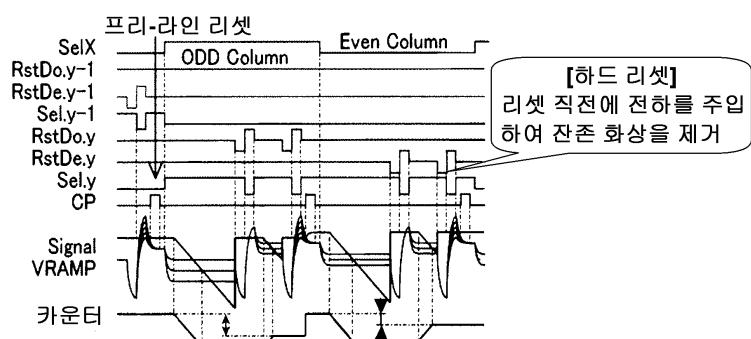

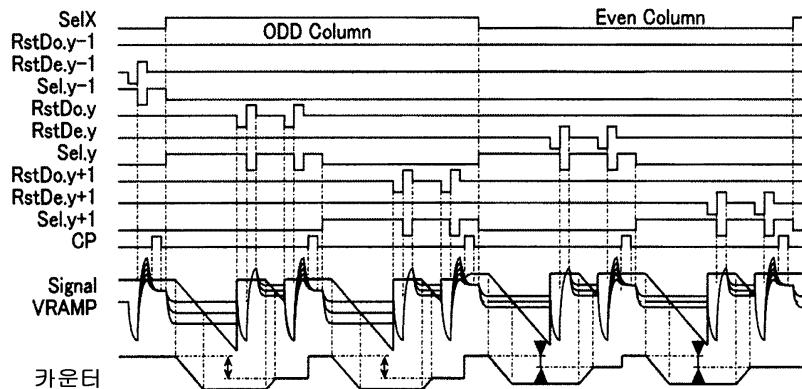

- [0297] 먼저, 본 실시예에 있어서는, 고체 활상 장치(1)는, 컬럼 회로(400)(410)의 비교기(401)(411)의 기준 레벨을, 전 라인(preceding line)의 리셋 레벨을 이용해서 대 광량 내성(large light amount resistance)을 향상시키는 프리 라인 세트 기능을 가지고 있다.

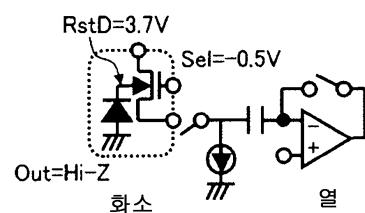

- [0298] 도 30a 및 도 30b는, 프리 라인 세트의 기본 개념을 나타낸 도면이며, 도 30a는 등가 회로를 나타내고, 도 30b는 타이밍 차트를 각각 나타내고 있다.

- [0299] 이 경우, 비교기(401)(411) 내의 램프(ramp) 파형 VRAMP와의 비교 동작에 들어가기 전(D 상 판독 전)에, 컬럼

회로(400)(410)의 스위치(SW)(402)(412)를 온으로 하고, 비교기의 입출력을 접속하여 회로 리셋을 행한다.

[0300] 이로써, 컬럼 회로(400)(410)의 비교기(401)(411)의 기준 레벨을, 전 라인의 리셋 레벨을 이용해 대 광량 내성을 향상시킨다.

[0301] 또한, 본 실시예에 있어서는, 화소 리셋 직전에 드레인으로부터 화소에 전하를 주입하여 화소 셀을 포화 상태(화소 셀을 하드 리셋 상태)로 한 후 리셋 동작시킴으로써, 잔상을 경감하는 기능을 채용하고 있다.

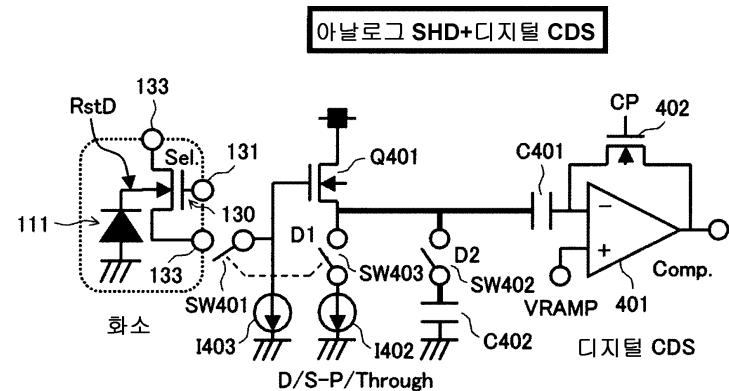

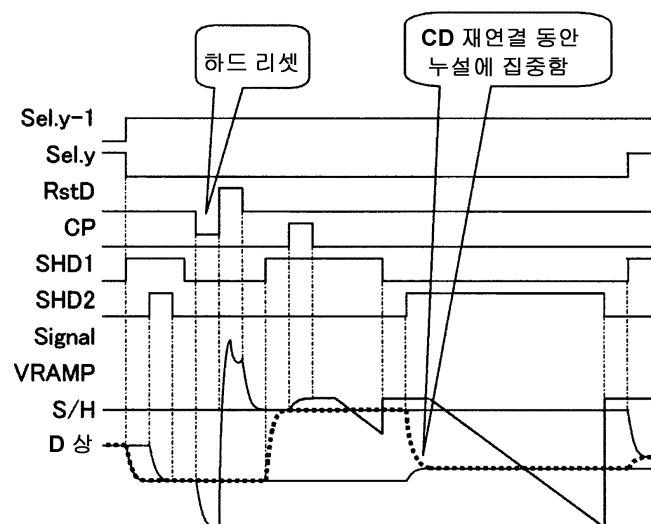

[0302] 도 31a 및 도 31b는, 본 실시예에 따른 하드 리셋 기능에 대응한 신호 처리계를 개념적으로 나타낸 도면이며, 도 31a는 등가 회로를 나타내고, 도 31b는 타이밍 차트를 각각 나타내고 있다.

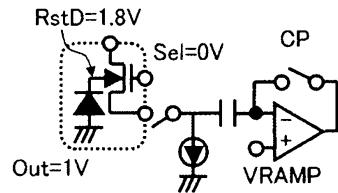

[0303] 이 경우, 신호 전송 라인과 컬럼 회로(400)(410) 사이에 배치된 스위치 SW401과 커패시터 C401(C411)에 사이에, 드레인이 전원 전위에 접속되고 소스가 커패시터 C401(C411)에 접속된 트랜지스터 Q401과, 트랜지스터 Q401의 접속점과 접지 라인 사이에 스위치 SW402를 통하여 접속된 커패시터 C402와, 트랜지스터 Q401의 소스에 스위치 SW403을 통하여 접속된 전류원 I402와, 트랜지스터 Q401의 게이트에 접속된 전류원 I403을 가지고 있다. 또한, 트랜지스터 Q401의 게이트는 스위치 SW401에 접속되어 있다.

[0304] 하드 리셋은, 트랜지스터(130)의 게이트 전압 VG를 0V ~ -1.0V, 드레인 전압 VD를 1.8V로 하면, 소스 전압 VS는 하이 임피던스 Hi-Z 또는 LD이며, 측적된 전자가 오버플로하는 상태로 한다. 환언하면, 화소 셀 Ce1을 포화시킨다. 이때 신호를 유지한다.

[0305] 계속되는 리셋 동작에서는, 트랜지스터(130)의 게이트 전압 VG를 0 ~ -1.0V, 드레인 전압 VD를 3.0V 이상, 예를 들면, 3.7V로 하면, 소스 전압 VS는 하이 임피던스 Hi-Z 또는 LD이며, 측적 웨尔 내에 존재하는 전자를, 드레인 전극을 통해 외부로 배출시킨다.

[0306] 이 경우, 샘플링 시간이 걸리는 신호 측의 누락 포함을 회피하는 데는 신호측만 아날로그 샘플링으로 하여, CDS를 디지털로 하는 등으로, 1개의 용량 추가로 큰 개선 효과가 얻어진다.

[0307] 예를 들면, D 상을 아날로그, P 상을 디지털의 샘플링의 조합으로, 소 사이즈로 대 광량 내성을 향상시키는 것이 가능해진다.

[0308] 이 아날로그 SHD 및 디지털 CDS에 대응하는 회로 구성은, 이른바 플로팅 디퓨전(FD) 구성의 화소 셀에도 적용할 수 있다.

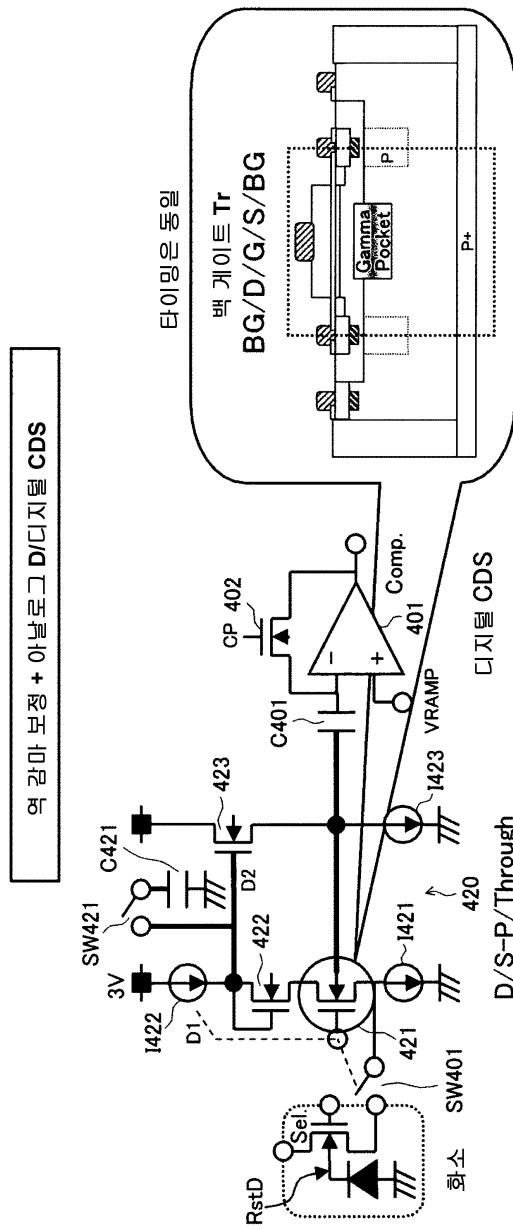

[0309] 본 실시예에 있어서는, 화소 셀에  $\gamma$  특성을 적극적으로 갖게 하고 있다.  $\gamma$  특성에 대응하여, 화소 셀의 트랜지스터(130)와 동일한 구조의 백 게이트 단자를 가지는 트랜지스터를 사용하여 역  $\gamma$  보정 회로를 구성하고 있다.

[0310] 도 32는, 역  $\gamma$  보정 회로를 포함하는 신호 처리계의 기본 개념을 나타내는 등가 회로도이다.

[0311] 역  $\gamma$  보정 회로(420)는, 백 게이트 단자를 가지는 트랜지스터(421), 전류 미러를 구성하는 트랜지스터(422, 423), 스위치 SW421, 커패시터 C421, 및 전류원 I421, I422, I423을 가진다.

[0312] 트랜지스터(421)의 소스와 전류원 I421이 접속되고, 트랜지스터(421)의 소스와 전류원 I421의 접속점이 스위치 SW401에 접속되어 있다. 트랜지스터(421)의 드레인이 트랜지스터(422)의 소스에 접속되어 있다. 트랜지스터(422)의 게이트와 드레인끼리가 접속되고, 게이트와 드레인의 접속점이 전류원 I422, 트랜지스터(423)의 게이트, 및 스위치 SW421에 접속되어 있다.

[0313] 트랜지스터(423)의 드레인이 전원 전위에 접속되고, 트랜지스터(423)의 소스가 전류원 I423에 접속되고, 트랜지스터(423)의 소스와 전류원 I423의 접속점이 트랜지스터(421)의 기판 및 커패시터 C401에 접속되어 있다. 또한, 스위치 SW421에는 커패시터 C421이 접속되어 있다.

[0314] 신호 처리계의 타이밍 차트는, 도 32b와 동일하므로, 여기서는 나타내고 있지 않다.

[0315] 역  $\gamma$  보정 회로(420)에서  $\gamma$  특성을 떨어뜨려, 즉  $\gamma$  특성의 비선형성을 선형으로 변화시켜 아날로그/디지털 변환을 행한다.

[0316] 이와 같이, 본 실시예에 따른 신호 처리계가 이상의 특징을 가진다.

[0317] 일반적인 컬럼 디지털 CDS/ADC에서, 1H(수평) 기간을 사용하여 천천히 CDS/ADC를 수행하여, FD에 기억된 신호를 상정하고 있다.

- [0318] 그러나 임계값 변조 방식에서는, CDS/ADC 중에도 수광에 의한 신호 변화가 일어나기 때문에, 큰 광량으로 고속 전자 셔터를 사용했을 때는, 신호 오차 및 플로팅 블랙(floating black)이 발생할 우려가 있다.

- [0319] 일반적으로는, 고속 아날로그 CDS로 이것을 회피하고 있었지만, 본 방식에 있어서는, 셔터 속도와 신호량을 고려하여 흑레벨을 보정하는 것도 생각되지만, 실용적인 범위의 전자 셔터 속도에서는 별문제가 되지 않는 것으로 생각된다.

- [0320] 샘플링 시간이 걸리는 신호 측의 누락 포함을 회피하는 데는, 전술한 바와 같이, 신호측만 아날로그 샘플링으로 한다. 그 결과, 1개의 커페시터 추가에 의해 큰 개선 효과가 얻어진다.

- [0321] 또한, 컬럼 디지털 CDS의 리셋에는, 전 라인의 리셋 레벨을 이용하는 프리 라인 리셋 방식으로 대처할 수 있다.

- [0322] 도 33a ~ 도 33c는, 프리 라인 리셋 방식의 레벨 다이어그램과 2컬럼 공유와  $2 \times 2$  화소 타이밍을 모아서 나타낸 도면이며, 도 33a는 동작 전압을, 도 33b는 2컬럼 공유에서의 정지화상 시퀀스를, 도 33c는  $2 \times 2$  화소 가산 시퀀스의 예를 나타내고 있다.

- [0323] 또한, 본 실시예에 있어서는, 예를 들면, 도 34에 나타낸 바와 같이, 화소 셀(트랜지스터)을 어레이형으로 배열하여, 복수 화소로 하나의 출력 신호로 함으로써, 고Qs 및 저노이즈인 다이나믹 레인지(dynamic range)를 달성할 수 있다.

- [0324] 하나의 출력 신호로 하는 방법은, 고체 활상 소자 내에서도, 소자 외의 신호 처리 IC에서도 상관없다. 소자 외의 신호 처리 IC로 행하는 경우는, 예를 들면, 결함 화소의 보정을 할 수 있는 이점이 있다.

- [0325] 또한, 본 실시예에 있어서는, 예를 들면, 도 35의 평면도 및 도 36a의 간략 단면도에 나타낸 바와 같이, 최종적으로 1출력으로 되는 것을 전제로, 어레이형으로 배열된 복수 화소 내에서 신호가 서로 혼합되도록 복수 화소 단위로 소자 분리를 행한다. 결과적으로, 센서 축적 영역이 더 확대되어 고다이나믹 레인지(D-Range)를 달성할 수 있다.

- [0326] 또한, 본 실시예에 있어서는, 예를 들면, 도 36b의 간략 단면도에 나타낸 바와 같이, 컬러 필터 코딩이 어레이형으로 배열된 복수 화소 내에서 같은 색이 아닌, 예를 들면, 원색의 B(Blue) 및 R(Red)로 하면, 보색의 마젠타(Magenta)로 된다. 그러므로 캠코더 등에서 사용되는 보색 신호 처리를 이용할 수 있다. 그 결과, 색재현은 원색과 같은 성능으로 되고, 또한, 컬러 필터 재료의 공유에 의한 양산성(mass productivity)의 향상을 달성할 수 있다.

- [0327] 본 실시예에 있어서는, 예를 들면, 도 37 및 도 38a 및 도 38b에 나타낸 바와 같이, 인접 화소 셀과 드레인 또는 소스 또는 기판(웰) 또는 게이트의 컨택트를, 일부 또는 복수 공유하는 화소 셀에 있어서는, 복수 화소 단위로 소자 분리를 행하는 구조로 한 경우는, 리셋 드레인 아래의 소자 분리 p웰(p-well)을 제거할 수 있기 때문에, 리셋 전압을 저감할 수 있는 효과가 얻어진다.

- [0328] 또한, 본 실시예의 고체 활상 장치(1)에 있어서는, 화소로부터의 신호 판독시에, 화소 리셋을 하지 않고 광전변환을 계속함으로써, 암 전류의 악화가 없는 비파괴 판독을 가능하게 하는 구성을 가진다.

- [0329] 이 비파괴 판독에 의해, 예를 들면, 고S/N인 와이드 다이나믹 레인지(Wide D-Range), 저속 노광이나 뱈브 노광 중의 라이브 뷰(Live View)를 실현할 수 있다.

- [0330] 또한, 이 비파괴 판독에 의해, 정지화상 저속 노광, 동영상의 비동기 및 동기에서의 동시 동작을 가능하게 하는, AE/AF 겸용이 가능하고, 고속 부분 스캔(SCAN)으로, 전 영역(entire area)에서 랜덤으로 리얼타임 AE/AF를 가능하게 한다.

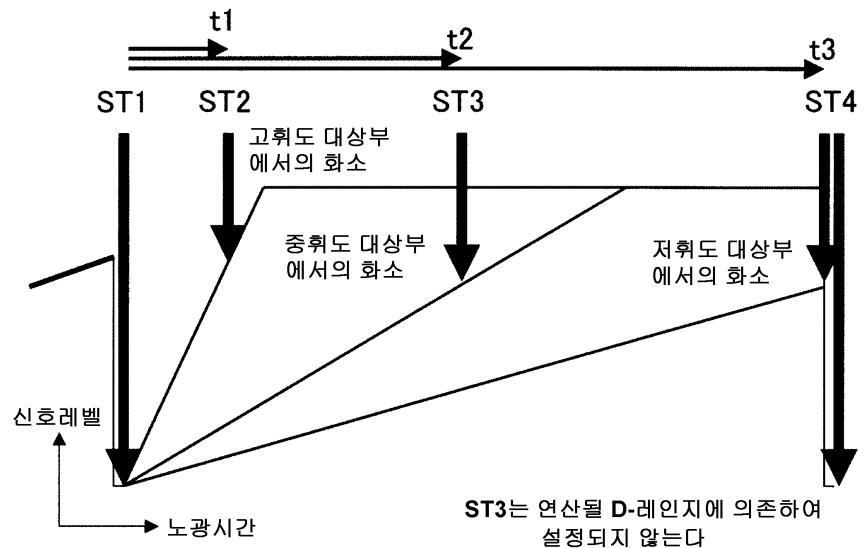

- [0331] 도 39는, 비파괴 판독에 의한 와이드 다이나믹 레인지(Wide D-Range) 시퀀스 예를 나타낸 도면이다.

- [0332] 도 39에 있어서, 세로 방향이 신호 레벨을, 가로 방향이 노광 시간을 나타내고 있다.

- [0333] <스텝 ST1>

- [0334] 신호 레벨을 리셋하고, 블랙 스캔(Black SCAN)을 행한다. 여기서는 임계값 Vth 불균일 화상이 포착된다.

- [0335] <스텝 ST2>

- [0336] 시각 t1에서, 제1 중간 스캔(SCAN#1)을 행한다. 여기서는, 고휘도 화상이 받아들여지고 Vth 차분을 얻을 수 있다.

[0337] <스텝 ST3>

[0338] 시각 t2에서, 제2 중간 스캔(SCAN#2)을 행한다. 여기서는, 중 휘도 화상이 받아들여지고 Vth 차분을 얻을 수 있다.

[0339] <스텝 ST4>

[0340] 시각 t3에서, 파이널 스캔(Final SCAN)을 행하여 리셋을 행한다. 여기서는, 저휘도 화상이 포착된다(CDS).

[0341] 그리고 도시하지 않지만, 스텝 ST5로서, 고휘도 화상과 중 휘도 화상과 저휘도 화상의 화상 합성으로 와이드 다이나믹 레인지(Wide Dynamic Range)화가 도모된다. (각 화상에 시간 비를 승산하고, 레벨별로 합성하여 고DR 화상으로 함)

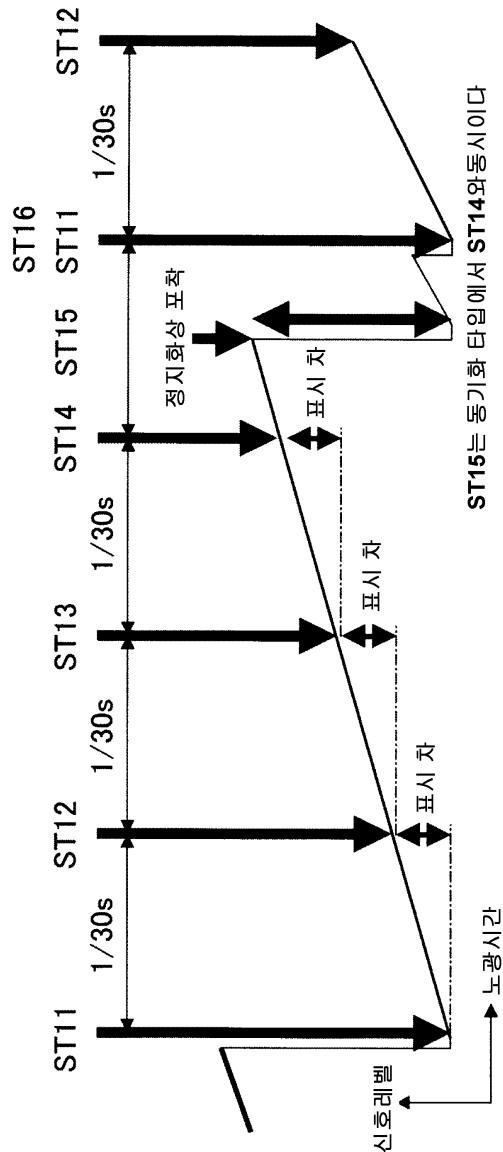

[0342] 도 40은, 비파괴 판독에 의한 저속 라이브 뷰(Live View) 시퀀스 예를 나타낸 도면이다.

[0343] 도 40에 있어서, 세로 방향이 신호 레벨을, 가로 방향이 노광 시간을 나타내고 있다.

[0344] <스텝 ST11>

[0345] 신호 레벨을 리셋하고, 블랙 스캔(Black SCAN)을 행한다. 여기서는 임계값 Vth 불균일 화상이 포착된다.

[0346] <스텝 ST12>

[0347] 제1 중간 스캔(SCAN#1)을 행한다. 여기서는, #1 화상이 포착되고 #0 Vth 차분을 얻을 수 있고, 예를 들면, 모니터링을 위해 표시된다.

[0348] <스텝 ST13>

[0349] 제2 중간 스캔(SCAN#2)을 행한다. 여기서는, #2 화상이 포착되고 #1 Vth 차분을 얻을 수 있고, 예를 들면, 모니터링을 위해 표시된다.

[0350] <스텝 ST14>

[0351] 파이널 스캔(Final SCAN)을 행한다. 여기서는, #n 화상이 포착되고 #n Vth 차분을 얻을 수 있고, 예를 들면, 모니터링을 위해 표시된다.

[0352] <스텝 ST15>

[0353] 입력 스캔을 행하여 리셋을 행한다. 여기서는, 최종 화상 포착 CDS와 메모리로의 기록이 행해진다.

[0354] <스텝 ST16>

[0355] 비동기 타입의 경우는, 스텝 ST15에서의 화상 포착(정지화상)을 1/30s로 환산하여 표시한다.

[0356] 이와 같이, 비파괴 판독에 의해, 예를 들면, 고S/N인 와이드 다이나믹 레인지(Wide D-Range), 저속 노광이나 빨르 노광 중의 라이브 뷰(Live View)를 실현할 수 있다.

[0357] 이상 설명한 바와 같이, 본 실시예에 의하면, 기판(100)은, 광이 조사되는 제1 기판면(101) 측과 소자가 형성되는 제2 기판면(102) 측을 가지고, 인접 셀과 소자 분리층에 의해 분리된 복수의 화소 셀 Cel(2A)이 형성되고, 화소 셀 Cel은, 제1 기판면(101) 측에 형성된 제1 도전형(본 실시예에 있어서는 n형) 웨(제1 웨)(110)과, 제1 웨(110)보다 제2 기판면(102) 측에 형성된 제2 도전형(p형) 웨(제2 웨)(120)을 가지고, n형의 제1 웨(110)은, 제1 기판면(101) 측으로부터의 광을 수광하는 수광부로서 기능하고, 수광된 광의 광전 변환 기능 및 전하 축적 기능을 가지고, 제2 웨(120)은, 제1 웨(110)의 수광부에 있어서의 축적 전하를 검출하고, 임계값 변조 기능을 가지는 MOS형의 트랜지스터(130)가 형성되어 있고, 제1 웨(110)(및 제2 웨(120))의 측벽에는 이들을 에워싸도록 제1 도전형(본 실시예에서는 n형)의 역의 도전형의 제2 도전형인 p형 소자 분리층(도전 층)(140)이 형성되어 있으므로, 다음과 같은 효과를 얻을 수 있다.

[0358] 드레인(D)/게이트(G)/소스(S) 구조의 1트랜지스터로 화소를 구성할 수 있다. 화소 구조가 로직(Logic) 프로세스와 양립할 수 있기 때문에 공정수 증가가 최소로 된다.

[0359] 드레인, 소스, 게이트, 웨의 컨택트를 공유할 수 있기 때문에 레이아웃 효율이 높고, 미세 화소가 실현할 수 있다.

[0360] 게이트 면적이 크므로, 트랜지스터 노이즈가 매우 적다.

- [0361] 또한, 화소 전체가 축적 영역이기 때문에, 포화 신호량이 크고 고다이나믹 레인지(DR)를 실현할 수 있다.

- [0362] 또한, 계면으로부터 발생하는 암 전류가 드레인으로 배출되기 때문에, 계면의 암 전류 화상 결함이 발생하지 않는다.

- [0363] 또한, 게이트 ON/OFF에 관계없이 암 전류 악화가 없는 비파괴 판독이 가능해진다.

- [0364] 또한, 수광부 전체가 게이트이다. 리플렉터가 탑재될 때 근적외 고감도 및 초미세 화소 실현을 할 수 있다.

- [0365] 또한, 역  $\propto$  보정 기능에 의해 저노이즈화가 가능하다.

- [0366] 이상과 같은 특징을 가지는 고체 활상 장치는, 디지털 카메라나 비디오 카메라의 활상 디바이스로서 적용될 수 있다.

- [0367] 도 41은, 본 발명의 실시예에 따른 고체 활상 소자가 적용되는 카메라 시스템의 구성의 일례를 나타낸 도면이다.

- [0368] 카메라 시스템(500)은, 도 41에 나타낸 바와 같이, 본 실시예에 따른 고체 활상 장치(1)가 적용 가능한 활상 디바이스(510)와, 이 활상 디바이스(510)의 화소 영역에 입사광을 안내하는(피사체상을 결상하는) 광학계, 예를 들면, 입사광(상 광)을 활상면 상에 결상시키는 렌즈(520)와, 활상 디바이스(510)를 구동하는 구동 회로(DRV)(530)와, 활상 디바이스(510)의 출력 신호를 처리하는 신호 처리 회로(PRC)(540)를 가진다.

- [0369] 구동 회로(530)는, 활상 디바이스(510) 내의 회로를 구동하는 스타트 펄스나 클록 펄스를 포함하는 각종의 타이밍 신호를 생성하는 타이밍 제너레이터(도시하지 않음)를 가지고, 소정의 타이밍 신호로 활상 디바이스(510)를 구동한다.

- [0370] 또한, 신호 처리 회로(540)는, 활상 디바이스(510)의 출력 신호에 대하여 CDS(Correlated Double Sampling; 상관 이중 샘플링)와 같은 신호 처리를 행한다.

- [0371] 신호 처리 회로(540)에서 처리된 화상 신호는, 예를 들면, 메모리 등의 기록 매체에 기록된다. 기록 매체에 기록된 화상 정보는, 프린터 등에 의해 하드 카피된다. 또한, 신호 처리 회로(540)에서 처리된 화상 신호를 액정 디스플레이 등으로 이루어지는 모니터에 동영상으로서 표시된다.

- [0372] 전술한 바와 같이, 디지털 스틸 카메라 등의 활상 장치에 있어서, 활상 디바이스(510)로서 전제로 한 고체 활상 장치(1)를 탑재함으로써, 고정밀도의 카메라를 실현할 수 있다.

- [0373] 본 발명은, 상기한 실시예의 설명에 한정되지 않는다.

- [0374] 예를 들면, 본 실시예에서 든 수치나 재료는 일례이며, 이에 한정되는 것은 아니다.

- [0375] 그 외에, 본 발명의 요지를 벗어나지 않는 범위에서, 각종의 변경이 가능하다.

- [0376] 첨부된 청구의 범위 및 그 등가물의 범주 내에 있는 한 설계 요건 및 그외 요인에 따라 다양한 변형, 조합, 서브-조합 및 대안이 이루어질 수 있다는 것을 당업자는 이해할 수 있다.

### 도면의 간단한 설명

- [0377] 도 1은 본 실시예에 따른 고체 활상 장치의 개략 구성을 나타낸 블록도이다.

- [0378] 도 2a 및 도 2b는 실시예에 따른 고체 활상 장치의 화소부의 기본 구조를 나타낸 도면이다.

- [0379] 도 3은 본 실시예에 따른 화소 셀의 등가 회로를 나타낸 도면이다.

- [0380] 도 4는 앞면 조사형 BMCD의 경우에 대하여, 입사광의 파장이 트랜지스터의 배치와 어떠한 관계가 되는지를 나타낸 도면이다.

- [0381] 도 5는 앞면 조사형의 경우에, 투명 전극/게이트 실리콘 산화막/실리콘 단결정이 형성하는 에너지 밴드 상태의 개략을 나타낸 도면이다.

- [0382] 도 6은 도 2a 및 도 2b에 나타낸 장치의 전위 상태 변화에 따른 각 영역에 있어서의 반도체 기판면과 수직 방향의 반도체 기판 내의 전자에 대한 전위의 변화를 나타낸 도면이다.

- [0383] 도 7은 도 2a 및 도 2b에 있어서의 a-a'선에 있어서의 포텐셜 분포의 일례를 나타낸 도면이다.

- [0384] 도 8은 본 실시예의 신호 판독 처리계의 구성을 모식적으로 나타낸 도면이다.

- [0385] 도 9는 본 실시예에 따른 화소부에 있어서의 화소 셀의 레이아웃의 일례를 나타낸 도면이다.

- [0386] 도 10a 및 도 1b는 도 9의 a-a'선 및 b-b'선에 있어서의 간략 단면도이다.

- [0387] 도 11은 도 9의 배치를 45도 회전시켜 배열한 구조도이다.

- [0388] 도 12는 게이트를 X 방향(가로 방향) 스트라이프에서 공통으로 한 레이아웃예를 나타낸 도면이다.

- [0389] 도 13은 드레인 측이 핀치(pinch)된 한 레이아웃예를 나타낸 도면이다.

- [0390] 도 14는 본 실시예에 따른 화소부에 있어서의 화소 셀의 레이아웃의 다른 예를 나타낸 도면이다.

- [0391] 도 15는 도 14의 a-a'선 및 b-b'선에 있어서의 간략 단면도이다.

- [0392] 도 16a 및 도 16b는 막두께가 상이한 화소 셀에 리플렉터를 설치한 예를 나타낸 도면이다.

- [0393] 도 17a 및 도 17b는 컨택트 공유형 화소부의 화소 셀 배열예를 나타낸 도면이다.

- [0394] 도 18은 도 17의 레이아웃을 채용하여 컬럼 회로(column circuit)를 공유하는 신호 처리계와 화소부를 간략화한 등가 회로를 나타낸 도면이다.

- [0395] 도 19a 및 도 19b는 도 17a 및 도 17b와 같은 정방 배열시의 신호 출력 순서를 나타낸 도면이다.

- [0396] 도 20a 및 도 20b는 도 17a 및 도 17b와 같은 정방 배열을 45도 회전시킨 지그재그(ZigZag) 배열을 나타낸 도면이다.

- [0397] 도 21은 도 20a의 레이아웃을 채용하여 컬럼 회로를 공유하는 신호 처리계와 화소부를 간략화한 등가 회로를 나타낸 도면이다.

- [0398] 도 22a 및 도 22b는 도 17a 및 도 17b와 같은 정방 배열을 45도 회전시킨 다른 지그재그(ZigZag) 배열을 나타낸 도면이다.

- [0399] 도 23은 도 22a의 레이아웃을 채용하여 컬럼 회로를 공유하는 신호 처리계와 화소부를 간략화한 등가 회로를 나타낸 도면이다.

- [0400] 도 24a 및 도 24b는 도 20a 및 도 20b와 같은 지그재그 배열시의 신호 출력 순서를 나타낸 도면이다.

- [0401] 도 25a 및 도 25b는 도 22a 및 도 22b와 같은 지그재그 배열시의 신호 출력 순서를 나타낸 도면이다.

- [0402] 도 26a 및 도 26b는 정방 배열을 채용한 경우의 리플렉터의 형성 예에 대하여 설명하기 위한 도면이다.

- [0403] 도 27은 리플렉터와 배선 공유 레이아웃의 제1 예를 나타낸 도면이다.

- [0404] 도 28은 리플렉터와 배선 공유 레이아웃의 제2 예를 나타낸 도면이다.

- [0405] 도 29는 리플렉터와 배선 공유 레이아웃의 제3 예를 나타낸 도면이다.

- [0406] 도 30a 및 도 30b는 프리 라인 리셋(pre-line reset)의 기본 개념을 나타낸 도면이다.

- [0407] 도 31a 및 도 31b는 본 실시예에 따른 하드 리셋 기능(hard reset function)에 대응한 신호 처리계를 개념적으로 나타낸 도면이다.

- [0408] 도 32는 역 y 보정 회로를 포함하는 신호 처리계의 기본 개념을 나타내는 등가 회로도이다.

- [0409] 도 33a 및 도 33b는 프리 라인 리셋 방식의 레벨 다이어그램과, 2 컬럼 공유와, 2×2 화소 타이밍을 모아서 나타낸 도면이다.

- [0410] 도 34는 복수 화소를 어레이형으로 배열하여 복수 화소로 하나의 출력 신호로 하는 구성예를 나타낸 평면도이다.

- [0411] 도 35는 복수 화소를 어레이형으로 배열하여 복수 화소 단위로 소자 분리를 행함으로써 하나의 출력 신호로 하는 구성예를 나타낸 평면도이다.

- [0412] 도 36a 및 도 36b는 복수 화소를 어레이형으로 배열하여 복수 화소 단위로 소자 분리를 행함으로써 하나의 출력 신호로 하는 구성예를 나타낸 단면도이다.

- [0413] 도 37은 복수 화소를 어레이형으로 배열하여 복수 화소 단위로 소자 분리를 행함으로써 하나의 출력 신호로 하는 다른 구성예를 나타낸 평면도이다.

- [0414] 도 38a 및 도 38b는 도 37의 a-a'선 및 b-b'선에 있어서의 간략 단면도이다.

- [0415] 도 39는 비파괴 관독에 의한 와이드 다이나믹 레인지(Wide D-Range) 시퀀스 예를 나타낸 도면이다.

- [0416] 도 40은 비파괴 관독에 의한 저속 라이브 뷰(Live View) 시퀀스 예를 나타낸 도면이다.

- [0417] 도 41은 본 발명의 실시예에 따른 고체 촬상 소자가 적용되는 카메라 시스템의 구성의 일례를 나타낸 도면이다.

## 도면

### 도면1

## 도면2

도면3

도면4

앞면 조사형 BMCD의 경우

10

## 도면5

## 도면6

## 도면7

S08P1891

### 도면8

도면9

도면10

도면11

도면12

도면13

도면14

### 도면15

도면16

### 도면17a

### 도면17b

## 도면18

### 도면19a

\* 화소 셀을 신호 출력 순서로 배열하기 위해,

레이아웃 도면에 도시된 흐로의 배치를 상하반전 시킴

EXPRESSION = COLOR ROW V. COLUMN H

### 도면19b

도면20

(a)

(b)

## 도면21

도면22

## 도면23

### 도면24a

신호 배선 #1

## ■ 가로열은 공유되지 않음

### 도면24b

## 도면25a

## ■ 가로 열은 공유되지 않음

도면25b

## 신호 배선 #2

도면26

## 도면27

도면28

도면29

도면30

도면31

(a)

(b)

도면32

## 도면33a

## 동작 전압

## 1. 축적 화소(비-선택 화소)

## 2. 데이터 판독

## 2. 리셋

## 도면33b

## 구동 타이밍

## ■ 2열을 공유하는 정지화상 시퀀스

## 도면33c

## ■ 2x2 화소 추가 시퀀스의 예

## 도면34

도면35

도면36

도면37

도면38

도면39

도면40

도면41