(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3929119号

(P3929119)

(45) 発行日 平成19年6月13日(2007.6.13)

(24) 登録日 平成19年3月16日(2007.3.16)

(51) Int.C1.

F 1

|                       |                 |

|-----------------------|-----------------|

| GO2F 1/1368 (2006.01) | GO2F 1/1368     |

| GO2F 1/1343 (2006.01) | GO2F 1/1343     |

| GO9F 9/30 (2006.01)   | GO9F 9/30 338   |

| HO1L 29/786 (2006.01) | HO1L 29/78 612C |

| HO1L 21/336 (2006.01) | HO1L 29/78 616J |

請求項の数 8 (全 11 頁)

(21) 出願番号 特願平9-209427

(22) 出願日 平成9年8月4日(1997.8.4)

(65) 公開番号 特開平11-52418

(43) 公開日 平成11年2月26日(1999.2.26)

審査請求日 平成15年10月14日(2003.10.14)

(73) 特許権者 595059056

株式会社アドバンスト・ディスプレイ

熊本県菊池郡西合志町御代志997番地

(74) 代理人 100065226

弁理士 朝日奈 宗太

(74) 代理人 100098257

弁理士 佐木 啓二

(72) 発明者 永野 慎吾

熊本県菊池郡西合志町御代志997番地

株式会社アドバンスト・ディスプレイ内

(72) 発明者 遠藤 幸雄

熊本県菊池郡西合志町御代志997番地

株式会社アドバンスト・ディスプレイ内

審査官 白石 光男

最終頁に続く

(54) 【発明の名称】 液晶表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

TFTアレイ基板と、対向基板と、該 TFTアレイ基板と該対向基板とのあいだに挟持された液晶とからなり、該 TFTアレイ基板上にはゲート配線、信号線、TFT、画素電極、ソース電極、ドレイン電極および補助容量配線が形成されてなる液晶表示装置であつて、

該補助容量配線は該ゲート配線と前段のゲート配線とのあいだに、そのいずれとも平行に配設され、かつ、該画素電極の外周に沿って延在させて4つの延長部を有しており、前記前段のゲート配線と、該前段のゲート配線側の前記延長部とにまたがるように2箇所でそれぞれ前記画素電極上または下に前記信号線と同一の金属膜が形成され、

前記ドレイン電極と、該ゲート配線側の前記延長部が2箇所でそれぞれ重なり、

該画素電極の周囲が、該前段のゲート配線、前記信号線と同一の金属膜、前記延長部および前記ドレイン電極によって完全に遮光するように覆われてなる液晶表示装置。

## 【請求項 2】

前記信号線と同一の金属膜は、前記前段ゲート配線と該前段のゲート配線側の前記延長部との隙間に近傍にのみ配置される請求項1記載の液晶表示装置。

## 【請求項 3】

前記画素電極と前記4つの延長部のそれぞれとの重なり部分が第1の補助容量である請求項1または2記載の液晶表示装置。

## 【請求項 4】

10

20

前記画素電極と前記前段のゲート配線との重なり部分が第2の補助容量である請求項1、2または3記載の液晶表示装置。

【請求項5】

前記画素電極が前記前段のゲート配線上に拡張部分を有してなる請求項1から4のいずれかに記載の液晶表示装置。

【請求項6】

前記延長部が前記ソース配線の下部に拡張され、隣接する画素の補助容量配線の延長部と一体に幅広に形成されてなる請求項1から5のいずれかに記載の液晶表示装置。

【請求項7】

前記ソース配線が、2層からなる2層構造であり、下層はアモルファスシリコンからなる請求項1から6のいずれかに記載の液晶表示装置。 10

【請求項8】

前記ドレイン電極および前記信号線と同一の金属膜と画素電極がコンタクトホールを介して接続されてなる請求項1から7のいずれかに記載の液晶表示装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明はアクティブマトリックス型液晶表示装置に関する。

【0002】

【従来の技術】

アクティブマトリックス型液晶表示装置は、通常、半導体薄膜などからなる薄膜トランジスタ(thin film transistor、以下、TFTという)などが設けられた薄膜トランジスタアレイ基板(以下、アレイ基板という)と対向基板との2枚の基板のあいだに液晶などの表示材料が挟持され、さらに上下に偏光板を設置した構成となっている。対向基板上には、対向電極、カラーフィルタおよびブラックマトリックスなどが設けられている。また、この表示材料に対して、画素ごとに選択的に電圧を印加し、その電圧を制御することにより、液晶材料の電気光学特性を利用して表示を行う。

【0003】

とくに、TFTを用いたアクティブマトリックス型液晶表示装置のばあい、基板上に形成された電極である、画素電極と対向電極とが容量の電極板(以下、極板という)の役割を果たし、この極板のあいだに蓄積される電荷の量をTFTによって制御し、液晶に印加される電圧を制御することで表示を行う。 30

【0004】

携帯性、表示品位の点でCRTや単純マトリックス液晶表示装置より優れた特徴をもつアクティブマトリックス型液晶表示装置はノート型などの携帯型パーソナルコンピュータなどに広く実用されている。これらの実用においては、携帯性の向上のために消費電力を小さくすることが求められている。この低消費電力化の技術の一つとして、バックライトからの光利用効率を大きくする観点から、画素開口率を大きくすることが試みられている。

【0005】

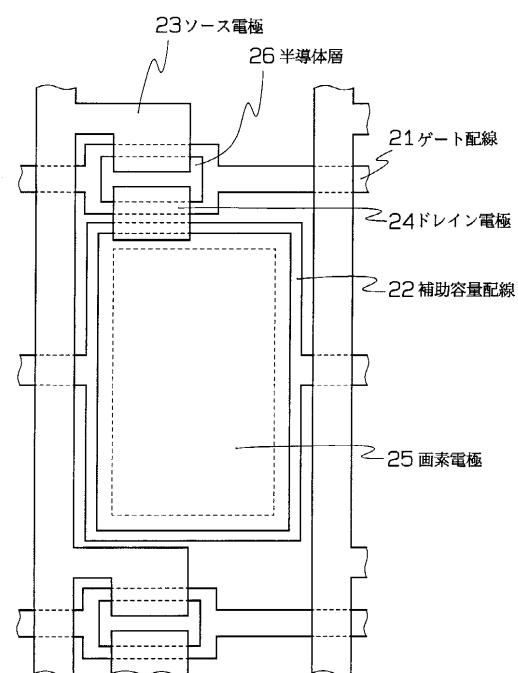

画素開口率を大きくする従来技術としては、たとえば、特開平5-297412号公報に、以下に説明する画素平面構造により画素開口率を大きくする技術が開示されている。一般に、画素開口率を制限する要因としては、表示品質向上のため液晶容量と並列に形成される補助容量電極が存在することや、画素電極以外の光透過領域からの光の漏れすなわち、漏れ光を防ぐ目的でカラーフィルタに形成されるブラックマトリックスが存在することがあげられる。図7および図8は、それぞれ従来技術の例による液晶表示装置の画素を示す平面説明図であり、図7において、21はゲート配線であり、22は補助容量配線であり、23はソース配線であり、24はドレイン電極であり、25は画素電極であり、26は半導体層である。また、図8において、31はゲート配線であり、33はソース電極であり、34はドレイン電極であり、35は画素電極であり、36は半導体層である。図7の例では、補助容量電極を画素電極の全周にわたり環状に形成することにより、アレイ基 40

板上での画素電極以外の光透過領域からの漏れ光に対する遮光と補助容量形成の2つの役割を画素電極の全周にわたり形成された補助容量電極にもたせている。これにより、カラーフィルタに形成するブラックマトリックスの開口部を、画素電極の全周にわたり環状に形成された補助容量電極の内径寸法より大きくすることができ、また非光透過領域である補助容量電極の画素開口部に与える影響を小さくすることで、開口率を大きくしている。

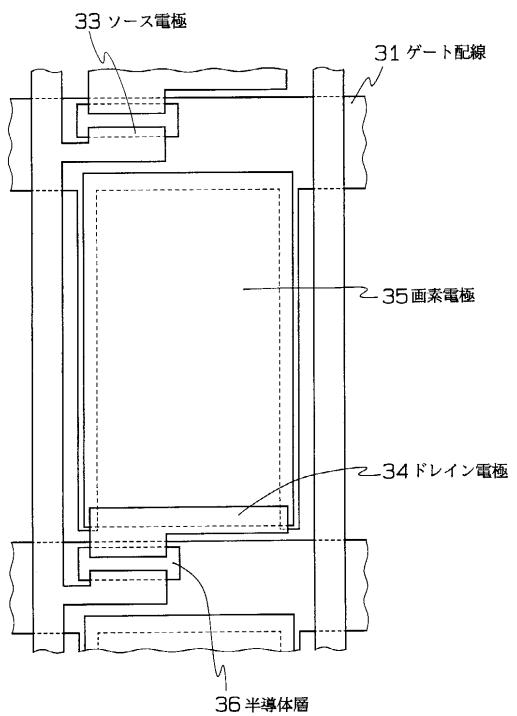

#### 【0006】

図8は、前述した従来例と同様の目的で、補助容量電極を形成するかわりに、ゲート電極を画素電極の全周を環状にとり囲むように設けて補助容量を形成した例である。このばあい、補助容量電極の形成が不要のため、ゲート配線と画素電極の間隔を小さくして開口率を大きくしている。

10

#### 【0007】

##### 【発明が解決しようとする課題】

しかしながら、図7に示した従来例では、大きな開口率をうるためにゲート配線と補助容量配線との間隔を小さくしなければならないという問題が生じる。このばあい、ゲート電極と補助容量電極とを同一の膜により形成すると、電極間隔の減少による両電極間の短絡が発生しやすいという問題が生じて表示特性に大きな影響を与える。また、ゲート電極と補助容量電極とのあいだに絶縁膜を設けて別々の膜で構成することにより前記問題を回避することも可能ではあるが、そのばあい、製造プロセスの増加により製造コストが高くなるので、実現するのはむずかしいという問題が生じる。また、図8で示した従来例では、ゲート電極により補助容量を形成するため、ゲート電極の配線容量が増大してしまい、液晶表示装置の大画面、高精細化を行ううえで信号遅延による表示特性が劣化するという大きな問題が生じる。

20

#### 【0008】

本発明はこのような従来技術の問題を解決するためになされたものであり、本発明の目的はアレイ基板の画素開口率が大きくでき、かつ表示特性の優れた量産性の高いアクティブマトリックス型液晶表示装置を提供することにある。

#### 【0009】

##### 【課題を解決するための手段】

前述の目的を達成するため本発明にかかる液晶表示装置は、TFTアレイ基板と、対向基板と、該TFTアレイ基板と該対向基板のあいだに挟持された液晶とからなり、該TFTアレイ基板上にはゲート配線、信号線、TFT、画素電極、ソース電極、ドレイン電極および補助容量配線が形成されてなる液晶表示装置であって、

30

該補助容量配線は該ゲート配線と前段のゲート配線とのあいだに、そのいずれとも平行に配設され、かつ、該画素電極の外周に沿って延在させて4つの延長部を有しており、

前記前段のゲート配線と、該前段のゲート配線側の前記延長部とにまたがるように2箇所でそれぞれ前記画素電極上または下に前記信号線と同一の金属膜が形成され、前記ドレイン電極と、該ゲート配線側の前記延長部が2箇所でそれぞれ重なり、

該画素電極の周囲が、該前段のゲート配線、前記信号線と同一の金属膜、前記延長部および前記ドレイン電極によって完全に遮光するように覆われている。また、前記信号線と同一の金属膜は、前記前段ゲート配線と該前段のゲート配線側の前記延長部との隙間の近傍にのみ配置される。

40

#### 【0010】

前記画素電極と前記4つの延長部のそれぞれとの重なり部分が第1の補助容量となるように形成することにより、補助容量形成部を遮光領域として使用でき、また、補助容量配線を画素中央部に配置できるので、ゲート配線と補助容量配線の短絡を防止できるので好ましい。

#### 【0011】

前記画素電極と前記前段のゲート配線との重なり部分が第2の補助容量となるように形成することにより、補助容量形成部を遮光領域として使用でき、また、補助容量配線を画素中央部に配置できるので、ゲート配線と補助容量配線の短絡を防止できるので好ましい。

50

## 【0012】

前記画素電極が前記前段のゲート配線上に拡張部分を有していると、拡張部分すなわち、画素電極と前段ゲート配線との重なり部分を補助容量の一部として積極的に利用しうるので好ましい。

## 【0013】

前記延長部が前記ソース配線の下部に拡張され、隣接する画素の補助容量配線の延長部と一緒に幅広に形成されていると、信号線の画素電極とのあいだから漏れ光を遮光できるので好ましい。

## 【0014】

前記ソース配線が、2層からなる2層構造であり、下層はアモルファスシリコン層であると、ソース電極から続く信号線下のアモルファスシリコン層の不連続部分をなくすことができ、その不連続部分での信号線断線を防止できるので好ましい。 10

## 【0016】

## 【発明の実施の形態】

以下、添付図を参照しつつ、本発明にかかるアクティブマトリックス型液晶表示装置について詳細に説明する。

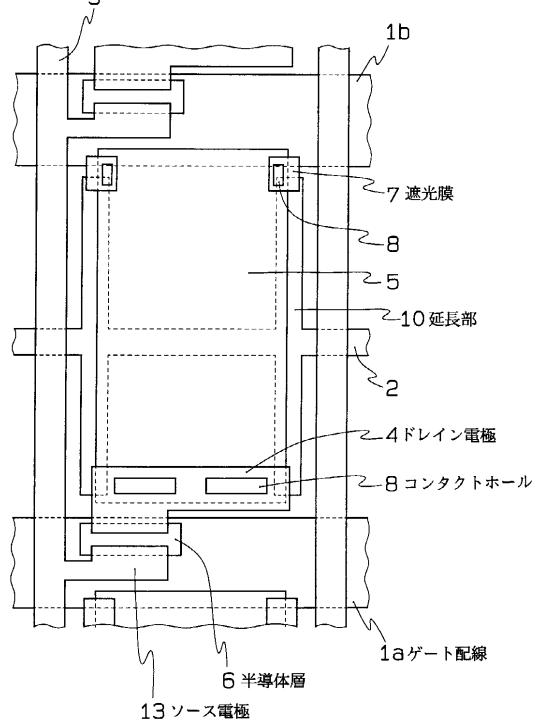

## 【0017】

## 実施の形態1

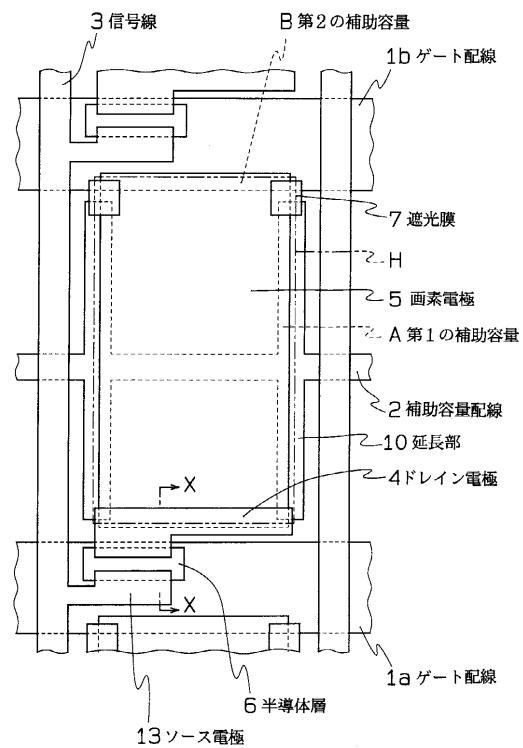

図1は、本発明の実施の形態1にかかるアクティブマトリックス型液晶表示装置に用いられるアレイ基板(図示せず)上の画素を示す平面構造説明図である。図において、1a 20

はゲート配線であり、1bは前段のゲート配線(以下、前段ゲート配線1bという)であり、2は補助容量配線であり、3は信号線であり、4はドレイン電極であり、5は画素電極であり、6はアモルファスシリコンなどからなる半導体層であり、7は金属膜からなる遮光膜であり、10は延長部であり、Hはブラックマトリックスの開口部であり、13はソース電極である。図中、二点鎖線で示した領域は、アレイ基板と一定の間隙を保ってアレイ基板に対向されている対向基板に設けたブラックマトリックスの開口部Hの位置を示している。

## 【0018】

本実施の形態では、アレイ基板上にマトリックス状に配置されたゲート配線1aと信号線3との交差点近傍のゲート配線1a上にアモルファスシリコンなどからなる半導体層6が形成されており、この半導体層6にソース電極13とドレイン電極4とが接続されてTFTが形成されている。ソース電極13は、信号線3から分岐して延設されており、ドレイン電極4は、画素電極5の外周のゲート配線に沿って、画素電極5の辺縁部分を覆うように形成されている。また、画素電極5は前段ゲート配線1bに重なり合うように形成され、前段ゲート配線1bに沿った画素電極5の外周は前段ゲート配線1bにより遮光される。補助容量配線2は、画素電極5の中央付近で画素電極の下層に、ゲート配線1aおよび1bに平行に配設され、さらに、この補助容量配線2は、この補助容量配線2から分岐して、隣接する前段のゲート配線1bの手前まで信号線3に沿って画素電極5の辺縁の一部に重なるようにして画素電極5の下層に延在させた延長部10を有する形で配設されている。ここで、画素電極5と補助容量配線2の延長部10との重なり部が第1の補助容量A 40

である。また、画素電極5と前段ゲート配線1bとの重なり部が第2の補助容量Bである。また、補助容量配線の延長部10の端部と前段ゲート配線とが、間隙をはさんで対向する対向部分の上層で延長部10の一部およびゲート配線の一部を覆うようにして遮光膜7が形成される。なお、のちに説明するように、前記遮光膜は信号線と同一の工程で形成される。

## 【0019】

以上説明したように、信号線用金属膜で遮光できるように画素電極5や補助容量配線2を構成することにより、画素電極5の外周は、補助容量配線の延長部10とドレイン電極4と遮光膜7とで完全に遮光されることになる。従来技術によれば、補助容量配線または前段ゲート配線といった1つの配線要素だけで遮光を行なっていたが、本発明では補助容量 50

配線と前段ゲート配線との両方と信号線用金属膜とを併用して画素電極外周の遮光を行なっている点が大きく異なる。また、カラーフィルタなどが形成された対向基板に形成されるブラックマトリックスの開口部Hをアレイ基板の開口部すなわち、補助容量配線の延長部10とドレイン電極4と遮光膜7とで囲まれた領域よりも大きくすることができ、アレイ基板の画素電極の開口部がカラーフィルタの設置により小さくならないようにすることによって、画素開口率を大きくすることができる。また、前段ゲート配線1bのみで補助容量を形成するばあいと比較して、前段ゲート配線1bと画素電極5との重なり部の幅を小さくすることができ、ゲート配線の配線容量を低減できるので、走査信号遅延による表示特性の劣化を軽減できる。

## 【0020】

10

また、ゲート配線1aや1bとは独立した補助容量配線2のみで補助容量を形成し、その補助容量配線2で画素電極5の外周を遮光するばあい、一般には補助容量配線とゲート配線の間隔を小さくしなければ大きな開口率はえられないが、本実施の形態では、画素電極5を前段ゲート配線1bの一部と重ねて形成し画素電極の前段ゲート配線に沿った外周部の遮光を行うので、補助容量配線2を画素電極5の中央部に配置することができる。したがって、補助容量配線2と前段ゲート配線との配線間の短絡を防止し、大きな開口率をうることが可能となる。

## 【0021】

つぎに、このような本発明の実施の形態にかかわるアレイ基板の製法を説明する。

## 【0022】

20

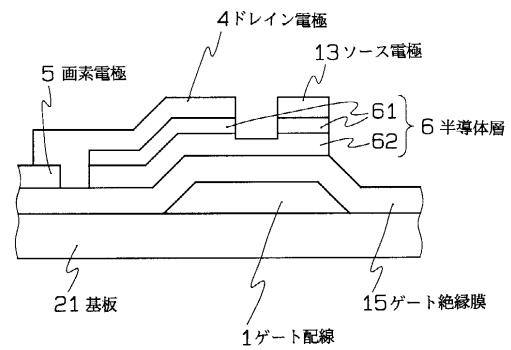

本実施の形態は、通常のTFT製造プロセスに適用可能であり、エッチストッパー型TFT、チャネルエッチ型TFTなどを用いたTFTアレイの製造プロセスに適用可能である。そこで、図1および図2を参照しつつ、たとえばチャネルエッチ型TFT製造プロセスにもとづいてアレイ基板の製法を示す。図2は、図1に示したTFT部のX-X線における断面説明図であり、15はゲート絶縁膜であり、21は基板であり、61はリンドープアモルファスシリコン層であり、62はアモルファスシリコン層であり、61と62とでTFTの半導体層6を構成しており、その他の符号は図1と共通である。まず、ガラスなどからなる基板21上にたとえば、クロムなどによりスピッタ法で金属膜を形成し、この金属膜をパターニングしてゲート配線1aや1b、補助容量配線2を形成する。つぎにプラズマCVD法でゲート絶縁膜15としてシリコン窒化膜を形成したのち、半導体層6としてアモルファスシリコン層62、リンドープアモルファスシリコン層61を成膜し、これらの半導体層6をパターニングしたのち、ITO膜をスピッタ法で成膜、パターニングし画素電極5を形成する。つぎに金属膜をスピッタ法で成膜し、パターニングすることでソース電極13とドレイン電極4とを形成したのち、ソース電極とドレイン電極とのあいだのリンドープアモルファスシリコン層をエッチングすることでTFTを形成する。遮光膜7は、ゲート配線と補助容量配線を遮光するように、延長部10とゲート配線1bとが間隙をはさんで対向する対向部分の上層で、延長部の一部およびゲート配線の一部を覆って形成される。

30

## 【0023】

このように、ガラス基板上にTFT、ゲート配線、ソース配線および画素電極などをアレイ状に作製して表示領域とするとともに、入力端子および駆動回路などを表示領域の周辺に配設する。このとき、それぞれの機能を発現させるために導電膜や絶縁膜を必要に応じてさらに配設する。また、対向基板上には対向電極を設けるとともにカラーフィルタ、ブラックマトリックスを設ける。

40

## 【0024】

TFTアレイ基板と対向基板とを作製したのち、のちに2枚の基板のあいだに液晶材料が注入されうるように所望の間隙を有する状態にして両基板をその周囲で貼りあわせたのち、2枚の基板のあいだの間隙に液晶材料を注入して液晶表示装置を作製する。

## 【0025】

以上のようにして、本実施の形態にかかわるアレイ基板およびこのアレイ基板を用いるア

50

クティブマトリックス型液晶表示装置を製造する。

【0026】

実施の形態2

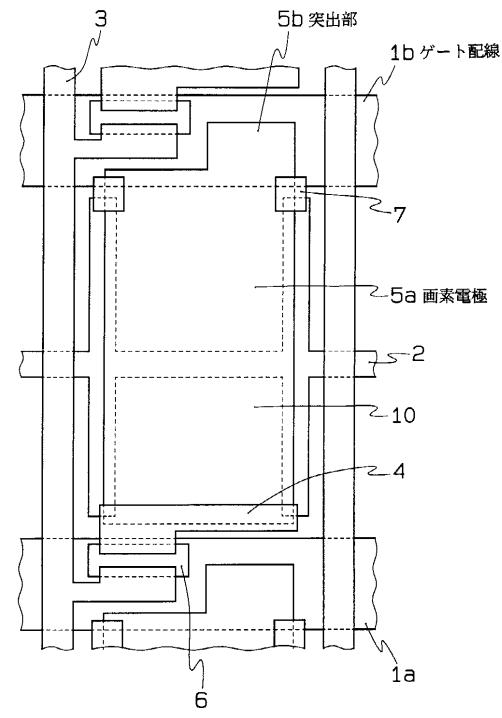

図3は本発明の実施の形態2にかかるアクティブマトリックス型液晶表示装置の画素を示す平面説明図である。図において、5aは本実施の形態における画素電極であり、5bは突出部であり、その他、図1および図2に示した要素と同じ要素には同じ符号を付して示した。

【0027】

本実施の形態では実施の形態1の画素平面構造において、画素電極5と前段ゲート配線1bとの重なり部の幅を大きく拡張した突出部5bを設けるようにして前段ゲート配線1bと画素電極5との重なり部を積極的に補助容量として用いるものである。なお、本実施の形態においては前段ゲート配線1bと画素電極5との重なり部を補助容量の一部として利用するため、走査信号中に補助容量配線用の信号電位を設ける必要がある。

10

【0028】

本実施の形態により、画素電極内における補助容量配線の占有率を低減でき、画素開口率を犠牲にすることなく、補助容量を形成することが可能となるため大きな開口率をうることが可能となる。また、補助容量が前段ゲート配線1bと補助容量配線との2つの要素で形成されるため、実施の形態1で示したばあいよりもゲート配線の配線容量は増加するが、前段ゲート配線のみで補助容量を形成するばあいと比較して、ゲート配線の配線容量は低減されるので、信号遅延による表示特性の劣化を軽減できる。

20

【0029】

本実施の形態は、実施の形態1と同様に、通常のTFT製造プロセスに適用可能であり、エッチストッパー型TFT、チャネルエッチ型TFTなどを用いたTFTアレイの製造プロセスに適用可能である。本実施の形態においては、画素電極5aを形成するばあいのパターンを変更して、前段のゲート配線1bとの重なり部を大きくとるようにすることのほかは、実施の形態1のばあいと同様にアレイ基板を製造することができる。

【0030】

実施の形態3

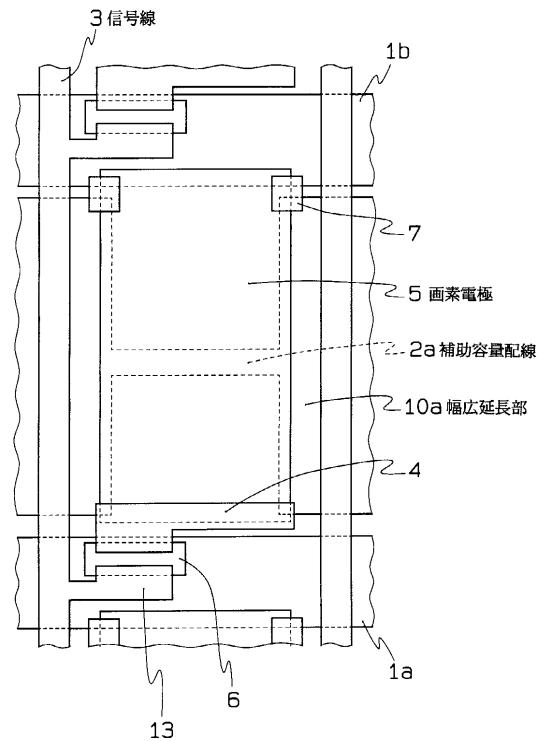

図4は本発明の実施の形態3にかかるアクティブマトリックス型液晶表示装置の画素を示す平面説明図である。図において、2aは補助容量配線であり、10aは幅広延長部であり、その他、図1および図2に示した要素と同じ要素には同じ符号を付して示した。

30

【0031】

本実施の形態は、実施の形態1で示した画素平面構造において、信号線3に沿った画素電極5の外周部に延在させて形成した延長部10を、さらに信号線3下にまで拡張部分をして延在させ、隣接する画素の補助容量配線の延長部と一体に幅広に形成した幅広延長部10aを有する補助容量配線2aとしたものである。これにより、信号線3と画素電極5とのあいだから漏れ光をアレイ基板上で遮光することができ、カラーフィルタに形成されるブラックマトリックスの開口部をさらに大きくすることが可能となる。本実施の形態のばあいのように補助容量配線2aを形成すると、とくに基板に対してある角度をもって入射する光の遮光に対して有効である。

40

【0032】

本実施の形態も、通常のTFT製造プロセスに適用可能であり、エッチストッパー型TFT、チャネルエッチ型TFTなどを用いたTFTアレイの製造プロセスに適用可能である。本実施の形態においては、補助容量配線を形成するばあいのパターンを変更して、実施の形態1のばあいの延長部10を隣接する画素の補助容量配線の延長部と一体に幅広にできるようにすることのほかは実施の形態1のばあいと同様にアレイ基板を製造することができる。

【0033】

本実施の形態は実施の形態1、2の画素平面構造に対して適用することが可能である。

【0034】

50

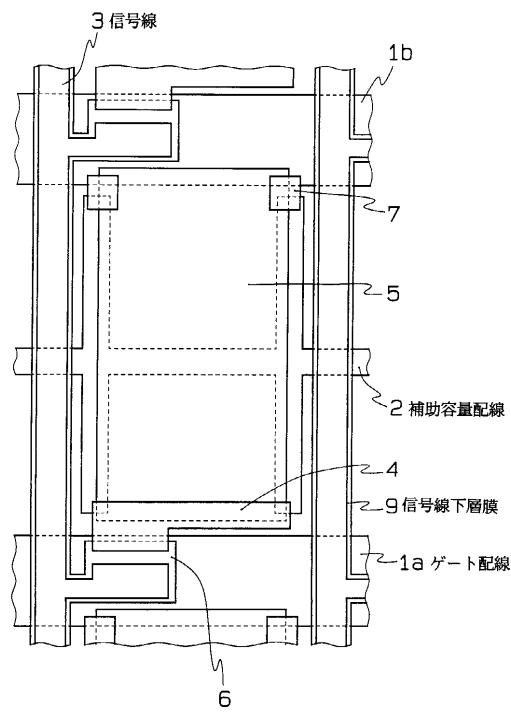

#### 実施の形態 4

図5は本発明の実施の形態4にかかるアクティブマトリックス型液晶表示装置の画素を示す平面説明図である。図において、9は信号線下層膜であり、その他、図1に示した要素と同じ要素には同じ符号を付して示した。

##### 【0035】

本実施の形態は、実施の形態1で示した画素平面構造において信号線を、信号線3の下層かつゲート絶縁膜の上層に、TFTのソース電極と連続してアモルファスシリコン層を形成する。すなわち、信号線としては2層となるように、もう1層の信号線下層膜9をアモルファスシリコンで形成したものであり、TFT部に形成される半導体層6のアモルファスシリコン層62をTFT部から連続して信号線3下に延在させて形成するものである。本実施の形態にかかるアレイ基板により、信号線3と補助容量配線2との重なり部の容量、信号線3、ゲート配線1aとの重なり部の容量を低減することが可能である。ソース電極から連続する信号線3下のアモルファスシリコン層の不連続部分をなくすることで、アモルファスシリコン層の不連続部段差における信号線の断線を防止できる。

10

##### 【0036】

本実施の形態も、通常のTFT製造プロセスに適用可能であり、エッチストッパー型TFT、チャネルエッチ型TFTなどを用いたTFTアレイの製造プロセスに適用可能である。本実施の形態においては、ゲート絶縁膜の形成後に、TFTの半導体層を形成する際のパターンを変更して、信号線の配設パターンにほぼ相似のパターンとして半導体層を形成することのほかは実施の形態1のばあいと同様にアレイ基板を製造することができる。

20

##### 【0037】

本実施の形態は実施の形態1～3のいずれの画素平面構造に対しても適用可能である。

##### 【0038】

#### 実施の形態 5

図6は本発明の実施の形態5にかかるアクティブマトリックス型液晶表示装置の画素を示す平面説明図である。図において、図1に示した要素と同じ要素には同じ符号を付して示した。

##### 【0039】

本実施の形態は、信号線3やドレイン電極4の上層のパッシベーション膜を設けたことにより、所望の位置にパッシベーション膜を貫通するコンタクトホール8を設けたものである。すなわち、アレイ基板上にマトリックス状に配置されたゲート配線1aと信号線3との交差点近傍のゲート配線1a上にアモルファスシリコンなどからなる半導体層6が形成され、半導体層6上に信号線3から伸びたソース電極13と画素電極5の外周のゲート配線1aに沿った部分を覆うように形成されたドレイン電極4を配置して、コンタクトホール8を介してドレイン電極4と画素電極5を接続することでTFTが形成される。補助容量配線2は実施の形態1のばあいと同様に形成され、画素電極5と補助容量配線2および延長部10との重なり部により補助容量が形成される。さらに、遮光膜7も実施の形態1と同様に形成され、本実施の形態においてはコンタクトホール8で画素電極5に接続される。なお、前記遮光膜7は信号線3と同一の工程で形成される。また、画素電極5は前段ゲート配線1bに重なり合うように形成され、前段ゲート配線に沿った画素電極の外周は前段ゲート配線により遮光される。

30

##### 【0040】

以上説明したように、画素電極5の外周は、補助容量配線2とドレイン電極4と遮光膜7で完全に遮光され、カラーフィルター基板に形成されるブラックマトリックスの開口部12をアレイ基板の開口部よりも大きくすることができ、アレイ基板の画素電極の開口部がカラーフィルタの設置により小さくならないようにすることで、画素開口率を大きくすることが可能となる。

40

##### 【0041】

本実施の形態は画素電極5の膜をパッシベーション膜上すなわち、アレイ基板の最上層に形成する製造プロセスに本発明を適用した例である。すなわち、信号線と画素電極とを別

50

層にして画素電極を最上層に形成する。このばあいドレイン電極と画素電極とは、コンタクトホールを介して接続される。この特徴のほかは実施の形態1のばあいと同様である。したがって、エッチストッパー型TFT、チャネルエッチ型TFTなどを用いたTFTアレイの製造プロセスにも適用可能である。すなわち、金属膜をスパッタ法により成膜しパターニングして信号線3、ドレイン電極4を形成したのち、その上に絶縁膜を形成しパッセーション膜を形成する。さらに、ドレイン電極4上にコンタクトホール8をパターニングし、その部分の絶縁膜を除去したのち、ITO膜をスパッタ法で成膜し、パターニングし、画素電極5を形成することで本実施の形態のアクティブマトリックス型液晶表示装置のアレイ基板が製造可能であり、さらにカラーフィルタと重ね合せて用いることでアクティブマトリックス型液晶表示装置がえられる。

10

#### 【0042】

本実施の形態は実施の形態1～4で示したいずれの画素の平面構造に対しても適用可能である。

#### 【0043】

#### 【発明の効果】

本発明によれば、画素電極を前段ゲート配線に重ね合せて形成し、補助容量配線を画素電極中央に配置し補助容量配線の一部を信号線に沿った画素電極の外周に延在させる形で形成し、かつ前段ゲート配線と補助容量電極の画素電極の外周に延在させた部分のあいだに金属膜を形成し、画素電極の外周を完全に遮光することで、ゲート配線と補助容量配線間の短絡不良を発生させることなく、画素開口率を大きくすることができる。また、ゲート配線の時定数増加による信号遅延が引き起こす表示特性の劣化を低減し、カラーフィルタに形成されるブラックマトリックスの開口部を補助容量配線、前段ゲート配線、金属膜により遮光された画素電極外周の内径より大きくし、アレイ基板の開口部がカラーフィルタの設置により小さくならないようにすることが可能となり、画素開口率の大きなアクティブマトリックス型液晶表示装置を量産性を高くして提供することができる。

20

#### 【図面の簡単な説明】

【図1】本発明の実施の形態1にかかわる画素を示す平面説明図である。

【図2】図1に示した画素のX-X線断面説明図である。

【図3】本発明の実施の形態2にかかわる画素を示す平面説明図である。

【図4】本発明の実施の形態3にかかわる画素を示す平面説明図である。

30

【図5】本発明の実施の形態4にかかわる画素を示す平面説明図である。

【図6】本発明の実施の形態5にかかわる画素を示す平面説明図である。

【図7】従来例の画素を示す平面説明図である。

【図8】従来例の画素を示す平面説明図である。

#### 【符号の説明】

1 a ゲート配線

1 b 前段ゲート配線

2、2 a 補助容量配線

3 信号線

4 ドレイン電極

40

5、5 a 画素電極

5 b 突出部

6 半導体層

7 遮光膜

8 コンタクトホール

10 延長部

10 a 幅広延長部

13 ソース電極

【 図 1 】

【 図 2 】

【図3】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(56)参考文献 特開平06-308533(JP,A)

特開平05-181159(JP,A)

特開平06-294971(JP,A)

特開平09-090420(JP,A)

特開平09-074203(JP,A)

特開平08-313933(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

G02F 1/1343

G09F 9/30

H01L 21/336

H01L 29/786