(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3649878号

(P3649878)

(45) 発行日 平成17年5月18日(2005.5.18)

(24) 登録日 平成17年2月25日(2005.2.25)

(51) Int.CI.<sup>7</sup>

F 1

H 04 L 27/22

H 04 L 27/22

F

請求項の数 4 (全 16 頁)

(21) 出願番号 特願平9-287345

(22) 出願日 平成9年10月20日(1997.10.20)

(65) 公開番号 特開平11-127207

(43) 公開日 平成11年5月11日(1999.5.11)

審査請求日 平成15年7月15日(2003.7.15)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 柴田 学

宮城県仙台市青葉区一番町1丁目2番25

号 富士通東北ディジタル・テクノロジ株

式会社内

審査官 藤井 浩

(56) 参考文献 特開平06-232934 (JP, A)

特開平07-177190 (JP, A)

最終頁に続く

(54) 【発明の名称】デジタル無線通信装置の検波方法及びその回路

## (57) 【特許請求の範囲】

## 【請求項1】

P S K変調信号を受信するデジタル無線通信装置の検波方法において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波方法であって、

前記再生クロックを中心とする前後の複数ポイントのサンプリングは、前記P S K変調信号の周期で離散的に行い、

前記位相データの合成は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする

ことを特徴とするデジタル無線通信装置の検波方法。

## 【請求項2】

請求項1記載のデジタル無線通信装置の検波方法において、

前記位相データの合成は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均して得る

ことを特徴とするデジタル無線通信装置の検波方法。

## 【請求項3】

P S K変調信号を受信するデジタル無線通信装置の検波回路において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化

データから各シンボルの位相データを合成する合成手段を有し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波回路であって、

前記再生クロックを中心とする前後の複数ポイントは、前記PSK変調信号の周期で離散的に行い、

前記位相データの合成手段は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする頻度判定手段を有する

ことを特徴とするデジタル無線通信装置の検波回路。

#### 【請求項4】

請求項3記載のデジタル無線通信装置の検波回路において、

前記位相データの合成手段は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均する重み付け平均手段を有する

ことを特徴とするデジタル無線通信装置の検波回路。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明はデジタル無線通信装置の検波方法及びその回路に関し、PSK(フェイズシフトキーイング)変調信号を受信するデジタル無線通信装置の検波方法及びその回路に関する。

##### 【0002】

##### 【従来の技術】

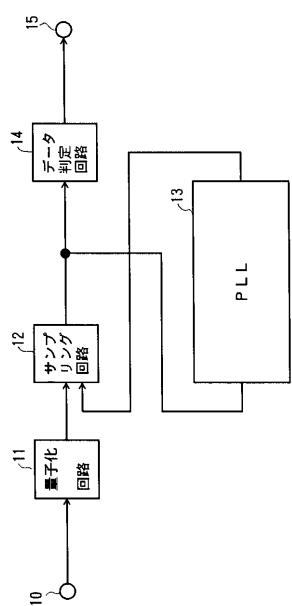

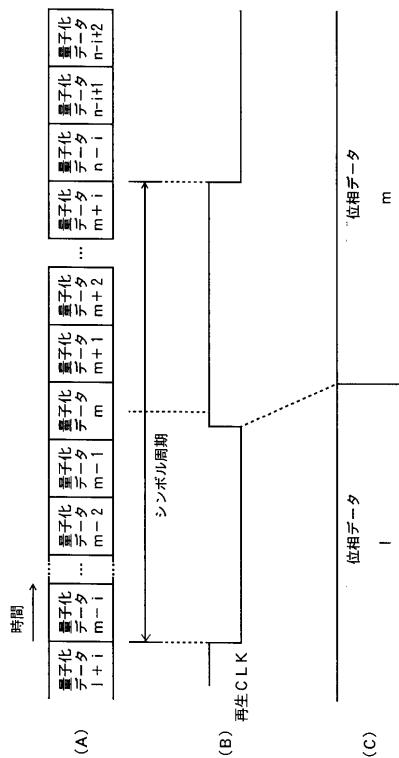

図13は従来のデジタル無線通信装置の検波回路の一例のブロック図を示す。同図中、端子10にはデジタル無線通信装置で受信した、例えばPSK(フェイズシフトキーイング)信号の中間周波信号(IF)が入来し量子化回路11に供給される。量子化回路11では中間周波信号の位相を量子化して図14(A)に示すような位相の量子化データをサンプリング回路12に供給する。サンプリング回路12にはPLL(フェーズロックループ)13から図14(B)に示すような再生クロックが供給されており、サンプリング回路12は再生クロックの立ち上がりエッジで上記の量子化データをサンプリングして図14(C)に示す位相の量子化データをPLL13及びデータ判定回路14に供給する。

##### 【0003】

PLL13はサンプリングされた量子化データに同期した再生クロックを生成する。データ判定回路14はサンプリングされた位相の量子化データから位相に応じた複数ビットのデータを判定することによりPSK復調(検波)を行い、得られたデータを端子15から出力する。

##### 【0004】

##### 【発明が解決しようとする課題】

従来回路は、再生クロックの1周期に1点のサンプリングポイントで位相の量子化データをサンプリングして、このサンプリングされた1周期に1点の量子化データを判定しているため、この1点のサンプリングポイントで突発的な位相ずれが発生した場合には、データの判定を誤ってしまうという問題があった。

##### 【0005】

また、前段にリミッタを設けて振幅制限し位相のみを再生に用いる方式では、リミッタがない場合に比してアイパターの開口点が狭くなり、再生クロックによるサンプリングポイントが厳密でなければならず、サンプリングポイントが多少でも前後にずれた状態では良好な検波を行うことができない。また、デジタル無線通信装置の受信能力や内部で発生するスプリアスの影響があると、アイパターがぼやけるため良好な検波を行うことができず、データの判定を誤ってしまうおそれがあるという問題があった。

##### 【0006】

本発明は、上記の点に鑑みなされたもので、データの判定を誤るおそれの少ないデジタル無線通信装置の検波方法及び回路を提供することを目的とする。

10

20

30

40

50

## 【0007】

## 【課題を解決するための手段】

請求項1に記載の発明は、P S K変調信号を受信するデジタル無線通信装置の検波方法において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波方法であって、

前記再生クロックを中心とする前後の複数ポイントのサンプリングは、前記P S K変調信号の周期で離散的に行い、

前記位相データの合成は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする。

10

## 【0008】

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターーンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止できる。

20

## 【0013】

請求項2に記載の発明は、請求項1記載のデジタル無線通信装置の検波方法において、

前記位相データの合成は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均して得る。

## 【0014】

これにより、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成できる。

30

請求項3に記載の発明は、P S K変調信号を受信するデジタル無線通信装置の検波回路において、

再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成する合成手段を有し、

合成位相データからデータ判定を行うデジタル無線通信装置の検波回路であって、

前記再生クロックを中心とする前後の複数ポイントは、前記P S K変調信号の周期で離散的に行い、

前記位相データの合成手段は、前記複数の位相の量子化データうち最大頻度の量子化データを前記位相データとする頻度判定手段を有する。

40

## 【0015】

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターーンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により1点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、請求項1の発明を実現できる。

50

## 【0021】

請求項4記載の発明は、請求項3記載のデジタル無線通信装置の検波回路において、

前記位相データの合成手段は、前記複数の位相の量子化データに最大頻度の量子化データが複数種類ある場合、前記再生クロックを中心とする前後の複数ポイントで、前記再生クロックより離れるほど減少する重み付けを行って平均する重み付け平均手段を有する。

## 【0022】

これにより、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成でき、請求項2の発明を実現できる。 10

## 【0023】

## 【発明の実施の形態】

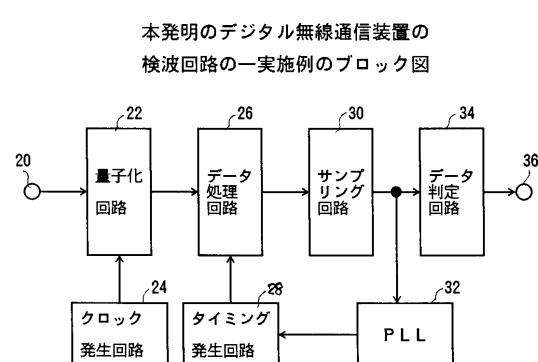

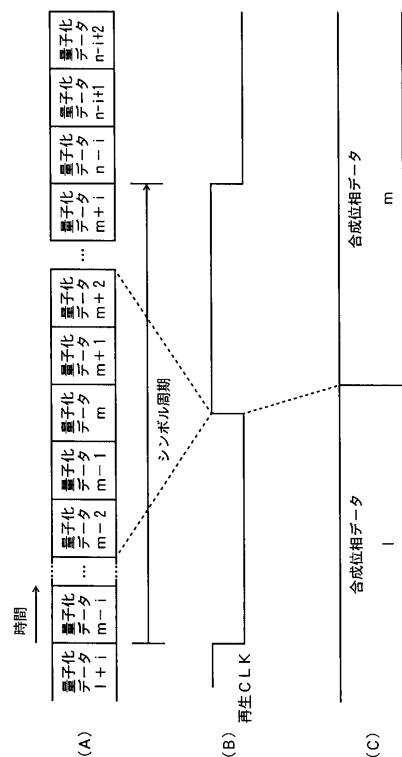

図1は本発明のデジタル無線通信装置の検波回路の一実施例のブロック図を示す。同図中、端子20にはデジタル無線通信装置で受信した、例えばPSK(フェイズシフトキーイング)信号の中間周波信号(IF)が入来し量子化回路22に供給される。量子化回路22ではクロック発生回路24から供給される高速クロックを用いて中間周波信号を量子化して図2(A)に示すような位相の量子化データを得て、時系列の量子化データをデータ処理回路(合成手段)26に供給する。

## 【0024】

データ処理回路26は図2(B)に示す再生クロックの立ち上がりを中心として前後の複数の量子化データm-2,m-1,m,m+1,m+2から図2(C)に示す位相データmを合成してサンプリング回路30に供給する。タイミング発生回路28はクロック及びタイミング信号を生成してデータ処理回路26及びサンプリング回路30それぞれに供給している。サンプリング回路30はタイミング発生回路28よりのシンボルクロック周波数のタイミング信号によって合成位相データをラッチしてPLL(フェーズロックループ)32及びデータ判定回路34に供給する。 20

## 【0025】

PLL32はサンプリングされた合成位相データに同期して図2(B)に示すようなシンボルクロック周波数の再生クロックを生成し、タイミング発生回路28に供給する。タイミング発生回路28はこの再生クロックを基準としてクロック及びタイミング信号を生成する。データ判定回路34はサンプリングされた合成位相データから位相に応じた複数ビットのデータを判定することによりPSK復調を行い、得られたデータを端子36から出力する。 30

## 【0026】

ここで、PSKのシンボル周波数、つまり再生クロック周波数は例えば21KHzであり、中間周波信号の周波数は例えば450KHzであり、量子化周波数は例えば14.4MHzである。

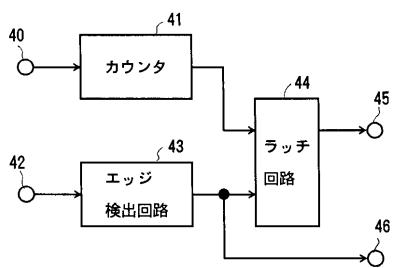

図3は量子化回路22の一実施例のブロック図を示す。同図中、カウンタ41には端子40を介してクロック発生回路24より、例えば周波数14.4MHzのクロックが供給され、カウンタ41はこのクロックをカウントしてラッチ回路44に供給する。また、エッジ検出回路43は端子42から供給される中間周波信号の立ち上がりエッジを検出してラッチ回路44に供給する。ラッチ回路44はエッジ検出信号の供給時にカウンタ41のカウント値を位相の量子化データとしてラッチして端子45より出力する。また、エッジ検出信号が端子46より出力される。 40

## 【0027】

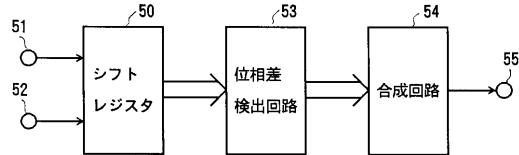

データ処理回路26は図4又は図5又は図6に示す構成である。図4はデータ処理回路26の第1方式の概略ブロック図を示す。同図中、端子51,52から入来する位相の量子化データ、タイミング発生回路28からのタイミング信号それぞれはシフトレジスタ50に供給され、シフトレジスタ50内をシフトされる。シフトレジスタ50の各段の出力する位相の量子化データは位相差検出回路(位相差検出手段)53に供給され各量子化データ

タの位相差が検出される。これらの各位相差データは合成回路（ベクトル合成手段）54に供給され、ここでベクトル合成により合成位相データが得られ、端子55から出力される。

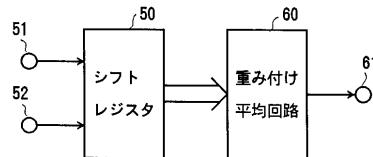

【0028】

図5はデータ処理回路26の第2方式の概略ブロック図を示す。同図中、端子51, 52から入来する位相の量子化データ、タイミング発生回路28からのタイミング信号それぞれシフトレジスタ50に供給され、シフトレジスタ50内をシフトされる。シフトレジスタ50の各段の出力する位相の量子化データは重み付け平均回路（重み付け平均手段）60に供給され各量子化データの重み付けした平均値が算出される。この量子化データの重み付け平均値は合成位相データとして端子61から出力される。

10

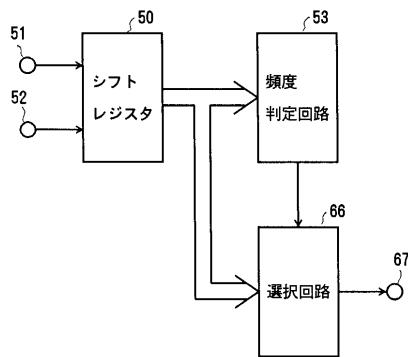

【0029】

図6はデータ処理回路26の第3の概略ブロック図を示す。同図中、端子51, 52から入来する位相の量子化データ、タイミング発生回路28からのタイミング信号それぞれシフトレジスタ50に供給され、シフトレジスタ50内をシフトされる。シフトレジスタ50の各段の出力する位相の量子化データは頻度判定手段としての頻度判定回路65及び選択回路66に供給される。頻度判定回路65はこれらの各量子化データから頻度の最も高い量子化データを検出し、検出した量子化データを選択するための制御信号を選択回路66に供給する。これによって、選択回路66は頻度の最も高い量子化データを選択し、選択された量子化データが合成位相データとして端子67から出力される。

【0030】

20

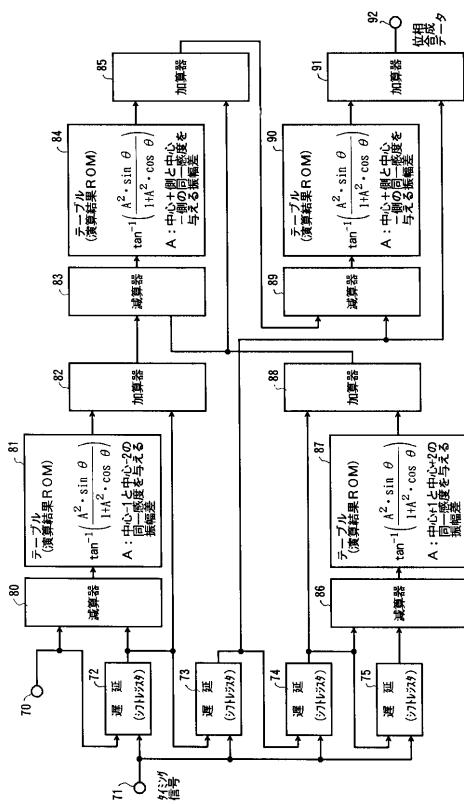

図7はデータ処理回路26の第1方式の一実施例のブロック図を示す。同図中、端子70, 71には量子化回路22から位相の量子化データ、タイミング発生回路28からのタイミング信号それがが入来し、シフトレジスタ50を構成する遅延素子72～75を位相の量子化データが順次シフトされる。ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの遅延素子73の出力量子化データを中心として、遅延素子74, 75の出力量子化データを中心+1, 中心+2と呼び、遅延素子72の出力量子化データを中心-1、端子70の入力量子化データを中心-2と呼ぶ。

【0031】

減算器80は中心-1と中心-2の量子化データの減算を行って減算値をテーブル81に供給する。テーブル81にはに対応して(1)式により得られる位相差が予め格納されている。

30

【0032】

【数1】

$$\tan^{-1} \left( \frac{A^2 \cdot \sin \theta}{1 + A^2 \cdot \cos \theta} \right) \quad \dots (1)$$

40

【0033】

但し、Aは中心-1と中心-2とに同一感度を与える振幅差としての定数。この(1)式について説明するに、長さA<sub>1</sub>位相<sub>1</sub>のベクトルと、長さA<sub>2</sub>位相<sub>2</sub>のベクトルとを合成したベクトルの位相は(2)式で表される。

【0034】

【数2】

$$\tan^{-1} \left( \frac{A_1 \cdot \sin \theta_1 + A_2 \cdot \sin \theta_2}{A_1 \cdot \cos \theta_1 + A_2 \cdot \cos \theta_2} \right) \quad \dots \quad (2)$$

## 【0035】

(2)式では4つの変数があるため、計算が複雑である。このため、 $A_1$ と $A_2$ との比を $A$ とし、 $\theta_1$ と $\theta_2$ との差を $\theta$ とすると、合成ベクトルの位相 $\theta_G$ は(3)式で表す。

## 【0036】

## 【数3】

10

$$\theta_G = \theta_1 + \tan^{-1} \left( \frac{A^2 \cdot \sin \theta}{1 + A^2 \cdot \cos \theta} \right) \quad \dots \quad (3)$$

## 【0037】

(3)式では変数が2つである上に、 $A$ の値がある程度大きくなると位相差の値が小さくなり影響が小さくなるため $A$ の範囲を限定できる。本実施例では $A$ の値として、中心からずれた位相で中心と同一のレベル(同一感度)を得る振幅を考慮している。これは中心が最も良好で、中心から位相がずれた位置でのレベルの劣化に応じて影響を小さくするためであり、即ち中心から位相がずれた位置でのレベルの大きさを表すものである。この(3)式に基づいて(1)式の演算を行う。

20

## 【0038】

減算器80の出力する位相差は加算器82で遅延素子73の出力する中心の量子化データに加算されてベクトル合成された後、減算器83に供給される。また、減算器86は中心+1と中心+2の量子化データの減算を行って減算値 $\Delta\theta$ をテーブル87に供給する。テーブル87には $\Delta\theta$ に対応して(1)式により得られる位相差が予め格納されている。但し、 $A$ は中心+1と中心+2とに同一感度を与える振幅差としての定数である。テーブル87からは(1)式による位相差が得られ、この位相差は加算器88で遅延素子74の出力する中心+1の量子化データに加算されてベクトル合成された後、減算器83に供給される。

30

## 【0039】

減算器83は加算器82, 88出力の量子化データの減算を行って減算値 $\Delta\theta$ をテーブル84に供給する。テーブル84には $\Delta\theta$ に対応して(1)式により得られる位相差が予め格納されている。但し、 $A$ は中心+側と中心-側とに同一感度を与える振幅差としての定数である。テーブル84からは(1)式による位相差が得られ、この位相差は加算器85で加算器88の出力する中心-側の量子化データに加算されてベクトル合成された後、減算器89に供給される。

40

## 【0040】

減算器89は加算器85, 遅延素子73出力の量子化データの減算を行って減算値 $\Delta\theta$ をテーブル90に供給する。テーブル90には $\Delta\theta$ に対応して(1)式により得られる位相差が予め格納されている。但し、 $A$ は中心+側と中心-側とに同一感度を与える振幅差としての定数である。テーブル90からは(1)式による位相差が得られ、この位相差は加算器91で遅延素子73の出力する中心の量子化データに加算されてベクトル合成された後、合成位相データとして端子92から出力される。上記の減算器80, 83, 86, 89及びテーブル81, 84, 87, 90が位相差検出回路53に対応し、加算器82, 85, 88, 91が合成回路54に対応する。

## 【0041】

50

この実施例では、合成する量子化データの一方を基準として他方の位相差を求め、その位相差に応じたテーブルを参照して合成後の位相差を得て、基準の量子化データに合成後の位相差を足し込むことで合成位相差を求めている。これにより、簡単な演算で正確な合成位相差求めることができる。

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減できる。この実施例は多少回路規模が大きくなるものの、各信号の合成により等価的にエネルギーの増加を図ることができ、C/Nが改善され、良好な特性を得ることができる。

10

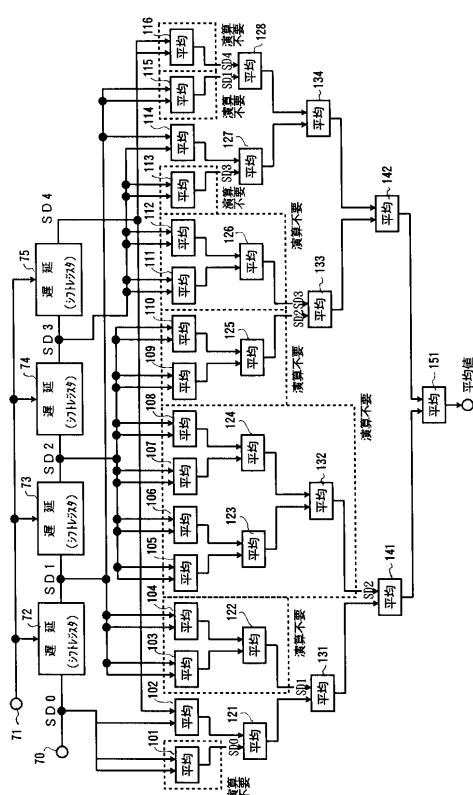

#### 【0042】

図8はデータ処理回路26の第2方式の一実施例のブロック図を示す。同図中、端子70, 71には量子化回路22から位相の量子化データ、タイミング発生回路28からのタイミング信号それぞれが入来し、シフトレジスタ50を構成する遅延素子72～75を位相の量子化データが順次シフトされる。ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの端子71の入力量子化データをSD0とし、遅延素子72～75それぞれの出力する量子化データをSD1～SD4とする。

#### 【0043】

平均回路101は2つの量子化データSD0の平均を取り、平均回路102は2つの量子化データSD0, SD4の平均を取り、平均回路103, 104それぞれは2つの量子化データSD1の平均を取り、平均回路105～110それぞれは2つの量子化データSD2の平均を取り。平均回路111～113それぞれは2つの量子化データSD3の平均を取り、平均回路114は2つの量子化データSD3, SD4の平均を取り、平均回路115は2つの量子化データSD1の平均を取り、平均回路116は2つの量子化データSD4の平均を取り。

20

#### 【0044】

平均回路121は2つの平均回路101, 102出力の量子化データの平均を取り、平均回路122は2つの平均回路103, 104出力の量子化データの平均を取り、平均回路123は2つの平均回路105, 106出力の量子化データの平均を取り、平均回路124は2つの平均回路107, 108出力の量子化データの平均を取り、平均回路125は2つの平均回路109, 110出力の量子化データの平均を取り、平均回路126は2つの平均回路111, 112出力の量子化データの平均を取り、平均回路127は2つの平均回路113, 114出力の量子化データの平均を取り、平均回路128は2つの平均回路115, 116出力の量子化データの平均を取り。

30

#### 【0045】

更に、平均回路131は2つの平均回路121, 122出力の量子化データの平均を取り、平均回路132は2つの平均回路123, 124出力の量子化データの平均を取り、平均回路133は2つの平均回路125, 126出力の量子化データの平均を取り、平均回路134は2つの平均回路127, 128出力の量子化データの平均を取り。更に、平均回路141は2つの平均回路131, 132出力の量子化データの平均を取り、平均回路142は2つの平均回路133, 134出力の量子化データの平均を取り、平均回路151は2つの平均回路141, 142出力の量子化データの平均を取り、合成位相データとして端子152より出力する。

40

#### 【0046】

ここで、平均回路102, 103～113, 115, 116, 122～126, 132は同一データを平均しているため、実際には不要である。この実施例では平均回路102～116に供給する量子化データのうち中心の量子化データSD2の数を多くして大きな重み付けを行い、次に中心に近い量子化データSD1, SD3の数を減らし重み付けを減らし、更に中心から遠い量子化データSD0, SD4の数を減らし重み付けを減らしている

50

。

**【0047】**

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減できる。この実施例は簡易的、かつ、柔軟な重み付けを行う回路構成とすることができます。

**【0048】**

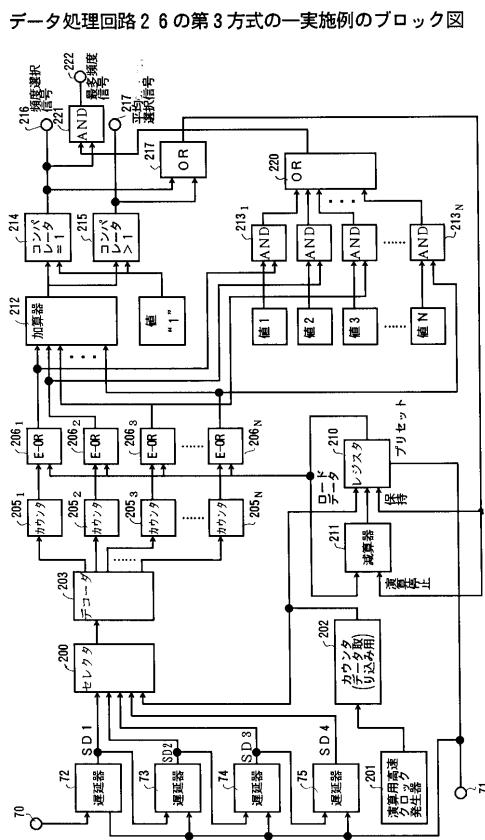

図9はデータ処理回路26の第3方式の一実施例のブロック図を示す。同図中、端子70, 71には量子化回路22から位相の量子化データ、タイミング発生回路28からのタイミング信号それがが入来し、シフトレジスタ50を構成する遅延素子72～75を位相の量子化データが順次シフトされる。ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子73から出力されるタイミングでの遅延素子72～75それぞれの出力する量子化データをSD1～SD4とする。この量子化データSD1～SD4は頻度判定回路65を構成するセレクタ200に供給される。

10

**【0049】**

演算用高速クロック発生器201は量子化データSD1～SD4を選択するために、シンボルクロックの4倍の周波数のクロックを発生してカウンタ202に供給する。カウンタ202は4進のカウンタであり、1～4のカウント値をセレクタ200に供給する。セレクタ200はこのカウント値に対応する量子化データSD1～SD4のいずれかを選択してデコーダ203に供給する。

20

**【0050】**

デコーダ203は供給される量子化データSD1～SD4それを順次デコードして、量子化データの値に応じた端子からカウンタ205<sub>1</sub>～205<sub>N</sub>のいずれかに値1の信号を出力し、他の端子から残りのカウンタ205<sub>1</sub>～205<sub>N</sub>に値0の信号を出力する。なお、本実施例では量子化データの値は0～32であり、N=33である。カウンタ205<sub>1</sub>～205<sub>N</sub>それぞれは量子化のタイミング信号の入来毎にリセットされて、値1の信号を供給されたときカウントアップを行い、それぞれのカウント値をイクスクルーシブオア回路206<sub>1</sub>～206<sub>N</sub>それぞれに供給する。

30

**【0051】**

レジスタ210は量子化のタイミング信号の供給によりカウンタ202の出力するカウント値をプリセットされ、その後、減算器211により値を1ずつ減じる。これによりレジスタ210の出力値はカウンタ202の出力するカウント値を上限として1ずつ値が減少し、この値はイクスクルーシブオア回路206<sub>1</sub>～206<sub>N</sub>それぞれに供給される。なお、遅延素子72～75それぞれの遅延時間をxとし、遅延素子72～75の個数をyとしたとき、減算器211の減算周期はx/(y+1)以下である。

**【0052】**

イクスクルーシブオア回路206<sub>1</sub>～206<sub>N</sub>それぞれは供給される2つの値が一致したときにのみ値1の信号を出力する。イクスクルーシブオア回路206<sub>1</sub>～206<sub>N</sub>それぞれの出力値は加算器212及びアンド回路213<sub>1</sub>～213<sub>N</sub>に供給され、加算器212はこれらの値を加算してコンパレータ214, 215それぞれに供給する。

40

**【0053】**

コンパレータ214, 215それぞれには値1が供給されている。加算器212出力が1のときコンパレータ214は値1の頻度選択信号を生成して端子216から出力し、加算器212出力が1を超えるときコンパレータ215は値1の平均選択信号を生成して端子216から出力する。つまり、カウンタ205<sub>1</sub>～205<sub>N</sub>のうちカウント値がレジスタ210の値と一致するカウンタの数が1のとき頻度選択信号が出力され、2以上のとき平均選択信号が出力される。この頻度選択信号又は平均選択信号はオア回路217を介してレジスタ210, 減算器211に供給され、レジスタ210に値を保持させると共に、減算器211の演算を停止させる。

50

**【0054】**

アンド回路 $213_1 \sim 213_N$  それぞれには量子化データの値 $1 \sim N$ が供給されており、イクスクルーシブオア回路 $206_1 \sim 206_N$  の出力値が値1のとき、対応する量子化データの値が出力されてオア回路 $220$ を介しアンド回路 $221$ に供給され、アンド回路 $221$ は頻度選択信号が値1のとき、この量子化データの値を合成位相データとして端子 $222$ より出力する。上記のセレクタ $200$ からアンド回路 $221$ が頻度判定回路 $65$ を構成している。

**【0055】**

これにより、量子化データ $SD1 \sim SD4$ が例えば全て「16」の場合、カウンタ $205_1$  ( $1 < I < N$ ) のカウント値が4となり、イクスクルーシブオア回路 $206_1$  出力が1 10 、加算器 $212$ 出力が1となって頻度選択信号が出力され、アンド回路 $213_1$  から出力される量子化データの値「16」が端子 $222$ より出力される。量子化データ $SD1 \sim SD4$ が例えば「16, 16, 17, 17」の場合、カウンタ $205_1$  ( $1 < I < N$ ) のカウント値が2、カウンタ $205_J$  ( $I < J < N$ ) のカウント値が2となり、イクスクルーシブオア回路 $206_1, 206_J$  出力が1、加算器 $212$ 出力が2となって平均選択信号が出力され、アンド回路 $213_1$  から出力される量子化データの値は端子 $222$ から出力されない。

**【0056】**

このように、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターんがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減できる。この実施例は小さい回路規模で構成することが可能であり、この回路の追加による品質の劣化が少ない。また、頻度判定のサンプル数を増加することでよりいっそうの改善が可能となる。 20

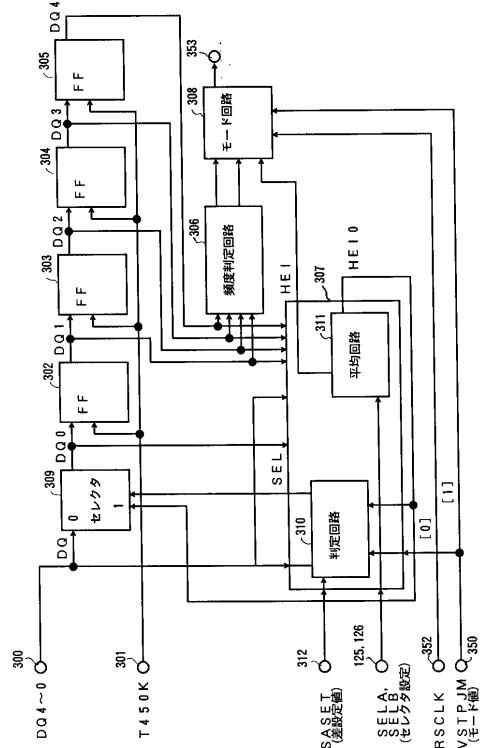

**【0057】**

図10は第2方式と第3方式を組み合わせたデータ処理回路 $26$ の一実施例のブロック図を示す。同図中、端子 $300, 301$ には量子化回路 $22$ から位相の量子化データ、タイミング発生回路 $28$ からのタイミング信号それぞれが入来し、位相の量子化データはセレクタ $309$ を通してシフトレジスタ $50$ を構成する遅延素子 $302 \sim 305$ に供給され、遅延素子 $302 \sim 305$ を位相の量子化データが順次シフトされる。 30

**【0058】**

ここで、シンボル周波数のシンボルクロックの立ち上がり時における量子化データが遅延素子 $73$ から出力されるタイミングでの端子 $300$ の入力量子化データを $DQ$ とし、遅延素子 $302$ の入力量子化データを $DQ1$ とし、遅延素子 $302 \sim 305$ それぞれの出力する量子化データを $DQ1 \sim DQ4$ とする。この量子化データ $DQ, DQ1 \sim DQ4$ は頻度判定回路 $306$ と判定及び平均回路 $307$ に供給される。頻度判定回路 $306$ は図9と同一構成であり、頻度判定回路 $306$ の出力する頻度選択信号、平均選択信号、合成位相データそれぞれはモード回路 $308$ に供給される。

**【0059】**

判定及び平均回路 $307$ 内の判定回路 $310$ は平均回路 $311$ から供給される量子化データの平均値を最新の量子化データ $DQ$ と比較してその差が端子 $311$ より供給される設定値 $SASET$ より大なるときのみ値1で、その他の場合値0の制御信号をセレクタ $309$ 及び平均回路 $311$ に供給する。セレクタ $309$ はこの信号が0のときは最新の量子化データ $DQ$ を $DQ0$ として出力するが、この信号が1で量子化データ $DQ$ の信頼性が低いときは平均回路 $311$ から供給される量子化データの平均値を最新の量子化データ $DQ$ の代わりに選択して $DQ0$ として出力する。 40

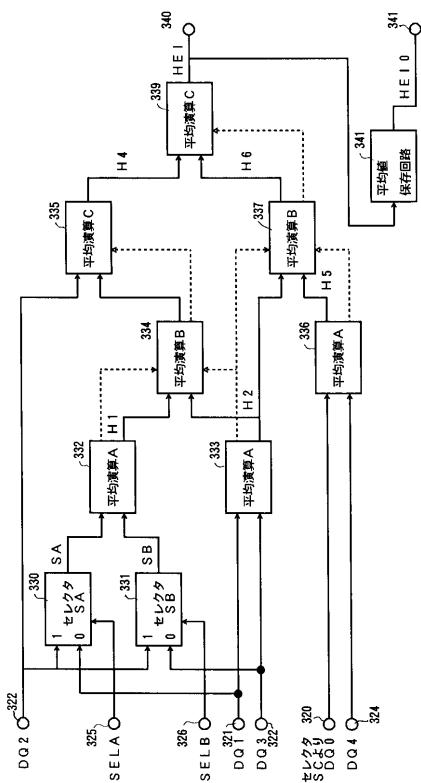

**【0060】**

平均回路 $311$ は図11に示す構成である。この構成は第2方式の他の実施例でもある。図11において、端子 $320 \sim 324$ には量子化データ $DQ, DQ1 \sim DQ4$ が供給され、端子 $325, 326$ には重み付けを変更するための制御信号 $SELA, SELB$ が供給 50

される。セレクタ 330 は制御信号 S E L A が 1 のとき量子化データ D Q 2 を選択し、制御信号 S E L A が 0 のとき D Q 1 を選択して平均演算回路 332 に供給する。セレクタ 331 は制御信号 S E L B が 1 のとき量子化データ D Q 2 を選択し、制御信号 S E L B が 0 のとき D Q 3 を選択して平均演算回路 332 に供給する。このセレクタ 330, 331 での選択によってどの量子化データの重みを大きくするかの重み付けを変更している。

#### 【0061】

平均演算回路 332 はセレクタ 330, 331 から供給される量子化データの平均を取って平均演算回路 334, 337 に供給し、平均演算回路 333 は量子化データ D Q 1, D Q 3 の平均を取って平均演算回路 334 に供給し、平均演算回路 334 は平均演算回路 332, 333 出力の量子化データの平均を取って平均演算回路 335 に供給する。平均演算回路 335 は平均演算回路 334 出力の量子化データと量子化データ D Q 2 との平均を取って平均演算回路 339 に供給する。10

#### 【0062】

平均演算回路 336 は量子化データ D Q 0, D Q 4 の平均を取って平均演算回路 337 に供給し、平均演算回路 337 は平均演算回路 333, 336 出力の量子化データの平均を取って平均演算回路 339 に供給する。平均演算回路 339 は平均演算回路 335, 339 出力の量子化データの平均を取って合成位相データとして端子 340 から出力する。

#### 【0063】

ここで、平均演算回路 332, 333, 336 それぞれは供給される 2 つの量子化データの位相差が 180 度異なるときマスク信号を出力する。平均演算回路 334, 335, 337, 339 それぞれはマスク信号を供給されると、マスク信号を供給してない方の量子化データを平均として出力し、更に平均演算回路 334, 337 それぞれは双方からマスク信号を供給されると、マスク信号を出力する。これはノイズが混入したときにその影響を除去するためである。20

#### 【0064】

平均演算回路 339 の出力する合成位相データは端子 340 から出力されると共に、平均値保存回路 341 に供給される。平均値保存回路 341 は端子 327 から量子化のタイミング信号を供給されるタイミングで、平均演算回路 339 からの合成位相データを保存して、端子 341 から出力する。

図 10 に戻って説明するに、平均回路 311 が端子 340 から出力する合成位相データはモード回路 308 に供給され、端子 341 から出力する保存された合成位相データはセレクタ 309 に供給される。モード回路 308 は端子 350 からのモード信号に応じて頻度判定回路 306 又は平均回路 311 からの合成位相データを端子 352 からのクロックに同期して端子 353 から出力する。30

#### 【0065】

通常モード時には、頻度判定回路 306 から頻度選択信号が供給されると、頻度判定回路 306 よりの合成位相データを端子 353 より出力し、頻度判定回路 306 から平均選択信号が供給されると、平均回路 311 よりの合成位相データを端子 353 より出力する。つまり、同一値の量子化データの頻度が高いときは、この量子化データが正常であるとして出力し、同一値の量子化データの頻度が低いときは平均値を取ってノイズ等の影響を低減し、出力している。40

#### 【0066】

この実施例では、特にノイズ等により 1 点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止できる。最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成できる。

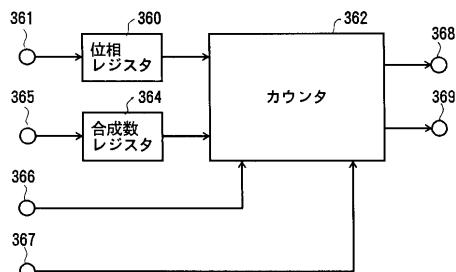

図 12 はタイミング発生回路 28 の一実施例のブロック図を示す。同図中、位相レジスタ 360 には外部の図示しない制御回路より端子 361 を介して再生クロックに対する中心の量子化データの位相差を指示する位相値が設定され、位相値はカウンタ 362 に供給される。また、合成数レジスタ 364 には外部の図示しない制御回路より端子 365 を介し50

て合成する量子化データ数を指示する合成数が設定され、合成数はカウンタ 362 に供給される。

#### 【0067】

カウンタ 362 には、このほかに、PLL 32 からの再生クロックが端子 366 を介して供給され、端子 367 を介して例えば周波数 14.4 MHz のクロックが供給されており、カウンタ 362 は再生クロックの立ち上がりから上記位相値だけ移相したタイミングを中心として、周波数 450 KHz の周期で前記中心及び中心の前後に合成数だけのパルスを発生して、これをタイミング信号として端子 368 からデータ処理回路 26 に供給する。また、前記中心で発生したパルスを端子 369 よりサンプリング回路 30 に供給している。

10

#### 【0068】

なお上記実施例では、4 相の PSK 信号の検波を例にして説明したが、これは 8 相又は 16 相の PSK 信号のデジタル無線通信装置の検波回路等にも適用でき、上記実施例に限定されない。

#### 【0069】

##### 【発明の効果】

上述の如く、請求項 1 に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1 つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により 1 点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により 1 点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止できる。

20

#### 【0076】

また、請求項 2 に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成できる。

30

また、請求項 3 に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを合成するため、1 つのサンプリングポイントで突発的な位相ずれが発生した場合やアイパターンがぼやけた場合に、誤差の少ない位相データを得ることができ、データ判定の誤りの発生を低減でき、ノイズ等により 1 点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、特にノイズ等により 1 点のサンプリングポイントで突発的な位相ずれが発生した場合に、データの判定を誤るおそれを防止でき、請求項 1 の発明を実現できる。

40

#### 【0084】

また、請求項 4 に記載の発明によれば、再生クロックを中心とする前後の複数ポイントでサンプリングした複数の位相の量子化データから各シンボルの位相データを簡単に合成することができ、最大頻度の量子化データが複数種類ある場合にも、複数の位相の量子化データから各シンボルの位相データを簡単に合成でき、請求項 2 の発明を実現できる。

##### 【図面の簡単な説明】

【図 1】本発明のデジタル無線通信装置の検波回路の一実施例のブロック図である。

【図 2】本発明の信号タイミングチャートである。

【図 3】量子化回路 22 の一実施例のブロック図である。

【図 4】データ処理回路 26 の第 1 方式の概略ブロック図である。

50

【図5】データ処理回路26の第2方式の概略ブロック図である。

【図6】データ処理回路26の第3方式の概略ブロック図である。

【図7】データ処理回路26の一実施例のブロック図である。

【図8】データ処理回路26の第2方式の一実施例のブロック図である。

【図9】データ処理回路26の第3方式の一実施例のブロック図である。

【図10】第2方式と第3方式を組み合わせたデータ処理回路26の一実施例のブロック図である。

【図11】データ処理回路26の第2方式の他の実施例のブロック図である。

【図12】タイミング発生回路28の一実施例のブロック図

【図13】従来のデジタル無線通信装置の検波回路の一例のブロック図である。 10

【図14】従来回路の信号タイミングチャートである。

#### 【符号の説明】

2 2 量子化回路

2 4 クロック発生回路

2 6 データ処理回路

2 8 タイミング発生回路

3 0 サンプリング回路

3 2 PLL

3 4 データ判定回路

5 0 シフトレジスタ

5 3 位相差検出回路

5 4 合成回路

6 0 平均回路

6 5 頻度判定回路

6 6 選択回路

【図1】

【図2】

本発明の信号タイミングチャート

【図3】

量子化回路22の一実例のブロック図

【図4】

データ処理回路26の第1方式の概略ブロック図

【図5】

データ処理回路26の第2方式の概略ブロック図

【図6】

データ処理回路26の第3方式の概略ブロック図

【図7】

データ処理回路26の第1方式の一実例のブロック図

【図8】

データ処理回路26の第2方式の一実例のブロック図

【図9】

【図10】

第2方式と第3方式を組み合わせた

データ処理回路26の一実施例のブロック図

【図11】

データ処理回路26の第2方式の他の実施例のブロック図

【図12】

タイミング発生回路28の一実施例の路図

【図13】

従来のデジタル無線通信装置の検波回路の一例のブロック図

【図14】

従来回路の信号タイミングチャート

---

フロントページの続き

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H04L 27/00-27/38