(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-196886

(P2006-196886A)

(43) 公開日 平成18年7月27日(2006.7.27)

| (51) Int.C1.                | F 1                     | テーマコード (参考) |

|-----------------------------|-------------------------|-------------|

| <b>H05K 3/46</b> (2006.01)  | H05K 3/46               | Q 4 E 3 5 1 |

| <b>H05K 1/16</b> (2006.01)  | H05K 1/16               | D 5 E 3 4 6 |

| <b>H01L 23/12</b> (2006.01) | H05K 3/46<br>H01L 23/12 | B B         |

審査請求 未請求 請求項の数 17 O L 外国語出願 (全 30 頁)

|              |                              |          |                                                                                                                                              |

|--------------|------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2005-368687 (P2005-368687) | (71) 出願人 | 390023674<br>イー・アイ・デュポン・ドゥ・ヌムール・<br>アンド・カンパニー<br>E. I. DU PONT DE NEMO<br>URS AND COMPANY<br>アメリカ合衆国、デラウェア州、ウイルミ<br>ントン、マーケット・ストリート 100<br>7 |

| (22) 出願日     | 平成17年12月21日 (2005.12.21)     | (74) 代理人 | 100077481<br>弁理士 谷 義一                                                                                                                        |

| (31) 優先権主張番号 | 60/637,813                   | (74) 代理人 | 100088915<br>弁理士 阿部 和夫                                                                                                                       |

| (32) 優先日     | 平成16年12月21日 (2004.12.21)     |          |                                                                                                                                              |

| (33) 優先権主張国  | 米国(US)                       |          |                                                                                                                                              |

| (31) 優先権主張番号 | 11/289,994                   |          |                                                                                                                                              |

| (32) 優先日     | 平成17年11月30日 (2005.11.30)     |          |                                                                                                                                              |

| (33) 優先権主張国  | 米国(US)                       |          |                                                                                                                                              |

最終頁に続く

(54) 【発明の名称】電力コアデバイス及びその作製方法

## (57) 【要約】

【課題】より高いICスイッチング速度に対応するため、改善された電圧応答と組み合わされた優れた配電インピーダンス低減を可能にすること。

【解決手段】電力コアが、少なくとも1つの埋込み個別化コンデンサ240を含む少なくとも1つの埋込み個別化コンデンサ層と、少なくとも1つの平面型コンデンサ積層薄板340とを備え、この平面型コンデンサ積層薄板340が、少なくとも1つの埋込み個別化コンデンサ240に電荷を供給するための低インダクタンス経路として機能し、少なくとも1つの埋込み個別化コンデンサ240が、平面型コンデンサ積層薄板340のうちの少なくとも1つに並列で接続され、電力コアが、少なくとも1つの信号層に相互接続される電力コアデバイスである。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

電力コアが、

少なくとも 1 つの埋込み個別化コンデンサを備えた少なくとも 1 つの埋込み個別化コンデンサ層と、

少なくとも 1 つの平面型コンデンサ積層薄板とを備え、

該平面型コンデンサ積層薄板が、前記埋込み個別化コンデンサに電荷を供給するための低インダクタンス経路として機能し、

前記埋込み個別化コンデンサが、前記平面型コンデンサ積層薄板のうちの少なくとも 1 つに並列に接続され、

前記電力コアが、少なくとも 1 つの信号層に相互接続されていることを特徴とする電力コアデバイス。

**【請求項 2】**

前記電力コアは、複数の埋込み個別化コンデンサ層と、複数の平面型コンデンサ積層薄板とを備えていることを特徴とする請求項 1 に記載の電力コアデバイス。

**【請求項 3】**

前記埋込み個別化コンデンサは、少なくとも第 1 の電極と第 2 の電極とを備えていることを特徴とする請求項 1 に記載の電力コアデバイス。

**【請求項 4】**

前記埋込み個別化コンデンサの第 1 の電極及び第 2 の電極が、半導体デバイスの少なくとも 1 つの電力端子に接続されていることを特徴とする請求項 3 に記載の電力コアデバイス。

**【請求項 5】**

前記半導体デバイスは、集積回路であることを特徴とする請求項 4 に記載の電力コアデバイス。

**【請求項 6】**

複数の信号層を備え、該信号層が導電バイアを介して接続されていることを特徴とする請求項 1 に記載の電力コアデバイス。

**【請求項 7】**

インターポーラ、プリント配線板、マルチチップモジュール、エリアアレイパッケージ、システムオンパッケージ、システムインパッケージから選択されることを特徴とする請求項 1 に記載の電力コアデバイス。

**【請求項 8】**

パターン形成された側とパターン形成されない側とを有する少なくとも 1 つの平面型コンデンサ構造を提供するステップと、

箔側と構成部品側とを有する少なくとも 1 つの、前記箔上に形成された個別化コンデンサを備えた少なくとも 1 つの箔構造を提供するステップと、

前記箔構造の前記構成部品側を前記平面型コンデンサ構造の前記パターン形成された側に積層するステップと、

前記箔構造の前記箔側をエッチングするとともに、前記平面型コンデンサ構造の前記パターン形成されない側をエッチングして電力コアを形成するステップと、

該電力コア上に少なくとも 1 つの信号層を形成するステップと

を有することを特徴とする電力コアデバイスの作製方法。

**【請求項 9】**

パターン形成された側とパターン形成されない側とを有する少なくとも 1 つの平面型コンデンサ構造を提供するステップと、

箔側と構成部品側とを有する少なくとも 1 つの、前記箔上に形成された個別化コンデンサを備えた少なくとも 1 つの箔構造を提供するステップと、

前記箔構造の前記箔側を前記平面型コンデンサ構造の前記パターン形成された側に積層するステップと、

10

20

30

40

50

前記箔構造の前記箔側をエッティングするとともに、前記平面型コンデンサ構造の前記パターン形成されない側をエッティングして電力コアを形成するステップと、

該電力コア上に少なくとも1つの信号層を形成するステップと

を有することを特徴とする電力コアデバイスの作製方法。

【請求項10】

前記電力コアの一方の表面又は両方の表面に誘電層を被着し、

該誘電層上に1つ又は複数の信号ラインを備える回路を形成し、

該信号ラインを備える層間で導電相互接続を形成することによって、前記信号層が形成されることを特徴とする請求項8又は9に記載の電力コアデバイスの作製方法。

【請求項11】

前記層間の前記相互接続は、導電バイアであることを特徴とする請求項10に記載の電力コアデバイスの作製方法。

【請求項12】

追加の受動構成部品が前記電力コアに接続され、該電力コアの外側にあることを特徴とする請求項8又は9に記載の電力コアデバイスの作製方法。

【請求項13】

信号ライン、抵抗、又はそれらの組合せを、前記個別化コンデンサと同じ層上で配置及び相互接続することを特徴とする請求項8又は9に記載の電力コアデバイスの作製方法。

【請求項14】

第1のパターン形成された側と第2のパターン形成された側とを有する少なくとも1つの平面型コンデンサ構造を提供するステップと、

箔側と構成部品側とを有する少なくとも1つの、前記箔上に形成された個別化コンデンサを備えた少なくとも1つの箔構造を提供するステップと、

前記箔構造の前記構成部品側を積層箔対に積層するステップと、

少なくとも1つの信号層を形成するステップと、

前記積層箔対の前記箔側をエッティングするステップと、

前記平面型コンデンサ構造のパターン形成されない側をエッティングするステップと、

電力コアデバイスを形成するために積層するステップと

を有することを特徴とする電力コアデバイスの作製方法。

【請求項15】

前記各層が導電バイアによって他の層に相互接続されることを特徴とする請求項14に記載の電力コアデバイスの作製方法。

【請求項16】

前記導電バイアが、バイアを導電材料で充填すること、バイアを導電材料でめっきすること、及び箔上で導電バンプを形成することから選択された方法によって形成されることを特徴とする請求項15に記載の電力コアデバイスの作製方法。

【請求項17】

パターン形成された側とパターン形成されない側とを有する少なくとも1つの平面型コンデンサ構造を提供するステップと、

箔側と構成部品側とを有する少なくとも1つの、前記箔上に形成された個別化コンデンサを備えた少なくとも1つの箔構造を提供するステップと、

前記箔構造の前記箔側を前記平面型コンデンサ構造の前記パターン形成された側に積層するステップと、

前記箔構造の前記箔側をエッティングするとともに、前記平面型コンデンサ構造の前記パターン形成されない側をエッティングして電力コアを形成するステップと、

予め作製された信号ライン組立体を形成するステップと、

前記電力コアと前記予め作製された信号ライン組立体とを接合するステップと

を有することを特徴とする電力コアデバイスの作製方法。

【発明の詳細な説明】

【技術分野】

10

20

30

40

50

## 【0001】

本発明は、電力コアデバイス及びその作製方法に関し、より詳細には、低インダクタンス機能と高キャパシタンス機能を有する電力コアデバイス及びその作製方法、並びに電力コアデバイスを有機誘電積層薄板 (organic dielectric laminates) とプリント配線板を含めて電力コアパッケージに組み込む方法に関する。

## 【背景技術】

## 【0002】

集積回路 (IC) を備えた半導体デバイスが、より高い周波数、より高いデータ転送速度、より低い電圧で動作するにつれて、電力ライン及び接地 (戻り) ライン内のノイズ、ならびにより速い回路スイッチングに対処するために十分な電流を供給することがますます重要な問題となり、配電システムにおいて低いインピーダンスを必要とする。低ノイズ、ICに対する安定した電力を実現するために、従来の回路におけるインピーダンスは、並列で相互接続された追加の表面実装コンデンサを使用して低減される。動作周波数がより高い (ICスイッチング速度がより高い) ことは、ICに対する電圧応答時間がより速くなければならないことを意味する。動作電圧がより低いことは、許容可能な電圧変動 (リップル) 及びノイズがより小さくなることを必要とする。例えば、マイクロプロセッサ ICは、スイッチングし、動作を開始したとき、スイッチング回路をサポートするための電力を必要とする。電圧供給の応答時間が遅すぎた場合、マイクロプロセッサは、許容可能なリップル電圧とノイズマージンを越える電圧降下又は電力減衰 (power drop) を受けることになり、ICは誤動作することになる。さらに、ICが電源投入されたとき、応答時間が遅いと、電力オーバーシュートが発生することになる。電力減衰 / オーバーシュートは、ICに十分に近接するコンデンサを使用することによって、それらが適切な応答時間内で電力を提供又は吸収する許容限界内で制御しなければならない。

## 【0003】

インピーダンス低減と、電力減衰又はオーバーシュートを弱めるためのコンデンサは、一般に、回路性能を改善するために可能な限り ICに近接して配置される。従来の設計は、プリント配線板 (PWB) 上で表面実装された、ICの周りに集められたコンデンサを有する。大きな値のコンデンサは、電源の近くで配置され、中間の値のコンデンサは、ICと電源の間の場所で配置され、小さな値のコンデンサは、ICの非常に近くで配置される。

## 【0004】

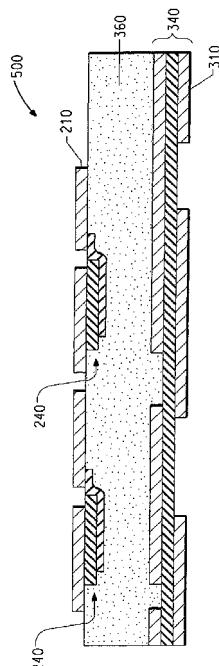

図1は、インピーダンス低減と電力減衰又はオーバーシュートを弱めるための典型的な従来のコンデンサを使用した回路構成図で、電源2とICデバイス10とコンデンサ4, 6, 8を示している。このコンデンサ4, 6, 8は、上述したインピーダンス低減と、電力減衰又はオーバーシュートを弱めるために使用され、それぞれ高い値のコンデンサ、中間の値のコンデンサ、小さな値のコンデンサを示している。

## 【0005】

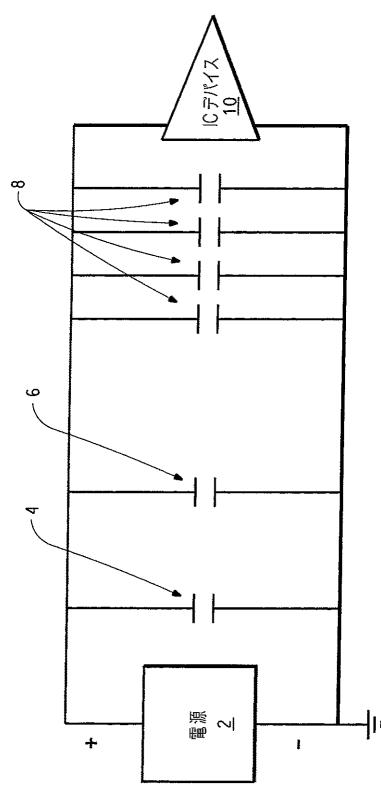

図2は、インピーダンス低減と電力減衰又はオーバーシュートを弱めるために使用される従来の表面実装 (SMT) コンデンサを有するプリント配線組立体の立断面図で、PWBの基板内の電力平面及び接地平面に対するSMTコンデンサ50及び60ならびにICデバイス40の接続関係を示している。ICデバイス40は、はんだフィレット44によってランド41に接続されている。このランド41は、回路ライン72及び73によって、バイア(via; ビア)90及び100のめっきスルーホールバイア(バイア)パッドに接続されている。このバイアパッドは、全体的に82として示されている。バイア90は、導体平面120に電気的に接続され、バイア100は、導体平面122に接続されている。導体平面120と122は、一方は電源の電力側に、他方は電源の接地側に接続されている。同様に、小さな値コンデンサ50及び60は、並列でICデバイス40に電気的に接続されるような方法で、バイア90及び100ならびに導体平面120及び122に電気的に接続されている。モジュール、インターポーザ、又はパッケージ上で配置されたICデバイスの場合には、大きな値のコンデンサと中間の値のコンデンサは、そのモジ

10

20

30

30

40

50

ュール、インターポーザ、又はパッケージが取り付けられるプリント配線マザーボード上に配置することができる。

#### 【0006】

並列で相互接続された多数のコンデンサは、しばしば、電力システムインピーダンスを低減するために必要とされ、複雑な電気経路設定を必要とする。これは回路ループインダクタンスを増大し、増大した回路ループインダクタンスは、インピーダンスを増大し、電流を制限し、それによって表面実装コンデンサの有益な効果を減少させる。周波数が高くなり、動作電圧が引き続き降下するにつれて、増大された電力をより速い速度で供給しなければならず、インダクタンス／インピーダンスレベルをますます下げる必要とする。

10

#### 【0007】

インピーダンスを最小限に抑えるために、少なからぬ努力が払われている。Howardらの米国特許（特許文献1参照）は、インピーダンス及び「ノイズ」を最小限に抑えるための一方法を提供している。Howardらは、コンデンサ積層薄板（平面型コンデンサ）が、多層の積層されたボード内に含まれる容量性プリント回路板を提供し、集積回路など多数のデバイスが、ボード上で載置又は形成され、借用（borrowed）又は共用キャパシタンスを使用して容量性機能を提供するように、コンデンサ積層薄板（又は複数のコンデンサ積層薄板）に動作可能に結合される。しかし、そのような方法は、必ずしも電圧応答を改善しない。電圧応答を改善することは、コンデンサがICデバイスに、より近接して配置されることを必要とする。単にコンデンサ積層薄板をICデバイスに、より近接して配置するだけでは十分でない可能性がある。というのは、使用可能な合計キャパシタンスが不十分となる可能性があるからである。

20

#### 【0008】

Chakravortyの米国特許（特許文献2参照）は、スイッチングノイズを低減するためにコンデンサを埋め込むことに対する代替の方法を提供し、集積回路ダイの電源端子は、多層セラミック基板内で少なくとも1つの埋込みコンデンサのそれぞれの端子に結合することができる。

30

#### 【0009】

【特許文献1】米国特許第5161086号明細書

【特許文献2】米国特許第6611419号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0010】

したがって、本発明者らは、集積回路パッケージ又は他の相互接続ボード、構造、もしくは要素内での使用を含む、電力コアパッケージ内で使用するための電力コア、すなわち、より高いICスイッチング速度に対処するために、改善された電圧応答と組み合わされた優れた配電インピーダンス低減を可能にする電力コアデバイス及びその作製方法を提供することを望んでいる。

#### 【0011】

本発明は、このような状況に鑑みてなされたもので、その目的とするところは、低インダクタンス機能と高キャパシタンス機能を有し、より高いICスイッチング速度に対処するために、改善された電圧応答と組み合わされた優れた配電インピーダンス低減を可能にする電力コアデバイス及びその作製方法提供することにある。

40

#### 【課題を解決するための手段】

#### 【0012】

本発明は、電力コアを備えた電力コアデバイスであって、この電力コアが、少なくとも1つの埋込み個別化コンデンサを含む少なくとも1つの埋込み個別化コンデンサ層と、少なくとも1つの平面型コンデンサ積層薄板とを備え、前記平面型コンデンサ積層薄板が、前記少なくとも1つの埋込み個別化コンデンサに電荷を供給するための低インダクタンス経路として機能し、前記少なくとも1つの埋込み個別化コンデンサが、前記平面型コンデ

50

ンサ積層薄板のうちの少なくとも1つに並列で接続され、前記電力コアが、少なくとも1つの信号層に相互接続される電力コアデバイスを対象としている。

【0013】

また本発明は、電力コアデバイスの作製方法であって、パターン形成された側とパターン形成されない側とを有する少なくとも1つの平面型コンデンサ構造を提供するステップと、箔側と構成部品側とを有する少なくとも1つの、前記箔上に形成された個別化コンデンサを備えた少なくとも1つの箔構造を提供するステップと、前記箔構造の構成部品側を前記平面型コンデンサ構造の前記パターン形成された側に積層するステップと、前記箔構造の箔側をエッチングするとともに、前記平面型コンデンサ構造の前記パターン形成されない側をエッチングして電力コアを形成するステップと、該電力コア上に少なくとも1つの信号層を形成するステップとを有する電力コアデバイスの作製方法を対象としている。

10

【0014】

さらに、他の実施形態は、電力コアデバイスの作製方法であって、パターン形成された側とパターン形成されない側とを有する少なくとも1つの平面型コンデンサ構造を提供するステップと、箔側と構成部品側とを有する少なくとも1つの、前記箔上に形成された個別化コンデンサを備える少なくとも1つの箔構造を提供するステップと、前記箔構造の前記箔側を前記平面型コンデンサ構造の前記パターン形成された側に積層するステップと、前記箔構造の前記箔側をエッチングするとともに、前記平面型コンデンサ構造の前記パターン形成されない側をエッチングして電力コアを形成するステップと、該電力コア上に少なくとも1つの信号層を形成するステップとを有する電力コアデバイスの作製方法を対象としている。

20

【発明を実施するための最良の形態】

【0015】

以下、図面を参照して本発明の実施形態について説明する。なお、詳細な説明における同じ番号は同一の構成要素を示している。

【0016】

本発明によれば、個別化コンデンサと平面型コンデンサ構造（積層薄板）が、電力コアを生み出すように積層構造内で埋め込まれて並列で接続される、電力コアデバイス及びその製造方法が開示されている。この電力コアは、少なくとも1つの信号層に相互接続されて電力コアデバイスを形成している。個別化コンデンサは、金属上で形成された個々のコンデンサとして構成することができる。典型的には、その金属は金属箔である。本明細書では「箔」という用語を使用するが、その箔は、一般的な金属層、めっきされた金属、スパッタされた金属などを包含するものである。電力コアデバイス内の個別化コンデンサは、高いスイッチング速度をサポートするようなICデバイスに対する速い電圧応答のために、近接する（例えば、本実施形態ではICデバイスの直下となる）ように設計されている。個別化コンデンサをICデバイスの電力端子に可能な限り近接して（例えば、直下に）配置することはまた、低インダクタンス接続を実現する。平面型コンデンサ構造は、電力-接地平面として使用され、電力-接地平面分離は、パッケージ内の高周波インピーダンスを低減するために薄くされている。

30

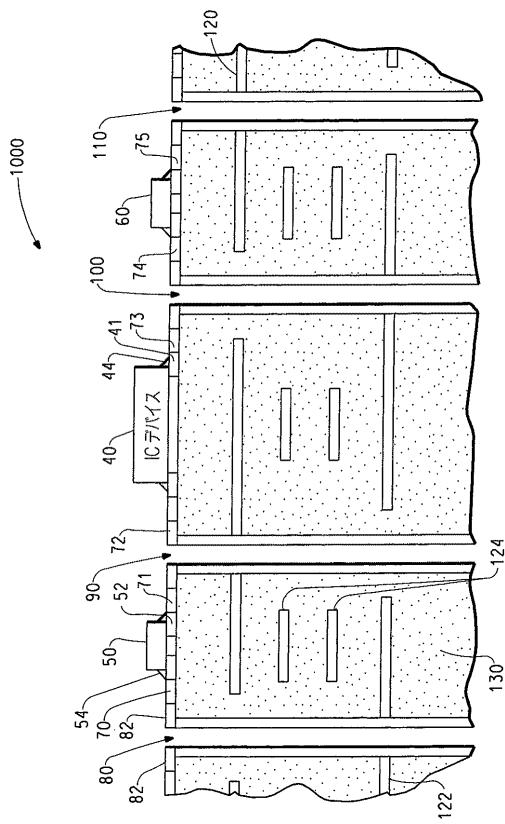

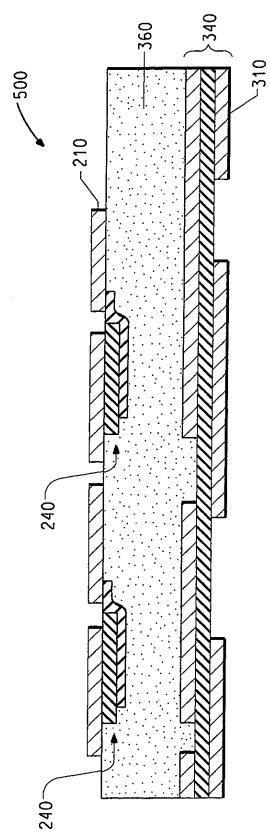

【0017】

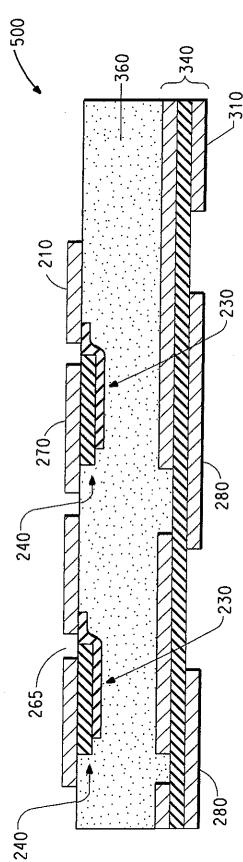

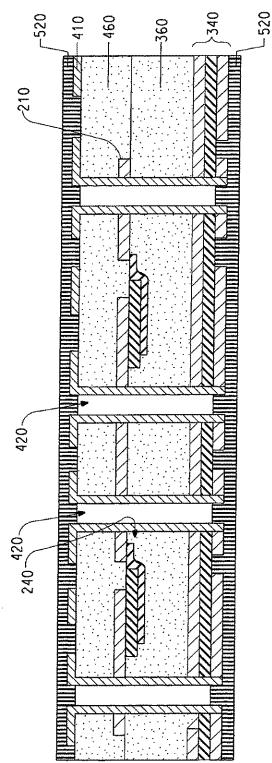

図3は、本発明による電力コアデバイスの立断面図である。この電力コアデバイス50を構成する電力コアは、少なくとも1つの信号層に相互接続されて電力コアデバイスを形成している。この電力コアデバイスは、個別化コンデンサを含む箔を様々な材料で形成し、その後で平面型コンデンサに積層し、電力コアデバイスを形成することを可能にする。そのような材料は、高kセラミックで充填されたポリマー厚膜コンデンサ誘電体及び金属で充填された厚膜電極ペーストが金属箔上でスクリーン印刷され硬化されたものの使用を含むことができる。E.I.duPont de Nemours and Companyから得ることが可能なHK04のような銅/ポリイミド/銅積層薄板など、従来の平面型コンデンサ積層薄板（planar capacitor laminate）のエッチングを使用し、銅箔上で個別化コンデンサ（embedded shingul

40

50

ated capacitor)を形成することもできる。しかし、そのようなポリマーを主成分とするコンデンサは、キャパシタンスが比較的低く、一般に、個別化コンデンサは、キャパシタンスが高いことが望ましい。そのような場合には、箔上形成 (formed-on-foil) 方法を使用し、セラミック組成物を使用して銅箔上で個別化セラミックコンデンサを作製することができることが好ましい。そのようなコンデンサは、薄膜方法からでも厚膜方法からでも形成することができる。コンデンサを含む箔は、標準的なプリント配線板積層プロセスを使用して平面型コンデンサに積層し、電力コアを形成することができる。

【0018】

上述した電力コアは、また、様々な材料を使用して平面型コンデンサ構造を形成することを可能にする。そのような材料は、金属箔 - 誘電体 - 金属箔積層構造を含むことができ、その誘電体は、有機層、セラミックで充填された有機層、又はセラミック層を含むことができる。複数の層が使用される場合、各層は、異なる材料のものとすることができる。そのような誘電体は、インピーダンスを低減するために、薄い層を用いて製造されることになる。平面型コンデンサ構造は、電力コアデバイスを形成するために、標準的なプリント配線板積層プロセスによって、箔上に形成されたコンデンサに積層する。

【0019】

上述した実施形態によれば、低インピーダンス機能と高キャパシタンス機能を共に単一の電力コア構造内に一体化することができ、その電力コア構造は、さらに他の積層構造内に一体化することができ、電圧リップルが低減された、より低い電圧での高速 I C の動作を可能にする。電力コア構造が、プリント配線板、モジュール、インターポーザ、又はパッケージなど電力コアデバイス内で一体化されたとき、貴重な表面積が使用可能になる。さらに、SMTデバイスに関連するはんだ継手をなくすことができ、それによって信頼性が改善される。電力コア構造は、従来のプリント配線板プロセスを使用して処理し、生産コストをさらに削減することができる。

【0020】

当業者なら、上記でリストされ、以下で詳述される図を参照して各実施形態の詳細な説明を読めば、上述した利点、ならびに本発明の様々な実施形態の他の利点及び利益を理解するであろう。

【0021】

一般的な実施によれば、図面の様々な特徴は、必ずしも原寸に比例して示されていない。様々な特徴の寸法は、本発明の各実施形態をより明確に示すために伸張又は縮小される可能性がある。

【0022】

本発明の各実施形態は、プリント配線板 (PWB)、モジュール、インターポーザ、又はパッケージの基板内に埋設することができる電力コア構造を対象とする。PWB、モジュール、インターポーザ、又はパッケージ基板内で電力コアの低インダクタンス / 高キャパシタンス機能を提供することにより、PWB、モジュール、インターポーザ、又はパッケージ上の貴重な表面積が保存され、また、従来のSMTコンデンサ構成ほどはんだ継手を必要としない。

【0023】

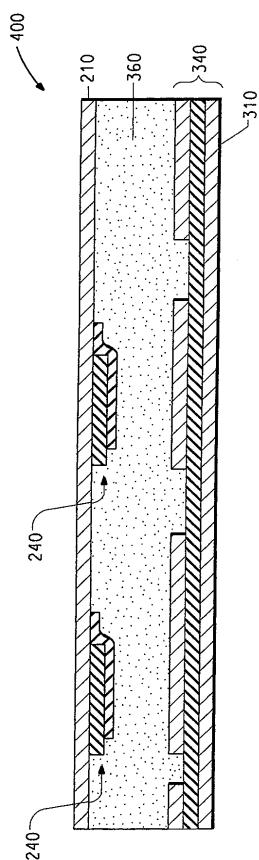

上述したように、図3には、本発明による電力コアデバイスの立断面図で、平面型コンデンサ積層薄板340と、箔上に形成された個別化コンデンサ240とを備えた電力コアデバイス500の側面図である。

【0024】

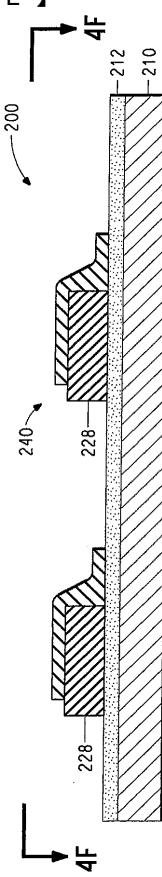

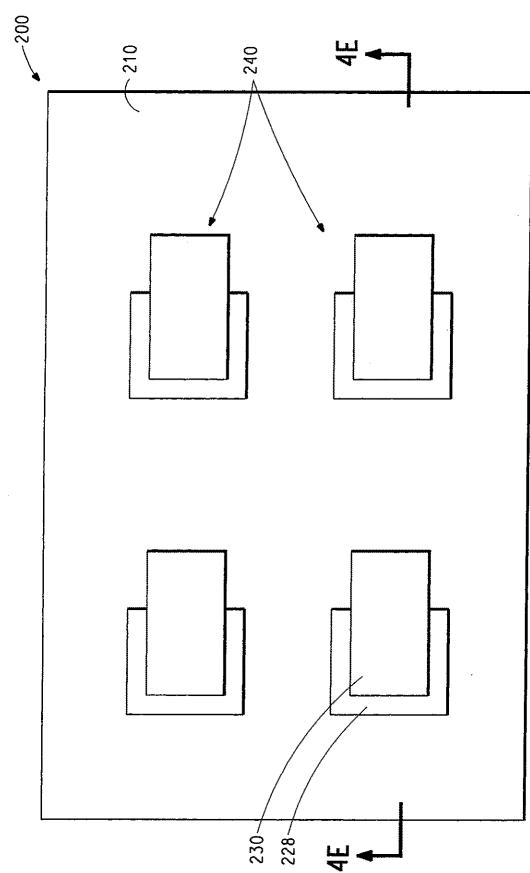

図4A乃至図4Fは、単層の（典型的には箔上で焼成された）箔上に形成された個別化コンデンサ構造の作製方法を説明するための側面図である。図4Fは、仕上げられた、箔上に形成された個別化コンデンサ構造の平面図である。厚膜の、箔上で焼成された個別化コンデンサ構造の特定の例について以下に説明する。

【0025】

10

20

30

40

50

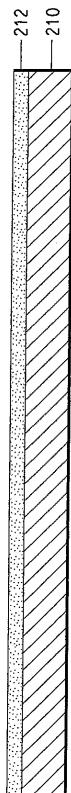

図 4 A は、個別化コンデンサ構造を作製する第 1 段階を示す側面図である。図 4 A に示す個別化コンデンサ構造（層）200 において、金属箔 210 が提供されている。この金属箔 210 は、業界内で一般に使用可能なタイプのものとすることができます。例えば、金属箔 210 は、銅、銅 - インバー - 銅、インバー、ニッケル、ニッケル被覆銅、又は、厚膜ペーストのための焼成温度を越える融点を有する他の金属とすることができます。好みの箔は、裏面処理銅箔 (reverse treated copper foils)、両面処理銅箔 (double-treated copper foils)、及び、多層プリント回路板業界内で一般に使用される他の銅箔など、主に銅からなる箔を含んでいます。この箔 210 の厚さは、例えば、約 1 ~ 100 ミクロン、好みは 3 ~ 75 ミクロン、最も好みは、約 1/3 オンス (10.33 g) と 1 オンス (30.98 g) 銅箔の間に応する 12 ~ 36 ミクロンの範囲内とすることができます。好適な箔 210 の一例は、Oak - Mitsui から得ることが可能な PLSP グレードの 1 オンス (30.98 g) 銅箔である。

10

20

30

40

50

## 【0026】

箔 210 は、この箔 210 にアンダープリント 212 を被着することによって前処理することができます。アンダープリント 212 は、箔 210 の構成部品側表面に被着された比較的薄い層である。図 4 A では、アンダープリント 212 は、箔 210 上の表面コーティングとして示されている。アンダープリント 212 は、箔 210 に、またアンダープリント 212 を覆って堆積された層に十分接着する。アンダープリント 212 は、例えば、箔 210 に被着されたペーストから形成することができ、次いで、不活性雰囲気内で、箔 210 の融点より低い温度で焼成される。ペーストは、箔 210 の表面全体を覆ってオープンコーティングとしてプリントすることも、箔 210 の選択された領域上でプリントすることもできる。一般に、箔 210 の選択された領域を覆ってアンダープリントペーストをプリントすることがより経済的である。銅箔 210 を銅アンダープリント 212 と共に使用したとき、銅アンダープリントペースト内のガラスが銅箔 210 の酸化腐食を遅らせ、したがって、酸素ドープ焼成が使用される場合、箔 210 の表面全体をコーティングすることが好み。好適な銅アンダープリントの一例は、E.I.duPont de Nemours and Company から入手可能な EP320 である。

## 【0027】

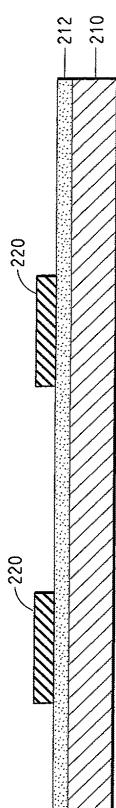

図 4 B は、個別化コンデンサ構造を作製する第 2 段階を示す側面図である。ここでは、コンデンサ誘電材料が前処理済み箔 210 上にスクリーン印刷され、第 1 のコンデンサ誘電層 220 を形成する。コンデンサ誘電材料は、例えば、厚膜誘電インクとすることができます。誘電インクは、例えば、ペーストから形成することができる。好適なコンデンサ誘電ペーストの一例は、E.I.duPont de Nemours and Company から得ることが可能な EP310 である。次いで、第 1 のコンデンサ誘電層 220 を乾燥させる。

## 【0028】

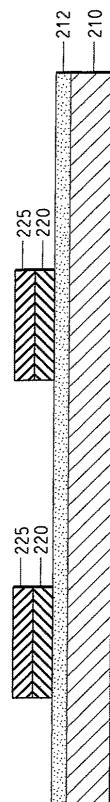

図 4 C は、個別化コンデンサ構造を作製する第 3 段階を示す側面図である。ここでは、第 2 のコンデンサ誘電層 225 を被着して乾燥させる。他の実施形態では、より粗いメッシュスクリーンを介して単層のコンデンサ誘電材料を堆積し、1 回のプリントで均等な厚さを実現することができる。

## 【0029】

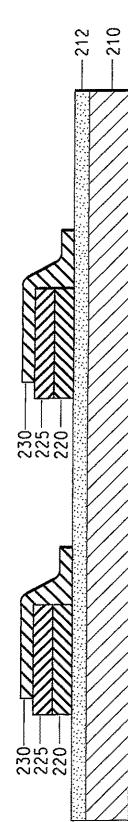

図 4 D は、個別化コンデンサ構造を作製する第 4 段階を示す側面図である。ここでは、第 2 のコンデンサ誘電層 225 を覆って電極 230 を形成して乾燥させる。電極 230 は、例えば、厚膜金属性インクをスクリーン印刷することによって形成することができる。銅箔 210 を銅アンダープリント 212 と共に使用したとき、銅電極を使用することができる。好適な銅電極ペーストの一例は、E.I.duPont de Nemours and Company から得ることが可能な EP320 である。一般に、第 2 のコンデンサ誘電層 225 の表面積は、電極 230 の表面積より大きくするべきである。

## 【0030】

次いで、第1のコンデンサ誘電層220、第2のコンデンサ誘電層225、電極230が同時に焼成される。この焼成は、例えば、窒素厚膜炉内で、ピーク温度900で行うことができる。厚膜の第1及び第2のコンデンサ誘電層220, 225は、例えば、チタン酸バリウムなど高誘電率機能相、様々なドーパント、及びガラスフリット相で形成することができる。同時焼成中には、ガラスフリット相が軟化し、機能相及びドーパント相を濡らし、ガラス-セラミックマトリクス内で機能相とドーパントの分散を生み出すように融合する。同時に、電極(層)230の銅電極粉末は、軟化したガラスフリット相によって濡らされ、共に焼結して固体電極を形成する。電極(層)230は、同時焼成に由来する、高k誘電体228に対する強い結合を有する。焼成後の構造が、図4Eに第5段階を示す側面図で示されている。

10

## 【0031】

図4Fは、図4Eに示した個別化コンデンサ構造の平面図で、仕上げられた個別化コンデンサ構造200を示している。この図4Fでは、箔210上の4つの個別化コンデンサ240が示されている。しかし、任意の数のオフセットかコンデンサ240を、様々なパターンで、箔210上で構成することができる。

## 【0032】

本明細書で説明されている、箔上に形成されたコンデンサでは、「ペースト」又は「インク」という用語は、電子材料業界内で使用される従来の用語に対応することができ、全体的に厚膜組成物を示している。典型的には、アンダープリントペーストの金属成分は、金属箔内の金属に一致させる。例えば、銅箔が使用されるならば、アンダープリントとして銅ペーストを使用することができる。他の応用例の各例は、銀箔及びニッケル箔を同様の金属アンダープリントペーストと対にする。厚膜ペーストを使用し、アンダープリントと受動構成部品を共に形成することができる。

20

## 【0033】

一般に、厚膜ペーストは、セラミック、ガラス、金属、又は他の固体の細粒が、可塑剤、分散剤、及び有機溶剤の混合物内で溶解されたポリマー内で分散されたものを含んでいる。銅箔上で使用するための好ましいコンデンサペーストは、窒素雰囲気内で良好なバーンアウトを有する有機溶剤を有する。そのような溶剤は、一般に、高分子量エチルセルロースなど、非常に少量の樹脂を含有し、その場合、スクリーン印刷に適した粘度を生成するために少量が必要であるにすぎない。さらに、硝酸バリウム粉末など酸化成分が誘電粉末混合物内に混和されたものは、有機成分が窒素雰囲気内で燃焼する助けるとなる。固体は、本質的に不活性な液体媒質(溶剤)と混合され、次いで、3ロールミル(three-roller mill)上で分散され、スクリーン印刷に適したペーストのような組成物を形成する。任意の本質的に不活性な液体を溶剤として使用することができる。例えば、増粘剤及び/もしくは安定剤ならびに/又は他の一般的な添加剤を有する、又は有さない様々な有機液体を溶剤として使用することができる。

30

## 【0034】

高誘電率(高k)厚膜コンデンサ誘電ペーストは、一般に、少なくとも1つの高k機能相粉末及び少なくとも1つのガラス粉末が、少なくとも1つの樹脂及び溶剤からなる溶剤系内で分散されたものを含有する。溶剤系は、スクリーン印刷されて、稠密な、空間的に十分画定された膜をもたらすように設計される。高k機能相粉末は、500を越えるバルク誘電率を有し、一般式 $ABO_3$ を有するペロブスカイト型強誘電組成物を含むことができる粉末として説明することができる。そのような組成物の各例には、 $BaTiO_3$ 、 $SrTiO_3$ 、 $PbTiO_3$ 、 $CaTiO_3$ 、 $PbZrO_3$ 、 $BaZrO_3$ 、 $SrZrO_3$ 、又はそれらの混合物が含まれる。代替の元素をA及び/又はB位置に置換することによって、 $Pb(Mg_{1/3}Nb_{2/3})O_3$ 及び $Pb(Zn_{1/3}Nb_{2/3})O_3$ など、他の組成物もまた可能である。好適な高k機能相粉末は、富士チタン工業株式会社から得ることが可能なチタン酸バリウムである。上述した組成物のドープされた、また混合された金属バージョンもまた好適である。ドーピング及び混合は、主に、材料が「X7R」又は「Z5U」標準など業界定義を満たすために、必要な末端使用の特性仕様、例えば

40

50

、必要なキャパシタンス温度係数（TCC）を達成するよう行われる。

【0035】

ペースト内のガラスは、例えば、Ca-A1ホウケイ酸塩、Pb-Baホウケイ酸塩、Mg-Aiケイ酸、希土類ホウ酸塩、及び他の同様のガラス組成物とすることができます。ゲルマニウム酸鉛（Pb<sub>5</sub>Ge<sub>3</sub>O<sub>11</sub>）など、高kガラス・セラミック粉末が好ましい。

【0036】

電極層を形成するために使用されるペーストは、銅、ニッケル、銀、銀含有貴金属組成物のいずれかの金属粉末、又はこれらの化合物の混合物に基づくものとすることができます。銅粉末組成物が好ましい。

10

【0037】

本明細書で述べられている個別化コンデンサ構造は、キャパシタンスを増大するために、多層の誘電体及び電極を使用して製造することができる。

【0038】

上述した例では、誘電体は、厚膜ペーストをスクリーン印刷することによって形成されるものとして述べられている。しかし、溶液コーティングによる堆積、キャストオンカバー（cast on copper）プロセス、又はスパッタリングなど、他の方法を使用することもできる。他の方法として、誘電体を被着し、次いでフォトデファイン（光学構成；photo defined）することができる。さらに、電極層は、スクリーン印刷することによって形成されるものとして述べられている。しかし、スパッタリングによる堆積、電極金属を誘電層表面上にめっき又は蒸着することなど、他の方法を使用することもできる。さらに、フォトデファインされたペーストを使用することもできる。

20

【0039】

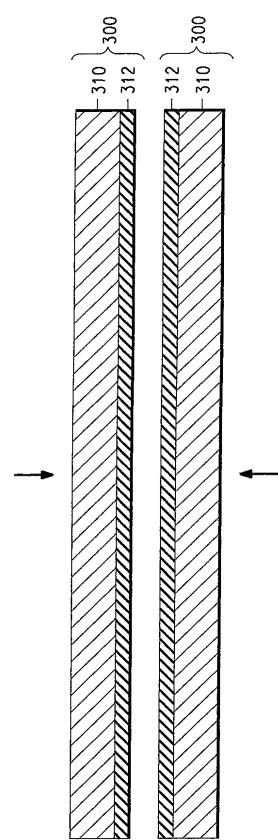

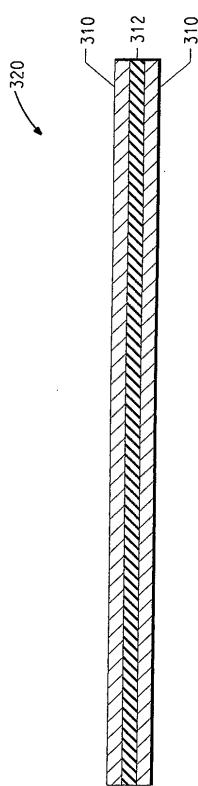

図5A及び図5Bは、平面型コンデンサ積層薄板の作製方法を説明するための側面図である。図5Aは、図5Bに示されている平面型コンデンサ積層薄板の作製方法の第1段階を示す立断面図である。ここでは、第1の金属箔310が提供されている。この第1の金属箔310は、例えば、銅、銅を主成分とする材料、及び他の金属から作製することができる。好ましい金属箔310は、裏面処理銅箔、両面処理銅箔、及び、多層プリント回路板業界内で一般に使用される他の銅箔など、主に銅からなる箔を含んでいる。いくつかの好適な銅箔の各例は、0.1in Brass (Somers Thin Strip) 及びJECから入手可能なものである。金属箔310の厚さは、例えば、約1~100ミクロン、好ましくは3~75ミクロン、最も好ましくは、約1/3オンス(10.33g)と1オンス(30.98g)銅箔の間に応する12~36ミクロンの範囲内とすることができる。

30

【0040】

スラリー材料又は溶液を金属箔310上に注型又は被覆し、乾燥及び硬化させ、第1の誘電層312を形成することができ、その結果、被覆金属箔300となる。積層薄板の誘電層又は各層は、有機化合物、セラミック、セラミックで充填された有機化合物、及びそれらの混合物の各層から選択することができる。硬化は、スラリーが熱可塑性のものである場合、例えば、350でペークすることによって行うことができる。スラリーが熱硬化性材料である場合、より高い硬化温度を使用することができる。ポリマーを一部分だけ硬化し、ポリマーの「B」ステージ状態を生み出すことが意図されている場合、硬化は、例えば、120~200で乾燥させることによって実行することができる。

40

【0041】

第1の誘電層312を形成するために使用される溶液は、例えば、溶媒内で溶解されたポリマーを含むことができる。スラリー材料は、例えば、高誘電率（高k）フィラー/セラミックフィラー又は機能相を有するポリマー溶媒溶液を含むことができる。スラリー又は溶液として好適なポリマーは、それだけには限らないが、例えば、エポキシ樹脂又はポリイミド樹脂を含むことができる。高k機能相は、500より大きい誘電率を有する材料として定義することができ、一般式ABO<sub>3</sub>のペロブスカイトを含むことができる。好適

50

なフィラーには、例えば、結晶性チタン酸バリウム( BT )、チタン酸バリウムストロンチウム( BST )、チタン酸ジルコン酸鉛( PZT )、チタン酸ランタン鉛、チタン酸ジルコン酸ランタン鉛( PLZT )、ニオブ酸マグネシウム鉛( PMN )、チタン酸カルシウム銅が含まれる。フィラーは、粉末形態とすることができます。好適な高 k フィラー相は、 Ferrero Corporation 、 Tam Ceramics 、富士チタン工業株式会社から得ることが可能なチタン酸バリウムである。

#### 【 0042 】

500より低い誘電率を有する機能相もまた、他の理由で適切とすることができます。そのような材料は、チタン、タンタル、ハフニウム、ニオブの酸化物を含むことができる。

#### 【 0043 】

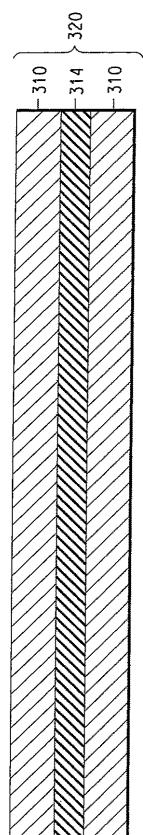

誘電層 312 が熱可塑性である、又は一部分だけ硬化される場合、2枚の被覆金属箔 300 を、図 5A に矢印によって示されている方向で、熱及び圧力の下で共に積層し、図 5B に示されている平面型コンデンサ構造 320 を形成することができます。

#### 【 0044 】

誘電層 312 が熱硬化性である場合、薄い接着層を誘電層 312 の一方又は両方に被着することができます。商用熱硬化性誘電体には、 E. I. du Pont de Nemours and Company から入手可能なポリイミドグレードが含まれる。

#### 【 0045 】

図 5B を参照すると、積層により誘電層 312 から单一の誘電層 314 が形成される。得られる誘電層 314 は、例えば、積層後 4 ~ 25 ミクロン程度の薄い層とすることができます。平面型コンデンサ積層薄板 320 は、銅 - 誘電層 - 銅積層薄板である。金属 - 誘電層 - 金属構造を形成するために使用することができる埋込みコンデンサ材料 / プロセスには、 Motorola にライセンスされた Vantico の Probelec 81CFP 、ならびに、日立化成工業株式会社の MCF6000E 、三井金属鉱業株式会社の MR - 600 、松下電工株式会社の R - 0880 、住友ベークライト株式会社の APL - 4000 など樹脂被覆箔製品が含まれる。

#### 【 0046 】

誘電層 314 を形成する他の方法は、フィラー入り( filled )、又はフィラーなしの( unfilled )熱可塑性ポリマーを箔 310 上に注型すること、及び第 2 の被覆されない箔をフィラー入り熱可塑性ポリマーに直接積層することができます。さらに他の作製方法は、誘電層 314 を单一の膜として別々に形成し、熱と圧力を使用して、第 1 の金属箔 310 及び第 2 の金属箔 310 に積層することを含んでいる。さらに他の作製方法は、誘電層 314 を单一の膜として別々に形成し、金属のシード層を前記別々に形成された誘電層の両側上にスパッタし、次いで、無電解又は電解めっき技術を使用して追加の金属をシード層上にめっきすることを含んでいる。好適な平面型コンデンサ積層薄板には、 E. I. du Pont de Nemours and Company の Interra (商標) HK04 シリーズ、 E. I. duPont de Nemours and Company の Interra (商標) HK11 シリーズ、 Sanmina によってライセンスを受けた積層薄板業者の BC - 2000 及び BC - 1000 、 Oak - Mitsui Technologies の FaradFlex シリーズ、 Rohm and Haas Electronic Materials の InSite (商標) 埋込みコンデンサシリーズ、 Gould Electronics の TCC (商標) 、 3M の C - Ply が含まれる。

#### 【 0047 】

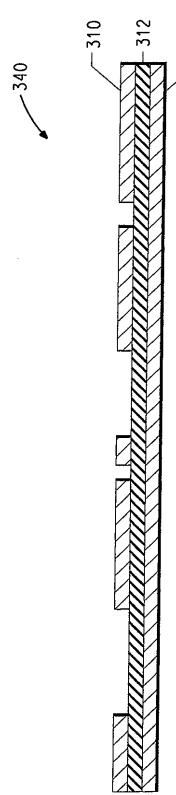

図 6A 及び図 6B は、本発明による電力コアデバイスを作製するための平面型コンデンサ積層薄板の初期段階を示す図で、電力コアデバイスを作製するための平面型コンデンサ積層薄板の側面図である。

#### 【 0048 】

また、図 6A は、図 5B に示した平面型コンデンサ積層薄板の側面図である。ここでは、( 図 6A には示されていない ) フォトレジストが金属箔 310 のそれぞれに被着される

。しかし、箔310の一方だけエッティングされるように、フォトレジストの一方だけがイメージング及び現像される。次いで、残りのフォトレジストすべてが、標準的なプリント配線板処理条件を使用して剥離される。好適なフォトレジストの一例は、E. I. du Pont de Nemours and Company から入手可能なRiston (登録商標) フォトレジストであろう。

【0049】

図6Bは、得られるエッティング済みの平面型コンデンサ積層薄板340の側面図である。ここでは、エッティングによって金属箔310の一部分が除去された一方の側を示し、一方、他方の金属箔310は元のままである。

【0050】

図7は、本発明による電力コアデバイスの第1段階の立断面図である。厚膜の、箔上で形成された個別化コンデンサ240を含む箔210が、平面型コンデンサ層340に積層されている。箔上コンデンサ構造を裏返し、箔の構成部品面を平面型コンデンサ積層薄板340のエッティング済み側に積層し、図7に示されている電力コアデバイスのサブパートを形成することができる。他の方法として、箔上コンデンサ構造の箔側を平面型コンデンサ積層薄板のエッティング済み側に積層することができる。積層は、例えば、標準的なプリント配線板プロセスにおいてFR4エポキシプリプレグ(epoxy preprag)360を使用して実行することができる。本実施形態では、エポキシプリプレグタイプ106を使用することができる。好適な積層条件は、28インチHg(94.82kPa)に真空引きされた(evacuated)真空チャンバ内で、185、208psig(1434.11kPa)、1時間とすることができます。シリコンゴムプレスピッド、及び滑らかなPTFEで充填されたガラスリリースシートを箔210及び310と接触させ、エポキシで積層薄板が共に接着するのを防止することができる。誘電プリプレグ及び積層材料は、例えば、標準的なエポキシ、高Tgエポキシ、ポリイミド、ポリテトラフルオロエチレン、シアン酸エステル樹脂、フィラー入り樹脂系、BTエポキシ、ならびに、絶縁をもたらす他の樹脂及び積層薄板など、任意のタイプの誘電材料とすることができます。リリースシートを箔と接触させ、回路層間で、エポキシで積層薄板が共に接着するのを防止することができる。得られるサブパート400は、一方の側上の箔210と他方の側上の箔310によってカプセル化される。

【0051】

電力コアの他の設計は、個別化コンデンサ層の構成部品側をパターン形成された平面型コンデンサ積層薄板まで積層することを含むことができる。そのような方法は、適切な層を接続するために、異なるエッティングパターン形成及びバイア形成を必要とすることになる。これらなど他の設計は、同じ設計要件を達成することができる。

【0052】

代替のエッティングパターンを、上述した電力コアデバイスの実施形態(すなわち、フェースダウン)と共に使用し、同様の電気機能を生み出すこともできる。

【0053】

図8は、本発明による電力コアデバイスの第2段階の立断面図である。積層後に、箔上で形成されたコンデンサ箔210及び平面型コンデンサ箔310にフォトレジストが被着される。標準的なプリント配線板処理条件を使用して、そのフォトレジストがイメージング、現像され、金属箔がエッティングされ、フォトレジストが剥離される。エッティングにより、箔210内でトレンチ265が生成され、第1の電極230と箔210との電気的な接触が断ち切られ、箔210から第2の電極270が作製されている。任意の関連する回路もまた、箔210から作成される。また、エッティングにより、平面型コンデンサ箔310上で、電極280と、関連する回路とが生成される。

【0054】

電力コアは、層を積層する他のシーケンス、例えば、最初に図6に示されている平面型コンデンサ積層薄板340のイメージング済みの側を他のプリント配線板層に積層し、イメージングされていない箔310にフォトレジストを被着し、箔をエッティングし、フォト

10

20

30

40

50

レジストを剥離し、次いで、埋込み個別化コンデンサ層を平面型コンデンサ積層薄板に積層することによって形成することができる。

【0055】

図9乃至図15は、電力コアデバイスの最終段階となる図8の様々な立断面図である。平面型コンデンサ積層薄板340と埋込み個別化コンデンサ240とを備えた電力コアデバイス500は、「電力コアパッケージ」と呼ばれる複数のパッケージ内に組み込むことができる。電力コアパッケージは、プリント配線板、ICパッケージ、モジュール、インターポーラなどとすることができます。

【0056】

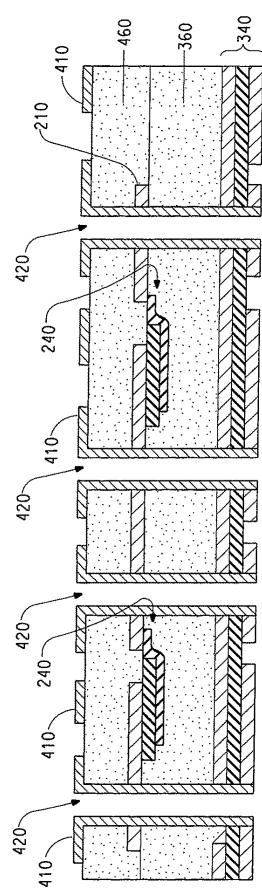

図9には、追加のプリプレグ層と金属層が電力コアに積層された電力コアデバイスの立断面図で、追加のプリプレグ層460と金属層410が電力コアに積層された電力コアデバイス500が示されている。さらに、穿設されためっきスルーホールバイア420が形成されている。このスルーホールバイア420は、メタライズされ、導電ペーストもしくはインクで、又は非導電性の材料で充填することができる。

【0057】

図10は、誘電膜の「ビルドアップ」層が電力コアに積層された電力コアデバイスの立断面図で、対称的な(平衡)スタックアップ電力コアデバイスの立断面図を示している。電力コアデバイスのこの実施形態は、反りの回避など機械的な考慮すべき点により保証される場合、使用することができる。これは、電力コアデバイスが複数の埋込み個別化コンデンサ層と複数の平面型コンデンサ層とを備えた本発明の一実施形態を示している。

【0058】

図11は、誘電膜の、組み合わせられた「ビルドアップ」層が電力コアに被着された電力コアデバイスの立断面図で、誘電膜520の、組み合わせられた「ビルドアップ」層が電力コアに被着された(典型的には、積層された)電力コアデバイスを示している。ビルドアップ層は、電力コアの周りで対称にも非対称にも構成することができる。ビルドアップ層は、誘電膜、(スピンドルコート又はカーテンコートされた)液体、又は(例えば、銅箔など)金属の層上で被覆された樹脂として、あるいは、強化プリプレグ、例えばBステージ樹脂として被着(積層)することができる。強化は、織布又は不織布、無機(例えば、ガラス)又は有機(例えば、アラミド繊維)とすることができます。

【0059】

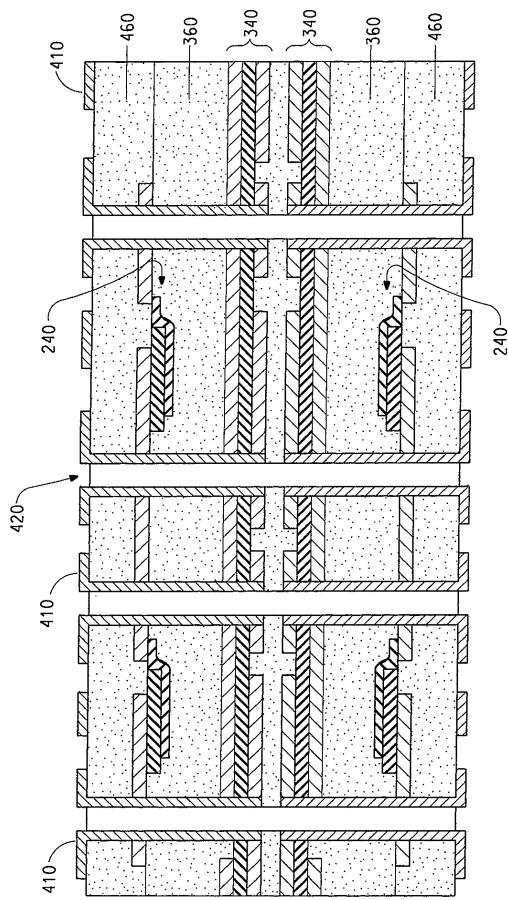

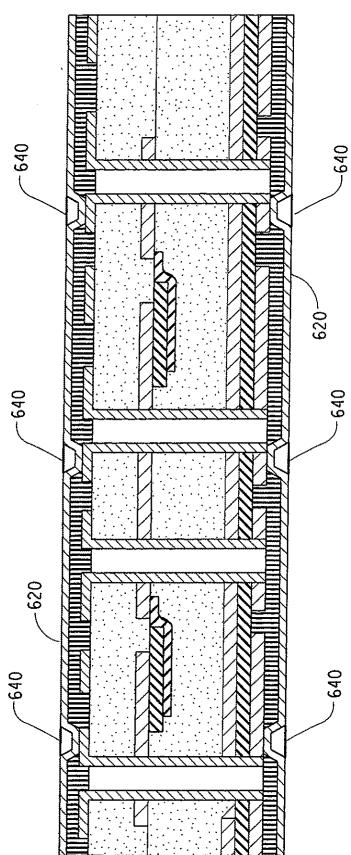

図12は、ビルドアップ層の表面上の、メタライズされたマイクロバイア(ブラインドバイア)接続及び回路を含む追加の「ビルドアップ」層を有する電力コアデバイスの立断面図である。

【0060】

マイクロバイア640は、レーザ穿孔によって、又はフォトリソグラフィによって、又は深さが制御された機械穿孔によって形成することができる。ビルドアップ層の表面及びマイクロバイアホール壁の初期メタライゼーションは、金属シード層620、例えば、無電解銅を堆積することによって行われる。シード層堆積は、表面上で堆積された触媒、例えば、本実施形態ではパラジウム、あるいは、ビルドアップ層全体にわたって分散された触媒又は金属前駆体によって活性化することができる。他の方法として、ビルドアップ層は、マイクロバイア穿設後に金属シード層が堆積される金属の層(銅箔)によって覆うことができる。

【0061】

図13は、ビルドアップ層の表面上のパターン形成済み導体を備えた電力コアデバイスの立断面図である。導体パターン形成は、ビルドアップ層を覆う、連続する金属カバーから始めて、セミアディティブプロセス(SAP)、又は「テントアンドエッチ(tent & etch)」プロセスを用いて、あるいはパターンめっきによって、あるいは修正されたパネルめっき/テントアンドエッチプロセスによって行うことができる。図13には、ビルドアップ層の表面上のパターン形成済み導体660が示されている。

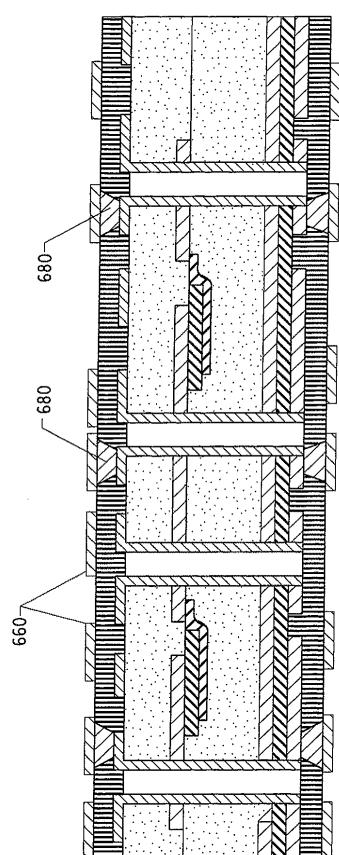

【0062】

10

20

30

40

50

マイクロバイア 640 は、電気めっきプロセス中にめっき銅 680 で充填する（めっきシャット）ことも、導電インク又はペーストで充填することも、非導電性の材料で充填することも、第 1 の誘電ビルドアップ層の上端上に被着される第 2 の誘電ビルドアップ層によって充填されるように未充填のままとすることもできる。

【0063】

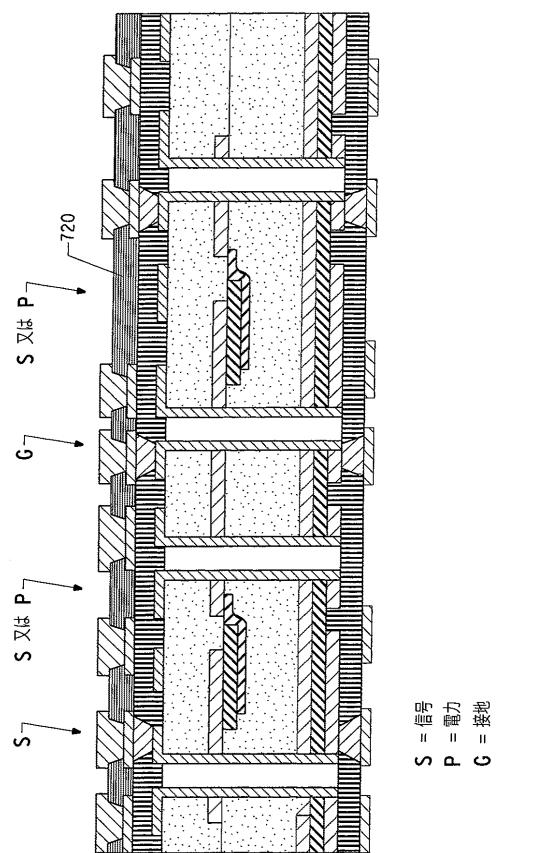

図 14 は、ビルドアップ層の表面上のパターン形成済み導体と、同様の形で形成、メタライズ、パターン形成された後続のビルドアップ層とを備えた電力コアデバイスの立断面図である。さらに図 14 は、平面型コンデンサ層 720 をビルドアップ誘電体内に組み込むことができることを示している。マイクロバイアを下にあるマイクロバイアの位置に対して積み重ねることができ、あるいは、それらを互い違いにすることができる。積み重ねられたバイアは、金属で充填することを必要とする。次いで、パッケージは、高温はんだ付けステップでフリップチップのバンプに接続し、より低い温度のはんだ付けステップで、はんだ継手を介してプリント配線板に接続することができる。導電性の、典型的には銅のフィーチャは、X-Y 軸において導体を、また Z 軸においてバイアを介して、はんだ継手に対する連続的な接続を形成する。

【0064】

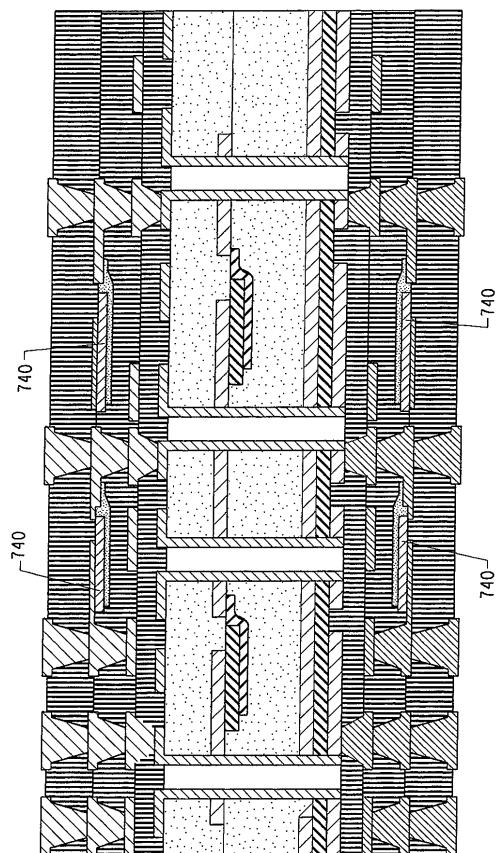

図 15 は、個別化コンデンサがビルドアップ誘電体層内に組み込まれた電力コアデバイスの立断面図で、個別化コンデンサ 740 もまた、ビルドアップ誘電体層内に組み込まれている。

【0065】

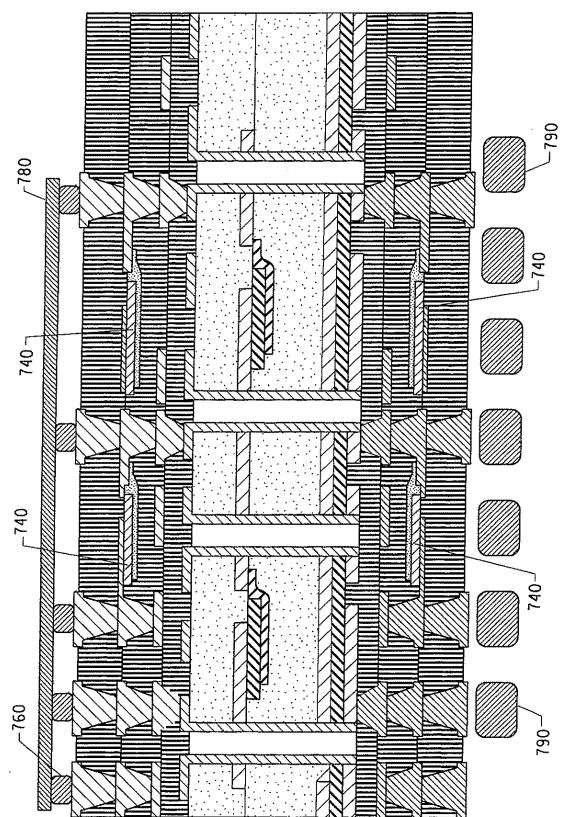

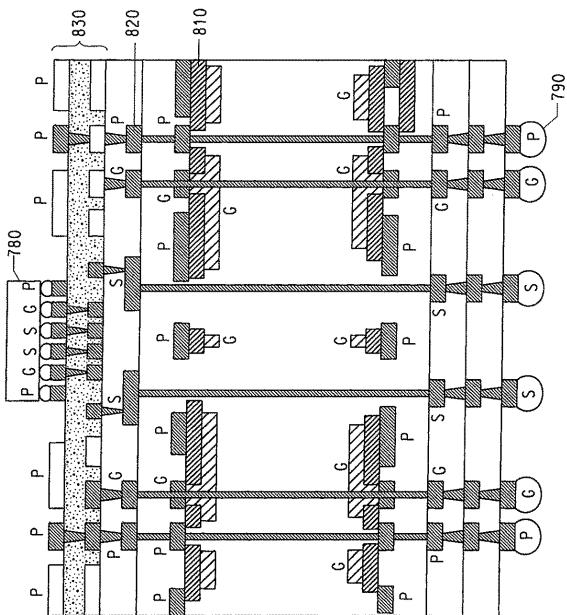

図 16 は、電力コアが、フリップチップのバンプに接続され、はんだ継手を介してプリント配線板に接続された電力コアデバイスの立断面図である。電力コアデバイスが、高温はんだ付けステップでフリップチップ 780 のバンプ 760 に接続され、より低い温度のはんだ付けステップで、はんだ継手 790 を介してプリント配線板に接続された、電力コアデバイスを示している。

【0066】

また、図 16 には、半導体デバイス、例えば、フリップチップ 780 の少なくとも 1 つの端子に対する（第 1 及び第 2 の電極を有する）埋込み個別化コンデンサの接続関係が示されている。この半導体デバイスは、集積回路とすることができます。

【0067】

図 17 は、電力コアの平面型コンデンサ層が、フリップチップボールグリッドアレイ構造の上端層を形成するようにビルドアップマイクロバイア膜層として形成される電力コアデバイスの立断面図である。埋込み個別化コンデンサ 810 は、電力コアとして平面型コンデンサ層 840 に並列で接続され、平面型コンデンサ層 840 は、ビルドアップマイクロバイア膜層として形成され、フリップチップボールグリッドアレイ構造の上端層を形成する。電力コアデバイスのこの実施形態は、平面型コンデンサの誘電体を作製するために、セラミックで充填されたポリマー膜 830 を使用することができます。そのポリマー膜 830 は、順次ビルドプロセスの一部として、下にあるマイクロバイアビルドアップ層上で積層することができます。下にある層は、平面型コンデンサの 1 つの電極として機能することができる金属の部分（典型的には銅）を有する。ポリマー膜 830 の積層後に、メタライゼーションがポリマー膜 830 上に形成される。具体的には、マイクロバイアとメタライゼーションラインが形成され、集積回路の信号端子及び電力 / 接地端子の経路設定を可能にする。その構造は又はんだバンプを介して集積回路を取り付けることができるパッドを有する。さらに、上端電極が形成され、平面型コンデンサ構造を完成する。この平面型コンデンサ構造は、適切な電力 / 接地フィーチャ 820 に電気的に接続されている。

【0068】

本発明の電力コアデバイスは、少なくとも 1 つの信号層を介して相互接続される電力コアを備えている。この電力デバイスは複数の信号層を備えることができ、この信号層は、導電バイアを介して接続されている。

【0069】

10

20

30

40

50

各層が個々に構築され、次いで1つのステップで積層される垂直相互接続（バイアが充填されたバンプ、印刷バンプ、エッティングバンプ、めっきバンプ）の各例を、本発明において使用することができる。埋込み平面型コンデンサと埋込みディスクリート（discrete）コンデンサの組合せもまた、いわゆる「コアなし／積重ねバイアパッケージ」に適用可能である。1つのそのような例は、（松下を介して入手可能な）ALIVH（Any Layer Interstitial Via Hole）プロセスである。ALIVHプロセスはまた、平面型コンデンサ及びディスクリートコンデンサを組み込むことができる。別のそのような積重ねバイアプロセスは、平面型コンデンサ及びディスクリートコンデンサを同様の形で組み込むことができる（株式会社東芝を介して入手可能な）B<sup>2</sup>intプロセス（登録商標）である。他の各例には、NMBI（Neo Manhattan Bump Interconnection）（株式会社ノース）、及びPALAP（patterned prepreg lay-up process）（株式会社デンソー）が含まれる。

10

20

30

40

50

## 【0070】

本発明の電力コアデバイスは、インターポーザ、プリント配線板、マルチチップモジュール、エリアアレイパッケージ、システムオンパッケージ、システムインパッケージなどから選択することができる。

## 【実施例】

## 【0071】

平面型コンデンサ積層薄板とディスクリート埋込みセラミックコンデンサとを含む構造を設計してテストした。平面型コンデンサ積層薄板は配電平面を形成し、埋込みコンデンサは、2つの内部金属層上で配置するように設計された。3つの異なるコンデンサの設計、すなわち、タイプA、タイプB、タイプCがあった。各タイプについて、有効コンデンササイズ（面積）1mm<sup>2</sup>、4mm<sup>2</sup>、9mm<sup>2</sup>を有する複数のコンデンサが、2つの内部金属層のそれぞれに配置された。コンデンサの設計は、箔電極の相対位置及びサイズ、誘電体のサイズ、ならびにスクリーン印刷銅電極のサイズが異なっていた。さらに、2枚の銅箔電極を絶縁するクリアランス（間隙）の設計が異なり、また、埋込みコンデンサを、上方の次の金属層に接続するバイアの位置及び数が異なっていた。例えば、9mm<sup>2</sup>サイズコンデンサでは、タイプA設計は4個のバイア接続を扱い、タイプBは28個のバイアを有し、タイプCは52個のバイアを有した。3つのタイプすべてについて、スクリーン印刷導体がコンデンサの一方の電極を形成し、誘電体によってスクリーン印刷導体から分離された箔が他方のコンデンサ電極として機能した。

## 【0072】

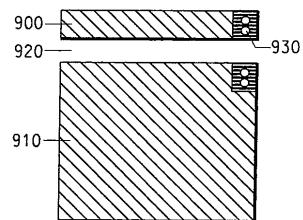

図18は、箔側から見たタイプAのディスクリートコンデンサを示す図である。このタイプAのディスクリートコンデンサの設計は、箔側から見たとき、方形フォームファクタを有し、第1の箔電極900が、コンデンサの幅を跨いで延びるスクリーン印刷導体に接続されていた。この箔電極900は、他方のコンデンサ電極として機能する第2の箔電極910から250ミクロン間隙920によって分離されていた。この間隙920は、コンデンサの幅を跨いで延びていた。この第2の箔電極910は、コンデンサ長の約4/5の長さを有するコンデンサの幅を跨いで延びていた。直径150ミクロンのバイア接続930が、次の金属層に対して、コンデンサの上方で形成され、箔側から見たとき、2つの電極のそれぞれの右上隅部に配置された。すべてのサイズについて、各電極内で2つのバイアが使用された。

## 【0073】

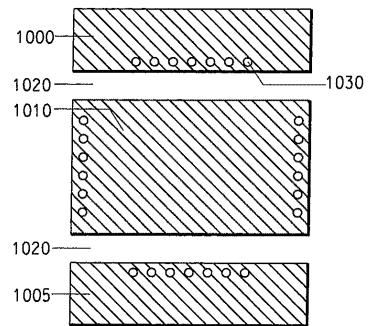

図19は、箔側から見たタイプBのディスクリートコンデンサを示す図である。このタイプBのディスクリートコンデンサの設計は、箔側から見たとき、方形フォームファクタを有し、2つの第1の箔電極1000,1005がスクリーン印刷導体に接続されていた。各電極は、コンデンサの上端及び底部でコンデンサの幅を跨いで延び、それぞれ長さがコンデンサの長さの1/5であった。これらの電極は、他方のコンデンサ電極として機能する第2の箔電極1010から、コンデンサの幅を跨いで延びる250ミクロン間隙10

20によって分離されていた。この第2の電極1010は、長さがコンデンサの長さの3/5よりわずかに短かった。直径150ミクロンのバイア接続1030が、次の金属層に對して、コンデンサの上方で形成され、コンデンサの上端及び底部でコンデンサ電極の幅を跨いで1列で均一に配置され、スクリーン印刷導体に接続していた。コンデンサの第2の電極は、コンデンサの各側の長さに沿って、1列のバイアを有していた。 $9\text{ mm}^2$  サイズについては、28個のバイアが使用された。

#### 【0074】

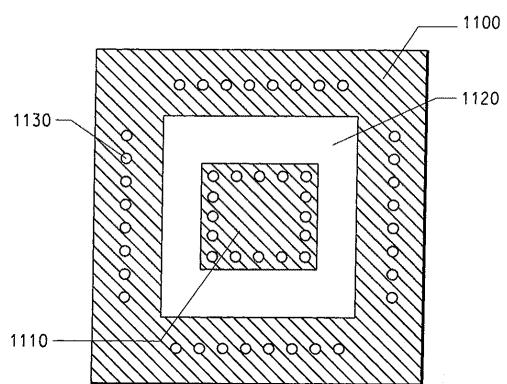

図20は、箔側から見たタイプCのディスクリートコンデンサを示す図である。このタイプCのディスクリートコンデンサの設計は、箔側から見たとき、方形フォームファクタを有していた。第1の箔電極1100は、スクリーン印刷導体に接続し、第2のコンデンサ電極1110の周りで、方形の「絵画用額縁」のようなフィーチャを形成した。第2のコンデンサ(箔)電極1100もまた方形であり、連続する250ミクロン間隙1120によって、周囲の第1の箔電極1100から分離されていた。次の金属層に対する、コンデンサの上方の直径150ミクロンのバイア接続1130が、スクリーン印刷導体に接続された第1のコンデンサ(箔)電極1100の4つの側すべてに均一に配置され、 $9\text{ mm}^2$  サイズについて合計32個のバイアであった。コンデンサの第2の電極は、 $9\text{ mm}^2$  サイズについて20個のバイアを有し、電極の周部の周りで均一に配置された。

#### 【0075】

個々のコンデンサの電気的なパラメータ(キャパシタンス、抵抗、インダクタンス)が、バイア接続を有する場合と有さない場合で測定された。個々のコンデンサについてインピーダンス対周波数応答が測定され、その測定された応答がシミュレーションモデルによって生成された曲線と比較された。次いで、そのモデルを使用し、埋込みコンデンサアレイについて従来の、ならびに最新の設計規則を適用して、いくつかのコンデンサアレイのインピーダンスをシミュレーションした。

#### 【0076】

##### <結果>

バイア接続を有さない、1、4、 $9\text{ mm}^2$  サイズのタイプA、B、Cコンデンサについてのキャパシタンス、抵抗、インダクタンスは、ベクトルネットワークアナライザ、及びSOLT較正を使用する2ポート測定法を使用して測定された。500ミクロン間隔を有する同軸スタイルの接地-信号プローブを使用し、コンデンサSパラメータを測定し、そのコンデンサの実数インピーダンス成分と虚数インピーダンス成分が計算された。表1(バイアなし)及び表2(バイアあり)において、コンデンサ1, 4, 9は、タイプA設計のものであり、コンデンサ2, 5, 8は、タイプB設計のものであり、コンデンサ3, 6, 7は、タイプC設計のものである。コンデンサ1からコンデンサ3は、サイズが $1\text{ mm} \times 1\text{ m}$ であり、コンデンサ4からコンデンサ6は、サイズが $2\text{ mm} \times 2\text{ mm}$ であり、コンデンサ7からコンデンサ9は、サイズが $3\text{ mm} \times 3\text{ mm}$ であった。

#### 【0077】

10

20

30

## 【表1】

表1 バイアなし

|        | キャパシタンス | ESR (抵抗) | インダクタンス  |

|--------|---------|----------|----------|

| コンデンサ1 | 1.26 nF | 36 mΩ    | 48 pH    |

| コンデンサ2 | 1.17 nF | 50 mΩ    | 47.3 pH  |

| コンデンサ3 | 1.63 nF | 34 mΩ    | 41.6 pH  |

| コンデンサ4 | 5.15 nF | 8 mΩ     | 33.7 pH  |

| コンデンサ5 | 5.16 nF | 10.7 mΩ  | 35.07 pH |

| コンデンサ6 | 6.16 nF | 10.7 mΩ  | 35.48 pH |

| コンデンサ9 | 10.6 nF | 7.9 mΩ   | 35.44 pH |

| コンデンサ8 | 11 nF   | 10 mΩ    | 40 pH    |

| コンデンサ7 | 13.6 nF | 8.9 mΩ   | 33.8 pH  |

10

20

30

## 【0078】

これは、予想されたように、キャパシタンスがサイズと共に増大し、設計タイプと共にあまり変わらないことを示す。バイア接続を有さない場合、3つのタイプすべてのインダクタンス値は、かなり似ている。バイア接続を有する場合、タイプA、B、Cのコンデンサについての同じパラメータは、同じ機器及び方法を使用して測定された。

## 【0079】

## 【表2】

表2 バイアあり

|        | キャパシタンス  | ESR (抵抗) | インダクタンス  |

|--------|----------|----------|----------|

| コンデンサ1 | 10.5 nF  | 89 mΩ    | 382 pH   |

| コンデンサ2 | 1.20 nF  | 86.5 mΩ  | 125 pH   |

| コンデンサ3 | 1.7 nF   | 37.1 mΩ  | 74.6 pH  |

| コンデンサ4 | 6.49 nF  | 50.1 mΩ  | 308 pH   |

| コンデンサ5 | 5.28 nF  | 128 mΩ   | 120.5 pH |

| コンデンサ6 | 6.6 nF   | 20.9 mΩ  | 65.17 pH |

| コンデンサ9 | 15.3 nF  | 100 mΩ   | 218.2 pH |

| コンデンサ8 | 13.26 nF | 15.4 mΩ  | 115 pH   |

| コンデンサ7 | 13.2 nF  | 17.3 mΩ  | 79.39 pH |

## 【0080】

データは、コンデンサタイプ、及びバイアの数とその位置が、コンデンサの抵抗及びインダクタンスに大きく影響を及ぼすことを示した。

## 【0081】

バイア接続を有する、また有さない2つのタイプCコンデンサについてのインピーダンス対周波数応答が測定された。上記でリストされているコンデンサ3について、結果は、バイア接続を有する場合、有さない場合両方の条件について約30ミリオームのインピーダンスと、バイアを有さないコンデンサについての約900MHzからバイアを有する場合の約500MHzへの、バイア接続による共振周波数シフトとを示した。バイアを有さないコンデンサ6について、結果は、共振周波数約350MHzで約10ミリオームのインピーダンスと、バイアを有する場合の条件について、共振周波数約200MHzで約20ミリオームのインピーダンスとを示した。

## 【0082】

サイズの異なる2つのコンデンサタイプについて、測定された周波数応答と、モデル化された応答との良好な相関が観察された。

## 【0083】

40

50

スルーホールインダクタンスの寄与がある場合とない場合で、平面型コンデンサインピーダンス対平面型コンデンサについての周波数応答のシミュレーションが実行された。スルーホール相互接続の面積は、総面積の約1%であった。スルーホールインダクタンスがない1つの平面型コンデンサの周波数応答は、共振周波数約300MHzでインピーダンスが約80ミリオームであり、一方、スルーホールインダクタンスがある2つの平面型コンデンサを有する場合の周波数応答は、共振周波数約250MHzでインピーダンスが約30ミリオームであった。

#### 【0084】

様々な個々のコンデンサの測定結果及びモデル化結果に基づいて、64個のディスクリート埋込みコンデンサのアレイにコンデンサ間の最小間隔500μmの従来の設計規則を適用したものについて、モデル化及びシミュレーションが実行された。コンデンサアレイのインピーダンス応答によりかなり均一な低インピーダンス値が生み出されるように、サイズが異なる、また共振周波数が異なるコンデンサが選択された。100MHzから1GHz範囲内で達成されたインピーダンスは、約40m未満であった。

10

#### 【0085】

1つの側当たり1.15から2.5mmでサイズ決めされたコンデンサのアレイについて、より要求の多い間隔設計規則を適用する測定結果及びモデル化結果に基づいて、0.7mのインピーダンスが100MHzから1GHz周波数範囲内で達成された。

#### 【0086】

電力平面から分離された、比誘電率3.8を有する38ミクロン厚基板上で経路設定された100本の結合されない伝送ラインについてのシミュレーションモデルが設計された。その伝送ラインは、10ミル(0.254mm)で離隔され、長さ15mm、幅2.82ミル(0.0716mm)であり、各ラインは、電力に対して、また接地平面に対して99オーム抵抗で終端された(50オームライン終端)。ある場合では、電力平面は、14ミクロン厚基板上で接地平面の反対側にあった。その基板は、比誘電率3.8、ロスタンジエント0.02を有する。別の場合では、電力平面は、比誘電率11、ロスタンジエント0.02を有する14ミクロン厚基板上で接地平面の反対側にあった。20ps立ち上がり/立ち下がり時間を有する、80psパルス幅を有する5GHz方形波ビットストリームを生成する出力ドライバを使用して100本の伝送ラインすべてを駆動し、中央に位置する伝送ラインの「アイ」パターン応答を得た。誘電率3.8を有する電力平面基板である第1の場合についてのアイパターンについて、得られるアイ開口高さは、2.4799ボルトであった。同じ条件と、誘電率11を有する電力平面基板とを用いた第2の場合についての応答では、アイ開口高さは、第1の場合に優る著しい改善である2.6929ボルトであった。伝送ライン間の間隔を3ミル(0.0762mm)に変更し、50の結合ライン対を得た。他の条件すべてを同じままとして、アイパターン応答を得た。誘電率3.8を有する電力平面基板であるこの第1の結合ラインの場合についてのアイパターンは、2.5297ボルトのアイ開口高さになった。同じ条件と、誘電率11を有する電力平面基板とを用いた第2の結合ラインの場合についての応答では、アイ開口高さは、第1の場合に優る改善である2.6813ボルトであった。より高い誘電率の電力平面基板も、やはりアイパターン応答が改善した。

20

30

40

#### 【0087】

同時スイッチングノイズ(SSN)の解析用の、平面型電力平面基板に加えてディスクリート減結合コンデンサを含む構成についてのシミュレーションモデルが構築された。このシミュレーションモデルは、電力平面から分離された、比誘電率3.8を有する38ミクロン厚基板上の50の結合伝送ライン対を有していた。その伝送ラインは、3ミル(0.0762mm)で離隔され、長さ15mm、幅2.82ミル(0.0716mm)であり、各ラインは、電力平面及び接地平面に対して99オーム抵抗で終端された(50オームライン終端)。いくつかの場合では、電力平面は、14ミクロン厚基板上で接地平面の反対側にあった。その基板は、比誘電率3.8、ロスタンジエント0.02を有する。他の場合では、電力平面は、比誘電率11、ロスタンジエント0.02を有する14ミクロン厚基板上で接地平面の反対側にあった。その基板は、比誘電率3.8、ロスタンジエント0.02を有する。

50

ン厚基板上で接地平面の反対側にあった。20 p s立ち上がり／立ち下がり時間有する、80 p sパルス幅有する5 GHz方形波ビットストリームを生成する出力ドライバを使用して100本の伝送ラインすべてを同時に駆動し、電力平面上で生成されたノイズ電圧を得た。SMTか埋込みディスクリートかというタイプとコンデンサの数における変化が解析された。コンデンサは、ドライバ部、又は伝送ラインの近端の領域内に位置していた。

#### 【0088】

ある場合では、50対の結合ライン（合計100本のライン）、すなわち25個のSMTコンデンサを有する構成が、伝送ラインのドライバ端部で、1ライン対置きに、ライン対1で開始し、次がライン対3、ライン対50で終わって配置された。平面型電力平面基板は、3.8の誘電率を有していた。各SMTコンデンサは、100nFのキャパシタンス、約205pHの等価直列インダクタンス（ESL）、100ミリオームの等価直列抵抗（ESR）を有していた。20 p s立ち上がり／立ち下がり時間有する、80 p sパルス幅有する5 GHz方形波ビットストリームを使用し、100本の伝送ラインすべてを同時に駆動し、電力平面上のノイズ電圧を測定した。これは、各コンデンサが1nFのキャパシタンス、約33pHの等価直列インダクタンス（ESL）、9ミリオームの等価直列抵抗（ESR）を有する埋込みディスクリートコンデンサについて再現された。この構成における平面型電力平面基板は、11の誘電率を有していた。誘電率3.8の平面型電力平面基板を用いた、25個のSMTコンデンサについての電力平面上の電圧変動には、約-0.1ボルトから+0.15ボルトのピーク間電圧変動があり、一方、誘電率11の平面型電力平面基板を用いた、25個の埋込みディスクリートコンデンサについての電力平面上の電圧変動には、約-0.05ボルトから+0.05ボルトの、電力平面上のピーク間電圧変動があった。出力ドライバの同時スイッチングによって生成された電力平面ノイズの著しい低減は、埋込み個別化コンデンサと、より高い誘電率の平面型電力平面基板の使用に起因していた。

#### 【0089】

埋込み個別化コンデンサ構成と等価のノイズ低減を実現するであろうSMTコンデンサの数を決定するために、追加のSMTコンデンサがSMTモデルに追加された。50個、75個、100個のSMTコンデンサがモデル化された。50個SMTコンデンサ構成は、あらゆるライン対のドライバ端部でコンデンサを配置することによって達成された。75個コンデンサ構成は、1つ置きのライン対のドライバ端部にそれぞれ位置するコンデンサの第2グループを追加することによって達成され、100個コンデンサ構成は、伝送ラインの第1の対から50番目の対までのドライバ端部でコンデンサの2×50アレイを生成するようにSMTコンデンサを追加することによって達成された。

#### 【0090】

50個のSMTコンデンサ及び誘電率3.8の平面型基板についての電力平面上の電圧変動には、約-0.12ボルトから+0.12ボルトの、電力平面上のピーク間電圧変動があった。75個のSMTコンデンサ及び誘電率3.8の平面型基板についての電力平面上の電圧変動には、約-0.1ボルトから+0.1ボルトの、電力平面上のピーク間電圧変動があった。100個のSMTコンデンサ及び誘電率3.8の平面型基板についての電力平面上の電圧変動には、約-0.075ボルトから+0.1ボルトの、電力平面上のピーク間電圧変動があった。4つのSMTコンデンサ構成すべてにおいて、出力ドライバの同時スイッチングの結果として、25個のコンデンサ及び誘電率11の電力平面を有する埋込みディスクリートコンデンサ構成より高い電力平面ノイズ、又は電圧変動が生じた。

#### 【図面の簡単な説明】

#### 【0091】

【図1】インピーダンス低減と電力減衰又はオーバーシュートを弱めるための典型的な従来のコンデンサを使用した回路構成図である。

【図2】インピーダンス低減と電力減衰又はオーバーシュートを弱めるために使用される従来の表面実装（SMT）コンデンサを有するプリント配線組立体の立断面図である。

10

20

30

40

50

【図3】本発明による電力コアデバイスの立断面図である。

【図4A】個別化コンデンサ構造を作製する第1段階を示す側面図である。

【図4B】個別化コンデンサ構造を作製する第2段階を示す側面図である。

【図4C】個別化コンデンサ構造を作製する第3段階を示す側面図である。

【図4D】個別化コンデンサ構造を作製する第4段階を示す側面図である。

【図4E】個別化コンデンサ構造を作製する第5段階を示す側面図である。

【図4F】図4Eに示した個別化コンデンサ構造の平面図である。

【図5A】平面型コンデンサ積層薄板の作製方法（第1段階）を説明するための側面図である。

【図5B】平面型コンデンサ積層薄板の作製方法（第2段階）を説明するための側面図である。

【図6A】本発明による電力コアデバイスを作製するための平面型コンデンサ積層薄板の初期段階を示す図（その1）である。

【図6B】本発明による電力コアデバイスを作製するための平面型コンデンサ積層薄板の初期段階を示す図（その2）である。

【図7】本発明による電力コアデバイスの第1段階の立断面図である。

【図8】本発明による電力コアデバイスの第2段階の立断面図である。

【図9】追加のプリプレグ層及び金属層が電力コアに積層された電力コアデバイスの立断面図である。

【図10】誘電膜の「ビルドアップ」層が電力コアに積層された電力コアデバイスの立断面図である。

【図11】誘電膜の、組み合わせられた「ビルドアップ」層が電力コアに被着された電力コアデバイスの立断面図である。

【図12】ビルドアップ層の表面上の、メタライズされたマイクロバイア（ブラインドバイア）接続及び回路を含む追加の「ビルドアップ」層を有する電力コアデバイスの立断面図である。

【図13】ビルドアップ層の表面上のパターン形成済み導体を備える電力コア構造の立断面図である。

【図14】ビルドアップ層の表面上のパターン形成済み導体と、同様の形で形成、メタライズ、パターン形成された後続のビルドアップ層とを備えた電力コアデバイスの立断面図である。

【図15】個別化コンデンサがビルドアップ誘電体層内に組み込まれた電力コアデバイスの立断面図である。

【図16】電力コアが、フリップチップのバンプに接続され、はんだ継手を介してプリント配線板に接続された電力コアデバイスの立断面図である。

【図17】電力コアの平面型コンデンサ層が、フリップチップボールグリッドアレイ構造の上端層を形成するようにビルドアップマイクロバイア膜層として形成される電力コアデバイスの立断面図である。

【図18】箔側から見たタイプAのディスクリートコンデンサを示す図である。

【図19】箔側から見たタイプBのディスクリートコンデンサを示す図である。

【図20】箔側から見たタイプCのディスクリートコンデンサを示す図である。

【符号の説明】

【0092】

2 電源

4, 6, 8 コンデンサ

10 I C デバイス

40 I C デバイス

41 ランド

44 はんだフィレット

50, 60 S M T コンデンサ

10

20

30

40

50

|                                     |                    |    |

|-------------------------------------|--------------------|----|

| 7 2 , 7 3 , 7 4 , 7 5               | 回路ライン              |    |

| 8 0 , 9 0 , 1 0 0 , 1 1 0           | バイア ( v i a ; ビア ) |    |

| 8 2                                 | バイアパッド             |    |

| 1 2 0 , 1 2 2                       | 導体平面               |    |

| 2 0 0                               | 個別化コンデンサ構造 ( 層 )   |    |

| 2 1 0                               | 金属箔                |    |

| 2 1 2                               | アンダープリント           |    |

| 2 2 0                               | 第 1 のコンデンサ誘電層      |    |

| 2 2 5                               | 第 2 のコンデンサ誘電層      |    |

| 2 2 8                               | 高 k 誘電体            | 10 |

| 2 3 0                               | 第 1 の電極            |    |

| 2 4 0                               | 個別化コンデンサ           |    |

| 2 6 5                               | トレンチ               |    |

| 2 7 0                               | 第 2 の電極            |    |

| 2 8 0                               | 電極                 |    |

| 3 0 0                               | 被覆金属箔              |    |

| 3 1 0                               | 金属箔                |    |

| 3 1 2                               | 誘電層                |    |

| 3 1 4                               | 単一の誘電層             |    |

| 3 2 0                               | 平面型コンデンサ構造         | 20 |

| 3 4 0                               | 平面型コンデンサ積層薄板       |    |

| 3 6 0                               | エポキシプレブルグ          |    |

| 4 0 0                               | 電力コアデバイスのサブパート     |    |

| 4 1 0                               | 金属層                |    |

| 4 2 0                               | めっきスルーホールバイア       |    |

| 4 6 0                               | 追加のプリブレグ層          |    |

| 5 0 0                               | 電力コアデバイス           |    |

| 5 2 0                               | 誘電膜                |    |

| 6 2 0                               | 金属シード層             |    |

| 6 4 0                               | マイクロバイア            | 30 |

| 6 6 0                               | パターン形成済み導体         |    |

| 6 8 0                               | めっき銅               |    |

| 7 2 0                               | 平面型コンデンサ層          |    |

| 7 4 0                               | 個別化コンデンサ           |    |

| 7 6 0                               | バンブ                |    |

| 7 8 0                               | フリップチップ            |    |

| 7 9 0                               | はんだ継手              |    |

| 8 1 0                               | 埋込み個別化コンデンサ        |    |

| 8 2 0                               | 電力 / 接地フィーチャ       |    |

| 8 3 0                               | ポリマー膜              | 40 |

| 8 4 0                               | 平面型コンデンサ構造         |    |

| 9 0 0 , 1 0 0 0 , 1 0 0 5 , 1 1 0 0 | 第 1 の箔電極           |    |

| 9 1 0 , 1 0 1 0 , 1 1 1 0           | 第 2 の箔電極           |    |

| 9 2 0 , 1 0 2 0 , 1 1 2 0           | 間隙                 |    |

| 9 3 0 , 1 0 3 0 , 1 1 3 0           | バイア接続              |    |

【図1】

【図2】

【図3】

【図4 A】

【図4B】

【図4C】

【図4D】

【図4E】

【図4F】

【図5A】

【図5B】

【図6A】

【図6B】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(72)発明者 ダニエル アーウィン エイミー ジュニア

アメリカ合衆国 27705 ノースカロライナ州 ダラム ミドルズバーロウ コート 6

(72)発明者 スーナク バネルジ

アメリカ合衆国 27513 ノースカロライナ州 カリー グッドウッド サークル 2222

(72)発明者 ウィリアム ジェイ・ボーランド

アメリカ合衆国 27513 ノースカロライナ州 カリー ターコイズ クリーク ドライブ

106

(72)発明者 デビッド ロス マクレガー

アメリカ合衆国 27539 ノースカロライナ州 エーベックス チャップリンシャー ウェイ

3618

(72)発明者 アッチガナル エヌ・スリーラム

アメリカ合衆国 27614 ノースカロライナ州 ローリー アベンズバーグ コート 300

9

(72)発明者 カール ハルトマン ディーツ

アメリカ合衆国 27613 ノースカロライナ州 ローリー ブロッサム ヒル コート 43

04

F ターム(参考) 4E351 AA01 AA03 AA04 AA07 BB03 BB30 BB31 BB33 BB49 CC11

CC22 DD04 DD19 DD21 DD43 DD52 GG07

5E346 AA12 AA15 AA43 CC04 CC05 CC09 CC10 CC16 CC32 CC37

CC55 DD02 DD12 DD32 DD44 EE01 FF01 FF04 FF07 GG15

GG17 GG18 GG19 GG22 GG25 GG28 HH02 HH06

【外國語明細書】

2006196886000001.pdf